Page 1

5

4

3

2

1

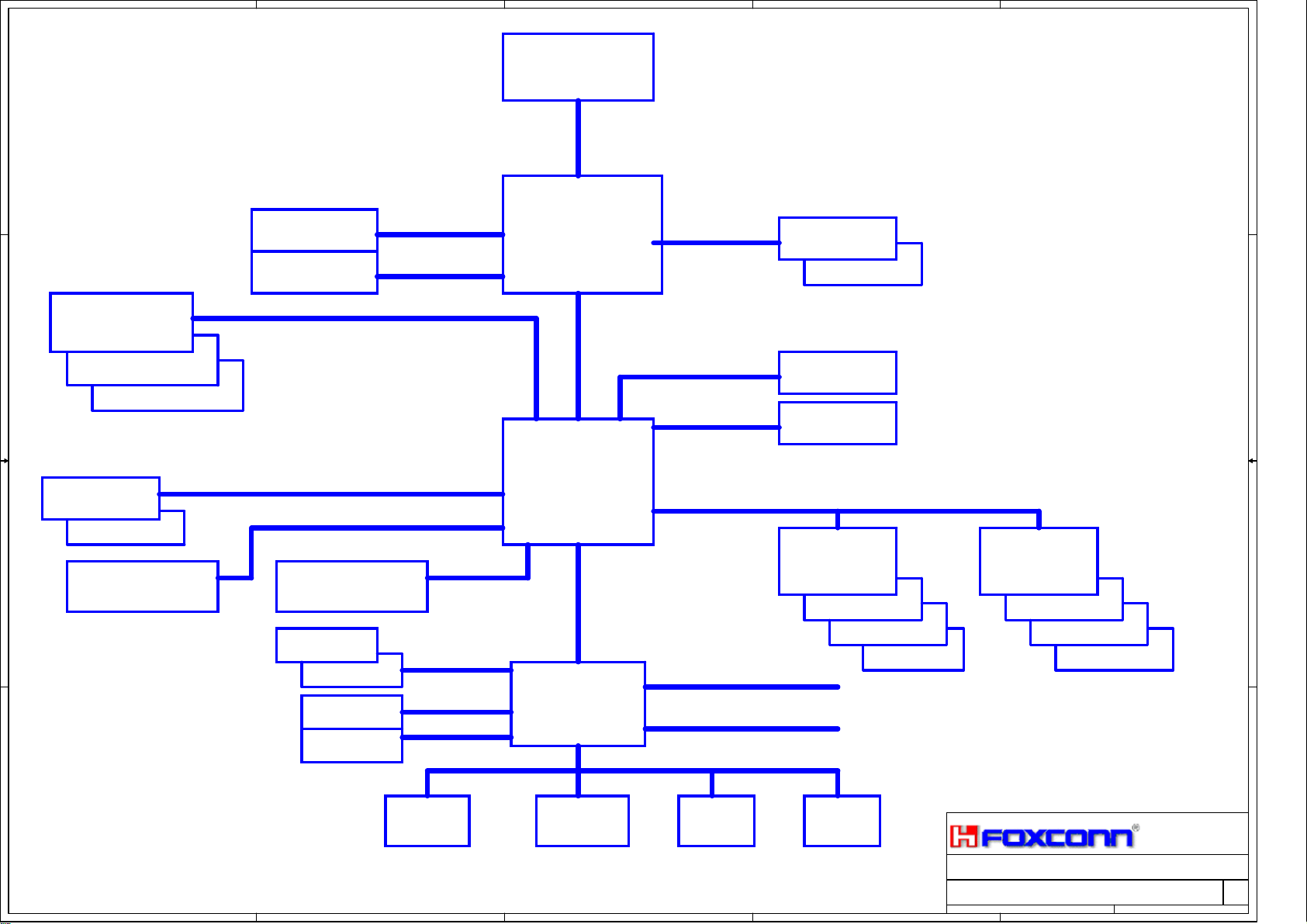

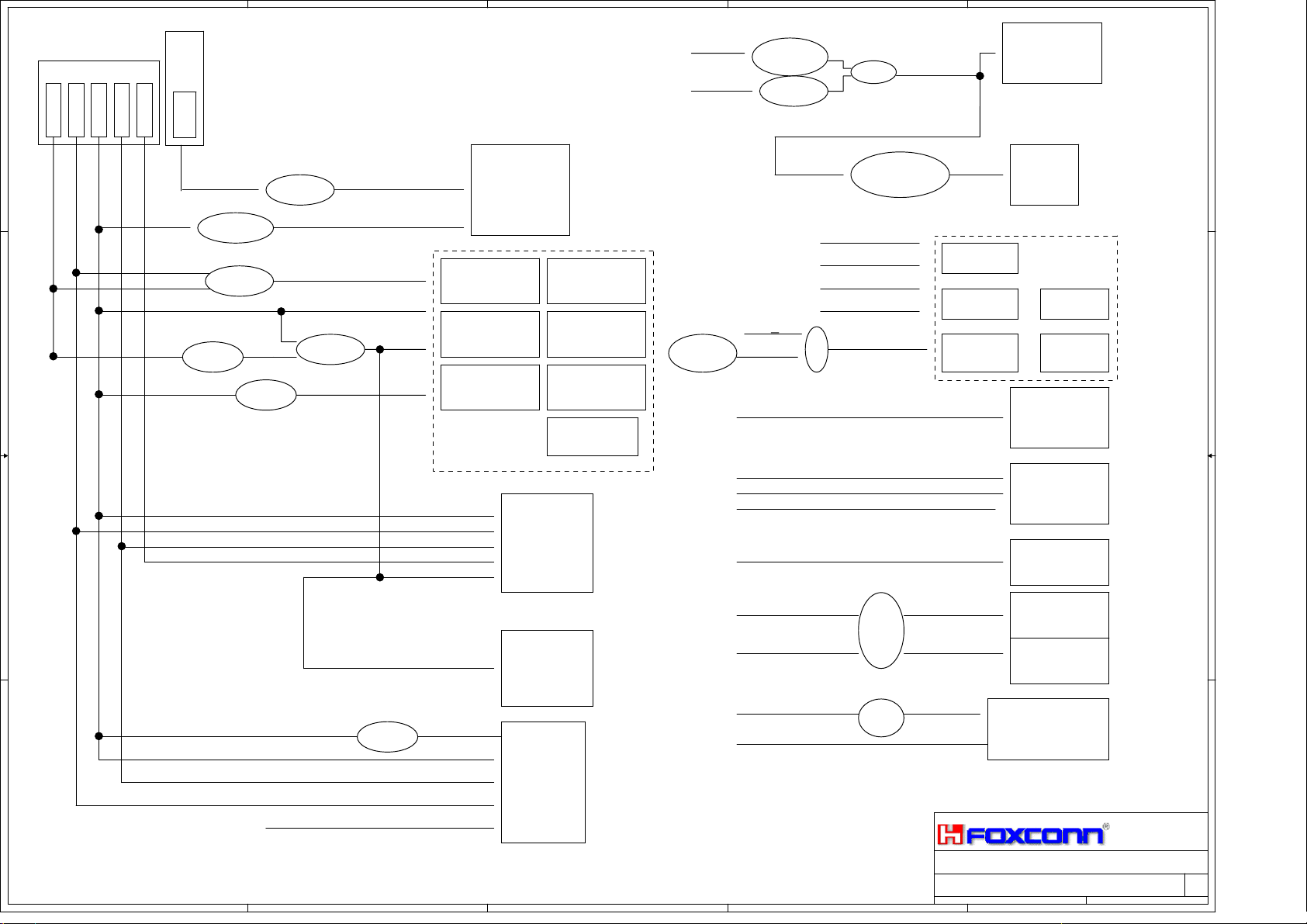

CPU-LGA775

Note:

D D

Do not include the schematic

when create netlist.

Host Bus

SiS661GX

PCI Slot 1

AGP SLOT

VGA

AGP BUS

AGP BUS

/661FX

/648FX/

648C

DDR SDRAM

DIMM1

DIMM2

C C

PCI Slot 2

MuTIOL 1G

LAN PHY

PCI Slot 3

AC'97

Audio Codec

SiS964/

IDE 1

IDE 2

B B

SATAX2

KEYBOARD

/MOUSE

FAN 1

FAN 2

SPI ROM

LPC

ROM

PS/2

FAN CONTROL

SPI Bus

LPC Bus

964L

LPC Bus

LPC Super I/O

Back Panel

VOLTAGE MONITOR

TEMPERATURE MONITOR

USB 0

USB 1

USB 2

USB 3

Front Panel

USB 4

USB 5

USB 6

USB 7

A A

IR

5

4

PARALLEL

3

COM

FLOPPY

TECHNOLOGY COPR.

TECHNOLOGY COPR.

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Topology

Topology

Topology

661M08

661M08

661M08

TECHNOLOGY COPR.

of

144Monday, August 01, 2005

of

144Monday, August 01, 2005

of

144Monday, August 01, 2005

1

A

A

A

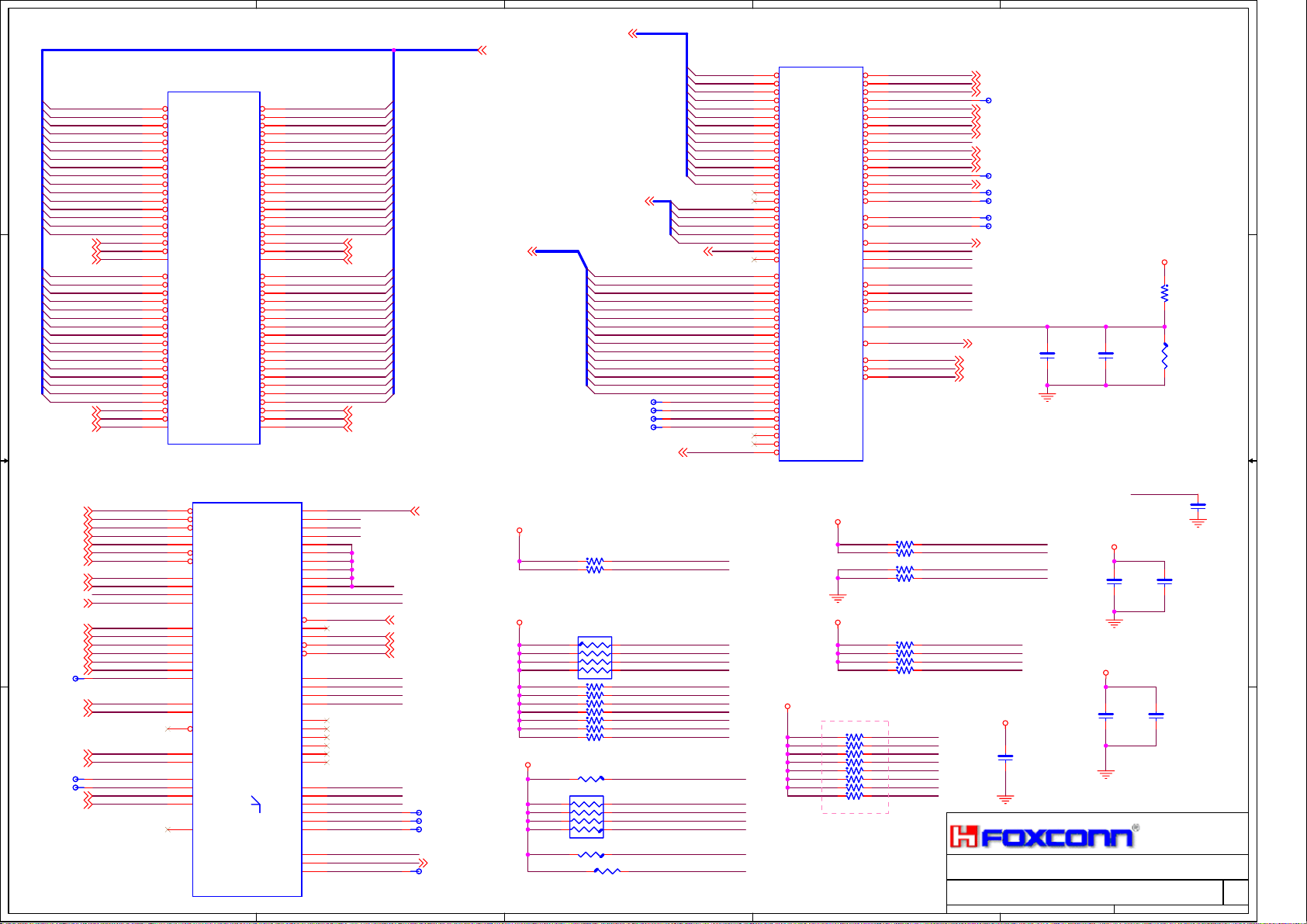

Page 2

5

4

3

2

1

Foxconn Precision Co. Inc.

661M08 Schematic

D D

Page Index

00. Index Page

01. Topology

02. Rest Map

03. Clock Distribution

04. Power Delivery Map

C C

05. LGA775-1

06. LGA775-2

07. Voltage regulator Down 10.1

08. Output CAP

09. 661FX-1 HOST & AGP

10. 661FX-2 DDR

11. 661FX Mutiol & VGA

12. 661FX Power

B B

13. 964/L-1 PCI/IDE/Link

14. 964/L-2 PC/MIL/CPU/GPIO

15. 964-3 USB/SATA

16. 964-4 Power

17. 952017/18AF Clock GEN

18. DDR Clock Buffer

19. AGP

20. VGA CON

A A

21. DIMM1 & DIMM2

22. DECOUPLE & EMI

23. Termination

24. PCI 1&2

25. PCI3

26. IDE CONN

27. USB & LAN PORT

28. SI/O_ITE8712F/JX

29. K/B & MS CONN

30. COM/PRT/GAME PORT

31. LPC/SPI BIOS_FLOPPY

32. FAN

33. 653/655 AC97 CODEC

34. AC97 I/O

35. LAN PHY AC131KML

36. Power BTN/RTC Batt

37. DDR 2.5V DDRVTT

38. Power CONN

39. SB3V, SB1.8V, VCC1.8V, VDDQ

40. TI1394(NA)

41. USB

42. Modification

43. Jumper Setting/Option Table

Fab.A

Data: 2005/06/28

FOXCONN PCEG

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Index Page

Index Page

Index Page

661M08

661M08

661M08

AB

AB

AB

144Monday, August 01, 2005

144Monday, August 01, 2005

144Monday, August 01, 2005

of

of

1

of

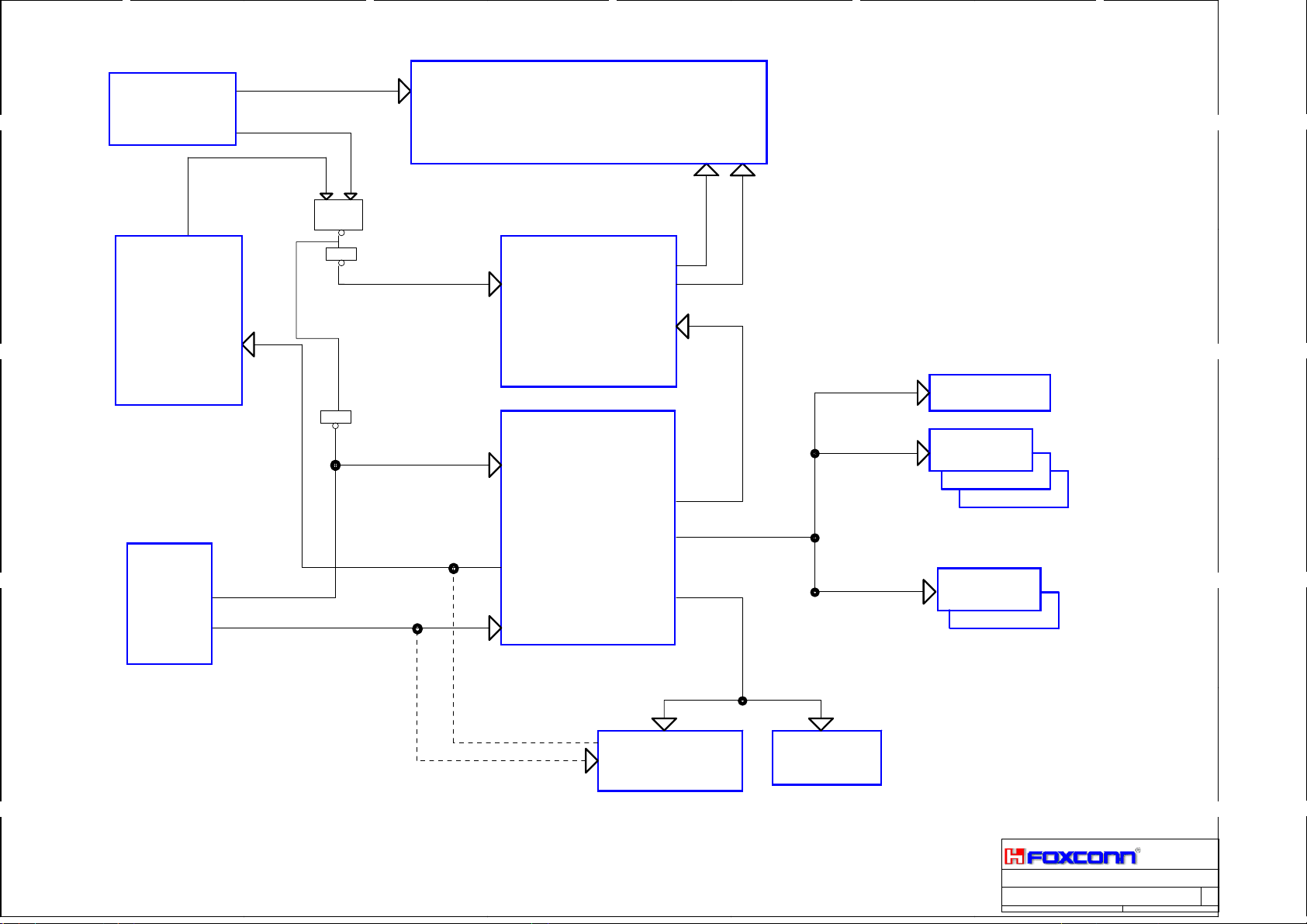

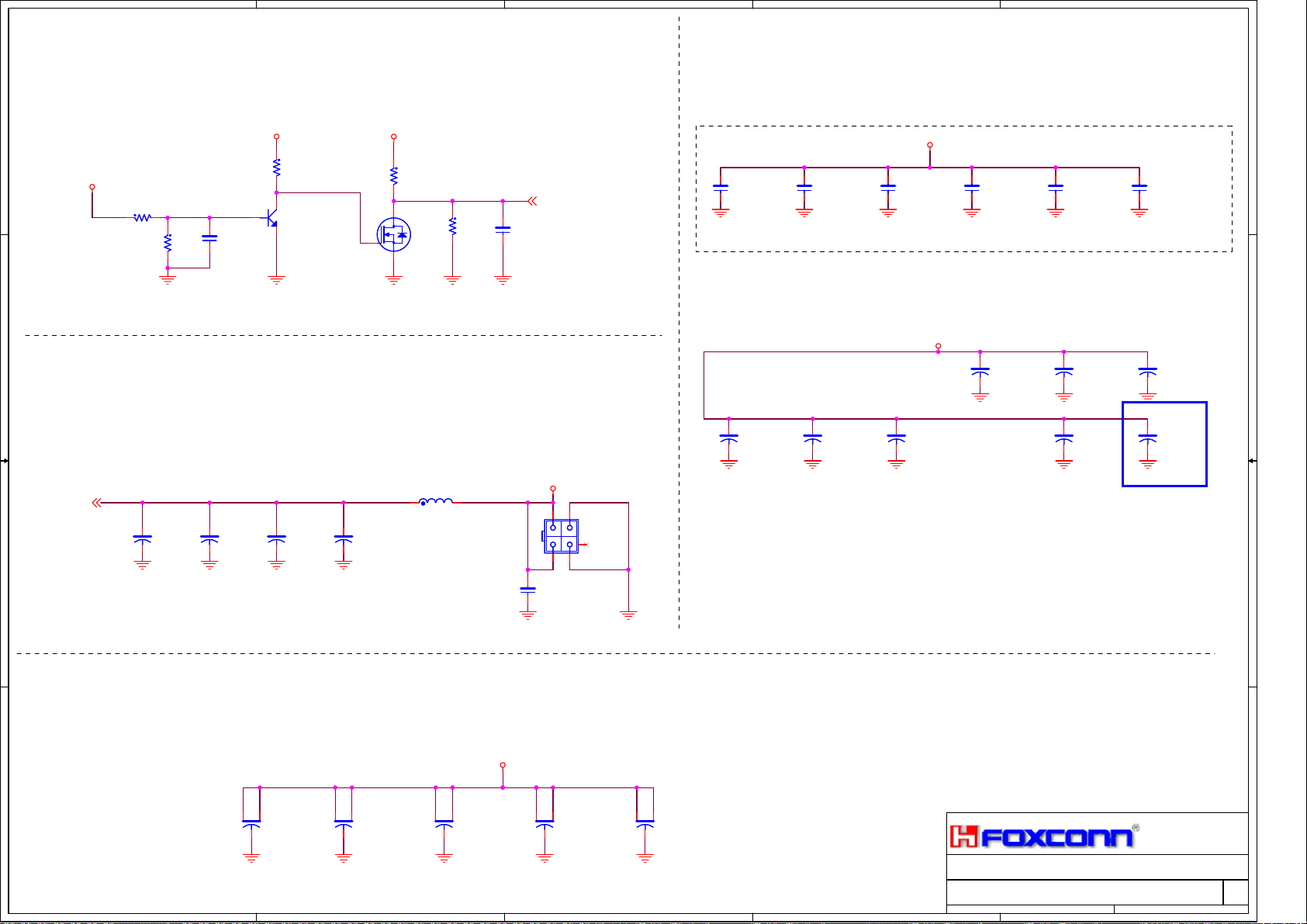

Page 3

5

4

3

2

1

VCCP

VCCP

Prescott

VRD10.1/VRM9.X

D D

VRMPWRGD

CPUPWRGD

CPURST_

&

PWOK

CPUPWRGD

ATX

Power

C C

PSON_

NBPWRGD

SiS648FX

SiS661FX

CPURST_

NBRST_

AGP 8X SLOT

SiS964/SiS964L

SBPWRGD

NBRST_

PCIRST_

Front Panel

PSON_

B B

RSTSW_

PWRBTN_

PWRBTN_

SIORST_

PCI Slot 1

PCI Slot 2

PCI Slot 3

IDE CONN 1

IDE CONN 2

SIORST_

Super IO

8712F/JX

SIORST_

Media

Interface

A A

TECHNOLOGY COPR.

TECHNOLOGY COPR.

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet

Reset Map

Reset Map

Reset Map

661M08

661M08

661M08

TECHNOLOGY COPR.

of

244Monday, August 01, 2005

244Monday, August 01, 2005

244Monday, August 01, 2005

A

A

A

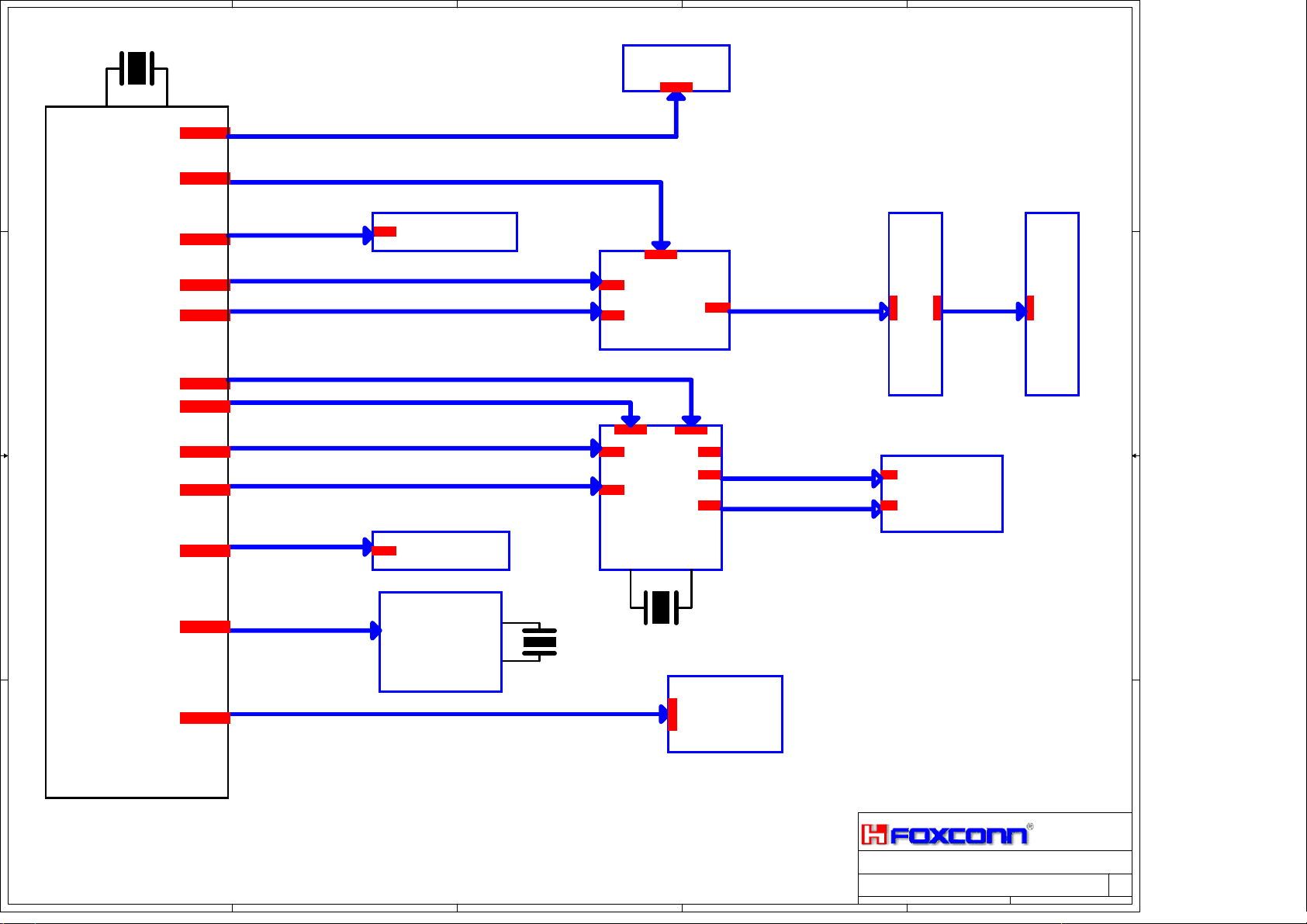

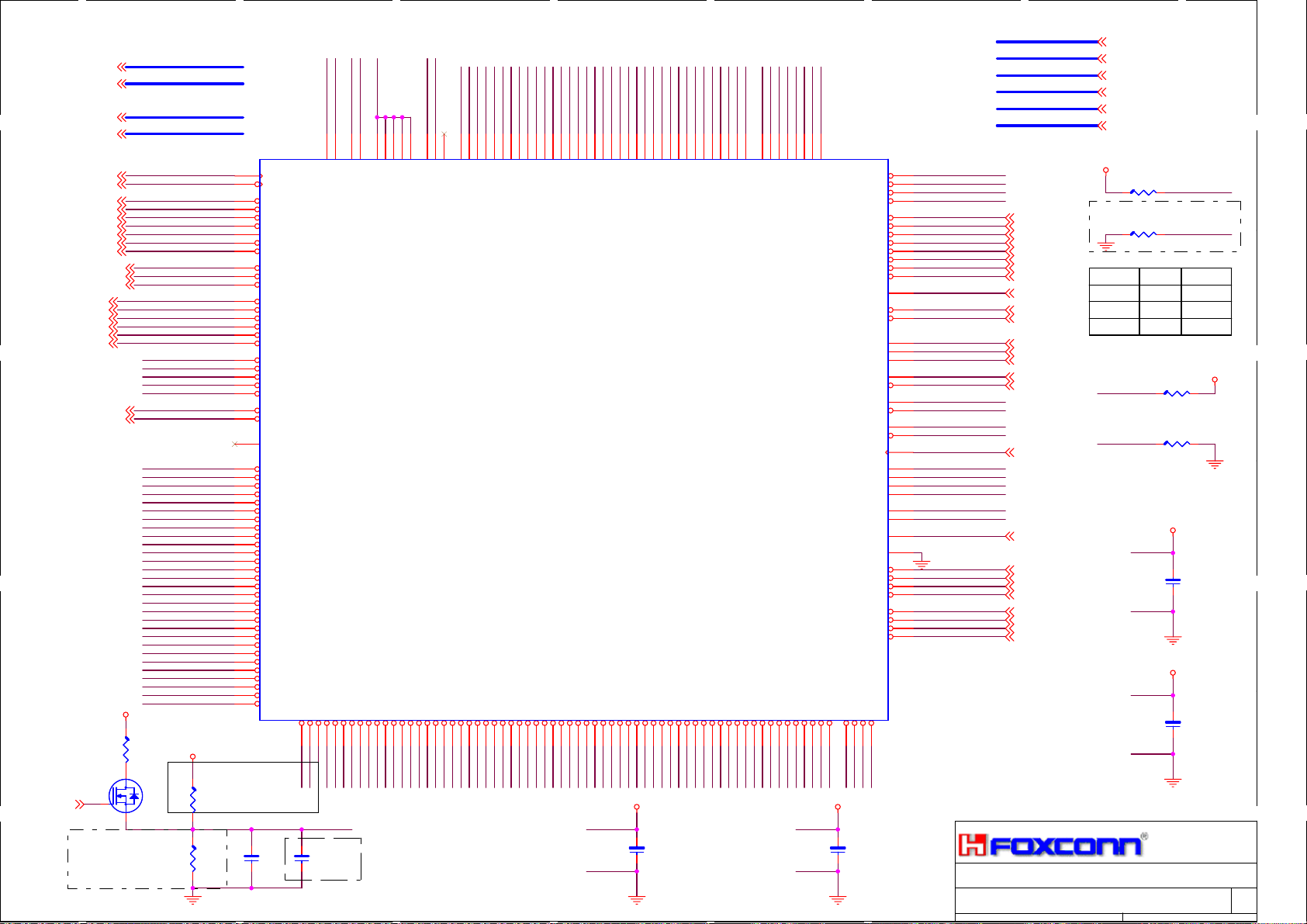

Page 4

5

14.318MHz

4

3

2

1

CPU

D D

CLOCK GENERATOR

C C

CPUCLK0

CPUCLK1

AGPCLK1

ZCLK0

AGPCLK0

100/133/200 MHz

100/133/200 MHz

66 MHz

133 MHz

66 MHz

AGP 8x

SiS648FX

/661FX

DDR CLOCK BUFFER

DIMM 1-2

DDRCLKFWDSDCLK0

33 MHz

96XPCLK

133 MHz

ZCLK1

48 MHz

UCLK48M

REFCLK

964L

SiS964/

PCICLK1-3

33 MHz

B B

PCI Slot 1-3

TXCLK

RXCLK

LAN PHY

AUDIO_CLK

32.768KHz

AC'97

24.576MHz/NC

SIO48M

48 MHz

A A

5

4

3

Super I/O

TECHNOLOGY COPR.

TECHNOLOGY COPR.

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Clock Distribution

Clock Distribution

Clock Distribution

661M08

661M08

661M08

TECHNOLOGY COPR.

of

344Monday, August 01, 2005

of

344Monday, August 01, 2005

of

344Monday, August 01, 2005

1

A

A

A

Page 5

5

4

3

2

1

VCC3:

3.3V

>

DDR 2 DIMMS:

2.5V +/-100mv

6.00A

DDR VTT

1.25V

2A

SIS964

CLK_GEN

3.3V

>

300mA

SUPER I/O

>

VCC5_DUAL

5V

>

VCC3_DUAL

>

FWH

>

VCC1.8V

1.8V

VCCPRTCVDD

ATX

ATX SPS

+

3

5

V

D D

S

B

1

.

5

2

3

V

V

V

12V

P/S

+

1

1

2

2

V

V

LGA775

VCCP

1.1V~1.85V 119A

>

VCC_VID

1.2V 30mA

>

>

+12V

MIC5258

>

VRD 10.1

CORE_CPU_SYS

VCCVID

SIS648FX/ 661FX

PWRG_ATX

5V_DUAL

>

VCC3

>

C C

B B

SB5V

SB3V

AIC1086

VCC3 VCC1.8V

PWRG_ATX

AIC1084

VCC3_DUAL

>

>

VCC3

VCC5

+12V

-12V

VCC3_DUAL

VCC3:

3.3V

108mA

VCC3_DUAL

33.4mA

VCC2.5_MEM

2.5V

501.3mA

>

>

>

>

PCI PER SLOT:

3.3V 7.6A

5V 5.0A

12V 0.5A

-12V 0.1A

3.3Vaux

0.375A

VCC1.8V

1.8V

1389.5mA

VDDQ:

AGP

1.5V 35.1/21.7mA

SB1.8V

1.8V

10mA

VCCP

VCC3

SB5V

3 VOLTS

BATTERY

>

>

SB3V

2.5V

REGULATOR

REGULATOR

>

>

VCC3

VCC5_DUAL

5V_SYS

VCC3_DUAL

VCC2.5_MEM

S3AUXSW-

VCC2.5_MEM

DDR_VTT_STR

1.25V

> >

REGULATOR

VCC3

VCC3_DUAL

VCC1.8V

VCCP

>

>

>

>

OR

VCC_RTC

VCC_RTC

>

VCC5

VCC3_DUAL

>

USB POWER

>

5V

PS2 KB/MS POWER

>

5V

VCC3_DUAL

>

LAN PHY

VCC5

SB5V

VCC5_DUAL

PWRG_ATX

VCC5_DUAL

+12V

VCC3

VCC3

+12V

A A

VCC5

VCC3_DUAL

AIC1084

VDDQ 1.5V

>

>

>

>

AGP

VCC3

AUDIO

VREG

>

5

4

3

2

VCC5A

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

AC' 97 AUDIO CODEC

>

A5V 70mA

3.3V 10mA

>

Power Delivery Map

Power Delivery Map

Power Delivery Map

661M08

661M08

661M08

TECHNOLOGY COPR.

TECHNOLOGY COPR.

TECHNOLOGY COPR.

444Monday, August 01, 2005

444Monday, August 01, 2005

444Monday, August 01, 2005

1

of

of

of

A

A

A

Page 6

5

2 OF 7

U33B

U33B

HDJ0

HDJ1

D D

C C

TBD

Pin D23

CRB 0.7: test point TP_VCCPLL

Pin AM5

CRB 0.7: test point TP_VID6

B B

A A

HDJ2

HDJ3

HDJ4

HDJ5

HDJ6

HDJ7

HDJ8

HDJ9

HDJ10

HDJ11

HDJ12

HDJ13

HDJ14

HDJ15

HDBIJ09

HDSTBNJ09

HDSTBPJ09

HDJ16

HDJ17

HDJ18

HDJ19

HDJ20

HDJ21

HDJ22

HDJ23

HDJ24

HDJ25

HDJ26

HDJ27

HDJ28

HDJ29

HDJ30

HDJ31

HDBIJ19

HDSTBNJ19

HDSTBPJ19

SMIJ14

A20MJ14

FERRJ14

INTR14

NMI14

IGNNEJ14

STPCLKJ14

HVCCA6

HVSSA6

HVCCIOPLL6

VID07

VID17

VID27

VID37

VID47

VID57

TP16TP16

CPUCLK017

CPUCLK-017

THERMDA32

THERMDC32

TP17TP17

TP18TP18

VCC_SENSE7

VSS_SENSE7

TP_VCCPLL

TP_VID6

TP_VCCSENSE

TP_VSSSENSE

B4

D00#

C5

D01#

A4

D02#

C6

D03#

A5

D04#

B6

D05#

B7

D06#

A7

D07#

A10

D08#

A11

D09#

B10

D10#

C11

D11#

D8

D12#

B12

D13#

C12

D14#

D11

HDBIJ0

HDBIJ1 HDBIJ3

VID0

VID1

VID2

VID3

VID4

VID5

D15#

A8

DBI0#

C8

DSTBN0#

B9

DSTBP0#

G9

D16#

F8

D17#

F9

D18#

E9

D19#

D7

D20#

E10

D21#

D10

D22#

F11

D23#

F12

D24#

D13

D25#

E13

D26#

G13

D27#

F14

D28#

G14

D29#

F15

D30#

G15

D31#

G11

DBI1#

G12

DSTBN1#

E12

DSTBP1#

CPU_Socket

CPU_Socket

P2

K3

R3

K1

L1

N2

M3

A23

B23

D23

C23

AM2

AL5

AM3

AL6

AK4

AL4

AM5

F28

G28

AE8

AL1

AK1

AN3

AN4

AN5

AN6

F29

5

2 OF 7

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DBI2#

DSTBN2#

DSTBP2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI3#

DSTBN3#

DSTBP3#

3 OF 7

3 OF 7

U33C

U33C

SMI#

A20M#

FERR#/PBE#

LINT0

LINT1

IGNNE#

STPCLK#

VCCA

VSSA

RSVD5

VCCIOPLL

VID0

VID1

VID2

VID3

VID4

VID5

RSVD6

BCLK0

BCLK1

SKTOCC#

THERMDA

THERMDC

VCCSENSE

VSSSENSE

VCC_MB_REG

VSS_MB_REG

Changed pin name

Changed pin name

from RSV

from RSV

RSVD9

CPU_Socket

CPU_Socket

THERMTRIP#

BOOTSELECT

G16

E15

E16

G18

G17

F17

F18

E18

E19

F20

E21

F21

G21

E22

D22

G22

D19

G20

G19

D20

D17

A14

C15

C14

B15

C18

B16

A17

B18

C21

B21

B19

A19

A22

B22

C20

A16

C17

TESTHI00

TESTHI01

TESTHI11

TESTHI12

TESTHI02

TESTHI03

TESTHI04

TESTHI05

TESTHI06

TESTHI07

RSVD10

RSVD11

SLP#

RSVD12

PWRGOOD

PROCHOT#

COMP0

COMP1

COMP2

COMP3

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

LL_ID0

LL_ID1

HDJ32

HDJ33

HDJ34

HDJ35

HDJ36

HDJ37

HDJ38

HDJ39

HDJ40

HDJ41

HDJ42

HDJ43

HDJ44

HDJ45

HDJ46

HDJ47

HDBIJ2

HDJ48

HDJ49

HDJ50

HDJ51

HDJ52

HDJ53

HDJ54

HDJ55

HDJ56

HDJ57

HDJ58

HDJ59

HDJ60

HDJ61

HDJ62

HDJ63

TBD

Pin AL2 PROCHOT#

CRB 0.7: pull up to VTT_OUT_RIGHT

DG/611A: example VR thermal monitor circuit

TESTHI_0

F26

TESTHI_1

W3

TESTHI_11

P1

TESTHI_12

W2

F25

G25

G27

G26

G24

F24

AK6

G6

L2

AH2

N1

AL2

M2

A13

T1

G2

R1

N5

AE6

C9

G10

D16

A20

E23

E24

F23

H2

J2

J3

Y1

V2

AA2

4

HDJ[63..0]

HDBIJ2 9

HDSTBNJ2 9

HDSTBPJ2 9

HDBIJ3 9

HDSTBNJ3 9

HDSTBPJ3 9

TESTHI_0 6

TBD

Pin AK6, G6

refer to CRB 0.7

TESTHI_2_7

RSVD_AK6

RSVD_G6

CPUSLPJ 14

CPU_PWRG 14

PROCHOTJ 14

THERMTRIPJ 14

HCOMP0

HCOMP1

HCOMP2

HCOMP3

TBD

Pin N5 ~ Pin J3

CRB 0.7: connections ok?

TP_RSVD_CPU_N5

TP_RSVD_CPU_AE6

TP_RSVD_CPU_C9

TP_RSVD_CPU_G10

TP_RSVD_CPU_D16

TP_RSVD_CPU_A20

CPU_BOOT

LL_ID0

TP_LL_ID1

4

TP22TP22

TP23TP23

TP24TP24

TP25TP25

LL_ID0

HDJ[63..0] 9

HAJ[31..3]9

FSB_VTT

VTT_OUT_LEFT

VTT_OUT_RIGHT

HREQJ[4..0]9

HAJ[31..3]

R817 62 DummyR817 62 Dummy

R818 62R818 62

RN80

RN80

1

*

*

3

5

7 8

R825 62R825 62

R826 62R826 62

R827 100R827 100

R828 62R828 62

R829 62R829 62

R830 62 DUMMYR830 62 DUMMY

R831 62R831 62

R837 680

R837 680

RN81

RN81

6

4

2

680

680

R841 680

R841 680

+/-5%

+/-5%

R842

R842

HAJ[31..3]9

8P4R0603

8P4R0603

*

*

+/-5%

+/-5%

*

*

+/-5%

+/-5%

*

*

3

HAJ[31..3]

U33A

L5

A03#

P6

A04#

M5

A05#

L4

A06#

M4

A07#

R4

A08#

T5

A09#

U6

A10#

T4

A11#

U5

A12#

U4

A13#

V5

A14#

V4

A15#

W5

A16#

N4

RSVD1

P5

RSVD2

K4

REQ0#

J5

REQ1#

M6

REQ2#

K6

REQ3#

J6

REQ4#

R6

ADSTB0#

G5

PCREQ#

AB6

A17#

W6

A18#

Y6

A19#

Y4

A20#

AA4

A21#

AD6

A22#

AA5

A23#

AB5

A24#

AC5

A25#

AB4

A26#

AF5

A27#

AF4

A28#

AG6

A29#

AG4

A30#

AG5

A31#

AH4

A32#

AH5

A33#

AJ5

A34#

AJ6

A35#

AC4

RSVD3

AE4

RSVD4

AD5

ADSTB1#

CPU_Socket

CPU_Socket

FSB_VTT

U33A

DEFER#

EDRDY#

MCERR#

TESTHI08

TESTHI09

TESTHI10

GTLREF

RESET#

VTT_OUT_LEFT

VTT_OUT_RIGHT

INTEL THERMTRIPJ, FERRJ PULL HIGH FSB_VTT

R832 56R832 56

R833 56R833 56

R834 56R834 56

R835 56R835 56

R836 56R836 56

R838 56R838 56

R839 56R839 56

R840 56R840 56

NEAR CPU

HAJ3

HAJ4

HAJ5

HAJ6

HAJ7

HAJ8

HAJ9

HAJ10

HAJ11

HAJ12

HAJ13

HAJ14

HAJ15

HAJ16

HREQJ0

HREQJ1

HREQJ2

HREQJ3

HADSTBJ09

HAJ17

HAJ18

HAJ19

HAJ20

HAJ21

HAJ22

HAJ23

HAJ24

HAJ25

HAJ26

HAJ27

HAJ28

HAJ29

HAJ30

HAJ31

TP11TP11

TP12TP12

TP13TP13

TP14TP14

HADSTBJ19

62

62

2

4

6

78

5

3

*

*

1

+/-5%

+/-5%

Dummy

Dummy

3

HREQJ4

TP_LAG775_PIN_AH4

TP_LAG775_PIN_AH5

TP_LAG775_PIN_AJ5

TP_LAG775_PIN_AJ6

TESTHI_0

TESTHI_2_7

TESTHI_9

TESTHI_8

TESTHI_10

TESTHI_1

TESTHI_11

TESTHI_12

CPU_PWRG

HCPURSTJ

HBR0J

RSVD_G6

CPU_BOOT

VID0

VID3

VID2

VID4

VID1

VID5

RSVD_AK6

ADS#

BNR#

HIT#

RSP#

BPRI#

DBSY#

DRDY#

HITM#

IERR#

INIT#

LOCK#

TRDY#

BINIT#

AP0#

AP1#

BR0#

DP0#

DP1#

DP2#

DP3#

RS0#

RS1#

RS2#

1 OF 7

1 OF 7

2

D2

C2

D4

H4

G8

B2

C1

E4

AB2

P3

C3

E3

AD3

G7

F2

AB3

U2

U3

F3

G3

G4

H5

J16

H15

H16

J17

H1

G23

B3

F5

A3

10 mils width

7 mils spacing

R815 100R815 100

R816 100R816 100

R819 60.4R819 60.4

R820 60.4R820 60.4

10 mils width

7 mils spacing

R821 62R821 62

R822 62R822 62

R823 130R823 130

R824 62R824 62

A20MJ

STPCLKJ

CPUSLPJ

SMIJ

INITJ

IGNNEJ

INTR

NMI

2

1

HADSJ 9

HBNRJ 9

TP_RSPJ

HIERRJ

TP_BINITJ

TP_EDRDYJ

TP_MCERRJ

TP_APJ0

TP_APJ1

HBR0J

TESTHI_8

TESTHI_9

TESTHI_10

TP_DPJ0

TP_DPJ1

TP_DPJ2

TP_DPJ3

HGTLREF

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

HITJ 9

TP1TP1

HBPRIJ 9

HDBSYJ 9

HDRDYJ 9

HITMJ 9

INITJ 14

HLOCKJ 9

HTRDYJ 9

HDEFERJ 9

TP3TP3

TP4TP4

TP5TP5

TP6TP6

HBR0J 9

HCPURSTJ 9

HRSJ0 9

HRSJ1 9

HRSJ2 9

TBD

HCOMP2

HCOMP3

HCOMP0

HCOMP1

HIERRJ

THERMTRIPJ

PROCHOTJ

FERRJ

VTT_OUT_LEFT

*

*

TP2TP2

GTLREF voltage should be 0.67*FSB_VTT

12 mils width, 15 mils spacing

divider should be within 1.5" of the GTLREF pin

caps should be placed near CPU pin

VTT_OUT_RIGHT

*

BC938

BC938

*

*

1uF

1uF

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

C0603

C0603

Place at CPU end of route

HBR0J

CRB 0.7: 220 ohm, 5%

DG 0.51: 62 ohm, 5%

VTT_OUT_RIGHT

FSB_VTT

BC6

BC6

0.1uF

0.1uF

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

C0603

C0603

Clock Distribution

Clock Distribution

Clock Distribution

661M08

661M08

661M08

*

*

*

*

*

*

*

BC939

BC939

220pF

220pF

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

HCPURSTJ

BC4

BC4

0.1uF

0.1uF

*

*

C0603

C0603

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

BC8

BC8

0.1uF

0.1uF

*

*

C0603

C0603

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

TECHNOLOGY COPR.

TECHNOLOGY COPR.

TECHNOLOGY COPR.

544Monday, August 01, 2005

544Monday, August 01, 2005

544Monday, August 01, 2005

1

R813

R813

100

100

+/-1%

+/-1%

R0603

R0603

R814

R814

210

210

+/-1%

+/-1%

R0603

R0603

BC5

BC5

0.1uF

0.1uF

C0603

C0603

BC7

BC7

1uF

1uF

C0805

C0805

16V, X7R, +/-10%

16V, X7R, +/-10%

25V, Y5V, +80%/-20%

25V, Y5V, +80%/-20%

BC940

BC940

22pF

22pF

*

*

C0603

C0603

A

A

of

of

of

A

Page 7

5

4

3

2

1

VCCP VCCP

D D

C C

B B

A A

U33E

AG22

K29

AM26

AL8

AE12

AE11

W23

W24

W25

T25

Y28

AL18

AC25

W30

Y30

AN14

AD28

Y26

AC29

M29

U24

J23

AC27

AM18

AM19

AB8

AC26

J8

J28

T30

AM9

AF15

AC8

AE14

N23

W29

U29

AC24

AC23

Y23

AN26

AN25

AN11

AN18

Y27

Y25

AD24

AE23

AE22

AN19

V8

K8

AE21

AM30

AE19

AC30

AE15

M30

K27

M24

AN21

T8

AC28

N25

AE18

W26

AD25

M8

N30

AD26

AJ26

AM29

M25

M26

L8

U25

Y8

AJ12

AD27

U23

M23

AG29

N27

AM22

U28

K28

U8

AK18

AD8

K24

AH28

AH21

CPU_Socket

CPU_Socket

U33E

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCP25

VCCP26

VCCP27

VCCP28

VCCP29

VCCP30

VCCP31

VCCP32

VCCP33

VCCP34

VCCP35

VCCP36

VCCP37

VCCP38

VCCP39

VCCP40

VCCP41

VCCP42

VCCP43

VCCP44

VCCP45

VCCP46

VCCP47

VCCP48

VCCP49

VCCP50

VCCP51

VCCP52

VCCP53

VCCP54

VCCP55

VCCP56

VCCP57

VCCP58

VCCP59

VCCP60

VCCP61

VCCP62

VCCP63

VCCP64

VCCP65

VCCP66

VCCP67

VCCP68

VCCP69

VCCP70

VCCP71

VCCP72

VCCP73

VCCP74

VCCP75

VCCP76

VCCP77

VCCP78

VCCP79

VCCP80

VCCP81

VCCP82

VCCP83

VCCP84

VCCP85

VCCP86

VCCP87

VCCP88

VCCP89

VCCP90

VCCP91

VCCP92

5 OF 7

5 OF 7

VCCP93

VCCP94

VCCP95

VCCP96

VCCP97

VCCP98

VCCP99

VCCP100

VCCP101

VCCP102

VCCP103

VCCP104

VCCP105

VCCP106

VCCP107

VCCP108

VCCP109

VCCP110

VCCP111

VCCP112

VCCP113

VCCP114

VCCP115

VCCP116

VCCP117

VCCP118

VCCP119

VCCP120

VCCP121

VCCP122

VCCP123

VCCP124

VCCP125

VCCP126

VCCP127

VCCP128

VCCP129

VCCP130

VCCP131

VCCP132

VCCP133

VCCP134

VCCP135

VCCP136

VCCP137

VCCP138

VCCP139

VCCP140

VCCP141

VCCP142

VCCP143

VCCP144

VCCP145

VCCP146

VCCP147

VCCP148

VCCP149

VCCP150

VCCP151

VCCP152

VCCP153

VCCP154

VCCP155

VCCP156

VCCP157

VCCP158

VCCP159

VCCP160

VCCP161

VCCP162

VCCP163

VCCP164

VCCP165

VCCP166

VCCP167

VCCP168

VCCP169

VCCP170

VCCP171

VCCP172

VCCP173

VCCP174

VCCP175

VCCP176

VCCP177

VCCP178

VCCP179

VCCP180

VCCP181

VCCP182

VCCP183

VCCP184

AK12

AH22

T29

AM14

AM25

AE9

Y29

AK25

AK19

AG15

J22

T24

AG21

AM21

J25

U30

AL21

AG25

AJ18

J19

AH30

J15

AG12

AJ22

J20

AH18

AH26

W27

AL25

AN8

AH14

U27

T23

R8

AK22

AN29

AG11

AK26

J10

AJ15

AG26

AN9

AH15

AF18

AL15

J26

J18

J21

AG27

AK15

AF11

AD23

AM15

AF8

AK21

AG30

AJ21

AM11

AL11

AJ11

K30

AL14

AN30

AH25

AL12

AJ9

AK11

AG14

N29

AL30

AJ25

AH9

J29

J11

K25

P8

K23

AL19

AM8

T26

N28

AH12

AL22

AN15

AJ8

U26

AJ19

T27

AK8

AN12

AG9

N26

VCCP

VCC3

FSB_VTT

BSEL117 BSEL0 17

5

FSBSEL0

R341

R341

470

470

+/-5%

+/-5%

R0603

R0603

*

*

R338

R338

220

220

+/-5%

+/-5%

R0603

R0603

R271

R271

*

*

1K

1K

+/-5%

+/-5%

R0603

R0603

Q34

Q34

B

MMBT3904

MMBT3904

E C

R272

R272

*

*

2.7K

2.7K

+/-5%

+/-5%

R0603

R0603

R942

R942

Q35

Q35

4.7K

4.7K

B

MMBT3904

MMBT3904

+/-5%

+/-5%

*

*

R0603

R0603

E C

AF9

AF22

AH11

AJ14

AH19

AH29

AH27

AG28

AL26

AM12

J24

J13

T28

W28

J12

J27

AG19

AL9

AD30

AF21

Y24

AK14

J9

M27

AF14

J30

AG18

AA8

AG8

AL29

AD29

W8

AH8

N24

AN22

J14

K26

AF19

N8

AF12

M28

AK9

C10

D12

AM7

C24

K2

C22

AN1

B14

K7

AE16

B11

AL10

AK23

H12

AF7

AK7

H7

E14

L28

Y5

E11

AL16

AL24

AK13

AL3

D21

AL20

D18

AN2

AK16

AK20

AM27

AM1

AL13

AL17

C19

E28

AH7

AK30

D24

CPU_Socket

CPU_Socket

U33F

U33F

VCCP185

VCCP186

VCCP187

VCCP188

VCCP189

VCCP190

VCCP191

VCCP192

VCCP193

VCCP194

VCCP195

VCCP196

VCCP197

VCCP198

VCCP199

VCCP200

VCCP201

VCCP202

VCCP203

VCCP204

VCCP205

VCCP206

VCCP207

VCCP208

VCCP209

VCCP210

VCCP211

VCCP212

VCCP213

VCCP214

VCCP215

VCCP216

VCCP217

VCCP218

VCCP219

VCCP220

VCCP221

VCCP222

VCCP223

VCCP224

VCCP225

VCCP226

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

U33G

6 OF 7

6 OF 7

AL23

VSS41

A12

VSS42

L25

VSS43

J7

VSS44

AE28

VSS45

AE29

VSS46

K5

VSS47

J4

VSS48

AE30

VSS49

AN20

VSS50

AF10

VSS51

AE24

VSS52

AM24

VSS53

AN23

VSS54

H9

VSS55

H8

VSS56

H13

VSS57

AC6

VSS58

AC7

VSS59

AH6

VSS60

C16

VSS61

AM16

VSS62

AE25

VSS63

AE27

VSS64

AJ28

VSS65

AJ7

VSS66

F19

VSS67

AH13

VSS68

AD7

VSS69

AH16

VSS70

AK17

VSS71

E17

VSS72

AH17

VSS73

AH20

VSS74

AE5

VSS75

AH23

VSS76

AE7

VSS77

AM13

VSS78

AH24

VSS79

AJ30

VSS80

AJ10

VSS81

AF3

VSS82

AK5

VSS83

AJ16

VSS84

AF6

VSS85

AK29

VSS86

AJ17

VSS87

F22

VSS88

AH3

VSS89

AK10

VSS90

AM10

VSS91

F16

VSS92

AJ23

VSS93

F13

VSS94

AG7

VSS95

F10

VSS96

L26

VSS97

AD4

VSS98

H11

VSS99

L24

VSS100

L23

VSS101

AM23

VSS102

A15

VSS103

AH10

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

ICH_SYS_RSTJ

NBRST-11,13

FSBSEL0

FSBSEL1

4

H29

B24

L3

H27

A21

AE2

AJ29

A24

AK27

AK28

B20

AM20

H26

B17

H25

H24

AA3

AA7

H23

AA6

H10

HTCK

HTDI

HTDO

HTMS

HTRSTJ

HBPM0J

HBPM1J

HBPM2J

HBPM3J

HBPM4J

HBPM5J

R931

R931

1K

1K

+/-1%

+/-1%

R0603

R0603

DUMMY

DUMMY

GTLREF_SEL

AE1

AD1

AF1

AC1

AG1

AJ2

AJ1

AD2

AG2

AF2

AG3

AC2

AK3

AJ3

G29

H30

G30

U33D

U33D

TCK

TDI

TDO

TMS

TRST#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

DBR#

ITPCLKOUT0

ITPCLKOUT1

BSEL0

BSEL1

BSEL2

CPU_Socket

CPU_Socket

GTLREF_SEL 9

4 OF 7

4 OF 7

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTTPWRGD

VTT_OUT1

VTT_OUT2

VTT_SEL

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

AA1

J1

F27

U33G

H22

VSS126

H21

VSS127

H20

VSS128

H19

VSS129

H18

VSS130

AB7

VSS131

H17

VSS132

AJ24

VSS133

AM17

VSS134

AC3

VSS135

H14

VSS136

P28

VSS137

V6

VSS138

AK2

VSS139

P27

VSS140

P26

VSS141

AM28

VSS142

AJ13

VSS143

W4

VSS144

P25

VSS145

AJ20

VSS146

W7

VSS147

P23

VSS148

AG13

VSS149

AG16

VSS150

AG17

VSS151

C7

VSS152

Y2

VSS153

L30

VSS154

L29

VSS155

D15

VSS156

AL27

VSS157

Y7

VSS158

L27

VSS159

AA29

VSS160

N6

VSS161

N7

VSS162

AA28

VSS163

AN13

VSS164

AA27

VSS165

AA26

VSS166

P4

VSS167

AA25

VSS168

AA24

VSS169

P7

VSS170

E26

VSS171

V30

VSS172

R2

VSS173

V29

VSS174

V28

VSS175

R5

VSS176

V27

VSS177

R7

VSS178

E20

VSS179

AN10

VSS180

V25

VSS181

T3

VSS182

V24

VSS183

V23

VSS184

T6

VSS185

AL7

VSS186

E25

VSS187

U1

VSS188

R29

VSS189

R28

VSS190

R27

VSS191

R26

VSS192

R25

VSS193

U7

VSS194

R24

VSS195

R23

VSS196

P30

VSS197

V3

VSS198

P29

VSS199

AF16

VSS200

AE10

VSS201

AF13

VSS202

H6

VSS203

A18

VSS204

A2

VSS205

E2

VSS206

D9

VSS207

C4

VSS208

A6

VSS209

D6

VSS210

CPU_Socket

CPU_Socket

FSB_VTT

VTT_OUT_RIGHT

VTT_OUT_LEFT

R859 DummyR859 Dummy

1 2

7 OF 7

7 OF 7

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

GTLREF_SEL

VTT_PWRGD 38

3

D5

A9

D3

B1

B5

B8

AJ4

AE26

AH1

E29

V7

C13

AK24

AB30

L6

L7

AB29

M1

AB28

E8

AG20

AN17

AB27

AB26

AN16

M7

AB25

AB24

AB23

N3

AA30

F4

AG10

AE13

AF30

H28

F7

AF29

AF28

G1

AF27

AF26

AF25

AN28

AN27

AF24

AF23

AG24

AF17

AN24

H3

AN7

P24

AE20

AE17

E27

T7

R30

AJ27

AB1

AM4

V26

AA23

AL28

AF20

AG23

V1

F6

T2

Y3

AE3

W1

E7

B13

D14

E6

D1

E5

TESTHI_05

VTT_OUT_RIGHT

VTT_OUT_LEFT

VCC3

+12V

*

*

TESTHI_0

BC960

0.1uF

BC960

0.1uF

Place at CPU end of route

R855

R855

10K

10K

+/-5%

+/-5%

R0603

R0603

G

note: 7/6-change termination 49.9 to RN702 47

VTT_OUT_RIGHT

R843 62

R843 62

R844 62

R844 62

R845 62

R845 62

R846 62

R846 62

R847 62

R847 62

R848 62

R848 62

Intel Pull High RES 49.9Ohm.

VTT_OUT_RIGHT

R849 49.9

R849 49.9

R850 49.9

R850 49.9

R851 49.9

R851 49.9

R852 49.9

R852 49.9

R853 49.9

R853 49.9

FSB_VTT

12

L12

L12

L0805 10uH

L0805 10uH

0805

0805

+/-10%

+/-10%

HVCCIOPLL

HVCCIOPLL5

?

VCC3

R856

R856

*

*

249

249

+/-1%

+/-1%

R0603

R0603

DS

Q95

Q95

2N7002

2N7002

R857

R857

*

*

110

110

+/-1%

+/-1%

R0603

R0603

*

*

R858

R858

62

62

+/-5%

+/-5%

R0603

R0603

2

HVCCA5

HVSSA5

BC959

BC959

1uF

1uF

*

*

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

C0603

C0603

HVCCA

HVSSA

VTT_OUT_RIGHT

*

*

BC1025

BC1025

1uF

1uF

*

*

10V, Y5V, +80%/-20%

10V, Y5V, +80%/-20%

C0603

C0603

Place BPM termination near CPU

HBPM5J

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

*

PLL Supply Filter

R854

R854

0

0

+/-5%

+/-5%

R0603

R0603

HBPM4J

HBPM3J

HBPM2J

HBPM1J

HBPM0J

HTDO

HTMS

HTDI

HTCK

HTRSTJ

12

125mA125mA

L13

L13

L0805 10uH

L0805 10uH

0805

0805

+/-10%

+/-10%

Notes:

1. Cap. should be within 600 mils of the VCCA and VSSA pins

2. VCCA route should be parallel and next to VSSA route

3. Min. 12 mils trace from the filter to the processor pins

4. The inductors should be close to the cap.

EC98

EC98

33uF

33uF

*

*

16V, +/-20%

16V, +/-20%

CE20D50H110

CE20D50H110

ESL <= 5 nH, ESR < 0.3 ohm

FOXCONN PCEG

FOXCONN PCEG

Title

Title

Title

LGA775 -2

LGA775 -2

LGA775 -2

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

FOXCONN PCEG

661M08

661M08

661M08

1

A

A

A

of

of

of

644Monday, August 01, 2005

644Monday, August 01, 2005

644Monday, August 01, 2005

Page 8

5

D D

VRM_EN

VRM_EN8

VID_OUT0

VID05

VID_OUT1

VID15

VID_OUT2

VID25

VID_OUT3

VID35

VID_OUT4

VID45

VID_OUT5

VID55

C C

Select pull high

voltage by chipset

VRMPWRGD17,38

12V_VRM

Place close to MOSFET

*

*

RT2

RT2

T

T

100K

100K

+/-1%

+/-1%

R0603

R0603

Dummy

B B

A A

Dummy

50V, NPO, +/-5%

50V, NPO, +/-5%

7/20

7/20

R960

R960

8.2K

8.2K

+/-5%

+/-5%

R0603

R0603

R963

R963

8.2K

8.2K

+/-5%

+/-5%

R0603

R0603

Dummy

Dummy

R965

R965

+/-5%

+/-5%

R0603

R0603

BC1045

BC1045

47pF

47pF

C0603

C0603

7/20

*

*

0

0

*

*

R955

R0603

R955

R0603

Dummy

Dummy

100K

+/-1%

100K

+/-1%

BC1033

C0603

BC1033

C0603

Dummy

Dummy

10nF 25V, X7R, +/-10%

10nF 25V, X7R, +/-10%

*

*

R9520R0603

R9520R0603

Reserved

Reserved

+/-5%

+/-5%

BC1034

C0603

BC1034

C0603

Dummy

Dummy

10nF 25V, X7R, +/-10%

10nF 25V, X7R, +/-10%

*

*

R954 127K

R954 127K

R0603+/-1%

R0603+/-1%

R959

R0603

R959

R0603

150K

+/-1%

150K

+/-1%

R964

R0603

R964

R0603

5.1K

5.1K

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

18K

18K

+/-1% R967

+/-1%

R0603

R0603

VCCP

+/-5%

+/-5%

*

*

BC1044470pF

BC1044470pF

R967

BC1047

BC1047

4.7nF

4.7nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

4

Preliminary OVP Protection

R943

R943

10

10

+/-5%

+/-5%

R0805

R0805

BC1

BC1

1uF

1uF

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

C0805

C0805

U40

U40

5

4

35

OUTEN

VID0

VID1

VID2

VID3

VID4

VID5

VID_SEL

OVP

TC

CS_SEL

OFFSET

OSC/FAULT

SGND

SS_END

VSEN

FB

COMP

FBR

11

SGND

BC1049

BC1049

0.1uF

0.1uF

C0603

C0603

VCC

12

*

*

L6711TR

L6711TR

FBG

R973

R973

0

0

R0603

R0603

+/-5%

+/-5%

Dummy

Dummy

13

24

25

26

27

28

23

29

20

21

22

31

30

10

9

6

8

7

R971

R971

0

0

R0603

R0603

+/-5%

+/-5%

Dummy

Dummy

*

*

PGND3

VSS_SENSE 5VCC_SENSE5

optional

BC2

BC2

1uF

1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

C0805

C0805

38

39

PGND2

VCCDR3

R944

R944

0

0

+/-5%

+/-5%

R0805

R0805

41

3

PGND1

VCCDR2

NC37

NC484849

37

3

BC3

BC3

1uF

1uF

16V, X7R, +/-10%

16V, X7R, +/-10%

C0805

C0805

*

*

1

BOOT1

VCCDR1

UGATE1

PHASE1

LGATE1

CS1+

BOOT2

UGATE2

PHASE2

LGATE2

CS2+

BOOT3

UGATE3

PHASE3

LGATE3

CS3+

49

D43

D43

BAT54C

BAT54C

CS1-

CS2-

CS3-

2

1

45

46

47

2

14

15

44

43

42

40

16

17

34

33

32

36

18

19

BC1029

BC1029

1uF

1uF

*

*

16V, X7R, +/-10%

16V, X7R, +/-10%

C0805

C0805

D44

D44

1N4148W

1N4148W

VBOOT

2 1

BC10360.1uF

BC10360.1uF

25V, Y5V, +80%/-20%C0603

25V, Y5V, +80%/-20%C0603

*

*

R946 2.2

R946 2.2

R0805 +/-5%

R0805 +/-5%

R947 2.2

R947 2.2

R0805 +/-5%

R0805 +/-5%

R950 3K +/-1%R950 3K +/-1%

D45

D45

1N4148W

1N4148W

2 1

BC10350.1uF

BC10350.1uF

25V, Y5V, +80%/-20%C0603

25V, Y5V, +80%/-20%C0603

*

*

R953 2.2

R953 2.2

R0805 +/-5%

R0805 +/-5%

R957 2.2

R957 2.2

R0805 +/-5%

R0805 +/-5%

R961 3K +/-1%R961 3K +/-1%

D46

D46

1N4148W

1N4148W

VBOOT

2 1

BC10420.1uF

BC10420.1uF

25V, Y5V, +80%/-20%C0603

25V, Y5V, +80%/-20%C0603

*

*

R966 2.2

R966 2.2

R0805 +/-5%

R0805 +/-5%

R969 2.2

R969 2.2

R0805 +/-5%

R0805 +/-5%

R972 3K R0603+/-1%R972 3K R0603+/-1%

JS1 SHORTJS1 SHORT

3

12V_VRM

SB5V

12V_VRM

R945

R945

2.2

2.2

R0805

R0805

+/-5%

+/-5%

phase1

R951 1.2K

R951 1.2K

1 2

VBOOT

R962 1.2K

R962 1.2K

1 2

R974

R974

1 2

+/-1%

+/-1%

r0805h6

r0805h6

12

12V_VIN

12V_VIN 8

DS

Q109

Q109

G

AOD452L

AOD452L

DS

DS

Q110

Q110

Q111

G

AOD456L

AOD456L

12V_VIN 8

Q108

Q108

AOD452L

AOD452L

Q112

Q112

G

AOD456L

AOD456L

12V_VIN 8

Q114

Q114

AOD452L

AOD452L

Q115

Q115

G

AOD456L

AOD456L

HS1

HS1

MOSFET Heatsink

MOSFET Heatsink

PHC539C01012

PHC539C01012

mosfet_hsh180

mosfet_hsh180

Dummy

Dummy

AOD456L

AOD456L

DS

AOD456L

AOD456L

DS

AOD456L

AOD456L

Q111

Q113

Q113

Q116

Q116

G

12V_VIN

+/-1%

+/-1%

DS

G

phase2

DS

G

12V_VIN

+/-1%

+/-1%

r0805h6

r0805h6

DS

G

phase3

DS

G

1.2K

1.2K

Note: Put on Power

Mosfet surface.

R948

R948

2.2

2.2

R0805

R0805

+/-5%

+/-5%

BC1032

BC1032

1.5nF

1.5nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

R956

R956

2.2

2.2

R0805

R0805

+/-5%

+/-5%

BC1040

BC1040

1.5nF

1.5nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

R968

R968

2.2

2.2

R0805

R0805

+/-5%

+/-5%

BC1048

BC1048

1.5nF

1.5nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

BC1030

BC1030

4.7uF

4.7uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C1206

C1206

R949 1.8K

R949 1.8K

R0603+/-1%

R0603+/-1%

BC1038

BC1038

4.7uF

4.7uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C1206

C1206

R958 1.8K

R958 1.8K

R0603+/-1%

R0603+/-1%

BC1043

BC1043

4.7uF

4.7uF

*

*

16V, Y5V, +80%/-20%

16V, Y5V, +80%/-20%

C1206

C1206

R970

R970

1.8K

1.8K

R0603+/-1%

R0603+/-1%

L14

L14

*

*

0.6uH

0.6uH

BC1031 0.33uF

BC1031 0.33uF

16V, X7R, +/-10%

16V, X7R, +/-10%

L15

L15

*

*

0.6uH

0.6uH

BC1039 0.33uF

BC1039 0.33uF

16V, X7R, +/-10%

16V, X7R, +/-10%

L16

L16

*

*

0.6uH

0.6uH

BC1046 0.33uF

BC1046 0.33uF

16V, X7R, +/-10%

16V, X7R, +/-10%

2

0.33uF

0.33uF

C0805

C0805

Dummy

Dummy

0.33uF

0.33uF

C0805

C0805

Dummy

Dummy

0.33uF

0.33uF

C0805

C0805

Dummy

Dummy

16V, X7R, +/-10%C0805

16V, X7R, +/-10%C0805

*

*

BC1037

BC1037

16V, X7R, +/-10%C0805

16V, X7R, +/-10%C0805

*

*

BC1041

BC1041

16V, X7R, +/-10%C0805

16V, X7R, +/-10%C0805

*

*

BC1050

BC1050

1

*

*

VCCP

*

*

*

*

TECHNOLOGY COPR.

TECHNOLOGY COPR.

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet

VRD

VRD

VRD

661M08

661M08

661M08

1

TECHNOLOGY COPR.

of

744Monday, August 01, 2005

744Monday, August 01, 2005

744Monday, August 01, 2005

A

A

A

Page 9

5

4

PWM Controller Enable schematics

3

2

1

D D

VTT_OUT_RIGHT

R88

R88

R92

R92

BC1067

22.1K

22.1K

+/-1%

+/-1%

R0603

R0603

Dummy

Dummy

BC1067

*

*

1uF

1uF

16V, X5R, +/-10%

16V, X5R, +/-10%

C0603

C0603

Dummy

Dummy

4.7K

4.7K

R0603

R0603

+/-5%

+/-5%

Dummy

Dummy

C C

SB5V

R91

R91

10K

10K

+/-5%

+/-5%

R0603

R0603

Dummy

Dummy

Q24

Q24

B

MMBT3904

MMBT3904

SOT23_BEC

SOT23_BEC

E C

Dummy

Dummy

G

12V_VRM

R90

R90

10K

10K

+/-5%

+/-5%

R0603

R0603

DS

Dummy

Dummy

Q23

Q23

2N7002

2N7002

Dummy

Dummy

R89

R89

4.7K

4.7K

+/-5%

+/-5%

R0603

R0603

Dummy

Dummy

VRM_EN

BC1066

BC1066

1nF

1nF

*

*

50V, X7R, +/-10%

50V, X7R, +/-10%

C0603

C0603

Dummy

Dummy

VRM_EN 7

BC1059

BC1059

22uF

22uF

*

*

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

C1206

C1206

Dummy

Dummy

BC1060

BC1060

22uF

22uF

*

*

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

C1206

C1206

Dummy

Dummy

VRM Output MLCC

VCCP

BC1061

BC1061

22uF

22uF

*

*

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

C1206

C1206

Dummy

Dummy

place in socket

VCCP

BC1062

BC1062

22uF

22uF

*

*

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

C1206

C1206

Dummy

Dummy

EC4

EC4

560uF

560uF

*

*

4V, +/-20%

4V, +/-20%

CE35D80H90

CE35D80H90

Dummy

Dummy

BC1063

BC1063

22uF

22uF

*

*

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

C1206

C1206

Dummy

Dummy

EC5

EC5

560uF

560uF

*

*

4V, +/-20%

4V, +/-20%

CE35D80H90

CE35D80H90

Dummy

Dummy

BC1064

BC1064

22uF

22uF

*

*

6.3V, X5R, +/-10%

6.3V, X5R, +/-10%

C1206

C1206

Dummy

Dummy

EC6

EC6

560uF

560uF

*

*

4V, +/-20%

4V, +/-20%

CE35D80H90

CE35D80H90

Dummy

Dummy

VRM Input LC schematics

TC2

EC8

EC7

EC7

560uF

560uF

*

*

4V, +/-20%

4V, +/-20%

CE35D80H90

CE35D80H90

Dummy

Dummy

12V_VRM

12V_VIN7

B B

12V_VIN

*

*

EC11

EC11

1500uF

1500uF

16V, +/-20%

16V, +/-20%

CE50D100H300

CE50D100H300

EC22

EC22

1500uF

1500uF

*

*

16V, +/-20%

16V, +/-20%

CE50D100H300

CE50D100H300

EC38

EC38

1500uF

1500uF

*

*

16V, +/-20%

16V, +/-20%

CE50D100H300

CE50D100H300

*

*

L4

L4

EC23

EC23

1500uF

1500uF

16V, +/-20%

16V, +/-20%

CE50D100H300

CE50D100H300

*

*

Choke Coil 1.2uH

Choke Coil 1.2uH

BC1065

BC1065

0.1uF

0.1uF

*

*

25V, X7R, +/-10%

25V, X7R, +/-10%

C0603

C0603

Dummy

Dummy

3

4

PWR2

PWR2

1

ATX12V_P1_2X2

ATX12V_P1_2X2

PWR4NWP1

PWR4NWP1

5

2

*

*

EC8

560uF

560uF

4V, +/-20%

4V, +/-20%

CE35D80H90

CE35D80H90

Dummy

Dummy

EC9

EC9

560uF

560uF

*

*

4V, +/-20%

4V, +/-20%

CE35D80H90

CE35D80H90

Dummy

Dummy

*

*

TC1

TC1

100uF

100uF

2V,+30/-20%

2V,+30/-20%

ctdh16

ctdh16

Dummy

Dummy

*

*

7/20

TC2

100uF

100uF

2V,+30/-20%

2V,+30/-20%

ctdh16

ctdh16

Reserved

Reserved

VRM Output filter schematics

VCCP

A A

5

EC17

EC17

3300uF

3300uF

**

**

6.3V, +/-20%

6.3V, +/-20%

CE35_50D100H300

CE35_50D100H300

EC32

EC32

3300uF

3300uF

**

**

6.3V, +/-20%

6.3V, +/-20%

CE35_50D100H300

CE35_50D100H300

EC36

EC39

EC37

EC37

3300uF

3300uF

**

**

6.3V, +/-20%

6.3V, +/-20%

CE35_50D100H300

CE35_50D100H300

4

EC39

3300uF

3300uF

**

**

6.3V, +/-20%

6.3V, +/-20%

CE35_50D100H300

CE35_50D100H300

EC36

3300uF

3300uF

**

**

6.3V, +/-20%

6.3V, +/-20%

CE35_50D100H300

CE35_50D100H300

3

TECHNOLOGY COPR.

TECHNOLOGY COPR.

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Output CAP

Output CAP

Output CAP

661M08

661M08

661M08

TECHNOLOGY COPR.

of

844Monday, August 01, 2005

of

844Monday, August 01, 2005

of

844Monday, August 01, 2005

1

A

A

A

Page 10

8 7 6 5 4 3 2 1

A

AAD[0..31]

HDBIJ[0..3]5

HDJ[0..63]5

D D

C C

HAJ[31..3]5

HREQJ[4..0]5

CPUCLK117

CPUCLK-117

HLOCKJ5

HDEFERJ5

HTRDYJ5

HCPURSTJ5

CPUPWRGD_NB14

HBPRIJ5

HBR0J5

HRSJ25

HRSJ15

HRSJ05

HADSJ5

HITMJ5

HITJ5

HDRDYJ5

HDBSYJ5

HBNRJ5

HADSTBJ15

HADSTBJ05

B B

GTLREF_SEL6

G

R54 change from 100 to 149

HDBIJ[0..3]

HDJ[0..63]

HAJ[31..3]

HREQJ[4..0]

CPUCLK1

CPUCLK-1

HLOCKJ

HDEFERJ

HTRDYJ

HCPURSTJ

CPUPWRGD_NB

HBR0J

HADSJ

HITMJ

HITJ

HDRDYJ

HDBSYJ

HBNRJ

HREQJ4

HREQJ3

HREQJ2

HREQJ1

HREQJ0

VCCP

R803

R803

*

*

619

619

+/-1%

+/-1%

R0603

R0603

DS

Q91

Q91

2N7002

2N7002

HBPRIJ

HRSJ2

HRSJ1

HRSJ0

HADSTBJ1

HADSTBJ0

HAJ31

HAJ30

HAJ29

HAJ28

HAJ27

HAJ26

HAJ25

HAJ24

HAJ23

HAJ22

HAJ21

HAJ20

HAJ19

HAJ18

HAJ17

HAJ16

HAJ15

HAJ14

HAJ13

HAJ12

HAJ11

HAJ10

HAJ9

HAJ8

HAJ7

HAJ6

HAJ5

HAJ4

HAJ3

FSB_VTT

*

*

*

*

U6A

U6A

AJ31

CPUCLK

AJ33

CPUCLK#

T33

HLOCK#

T35

DEFER#

V32

HTRDY#

B23

CPURST#

F22

CPUPWRGD

R34

BPRI#

U31

BREQ0#

R33

RS#2

T32

RS#1

U35

RS#0

V35

ADS#

R35

HITM#

U34

HIT#

W34

DRDY#

U33

DBSY#

V33

BNR#

W35

HREQ4#

Y33

HREQ3#

W31

HREQ2#

W33

HREQ1#

Y35

HREQ0#

AG31

HASTB1#

AA33

HASTB0#

R36

DPWR#

AH33

HA31#

AG33

HA30#

AJ35

HA29#

AF32

HA28#

AJ34

HA27#

AH32

HA26#

AG35

HA25#

AE31

HA24#

AH35

HA23#

AF35

HA22#

AE35

HA21#

AE33

HA20#

AE34

HA19#

AF33

HA18#

AG34

HA17#

AC33

HA16#

AD32

HA15#

AD33

HA14#

AC35

HA13#

AD35

HA12#

AC31

HA11#

AC34

HA10#

AB35

HA9#

AB32

HA8#

AB33

HA7#

AA35

HA6#

AA31

HA5#

Y32

HA4#

AA34

HA3#

661FX

661FX

R52 change from 49.9 to 100

R52

R52

49.9

49.9

+/-1%

+/-1%

Rds-on(p) = 56 ohm

HPCVERF = 2/3 VCCP

R54

R54

100

100

+/-1%

+/-1%

BC50

BC50

10nF

10nF

*

*

*

*

place this capacitor

C1XAVSS

C4XAVSS

C4XAVDD

C1XAVDD

AK34

C1XAVSS

C1XAVDD

AJ36

AK35

C4XAVSS

AA26

C4XAVDD

AL36

HOST

HD63#

HD62#

HD61#

HD60#

HD59#

HD58#

HD57#

HD56#

HD55#

F24

E23

B24

B25

C24

HDJ63

HDJ62

HDJ61

HVREF

BC51

BC51

0.1uF

0.1uF

B26

D23

D25

C26

HDJ60

D27

HDJ57

HDJ56

HDJ59

HDJ58

HDJ55

SBA-2

AAD14

AAD7

AAD8

AAD0

AAD1

HNCOMP

W26

HVREF1

HPCOMP

U26

R26

L20

C22

B22

D22

HVREF2

HVREF3

HVREF4

HCOMP_P

HCOMP_N

HCOMPVREF_N

HVREF

HVREF0

AAD2

ST0

ST1

ST2

B5

ST0B6ST1F7ST2

AAD0Y5AAD1W4AAD2V2AAD3W6AAD4V4AAD5U2AAD6V5AAD7U4AAD8R2AAD9

AAD3

AAD9

AAD4

AAD5

AAD6

T4

AAD15

AAD16

AAD11

AAD10

AAD12

AAD13

AAD10R3AAD11T5AAD12P2AAD13R4AAD14N2AAD15R6AAD16L3AAD17L4AAD18K2AAD19L6AAD20J2AAD21J3AAD22K4AAD23J4AAD24J6AAD25H4AAD26G3AAD27H5AAD28F2AAD29G4AAD30E2AAD31

AAD22

AAD23

AAD24

AAD25

AAD26

AAD27

AAD28

AAD29

AAD19

AAD20

AAD21

AAD17

AAD18

AAD30

AAD31

SBA-7

G6

SBA7E3SBA6F4SBA5D2SBA4F5SBA3E4SBA2B2SBA1E6SBA0

AGP

661FX-1

HD54#

HD53#

HD52#

HD51#

HD50#

HD49#

HD48#

HD47#

HD46#

HD45#

HD44#

HD43#

HD42#

HD41#

HD40#

HD39#

HD38#

HD37#

HD36#

HD35#

HD34#

HD33#

HD32#

HD31#

HD30#

HD29#

HD28#

HD27#

HD26#

HD25#

HD24#

HD23#

HD22#

HD21#

HD20#

HD19#

HD18#

HD17#

HD16#

HD15#

HD14#

HD13#

HD12#

HD11#

HD10#

HD9#

HD8#

J34

J33

J31

J35

L31

L33

B27

F28

B28

E29

B29

B30

B31

B33

B35

B34

D28

C28

C30

C32

HDJ49

HDJ48

HDJ51

HDJ50

HDJ47

HDJ46

D29

HDJ45

HDJ44

HDJ41

HDJ40

HDJ43

HDJ42

under 661 solder side

E31

C33

D32

HDJ37

HDJ36

HDJ35

HDJ34

HDJ39

HDJ38

E27

D26

HDJ53

HDJ52

HDJ54

F33

F32

E35

F35

H35

G34

HDJ25

HDJ24

HDJ21

HDJ20

HDJ23

HDJ22

BC54

BC54

0.1uF

0.1uF

*

*

K32

H33

G35

HDJ17

HDJ16

HDJ19

HDJ18

HDJ15

HDJ14

D31

HDJ33

E33

D33

D35

C35

D34

G31

HDJ32

HDJ29

HDJ28

HDJ27

HDJ26

HDJ31

HDJ30

C1XAVDD C4XAVDD

C1XAVSS

L35

K33

K35

N33

HDJ13

HDJ12

HDJ9

HDJ8

HDJ11

HDJ10

SBA-6

HD7#

M35

M33

HDJ7

SBA-5

SBA-4

HD6#

HD5#

P32

HDJ5

HDJ6

SBA-1

SBA-3

HD4#

HD3#

HD2#

L34

P33

N34

HDJ4

HDJ3

HDJ2

C4XAVSS

SBA-0

B3

ADBIH/PIPE#

AGPCOMP_P

AGPCOMP_N

AGPVSSREF

HD1#

HD0#

P35

N35

HDJ1

HDJ0

VCC3VCC3

*

*

AC/BE3#

AC/BE2#

AC/BE1#

AC/BE0#

AREQ#

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

APAR

RBF#

WBF#

GC_DET#

ADBIL

SB_STB

SB_STB#

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

AGPCLK

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AGPVREF

HDSTBN3#

HDSTBN2#

HDSTBN1#

HDSTBN0#

HDSTBP3#

HDSTBP2#

HDSTBP1#

HDSTBP0#

DBI3#

DBI2#

DBI1#

F26

B32

E34

R31

HDBIJ2

HDBIJ1

HDBIJ3

BC53

BC53

0.1uF

0.1uF

K5

M5

P4

U6

C6

E8

N6

M4

N4

L2

P5

M2

N3

D7

B4

C7

C4

D6

C2

D3

T2

U3

G2

H2

D8

W2

Y2

B8

C8

A7

B7

W3

Y4

D24

F30

G33

N31

E25

D30

H32

M32

DBI0#

HDBIJ0

AC-BE3

AC-BE2

AC-BE1

AC-BE0

GCDETDBI_HI

DBI_LOW

ADSTBF0

ADSTBS0

ADSTBF1

ADSTBS1

AGPCLK0

AGPRCOMP

AGPRCOMN

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

HDSTBNJ3

HDSTBNJ2

HDSTBNJ1

HDSTBNJ0

HDSTBPJ3

HDSTBPJ2

HDSTBPJ1

HDSTBPJ0

SBA-[0..7]

AC-BE[0..3]

ST[0..2]

ADSTBF[0..1]

ADSTBS[0..1]

AREQ 19

AGNT 19

AFRAME 19

AIRDY 19

ATRDY 19

ADEVSEL 19

ASERR 19

ASTOP 19

APAR 19

RBF 19

WBF 19

GCDET- 19

DBI_HI 19

DBI_LOW 19

SBSTBF 19

SBSTBS 19

AGPCLK0 17

AVREFGC 19

HDSTBNJ3 5

HDSTBNJ2 5

HDSTBNJ1 5

HDSTBNJ0 5

HDSTBPJ3 5

HDSTBPJ2 5

HDSTBPJ1 5

HDSTBPJ0 5

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

661FX-1 HOST & AGP

661FX-1 HOST & AGP

661FX-1 HOST & AGP

AAD[0..31] 19

SBA-[0..7] 19

AC-BE[0..3] 19

ST[0..2] 19

ADSTBF[0..1] 19

ADSTBS[0..1] 19

FSB_VTT

R48 14

R48 14

*

*

R49 change from 100 to 120

R49 100

R49 100

*

*

HNCOMP

HPCOMP

R48 R49

648 10 1% 113 1%

648FX

661FX

AGPRCOMN

AGPRCOMP

BC48, BC49 Change to 0.1uF?

661M08

661M08

661M08

14 1%

14 1%

AGP3.0 = 50 ohm

R50 51

R50 51

*

*

R51 43.2

R51 43.2

*

*

VCC3

A1XAVDD

BC48

BC48

10nF

10nF

*

*

A1XAVSS

VCC3

A4XAVDD

BC49

BC49

10nF

10nF

*

*

A4XAVSS

TECHNOLOGY COPR.

TECHNOLOGY COPR.

TECHNOLOGY COPR.

944Monday, August 01, 2005

944Monday, August 01, 2005

944Monday, August 01, 2005

100 1%

100 1%

VDDQ

of

of

of

A

A

A

A

Page 11

8 7 6 5 4 3 2 1

A

MD[0..63]

DQM[0..7]

DQS[0..7]

MA[0..14]

CS-[0..3]

CKE[0..3]

D D

VCC2.5_MEM

BC590

*

C0603

C0603

C0603

C0603

*

*

BC590

BC589

BC589

0.1uF

0.1uF

0.1uF

0.1uF

*

*

*

BC591

BC591

0.1uF

0.1uF

C0603

C0603

BC592

BC592

0.1uF

0.1uF

*

*

C0603

C0603

C C

VCC2.5_MEM

BC596

BC596

BC595

BC595

BC594

BC594

0.1uF

0.1uF

0.1uF

0.1uF

*

*

C0603

C0603

*

*

*

*

C0603

C0603

0.1uF

0.1uF

C0603

C0603

BC597

BC597

0.1uF

0.1uF

*

*

C0603

C0603

B B

BC593

BC593

0.1uF

0.1uF

*

*

C0603

C0603

*

*

MD[0..63] 21,23

DQM[0..7] 21,23

DQS[0..7] 21,23

MA[0..14] 21,23

CS-[0..3] 21,23

CKE[0..3] 21

BC598

BC598

0.1uF

0.1uF

C0603

C0603

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7

AN35

AP36

AK33

AM33

AN34

AK32

AR34

AN33

AR35

AP34

AM32

AL31

AR31

AL30

AN32

AR33

AN31

AM31

AR32

AP32

AP30

AR30

AM29

AL27

AN30

AN29

AL28

AN28

AL29

AR29

AP26

AN25

AR24

AL24

AL25

AR26

AM25

AN24

AP24

AR25

AN21

AP20

AN20

AL18

AM21

AR21

AL19

AM19

AL20

AR20

AL15

AL14

AN15

AR15

AN16

AM15

AN14

AL13

AP16

AR16

AM13

AL12

AL11

AR12

AP14

AR14

AN13

AP12

AN12

AR13

AL10

AR11

AM9

AR9

AM11

AN11

AP10

AN9

AN10

AR10

U6B

U6B

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0/CSB0#

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1/CSB1#

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2/CSB2#

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3/CSB3#

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4/CSB4#

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5/CSB5#

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6/CSB6#

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7/CSB7#

661FX

661FX

661FX-2

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

SRAS#

SCAS#

SWE#

CS0#

CS1#

CS2#

CS3#

CS4#

CS5#

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

S3AUXSW#

FWDSDCLKO

DRAMTEST

DLLAVDD

DLLAVSS

DDRAVDD

DDRAVSS

DDRVREFA

DDRVREFB

TRAP2

DDRCOMP_P

DDRCOMP_N

put bottom side

DDRVREFA

MA0

AR23

MA1

AN23

MA2

AN22

MA3

AM23

MA4

AL23

MA5

AL26

MA6

AN26

MA7

AN27

MA8

AR27

MA9

AR28

MA10

AP22

MA11

AN18

MA12

AR22

MA13

AP28

MA14

AM27

AT14

NC

AL17

AR19

AN19

AM17

AL16

AN17

AR17

AP18

AR18

AP4

AT3

AR3

AP3

AR2

AN4

AP2

AL21

AL22

AL35

AL34

AM35

AN36

AF16

AF23

AP1

AR8

AP8

SRASSCASSWE-

CS-0

CS-1

CS-2

CS-3

R60 22

R60 22

DLLAVDD

DLLAVSS

DDRAVDD

DDRAVSS

DDRVREFA

DDRVREFB

DDRCOMP

DDRCOMN

/RSRAS- 21,23

/RSCAS- 21,23

/RSWE- 21,23

SB3V

CKE0

CKE1

CKE2

CKE3

*

*

FWDSDCLKO

DDRCOMN

DDRCOMP

FWDSDCLKO 18

R61 40.2

R61 40.2

R62 40.2

R62 40.2

*

*

*

*

R785

R785

*

*

4.7K

4.7K

+/-5%

+/-5%

R0603

R0603

S3AUXSW- 28,37

VCC2.5_MEM

DDRAVDD

DDRAVSS

DLLAVDD

DLLAVSS

DDRVREFB

FWDSDCLKO

BC58

BC58

0.1uF

0.1uF

*

*

BC59

BC59

0.1uF

0.1uF

*

*

FB21 BLM18BB470SN1DFB21 BLM18BB470SN1D

FB22 BLM18BB470SN1DFB22 BLM18BB470SN1D

VCC2.5_MEM

R56

R56

*

*

150

150

R57

21

21

R57

*

*

150

150

VCC2.5_MEM

*

*

*

*

BC57

BC57

10pF

10pF

*

*

VCC3

VCC3

R58

R58

150

150

R59

R59

150

150

BC55

BC55

10nF

10nF

*

*

BC56

BC56

10nF

10nF

*

*

A

TECHNOLOGY COPR.

TECHNOLOGY COPR.

Title

Title

Title

Document Number Rev

Document Number Rev

Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

661FX-2 DDR

661FX-2 DDR

661FX-2 DDR

661M08

661M08

661M08

TECHNOLOGY COPR.

A

A

of

10 44Monday, August 01, 2005

of

10 44Monday, August 01, 2005

of

10 44Monday, August 01, 2005

A

Page 12

8 7 6 5 4 3 2 1

A

Enable Disable

RSYNC

U6C

D D

ZCLK0

ZUREQ

ZDREQ

ZSTB0

ZSTB-0

ZSTB1

ZSTB-1

ZVREF

ZCMP_N

ZCMP_P

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

ZCLK017

ZUREQ13

ZDREQ13

ZSTB013

ZSTB-013

ZSTB113

ZSTB-113

NBPWRGD38

ZAD[0..16]13

VCC1.8V VCC3

R65

R65

*

*

150

150

ZVREF

BC60

R70

R70

*

*

51.1

51.1

BC60

0.1uF

0.1uF

*

*

ZAD[0..16]

C C

VCC3

Z4XAVDD

BC64

BC64

0.1uF

0.1uF

*

*

Z4XAVSS

U6C

AL6

ZCLK

AL4

ZUREQ

AK5

ZDREQ

AJ2

ZSTB0

AJ3

ZSTB0#

AE3

ZSTB1

AF2

ZSTB1#

AH5

ZAD0

AK2

ZAD1

AJ4

ZAD2

AJ6

ZAD3

AH2

ZAD4

AH4

ZAD5

AG3

ZAD6

AG6

ZAD7

AF4

ZAD8

AG2

ZAD9

AF5

ZAD10

AG4

ZAD11

AD2

ZAD12

AE6

ZAD13

AE2

ZAD14

AE4

ZAD15

AL3

ZAD16

AK4

ZVREF

AD5

ZCOMP_N

AD4

ZCOMP_P

AN1

Z1XAVDD

AM2

Z1XAVSS

AL2

Z4XAVDD

AL1

Z4XAVSS

661FX

661FX

NBRST-6,13

AUXOK14,36

NBPWRGD

AUXOK ENTEST

661FX-3

HyperZip

PCIRST#

PWROK

AUXOK

TRAP1F9TRAP0

AN2

AN3

AM4

D10

TESTMODE2C9TESTMODE1B9TESTMODE0

B10

VGA

DLLEN#

ENTEST

D9

E10

DACAVDD1

DACAVSS1

DACAVDD2

DACAVSS2

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

VOSCI

ROUT

GOUT

BOUT

HSYNC

VSYNC

VGPIO0

VGPIO1

INT#A

CSYNC

RSYNC

LSYNC

VCOMP

VRSET

VVBWN

A15

B12

B13

A13

A11

B11

E13

C11

C10

D12

E12

D11

E15

D15

E14

D13

C12

D14

C13

B15

C15

B14

C14

*

*

*

*

VCOMP

VRSET

VVBWN

DACAVDD

DACAVSS

DACAVDD

DACAVSS

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

R6433*R6433

R6633*R6633

R67100*R67100

R68100*R68100

REFCLK2 17

ROUT 20

GOUT 20

BOUT 20

HSYNC 20

VSYNC 20

DDC1CLK 20

DDC1DATA 20

INT-A 13,19,24,25

CSYNC

RSYNC

LSYNC

B B

VCC1.8V

*

*

BC70

BC70

0.1uF

0.1uF

DUMMY

DUMMY

R72 56

R72 56

R73 56

R73 56

U6_1

U6_1

+/-5%

+/-5%

*

*

R0603

R0603

+/-5%

+/-5%

*

*

R0603

R0603

ZCMP_N

ZCMP_P

VCC3

*

*

Z1XAVDD

BC71

BC71

0.1uF

0.1uF

Z1XAVSS

LSYNC

CSYNC VB

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

VVBWN

BC66 0.1uF

BC66 0.1uF

VCOMP

BC67 0.1uF

BC67 0.1uF

DACAVDD

DACAVSS

Put the cap bottom side

panel link

RSYNC

ENTEST

LSYNC

CSYNC

RSYNC

NBPWRGD

AUXOK

*

*

*

*

BC68

BC68

*

*

0.1uF

0.1uF

VGA

RN6 4.7K

RN6 4.7K

R69 4.7KDUMMY

R69 4.7KDUMMY

BC61 0.1uF

BC61 0.1uF

BC62 0.1uF