Service Manual

/ ON

LAST MEMO

RETURNON SCREEN A-B REPEAT

TV CH+ TV VOL+

TV POWER

P

U

T

E

S

SHIFT

ENTER

T

REV

I

T

L

SLOW

E

R

E

V

P

L

P

R

E

V

P

A

U

S

E

/

S

T

E

P

213

ANGLE A.REPLAY ZOOM

546

AUDIO

BOOKMARK

879

0

PROGRAM

SURROUND

BASS

-

REMOTE CONTROLLER RB-H5201ST

REPEAT

TV VOL-TV CH-TV/VIDEO

M

E

N

U

PICTURE

MODE

SEARCH

MODE

E

FWD

L

T

I

SLOW

T

B

U

S

D

W

F

Y

A

T

X

E

N

P

O

T

S

SLEEP

C

FUNCTION

SOUND

VOLUME

+

DVD Home Theater System

CONTENTS

Specifications .............................................................................. 1

Laser beam safety precaution.....................................................2

DVD mechanism replacement .................................................... 2

Removal & Installation ................................................................ 3

Mechanism replacement............................................................. 4

Mechanism operation..................................................................5

DVD P.W.Board operation .......................................................... 6

DVD P.W.Board operation

(Schematic diagram for signal check)......................................... 8

DVD P.W.Board operation

(Wiring diagram for signal check) ............................................... 18

DVD P.W.Board operation(Signal)..............................................20

DVD start-up program flow chart ................................................ 28

How to load software for MPEG P.W.Board ............................... 30

MPEG and FRONT END

P.W.Board operation (Block diagram) ...................................... 30

MPEG P.W.Board operation

(schematic diagram for waveform check) ................................... 32

MPEG and FRONT END

P.W.Board check waveform......................................................34

Trouble shooting ......................................................................... 41

Voltage of IC & Transistor ........................................................... 44

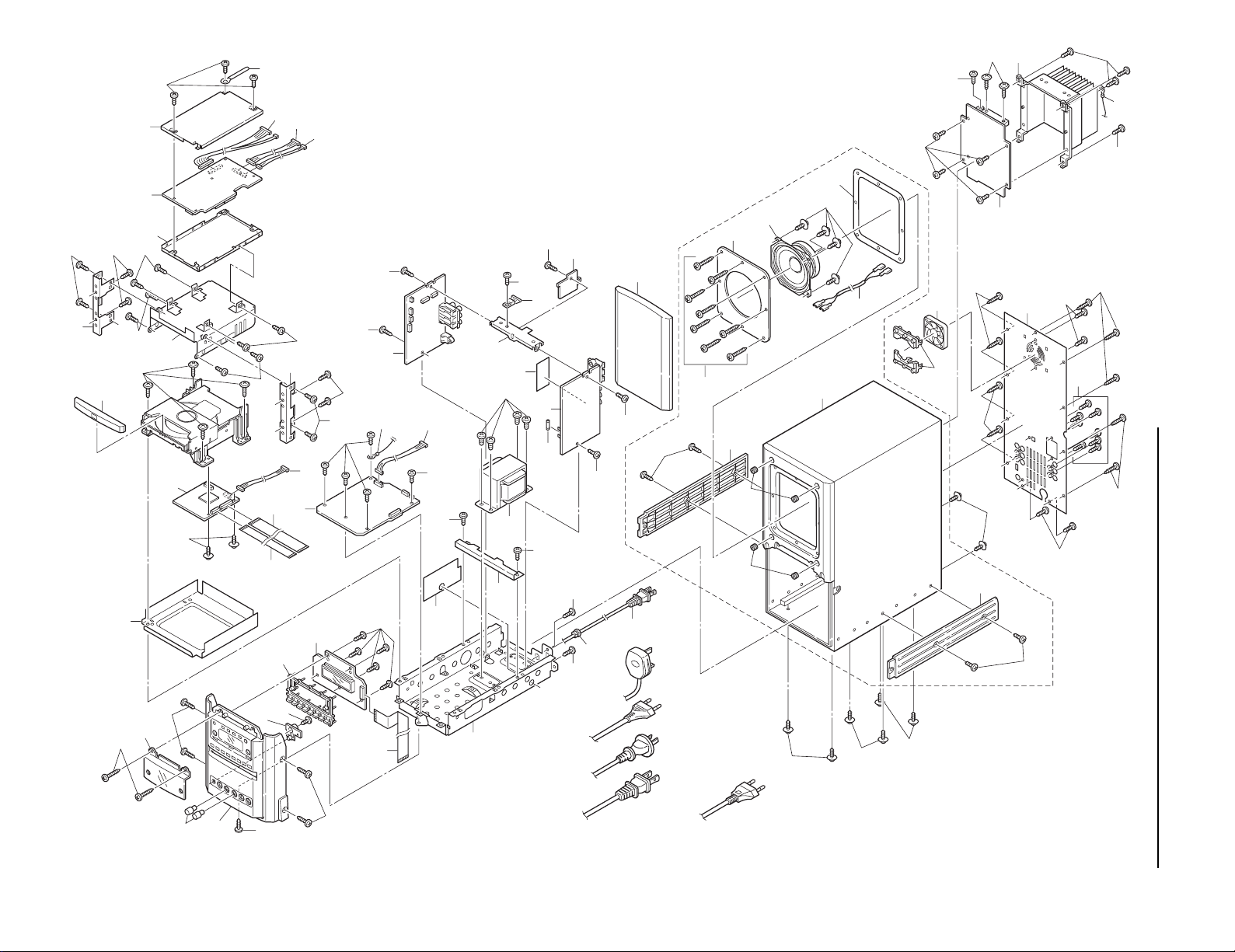

Exploded view (Cabinet & Chassis)........................................... 47

Parts list ...................................................................................... 48

Parts list & Exploded view (SP box)............................................57

Exploded view (DVD mechanism) ............................................. 58

IC Block diagram & description ................................................... 59

Memo .......................................................................................... 73

Schematic Diagram (MPEG)......................................................74

FILE NO.

DWM-1000

HTD-5201

PRODUCT CODE No.

129 590 00 (1000)

129 590 01 (XE)

129 590 02 (UK)

129 590 03 (SS)

129 590 04 (KR)

129 590 05 (US)

129 590 06 (CA)

129 590 07 (AU)

Wiring Diagram (MPEG A SIDE) ............................................... 76

Wiring Diagram (MPEG B SIDE) ............................................... 78

Schematic Diagram (AMP for 1000,US,CA) .............................. 80

Wiring Diagram (Pre AMP,Power AMP,Video AMP,

Socket-A for 1000,US,CA) ........................................................ 82

Schematic Diagram (AMP for XE,UK) ....................................... 86

Wiring Diagram (Pre AMP,Power AMP,Video AMP,

Socket-A for XE,UK) ................................................................. 88

Schematic Diagram (AMP for SS) ............................................. 92

Wiring Diagram (Pre AMP,Power AMP,Video AMP,

Socket-A for SS) ....................................................................... 94

Schematic Diagram (AMP for KR) ............................................. 98

Wiring Diagram (Socket-A for KR) .............................................. 100

Wiring Diagram (Regulator & Digital Out) ................................... 101

Schematic Diagram (AMP for AU) ............................................. 102

Wiring Diagram (Pre AMP,Power AMP,Video AMP,

Socket-A for AU) ....................................................................... 104

Wiring Diagram (Front for 1000,US,CA) .................................... 108

Wiring Diagram (Front for XE,UK) ............................................. 109

Schematic Diagram (Front for 1000,XE,UK,US,CA)................... 110

Schematic Diagram (Front for SS,KR)....................................... 112

Wiring Diagram (Front for SS,KR) .............................................. 114

Wiring Diagram (Front for AU) .................................................... 115

Schematic Diagram (Front for AU).............................................116

Schematic Diagram (DVD).........................................................118

Wiring Diagram (DVD A side) ..................................................... 128

Wiring Diagram (DVD B side) ..................................................... 129

Wiring Connection (1000,US,CA,AU) ......................................... 130

Wiring Connection (XE,UK,SS,KR).............................................Rear

R

(US)

(XE)

(UK)

(SS)

(KR)

(US)

(CA)

(AU)

This service manual consists of "DWM-1000M"[US](Main unit: 129 591 00), "DWM-1000SP"[US](Speaker system: 165 029 00). "HTD-5201M"

[XE](Main unit: 129 591 01), [UK](Main unit: 129 591 02), [SS](Main unit: 129 591 03), [KR](Main unit: 129 591 04), [US](Main unit: 129 591 05),

[CA](Main unit : 129 591 06), [AU](Main unit: 129 591 07), "SX-5201/XE" [XE](Speaker system: 165 029 01), "SX-5201/SS" [UK,SS,KR,AU](Speaker

system: 165 029 02), "STM-5201/US" [US](Speaker system: 165 029 04) and SX-5201/CA[CA](Main unit: 165 029 05).

REFERENCE No.

SM5810205

SPECIFICATIONS

Main unit with Main Speaker

Amplifier Section

<US>

Main Amplifier

Continuous minimum sine wave RMS power output

per channel at 1kHz into 6 ohms with no more than

10 % total harmonic distortion ................ 3 0 W a t t s

Subwoofer Amplifier

Continuous minimum sine wave RMS power output at

100Hz into 6 ohms with no more than 10 % total

harmonic distortion ..................................... 30 Watts

General

Output power

Total power : 90W

Main Amplifier : 30 x 2 (at 6 ohms, 10% distortion)

Subwoofer Amplifier : 30W (st 6 ohms, 10% distortion)

Input level and impedance:

VIDEO: VIDEO IN : 1.0 Vp-p (75 ohms)

AUDIO IN (L/R): 600 mV/50k ohms

AUX/TV (L/R): 600 mV/50k ohms

Outputs:

MAIN SPEAKER (L/R): 6 ohms

SUBWOOFER: 6 ohms

PHONES:8-32 ohms (XE,UK,SS,KR,AU)

DIGITAL OUT: Optical

AV EURO CONNECTOR : For Euro-AV cable (XE,UK)

COMPONENT VIDEO OUT: CB/CR: 0.7 Vp-p (75 )

Y: 1.0 Vp-p (75 )

MONITOR VIDEO OUT: 1.0 Vp-p (75 ohms)

AUDIO OUT (L/R): 600 mV (1 kohms)

S-VIDEO OUT: Y: 1.0 Vp-p (75 ohms)NTSC

Y: 1.0 Vp-p (75 ohms)PAL

C: 0.286 Vp-p (75 ohms)NTSC

C: 0.3Vp-p (75 ohms)PAL

Main Speaker (magnetic shield)

Unit used: 10cm ( 4" diameter), Cone type

Maximum music power handling capacity: 60 Watts

Nominal impedance: 6 ohms

General

Power requirements: AC 120V, 60Hz (1000,US,CA)

AC 230V, 50Hz (XE,UK)

AC 230-240V,50Hz (AU)

AC 220V, 60Hz (KR)

Power consumption: 100 Watts

1.4W (standby mode)

Dimensions (W x H x D):Approx. 200(W) x 400(H) x 320(D) mm

Approx. 7.9" x 15.9" x 12.6"

Weight: :Approx.8.7 kg (19.4 lbs)

Main Speaker with Subwoofer (magnetic shield)

Main Speaker

Unit used: 10cm (4" diameter), Cone type

Maximum music power handling capacity: 60 Watts(peak)

Nominal impedance: 6 ohms

Subwoofer

Unit used: 13cm ( 5.1" diameter), Cone type

Maximum music power handling capacity: 60 Watts (peak)

Nominal impedance: 6 ohms

General

Dimensions (W x H x D): Approx 200(W) x 400(H) x 320(D) mm

Approx. 7.9" x 15.9" x 12.6"

Weight: Approx. 5.8 kg (13.2 lbs)

IMPORTANT INFORMATION

Because its products are subject to continuous improvement,

SANYO reserves the right to modify product designs and

specifications without notice and without incurring any obligation.

Specifications subject to change without notice.

DVD Video Player Section

Type: DVD/CD player

Playback standard : PAL or NTSC

Laser: Semiconductor laser, wavelength 650 nm

Laser output (Continuous wave max.)

1mW (DVD)

0.5mW (CD)

Frequency range (digital audio):

4 Hz to 44 kHz (DVD fs: 96 kHz)

Signal to noise ratio: More than 105 dB

Harmonic distortion (digital audio): 0.003 %

Wow and flutter: Below measurable level

- 1 -

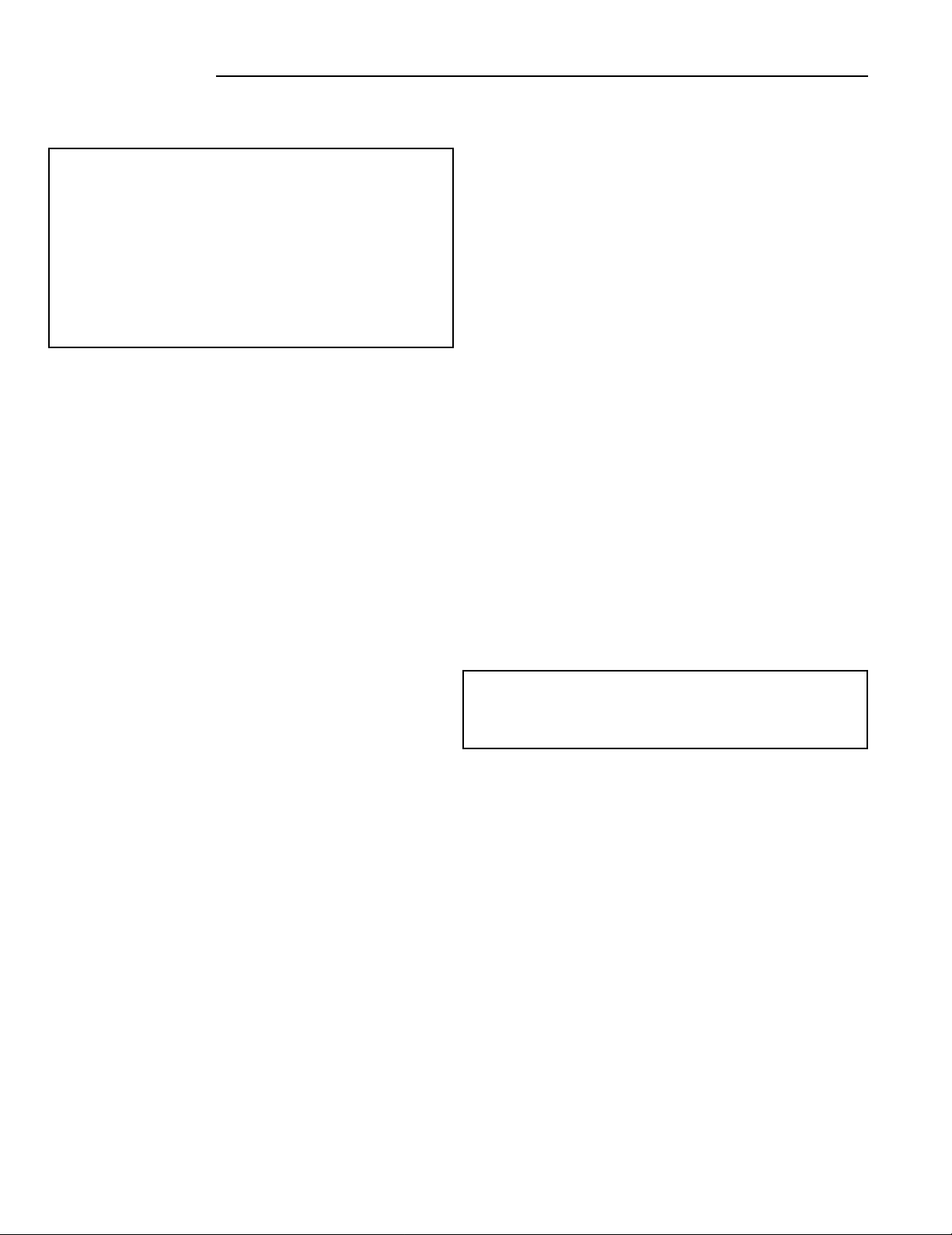

LASER BEAM SAFETY PRECAUTION

SUB

WOOFER

VIDEO IN

AUDIO IN

VIDEO OUT SELECT

RGB

S-VIDEO

S-VIDEO OUT

(DVD ONLY)

MONITOR

VIDEO OUT

AUDIO OUT

R

L

R

VIDEO

AUX/TV

LRL

R

L

OPTICAL

DIGITAL OUT

TV SYSTEM

AV EURO

CONNECTOR

(RGB OUT)

PAL

NTSC

SPEAKERS(6ΩMIN.)

XE,UK,SS,AU

XE,SS

CAUTION – INVISIBLE LASER RADIATION WHEN OPEN AND

INTERLOCKS DEFEATED. AVOID EXPOSURE TO BEAM.

ADVARSEL – USYNLIG LASER STRÅLING VED ÅBNING, NÅR

SIKKERHEDSAFBRYDERE ER UDE AF FUNKTION, UNDGÅ UDS ÆTTELSE

FOR STRÅLING.

VARNING – OSYNLIG LASER STRÅLNING NÄR DENNA DEL ÄR ÖPPNAD

OCH SPÄRR ÄR URKOPPLAD. STRÅLEN ÄR FARLIG.

VORSICHT – UNSICHTBARE LASERSTRAHLUNG TRITT AUS, WENN

DECKEL GEÖFFNET UND WENN SICHERHEITSVERRIEGELUNG

ÜBERBRÜCKT IST. NICHT, DEM STRAHL AUSSETZEN.

VARO – AVATTAESSA JA SUOJALUKITUS OHITETTAESSA OLET ALTTIINA

NÄKYMÄTTÖMÄLLE LASERSÄTEILYLLE. ÄLÄ KATSO SÄTEESEEN.

DVD MECHANISM REPLACEMENT

1. Cautionary instructions in handling the assy

(Safety instructions)

Optical pickup

The laser beam used in the pickup is classified as "class 2". Exposing

your eyes or skin to the beam is harmful. Take care not to do so.

(Caution against static electricity and leakage voltage)

Ground securely the work tables, tools, fixtures, soldering irons

(including those made of ceramic) and measuring instruments used

in the production lines and inspection departments that handle

loaders. The workers shall also be grounded.

(Cautionary instructions in handling)

Do not touch the object lens when handling a loader, or the lens

will be stained, resulting in inadequate playability.

There is no power supply protection circuit provided for this product

or adjustment/inspection device. Short-circuiting may lead to fire or

damage.

Take care so as to protect from exposure to water, the entry of

metallic pieces or dew condensation.

In particular, a strong magnet adjacent to the pickup will not only

get inoperative but can damage the pickup if a small metallic piece,

such as a screw or swarm, enters.

The loader edge can cause injury if inadvertently handled.

Do not touch a rotating disk, or injury may result.

This product is a precision device. Handle carefully.

A shock or dropping will cause misalignment or destruction. If it

should occur, refer to clause 2.

This product is so designed as to endure an initial shock equivalent

to a drop from a height of approx. 90 cm under the packed condition.

After the initial shock, the resistivity will still remain at a level of 50

to 60 G, but the mechanical robustness

The entry and deposition of dirt into or on the pickup lens or moving

section will cause malfunction or degradation.

SPEAKERS(6ΩMIN.)

TV SYSTEM

L

R

SUB

WOOFER

VIDEO IN

LRL

AUDIO IN

R

VOLTAGE SELECTOR

PAL

NTSC

OPTICAL

DIGITAL OUT

C

R

C

B

VIDEO

AUX/TV

230V

115V

COMPONENT

VIDEO OUT

(DVD ONLY)

XE,UK SS,AU

(Connectors)

Do not connect or disconnect while power is on.

Connecting or disconnecting signal wires or the main power cord

when the power is on may destruct the unit or fixture.

When connecting, push all the way in securely.

An insufficient insertion may cause a bad contact, leading to an

erroneous operation.

Do not connect or disconnect roughly by an excessively strong force,

or a broken wire or bad contact may result.

Semiconductors are connected. Do not touch connector terminals

directly.

If the worker is grounded, there is nothing to worry about static

electricity, but the rust on the connector terminal surface caused

by the touch may result in bad contact.

(Power source)

The power source need be good in quality (free from instantaneous

interruptions or noises).

A low quality power source may well cause malfunction.

(Storage)

Do not place or store in a dusty place or a place where dew

condensation is possible.

The entry and deposition of dirt or dust into or on the pickup lens or

moving section will cause malfunction or degradation.

Also, dew condensation causes rust ; the rust penetrate into the

precision part of a pickup, causing malfunction, or degrading the

optical quality of the internal lens and reflector, which also leads to

malfunction.

- 2 -

MONITOR

VIDEO OUT

AUDIO OUT

RLY

VIDEO OUT SELECT

COMPONENT

S-VIDEO

S-VIDEO OUT

(DVD ONLY)

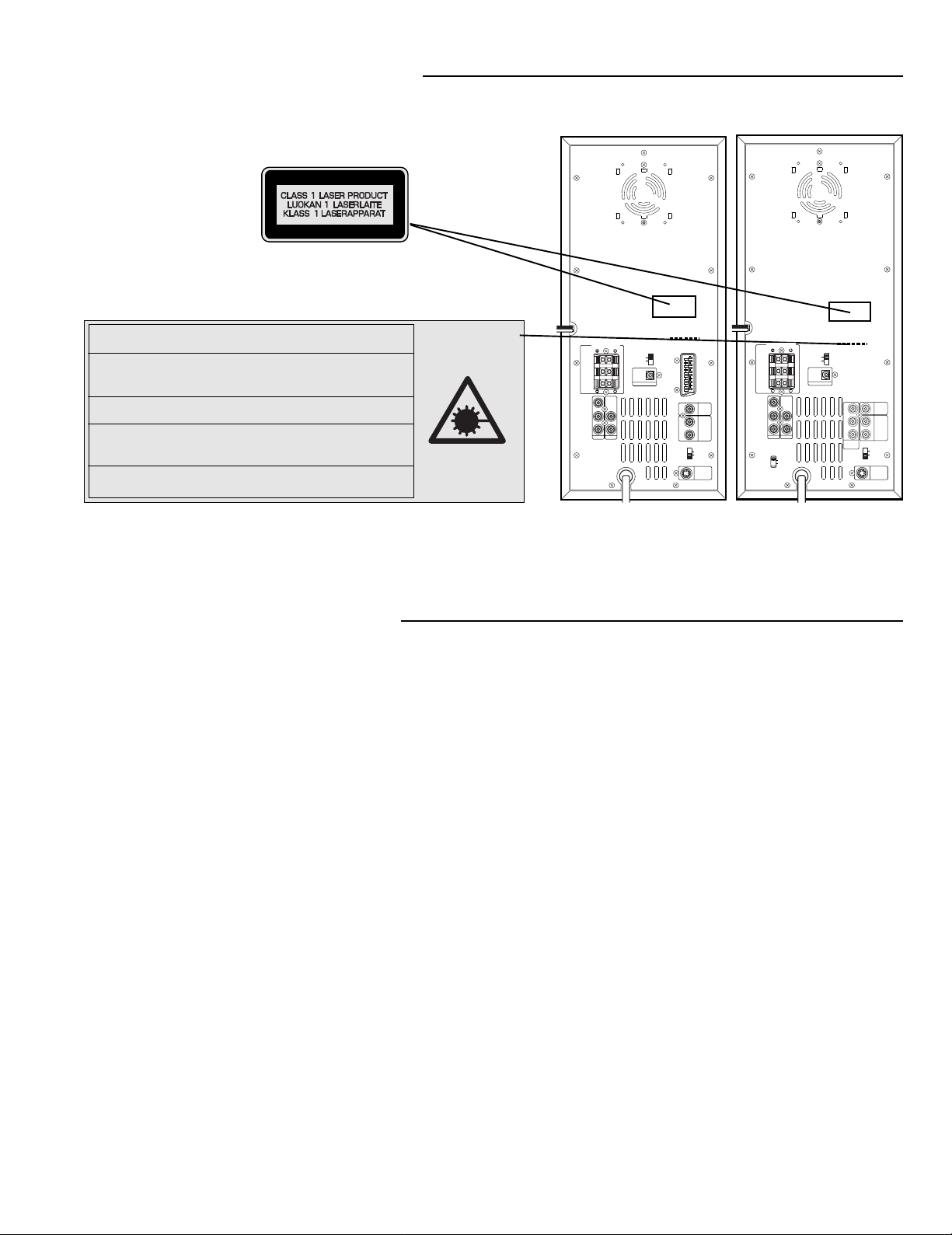

REMOVAL & INSTALLATION

Remove the power supply cord from AC outlet.

All wiring should be returned to the original position after work is completed.

Check and maintenance can do, if operate the following order.

1. Removal Rear Panel 2. Removal Power supply P.W.B.

3

CN439

2

4

CN438

2

CN472

CN471

3

CN475 CN477

CN476

CN470

CN474

UK,XE only

3. Removal Front grill Block

3

CN439

1

1

2

1

3

1

4

1000,XE,UK,US,CA,AU

5

2

4

SS,KR

- 3 -

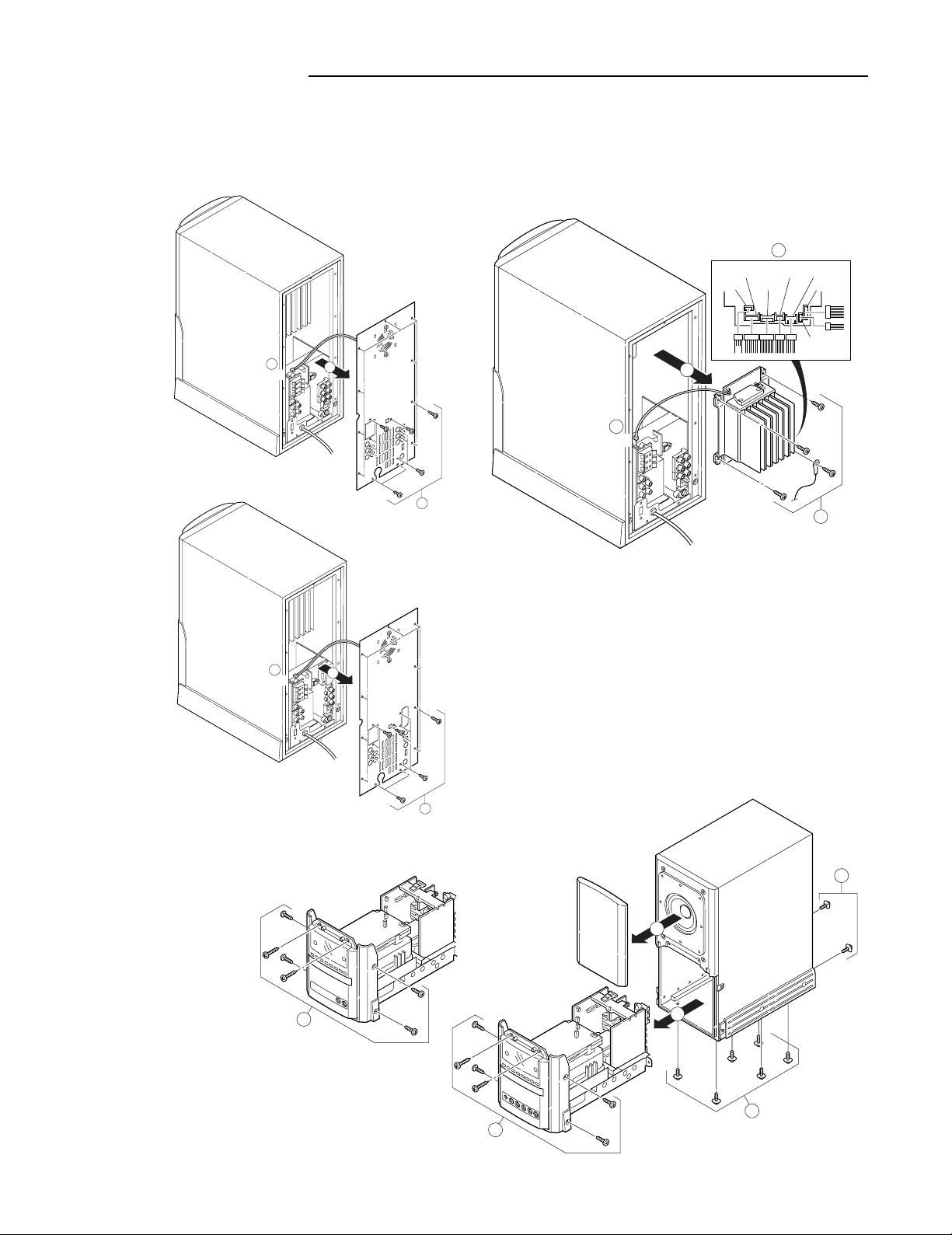

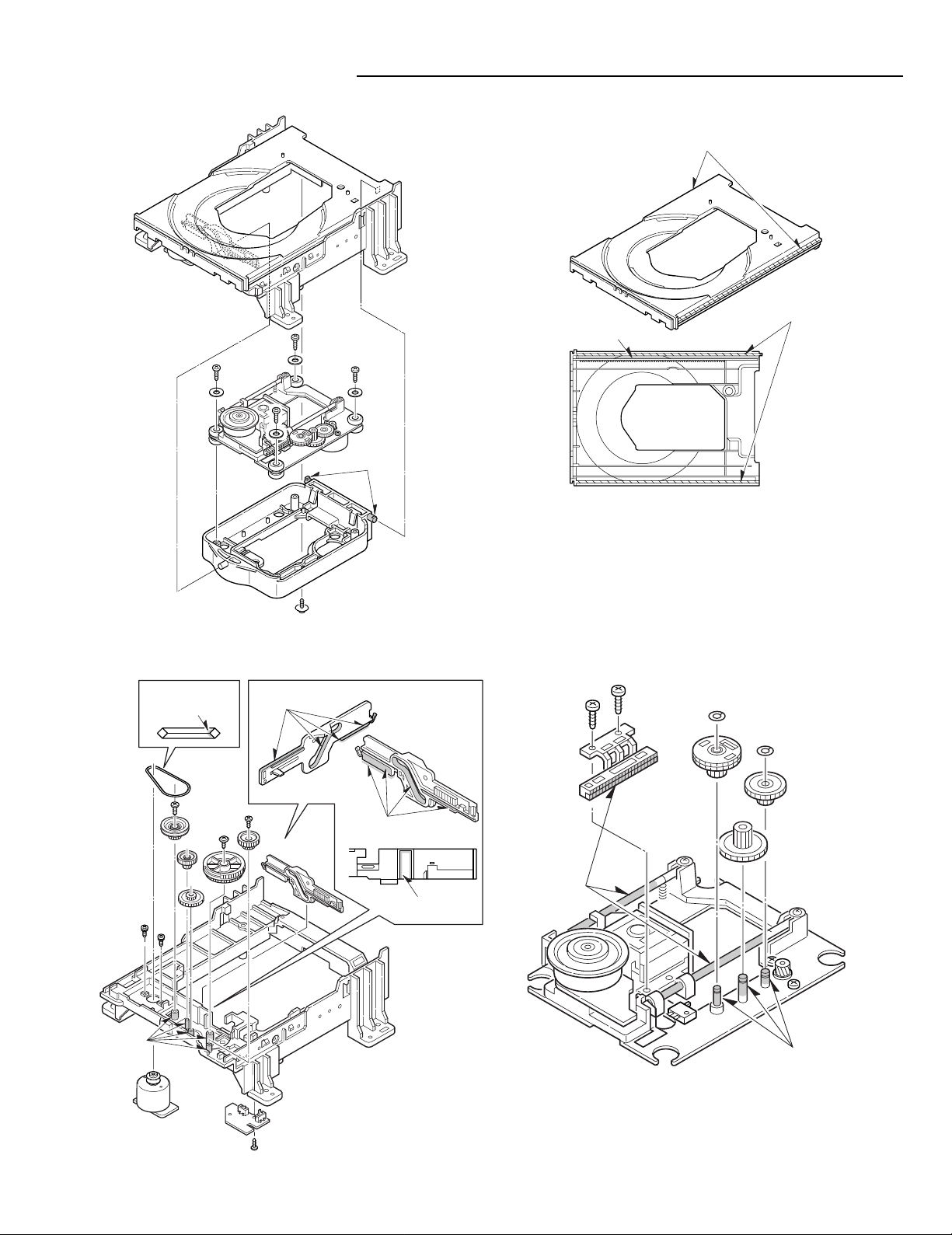

MECHANISM REPLACEMENT

FLOIL OIL

G-2000B

FLOIL OIL

G-2000B

1. TRAY and BASE MechanismPart

FLOIL OIL

G-474B

3. TRAY Part

MOLYKOTE

EM-50L

GREASE

CDF-409

GREASE

CDF-409

2. BASE Mechanism Mounting Part

SILICON GREASE

KS-64

MOLYKOTE

EM-50L

MOLYKOTE

EM-50L

4. BASE Mechanism Part

MOLYKOTE

EM-50L

MOLYKOTE

EM-50L

Do not remove the pick-up from base mechanism because of

adjustment difficulty.

- 4 -

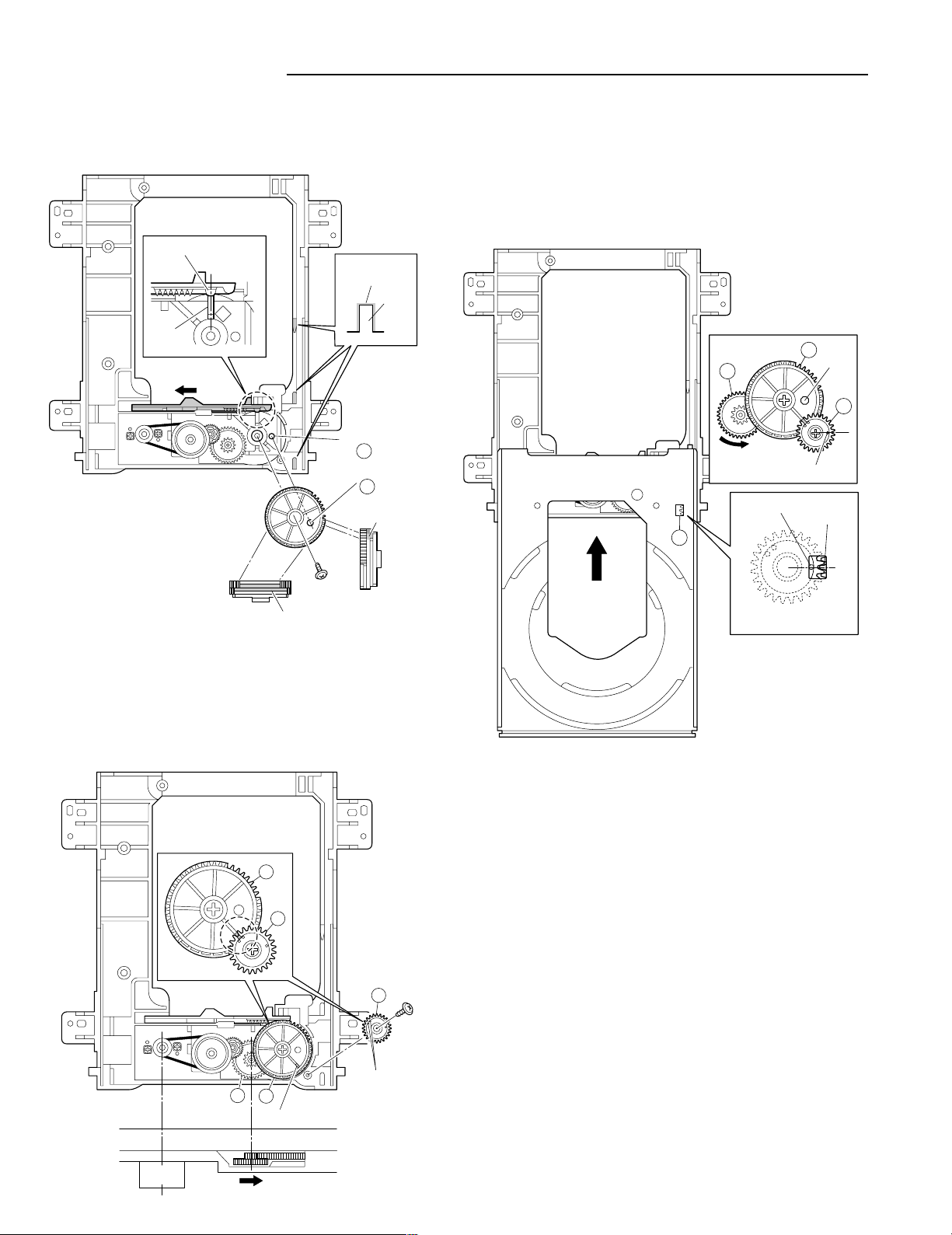

MECHANISM OPERATION

1.How to setting the TRAY

1. Move the SLIDE left side.

2. Match the Hole of GEAR

LARGE TOOTH

5 and Hole of CHASSIS 4.

GREASE

EM-50L

RIB

6. Match the hole of GEAR 7 and hole of chassis while turning

GEAR 6.

7. Match the mark of LOADING GEAR

8 and gear of TRAY

where see horn hole 9 of tray.

8. Push a TRAY with the state that turned the entire surface of a

TRAY into approximately 5 degrees the lower part slowly.

RIB

CHASSIS HOLE

4

GEAR HOLE

5

GREASE

EM-50L

GREASE

EM-50L

3. Match the mark of GEAR 2 and mark of GEAR 3, and then

install the BOSS.

4. Turn the GEAR

1 counterclockwise, and then SLIDE move

right side.

5. The GEAR

1 move from side to side.

TRAY

7

6

HOLE

8

MARKER

MARKER

LOARDING

GEAR

9

MOTOR

CHASSIS

FRONT SIDE

3

2

2

MARKER

1

3

MARKER

- 5 -

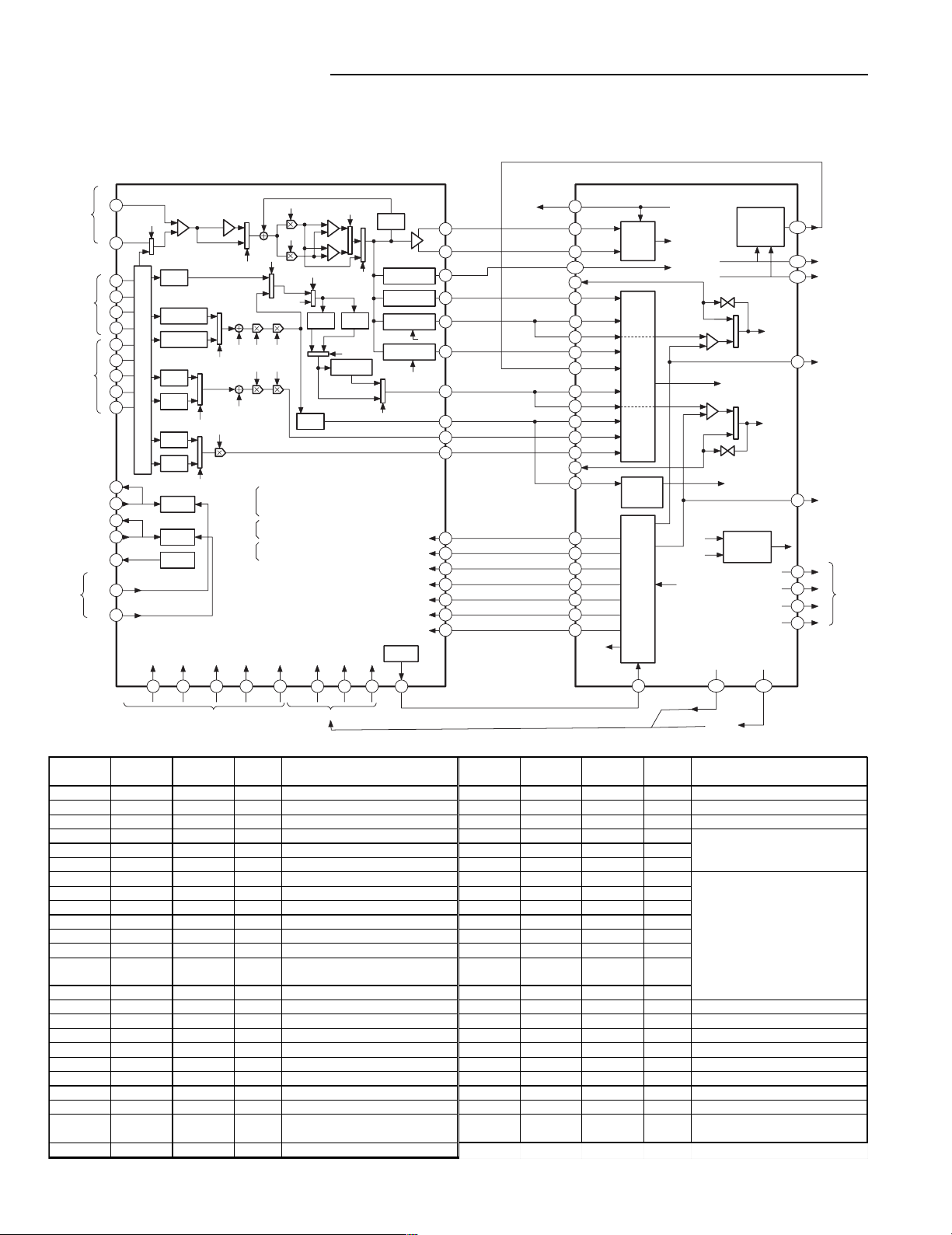

DVD P.W.BOARD OPERATION

1. General operation diagram ( This is a basic general operation diagram)

The circuit mounted on the Loader part (Frontend Board) is configured as shown, which is divided into following bl;ocks according to

main IC's.

DVD/CD PD

LASER

DIODE

ACTUATOR

SLED

MOTOR

LIMIT

SWITCH

OPEN/CLOSE

SWITCH

LOADING

MOTOR

PICK-UP;SF-HD6

High-

frequency

circuit

FOCUS

TRACKING

M

M

SPINDLE

MOTOR

HALL

LD

VR-CD

VR-DVD

MD

LD-CD

VD

HFM

D

GND-LD

VREF

LSI_RESET

HDAT[0;7]

DSPJVAD

16.934MHZ

3.3V

(FOR DSP)

DACK

DREQ

DCLK,DBGN,DERR

SDT[O;7]

EMPH,C2F,LRCK,BCK,CD_DATA,SPDIF

16MHZ

HADR[0;12]

HRDB,HERB,HCSB

HWAITB(RDY),HBUSYB

HIRQB(INT_DEC),WRQ

LE28C1001

FLASH MEMORY

RXD,SCLK

HD_INT,TXD,RDY_HIF

RESET HRST

16MHZ

IC201

T224162B

DRAM

IC900

BA033

REGULATOR

IC504

TC7SHU04FU

INVERTER

IC550

IC502

M51953

RESET

9V

(actuator)

(motor)

5V

(analog)

5Vd

(digital)

PH 6P

FFC 26P

FFC 16P

TO BACK-END

BLOCK

CN900CN200CN500

RF AMP

A

B

C

D

E

F

F-

F+

T-

T+

MD

LD

MD

LD

5Vd

CAO

U+,UV+,VW+,W- SPD

U,V,W

IC100

LA9702

CAN

LDON1,LDON2

CD x2

RFSCT,EQSCT

CD x4

PP/TE,DPD/TE

4-CH BTL DRIVER

IC601

BA5937

DMUTE2

3-PHASE MOTOR DRIVER

IC602

BA6849

9V

FDD

TDD

SLD

OPEN/

CLOSE

9V

FG

FR

DMUTE

TOST,FOST,BST,VCA

TBAL,FBAL,SGC

DEF

FE

RFOP,RFON,PH,TE,ADBH

ADBH

DEF_INH

DEFECTO

XHTR

IC101

BU4066

ANALOG SWITCH

JV

BH

DEFECTI

M37903S4CHP

FE

IC500

IC200

LC78661W

MICRO COMPUTER

- 6 -

DVD P.W.BOARD OPERATION

1

2

3

4

5

6

7

8

9

10

11

14

13

16

15

79

72

70

76 61 68 63 59 53 27

18

19

20

21

22

23

24

35

34

33

32

31

30

29

1

2

10

14

7

6

13

9

8

5

28

29

32

45

41

40

46

44

42 12

18

16

206

44

26

154

134

136

28

39

27

38

37

36

20120525

11

30

5157

XHTRC

DEFECT0

RFP1

TH

TESBIAS

HFLBIAS

HFLBIAS

TESBIAS

TES

HFL

PCK

PCK

JV

JITTER

DETECTION

CIRCUIT

SLCBIAS

LDO1

LDS1

LDO2

LDS2

SLC

SLCBIAS

EFMINP

EFMINN

DEFECTI

HFLIO

RF-PH

RF-BH

AD5/BH

AD2

AD1

TE

AD4/TE

AD3

FE

AD0

TESIO

EFMOUT

EFM,EFM+

EFM+

EFM

DEFECT

FE,TE,PH,BH,RPEC,

JV,BCA,WO

DEGITAL.

CLK

COUNTER

FDO

TDO

SPDO

SLDO

CPOF

VREF

SLCBIAS

SGC

OFSET

BCA

BOOT3T

RFVCA

TBAL

FBAL

D/A

8bit

11ch

+3ch

D/A

8bit

10ch

TES

WO-CNT

HFL

TRACK

COUNTER

DEGITAL.

OFSET,BCA,BOOT3T,

RFVCA,TBAL,FBAL,

SGC,HFLBIAS,TESBIAS,

FDO,TDO,SPDO,SLDO,

SLCBTAS.

RFPI

RFOP

RFON

DEF

PH

BH

BCA

TE

WO

FE

RREC

TOST

FOST

BST

VGA

TEBL

FEBL

SGC

SERVO

VREFS

VREFS

TH

CPOF

XHTRC

DPD/TE

XQBHPP/TEEQSCT

RFSCT

VREFP

LDON1

LDON2

PICK

APC1

RR 1

B

FE 1

FE 2

RR 2

APC2

VREFP1

MTX

A

D

C

C

A

DVD

PU

DVD

PU

B

F

E

DPD

2C+A+B

3-BEAM

PUSH-PULL

REN

REP

LPF

BCA TH

DEFECT

PEAK HOLD

BOTOM HOLD

TE HOLD

LPF2LPF1

BPF

DPD: PHASE A,B,C,D

3-BEAM: F~E

PUSH-PULL: (B+C)-(A+D)

FE1: (B+D)-(A+C)

FE2: A-B

RR1: A+B+C+D

RR2: A+C+B

TE

FE

RREC

RFSCT

CD-3T

BOOST

DPD / TE

VGA

BST

DPD / TE

EQ2

EQ1

EQSCT

CPOF OR TH

DPD / TE

VREF

XHTRC

XHTRC

PP / TE

TOST

FOST

TE

FE

SGC

SGC

SGC

RFSCT

RFSCT

TH

BCATH

CD

PU

MI-COM

PORT

MI-COM PORT DSP CONTROL

to

DRIVE

IC

LA9702W(AMP) LC78661W(DSP)

IC100

IC200

2. Circuit configuration inside IC100 (LA9702W) and IC200 (LC78661W).

(This is a basic circuit configuration diagram)

Name TP label

FE TP101 IC100 25 Focus Error Signal(Analog) TD TP601 IC200 3 8 Tracking Driver out(analog)

TE TP102 IC100 30 Tracking Error Signal(Analog) FD TP602 IC2 00 39 Focus Driver out(analog)

RFN TP104 IC100 4 0 RF Signal(Analog) SPD-FG TP604 IC 602 24 Spindle FG signal

RFP TP105 IC100 41 RF Signal(Analog) W TP621 ------ ------

BH TP106 IC100 42 Bottom Hold Signal(Analog) V TP620 ------ ------

PH TP107 IC100 44 Peak Hold Signal(Analog) U TP611 ------ -----DEF TP230 IC100 46 High : When passing defection H+ TP619 ------ -----LD1 TP122 Q1004 E DVD Laser Power Supply(Analog) U+ TP618 ------ -----LD2 TP124 Q1005 E CD Laser Power Supply(analog) U- TP617 ------ ------

TESI0 TP201 IC200 2 TES(Track crossing signal) V+ TP616 ------ ------

HFLBIAS TP204 IC200 2 8 MIRROR Slice Bias(Analog) V- TP615 ------ ------

HFLIO TP206 IC200 44 MIRROR signal W+ TP614 ------ ------

FSEQ TP211 IC200 8 4

EFMOUT TP226 IC200 134 RF Digitized signal H- TP612 ------ ------

DEFECT0 TP229 IC200 201 High : When passing defection SLD TP607 I C200 36 Sled Driver out(analog)

TOST TP246 IC200 29 Tracking Offset Control(analog) SPD TP608 IC200 3 7 Spindle Driver out(analog)

FOST TP247 IC200 30 Focus Offset Control(analog) OPEN ------ I C60 1 1 6 TRAY control signal

BOOST3T TP248 IC200 3 1 RF EQ Control(analog) CLOSE ------ IC601 15 TRAY control signal

RFVCA TP249 IC200 32 RF Voltage Control(analog) OPEN-SW TP627 CN600 5 TRAY Limit SW

TBAL TP250 IC200 33 Tracking Balance Control(analog) CLOSE-SW TP626 CN600 3 TRAY Limit SW

FBAL TP251 IC200 34 Focus Balance Control(analog) HRST TP700 CN500 2 RESET from Backend

SGC TP252 IC200 35 Signal Gain Control(anlog) RESET ------ IC502 6 RESET to Micom

HFBUSYB TP254 IC200 50

IC, CN

Location Pin no. Description Name TP label

JVAO TP257 IC200 154 Jitters value(analog)

High : Sync synchronised

LO : Async W- TP613 ------ ------

Function Busy Low during jump,

adjustment so on.

IC, CN

Location Pin no. Description

VREF ------ IC100 27, 79 Reference Voltage(2.5V)

Spindle Coil Voltage

Spindle Hall Voltage

- 7 -

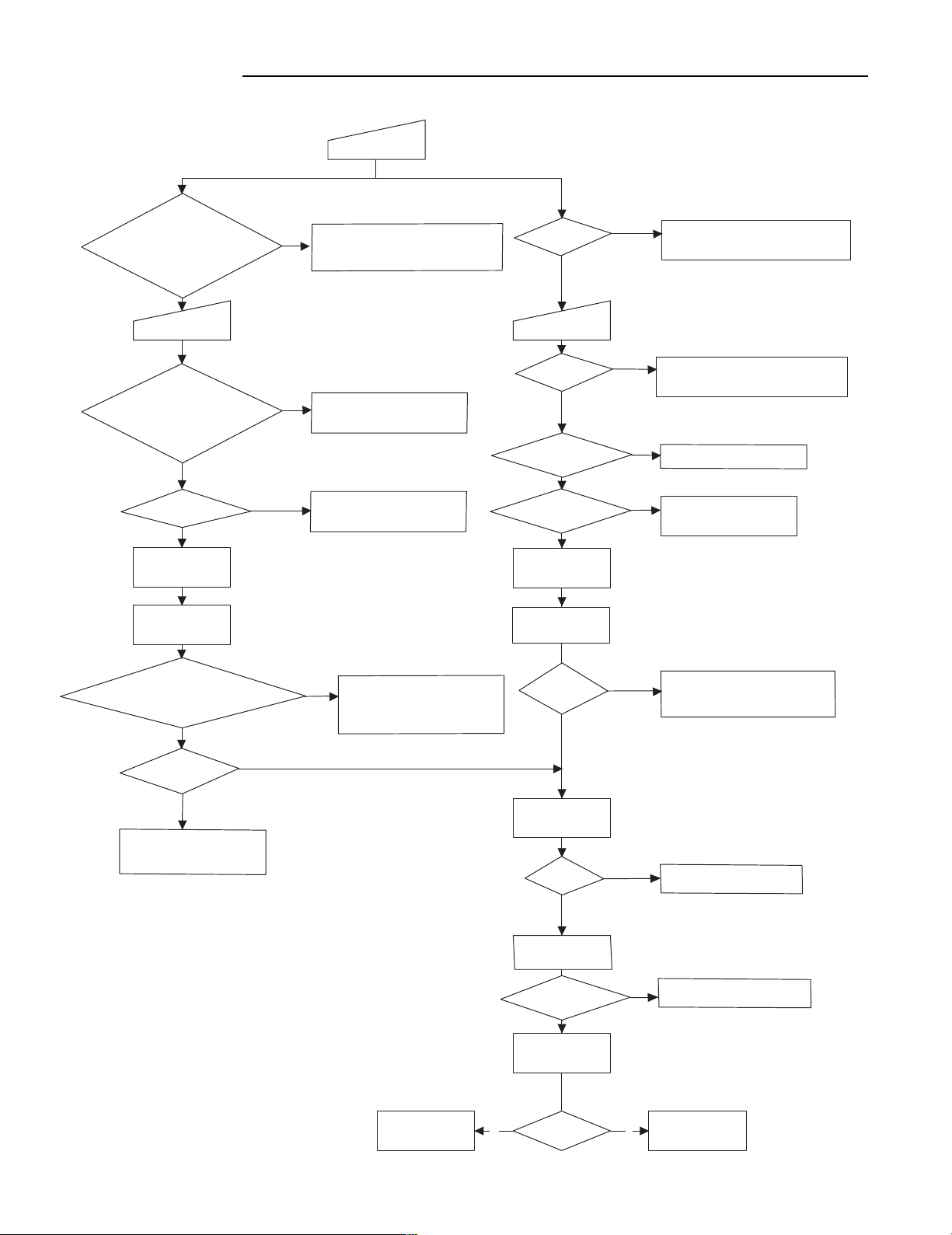

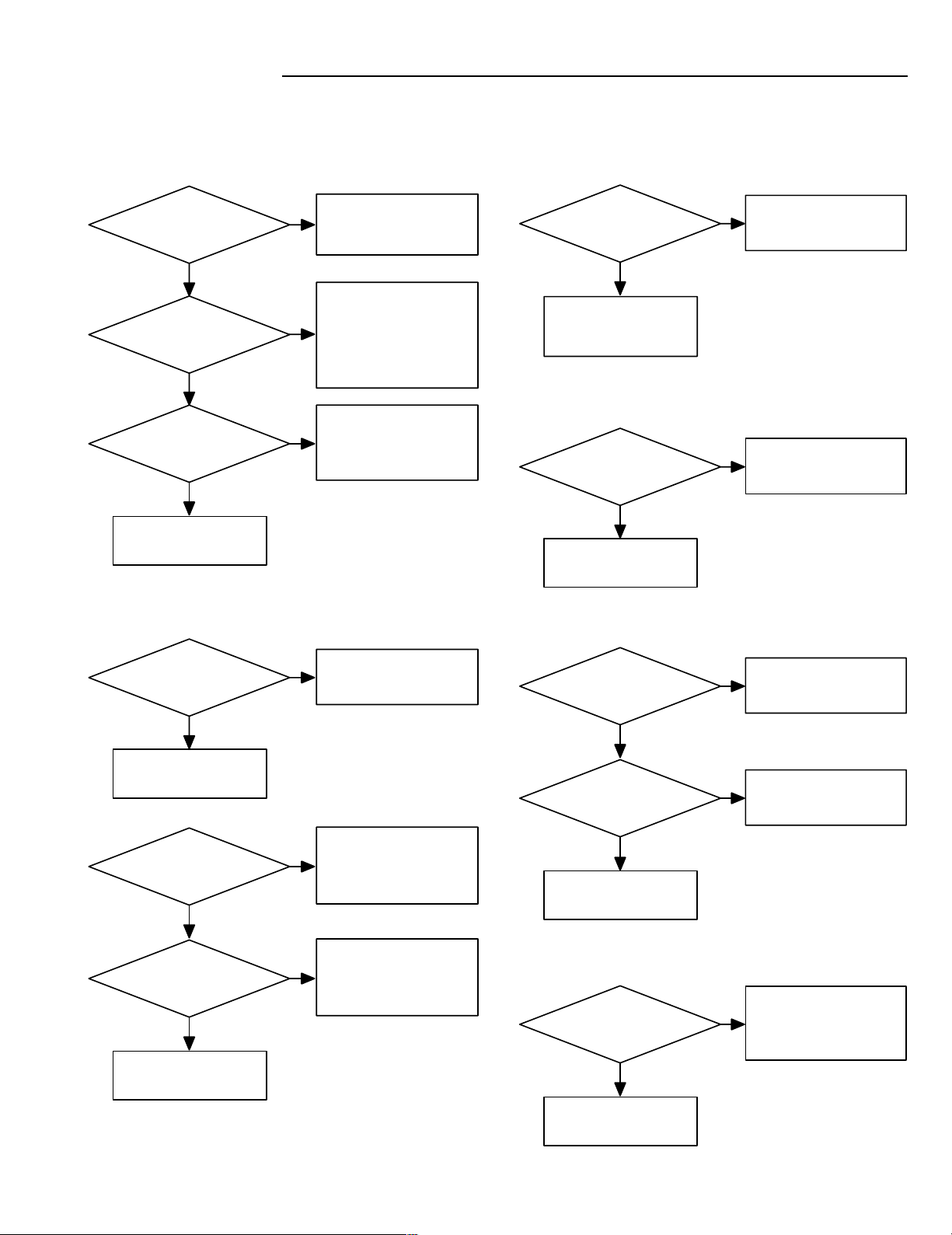

TROUBLE SHOOTING

(This is a basic trouble shooting.)

General flow

XE,UK Version

AC-CORD PLUG IN

Except XE,UK Version

POWER SUPPLY.FSTANDBY mode

IC601 ACTIVE/P-CON.FLOW

+5V/+12/-30/FIL.FOFF

STANDBY LED LIGHT

OK

POWER KEY

PRESS

P-CON.FHIGH

+5V/+12/-30/FIL.FON

OPEN/CLOSE.ETRAY LED LIGHT

IC601 STANDBY DATA WAITE

STANDBY LED OFF

OK

RESET LOADER AND

CHIPS

OK

READ/WRITE DATA

IN EEPROM

START

COMMUNICATION

WITH VFD

FROM MPU STANBY DATA SEND

IC601 STANDBY DATA RCVD

IC601 POWER ON DATA SEND

OK

NG

IC601 VDD/RESET/OSC confirm

NG

IC601:FPC16316-80 confirm

STANDBY LED peripheral circuit confirm

P-COn/+5V/+12/-30/FIL confirm

POWER KEY confirm

NG

LED peripheral circuit confirm

P-CON/+5V/+12/-30/FIL confirm

RESET (IC130) confirm

VDD/CLOCK confirm

IC116 peripheral confirm

NG

Communication LINE confirm

REMCON NG. IC116/IC113,112

l

periphera confirm

REMCON OK. then IC601

peripheral confirm

STANDBY LED

LIGHT

OK

POWER KEY

PRESS

STANDBY LED

OFF

OK

OPEN/CLOSE.ETRAY

LED LIGHT

OK

RESET LOADER AND

CHIPS

OK

READ/WRITE DATA

IN EEPROM

START

COMMUNICATION

WITH VFD

VFD

INDICATE

"READING"

OK

NG

NG

NG

IC601 VDD/RESET/OSC confirm

IC601:UPD16311 confirm

STANDBY LED peripheral circuit confirm

POWER KEY confirm

STANDBY LED peripheral circuit confirm

NG

LED peripheral circuit confirm

RESET (IC130) confirm

NG

VDD/CLOCK confirm

IC116 peripheral confirm

IC BUS LINE confirm

IC601 VFD

peripheral circuit confirm

-30V.EFILAMENT voltage confirm

Communication LINE confirm

VFD

INDICATE

"READING"

OK

IC BUS LINE confirm

IC601 VFD peripheral confirm

-30V.EFILAMENT voltage confirm

Communication LINE confirm

NG

VFD

INDICATE

"NO DISC"

- 41 -

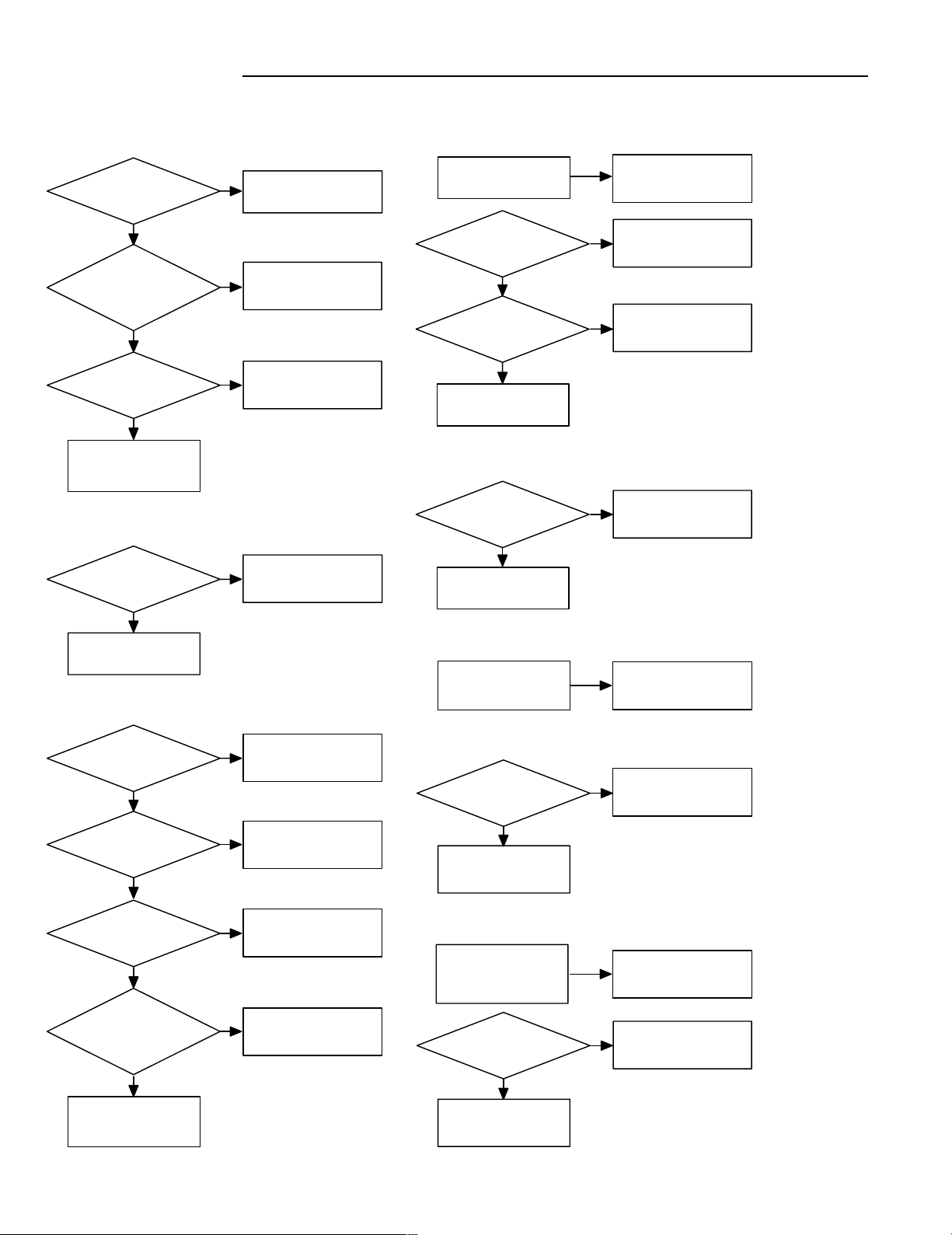

INITIALISE

MPEG DECODER

(IC127)

OK

OK

NG

IC118-IC127 BUS-LINE confirm

IC127/116 peripheral confirm

LOADER confirm

NG

Communication LINE confirm (FFC)

PLAYBACK mode

DISPLAY

LOGO

START CONTROL OF

LOADER

PICK INITIALISE

SPINDLE ROTATE

INITIALISE

ADAC(IC130)

DISC Y/NN Y

TROUBLE SHOOTING

(This is a basic trouble shooting.)

AUDIO PART

1. When time display OK and sound NG

or When S/PDIF OK and analogue NG.

Check DAC output

(IC131 pin11/14).

NG

Check (BCLK/

ASDATA/LRCLCIC131

pin 16/17/18).

NG

Check IC127

pin 105/106/107.

NG

Check IC127 peripheral.

(IC127 NG)

OK

OK

OK

Tracking signal of

after DAC output.

Check MUTE signal.

Check IC131 pin1(27MHz)

and pin2(384FS).

Check IC131 power source

and peripheral circuit.

Check IC131 RESET/

control signal(pin6/7/8/9).

Check BCLK/ASDATA/

LRCLK signal line.

Check IC127 and

its peripheral.(IC127 NG)

3. When S/PDIF NG and analogue OK.

Check optical module

and signal line.

NG

Check signal line

peripheralpattern

and parts.

OK

Check IC127 peripheral.

4. When S/PDIF NG and analogue NG.

Check time display.

OK

NG

Check check 2

Check check 1

(IC127 NG)

2. When time display NG and sound NG.

Exchange DVD:Loader.

OK

NG

Check IC127 peripheral.

(IC128 NG)

Check CD:CN810 pin2/3/4.

OK

NG

Exchange loader.

OK

NG

Exchange MPEG

p.w.board.

Loader NG.

Check IC127 peripheral.

(IC127 NG)

Loader NG.

5. When pop noise (when usual operate.)

Check same output as

SPDIF and RCA.

NO

Check pop noise only

RCA output.

NO

IC127 (MPEG) NG.

YES

YES

Loader NG

Muting circuit trouble.

Check MUTE signal.

6. When pop noise (Power ON/OFF).

Specity place of noise

Check MUTE circuit.

(Normality ?)

NO

YES

generation.

Check timing with MUTE

signal and its peripheral.

- 42 -

Check MUTE circuit.

TROUBLE SHOOTING

(This is a basic trouble shooting.)

VIDEO PART

1. When sound OK and picture NG.

4. When confusion of the picture.

Check IC102:video

encorder output.

NG

Check IC102:

video encorder peripheral.

(DVD/reset/pd0-8/

sync/RSET)

NG

Something is wrong

with pd0-8.

NO

Exchange disc

(error rate high).

Inquire the whole.

Check wirng from encorder

OK

OK

TES

output to set output.

IC102 NG.

IC127 NG.

Check wiring.

2. When sound and picture NG and display OK.

Check dac output and

video encorder output.

NG

IC127 NG.

Check the whole.

OK

Inquire wiring.

3. When confusion of the picture.

Color change.

Horizontal/

vertical line enter.

Check video sync.

NG

IC102 video

encorder output.

NG

Check IC102 peripheral.

(IC102 NG)

27MHz oscillating circuit

Check IC127 pin15/16.

OK

Check circuit from IC102

OK

output to set output.

5. When color NG.

27MHz

oscillating circuit trouble.

Check frequency.

NG

Exchange oscillator.

Exchange C8121/C8122.

OK

6. when not change to PAL or NTSC.

Check PAL/NTSC control

line (IC116 pin16 cn671

pin9:high NTSC/low PAL).

Check signal pattern

trouble.

Check frequency.

IC102 NG.

and S6702.

Recover at exchanged

loader.

NO

Recover at exchanged

MPEG p.c.board.

NO

Recover at exchanged

disc.

NG

Check fluctuation

of power source 5V.

Check contact of

connector.

NG

Check power source

p.w.board NG.

Exchange p.w.board.

YES

Check MPEG p.w.board.

YES

OK

OK

Exchange disc.

Check the whole.

Check loader.

7. When s-terminal output NG and color NG.

Check IC102:video

encorder output.

NO

Check solder of

output terminal.

(IC102 NG)

Check circuit from IC102

output to set output.

Check S6701 peripheral.

YES

8. When YUV/RGB NG and color NG.

Check IC102:video

encorder output.

Check S6701 peripheral

circuit.

Check RGB/YUV setting.

NO

Check setting signal

pattern.

(IC102 NG)

Check circuit from IC102

output to set output.

Check S6701 peripheral.

IC102 NG.

YES

- 43 -

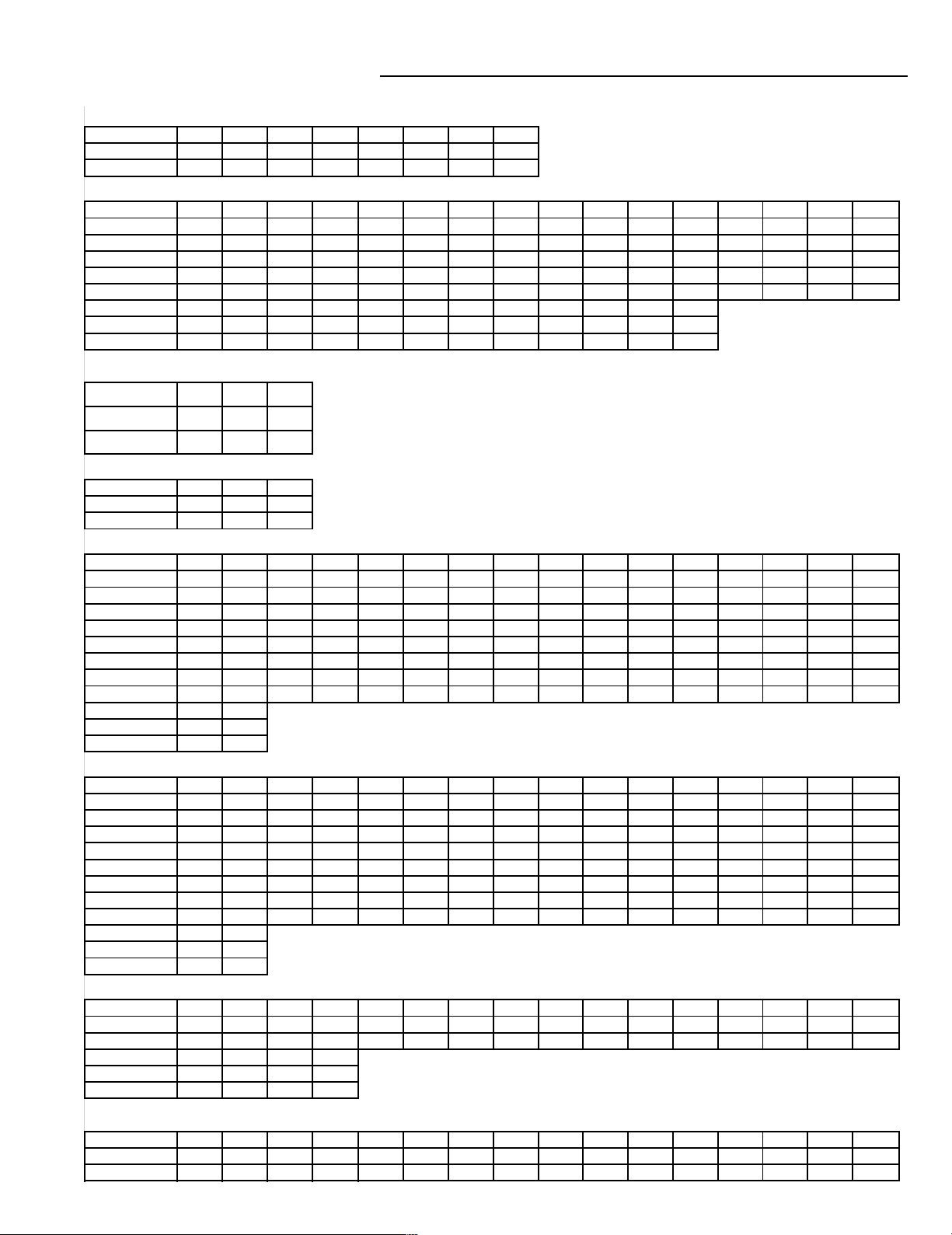

VOLTAGE OF IC & TRANSISTOR

V

V

V

V

1. MPEG part

IC101

Pin No. 12345678

Power OFF

Power ON

0V 0V 0V 0V 0.1V 0.1V 0V 0.1V

0V 0V 0V 0V 3.3V 3.3V 0V 3.3V

IC102

Pin No. 12345678910111213141516

Power OFF

Power ON

Pin No. 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

Power OFF

Power ON

Pin No. 33 34 35 36 37 38 39 40 41 42 43 44

Power OFF 0V 0V 0V 0V 0.1V 0.2V 0.1V 0.1V 0.1V 0.1V 0V 0V

Power ON 1.2V 1.2V 0V 0V 3.2V 0.9V 0.9V 0.6V 1.3V 2.5V 0V 1.6V

0.1V 0.1V 0.1V 0.1V 0.1V 0.1V 0.1V 0.1V 0.1V 0V 0.1V 0.1V 0.1V 0.1V 0.1V 0.1V

3.3V 0.8V 0.6V 1.1V 3.3V 3.3V 3.3V 3.3V 3.3V 0V 3.3V 3.3V 3.3V 3.3V 3.3V 3.3V

0.1V 0.1V 0V 0.1V 0V 0.1V 0.1V 0.1V 0V 0V 0V 0.1V 0V 0.1V 0V 0V

2.5V 3.3V 0V 3.3V 0V 3.3V 3.3V 3.3V 1.2V 0.8V 0.8V 3.3V 0V 3.3V 0.7V 0.4V

(V)

(V)

IC103

Pin No. 1 2 3

Power OFF

Power ON

0.6V 0V 0V

5.1V 0V 2.5V

IC104

Pin No. 1 2 3

Power OFF 0.6V 0V 0.1V

Power ON 5.1V 0V 3.3V

(V)

(V)

IC110

Pin No. 12345678910111213141516

Power OFF 0.1V 0V 0V 0V 0V 0V 0.1V 0V 0V 0V 0V 0V 0.1V 0.1V 0.1V 0.1V

Power ON 3.3V --- --- 0V --- --- 3.3V --- --- 0V --- --- 3.3V 0V 3.3V 3V

Pin No. 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

Power OFF 0.1V 0.1V 0.1V 0.1V --- --- 0.5V --- 0.1V 0V --- --- 0V 0V 0.1V 0.1V

Power ON 3.1V 3.1V 0.2V 0V 0 V 0V 0.2V 0.2V 3.3V 0V 0.2V 0.2V 0.2V 0.2V 0V 0V

Pin No. 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48

Power OFF 0V 0.1V 0.1V 0.1V 0V 0.1V 0V 0V 0V 0V 0V 0.1V 0V 0 V 0V 0V

Power ON 0V 3.3V 1.6V 0 V 0V 3.3V --- --- 0V --- --- 3.3V --- --- 0V ---

Pin No. 4 9 5 0

Power OFF 0 V 0V

Power ON --- 0V

IC111

Pin No. 12345678910111213141516

Power OFF 0.1V 0V 0V 0V 0V 0V 0.1V 0V 0V 0V 0V 0V 0.1V 0.1V 0.1V 0.1V

Power ON 3.3V --- --- 0V --- --- 3.3V --- --- 0V --- --- 3.3V 0V 3.3V 3V

Pin No. 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

Power OFF 0.1V 0V 0.1V 0.1V --- --- --- --- 0.1V 0V 0.5V --- 0.1V 0.1V 0.1V 0.1V

Power ON 3.1V 3V 0.2V 0V 0V 0V 0.2V 0.2V 3.3V 0V 0.2V 0.2V 0.2V 0.2V 0V 0V

Pin No. 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48

Power OFF 0V 0.1V 0.1V 0.1V 0V 0.1V 0V 0V 0V 0V 0V 0.1V 0V 0 V 0V 0V

Power ON 0V 3.3V 1.6V 0V 0V 3.3V --- --- 0V --- --- 3.3V --- --- 0V ---

Pin No. 4 9 5 0

Power OFF 0 V 0V

Power ON --- 0V

IC112

Pin No. 12345678910111213141516

Power OFF 0 V 0V 0V 0 V 0V 0.5V 0V 2V 0V 0V 0V 0V 0.6V 0V 0V 0.019

Power ON 0V 0.1V 3.3V 5V 3.3V 0.1V 3.3V 4.9V 0V 0V 0V 3.3V 5V 0V 5V 3.317

Pin No. 17 18 19 20

Power OFF 0.581V0.020V 0V 0.092V

Power ON 5.05V 0V 0V 3.317V

(V)

(V)

(V)

IC113

Pin No. 12345678910111213141516

Power OFF 0 V 0V 0.660V 0V 0.581V 0.015V 1.204V 0.016V1.627V 0V 0.092V 1.208V 0.011V 0.581V 0.016V 0.531

Power ON 0V 0V 0.001V 0.001V 5.05V 0.001V 4.98V 0.018V 4.87V 0V 3.217V 0.053V3.281V0.039V 3.309V 0.027

- 44 -

(V)

VOLTAGE OF IC & TRANSISTOR

IC113

Pin No. 12345678910111213141516

Power OFF 0 V 0V 0V 0V 4.9V 0 V 4.9V 0V 4.6V 0 V 3.2V 0V 3.2V 0V 3.3V 0V

Power ON 0V 0V 0V 0V 4.9V 0V 4.9V 0V 4.6V 0V 3.2V 0V 3.3V 0V 3.3V 0V

Pin No. 17 18 19 20

Power OFF 0 V 0V 0V 4.9V

Power ON 0V 0V 0 V 4.9V

IC116

Pin No. 12345678910111213141516

Power OFF 0 V 2.5V 3.3V 0V 0V 0V 0V 0V 0V 0V 0V 3.3V 3.3V 3.3V 3.3V 3.3V

Power ON 0V 2.5V 3.3V 0V 0V 0V 0V 0V 0V 0V 0V 3.3V 3.3V 3.3V 0V 3.3V

Pin No. 17 18 19 20 21 22 23 24 25 26 27 28 2 9 30 31 32

Power OFF 3.3V 3.3V 0V 3.3V 3.3V 0V 3.3V 3.3V 3.3V 0V 0V 3.3V 0V 0V 0V 0V

Power ON 3.3V 3.3V 0V 3.3V 3.3V 0V 3.3V 3.3V 3.3V 0V 0V 3.3V 0V 0V 0V 0V

Pin No. 33 34 35 36 37 38 39 40 41 42 43 44 4 5 46 47 48

Power OFF 0 V 0V 3.3V 3.3V 0 V 3.3V 2.5V 0V 3.3V 0V 3.1V 0V 0.6V 3.1V 3.3V 2.7V

Power ON 0V 0V 3.3V 3.3V 3.3V 3.3V 2.5V 0 V 3.3V 0V 3.1V 0V --- 3.2V 3.3V 2.7V

Pin No. 49 50 51 52 53 54 55 56 57 58 59 60 6 1 62 63 64

Power OFF 0 V 0V 0V 2.5V 2.5V 0V 1.6V 3.3V 0V 3.3V 3.3V 3.3V 0V 3.3V 3.3V 3.3V

Power ON 0V 0V 0V 2.5V 2.5V 0V 1.6V 3.2V 3.3V 3.3V 3.3V 0V 0V 3.3V 3.3V 3.3V

Pin No. 65 66 67 68 69 70 71 72 73 74 75 76 7 7 78 79 80

Power OFF 0 V 0V 0.5V 0V 0V 3.3V 3.3V 0V 0 V 3.3V 3.3V 3.3V 3.3V 3.3V 3.3V 3.3V

Power ON 0V 0V 3.3V 0V 0V 0V 3.3V 0V 0V 3.3V 3.1V 3.3V 3.3V 3.3V 3.2V 3.3V

Pin No. 81 82 83 84 85 86 87 88 89 90 91 92 9 3 94 95 96

Power OFF 0 V 2.5V 0V 3.3V 0 V 0V 0V 3.3V 3.3V 3.3V 3.3V 3.3V 0V 3.3V 3.3V 0V

Power ON 0V 2.5V 3.3V 3.3V 0V 3.3V 0V 3.3V 3.3V 3.3V 3.3V 0V 3.3V 3.2V 3.3V 0V

Pin No. 97 98 99 10 0 101 102 103 104 105 106 107 108 109 110 111 112

Power OFF 3.3V 0V 3.3V 0V 3.3V 0.4V 0V 0.6V 0.5V 0.5V 0.6V 0.5V 0V 3.3V 0.5V 0V

Power ON 3.3V 0V 3.3V 0V 2.7V --- --- --- --- --- --- --- 0V 3.3V --- 0V

Pin No. 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128

Power OFF 3.3V 3.3V 3.3V 3.3V 3.3V 0V 0V 3.3V 0V 2.5V 1.6V 0V --- --- --- ---

Power ON 3.3V 3.3V 3.3V 3.3V 3.3V 0V 0V 3.3V 0V 2.5V 1.6V 0V --- --- --- ---

Pin No. 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144

Power OFF --- 0V 3.3V --- --- 0.6V 3.3V 3.3V 3.3V 3.3V 3.3V 0V 3.3V 0.1V 3.3V 0V

Power ON --- 0V 3.3V --- --- 1.1V 3.3V 3.3V 3.1V 3.1V 3.1V 0V 3.3V 0V 3.2V 0V

Pin No. 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160

Power OFF 0 V 0V 0V 0V 0V 0V 3.3V 0V 0V 0V 0V 0V 0V 0V 0V 3.3V

Power ON 0V 0 V 0V 0V 0V 0V 3.3V 0V 0V 0 V 0V 0V 0V 0V 0V 3.3V

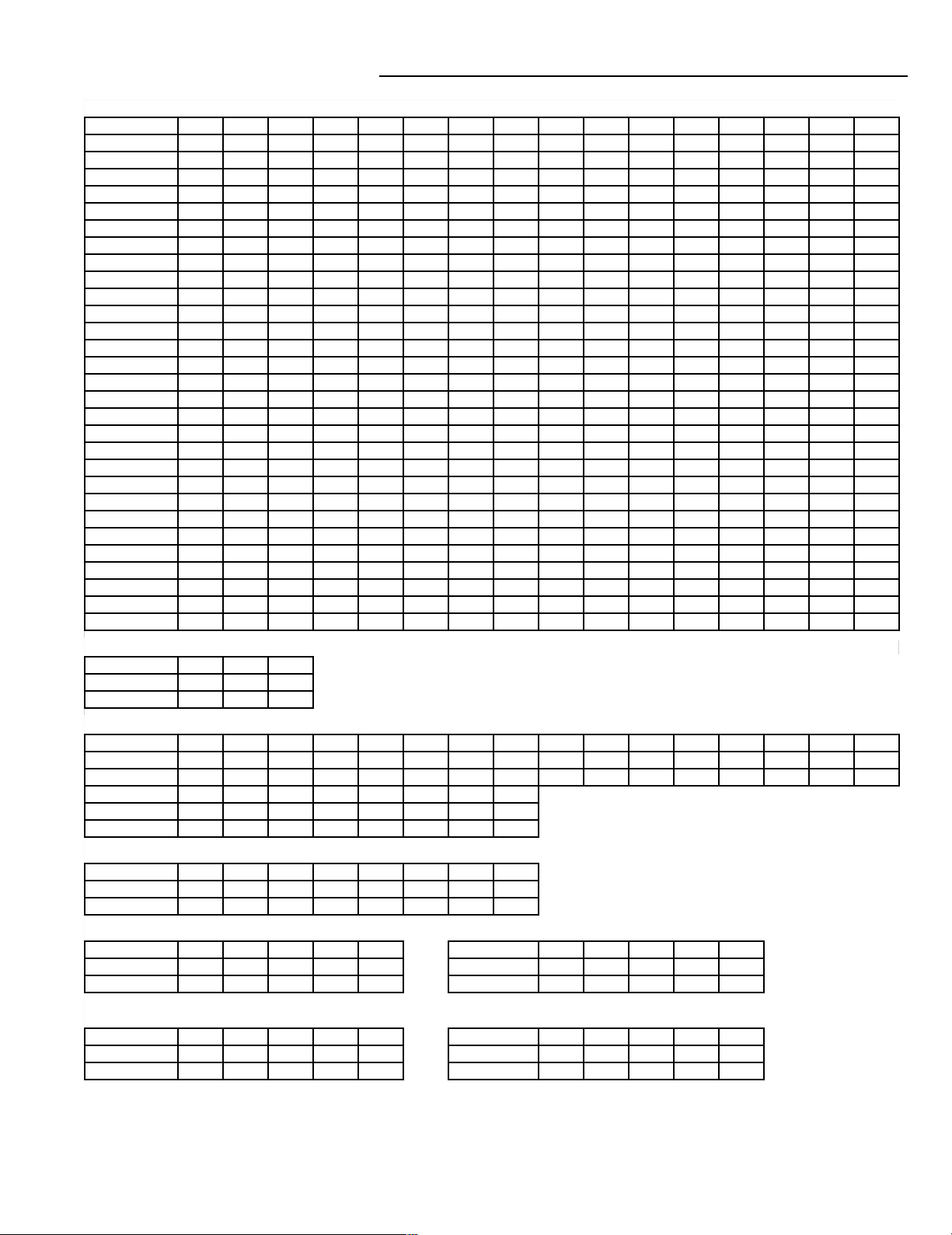

IC117

Pin No. 12345678910111213141516

Power OFF 3.3V --- --- 0V --- --- 3.3V --- 0.3V 0V 0.3V 0.3V 3.3V 0V 2.1V 2.6V

Power ON 3.3V --- --- 0V --- --- 3.3V --- --- 0V --- --- 3.3V 0V 3.3V 3.2V

Pin No. 17 18 19 20 21 22 23 24 25 26 27 28 2 9 30 31 32

Power OFF 2.5V 11.9V 0V 0V 2.3V 2.4V 0.8V 1.7V 3.3V 0V 3.2V 1.7V 1.5V 3.1V 1.8V 0V

Power ON 3.3V 3.2V 0.2V 0.1V 3.1V 3.2V 3.1V 0V 3.3V 0V 0V 0.2V 3.3V 0V 0V 0V

Pin No. 33 34 35 36 37 38 39 40 41 42 43 44 4 5 46 47 48

Power OFF 0 V 3.3V 1.6V 0V 0V 3.3V --- --- 0 V --- --- 3.3V --- --- 0V ---

Power ON 0V 3.3V 1.6V 0V 0V 3.3V --- --- 0V --- --- 3.3V --- --- 0V ---

Pin No. 49 50

Power OFF --- 0V

Power ON --- 0V

IC118

Pin No. 12345678910111213141516

Power OFF 0 V --- 0V 0V 0.1V 3.2V 0V --- 3.3V 0V 0V 0V 0V 0V 0V 0V

Power ON 0.1V --- 0.1V 0.1V 0.1V 3.1V 0.1V --- 3.3V 0.1V 0V 0.1V 0.1V 3.3V 0.1V 0V

Pin No. 17 18 19 20 21 22 23 24 25 26 27 28 2 9 30 31 32

Power OFF

Power ON

Pin No. 33 34 35 36 37 38 39 40 41 42 43 44 4 5 46 47 48

Power OFF --- --- --- --- 3.3V 0V --- --- --- --- --- --- --- --- 0V 0V

Power ON --- --- --- --- 3.3V 0V --- --- --- --- --- --- --- --- 0V 0.1V

0V

---

3.1V 3.2V 0.1V 0.1V 0V 0.1V 0V 0.1V 0V 0 V

0V 0 V 0V 3.3V 0V 0.1V 0V 3.3V 3.3V 3.3V 0V 3.2V

--- --- --- ---

--- --- --- ---

(V)

(V)

(V)

(V)

- 45 -

VOLTAGE OF IC & TRANSISTOR

IC127

Pin No. 12345678910111213141516

Power OFF

Power ON

Pin No. 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32

Power OFF

Power ON

Pin No. 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48

Power OFF

Power ON

Pin No. 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64

Power OFF

Power ON

Pin No. 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80

Power OFF

Power ON

Pin No. 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96

Power OFF

Power ON

Pin No. 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112

Power OFF

Power ON

Pin No. 113 114 115 116 117 1 1 8 119 120 121 122 123 124 125 126 127 128

Power OFF

Power ON

Pin No. 129 130 131 132 133 1 3 4 135 136 137 138 139 140 141 142 143 144

Power OFF

Power ON

Pin No. 145 146 147 148 149 1 5 0 151 152 153 154 155 156 157 158 159 160

Power OFF

Power ON

IC130

Pin No. 1 2 3

Power OFF

Power ON

0V --- --- --- --- 3.3V --- --- --- --- 0V 3.3V 3.3V 3.3V 3.3V 3.3V

0V --- --- --- --- 3.3V --- --- --- --- 0V 3.3V 0V 3.3V 0V 3.3V

3.3V 3.3V 3.3V 0V 3.3V 0V 0V 3.3V 3.3V 3.3V 3.3V 0V 3.3V 3.3V 0V 0V

0V 0V 3.3V 0V 3.3V 0V 0V 3.3V 3.3V 3.3V 3.3V 0V 3.3V 0V 0V 0V

0V --- 3.1V 3.2V 0.1V 3.2V 3.2V 3.3V 0.1V 3.3V 3.3V 3.3V 3.3V 0V --- --0V 0V 3.3V 0V 3.3V 0V 0V 3.3V 0V 3.3V 3.3V 3.1V 3V 0V --- ---

--- --- --- --- --- --- 0V 1.7V 0V 3.3V 0V 0V 3.3V --- 0V 3.3V

--- --- --- --- --- --- 0V 1.6V 3.3V 3.3V 0V 0V 3.3V --- 3.2V 3.3V

3.3V 0V 3.3V 3.3V 0.6V 0.7V 3.3V 0V 0V 0V 0V 0V 0V 0V 3.3V 0V

3.3V 0V 3.3V 3.3V 3.3V 3.3V 3.3V 0V 0.5V 0.5V 0V 0.5V 0.5V 1.7V 3.3V 0V

0V 0V 0V 0V 0V 0V 3.3V 0V 0V 0V 0V 0V 3.3V 3.3V 3.3V 3.3V

0V 0.5V 0.4V 1.5V 0V 0.7V 0.8V 0V 0V 0V 0V 0V 3.3V 1.7V 17V 1.7V

0V 1.1V 1.6V 0V 0V 1.6V 0V 3.3V 0V 0V 0V 0V 0V 0V 0V 0V

0V 1.1V 1.6V 0V 0V 1.6V 1.7V 3.3V 1.6V 1.6V 0V 0V 0V 0V 1.6V 0V

0V 0V 3.3V 0V 3.3V 3.3V --- --- 0V --- 0V --- --- --- 3.3V --0V 0V 3.3V 0V 3.3V 3.3V --- --- 0V --- 0V --- --- --- 3.3V ---

--- 1.6V 0V 0V 0V 0V 3.3V 0V 0V 0V 0V 0V 0V 0V 3.3V 0V

--- 1.6V 0V 0V 0V 0.2 3.3V 0.2V 0.2V 0.2V 0V 0.2V 0.2V 0V 3.3V 0V

0V 0V 0V 3.3V 3.3V 3.3V 3.3V 3.3V 3.3V 0V 0V 3.3V 0V 0V 3.3V 0V

0V 0.2V 0V 3.1V 3V 3.1V 3.3V 3V 3.3V 0V 0V 3.3V 0V 0V 3.3V 0V

(V)

0V 4.9V 3.3V

0V 4.9V 3.3V

IC131

Pin No. 12345678910111213141516

Power OFF

Power ON

Pin No. 17 18 19 20 21 22 23 24

Power OFF

Power ON

IC132

Pin No. 12345678

Power OFF

Power ON

IC133

Pin No. 12345 12345

Power OFF

Power ON

1.6V 5V 5V 0V 1V 3.3V 3.3V 3.3V 0V 0V 2.5V 0V 5V 2.5V 2.5V 0V

1.7V 2.1V 5V 0V 1V 3.3V 3.3V 0V 3.3V 0V 2.5V 0V 5V 2.5V 2.5V 1.6V

0V 0V 0V 1V 5V 0V 0V 0V

0V 1.6V 0V 0.8V 5V 0V 0V 0V

(V)

6.6V 3.6V 3.5V 0V 3.5V 3.6V 6.6V 11.1V

6.6V 3.6V 3.5V 0V 3.5V 3.6V 6.6V 11.1V

(V)

5V 5V 0V 3.3V 3.3V 2.4V 2.4V 0V 1.6V 3.3V

2.2V 2.2V 0V 1.7V 3.3V 2.4V 2.4V 0V 1.6V 3.3V

IC135

Pin No.

Power OFF

Power ON

(V)

(V)

(V)

IC136

Pin No. 12345 12345

Power OFF

Power ON

--- 0V 0V 2.5V 3.3V 0V 0V 0V 0V 3.3V

--- --- 0V 2.5V 3.3V 1.6V 1.6V 0V 1.6V 3.3V

(V)

IC137

Pin No.

Power OFF

Power ON

- 46 -

(V)

EXPLODED VIEW (CABINET & CHASSIS)

13

12

4

14

7

5

22

21

6

18

Y27

Y27

64

61

63

57

59

2

1-1

11

10

1-2

1-3

1-4

1-6

1-7

1-11

62

60

19

8

9

3

4

4

17

78

56

53

55

79

75

52

51

58

54

76

71

16

74

77

72

73

Y06

Y17 Y01

Y07

Y07

Y23

Y08

Y23

Y28

Y04

Y20

Y21

Y01

Y21

Y02

Y10

Y10

Y13

Y09

Y15

Y14

Y25

Y16

Y15

Y14

1-8

1-8

Y19

Y22

Y05

Y05

Y05

Y05

Y11

Y22

Y18

Y18

Y18

1-9

1-5

1-5

Y25

Y26

Y24

Y03

61

Y03

1-10

Y13

Y01

20

(AU)

(UK)

(US,CA)

(XE)

(KR)

Y17

- 47 -

PARTS LIST

PRODUCT SAFETY NOTICE

EACH PRECAUTION IN THIS MANUAL SHOULD BE FOLLOWED DURING SERVICING. COMPONENTS IDENTIFIED WITH THE IEC

!!

!

SYMBOL

SPECIAL SIGNIFICANCE. WHEN REPLACING A COMPONENT IDENTIFIED BY

OR PARTS WITH THE SAME RATINGS OF RESISTANCE, WATTAGE OR VOLTAGE THAT ARE DESIGNATED IN THE PARTS LIST

IN THIS MANUAL. LEAKAGE-CURRENT OR RESISTANCE MEASUREMENTS MUST BE MADE TO DETERMINE THAT EXPOSED

PARTS ARE ACCEPTABLY INSULATED FROM THE SUPPLY CIRCUIT BEFORE RETURNING THE PRODUCT TO THE CUSTOMER.

CAUTION : Regular type resistors and capacitors are not listed. To know those values, refer to the schematic diagram.

IN THE PARTS LIST AND THE SCHEMATIC DIAGRAM DESIGNATED COMPONENTS IN WHICH SAFETY CAN BE OF

!!

!

, USE ONLY THE REPLACEMENT PARTS DESIGNATED,

Regular type resistors are less than 1/4 W Carbon type and Chip type resistors.

Regular type capacitors are less than 50 V and less than 1000 µF type of Ceramic type, Electrical type and Chip type.

PACKING & ACCESSORIES

REF.NO. PART NO. DESCRIPTION

614 315 8875 CARTON CASE(1000)

614 317 9689 CARTON CASE(XE)

614 317 9696 CARTON CASE(UK)

614 318 0760 CARTON CASE(SS)

614 318 6366 CARTON CASE(KR)

614 317 3328 CARTON CASE(US)

614 318 3853 CARTON CASE(CA)

614 318 6373 CARTON CASE(AU)

614 278 9117 NOTICE(1000,US)

614 303 7484 LABEL,CAUTION,CUSHION TOP(1000)

614 315 9001 INSTRUCTION,MANUAL(1000)

614 317 9795 INSTRUCTION MANUAL(XE)

614 317 9818 INSTRUCTION MANUAL(UK)

614 318 0845 INSTRUCTION MANUAL(SS)

614 318 6434 INSTRUCTION MANUAL(KR)

614 317 3359 INSTRUCTION MANUAL(US)

614 318 3907 INSTRUCTION MANUAL(CA)

614 318 6441 INSTRUCTION MANUAL(AU)

614 317 9801 INSTRUCTION MANUAL,(GREEK)(XE)

614 317 3182 INSTRUCTION SHEET,QUICK GUIDE

(1000)

614 317 3366 INSTRUCTION,SHEET,QUICK GUIDE

(US)

614 315 8974 CUSHION,TOP

614 315 8981 CUSHION,BOTTOM

645 046 8278 POLY SHEET-1300X0500*NC,SET

(1000,UK,SS,KR,US,CA,AU)

645 047 3418 POLY SHEET-1300X0500*NC,SET(XE)

645 044 9413 REMOCON,RB-H520MT(1000,CA)

645 044 9420 REMOCON,RB-H5201ST(XE,UK,AU)

645 044 9437 REMOCON,RB-H5201(SS,KR)

645 046 8391 REMOCON,REM-H5201(US)

645 043 9735 BATTERY COVER,SERVICE PART

645 041 1373 CABLE,VIDEO,VIDEO-CABLE(1.5M)

645 047 0356 WIRE,MAIN SP

645 047 0363 WIRE,SUB WOOFER

645 017 2175 PLUG,ADAPTOR AC(SS)

or 645 006 4630 PLUG,ADAPTOR AC(SS)

CABINET & CHASSIS

REF.NO. PART NO. DESCRIPTION

1 614 315 8516 ASSY,CABINET(1000,UK,SS,KR,AU)

1 614 317 9481 ASSY,CABINET(XE)

1 614 317 3236 ASSY,CABINET(US,CA)

1-1 614 319 0523 ASSY.BOX,SPEAKER

1-2 645 048 4957 LEFT SIDE COVER

1-3 645 048 4964 RIGHT SIDE COVER

1-4 645 048 4988 MID RANGE HOLDER

1-5 645 048 4971 RUBBER CATCHER

1-6 645 048 5015 MID RANGE

1-7 645 048 5084 JOIN WIRE

1-8 645 048 5138 SCREW,SIDE COVER

1-9 645 048 5121 SCREW,MID RANGE HOLDER

1-10 645 048 5091 SCREW,MID RANGE UNIT

REF.NO. PART NO. DESCRIPTION

1-11 645 048 5169 CUSHION,MID RANGE

2 614 315 8127 ASSY,GRILLE(1000,XE,UK,SS,KR,AU)

2 614 317 3250 ASSY,GRILLE(US)

2 614 318 3648 ASSY,GRILLE(CA)

3 614 315 6611 BUTTON(1000,XE,UK,SS,KR,AU)

3 614 317 3274 BUTTON(US,CA)

4 614 315 6727 MOUNTING,PANEL

5 614 315 8134 ASSY,PANEL,FRONT(1000,XE,UK,AU)

5 614 318 0708 ASSY,PANEL,FRONT(SS,KR)

5 614 317 3267 ASSY,PANEL,FRONT(US,CA)

6 614 315 6642 CHASSIS,MECHA/TRANS/PWB

7 614 315 6666 DEC,WINDOW,FL

8 614 315 7762 HOLDER,TRANS

9 614 315 6734 MOUNTING,PWB,JACK PWB FIX

10 614 310 3837 MOUNTING,FAN

11 614 315 6765 PANEL,REAR(1000)

11 614 317 5445 PANEL,REAR(XE)

11 614 317 5452 PANEL,REAR(UK)

11 614 317 5469 PANEL,REAR(SS)

11 614 318 6182 PANEL,REAR(KR)

11 614 317 3298 PANEL,REAR(US)

11 614 318 3679 PANEL,REAR(CA)

11 614 318 6199 PANEL.REAR(AU)

12 614 314 7107 SHIELD,MPEG PWB BOTTOM

13 614 314 7114 SHIELD,MPEG PWB TOP

14 614 315 6796 SHIELD,DVD MECHA,BOTTOM

15 614 315 6802 SHIELD,DVD MECHA,TOP

16 614 307 2638 LABEL,INDICATION,FUSE(1000)

17 614 315 8110 ASSY,DEC ESCUTCHEON

(1000,XE,UK,SS,KR,AU)

17 614 317 3243 ASSY,DEC,ESCUTCHEON(US,CA)

18 614 129 1901 FIXER,AC CORD

or 614 284 1884 FIXER,AC CORD

19 614 318 0166 SPACER,SHEET,CHASSIS

(1000,US,CA)

19 614 317 2994 SPACER,SHEET,CHASSIS

(XE,UK,SS,KR,AU)

20 614 129 9136 LUG,LEAD FIX

21 614 315 6628 BUTTON,SELECT(SS,KR)

22 614 317 5438 KNOB,ROTARY,MIC/ECHO VOL(SS,KR)

614 317 3090 LABEL,SAFETY(XE,UK,AU)

FIXING PARTS

REF.NO. PART NO. DESCRIPTION

Y01 411 021 3503 SCR S-TPG BIN 3X10,

MOUNTING,PANEL

Y02 411 021 3503 SCR S-TPG BIN 3X10,FRONT PWB

Y03 645 046 8209 SCREW,HEAT SINK UNIT

Y04 645 046 8216 SCREW,PANEL FRONT SIDE

Y05 645 046 8261 SCREW,PANEL REAR

Y06 411 021 6405 SCR S-TPG BIN 3X8,

MPEG PWB-SHIELD MPEG

Y07 411 021 3503 SCR S-TPG BIN 3X10,MPEG UNIT

Y08 411 020 8905 SCR S-TPG BRZ+FLG 3X10,

DVD MECHA

- 48 -

PARTS LIST

REF.NO. PART NO. DESCRIPTION

Y09 411 001 4209 SCR S-TPG BIN 4X8,TRANS

Y10 411 021 3503 SCR S-TPG BIN 3X10,HOLDER TRANS

Y11 411 021 3701 SCR S-TPG BIN 3X10,MOUNTING FAN

Y12 411 021 3503 SCR S-TPG BIN 3X10,FRONT PWB

Y13 411 021 3503 SCR S-TPG BIN 3X10,

Y14 411 021 3503 SCR S-TPG BIN 3X10,JACK PWB L/R

Y15 411 021 3503 SCR S-TPG BIN 3X10,MOUNTING PWB

Y16 411 021 3503 SCR S-TPG BIN 3X10,JACK PWB C

Y17 411 021 3503 SCR S-TPG BIN 3X10,

Y18 411 020 8905 SCR S-TPG BRZ+FLG 3X10,

Y19 411 020 8905 SCR S-TPG BRZ+FLG 3X10,

Y20 411 021 3503 SCR S-TPG BIN 3X10,

Y21 411 123 9106 SCR S-TPG BIN 3X20,

Y22 411 021 3701 SCR S-TPG BIN 3X10,

Y23 411 021 6405 SCR S-TPG BIN 3X8,

Y24 411 021 4500 SCR S-TPG BIN 3X16,POWER IC 1

or 411 021 4500 SCR S-TPG BIN 3X16,POWER IC 2

Y25 411 021 3503 SCR S-TPG BIN 3X10,POSISTOR

or 411 021 3503 SCR S-TPG BIN 3X10,HEAT SINK 1

or 411 021 3503 SCR S-TPG BIN 3X10,HEAT SINK 2

or 411 021 3503 SCR S-TPG BIN 3X10,HEAT SINK 3

or 411 021 3503 SCR S-TPG BIN 3X10,HEAT SINK 4

Y26 411 021 6405 SCR S-TPG BIN 3X8,Q4990

Y27 411 021 1806 SCR S-TPG BIN 2.6X10,

ELECTRICAL PART

REF.NO. PART NO. DESCRIPTION

51 645 044 9567 FLEXIBLE FLAT CABLE (CN001)

52 645 044 9574 FLEXIBLE FLAT CABLE (CN002)

53 614 315 8653 ASSY,WIRE,POWER-MPEG (CN400)

54 614 315 8660 ASSY,WIRE,POWER-LODER (CN401)

55 614 315 8677 ASSY,WIRE,DIGITAL-MPEG (CN402)

56 614 315 8707 ASSY,WIRE,PRE-MPEG (CN404)

57 614 315 8745 ASSY,WIRE,PRE-POWER (CN406)

58 645 046 8421 FLEXIBLE FLAT CABLE,FRONT-PRE

59

59

or

60

61 614 129 9082 LUG,POWER PWB-GND

62 645 045 6930 MOTOR,FAN DC 0.72W(Except CA)

63

63

63

63

64

or

64

or

64

or

64

64

or

!!

!

423 028 7002 FUSE 250V 2.5A(1000,US,CA)

!!

!

423 028 8306 FUSE250V 1.25A(XE,UK,AU)

!!

!

423 005 6509 FUSE 250V 1.25A(XE,UK,AU)

!!

!

614 315 6994 ASSY,HEAT SINK,ASSY,HEAT SINK

!!

!

645 044 9635 TRANS,POWER(1000,US,CA)

!!

!

645 044 9642 TRANS,POWER(XE,UK,AU)

!!

!

645 044 9659 TRANS,POWER(SS)

!!

!

645 047 7959 TRANS,POWER(KR)

!!

!

645 037 7747 CORD,POWER-1.845MK(1000,US,CA)

!!

!

645 032 7537 CORD,POWER-1.86MK

!!

!

645 016 9939 CORD,POWER-1.74MK(XE,SS)

!!

!

614 255 2513 POWER CORD

!!

!

645 036 9797 CORD,POWER-1.6MK(UK)

!!

!

645 036 9803 POWER CORD

!!

!

645 039 2528 CORD,POWER-1.75MK(KR)

!!

!

645 032 1887 CORD,POWER-2.0MK(AU)

!!

!

614 256 5308 POWER CORD

!!

!

614 086 2164 COVER,CAPACITOR(C4300)(XE,UK)

FRONTJACK(PRE AMP) PWB

FRONT ASSY-CHASSIS ASSY

CHASSIS(BOTTOM SIDE)

CHASSIS(BACK SIDE)

PANEL FRONT(BOTTOM SIDE)

PANEL FRONT(L/R SIDE)

PANEL REAR/ELECT PARTS

SHIELD MECHA TOP

VOLTAGE SELECTOR(SS)

MPEG-LOADER 16P

MPEG-LOADER 26P

SOCKET-A P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

71 614 314 5721 ASSY,PWB,SOCKET-A(Only initial)

(1000,US,CA)

71 614 318 0234 ASSY,PWB,SOCKET-A(Only initial)(SS)

71 614 318 5529 ASSY,PWB,SOCKET-A(Only initial)(KR)

71 614 318 5826 ASSY,PWB,SOCKET-A(Only initial)(AU)

CN429 614 315 8776 ASSY,WIRE,POWER-AUDIO

(SS,KR,AU)

CN430 614 315 8776 ASSY,WIRE,POWER-AUDIO

(1000,US,CA)

CN430 645 005 9315 PLUG,2P(SS)

CN431 645 005 9315 PLUG,2P(1000,KR,US,CA,AU)

CN431 645 030 9878 PLUG,3P(SS)

CN432 645 045 7500 JACK,RCA-4

CN433 645 038 3670 JACK,RCA

CN434 645 011 8210 TERMINAL

CN435 645 023 4378 SOCKET,7P

CN436 614 315 8714 ASSY,WIRE,SOCKET_A-PRE

CN437 614 315 8691 ASSY,WIRE,VIDEO-SOCKET_A

CN438 614 310 2434 PLUG,2P

or 645 005 7366 PLUG,2P

CN439 614 310 2298 PLUG,2P

or 645 004 2683 PLUG,2P

CN491 645 031 7903 HOLDER,FUSE

or 645 006 4760 HOLDER,FUSE

CN492 645 031 7903 HOLDER,FUSE

or 645 006 4760 HOLDER,FUSE

CN493 645 031 7903 HOLDER,FUSE(SS)

or 645 006 4760 HOLDER,FUSE

CN494 645 031 7903 HOLDER,FUSE(SS)

or 645 006 4760 HOLDER,FUSE

!!

L4300

!

645 038 7364 INDUCTOR,70U

LUG43 645 023 8987 FIXER

!!

R4300

or

or

R4371

!

402 080 9803 CARBON 3.3M J- 1/2W

!!

!

402 078 8108 CARBON 3.3M J- 1/2W

!!

!

402 078 9501 CARBON 3.3M J- 1/2W

!!

!

614 241 3449 RESISTOR 0.22 K- 5W

S4399 645 031 5800 SWITCH,SLIDE 2P-2T(SS)

WR430 614 017 6964 TERMINAL BOARD

WR431 614 017 6964 TERMINAL BOARD

SOCKET-A P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

71 614 317 9351 ASSY,PWB,SOCKET-A,ASSY

!!

C4300

or

!

403 349 3303 CERAMIC 0.01U M 250V

!!

!

403 366 7803 CERAMIC 0.01U M 250V

C4305 403 329 5501 ELECT 2200U M 16V

C4311 404 079 6107 ELECT 47U M 16V

CN429 614 315 8776 ASSY,WIRE,POWER-AUDIO

CN430 645 005 9315 PLUG,2P

CN431 614 315 8684 ASSY,WIRE,VIDEO-SOCKET_A

CN432 645 045 7500 JACK,RCA-4

CN433 645 038 3670 JACK,RCA

CN434 645 011 8210 TERMINAL

CN435 645 023 4378 SOCKET,7P

CN436 614 315 8714 ASSY,WIRE,SOCKET_A-PRE

CN437 614 315 8691 ASSY,WIRE,VIDEO-SOCKET_A

CN438 614 310 2434 PLUG,2P

or 645 005 7366 PLUG,2P

CN439 614 310 2298 PLUG,2P

or 645 004 2683 PLUG,2P

CN491 645 031 7903 HOLDER,FUSE

or 645 006 4760 HOLDER,FUSE

CN492 645 031 7903 HOLDER,FUSE

or 645 006 4760 HOLDER,FUSE

!!

D4301

D4302

D4303

!

407 097 8009 DIODE MPG06G

!!

!

407 097 8009 DIODE MPG06G

!!

!

407 097 8009 DIODE MPG06G

(Only initial)(XE,UK)

- 49 -

PARTS LIST

REF.NO. PART NO. DESCRIPTION REF.NO. PART NO. DESCRIPTION

D4304

D4312 407 099 5402 ZENER DIODE MTZJ6.2B

D4313 407 012 4406 DIODE 1SS133

L4300

LUG43 645 023 8987 FIXER

Q4310 405 141 3208 TR KTC3198-Y

or 405 141 3307 TR KTC3198-GR

or 405 019 2708 TR 2SC536-F-NP

or 405 019 3804 TR 2SC536-G-NP

Q4311 405 141 3208 TR KTC3198-Y

or 405 141 3307 TR KTC3198-GR

or 405 019 2708 TR 2SC536-F-NP

or 405 019 3804 TR 2SC536-G-NP

R4371

RY430

or

T4300

WR430 614 017 8203 TERMINAL BOARD

WR431 614 017 8203 TERMINAL BOARD

DIGITAL OUT P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

72 614 314 5738 ASSY,PWB,SW(Only initial)

72 614 317 9368 ASSY,PWB,SW(Only initial)(XE,UK)

72 614 318 0241 ASSY,PWB,SW(Only initial)(SS)

72 614 318 5536 ASSY,PWB,SW(Only initial)(KR)

72 614 318 7417 ASSY,PWB,SW(Only initial)(AU)

CN420 407 218 1100 PHOTO COUPLE GP1FA550TZ

or 407 215 1608 PHOTO COUPLE TOTX178A

CN421 614 310 2458 PLUG,4P

or 645 005 8110 PLUG,4P

S4200 645 040 6119 SWITCH,SLIDE 2P-2TX2,

FRONT P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

73 614 314 5776 ASSY,PWB,FRONT(Only initial)

73 614 317 9375 ASSY,PWB,FRONT(Only initial)(XE,UK)

73 614 318 0258 ASSY,PWB,FRONT(Only initial)(SS,KR)

73 614 318 5833 ASSY,PWB,FRONT(Only initial)(AU)

BR601 614 315 5843 HOLDER,FL,FL_MOUNT

CN601 645 012 5515 SOCKET,FPC 18P

CN602 614 315 8530 ASSY,WIRE

CN603 614 315 8530 ASSY,WIRE

D6001 407 012 4406 DIODE 1SS133

D6002 407 012 4406 DIODE 1SS133

D6003 407 012 4406 DIODE 1SS133

D6004 407 003 4507 DIODE DAP202K

D6850 408 044 8509 LED SLZ-9G55B-24HAB-T1

D6851 408 044 8509 LED SLZ-9G55B-24HAB-T1

D6852 408 044 8509 LED SLZ-9G55B-24HAB-T1

D6853 408 044 8509 LED SLZ-9G55B-24HAB-T1

D6870 407 115 1302 LED SLP-144B-51-A,STANDBY

DS601 407 217 1101 PHOTO DIODE SPS-442-1G,IR

FL601 645 044 8232 FLUORESCENT TUBE,FL

IC601 410 404 1006 IC LC866540A-5V28,MICON

L6000 645 001 4550 INDUCTOR,10U K

or 645 031 7835 INDUCTOR,10U K

Q6001 405 146 2107 TR KTC3875-Y

or 405 146 2206 TR KTC3875-GR

or 405 014 4509 TR 2SC2412K-R

or 405 011 1006 TR 2SC1623-L6

Q6004 405 146 5306 TR KRA102S(SS)

or 405 000 0409 TR DTA114EK

Q6006 405 146 2107 TR KTC3875-Y(SS)

or 405 146 2206 TR KTC3875-GR

or 405 014 4509 TR 2SC2412K-R

or 405 011 1006 TR 2SC1623-L6

!!

!

407 097 8009 DIODE MPG06G

!!

!

645 038 7364 INDUCTOR,70U

!!

!

614 241 3449 RESISTOR 0.22 K- 5W

!!

!

645 030 5597 RELAY,PRIMARY

!!

!

645 035 6575 RELAY,PRIMARY

!!

!

645 041 4954 TRANS,POWER

PAL-NTSC(XE,UK,AU)

(1000,US,CA)

(1000,US,CA)

S6100 645 006 5958 SWITCH,PUSH 1P-1T

S6101 645 006 5958 SWITCH,PUSH 1P-1T

S6102 645 006 5958 SWITCH,PUSH 1P-1T

S6103 645 006 5958 SWITCH,PUSH 1P-1T

S6115 645 006 5958 SWITCH,PUSH 1P-1T

S6116 645 006 5958 SWITCH,PUSH 1P-1T

S6117 645 006 5958 SWITCH,PUSH 1P-1T

S6118 645 006 5958 SWITCH,PUSH 1P-1T

S6119 645 006 5958 SWITCH,PUSH 1P-1T

S6120 645 006 5958 SWITCH,PUSH 1P-1T

X6002 645 018 6103 OSC,CERAMIC 6.000MHZ

POWER AMP P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

74 614 314 5783 ASSY,PWB,POWER(Only initial)

74 614 317 9382 ASSY,PWB,POWER(Only initial)(XE,UK)

74 614 318 0265 ASSY,PWB,POWER(Only initial)(SS,KR)

74 614 318 5840 ASSY,PWB,POWER(Only initial)(AU)

C4705 403 057 2407 POLYESTER 0.1U J 50V

C4706 403 057 2407 POLYESTER 0.1U J 50V

C4750 403 185 0108 MT-POLYEST 0.47U J 50V

C4751 403 184 9805 MT-POLYEST 0.22U J 50V

C4805 403 057 2407 POLYESTER 0.1U J 50V

C4806 403 057 2407 POLYESTER 0.1U J 50V

C4825 403 057 2407 POLYESTER 0.1U J 50V

C4826 403 057 2407 POLYESTER 0.1U J 50V

C4900 403 329 6201 ELECT 2200U M 35V

!!

C4900

!

404 085 9505 ELECT 2200U M 35V(XE,UK)

C4901 403 329 6201 ELECT 2200U M 35V

!!

C4901

!

404 085 9505 ELECT 2200U M 35V(XE,UK)

C4910 403 329 6201 ELECT 2200U M 35V

!!

C4910

!

404 085 9505 ELECT 2200U M 35V(XE,UK)

C4914 403 326 2503 ELECT 1200U M 10V

C4918 404 079 6305 ELECT 10U M 50V(1000,US,CA)

C4924 403 337 1205 ELECT 1200U M 6.3V

CN470 614 310 2496 PLUG,8P

or 645 005 8134 PLUG,8P

CN471 614 310 2342 PLUG,7P

or 645 004 2737 PLUG,7P

CN472 614 310 2465 PLUG,5P

or 645 005 9292 PLUG,5P

CN473 614 315 8752 ASSY,WIRE,POWER-SOCKET_A

CN474 614 310 2458 PLUG,4P

or 645 005 8110 PLUG,4P

CN475 645 006 0939 PLUG,6P

or 614 310 2625 PLUG,6P

CN476 645 006 0960 PLUG,9P

or 614 310 2656 PLUG,9P

CN477 645 006 1905 PLUG,5P

D4730 407 012 4406 DIODE 1SS133

D4731 407 012 4406 DIODE 1SS133

D4750 407 012 4406 DIODE 1SS133

!!

D4900

D4904

D4905

D4906

D4907

!

408 043 8005 DIODE G5SBA60L-BU04

!!

!

407 196 5800 DIODE 1N5402BD82

!!

!

407 196 5800 DIODE 1N5402BD82

!!

!

408 044 6208 DIODE SB240L 19C2-105

!!

!

408 044 6208 DIODE SB240L 19C2-105

HS490 614 264 0159 HEAT SINK(XE,UK,SS,KR)

!!

IC470

IC491

IC492

or

IC493

!

409 473 9501 IC STK402-230

!!

!

409 499 5808 IC PQ1CZ31H2ZP,PQ1CZ31H2ZP

!!

!

409 463 6701 IC KIA7805API

!!

!

409 145 2809 IC NJM7805FA

!!

!

409 499 5808 IC PQ1CZ31H2ZP,PQ1CZ31H2ZP

L4700 614 202 1712 V.H.F COIL 1AV4L20B0320N

or 614 196 9763 V.H.F COIL

(1000,SS,KR,US,CA,AU)

(1000,SS,KR,US,CA,AU)

(1000,SS,KR,US,CA,AU)

(1000,US,CA)

- 50 -

PARTS LIST

L4800 614 202 1712 V.H.F COIL 1AV4L20B0320N

or 614 196 9763 V.H.F COIL

L4820 614 202 1712 V.H.F COIL 1AV4L20B0320N

or 614 196 9763 V.H.F COIL

L4900 645 043 3054 INDUCTOR,10U

L4901

L4902 645 043 3054 INDUCTOR,10U

L4904

L4905 645 043 3054 INDUCTOR,10U

PR490

PR491

PR492

PR493

Q4700 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4730 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4731 405 143 6504 TR KTA1267-GR

or 405 004 4601 TR 2SA608-F-SPA

or 405 004 5103 TR 2SA608-G-SPA

or 405 006 1806 TR 2SA933S-R

or 405 006 1905 TR 2SA933S-S

Q4732 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4733 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4734 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4735 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4736 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4737 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4738 405 141 3208 TR KTC3198-Y

or 405 141 3307 TR KTC3198-GR

or 405 019 2708 TR 2SC536-F-NP

or 405 019 3804 TR 2SC536-G-NP

Q4739 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4740 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

!!

!

645 045 7241 INDUCTOR,65U

!!

!

645 045 7241 INDUCTOR,65U

!!

!

645 042 2720 PROTECTOR,5A 125V

!!

!

645 042 2652 PROTECTOR,10A 125V

!!

!

645 042 2720 PROTECTOR,5A 125V

!!

!

645 042 2652 PROTECTOR,10A 125V

REF.NO. PART NO. DESCRIPTIONREF.NO. PART NO. DESCRIPTION

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4741 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4750 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4800 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4820 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4910 405 146 1605 TR KRC102S

or 405 000 2908 TR DTC114EK

Q4911 405 146 1605 TR KRC102S

or 405 000 2908 TR DTC114EK

Q4912 405 146 1605 TR KRC102S

or 405 000 2908 TR DTC114EK

Q4920 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

!!

R4706

R4707

R4708

R4716

R4717

R4730

!

402 081 0403 RESISTOR 4.7 J- 2W

!!

!

402 081 0502 RESISTOR 330 J- 3W

!!

!

402 081 0403 RESISTOR 4.7 J- 2W

!!

!

402 081 1103 FUSIBLE RES 100 JA 1/4W

!!

!

402 081 1103 FUSIBLE RES 100 JA 1/4W

!!

!

614 241 3449 RESISTOR 0.22 K- 5W

R4799 408 017 0806 TH PTH9M04BB471TS2F333

!!

R4806

R4807

R4808

R4826

R4828

!

402 081 0403 RESISTOR 4.7 J- 2W

!!

!

402 081 0502 RESISTOR 330 J- 3W

!!

!

402 081 0403 RESISTOR 4.7 J- 2W

!!

!

402 081 0403 RESISTOR 4.7 J- 2W

!!

!

402 081 0403 RESISTOR 4.7 J- 2W

RY470 614 224 4531 RELAY,SPEAKER

or 645 035 6582 RELAY,SPEAKER

RY480 645 046 1279 RELAY,SPEAKER

or 645 046 1743 RELAY,SPEAKER

PRE AMPLIFIER P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

75 614 315 8080 ASSY,PWB,PRE(Only initial)

75 614 317 9399 ASSY,PWB,PRE(Only initial)(XE,UK)

75 614 318 0272 ASSY,PWB,PRE(Only initial)(SS,KR)

75 614 318 5857 ASSY,PWB,PRE(Only initial)(AU)

CN440 614 315 8738 ASSY,WIRE,POWER-PRE

CN441 645 047 2060 JACK,PHONE D3.6

CN442 645 047 2060 JACK,PHONE D3.6

CN443 645 047 2060 JACK,PHONE D3.6 (SS,KR)

CN445 614 035 4942 SOCKET,DIP 5P

CN451 614 310 2472 PLUG,6P

or 645 005 8127 PLUG,6P

CN452 614 310 2441 PLUG,3P

or 645 005 7373 PLUG,3P

CN453 645 012 5515 SOCKET,FPC 18P

CN456 614 310 2496 PLUG,8P

or 645 005 8134 PLUG,8P

(1000,US,CA)

- 51 -

PARTS LIST

REF.NO. PART NO. DESCRIPTION REF.NO. PART NO. DESCRIPTION

CN457 614 315 8530 ASSY,WIRE,VIDEO-PRE

D4560 407 099 5303 ZENER DIODE MTZJ5.6B(SS,KR)

D4561 407 012 4406 DIODE 1SS133(SS,KR)

D4562 407 012 4406 DIODE 1SS133(SS,KR)

IC450 409 474 6103 IC LC75342M

IC451 409 478 1104 IC LA2615M,SURROUND

IC452 409 426 1804 IC KIA4558S

IC453 409 426 1804 IC KIA4558S

IC455 409 390 8908 IC BA3838F(SS,KR)

IC456 409 294 6109 IC TA2011S(SS,KR)

IC457 409 400 9505 IC BU9255FS(SS,KR)

L4401 645 001 4581 INDUCTOR,100U K(Eecept XE,UK)

or 645 031 7842 INDUCTOR,100U K

L4401 645 006 9864 INDUCTOR,80U(XE,UK)

or 645 212 3171 INDUCTOR,FERITE

L4402 645 001 4581 INDUCTOR,100U K(Eecept XE,UK)

or 645 031 7842 INDUCTOR,100U K

L4402 645 006 9864 INDUCTOR,80U(XE,UK)

or 645 212 3171 INDUCTOR,FERITE

L4403 645 001 4581 INDUCTOR,100U K(Eecept XE,UK)

or 645 031 7842 INDUCTOR,100U K

L4404 645 001 4581 INDUCTOR,100U K(Eecept XE,UK)

or 645 031 7842 INDUCTOR,100U K

L4451 645 001 4581 INDUCTOR,100U K(Eecept XE,UK)

or 645 031 7842 INDUCTOR,100U K

L4451 645 006 9864 INDUCTOR,80U(XE,UK)

or 645 212 3171 INDUCTOR,FERITE

L4452 645 001 4581 INDUCTOR,100U K(Eecept XE,UK)

or 645 031 7842 INDUCTOR,100U K

L4452 645 006 9864 INDUCTOR,80U(XE,UK)

or 645 212 3171 INDUCTOR,FERITE

L4453 645 001 4581 INDUCTOR,100U K(Eecept XE,UK)

or 645 031 7842 INDUCTOR,100U K

L4454 645 001 4581 INDUCTOR,100U K(Eecept XE,UK)

or 645 031 7842 INDUCTOR,100U K

Q4430 405 151 4400 TR KTD1303

or 405 021 0204 TR 2SD1012-F-SPA

or 405 021 0600 TR 2SD1012-G-SPA

or 405 033 6706 TR 2SD1468S-R

or 405 033 6805 TR 2SD1468S-S

Q4480 405 151 4400 TR KTD1303

or 405 021 0204 TR 2SD1012-F-SPA

or 405 021 0600 TR 2SD1012-G-SPA

or 405 033 6706 TR 2SD1468S-R

or 405 033 6805 TR 2SD1468S-S

Q4500 405 151 4400 TR KTD1303

or 405 021 0204 TR 2SD1012-F-SPA

or 405 021 0600 TR 2SD1012-G-SPA

or 405 033 6706 TR 2SD1468S-R

or 405 033 6805 TR 2SD1468S-S

Q4520 405 151 4400 TR KTD1303(SS,KR)

or 405 021 0204 TR 2SD1012-F-SPA

or 405 021 0600 TR 2SD1012-G-SPA

or 405 033 6706 TR 2SD1468S-R

or 405 033 6805 TR 2SD1468S-S

Q4531 405 143 6504 TR KTA1267-GR

or 405 004 4601 TR 2SA608-F-SPA

or 405 004 5103 TR 2SA608-G-SPA

or 405 006 1806 TR 2SA933S-R

or 405 006 1905 TR 2SA933S-S

Q4532 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4535 405 143 6504 TR KTA1267-GR

or 405 004 4601 TR 2SA608-F-SPA

or 405 004 5103 TR 2SA608-G-SPA

or 405 006 1806 TR 2SA933S-R

or 405 006 1905 TR 2SA933S-S

Q4536 405 143 8706 TR KTC3199-GR

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4560 405 143 8706 TR KTC3199-GR(SS,KR)

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4561 405 143 8706 TR KTC3199-GR(SS,KR)

or 405 017 9600 TR 2SC3330-T

or 405 017 9709 TR 2SC3330-U

or 405 011 8500 TR 2SC1740S-R

or 405 011 8609 TR 2SC1740S-S

Q4562 405 109 9204 TR KRC102M-A(SS,KR)

or 405 000 3103 TR DTC114ES

Q4563 405 109 9204 TR KRC102M-A(SS,KR)

or 405 000 3103 TR DTC114ES

Q4600 405 151 4400 TR KTD1303

or 405 021 0204 TR 2SD1012-F-SPA

or 405 021 0600 TR 2SD1012-G-SPA

or 405 033 6706 TR 2SD1468S-R

or 405 033 6805 TR 2SD1468S-S

S4400 614 215 9828 SWITCH,TACT,VOCALFADER

VR440 645 012 3054 VR,ROTARY 10KB

VR441 645 012 3054 VR,ROTARY 10KB

VIDEO P.W.BOARD ASSY

REF.NO. PART NO. DESCRIPTION

76 614 315 8097 ASSY,PWB,VIDEO(Only initial)

76 614 317 9405 ASSY,PWB,VIDEO(Only initial)(XE,UK)

76 614 318 0289 ASSY,PWB,VIDEO(Only initial)(SS,KR)

76 614 318 5864 ASSY,PWB,VIDEO(Only initial)(AU)

C4112 403 325 0401 ELECT 1000U M 6.3V

C4970 403 329 6201 ELECT 2200U M 35V

C4971 403 329 6102 ELECT 1000U M 35V

CN410 614 310 2526 PLUG,11P

or 645 005 8165 PLUG,11P

CN411 645 041 1298 JACK,RCA-6)(1000,SS,KR,US,CA)

CN411 645 041 1694 JACK,RCA-3(XE,UK)

CN412 645 044 9086 SOCKET,DIN 4P

CN413 614 035 4928 SOCKET,DIP 3P

CN415 645 021 1508 SOCKET,RGB 21P(XE,UK)

CN416 614 310 2434 PLUG,2P

or 645 005 7366 PLUG,2P

CN417 614 310 2496 PLUG,8P

or 645 005 8134 PLUG,8P

CN495 645 006 0922 PLUG,5P

or 614 310 2618 PLUG,5P

CN496 645 006 0953 PLUG,8P

or 614 310 2649 PLUG,8P

CN497 614 315 8783 ASSY,WIRE,VIDEO-POWER

CN498 645 005 8226 PLUG,3P(XE,UK)

or 614 310 2595 PLUG,3P

D4101 407 218 9205 ZENER DI0DE KDZ15V(XE,UK)

or 407 187 8001 ZENER DIODE UDZ10B

or 407 206 5608 ZENER DIODE UDZS10B

or 407 179 1003 ZENER DIODE UDZ15B

or 407 218 7409 ZENER DIODE UDZS15B

D4102 407 218 9205 ZENER DI0DE KDZ15V(XE,UK)

or 407 187 8001 ZENER DIODE UDZ10B

or 407 206 5608 ZENER DIODE UDZS10B

or 407 179 1003 ZENER DIODE UDZ15B

or 407 218 7409 ZENER DIODE UDZS15B

D4103 407 218 9205 ZENER DI0DE KDZ15V(XE,UK)

or 407 187 8001 ZENER DIODE UDZ10B

or 407 206 5608 ZENER DIODE UDZS10B

or 407 179 1003 ZENER DIODE UDZ15B

or 407 218 7409 ZENER DIODE UDZS15B

(1000,US,CA)

- 52 -

PARTS LIST

REF.NO. PART NO. DESCRIPTION

D4104 407 218 9205 ZENER DI0DE KDZ15V(XE,UK)

or 407 187 8001 ZENER DIODE UDZ10B

or 407 206 5608 ZENER DIODE UDZS10B

or 407 179 1003 ZENER DIODE UDZ15B

or 407 218 7409 ZENER DIODE UDZS15B

D4105 407 218 9205 ZENER DI0DE KDZ15V(XE,UK)

or 407 187 8001 ZENER DIODE UDZ10B

or 407 206 5608 ZENER DIODE UDZS10B

or 407 179 1003 ZENER DIODE UDZ15B

or 407 218 7409 ZENER DIODE UDZS15B

D4106 407 218 9205 ZENER DI0DE KDZ15V(XE,UK)

or 407 187 8001 ZENER DIODE UDZ10B

or 407 206 5608 ZENER DIODE UDZS10B

or 407 179 1003 ZENER DIODE UDZ15B

or 407 218 7409 ZENER DIODE UDZS15B

D4107 407 218 9205 ZENER DI0DE KDZ15V(XE,UK)

or 407 187 8001 ZENER DIODE UDZ10B

or 407 206 5608 ZENER DIODE UDZS10B

or 407 179 1003 ZENER DIODE UDZ15B

or 407 218 7409 ZENER DIODE UDZS15B

D4108 407 218 9205 ZENER DI0DE KDZ15V(XE,UK)

or 407 187 8001 ZENER DIODE UDZ10B

or 407 206 5608 ZENER DIODE UDZS10B

or 407 179 1003 ZENER DIODE UDZ15B

or 407 218 7409 ZENER DIODE UDZS15B

D4109 407 218 9205 ZENER DI0DE KDZ15V(XE,UK)

or 407 187 8001 ZENER DIODE UDZ10B

or 407 206 5608 ZENER DIODE UDZS10B

or 407 179 1003 ZENER DIODE UDZ15B

or 407 218 7409 ZENER DIODE UDZS15B

D4110 407 218 9205 ZENER DI0DE KDZ15V(XE,UK)

or 407 187 8001 ZENER DIODE UDZ10B

or 407 206 5608 ZENER DIODE UDZS10B

or 407 179 1003 ZENER DIODE UDZ15B

or 407 218 7409 ZENER DIODE UDZS15B

D4111 407 218 9205 ZENER DI0DE KDZ15V

or 407 187 8001 ZENER DIODE UDZ10B

or 407 206 5608 ZENER DIODE UDZS10B

or 407 179 1003 ZENER DIODE UDZ15B

or 407 218 7409 ZENER DIODE UDZS15B

D4112 407 218 9205 ZENER DI0DE KDZ15V

or 407 187 8001 ZENER DIODE UDZ10B

or 407 206 5608 ZENER DIODE UDZS10B

or 407 179 1003 ZENER DIODE UDZ15B

or 407 218 7409 ZENER DIODE UDZS15B

D4113 407 012 4406 DIODE 1SS133(XE,UK)

D4114 407 012 4406 DIODE 1SS133(XE,UK)

D4954 407 012 4406 DIODE 1SS133

D4955 407 012 4406 DIODE 1SS133

D4956 407 012 4406 DIODE 1SS133

D4957 407 012 4406 DIODE 1SS133

D4958 407 099 9509 ZENER DIODE MTZJ30B

D4959 407 099 5204 ZENER DIODE MTZJ5.1B

D4960 407 099 4603 ZENER DIODE MTZJ3.9B

D4961 407 012 4406 DIODE 1SS133

D4962 407 099 6102 ZENER DIODE MTZJ10B

D4963 407 012 4406 DIODE 1SS133

D4964

D4965

D4966 407 012 4406 DIODE 1SS133

D4970

D4971

D4972

D4973

D4974 407 099 4603 ZENER DIODE MTZJ3.9B

D4975 407 099 6805 ZENER DIODE MTZJ13B

D4976 407 099 6805 ZENER DIODE MTZJ13B

HS410 614 270 2598 HEAT SINK

IC410 409 499 5907 IC MM1508XNRE,MM1508XNRE

IC495

or

!!

!

407 097 8009 DIODE MPG06G(XE,UK)

!!

!

407 097 8009 DIODE MPG06G(XE,UK)

!!

!

407 097 8009 DIODE MPG06G

!!

!

407 097 8009 DIODE MPG06G

!!

!

407 098 3300 DIODE RL153-BF-S2

!!

!

407 098 3300 DIODE RL153-BF-S2

!!

!

409 463 6701 IC KIA7805API

!!

!

409 145 2809 IC NJM7805FA

REF.NO. PART NO. DESCRIPTION

L4100 645 034 7887 INDUCTOR,1000 OHM(XE,UK)

or 645 020 1813 INDUCTOR,1000 OHM

L4101 645 034 7887 INDUCTOR,1000 OHM(XE,UK)

or 645 020 1813 INDUCTOR,1000 OHM

LUG41 645 023 8987 FIXER

!!

PR410

or

PR411

PR495

PR496

PR497

or

PR498

!

645 042 2577 PROTECTOR,0.8A 125V(XE,UK)

!!

!

645 014 2505 PROTECTOR,0.8A 125V

!!

!

645 027 4169 PROTECTOR,0.125A 125V

!!

!

645 042 2720 PROTECTOR,5A 125V

!!

!

645 042 2720 PROTECTOR,5A 125V

!!

!

645 042 2577 PROTECTOR,0.8A 125V

!!

!

645 014 2505 PROTECTOR,0.8A 125V

!!

!

645 027 4169 PROTECTOR,0.125A 125V

Q4100 405 151 4400 TR KTD1303

or 405 021 0204 TR 2SD1012-F-SPA

or 405 021 0600 TR 2SD1012-G-SPA

or 405 033 6706 TR 2SD1468S-R

or 405 033 6805 TR 2SD1468S-S

Q4101 405 151 4400 TR KTD1303

or 405 021 0204 TR 2SD1012-F-SPA

or 405 021 0600 TR 2SD1012-G-SPA

or 405 033 6706 TR 2SD1468S-R

or 405 033 6805 TR 2SD1468S-S

Q4102 405 146 2107 TR KTC3875-Y(XE,UK)

or 405 146 2206 TR KTC3875-GR

or 405 014 4509 TR 2SC2412K-R

or 405 011 1006 TR 2SC1623-L6

Q4120 405 146 1605 TR KRC102S(XE,UK)

or 405 000 2908 TR DTC114EK

Q4121 405 146 5306 TR KRA102S(XE,UK)

or 405 000 0409 TR DTA114EK

Q4950 405 141 3703 TR KTA1271-Y

or 405 008 2405 TR 2SB698-F

or 405 008 2504 TR 2SB698-G

Q4951 405 146 1704 TR KTA1504-Y

or 405 146 9700 TR KTA1504-GR

or 405 005 5508 TR 2SA812-M6

Q4952 405 146 1704 TR KTA1504-Y

or 405 146 9700 TR KTA1504-GR

or 405 005 5508 TR 2SA812-M6

Q4970 405 143 6504 TR KTA1267-GR

or 405 004 4601 TR 2SA608-F-SPA

or 405 004 5103 TR 2SA608-G-SPA

or 405 006 1806 TR 2SA933S-R

or 405 006 1905 TR 2SA933S-S

Q4971 405 143 6504 TR KTA1267-GR

or 405 004 4601 TR 2SA608-F-SPA

or 405 004 5103 TR 2SA608-G-SPA

or 405 006 1806 TR 2SA933S-R