Fairchild Semiconductor ML6426X4 Datasheet

ML6426

High Bandwidth Triple Video Filters with Buffered

Outputs for RGB or YUV

GENERAL DESCRIPTION

The ML6426 are a family of triple video filters with

buffered outputs. There are several versions of the

ML6426, each with different passband cut-off frequencies

of 6.7MHz, 12MHz, 15MHz, 24MHz, 30MHz, 36MHz,

and 48MHz. Each channel contains a 4

th

-order

Butterworth lowpass reconstruction video filter. The filter

is optimized for minimum overshoot and flat group delay

and guaranteed differential gain and phase at the outputs

of the integrated cable drivers.

All input signals from DACs are AC coupled into the

ML6426. All channels have DC restore circuitry to clamp

the DC input levels during video H-sync, using an output

feedback clamp. An external H-sync signal is required for

this purpose.

All outputs must be AC coupled into their loads. Each

output can drive 2V

P-P

into a 150Ω load. All channels

have a gain of 2 (6dB) at 1V

P-P

input levels.

FEATURES

■ 5V ±10% operation

■ RGB/YUV filters for ATSC Digital Television VESA

Standard

■ 2:1 Mux Inputs for multiple RGB/YUV inputs

■ Triple Reconstruction Filter options for 6.7, 12, 15, 24,

30, 36, and 48MHz to handle various line rates

■ Multiple ML6426 outputs can be paralleled to drive

RGB/YUV outputs at different frequencies for various

line rates by means of Disable/Enable pin.

■ 6dB drivers and sync tip clamps for DC restore

■ DC restore with minimal tilt

■ 0.4% differential gain on all channels

0.4º differential phase on all channels

0.8% total harmonic distortion on all channels

■ 2kV ESD protection

BLOCK DIAGRAM

RINA/YINA

2

RINB/YINB

BINA/VINA

8

BINB/VINB

9

A/B MUX

GINA/UINA

6

GIN/UINB

7

R

OUT/YOUT

13

G

OUT/UOUT

11

B

OUT/VOUT

10

4th-ORDER

FILTER A

4th-ORDER

FILTER B

4th-ORDER

FILTER C

MUX

MUX

MUX

×2

×2

×2

TRANSCONDUCTANCE

ERROR AMP

TRANSCONDUCTANCE

ERROR AMP

TRANSCONDUCTANCE

ERROR AMP

1

SYNCIN

16

GNDO

14

DISABLE

15

V

CCO

12

V

CC

4

GND

3

5

+

–

+

–

+

–

0.5V

0.5V

0.5V

ML6426-1 ML6426-2 ML6426-3 ML6426-4 ML6426-5 ML6426-6 ML6426-15

Filter A 6.7MHz 12MHz 24MHz 30MHz 36MHz 48MHz 15MHz

Filter B 6.7MHz 12MHz 24MHz 30MHz 36MHz 48MHz 15MHz

Filter C 6.7MHz 12MHz 24MHz 30MHz 36MHz 48MHz 15MHz

REV. 1.1 2/8/2001

ML6426

2 REV. 1.1 2/8/2001

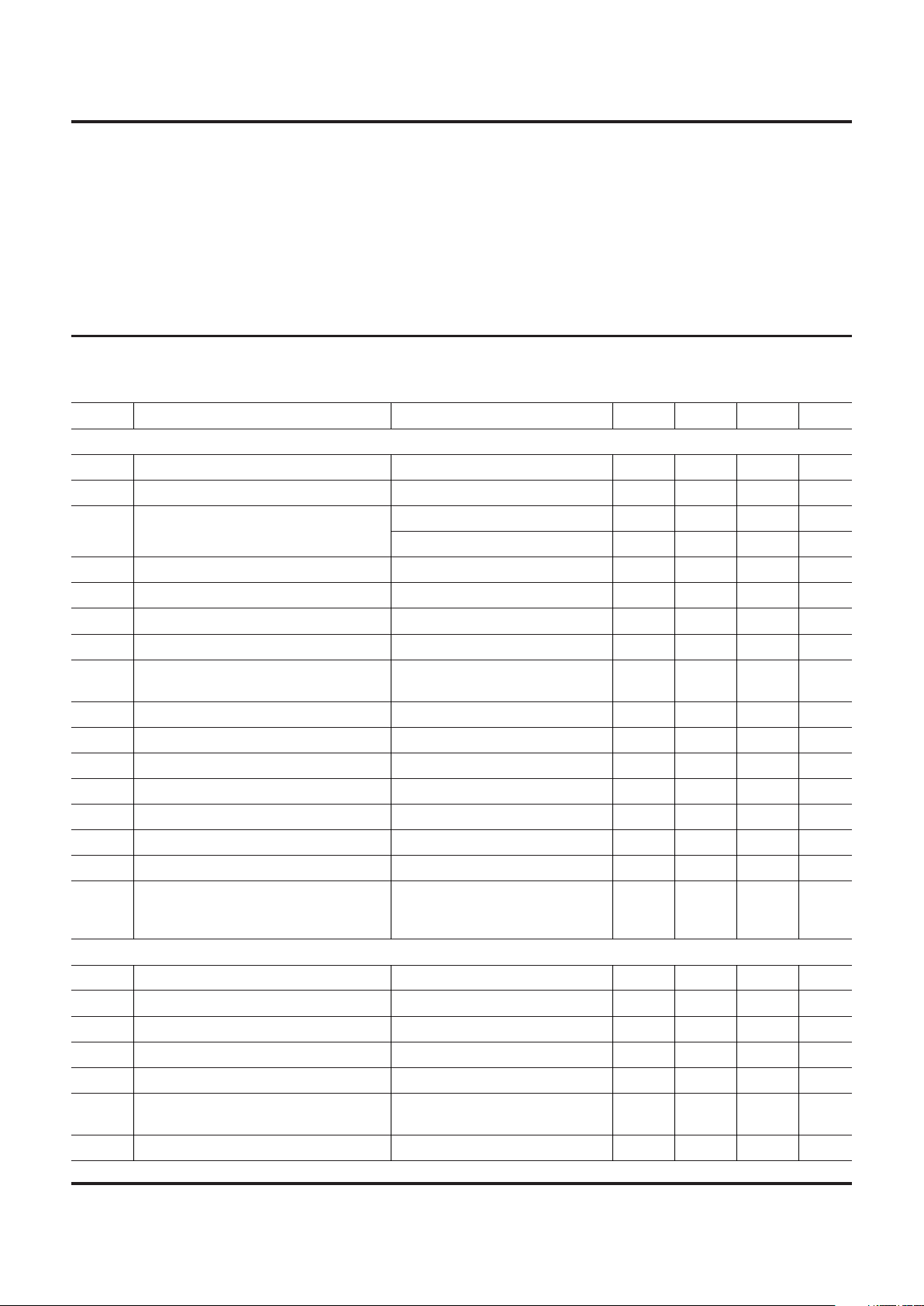

PIN CONFIGURATION

PIN DESCRIPTION

PIN NAME FUNCTION

1A/B MUX Logic input pin to select between

Bank <A> and Bank <B> video inputs.

This pin is internally pulled high.

2R

IN

A/YINA Unfiltered analog R- or Y-channel

input for Bank <A>. Sync must be

provided at SYNC IN pin.

3 GND Analog ground

4V

CC

Analog 5V supply

5R

IN

B/YINB Unfiltered analog R- or Y-channel

input for Bank <B>. Sync must be

provided at SYNC IN pin.

6G

IN

A/UINA Unfiltered analog G- or U-channel

input for Bank <A>. Sync must be

provided at SYNC IN pin.

7G

IN

B/UINB Unfiltered analog G- or U-channel

input for Bank <B>. Sync must be

provided at SYNC IN pin.

PIN NAME FUNCTION

8BINA/VINA Unfiltered analog B- or V-channel

input for Bank <A>. Sync must be

provided at SYNC IN pin.

9B

IN

B/VINB Unfiltered analog B- or V-channel

input for Bank <B>. Sync must be

provided at SYNC IN pin.

10 B

OUT

Analog B or V-channel output

11 G

OUT

Analog G or U-channel output

12 V

CCO

5V power supply for output buffers

13 R

OUT

Analog R or Y-channel output

14 GNDO Analog ground

15 DISABLE Disable/Enable pin. Turns the chip off

when logic high. Internally pulled low.

16 SYNC IN Input for an external H-sync logic

signal for filter channels. CMOS

level input. Active High.

ML6426

16-Pin Narrow SOIC (S16N)

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

TOP VIEW

A/B MUX

RINA/YINA

GND

V

CC

RINB/YINB

GINA/UINA

GINB/UINB

BINA/VINA

SYNC IN

DISABLE

GNDO

R

OUT/YOUT

V

CCO

G

OUT/UOUT

B

OUT/VOUT

BINB/VINB

ML6426

REV. 1.1 2/8/2001 3

ABSOLUTE MAXIMUM RATINGS

Absolute maximum ratings are those values beyond which

the device could be permanently damaged. Absolute

maximum ratings are stress ratings only and functional

device operation is not implied.

V

CC

................................................................................

–0.3V to 7V

Junction Temperature .............................................. 150°C

ESD ..................................................................... >2000V

Analog and Digital I/O........... GND –0.3V to V

CC

+ 0.3V

Storage Temperature Range ..................... –65°C to 150°C

Lead Temperature (Soldering, 10 sec) ..................... 260°C

Thermal Resistance (θ

JA

) .................................... 100°C/W

OPERATING CONDITIONS

Temperature Range ....................................... 0°C to 70°C

V

CC

Range ...................................................4.5V to 5.5V

ELECTRICAL CHARACTERISTICS

Unless otherwise specified, VCC = 5V±10%, TA = Operating Temperature Range (Note 1)

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

GENERAL

I

CC

Supply Current No Load (VCC=5.5V) 52 80 mA

A

V

Low Frequency Gain (R, G, B) VIN= 100mV

P-P

at 100KHz 5.34 6.0 6.65 dB

V

OUT

Output Level during Sync (R, G, B,) DURING SYNC 0.7 0.9 1.1 V

Output Capability RL = 150W, AC-coupled@1MHz 2 VP-P

t

CLAMP

Clamp Response Time Settled to Within 10mV, CIN = 0.1µF 10 ms

V

I

Input Signal Dynamic Range (R, G, B,) AC Coupled 1.4 V

P-P

OS Peak Overshoot (R, G, B,) 2V

P-P

Output Pulse 4.3 %

C

L

Output Load Capacitance (R, G, B,) All Outputs 35 pF

Output Load Drive Capability, per Pin One Load is 150Ω 2 loads

(YUV or RGB Outputs)

dG Differential Gain (R, G, B,) All Outputs at fC/2 0.4 %

dφ Differential Phase (R, G, B,) All Outputs at fC/2 0.4 º

T

HD

Output Distortion (R, G, B,) V

OUT

= 2V

P-P

at 1 MHz 0.8 %

PSRR PSRR (R, G, B,) 0.5V

P-P

(100kHz) at V

CC

35 dB

I

SC

Output Short Circuit Current (R, G, B,) Note 2 120 mA

V

IH

Input Voltage Logic High DISABLE, SYNC IN 2.5 V

V

IL

Input Voltage Logic Low DISABLE, SYNC IN 1.0 V

T

MUX

Input Mux A/B Mux 2 µs

Data Valid Pin Valid

Time High or Low

6.7MHz FILTER: ML6426-1

f

1dB

–1dB Bandwidth Flatness (R, G, B,) 25ºC 4.0 4.8 MHz

f

c

–3dB Bandwidth Flatness (R, G, B,) 25ºC 6.0 6.7 7.3 MHz

f

0.8fc

0.8 x fC Attenuation 1.5 dB

f

SB

StopBand Rejection (All Channels ≥ 4 fC)fIN ≥ 4 fC, Note 3 –38 –42 dB

NOISE Output Noise (R, G, B,) Fullband 1.0 mV

RMS

X

TALK

Crosstalk Input of 0.5V

P-P

at 1 MHz –55 dB

Between any two Channels

X

TALK

A/B MUX Crosstalk Input of 0.5V

P-P

at 3.58/4.43MHz –54 dB

ML6426

4 REV. 1.1 2/8/2001

ELECTRICAL CHARACTERISTICS (Continued)

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

6.7MHZ FILTER: ML6426-1 (continued)

T

PD

Group Delay (R, G, B,) 100kHz 70 ns

∆T

PD

Group Delay Deviation from Flatness to 3.58MHz 4.0 ns

(R, G, B,) to 4.43MHz 8.0 ns

to 10MHz 9 ns

2MHz FILTER: ML6426-2

f

1dB

–1dB Bandwidth Flatness (R, G, B,) 25ºC 7.8 9.2 MHz

f

c

–3dB Bandwidth Flatness (R, G, B,) 25ºC 10.8 12 13.2 MHz

f

0.8fc

0.8 x fC Attenuation 1.2 dB

f

SB

StopBand Rejection (All Channels ≥ 4 fC)fIN ≥ 4 fC, Note 3 –40 dB

NOISE Output Noise (R, G, B,) Fullband 1 mV

RMS

X

TALK

Crosstalk Input of 0.5V

P-P

at 1 MHz –55 dB

Between any two Channels

X

TALK

A/B MUX Crosstalk Input of 0.5V

P-P

at 3.58/4.43MHz –54 dB

T

PD

Group Delay (R, G, B,) 100kHz 40 ns

∆T

PD

Group Delay Deviation from Flatness to 3.58MHz 1 ns

(R, G, B,) to 4.43MHz 1 n s

to 10MHz 7 ns

24MHz FILTER: ML6426-3

f

1dB

–1dB Bandwidth Flatness (R, G, B,) 25ºC 13.6 16 MHz

f

c

–3dB Bandwidth Flatness (R, G, B,) 25ºC 21.6 24 26.4 MHz

f

0.8fc

0.8 x fC Attenuation 1.7 dB

f

SB

StopBand Rejection (All Channels ≥ 4 fC)fIN ≥ 4 fC, Note 3 – 40 dB

NOISE Output Noise (R, G, B,) Fullband 1.0 mV

RMS

X

TALK

Crosstalk Input of 0.5V

P-P

at 1 MHz –55 dB

Between any two Channels

X

TALK

A/B MUX Crosstalk Input of 0.5V

P-P

at 3.58/4.43MHz -54 dB

T

PD

Group Delay (R, G, B,) 100kHz 22 ns

∆T

PD

Group Delay Deviation from Flatness to 3.58MHz 1 ns

(R, G, B,) to 4.43MHz 1 n s

to 10MHz 2 ns

30MHz FILTER: ML6426-4

f

1dB

–1dB Bandwidth Flatness (R, G, B,) 25ºC 15.3 18 MHz

f

c

–3dB Bandwidth Flatness (R, G, B,) 25ºC 27 30 3 3 MHz

f

0.8fc

0.8 x fC Attenuation 1.7 dB

f

SB

StopBand Rejection (All Channels ≥ 4 fC)fIN ≥ 4 fC, Note 3 –40 dB

NOISE Output Noise (R, G, B,) Fullband 1.0 mV

RMS

ML6426

REV. 1.1 2/8/2001 5

Note 1. Limits are guaranteed by 100% testing, sampling, or correlation with worst case test conditions.

Note 2. Sustained short circuit protection limited to 10 seconds.

Note 3. 38dB is based on tester noise limits.

ELECTRICAL CHARACTERISTICS (Continued)

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

30MHz FILTER: ML6426-4 (Continued)

X

TALK

Crosstalk Input of 0.5V

P-P

at 1 MHz –55 dB

Between any two Channels

X

TALK

A/B MUX Crosstalk Input of 0.5V

P-P

at 3.58/4.43MHz -54 dB

T

PD

Group Delay (R, G, B,) 100kHz 18 ns

∆T

PD

Group Delay Deviation from Flatness to 10MHz 0.5 ns

(R, G, B,) to 27MHz 2 n s

36MHz FILTER: ML6426-5

f

1dB

–1dB Bandwidth Flatness (R, G, B,) 25ºC 17 20 MHz

f

c

–3dB Bandwidth Flatness (R, G, B,) 25ºC 32.4 36 39.6 MHz

f

0.8fc

0.8 x fC Attenuation 2dB

f

SB

StopBand Rejection (All Channels ≥ 4 fC)fIN ≥ 4 fC, Note 3 –40 dB

NOISE Output Noise (R, G, B,) Fullband 1.0 mV

RMS

X

TALK

Crosstalk Input of 0.5V

P-P

at 1 MHz –55 dB

Between any two Channels

X

TALK

A/B MUX Crosstalk Input of 0.5V

P-P

at 3.58/4.43MHz –54 dB

T

PD

Group Delay (R, G, B,) 100kHz 17 ns

∆T

PD

Group Delay Deviation from Flatness to 10MHz 0.5 ns

(R, G, B,) to 30MHz 4 n s

48MHz FILTER: ML6426-6

f

1dB

–1dB Bandwidth Flatness (R, G, B,) 25ºC 25.5 30 MHz

f

c

–3dB Bandwidth Flatness (R, G, B,) 25ºC 43.2 48 52.8 MHz

f

0.8fc

0.8 x fC Attenuation 1.2 dB

f

SB

StopBand Rejection (All Channels ≥ 4 fC)fIN ≥ 4 fC, Note 3 –40 dB

NOISE Output Noise (R, G, B,) Fullband 1.0 mV

RMS

X

TALK

Crosstalk Input of 0.5V

P-P

at 1 MHz –55 dB

Between any two Channels

X

TALK

A/B MUX Crosstalk Input of 0.5V

P-P

at 3.58/4.43MHz –54 dB

T

PD

Group Delay (R, G, B,) 100kHz 16 ns

∆T

PD

Group Delay Deviation from Flatness to 10MHz 0.5 ns

(R, G, B,) to 40MHz 2 n s

ML6426

6 REV. 1.1 2/8/2001

FUNCTIONAL DESCRIPTION

The ML6426 is a triple monolithic continuous time video

filter designed for reconstructing video signals from an

YUV/RGB video D/A source. The ML6426 is intended for

use in AC coupled input and output applications.

The filters approximate a 4th-order Butterworth

characteristic with an optimization toward low overshoot

and flat group delay. All outputs are capable of driving

2V

P-P

into AC coupled 150Ω video loads, with up to 35pF

of load capacitance. All outputs are capable of driving a

75Ω load at 1V

P-P

.

All channels are clamped during sync to establish the

appropriate output voltage swing range (DC restore). Thus

the input coupling capacitors do not behave according to

the conventional RC time constant. In most applications,

the ML6426's input coupling capacitors are only 0.1µF.

Figure 1. Typical Application Schematic

An external CMOS compatible H

SYNC

pulse is required

which is Active High on the SYNC IN Pin. See Figure 2.

During sync, the feedback clamp sources/sinks current to

restore the DC level. The net result is that the average

input current is zero. Any change in the input coupling

capacitors' value will linearly affect the clamp response

times.

Each channel is essentially tilt-free. Each input is

clamped by a feedback amp which responds to the output

during sync.

The ML6426 is robust and stable under all stated load and

input conditions. Bypassing both V

CC

pins directly to

ground ensures this performance.

R

IN

5V 5V

R

G

0.1µF

220µF

75Ω

G

IN

0.1µF

220µF

75Ω

B

220µF

75Ω

B

IN

SYNC IN

0.1µF

RINA/YINA

2

RINB/YINB

BINA/VINA

8

BINB/VINB

9

A/B MUX

GINA/UINA

6

GINB/UINB

7

R

OUT/YOUT

13

G

OUT/UOUT

11

B

OUT/VOUT

10

4th-ORDER

FILTER A

4th-ORDER

FILTER B

4th-ORDER

FILTER C

MUX

MUX

MUX

×2

×2

×2

TRANSCONDUCTANCE

ERROR AMP

TRANSCONDUCTANCE

ERROR AMP

TRANSCONDUCTANCE

ERROR AMP

1

SYNCIN

16

GNDO

14

DISABLE

15

V

CCO

12

V

CC

4

GND

3

5

+

–

+

–

+

–

0.5V

0.5V

0.5V

ACTIVE HIGH

Figure 2. SYNC IN Pulse Width

VIL = 1.0V

50% x V

SYNC IN

V

IH

= 2.5V

PW

MIN

= 2µS

Loading...

Loading...