Fairchild Semiconductor ML4824CS1 Datasheet

December 2000

ML4824

P ow er F actor Correction and PWM Contr oller Combo

GENERAL DESCRIPTION

The ML4824 is a controller for power factor corrected,

switched mode power supplies. Power Factor Correction

(PFC) allows the use of smaller, lower cost bulk capacitors,

reduces power line loading and stress on the switching

FETs, and results in a power supply that fully complies

with IEC1000-2-3 specification. The ML4824 includes

circuits for the implementation of a leading edge, average

current, “boost” type power factor correction and a trailing

edge, pulse width modulator (PWM).

The device is available in two versions; the ML4824-1

= f

(f

PWM

) and the ML4824-2 (f

PFC

PWM

= 2 x f

PFC

).

Doubling the switching frequency of the PWM allows the

user to design with smaller output components while

maintaining the best operating frequency for the PFC. An

over-voltage comparator shuts down the PFC section in the

event of a sudden decrease in load. The PFC section also

includes peak current limiting and input voltage brownout protection. The PWM section can be operated in

current or voltage mode at up to 250kHz and includes a

duty cycle limit to prevent transformer saturation.

BLOCK DIAGRAM

15

2

4

3

7

8

6

5

9

V

FB

2.5V

I

AC

V

RMS

I

SENSE

RAMP 1

RAMP 2

V

DC

V

SS

DC I

LIMIT

CC

VEA

–

+

8V

50µA

8V

16

VEAO

GAIN

MODULATOR

1.25V

3.5kΩ

IEA

+

–

3.5kΩ

–

+

1

IEAO

+

–

OSCILLATOR

(-2 VERSION ONLY)

–

+

POWER FACTOR CORRECTOR

x 2

V

–

FB

2.5V

+

PULSE WIDTH MODULATOR

FEATURES

■ Internally synchronized PFC and PWM in one IC

■ Low total harmonic distortion

■ Reduces ripple current in the storage capacitor between

the PFC and PWM sections

■ Average current, continuous boost leading edge PFC

■ Fast transconductance error amp for voltage loop

■ High efficiency trailing edge PWM can be configured

for current mode or voltage mode operation

■ Average line voltage compensation with brownout

control

■ PFC overvoltage comparator eliminates output

“runaway” due to load removal

■ Current fed gain modulator for improved noise immunity

■ Overvoltage protection, UVLO, and soft start

13

V

CC

7.5V

PFC OUT

PWM OUT

DUTY CYCLE

VIN OK

LIMIT

2.7V

–1V

1V

OVP

+

–

+

–

PFC I

–

+

LIMIT

DC I

LIMIT

V

CCZ

V

CCZ

13.5V

REFERENCE

SRQ

Q

SRQ

Q

SRQ

Q

UVLO

V

REF

14

12

11

REV. 1.01 12/7/2000

ML4824

PIN CONFIGURATION

PIN DESCRIPTION

ML4824

16-Pin PDIP (P16)

16-Pin Wide SOIC (S16W)

IEAO

I

AC

I

SENSE

V

RMS

V

DC

RAMP 1

RAMP 2

SS

1

2

3

4

5

6

7

8

TOP VIEW

16

VEAO

15

V

FB

14

V

REF

13

V

CC

12

PFC OUT

11

PWM OUT

10

GND

9

DC I

LIMIT

PIN NAME FUNCTION

1 IEAO PFC transconductance current error

amplifier output

2I

AC

3I

SENSE

PFC gain control reference input

Current sense input to the PFC current

limit comparator

4V

RMS

Input for PFC RMS line voltage

compensation

5 SS Connection point for the PWM soft start

capacitor

6V

DC

PWM voltage feedback input

7 RAMP 1 Oscillator timing node; timing set

by R

TCT

8 RAMP 2 When in current mode, this pin

functions as as the current sense input;

when in voltage mode, it is the PWM

input from PFC output (feed forward

ramp).

PIN NAME FUNCTION

9 DC I

LIMIT

PWM current limit comparator input

10 GND Ground

11 PWM OUT PWM driver output

12 PFC OUT PFC driver output

13 V

CC

Positive supply (connected to an

internal shunt regulator)

14 V

REF

Buffered output for the internal 7.5V

reference

15 V

FB

PFC transconductance voltage error

amplifier input

16 VEAO PFC transconductance voltage error

amplifier output

2 REV. 1.01 12/7/2000

ABSOLUTE MAXIMUM RATINGS

ML4824

Absolute maximum ratings are those values beyond which

the device could be permanently damaged. Absolute

maximum ratings are stress ratings only and functional

device operation is not implied.

Junction Temperature.............................................. 150°C

Storage Temperature Range ..................... –65°C to 150°C

Lead Temperature (Soldering, 10 sec) ..................... 260°C

Thermal Resistance (θ

)

JA

Plastic DIP ....................................................... 80°C/W

V

Shunt Regulator Current .................................. 55mA

CC

Voltage.................................................. –3V to 5V

I

SENSE

Voltage on Any Other Pin ... GND – 0.3V to V

............................................................................................

I

REF

I

Input Current .................................................... 10mA

AC

CCZ

+ 0.3V

20mA

Peak PFC OUT Current, Source or Sink ................ 500mA

Peak PWM OUT Current, Source or Sink .............. 500mA

PFC OUT, PWM OUT Energy Per Cycle .................. 1.5µJ

Plastic SOIC ................................................... 105°C/W

OPERATING CONDITIONS

Temperature Range

ML4824CX................................................. 0°C to 70°C

ML4824IX .............................................. –40°C to 85°C

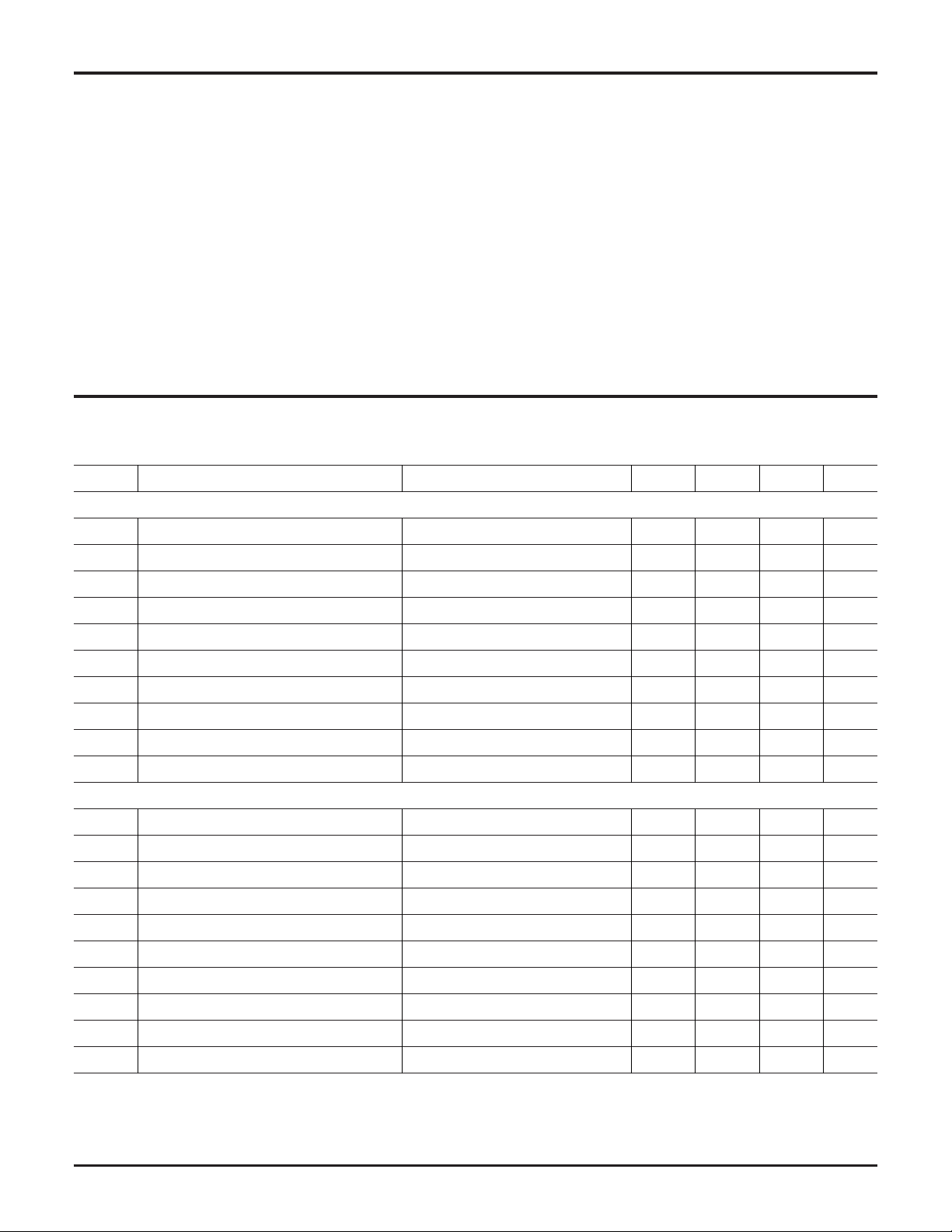

ELECTRICAL CHARACTERISTICS

Unless otherwise specified, ICC = 25mA, R

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

VOLTAGE ERROR AMPLIFIER

Input Voltage Range 0 7 V

Transconductance V

Feedback Reference Voltage 2.46 2.53 2.60 V

= 52.3kΩ, C

T

= 470pF, TA = Operating Temperature Range (Note 1)

T

= V

NON INV

, VEAO = 3.75V 50 85 120 µ

INV

Ω

Input Bias Current Note 2 -0.3 –1.0 µA

Output High Voltage 6.0 6.7 V

Output Low Voltage 0.6 1.0 V

Source Current ∆VIN = ±0.5V, V

Sink Current ∆VIN = ±0.5V, V

Open Loop Gain 60 75 dB

Power Supply Rejection Ratio V

CURRENT ERROR AMPLIFIER

Input Voltage Range –1.5 2 V

Transconductance V

Input Offset Voltage 0 8 15 mV

Input Bias Current –0.5 –1.0 µA

Output High Voltage 6.0 6.7 V

Output Low Voltage 0.6 1.0 V

Source Current ∆VIN = ±0.5V, V

Sink Current ∆VIN = ±0.5V, V

Open Loop Gain 60 75 dB

Power Supply Rejection Ratio V

- 3V < VCC < V

CCZ

NON INV

CCZ

= V

- 3V < VCC < V

= 6V –40 –80 µA

OUT

= 1.5V 40 80 µA

OUT

- 0.5V 60 75 dB

CCZ

, VEAO = 3.75V 130 195 310 µ

INV

= 6V –40 –90 µA

OUT

= 1.5V 40 90 µA

OUT

- 0.5V 60 75 dB

CCZ

Ω

REV. 1.01 12/7/2000 3

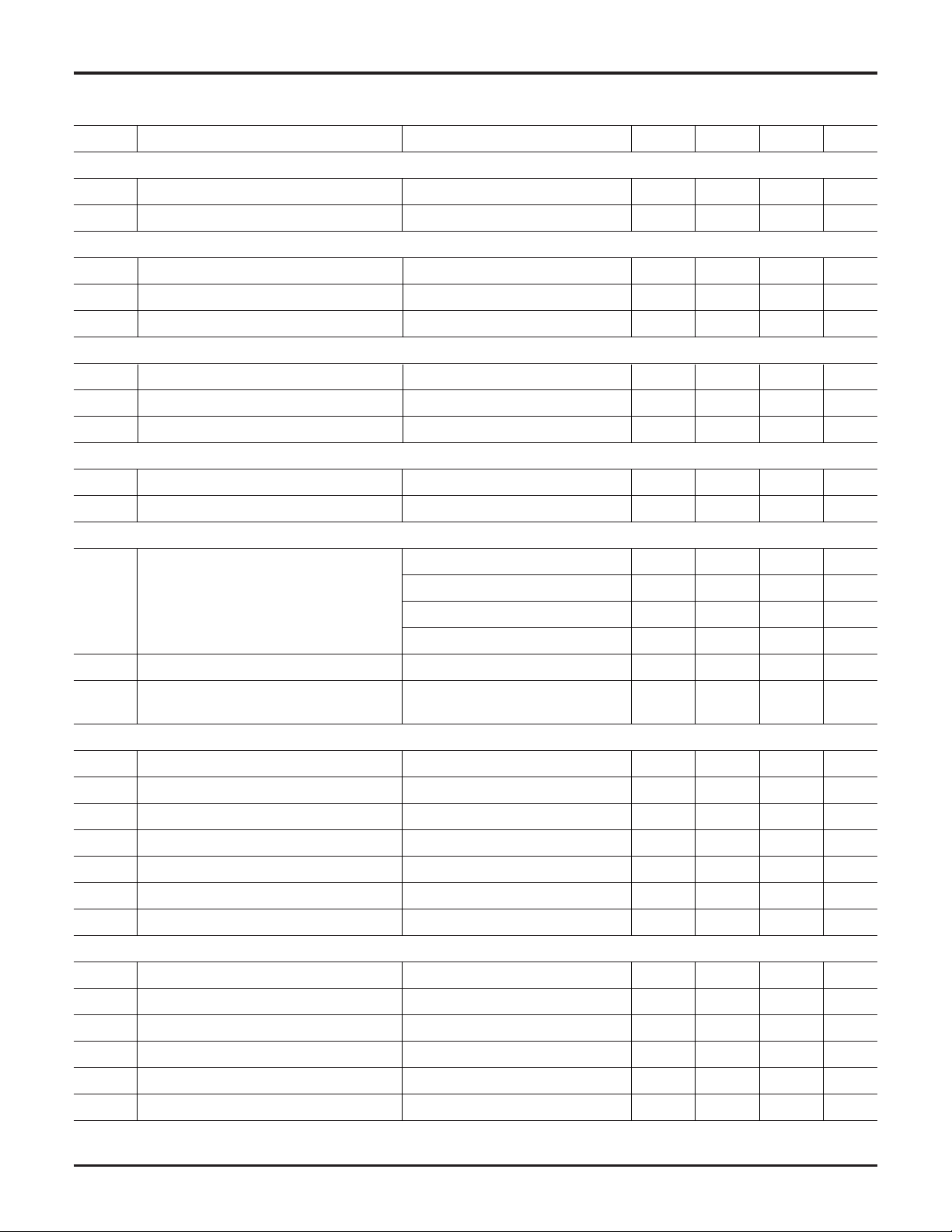

ML4824

ELECTRICAL CHARACTERISTICS (Continued)

SMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

OVP COMPARATOR

Threshold Voltage 2.6 2.7 2.8 V

Hysteresis 80 115 150 mV

PFC I

COMPARATOR

LIMIT

Threshold Voltage –0.8 –1.0 –1.15 V

∆(PFC I

LIMIT VTH

Delay to Output 150 300 ns

DC I

COMPARATOR

LIMIT

Threshold Voltage 0.97 1.02 1.07 V

Input Bias Current ±0.3 ±1 µA

Delay to Output 150 300 ns

VIN OK COMPARATOR

Threshold Voltage 2.4 2.5 2.6 V

Hysteresis 0.8 1.0 1.2 V

GAIN MODULATOR

Gain (Note 3) IAC = 100µA, V

Bandwidth IAC = 100µA 10 MHz

Output Voltage I

OSCILLATOR

- Gain Modulator Output) 100 190 mV

= VFB = 0V 0.36 0.55 0.66

RMS

IAC = 50µA, V

IAC = 50µA, V

IAC = 100µA, V

= 250µA, V

AC

= 1.2V, VFB = 0V 1.20 1.80 2.24

RMS

= 1.8V, VFB = 0V 0.55 0.80 1.01

RMS

= 3.3V, VFB = 0V 0.14 0.20 0.26

RMS

= 1.15V, 0.74 0.82 0.90 V

RMS

VFB = 0V

Initial Accuracy TA = 25°C 71 76 81 kHz

Voltage Stability V

- 3V < VCC < V

CCZ

- 0.5V 1 %

CCZ

Temperature Stability 2%

Total Variation Line, Temp 68 84 kHz

Ramp Valley to Peak Voltage 2.5 V

Dead Time PFC Only 270 370 470 ns

CT Discharge Current V

RAMP 2

= 0V, V

= 2.5V 4.5 7.5 9.5 mA

RAMP 1

REFERENCE

Output Voltage TA = 25°C, I(V

Line Regulation V

- 3V < VCC < V

CCZ

Load Regulation 1mA < I(V

) = 1mA 7.4 7.5 7.6 V

REF

- 0.5V 2 10 mV

CCZ

) < 20mA 2 15 mV

REF

Temperature Stability 0.4 %

Total Variation Line, Load, Temp 7.35 7.65 V

Long Term Stability TJ = 125°C, 1000 Hours 5 25 mV

4 REV. 1.01 12/7/2000

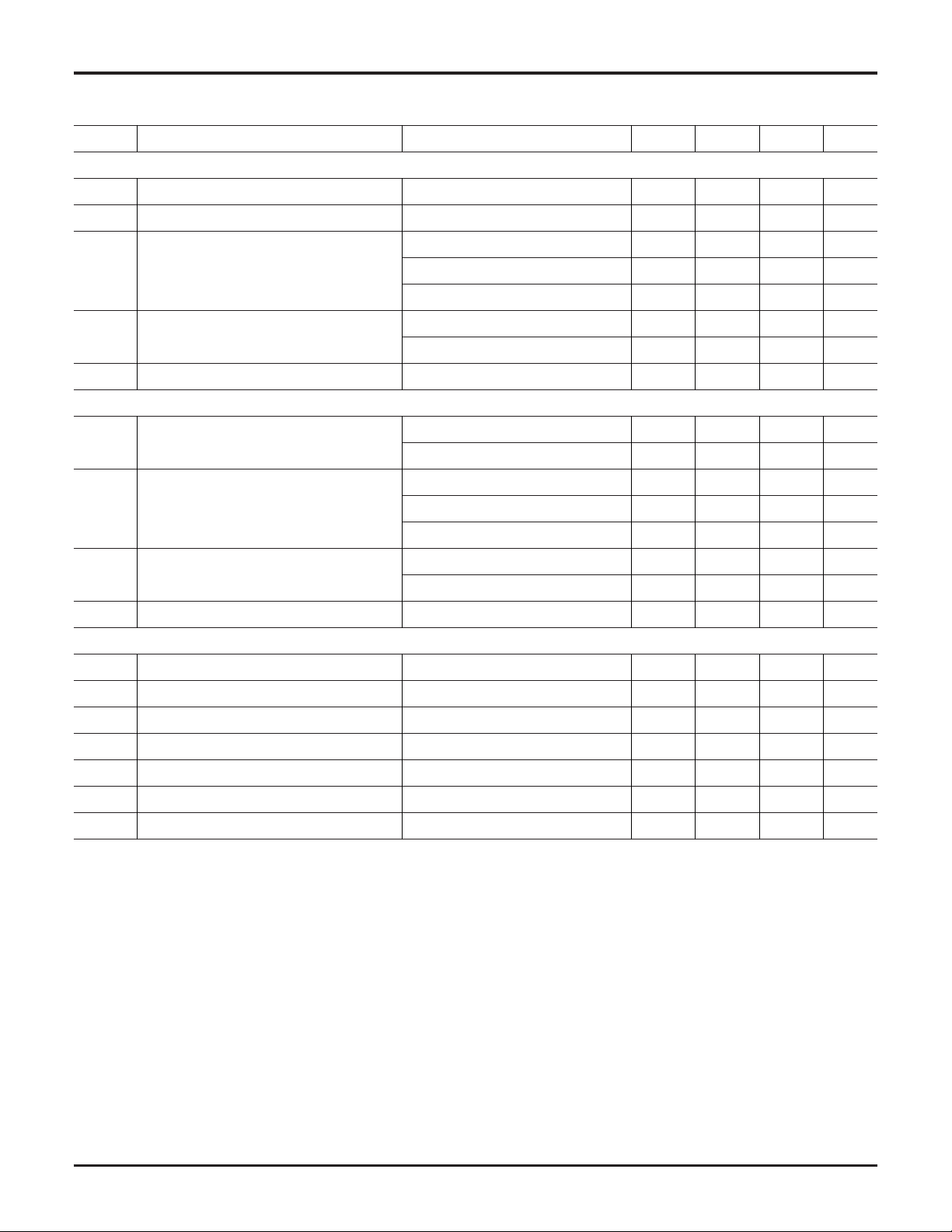

ML4824

ELECTRICAL CHARACTERISTICS (Continued)

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

PFC

PWM

SUPPLY

Minimum Duty Cycle V

Maximum Duty Cycle V

Output Low Voltage I

Output High Voltage I

> 4.0V 0 %

IEAO

< 1.2V 90 95 %

IEAO

= -20mA 0.4 0.8 V

OUT

I

= -100mA 0.8 2.0 V

OUT

I

= 10mA, VCC = 8V 0.7 1.5 V

OUT

= 20mA 10 10.5 V

OUT

I

= 100mA 9.5 10 V

OUT

Rise/Fall Time CL = 1000pF 50 ns

Duty Cycle Range ML4824-1 0-44 0-47 0-50 %

ML4824-2 0-37 0-40 0-45 %

Output Low Voltage I

Output High Voltage I

= -20mA 0.4 0.8 V

OUT

I

= -100mA 0.8 2.0 V

OUT

I

= 10mA, VCC = 8V 0.7 1.5 V

OUT

= 20mA 10 10.5 V

OUT

I

= 100mA 9.5 10 V

OUT

Rise/Fall Time CL = 1000pF 50 ns

Shunt Regulator Voltage (V

V

Load Regulation 25mA < ICC < 55mA ±100 ±300 mV

CCZ

V

Total Variation Load, Temp 12.4 14.6 V

CCZ

) 12.8 13.5 14.2 V

CCZ

Start-up Current VCC = 11.8V, CL = 0 0.7 1.0 mA

Operating Current VCC < V

- 0.5V, CL = 0 16 19 mA

CCZ

Undervoltage Lockout Threshold 12 13 14 V

Undervoltage Lockout Hysteresis 2.7 3.0 3.3 V

Note 1: Limits are guaranteed by 100% testing, sampling, or correlation with worst-case test conditions.

Note 2: Includes all bias currents to other circuits connected to the V

Note 3: Gain = K x 5.3V; K = (I

GAINMOD

- I

) x IAC x (VEAO - 1.5V)-1.

OFFSET

pin.

FB

REV. 1.01 12/7/2000 5

Loading...

Loading...