May 1997

ML4819

Power Factor and PWM Controller “Combo”

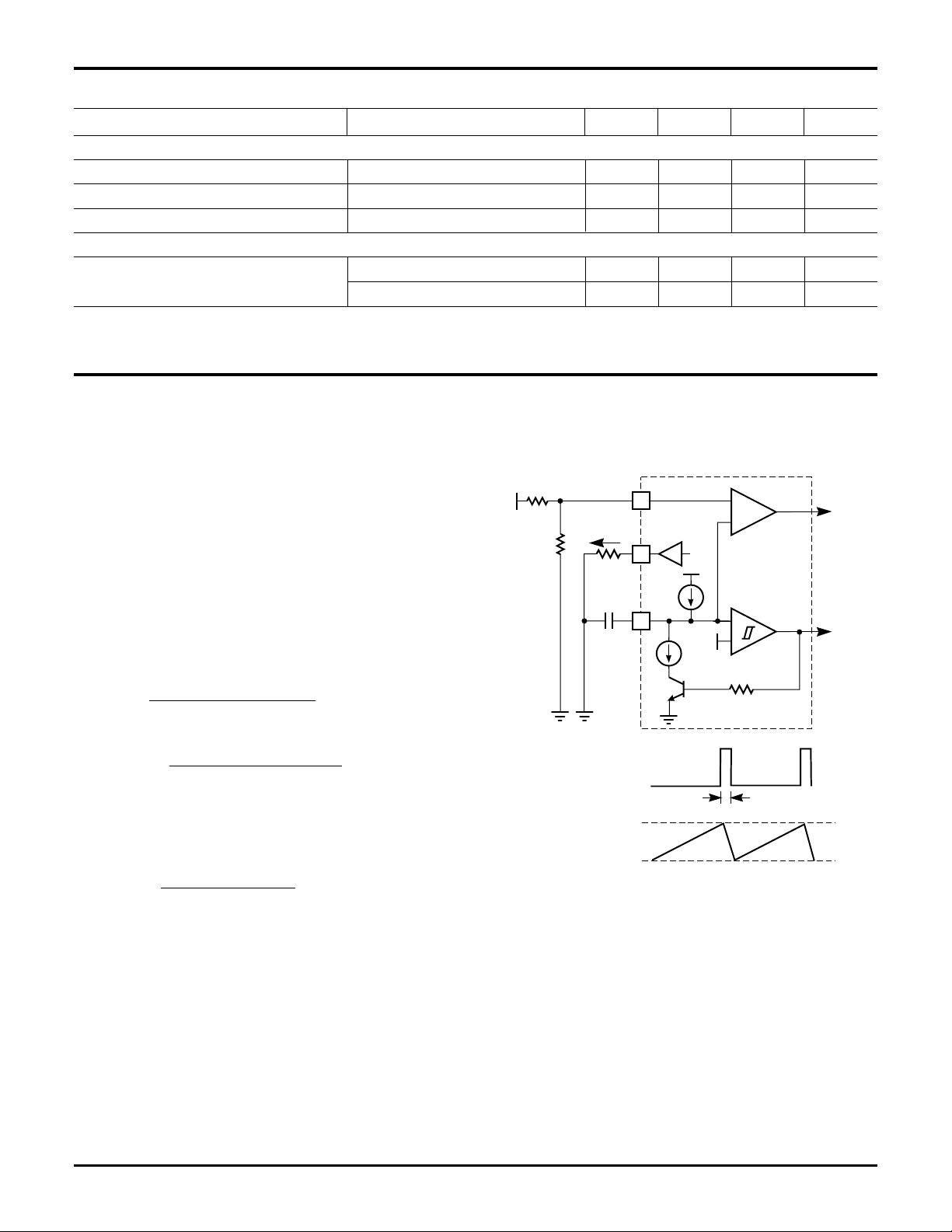

GENERAL DESCRIPTION

The ML4819 is a complete boost mode Power factor

Controller (PFC) which also contains a PWM controller.

The PFC circuit is similar to the ML4812 while the PWM

controller can be used for current or voltage mode control

for a second stage converter. Since the PWM and PFC

circuits share the same oscillator, synchronization of the

two stages is inherent. The outputs of the controller IC

provide high current (>1A peak) and high slew rate to

quickly charge and discharge MOSFET gates. Special care

has been taken in the design of the ML4819 to increase

system noise immunity.

The PFC section is of the peak current sensing boost type,

using a current sense transformer or current sensing

MOSFETs to non-dissipatively sense switch current. This

gives the system overall efficiency over average current

sensing control method.

The PWM section includes cycle by cycle current limiting,

precise duty cycle limiting for single ended converters,

and slope compensation.

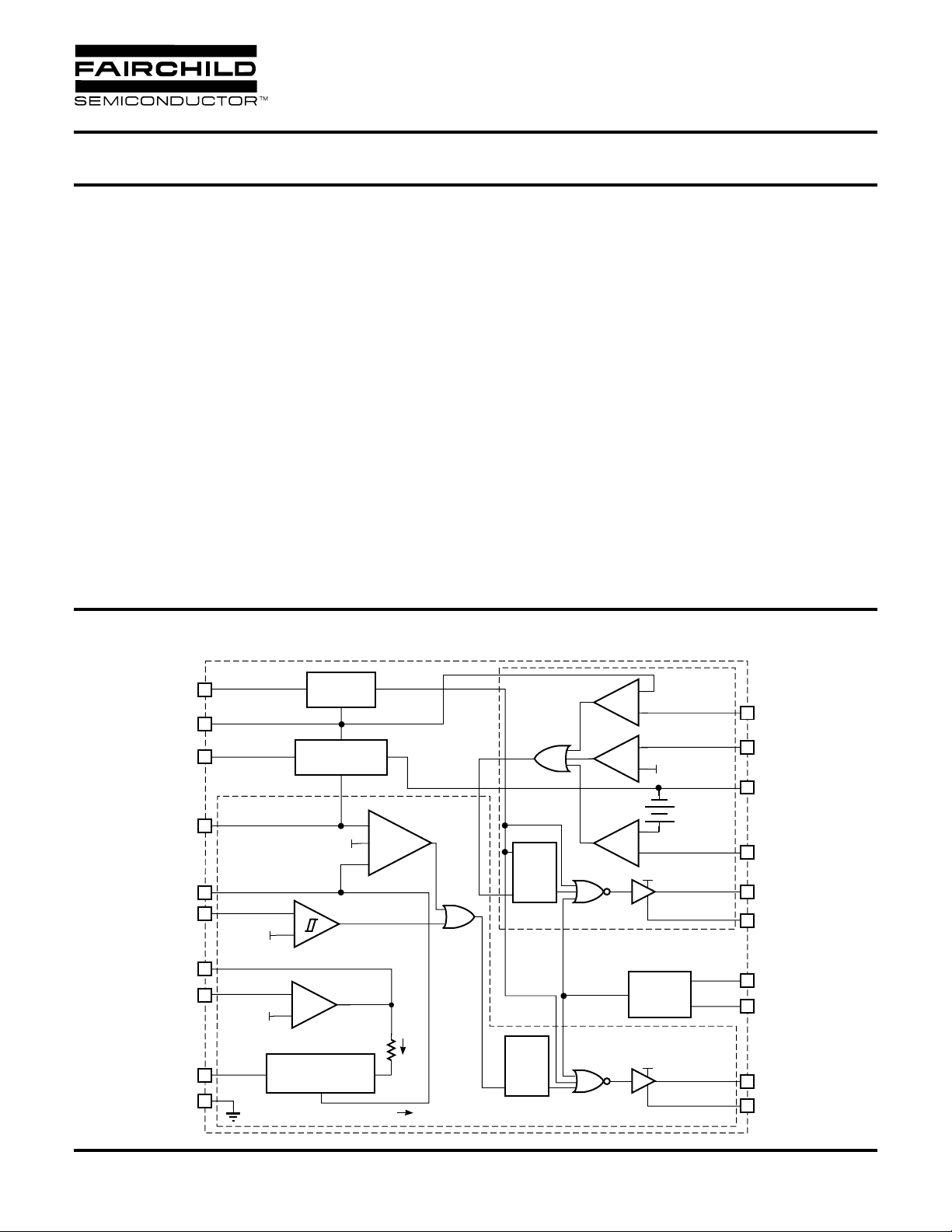

BLOCK DIAGRAM

FEATURES

■ Two 1A peak current totem-pole output drivers

■ Precision buffered 5V reference (±1%)

■ Large oscillator amplitude for better noise immunity

■ Precision duty cycle limit for PWM section

■ Current input gain modulator improves noise immunity

■ Programmable Ramp Compensation circuit

■ Over-Voltage comparator helps prevent output

“runaway”

■ Wide common mode range in current sense

compensators for better noise immunity

■ Under-Voltage Lockout circuit with 6V hysteresis

R

T

10

C

T

20

RAMP COMP

12

I

A

SENSE

1

GM OUT

3

OVP

2

5V

EA OUT A

4

INV A

5

5V

I

SINE

6

GND

Please See Ml4824 for New Designs

19

GAIN MODULATOR

OSC

SLOPE

COMPENSATION

5V

+

–

+

–

ERROR

AMP

I

POWER FACTOR

CONTROLLER

+

–

–

I

EA

MULT

PWM

CONTROLLER

R

Q

S

R

Q

S

–

+

DUTY CYCLE

–

+

1V

–

+

V

CC

UNDER

VOLTAGE

LOCKOUT

V

CC

I

SENSE

0.7V

PWM B

OUT B

PGND B

OUT A

PGND A

7

I

LIM

11

B

9

8

14

13

V

REF

18

V

CC

15

16

17

REV. 1.0 10/10/2000

ML4819

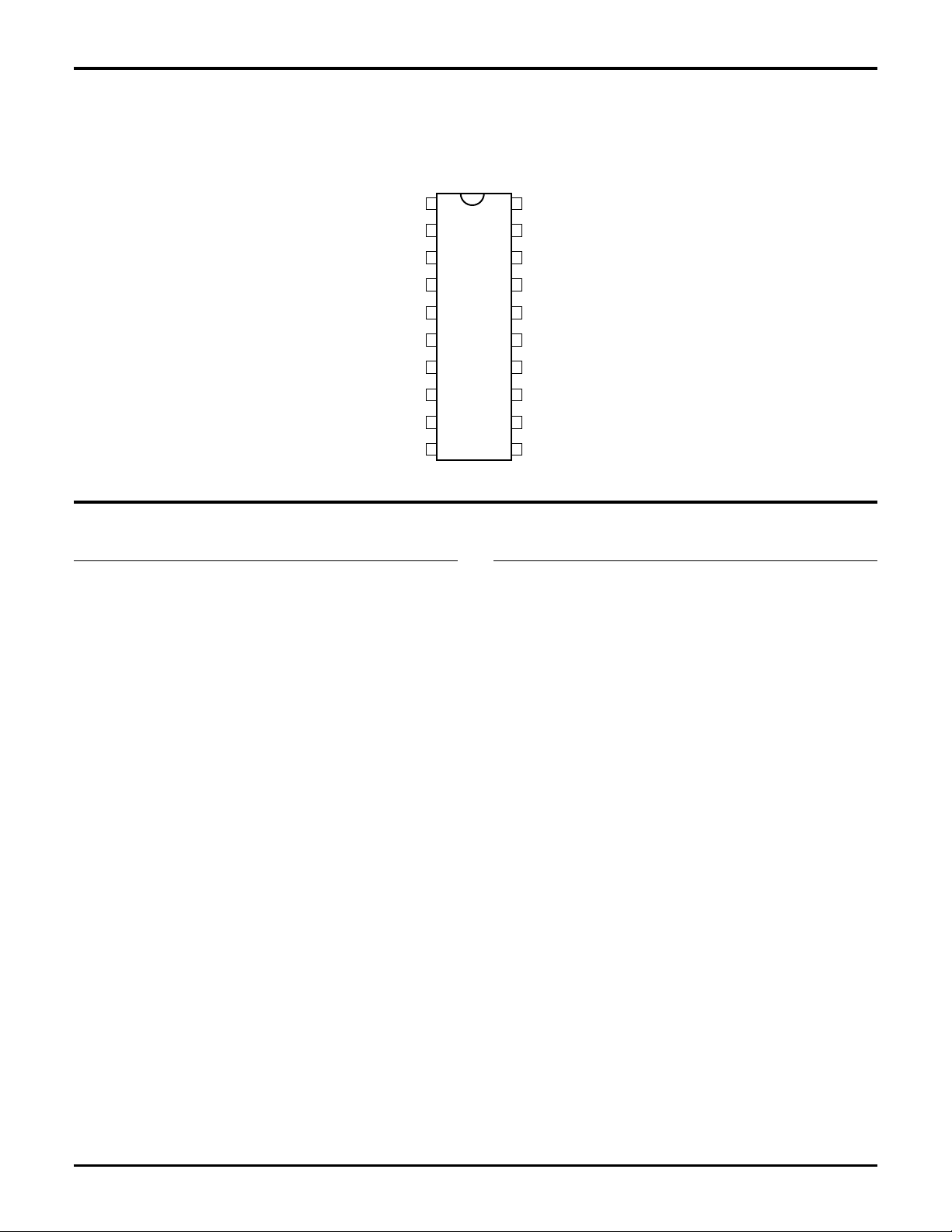

PIN CONFIGURATION

I

SENSE

A

OVP

ML4819

20-Pin PDIP

1

2

20

19

C

T

GND

GM OUT

EA OUT A

INV A

I

SINE

DUTY CYCLE

PWM B

I

SENSE

3

4

5

6

7

8

B

9

R

10

T

TOP VIEW

18

17

16

15

14

13

12

11

V

REF

PGND A

OUT A

V

CC

OUT B

PGND B

RAMP COMP

I

LIM

PIN DESCRIPTION

PIN NAME FUNCTION PIN NAME FUNCTION

1 I

2 OVP Input to Over-Voltage comparator.

3 GM OUT Output of Gain Modulator. A resistor

4 EA OUT A Output of error amplifier.

5 INV A Inverting input to error amplifier.

6I

7 DUTY CYCLE PWM controller duty cycle is limited

8 PWM B Error voltage feedback input.

9I

10 R

A Input form the PFC current sense

SENSE

transformer to the PWM comparator

(+). Current Limit occurs when this

point reaches 5V.

to ground on this pin converts the

current to a voltage.

SINE

Current Multiplier input.

by setting this pin to a fixed voltage.

B Input for Current Sense resistor for

SENSE

current mode operation or for

Oscillator ramp for voltage mode

operation.

T

Oscillator timing resistor pin. A 5V

source across this resistor sets the

charging current for C

11 I

LIM

Cycle by cycle PWM current limit.

Exceeding 1V threshold on this pin

terminates the PWM cycle.

12 RAMP COMP Buffered output from the Oscillator

Ramp (C

T

current, 1/2 of which is sourced on

pins 9 and 11.

13 GND B Return for the high current totem pole

output of the PWM controller.

14 OUT B PWM controller totem pole output.

15 V

CC

Positive Supply for the IC.

16 OUT A PFC controller totem pole output.

17 GND A Return for the high current totem pole

output of the PFC controller.

18 V

REF

Buffered output for the 5V voltage

reference

19 GND Analog signal ground.

20 C

T

T

Timing Capacitor for the Oscillator.

). A resistor to ground sets a

2 REV. 1.0 10/10/2000

ABSOLUTE MAXIMUM RATINGS

ML4819

Absolute maximum ratings are those values beyond which

the device could be permanently damaged. Absolute

maximum ratings are stress ratings only and functional

device operation is not implied.

Analog Inputs (ISENSE A, EA OUT A, INV A)

............................................................... –0.3V to 5.5V

Junction Temperature ............................................. 150°C

Storage Temperature Range ..................... –65°C to 150°C

Lead Temperature (soldering 10 sec.) ..................... 260°C

Supply Voltage (V

) ................................................. 35V

CC

Output Current, Source or Sink (RAMP COMP)

Thermal Resistance (θ

)

JA

Plastic DIP or SOIC ......................................... 60°C/W

DC ....................................................................... 1.0A

Output Energy (capacitive load per cycle) ...................5µJ

Multiplier I

SINE

Input (I

) ................................... 1.2mA

SINE

Error Amp Sink Current (GM OUT) ........................ 10mA

Oscillator Charge Current ........................................ 2mA

OPERATING CONDITIONS

Temperature Range

ML4819C .................................................. 0°C to 70°C

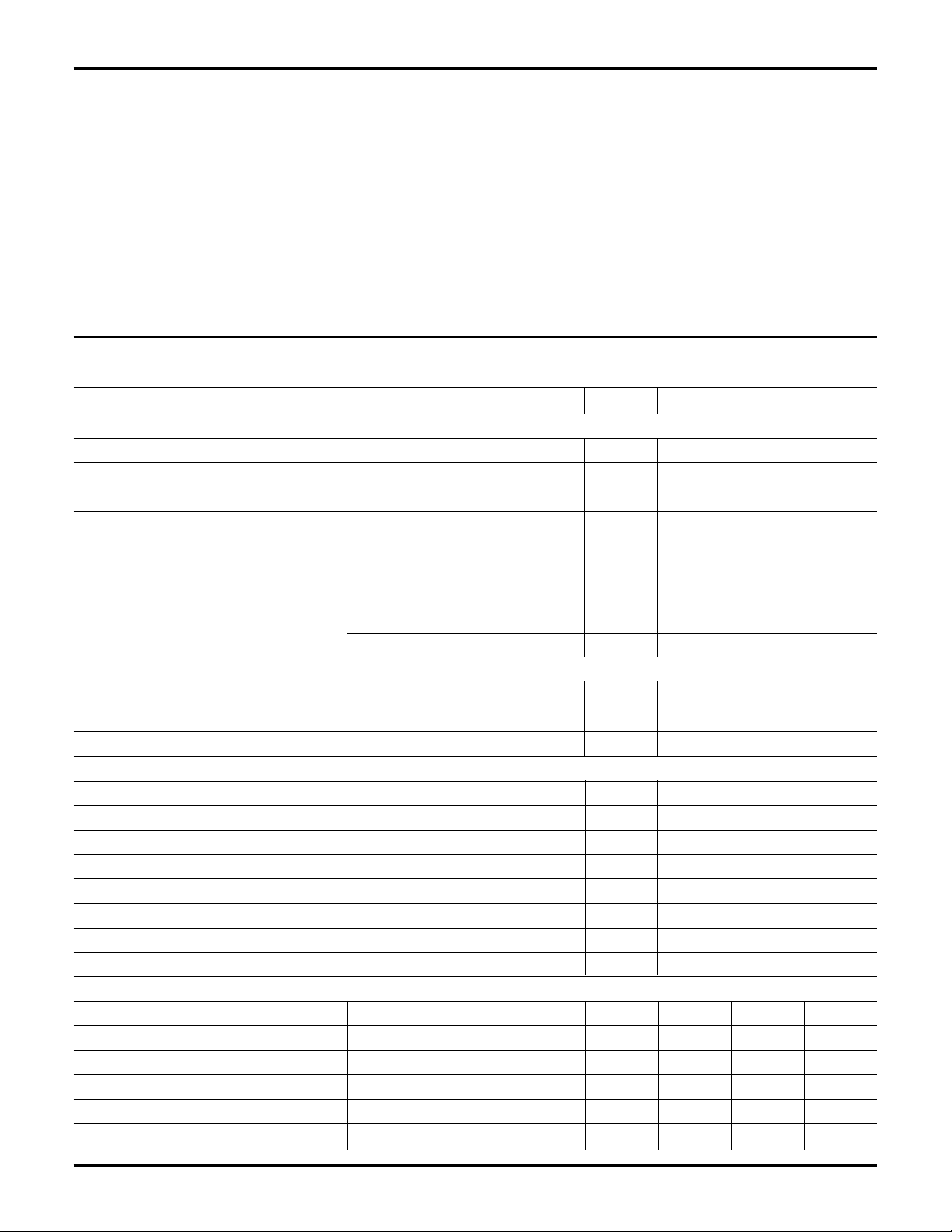

ELECTRICAL CHARACTERISTICS

Unless otherwise specified, RT = 14kΩ, CT = 1000pF, TA = Operating Temperature Range, VCC = 15V (Notes 1, 2).

PARAMETER CONDITIONS MIN TYP MAX UNITS

OSCILLATOR

Initial Accuracy TJ = 25°C 90 97 104 kHz

Voltage Stability 12V < VCC < 18V 0.2 %

Temperature Stability 2%

Total Variation Line, temp. 88 106 kHz

Ramp Valley 0.9 V

Ramp Peak 4.3 V

RT Voltage 4.8 5.0 5.2 V

Discharge Current (PWM B open) TJ = 25°C, V

V

= 2V 7.2 8.4 9.5 mA

OUT A

DUTY CYCLE LIMIT COMPARATOR

Input Offset Voltage –15 15 mV

Input Bias Current –2 –10 µA

Duty Cycle V

REFERENCE

Output Voltage TJ = 25°C, IO = 1mA 4.95 5.00 5.05 V

Line Regulation 12V < VCC < 25V 2 20 mV

Load Regulation 1mA < IO < 20mA 8 25 mV

Temperature Stability 0.4 %

Total Variation Line, load, temperature 4.9 5.1 V

Output Noise Voltage 10Hz to 10kHz 50 µV

Long Term Stability TJ = 125°C, 1000 hours, (Note 1) 5 25 mV

Short Circuit Current V

ERROR AMPLIFIER

Input Offset Voltage –15 15 mV

Input Bias Current –0.1 –1.0 µA

Open Loop Gain 1 < V

PSRR 12V < VCC < 25V 60 90 dB

Output Sink Current V

Output Source Current V

DUTY CYCLE

= 0V –30 –85 –180 mA

REF

EA OUT A

EA OUT A

EA OUT A

= 1.1V, V

= 5.0V, V

= 2V 7.5 8.4 9.3 mA

OUT A

= V

REF/2

< 5V 60 75 dB

= 5.2V 2 12 mA

INV A

= 4.8V –0.5 –1.0 mA

INV A

43 45 49 %

REV. 1.0 10/10/2000 3

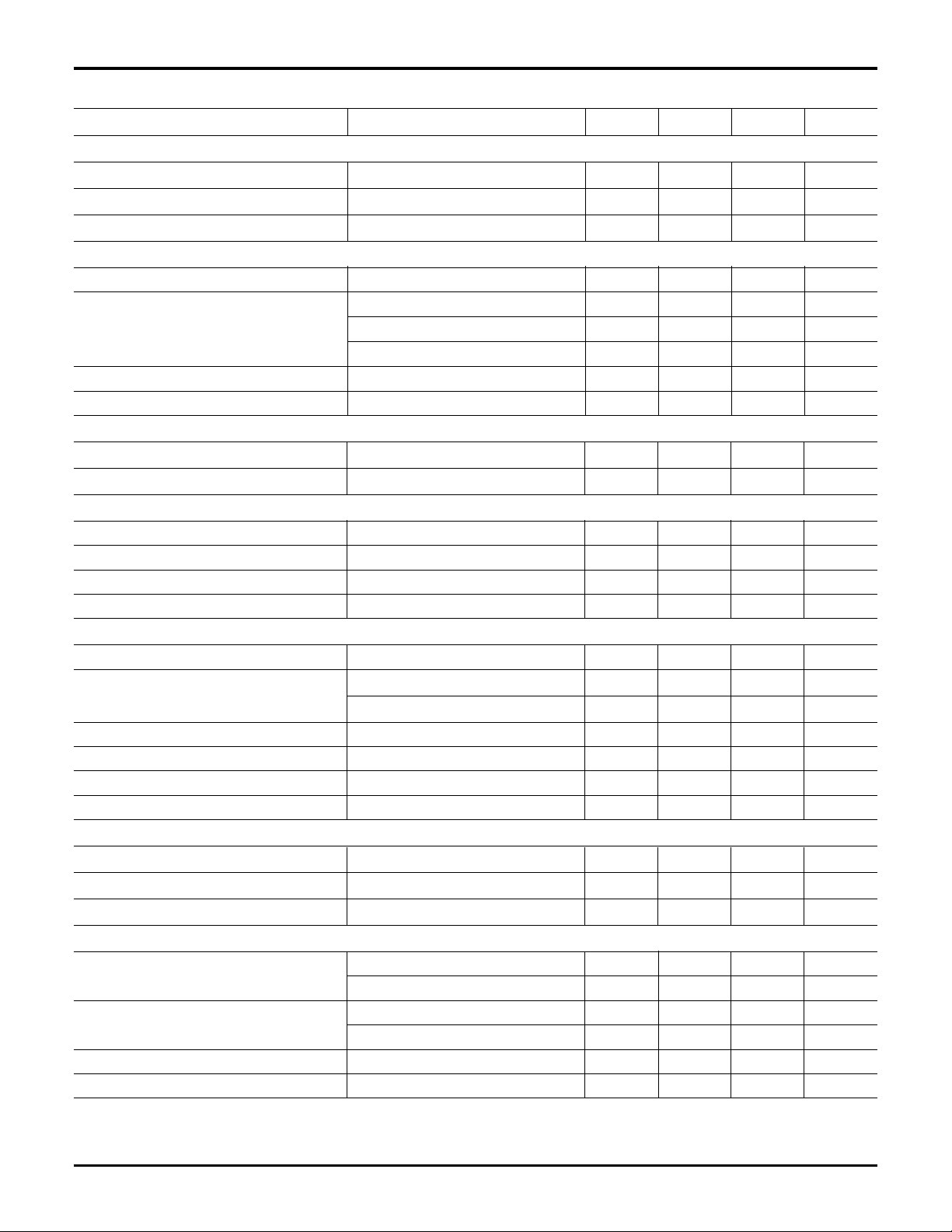

ML4819

ELECTRICAL CHARACTERISTICS (Continued)

PARAMETER CONDITIONS MIN TYP MAX UNITS

ERROR AMPLIFIER (continued)

Output High voltage I

Output Low Voltage I

EA OUT A

EA OUT A

= –0.5mA, V

= 2mA, V

INV A

= 4.8V 6.5 7.0 V

INV A

= 5.2V 0.7 1.0 V

Unity Gain Bandwidth 1.0 MHz

GAIN MODULATOR

I

Input Voltage I

SINE

Output Current (GM OUT) I

= 500µA 0.4 0.7 0.9 V

SINE

= 500µA, INV A = V

SINE

I

= 500µA, INV A = V

SINE

I

= 1mA, INV A = V

SINE

–20mV 460 495 505 µA

REF

+ 20mV 0 10 µA

REF

– 20mV 900 990 1005 µA

REF

Bandwidth 200 kHz

PSRR 12V < VCC < 25V 70 dB

SLOPE COMPENSATION CIRCUIT

RAMP COMP Voltage V

I

(I

OUT

SENSE

A or I

B) I

SENSE

RAMP COMP

= 100µA (Note 3) 45 48 51 µA

– 1 V

C(T)

OVP COMPARATOR

Input Offset Voltage Output Off –15 15 mV

Hysteresis Output On 100 120 140 mV

Input Bias Current –0.3 –3 µA

Propagation Delay 150 ns

I

COMPARATORS

SENSE

Input Common Mode Range –0.2 5.5 V

Input Offset Voltage I

A –15 15 mV

SENSE

I

B 0.4 0.7 0.9 V

SENSE

Input Bias Current –3 –10 µA

Input Offset Current –3 0 3 µA

Propagation Delay 150 ns

I

(A) Trip Point V

LIMIT

I

COMPARATOR

LIM

I

Trip Point .95 1.0 1.05 V

LIMIT

= 5.5V 4.8 5 5.2 V

OVP

Input Bias Current –2 –10 µA

Propagation Delay 150 ns

OUTPUT DRIVERS

Output Voltage Low I

Output Voltage High I

Output Voltage Low in UVLO I

= –20mA 0.1 0.4 V

OUT

I

= –200mA 1.6 2.2 V

OUT

= 20mA 13 13.5 V

OUT

I

= 200mA 12 13.4 V

OUT

= –1mA, VCC = 8V 0.1 0.8 V

OUT

Output Rise/Fall Time CL = 1000pF 50 ns

4 REV. 1.0 10/10/2000

ML4819

ELECTRICAL CHARACTERISTICS (Continued)

PARAMETER CONDITIONS MIN TYP MAX UNITS

UNDER-VOLTAGE LOCKOUT

Start-Up Threshold 15 16 17 V

Shut-Down Threshold 9 10 11 V

V

Good Threshold 4.4 V

REF

SUPPLY

Supply Current Start-Up, VCC = 14V 0.6 1.2 mA

Operating, TJ = 25°C2535mA

Note 1: Limits are guaranteed by 100% testing, sampling, or correlation with worst-case test conditions.

Note 2: V

Note 3: PWM comparator bias currents are subtracted from this reading.

is raised above the Start-Up Threshold first to activate the IC, then returned to 15V.

CC

FUNCTIONAL DESCRIPTION

OSCILLATOR

ramp

T

)

T

+5V

The ML4819 oscillator charges the external capacitor (C

with a current (I

) equal to 5/R

SET

. When the capacitor

SET

voltage reaches the upper threshold, the comparator

changes state and the capacitor discharges to the lower

threshold through Q1. While the capacitor is discharging,

the clock provides a high pulse.

The oscillator period can be described by the following

relationship:

t

OSC

= t

RAMP

+ t

DEADTIME

where:

t=

C(Ramp Valley to Peak)

RAMP

I

SET

and:

t

DEADTIME

C(Ramp Valley to Peak)

=

8.4mA - I

SET

The maximum duty cycle of the PWM section can be

limited by setting a threshold on pin 7. when the C

is above the threshold at pin 7, the PWM output is held

off and the PWM flip-flop is set:

D (V -0.9)

×

D

LIMIT

OSC PIN7

≅

3.4

where:

= Desired duty cycle limit

D

LIMIT

= Oscillator duty cycle

D

OSC

DUTY CYCLE

RAMP PEAK

RAMP VALLEY

I

SET

R

T

C

T

CLOCK

7

5V

10

I

SET

20

8.4mA

Q1

t

C

T

+

–

V

REF

CLOCK

+

–

D

Figure 1. Oscillator Block Diagram

TO PWM

LATCH B

TO PWM

LATCHES

REV. 1.0 10/10/2000 5

Loading...

Loading...