Fairchild Semiconductor ML4812CQ Datasheet

www.fairchildsemi.com

ML4812

Power Factor Controller

Features

• Precision buffered 5V reference (±0.5%)

• Current-input gain modulator reduces external

components and improves noise immunity

• Programmable ramp compensation circuit

• 1A peak current totem-pole output drive

• Overvoltage comparator helps prevent output voltage

“runaway”

• Wide common mode range in current sense comparators

for better noise immunity

• Large oscillator amplitude for better noise immunity

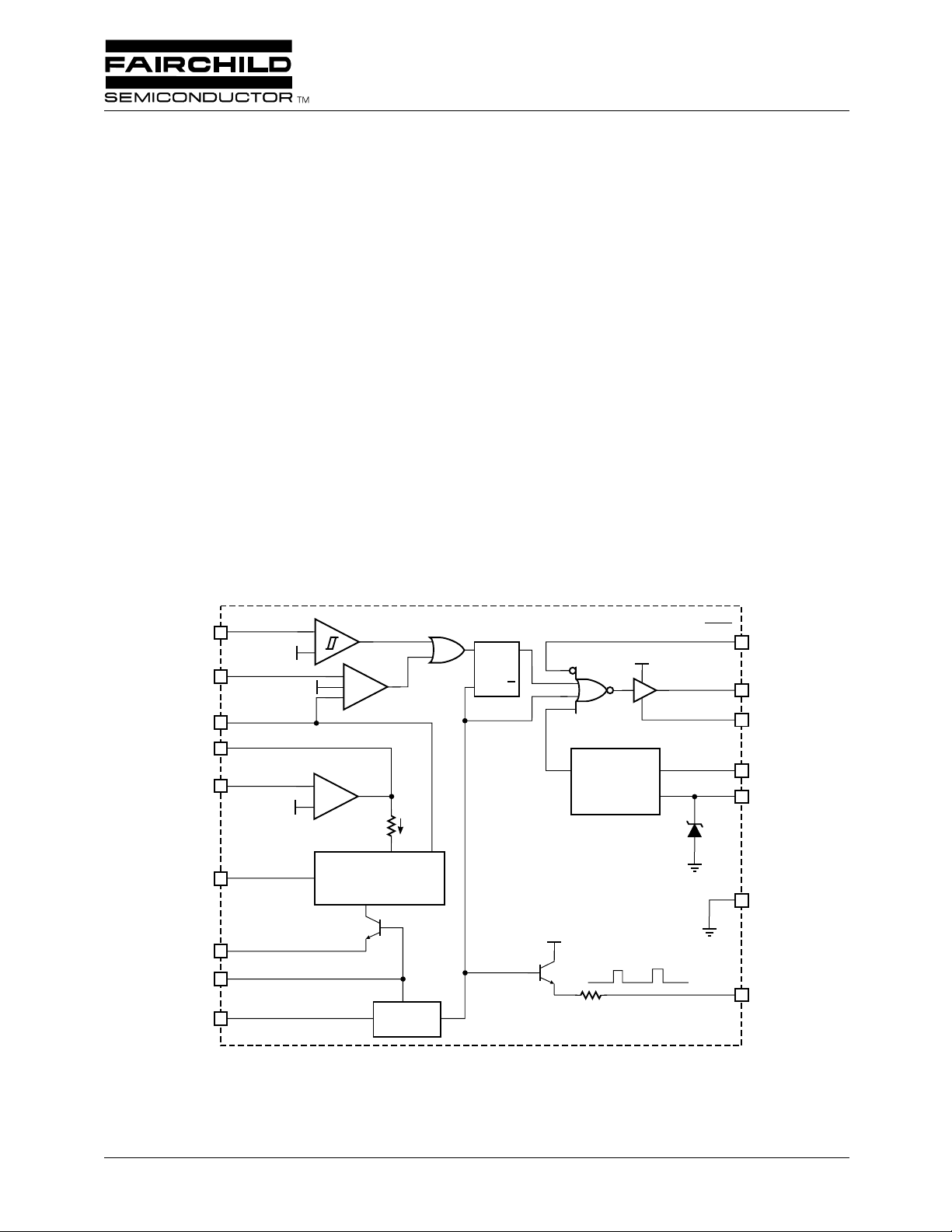

Block Diagram

(Pin Configuration Shown is for DIP Version)

OVP

5

I

SENSE

1

GM OUT

2

EA OUT

3

EA–

4

5V

5V

5V

+

–

+

–

+

–

–

ERROR

AMP

I

EA

Description

The ML4812 is designed to optimally facilitate a peak

current control boost type power factor correction system.

Special care has been taken in the design of the ML4812 to

increase system noise immunity. The circuit includes a

precision reference, gain modulator, error amplifier, overvoltage protection, ramp compensation, as well as a high

current output. In addition, start-up is simplified by an undervoltage lockout circuit with 6V hysteresis.

In a typical application, the ML4812 functions as a current

mode regulator . The current which is necessary to terminate

the cycle is a product of the sinusoidal line voltage times the

output of the error amplifier which is regulating the output

DC voltage. Ramp compensation is programmable with an

external resistor, to provide stable operation when the duty

cycle exceeds 50%.

SHDN

V

32V

OUT

REF

V

CC

10

12

11

14

13

SRQ

V

CC

Q

PWR GND

UNDER

VOLTAGE

LOCKOUT

I

SINE

6

RAMP COMP

7

C

T

16

R

T

8

GAIN MODULATOR

OSC

5V

1kΩ

GND

15

CLOCK

9

REV. 1.0.4 5/31/01

ML4812 PRODUCT SPECIFICATION

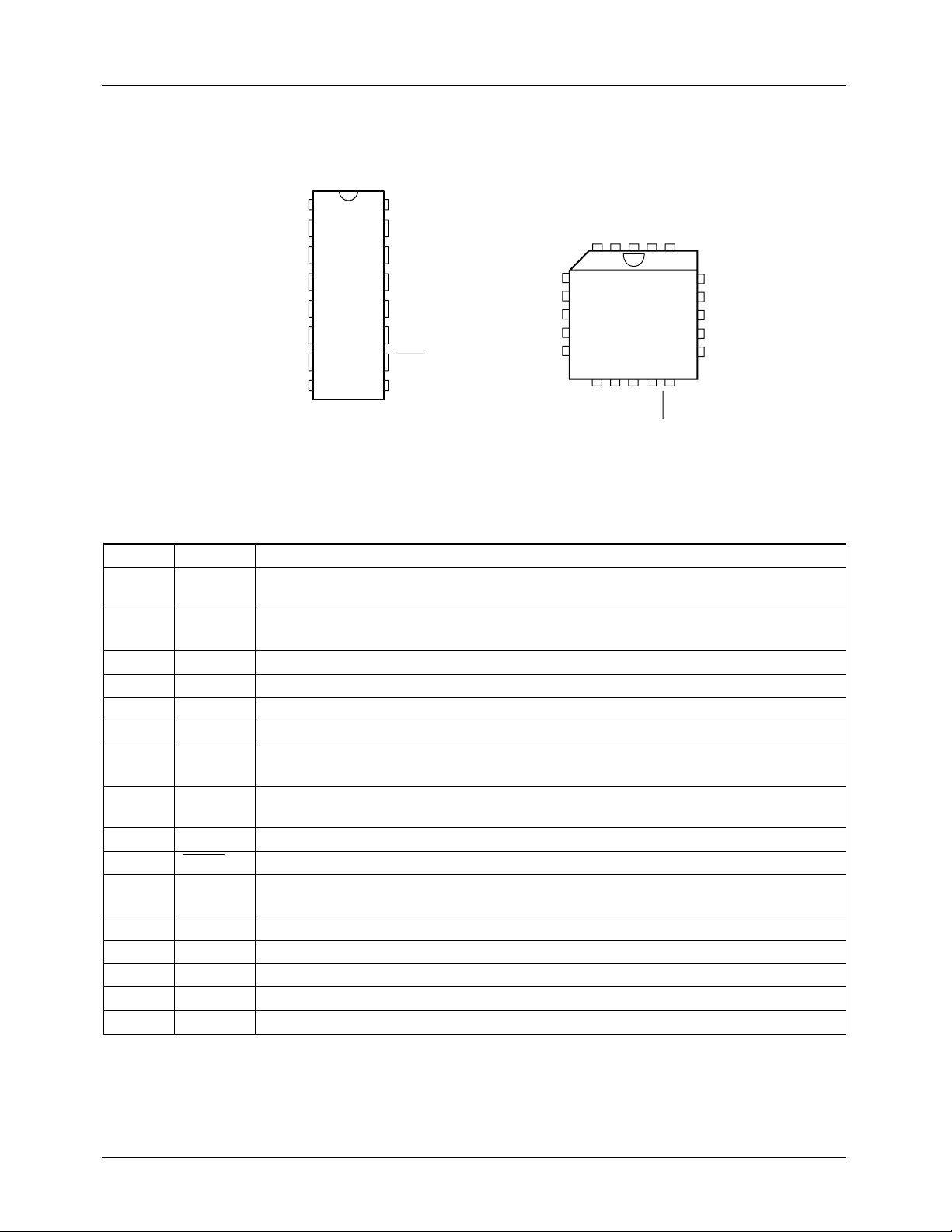

Pin Configuration

ML4812

20-Pin PLCC (Q20)

SENSE

GM OUT

I

NC

CTGND

3212019

NC

SHDN

CLOCK

18

17

16

15

14

4

5

6

7

8

910111213

T

R

RAMP COMP

Top View

V

REF

V

CC

NC

OUT

PWR GND

16-Pin PDIP (P16)

I

SENSE

GM OUT

EA OUT

EA–

OVP

I

SINE

RAMP COMP

R

T

ML4812

1

2

3

4

5

6

7

8

Top View

16

15

14

13

12

11

10

9

C

T

GND

V

REF

V

CC

OUT

PWR GND

SHDN

CLOCK

EA OUT

EA–

NC

OVP

I

SINE

Pin Description

Number Name Function

1 I

SENSE

2 GM OUT Output of gain modulator. A resistor to ground on this pin converts the current to a

3 EA OUT Output of error amplifier.

4EA– Inverting input to error amplifier.

5 OVP Input to over voltage comparator.

6 I

SINE

7 RAMP

COMP

8R

T

9 CLOCK Digital clock output.

10 SHDN A TTL compatible low level on this pin turns off the output.

11 PWR

GND

12 OUT High current totem pole output.

13 V

14 V

CC

REF

15 GND Analog signal ground.

16 C

T

Input from the current sense transformer to the non-inverting input of the PWM

comparator.

voltage. This pin is clamped to 5V and tied to the inverting input of the PWM comparator.

Current gain modulator input.

Buffered output from the oscillator ramp (C

is internally subtracted from the product of I

). A resistor to ground sets the current which

T

SINE

and I

in the gain modulator.

EA

Oscillator timing resistor pin. A 5V source sets a current in the external resistor which is

mirrored to charge C

.

T

Return for the high current totem pole output.

Positive Supply for the IC.

Buffered output for the 5V voltage reference.

Timing capacitor for the oscillator.

2

REV. 1.0.4 5/31/01

ML4812 PRODUCT SPECIFICATION

Absolute Maximum Ratings

Supply Current (I

) 30mA

CC

1

Output Current Source or Sink (OUT) DC 1.0A

Output Energy (capacitive load per cycle) 5µJ

Gain Modulator I

SINE

Input (I

) 1.2mA

SINE

Error Amp Sink Current (EA OUT) 10mA

Oscillator Charge Current 2mA

Analog Inputs (I

, EA–, OVP) –0.3V to 5.5V

SENSE

Junction Temperature 150°C

Storage Temperature Range –65°C to 150°C

Lead Temperature (soldering 10 sec.) 260°C

Thermal Resistance ( θ

20-Pin PLCC

16-Pin PDIP

Note:

1. Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum

ratings are stress ratings only and functional device operation is not implied.

JA

)

60°C/W

65°C/W

Operating Conditions

Temperature Range

ML4812CX 0°C to 70°C

3

REV. 1.0.4 5/31/01

PRODUCT SPECIFICATION ML4812

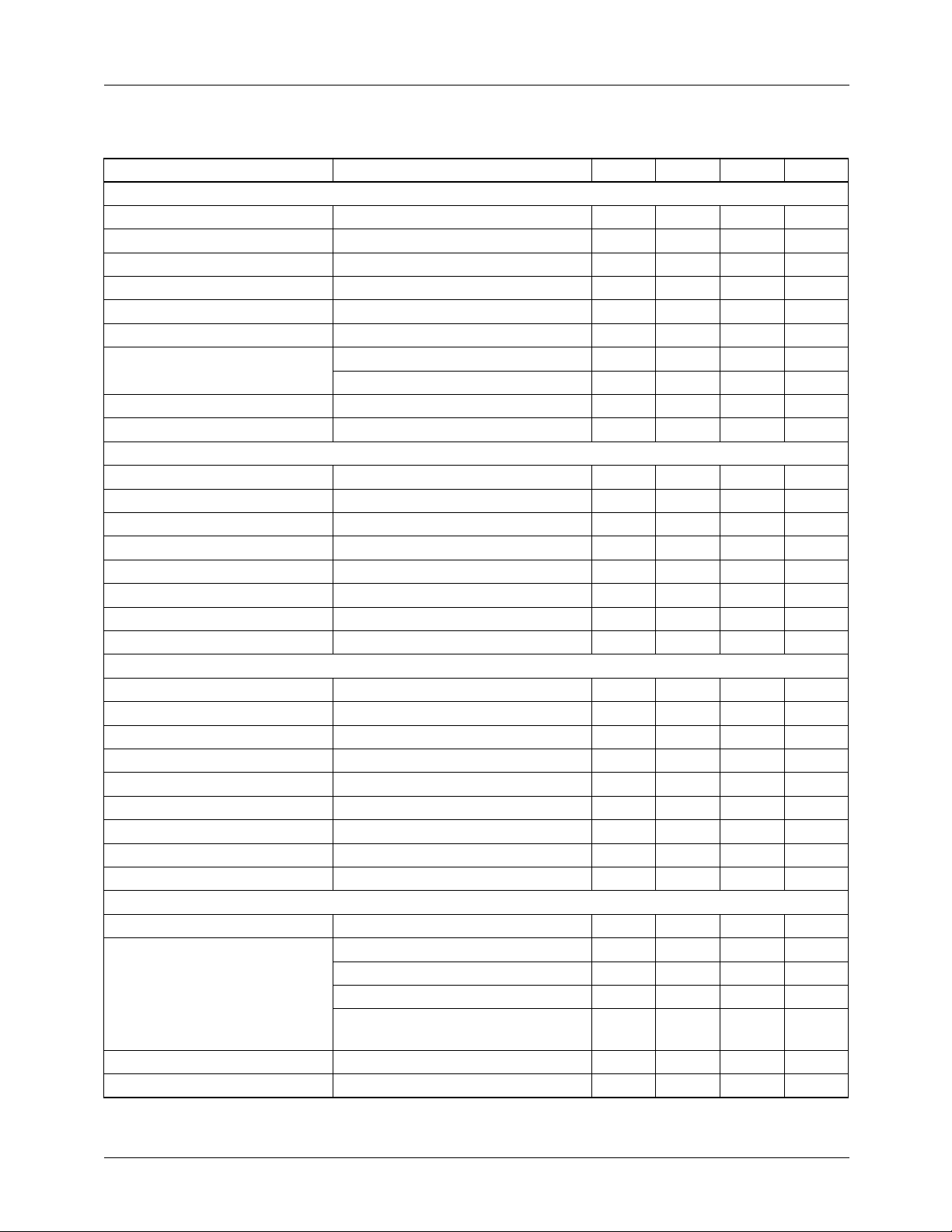

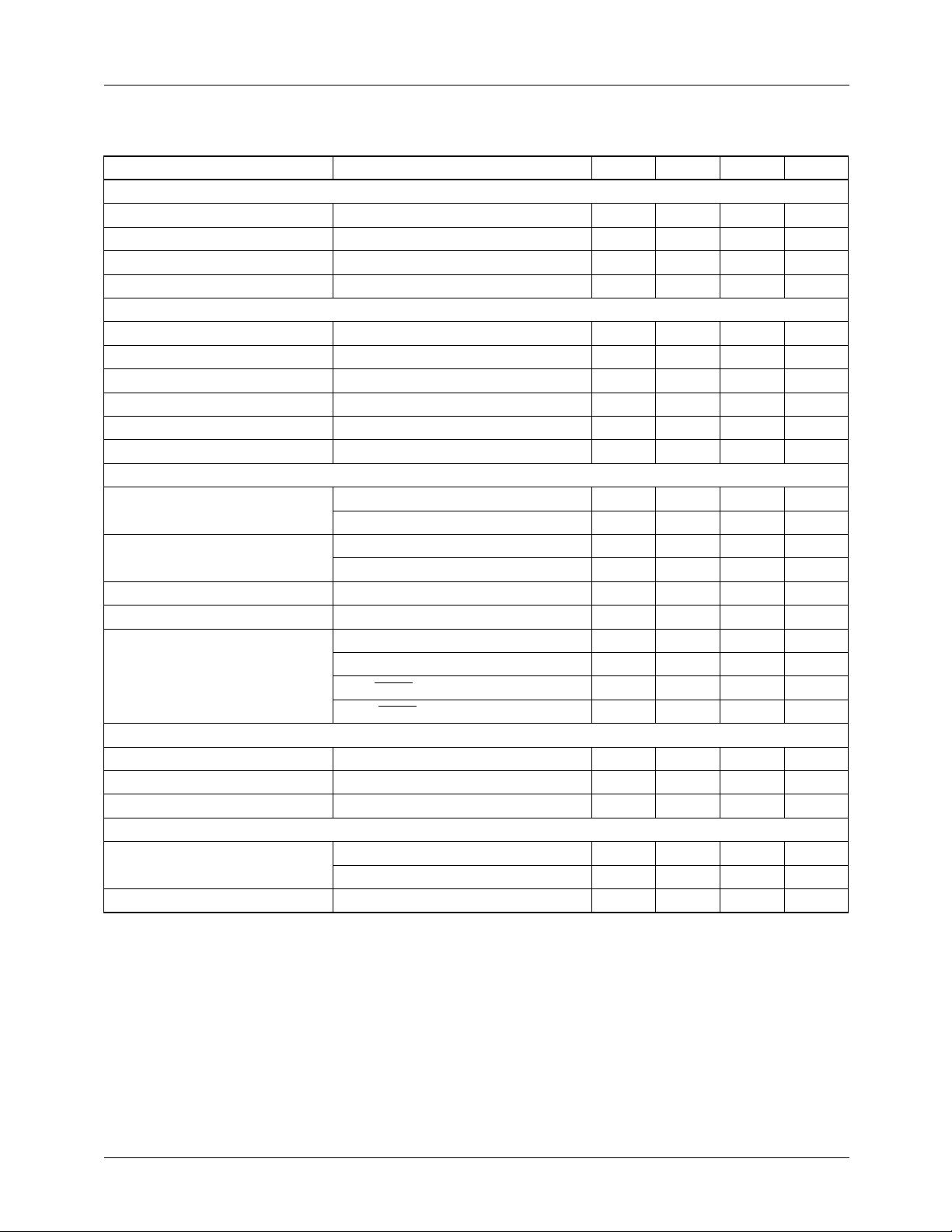

Electrical Characteristics

Unless otherwise specified, V

Parameter Conditions Min. Typ. Max. Units

Oscillator

Initial Accuracy T

Voltage Stability 12V < V

Temperature Stability 2 %

Total Variation Line, temperature 90 108 kHz

Ramp Valley to Peak 3.3 V

R

Voltage 4.8 5.0 5.2 V

T

Discharge Current (R

open) T

T

Clock Out Voltage Low RL = 16k Ω

Clock Out Voltage High RL = 16k Ω

Reference

Output Voltage T

Line Regulation 12V < V

Load Regulation 1mA < IO < 20mA 2 20 mV

Temperature Stability 0.4 %

Total Variation Line, load, temp. 4.9 5.1 V

Output Noise Voltage 10Hz to 10kHz 50 µV

Long Term Stability T

Short Circuit Current V

Error Amplifier

Input Offset Voltage ±15 mV

Input Bias Current –0.1 –1.0 µA

Open Loop Gain 1 < V

PSRR 12V < V

Output Sink Current V

Output Source Current V

Output High Voltage I

Output Low Voltage I

Unity Gain Bandwidth 1.0 MHz

Gain Modulator

I

Input Voltage I

SINE

Output Current (GM OUT) I

Bandwidth 200 kHz

PSRR 12V < V

= 15V , R

CC

= 14k Ω , C

T

= 25°C 91 98 105 kHz

J

< 18V 0.3 %

CC

= 25°C, V

J

V

= 2V 7.3 8.4 9.3 mA

CT

= 1000pF, T

T

= 2V 7.8 8.4 9.0 mA

CT

= Operating Temperature Range (Notes 1, 2).

A

0.2 0.5 V

3.0 3.5 V

= 25°C, I

J

= 125°C, 1000 hours 5 25 mV

J

= 0V –30 –85 –180 mA

REF

EA OUT

EA OUT

EA OUT

EA OUT

EA OUT

= 500µA 0.4 0.7 0.9 V

SINE

= 500µA, EA– = V

SINE

I

= 500µA, EA– = V

SINE

I

= 1mA, EA– = V

SINE

I

= 500µA, EA– = V

SINE

I

RAMP COMP

= 1mA 4.95 5.00 5.05 V

O

< 25V 2 20 mV

CC

< 5V 60 75 dB

< 25V 60 75 dB

CC

= 1.1V, V

= 5.0V, V

= –0.5mA, V

= 1mA, V

= 6.2V 2 12 mA

EA–

– = 4.8V –0.5 –1.0 mA

EA

– = 4.8V 5.3 5.5 V

EA

– = 6.2V 0.5 1.0 V

EA

– 20mV 430 470 510 µA

REF

+ 20mV 3 10 µA

REF

– 20mV 860 940 1020 µA

REF

REF

– 20mV,

455 µA

= 50µA

< 25V 70 dB

CC

REV. 1.0.4 5/31/01

4

ML4812 PRODUCT SPECIFICATION

Electrical Characteristics

Unless otherwise specified, V

CC

(Continued)

= 15V , R

= 14k Ω , C

T

= 1000pF, T

T

= Operating Temperature Range (Notes 1, 2).

A

Parameter Conditions Min. Typ. Max. Units

OVP Comparator

Input Offset Voltage Output Off –25 +5 mV

Hysteresis Output On 95 105 115 mV

Input Bias Current –0.3 –3µA

Propagation Delay 150 ns

PWM Comparator: I

SENSE

Input Offset Voltage ±15 mV

Input Offset Current ±1 µA

Input Common Mode Range –0.2 5.5 V

Input Bias Current –2 –10 µA

Propagation Delay 150 ns

I

Trip Point V

LIMIT

GM OUT

= 5.5V 4.8 5 5.2 V

Output

Output Voltage Low I

Output Voltage High I

Output Voltage Low in UVLO I

Output Rise/Fall Time C

Shutdown V

= –20mA 0.1 0.4 V

OUT

I

= –200mA 1.6 2.2 V

OUT

= 20mA 13 13.5 V

OUT

I

= 200mA 12 13.4 V

OUT

= –5mA, V

OUT

= 1000pF 50 ns

L

IH

V

IL

I

, V

IL

IIH, V

= 0V –1.5 mA

SHDN

= 5V 10 µA

SHDN

= 8V 0.1 0.8 V

CC

2.0 V

0.8 V

Under-Voltage Lockout

Startup Threshold 15 16 17 V

Shutdown Threshold 9 10 11 V

V

Good Threshold 4.4 V

REF

Supply

Supply Current Start-Up, V

Operating, T

Internal Shunt Zener Voltage I

Notes:

1. Limits are guaranteed by 100% testing, sampling, or correlation with worst-case test conditions.

2. V

is raised above the Startup Threshold first to activate the IC, then returned to 15V.

CC

= 30mA 25 30 34 V

CC

= 14V, T

CC

= 25°C2025mA

J

= 25°C 0.8 1.2 mA

J

5

REV. 1.0.4 5/31/01

ML4812 PRODUCT SPECIFICATION

Functional Description

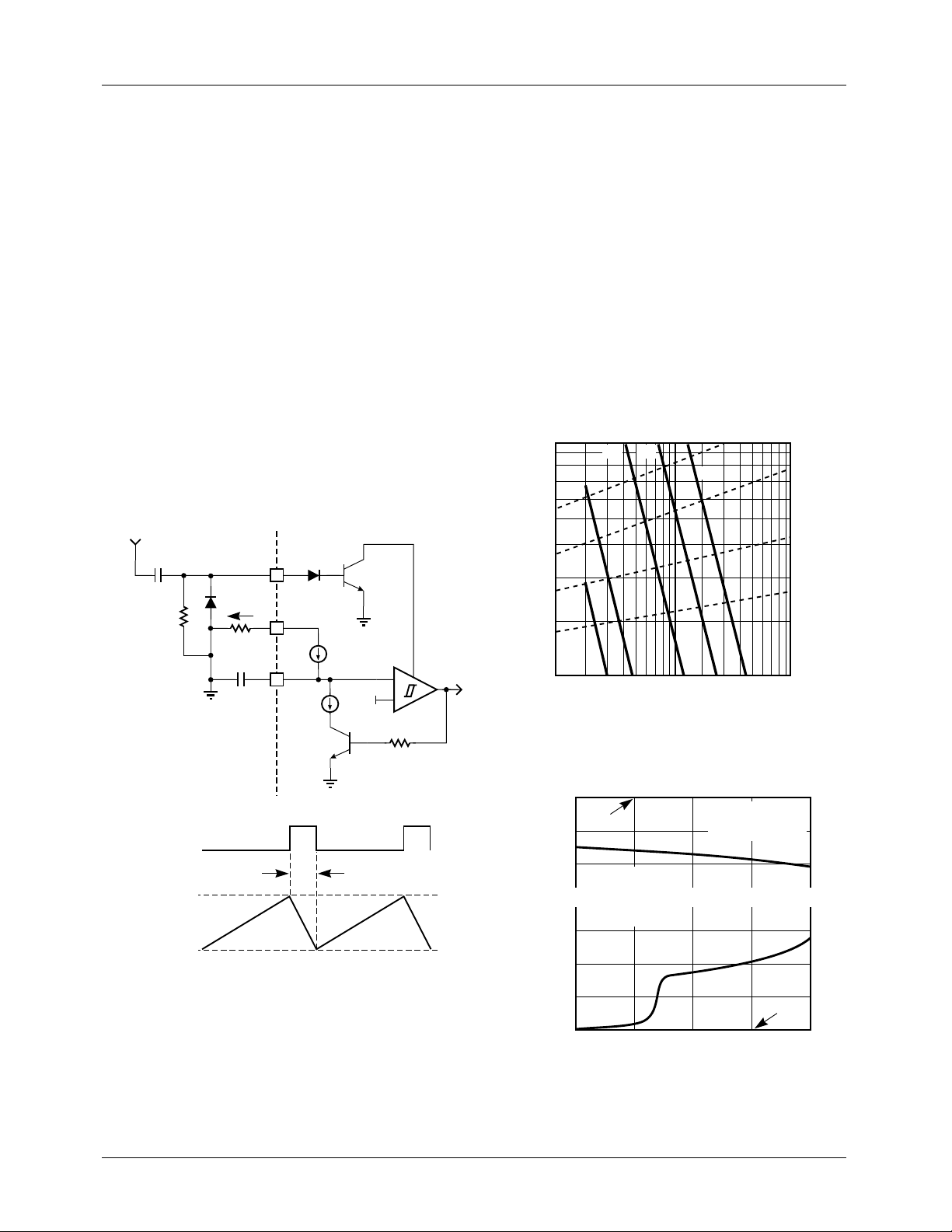

Oscillator

The ML4812 oscillator charges the external capacitor (CT)

with a current (I

voltage reaches the upper threshold, the comparator changes

state and the capacitor discharges to the lower threshold

through Q1. While the capacitor is discharging, Q2 provides

a high pulse.

EXTERNAL

CLOCK

C

SYNC

R

SYNC

) equal to 5/R

SET

I

SET

R

T

C

T

10

9

16

. When the capacitor

SET

SYNC

R

T

I

T

8.4mA

SET

5.6V

C

Q

2

+

-

The Oscillator period can be described by the following

relationship:

T

OSCTRAMPTDEADTIME

+=

where:

OUT

--------------------=

1D

–

ON

V

V

IN

and:

CTV

×

T

DEADTIME

10

8

5

(kΩ)

T

R

3

2

1

10 100 1000

5nF 2nF

10nF

20nF

OSCILLATOR FREQUENCY (kHz)

RAMPVALLEYTOPEAK

-------------------------------------------------------------------------=

8.4mA I

1nF

–

SET

90%

85%

80%

70%

MAXIMUM DUTY CYCLE (%)

RAMP PEAK

RAMP VALLEY

6

Q

1

CLOCK

t

D

V(CT)

Figure 1. Oscillator Block Diagram

Figure 2. Oscillator Timing Resistance vs. Frequency

15

V

CC

14

13

SOURCE SATURATION

LOAD TO GROUND

SINK SATURATION

LOAD TO V

3

2

1

OUTPUT SATURATION VOLTAGE (V)

0

0 200 400 800

CC

OUTPUT CURRENT (mA)

VCC = 15V

80µs PULSED LOAD

120Hz RATE

GND

600

Figure 3. Output Saturation Voltage vs. Output Current

REV. 1.0.4 5/31/01

Loading...

Loading...