MJD44H11

General Purpose Power and Switching Such

as Output or Driver Stages in Applications

D-PAK for Surface Mount Applications

• Load Formed for Surface Mount Application (No Suffix)

• Straight Lead (I-PAK, “- I” Suffix)

• Electrically Similar to Popular MJE44H

• Fast Switching Speeds

• Low Collector Emitter Saturation Voltage

NPN Epitaxial Silicon Transistor

11

D-PAK I-PAK

1.Base 2.Collector 3.Emitter

MJD44H11

Absolute Maximum Ratings

TC=25°C unless otherwise noted

Symbol Parameter Value Units

V

CEO

V

EBO

I

C

I

CP

PC

T

J

T

STG

Electrical Characteristics

Collector-Emitter Voltage 80 V

Emitter-Base Voltage 5 V

Collector Current (DC) 8 A

Collector-Current (Pulse) 16 A

Collector Dissipation (TC=25°C) 20 W

Collector Dissipation (T

=25°C) 1.75 W

a

Junction Temperature 150 °C

Storage T emperature - 65 ~ 150 °C

TC=25°C unless otherwise noted

Symbol Parameter Test Condition Min. Typ. Max. Units

V

(sus) *Collector-Emitter Sustaining Voltage IC = 30mA, IB = 0 80 V

CEO

I

CEO

I

EBO

hFE

(sat) *Collector-Emitter Saturation Voltage IC = 8A, IB = 0.4A 1 V

V

CE

(on) *Base-Emitter ON Voltage IC = 8A, IB = 0.8A 1.5 V

V

BE

f

T

Cob

tON

tSTG

tF

* Pulse Test: PW≤300µs, Duty Cycle≤2%

Collector Cut-off Current V

Emitter Cut-off Cu rr e nt V

*DC Current Gain V

Current Gain Bandwidth Product V

Output Capacitance V

Turn ON Time IC = 5A

Storage Time 500 ns

= 80V, IB = 0 10 µA

CE

= 5V, IC = 0 50 µA

BE

= 1V, IC = 2A

CE

V

= 1V, IC = 4A

CE

= 10V, IC = 0.5A 50 MHz

CE

=10V, f = 1MHz 130 pF

CB

60

40

300 ns

= - IB2 = 0.5A

I

B1

Fall Time 140 ns

©2001 Fairchild Semiconductor Corporation Rev. A2, June 2001

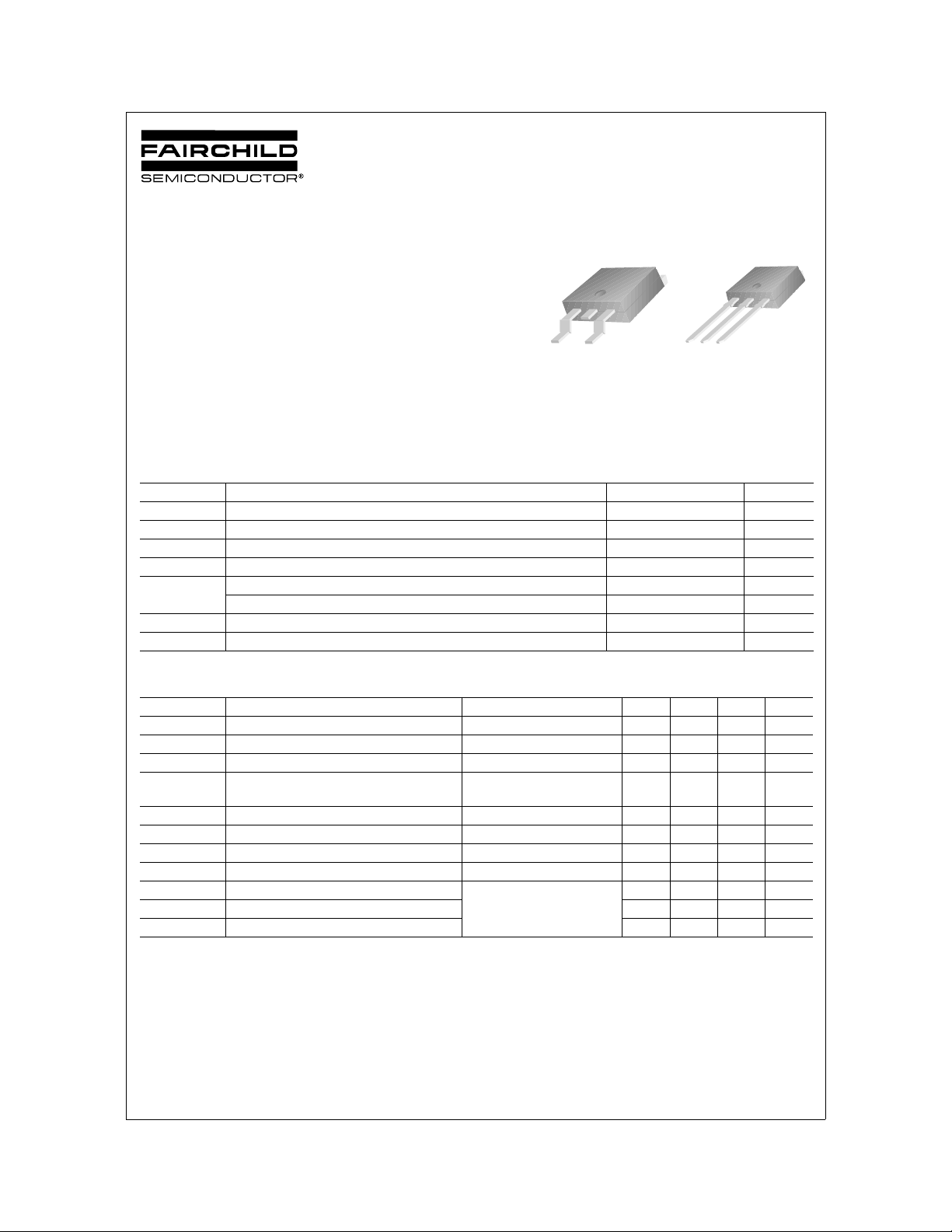

Typical Characteristics

MJD44H11

1000

100

10

, DC CURRENT GAIN

FE

h

1

0.01 0.1 1 10

IC[A], COLLECTOR CURRENT

Figure 1. DC current Gain Figure 2. Safe Operating Area

25

20

15

10

VCE = 1V

100

ICP(max)

10

IC(max)

1

0.1

[A], COLLECTOR CURRENT

C

I

0.01

1 10 100 1000

100

µ

s

500

µ

s

1ms

5ms

DC

VCE[V], COLLECTOR-EMITTER VOLTAGE

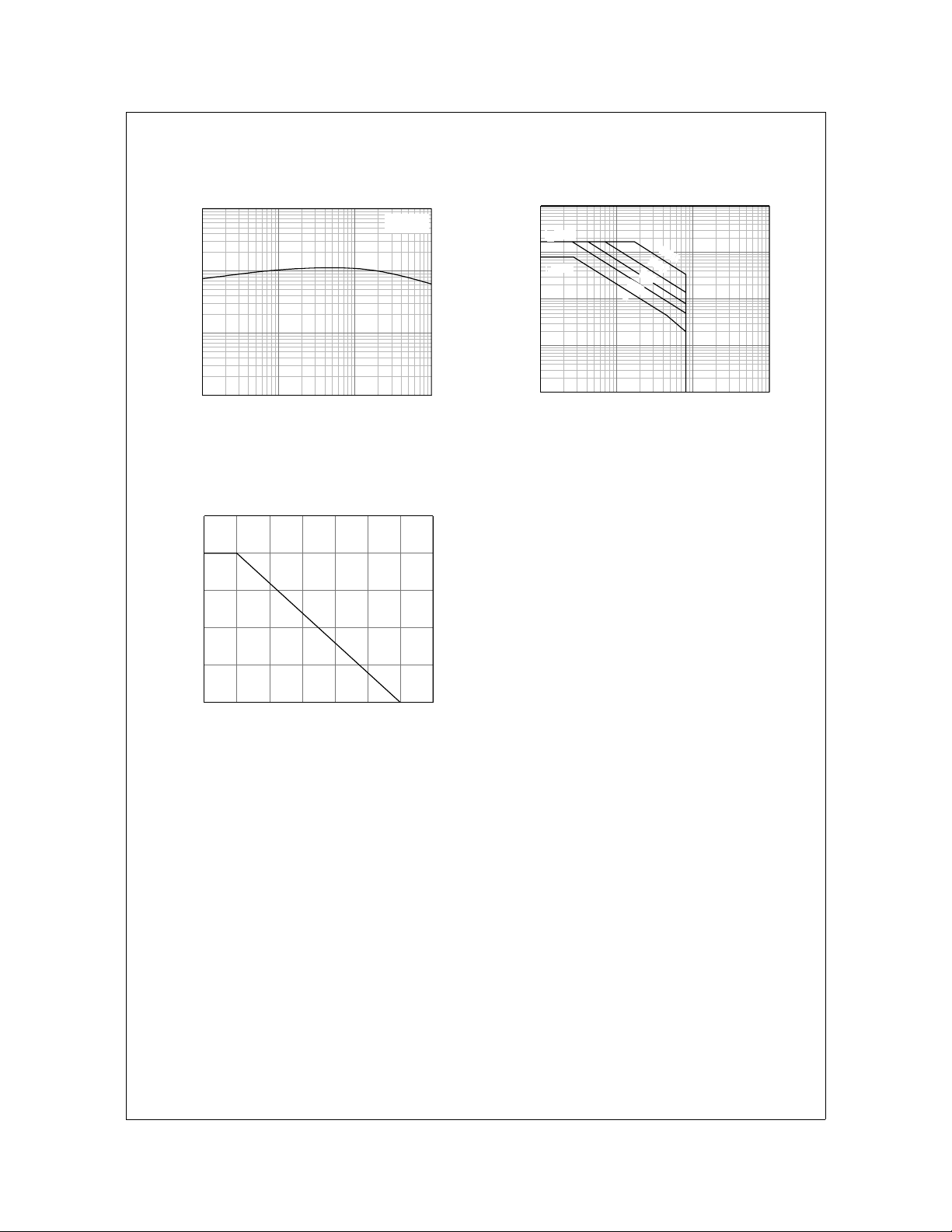

5

[W], POWER DISSIPATION

C

P

0

0 25 50 75 100 125 150 175

TC[oC], CASE TEMPERATURE

Figure 3. Power Derating

©2001 Fairchild Semiconductor Corporation

Rev. A2, June 2001

Loading...

Loading...