Fairchild Semiconductor KA9259CDTF Datasheet

KA9259D

5-Channel Motor Driver

www.fairchildsemi.com

Features

• 1-phase, full-wave, linear DC motor driver

• Built-in TSD (Thermal shutdown) circuit

• Built-in 5V regulator (With an external PNP Transistor)

• Built-in mute circuit

• Built-in loading motor speed control circuit

• Wide operating supply voltage range: 6V~13.2V

Description

The KA9259D is a monolithic integrated circuit, suitable for

5-ch motor driver which drives focus actuator, tracking actuator, sled motor, s pindle motor and loading motor of CD system.

28-SSOPH-375

Typical Applications

• Compact disk player (CDP)

• Video compact disk player (VCD)

• Automotive compact disk player (CDP)

• Other compact disk media

©2000 Fairchild Semiconductor International

Ordering Information

Device Package Operating Temp.

KA9259CD 28-SSOPH-375 −25°C ~ +75°C

KA9259CDTF 28-SSOPH-375 −25°C ~ +75°C

KA9259ED 28-SSOPH-375 −25°C ~ +75°C

KA9259EDTF 28-SSOPH-375 −25°C ~ +75°C

Rev. 1.0.1

February. 2000.

1

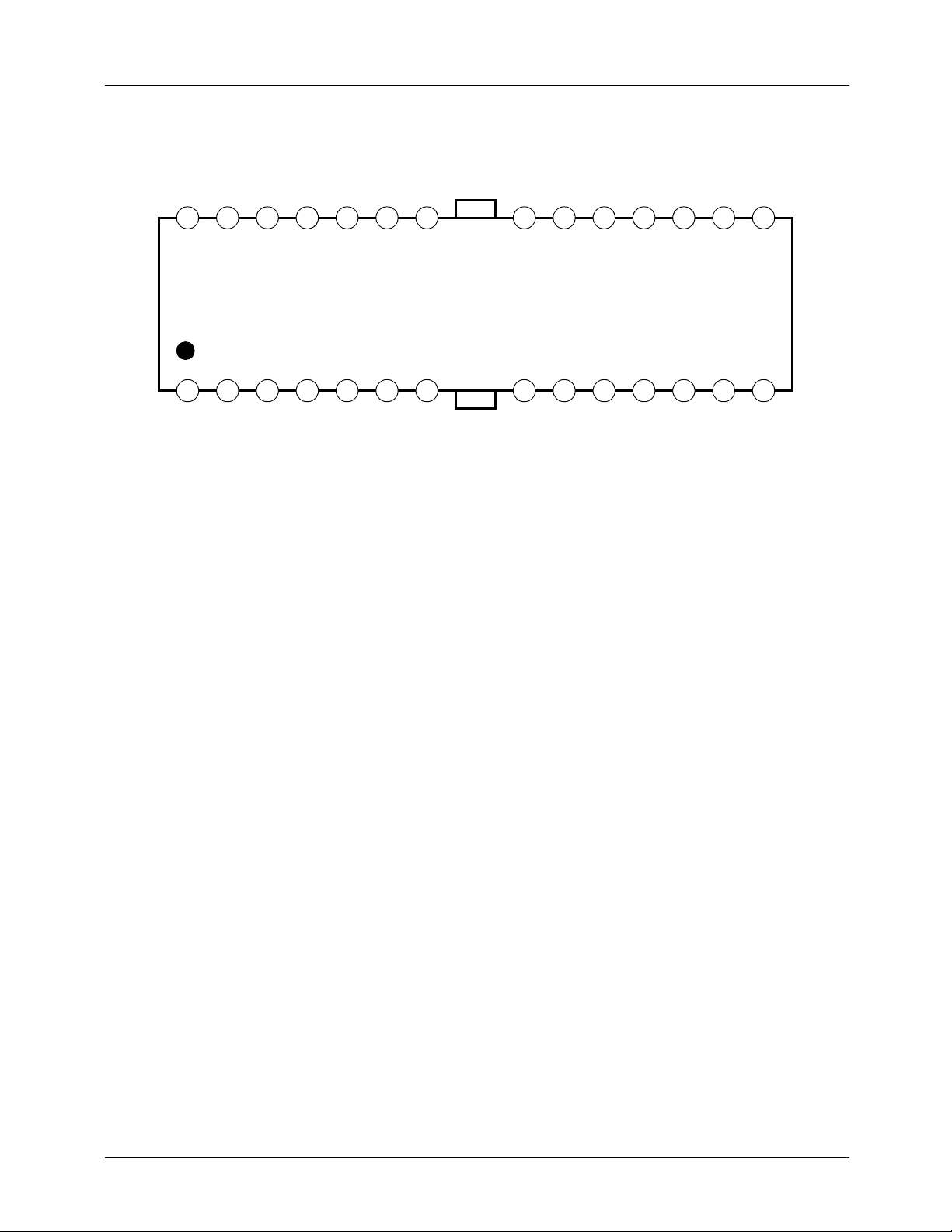

Pin Assignments

GND3

DO4.2

1234567 891011121314

DO1.1

DO1.2

KA9259D

FIN

(GND)

DO4.2

DI4.2

DI4.1

VREF

CC2

V

CC1

V

LD CTL

DI3

DO3.2

DO3.1

DO5.2

DO5.1

1516171819202122232425262728

KA9259D

REB

DI1.1

DI1.2

REO

MUTE

FIN

(GND)

GND1

DI2

DI5.1

DO2.1

DO2.2

GND2

DI5.2

2

KA9259D

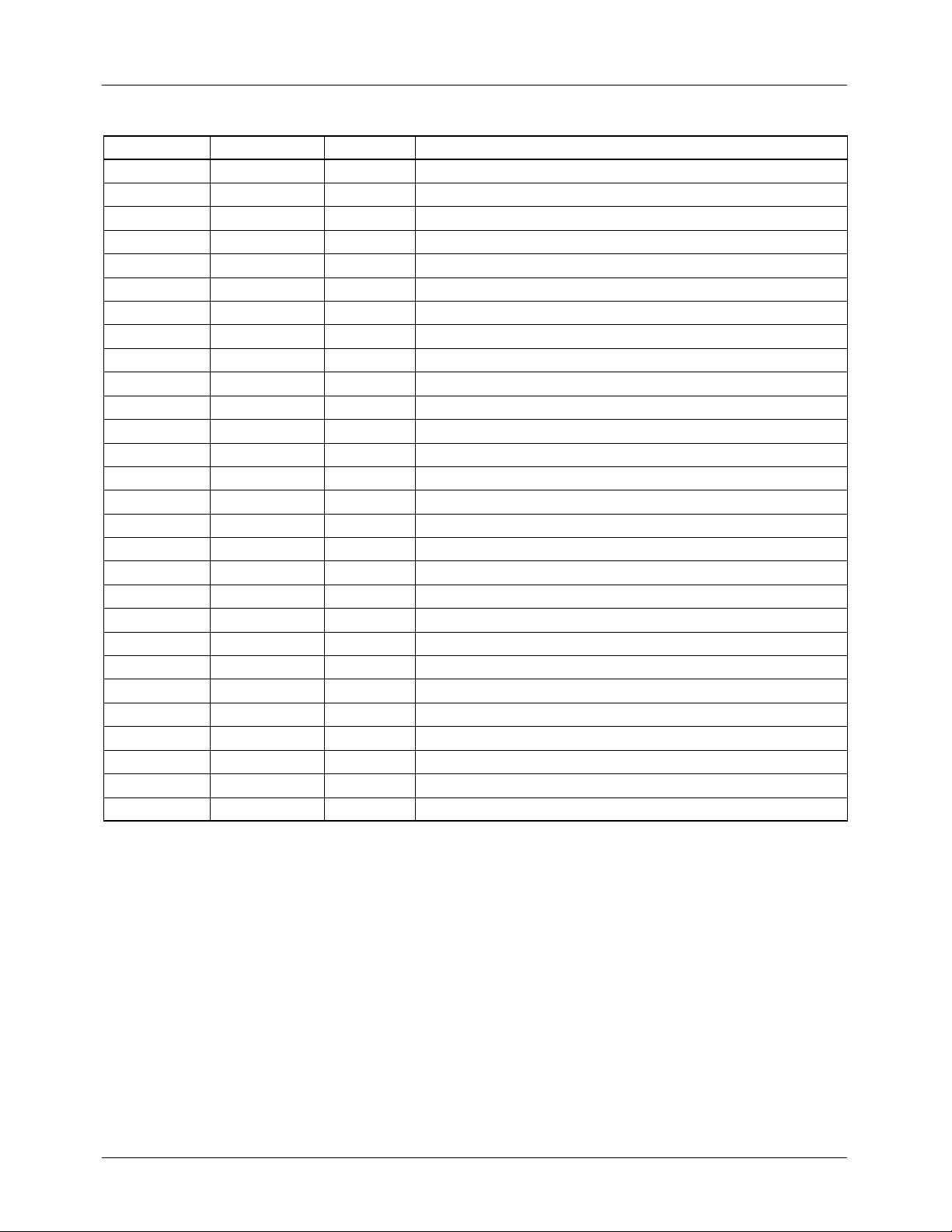

Pin Definitions

Pin Number Pin Name I/O Pin Function Description

1 DO1.1 O Focus output 1 (−)

2 DO1.2 O Focus output 2 (+)

3 DI1.1 I Focus input 1

4 DI1.2 I Focus input 2 (Adjustable)

5 REB O Regulator base

6 REO O Regulator output, 5V

7MUTEIMute

8 GND1 - Ground 1

9 DI5.1 I Loading input 1

10 DI2 I Spindle input 2

11 DO2.1 O Spindle output (+)

12 DO2.2 O Spindle output (−)

13 GND2 - Ground 2

14 DI5.2 I Loading input 2

15 DO5.1 O Loading output 1(+)

16 DO5.2 O Loading output 2(−)

17 DO3.1 O Sled output (−)

18 DO3.2 O Sled output (+)

19 DI3 I Sled input

20 LD CTL I Loading motor speed control

21 V

22 V

CC1

CC2

23 VREF I 2.5V bias

24 DI4.1 I Tracking input 1 (Adjustable)

25 DI4.2 I Tracking input 2

26 DO4.1 O Tracking output 1 (+)

27 DO4.2 O Tracking output 2 (−)

28 GND3 - Ground 3

- Supply voltage 1

- Supply voltage 2

3

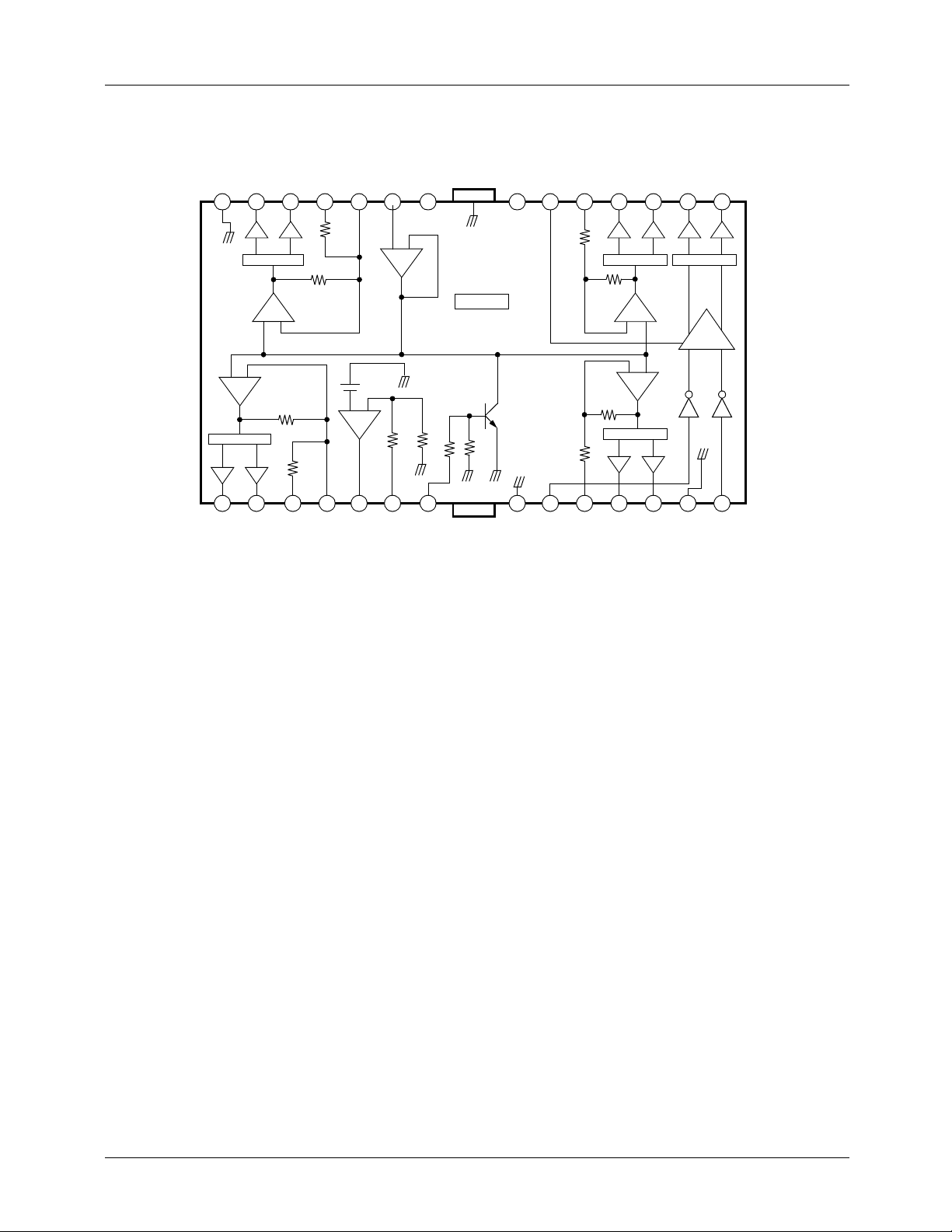

Internal Block Diagram

GND3

DO4.2

DO4.1

KA9259D

FIN

(GND)

DI4.2

DI4.1

CC2

VREF

V

22232425262728

CC1

V

LD CTL

DI3

DO3.2

DO3.1

DO5.2

DO5.1

15161718192021

10k

+

+

REB

−

TSD

Regulator

Mute

50k

10k

10k

714

REO

MUTE

50k

FIN

(GND)

+

−

Level

shift

+

−

Level

shift

+

−

12 345 6 8 9 10 11 12 13

DO1.1

DO1.2

10k

−

+

2.5V

10k

10k

DI1.1

−

DI1.2

GND1

10k

+

−

Level

shift

10k

+

−

−

+

10k

Level

shift

−

+

10k

DI2

DI5.1

DO2.1

DO2.2

−

Level

shift

+

COMP

GND2

+

−

DI5.2

4

KA9259D

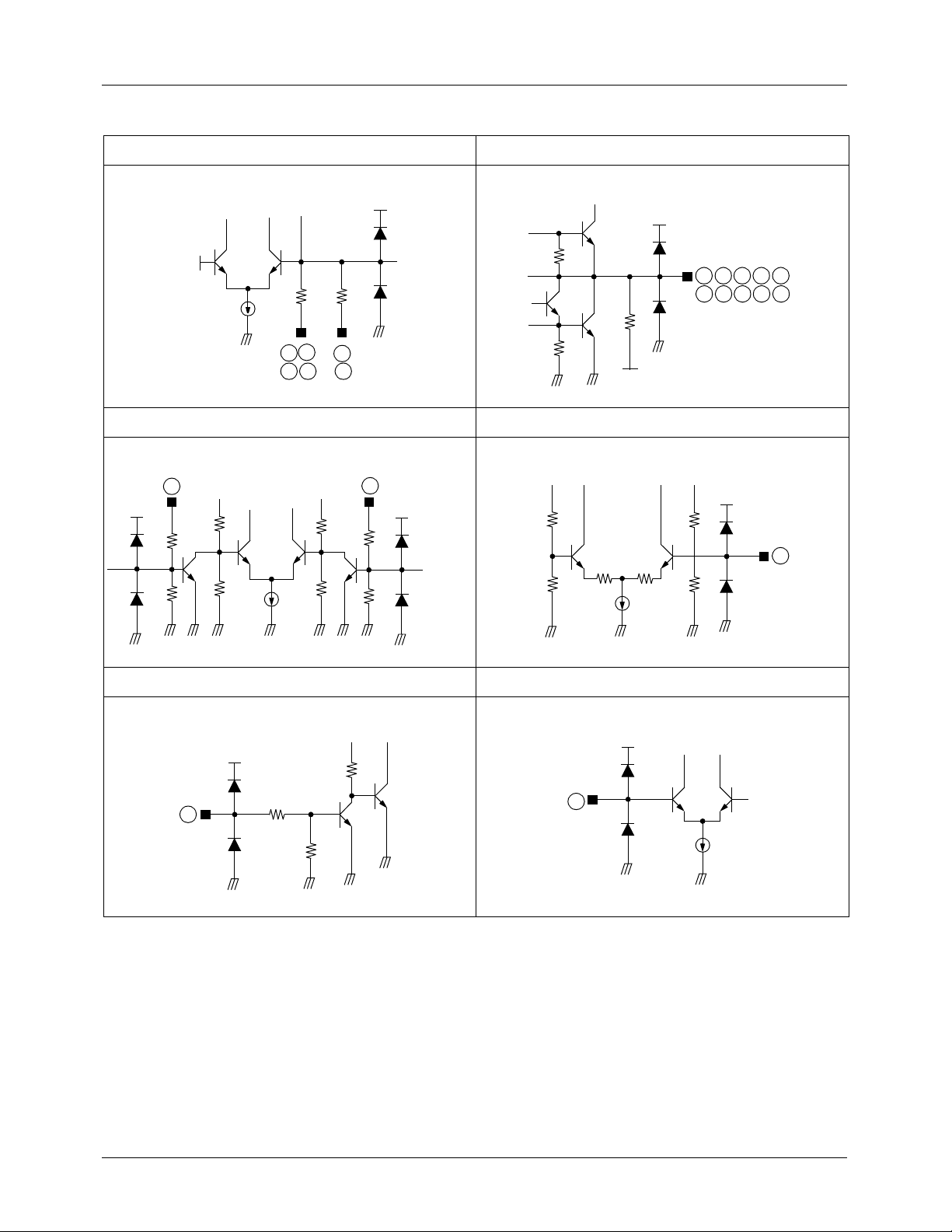

Equivalent Circuits

Driver input (Except for loading motor driver) Driver output

50k

50k

2.5V

10k

10

4

2419325

10k

0.58k

20k

V

REF1

Loading motor driver input Loading motor speed control input

50k

50k

14

50k

50k 50k

50k

50k

50k

9

50k

50k

50k

50k

Mute input Bias input

1162171118122715

26

20

50k

7

50k

50k

23

5

Loading...

Loading...