Fairchild Semiconductor KA7630 Datasheet

KA7630/KA7631

Fixed Multi-Output Regulator

www.fairchildsemi.com

Features

• Output Currents up to 0.5A (Output1 & 2)

• Output Current up to 1A with External Transistor

(Output3)

• Fixed Precision Output 1 Voltage 5.1V ±2%

• Fixed Precision Output 2 Voltage 8V ±2% (KA7630)

• Fixed Precision Output 2 Voltage 9V ±2% (KA7631)

• Control Signal Generator for Output 3 Voltage (12V ±2%)

• Reset Facility for Output Voltage1

• Output 2,3 wit h Disable by TTL Input

• Current Limit Protection at Each Output

• Thermal Shut Down

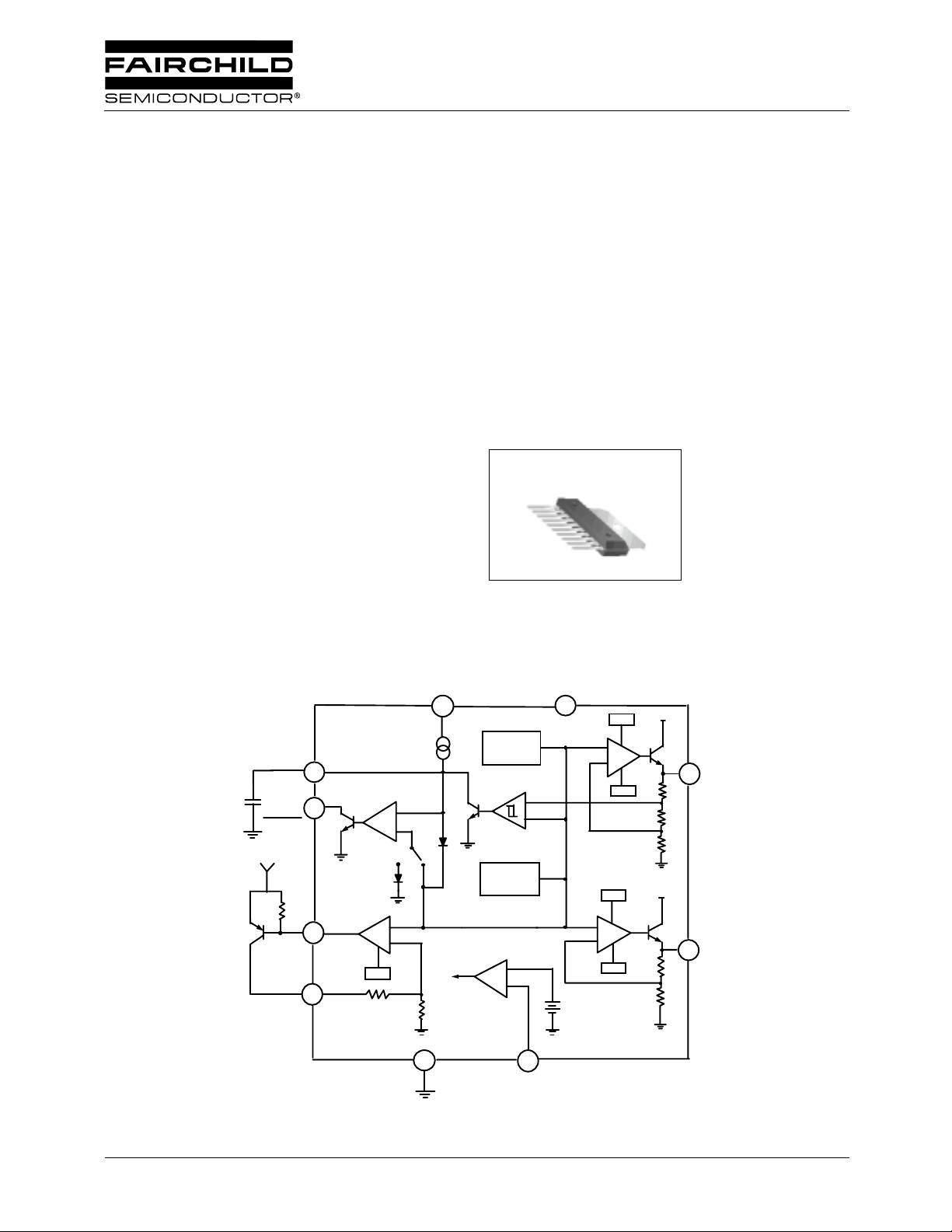

Internal Block Diagram

Vin1

10uA

+

SW

+

SCP

Output

Cd

100nF

A614"Y"

DEL.CAP

3

6

RESET

Vsys

10K

7

Control

10

Output3

Description

The KA7630/KA7631 is a multi-output positive voltage

regulator des igned to provide fix e d pr ec i sion output voltage s

of 5.1V, 8V (7630) / 9V(7631) at current up to 0.5Aand 12V

at current up to 1A with external PNP transistor.

An internal reset circuit genera tes a reset pulse when the

output 1 decreases below the regulated value. Output2 & 3

can be disabled by TTL input. Protection features include

over voltage protection, short circuit protection and thermal

shutdown.

10-SIP H/S

Vin2

Bandgap

Reference

+

50mV

Thermal

Shut Do wn

+

-

2,3

21

2.5V

1.4V

+

-

OVP

+

-

SCP

OVP

SCP

Vin1

Vin2

9

8

Output1

Output2

©2002 Fairchild Semiconductor Corporation

GND

5

4

Disable

Rev. 1.0.1

KA7630/KA7631

Absolute Maximum Ratings

Parameter Symbol Value Unit Remark

DC Input Voltage Vin 20 V Disable Input Voltage Vc 20 V Output Current Io 0.5 A Power Dissipation Pd 1.5 W No Heatsink

Junction Temperature Tj +150 °C-

Operating Temperature Topr 0 ~ +125 °C-

Electrical Characteristics(KA7630)

(Refer to test circuit Vin1=7.5V ,Vin2=10.5V ,Tj = +25°C, unless otherwise specified)

Parameter Symbol Conditions Min. Typ. Max. Unit

Io1 = 10mA

Output Voltage 1 Vo1

Output Voltage 2 Vo2

Dropout Output Voltage 1,2 Vd1,2 Io1,2 = 500mA - - 2.5 V

Line Regulation 1,2 ∆Vo 1,2

Load Regulation 1,2 ∆Vo 1,2

Output Voltage 3 Vo3 Vsys=13V, Io3=100mA 11.7 12 12.3 V

Line Regulation 3 ∆Vo3 13V< Vin2 < 18V, Io3 =100mA - - 120 mV

Load Regulation 3 ∆Vo3 5mA < Io3 < 1A - - 250 mV

Reset Pulse Delay Trd Cd = 100nF, Note1 - 25 - ms

Saturation Voltage in Reset

Condition

Leakage Current at Pin 6 IrH V6 = 10V - - 10 µA

Output Voltage Thermal Drift STt 0°C <Tj < +125°C , Note2 - 100 ppm/°C

Short Circuit Output Current Isc1,2 Vin1 = 7.5V ,Vin2 = 10.5V - - 1.6 A

Disable Voltage High VdisH Output 2 Active 0.8 - 2.0 V

Disable Voltage Low VdisL Output 2 Disabled 0.8 - 2.0 V

Disable Bias Current Idis 0V < Vdis < 7V -100 - 2 µA

Junction Temperature for TSD Ttsd Note 2 - 145 - °C

Quiescent Current Iq Io1 = 10mA, Output2 Disabled - - 2 mA

Reset Threshold Voltage Vr K = Vo1 K-0.4 K-0.25 K -0.1 V

Reset Threshold Hysteresis Vrth Note1 20 50 100 mA

VrL I6 = 5mA - - 0.4 V

7.5V<Vin1<14V

5mA < Io1< 500mA

Io2 = 10mA

10.5V < Vin2< 18V

5mA < Io2 < 500mA

7.5V < Vin1<14V

10.5V < Vin2 < 18V

Io1,2 = 200mA

5mA < Io1< 500mA

5mA < Io2< 500mA

5

4.9

7.84

7.7

--

--

5.1

5.1

8

8

5.2

5.3

8.16

8.3

50

80

100

160

V

V

mV

mV

Notes:

1. To check the reset circuit ,the reset output is low to discharge the delay capacitor(=Cd). it’s less than Vo1-0.25V. And the

reset output is high when the delay capacitor voltage linearly increased by the internal current source(10µA ) if it’s more than

Vo1- 0.2V. T he equation of delay time is same as below. Trd = (Cd × 2.5) / 10µA

2. These parameters, although guaranteed, are not 100% tested in production.

2

Loading...

Loading...