Fairchild Semiconductor DM74S283N Datasheet

DM74S283

4-Bit Binary Adder with Fast Carry

DM74S283 4-Bit Binary Adder with Fast Carry

August 1986

Revised May 2000

General Description

These full adders perfor m the addition of two 4-bi t binary

numbers. The sum (∑) outputs are pr ovided for each bit

and the resultant car ry (C4 ) is obtaine d from the f ourth bit.

These adders feature full internal look ahead across all four

bits. This provides the system designer with partial lookahead performance at the econom y and red uced packa ge

count of a ripple-carry implementation.

The adder logic, including the carry, is implemente d in its

true form meaning that the end-around carry can be

accomplished without the need for logic or level inversion.

Features

■ Full-carry look-ahead across the four bits

■ Systems achieve partial look-ahead performance with

the econo m y of ripple carry

■ Typical add times

Two 8-bit words 15 ns

Two 16-bit words 30 ns

■ Typical power dissipation 510 mW

Ordering Code:

Order Number Package Number Package Description

DM74S283N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

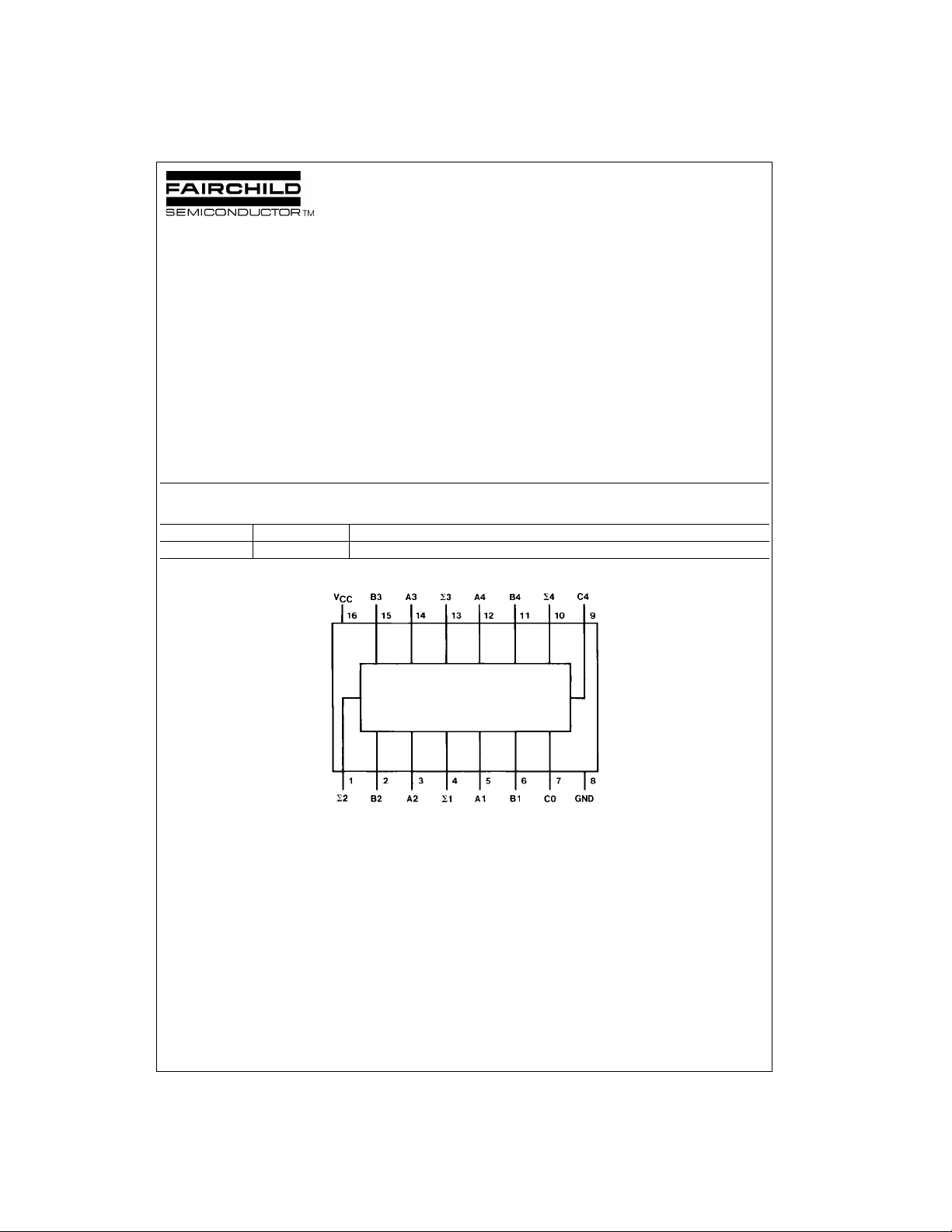

Connection Diagram

© 2000 Fairchild Semiconductor Corporation DS006484 www.fairchildsemi.com

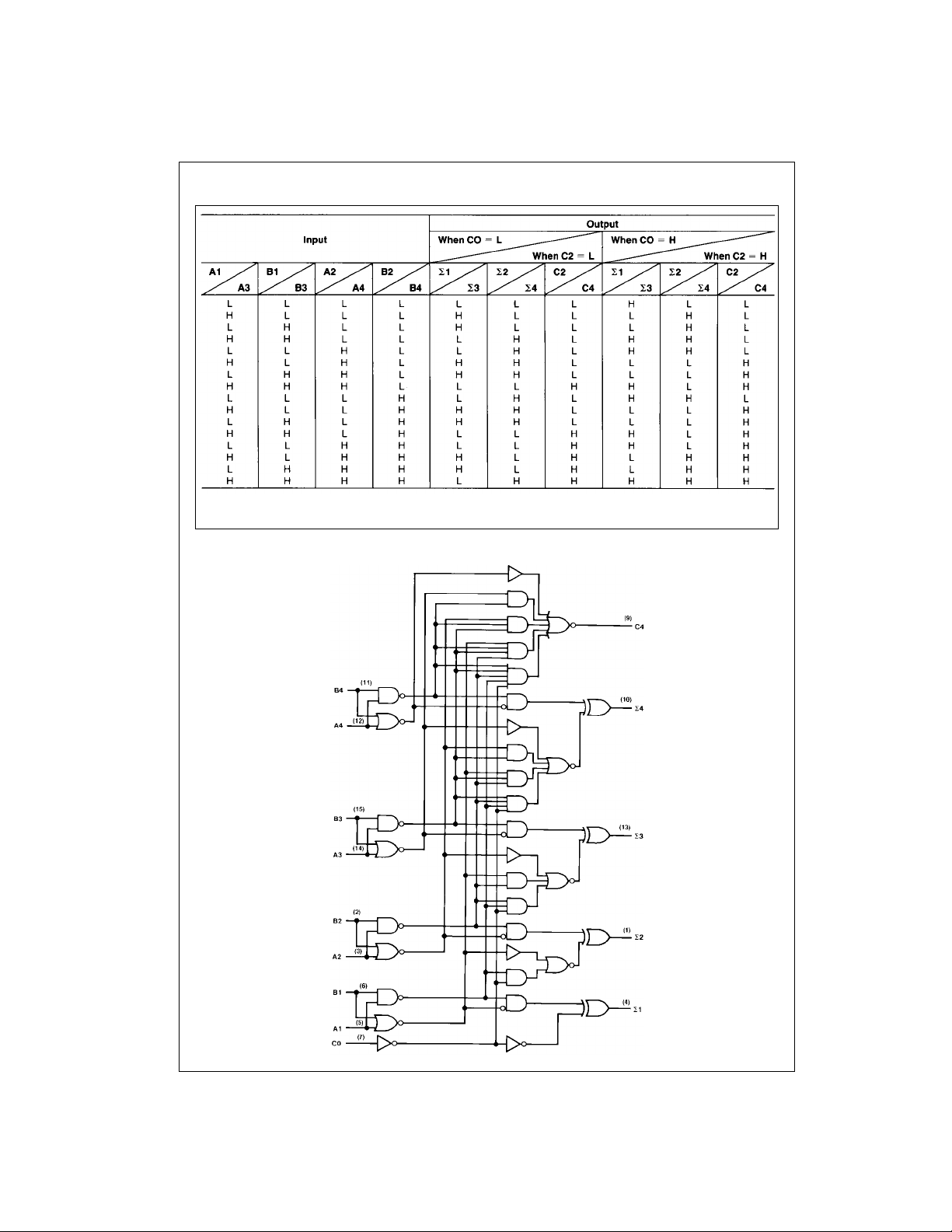

Function Table

DM74S283

H = HIGH Level, L = LOW Level

Note: Input conditions at A1, B1, A2, B2, and C0 are used to determine outputs ∑1 and ∑2 and the value of the internal carry C2. The values at C2, A3,

B3, A4, and B4 are then used to determine outputs ∑3, ∑4, and C4.

Logic Diagram

www.fairchildsemi.com 2

Loading...

Loading...