Fairchild Semiconductor DM74LS156N, DM74LS156MX, DM74LS156M Datasheet

© 2000 Fairchild Semiconductor Corporation DS006395 www.fairchildsemi.com

August 1986

Revised April 2000

DM74LS155 • DM74LS156 Dual 2-Line to 4-Line Decoders/Demultiplexers

DM74LS155 • DM74LS156

Dual 2-Line to 4-Line Decoders/Demultiplexers

General Description

These TTL circuits feature dual 1-line-to-4-line demultiplexers with individual strobes and common binary-address

inputs in a single 16-pin package. W hen both sectio ns are

enabled by the strobes, the common address inputs

sequentially select and route ass ociated input data to the

appropriate output of each section . The individual strobes

permit activating or i nhibiting each of the 4-bit sections as

desired. Data applied to input C1 is inverted at its outputs

and data applied at C2 is true through its outputs. The

inverter following the C1 data input permits use as a 3-to-8line decoder, or 1-to-8-line demultiplexer, without external

gating. Input clamping diod es are provided on these circuits to minimize transmission-line effects and simplify system design.

Features

■ Applications:

Dual 2-to-4-line decoder

Dual 1-to-4-line demultiplexer

3-to-8-line decoder

1-to-8-line demultiplexer

■ Individual strobes simplify cascading for decoding or

demultiplexing larger words

■ Input clamping diodes simplify system design

■ Choice of outputs:

Totem-pole (DM74LS155)

Open-collector (DM74LS156)

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

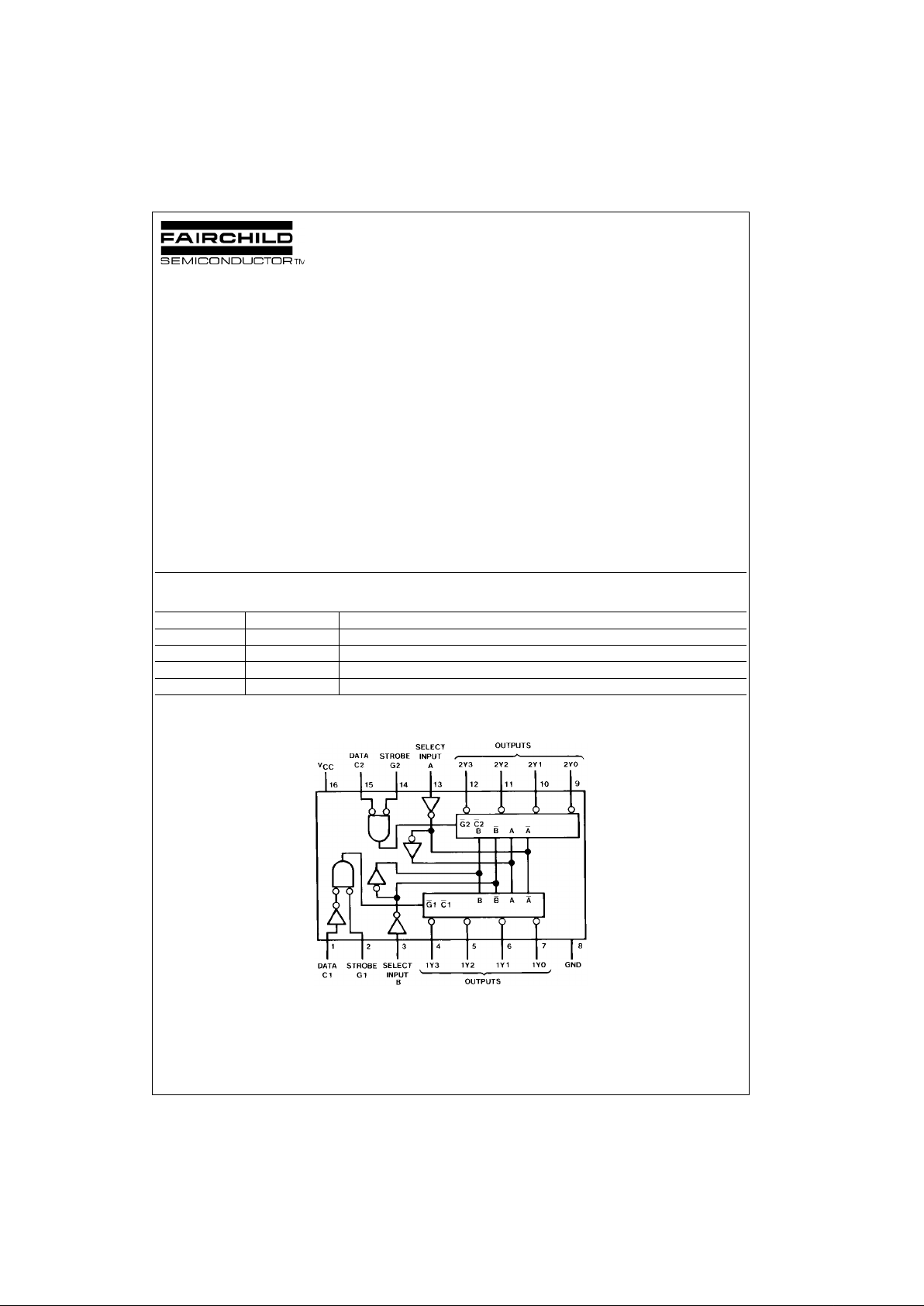

Connection Diagram

Order Number Package Number Package Description

DM74LS155M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

DM74LS155N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

DM74LS156M M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

DM74LS156N N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

www.fairchildsemi.com 2

DM74LS155 • DM74LS156

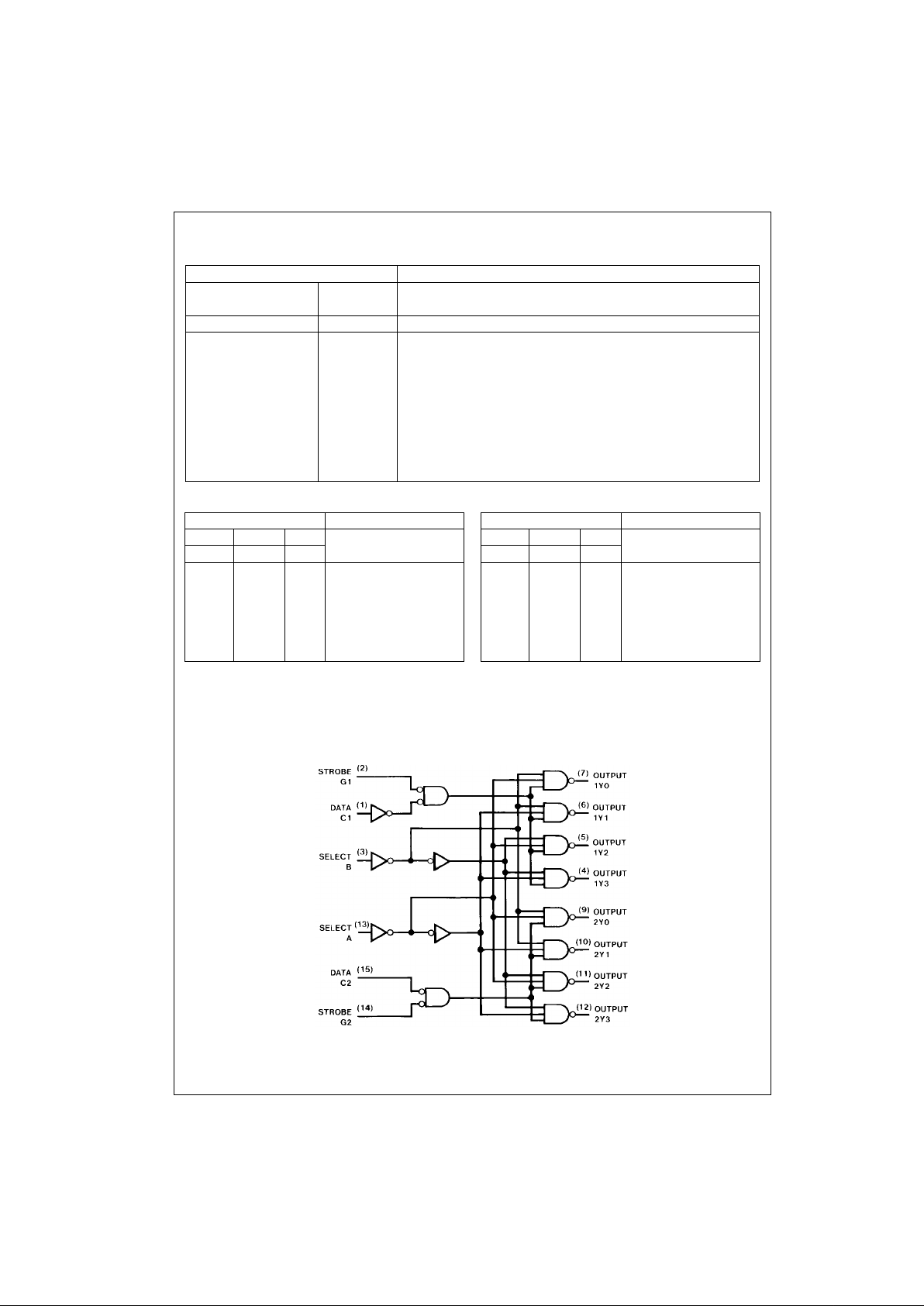

Function Tables

3-Line-to-8-Line Decoder or 1-Line-to-8-Line Demultiplexer

2-Line-to-4-Line Decoder or 1-Line-to-4-Line Demultiplexer

H = HIGH level

L = LOW level

X = don’t care

Note 1: C = inputs C1 and C2 connected together

Note 2: G = inputs G1 and G2 connected together

Logic Diagram

Inputs Outputs

Select

Strobe

(0) (1) (2) (3) (4) (5) (6) (7)

Or Data

C (Note 1) B A G (Note 2) 2Y0 2Y1 2Y2 2Y3 1Y0 1Y1 1Y2 1Y3

X XX H HHHHHHHH

L LL L LHHHHHHH

L LH L HLHHHHHH

L HL L HHLHHHHH

L HH L HHHLHHHH

H LL L HHHHLHHH

H LH L HHHHHLHH

H HL L HHHHHHLH

H HH L HHHHHHHL

Inputs Outputs

Select Strobe Data

1Y0 1Y1 1Y2 1Y3

BA G1 C1

XX H X HHHH

LL L H LHHH

LH L H H L H H

HL L H H H L H

HH L H H H H L

XX X L HHHH

Inputs Outputs

Select Strobe Data

2Y02Y12Y22Y3

BA G2 C2

XX H X HHHH

LL L L L H H H

LH L L H L H H

HL L L H H L H

HH L L H H H L

XX X H HHHH

Loading...

Loading...