Fairchild Semiconductor DM74LS154WMX, DM74LS154WM, DM74LS154N Datasheet

© 2000 Fairchild Semiconductor Corporation DS006394 www.fairchildsemi.com

August 1986

Revised March 2000

DM74LS154 4-Line to 16-Line Decoder/Demultiplexer

DM74LS154

4-Line to 16-Line Decoder/Demultiplexer

General Description

Each of these 4-line-to-16-line decoders utilize s TTL circuitry to decode four bina ry-coded inputs into one of sixteen mutually exclusive outputs when both the strobe

inputs, G1 and G2, ar e LOW. The demultiplexing f unction

is performed by using the 4 input lines to address the output line, passing data from one of the strobe inputs with the

other strobe input LOW. When either strobe input i s HIGH,

all outputs are HIGH. These demultiplexers are ideally

suited for implementing hi gh-performan ce memory decoders. All inputs are buffer ed and input clamp ing diodes are

provided to minimiz e transmiss ion-line effects and th ereby

simplify system design.

Features

■ Decodes 4 binary-coded inp uts into one of 16 mutuall y

exclusive outputs

■ Performs the demultiplexing function by distributing data

from one input line to any one of 16 outputs

■ Input clamping diodes simplify system design

■ High fan-out, low-impedance, totem-pole outputs

■ Typical propagation delay

3 levels of logic 23 ns

Strobe 19 ns

■ Typical power dissipation 45 mW

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

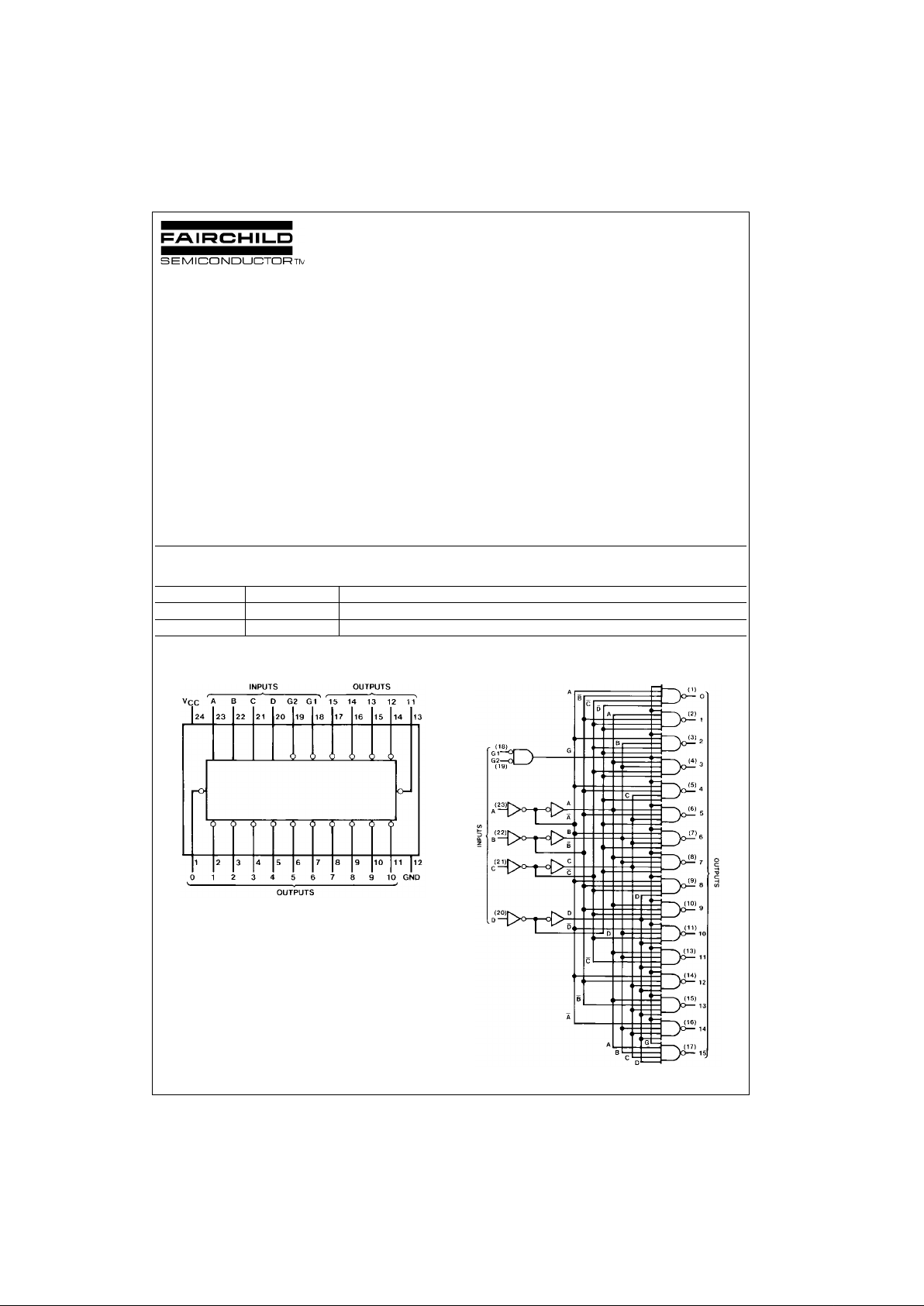

Connection Diagram Logic Diagram

Order Number Package Number Package Description

DM74LS154WM M24B 24-Lead Small Outline Integrated Circuit (SOIC), JED EC MS-013, 0.300 Wide

DM74LS154N N24A 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.600 Wide

www.fairchildsemi.com 2

DM74LS154

Function Table

H = HIGH Level

L = Low Level

X = Don’t Care

Inputs Outputs

G1G2DCBA0123456789101112131415

L L L LL LLHHHHHHHHH H H H H H H

L L L LLHHLHHHHHHHH H H H H H H

L L L LHLHHLHHHHHHH H H H H H H

L L L LHHHHHLHHHHHH H H H H H H

L L LHLLHHHHLHHHHH H H H H H H

L L LHLHHHHHHLHHHH H H H H H H

L L LHHLHHHHHHLHHH H H H H H H

L L LHHHHHHHHHHLHH H H H H H H

L L HL LLHHHHHHHHLH H H H H H H

L L HL LHHHHHHHHHHL H H H H H H

L L HLHLHHHHHHHHHH L H H H H H

L L HLHHHHHHHHHHHH H L H H H H

L L HHL LHHHHHHHHHH H H L H H H

L L HHLHHHHHHHHHHH H H H L H H

L L HHHLHHHHHHHHHH H H H H L H

L L HHHHHHHHHHHHHH H H H H H L

L H XXXXHHHHHHHHHH H H H H H H

H L XXXXHHHHHHHHHH H H H H H H

H H XXXXHHHHHHHHHH H H H H H H

Loading...

Loading...