© 2000 Fairchild Semiconductor Corporation DS006368 www.fairchildsemi.com

June 1986

Revised March 2000

DM74LS109A Dual Positive-Edge-Triggered J-K Flip-Flop with Preset, Clear, and Complementary Outputs

DM74LS109A

Dual Positive-Edge-Triggered J-K

Flip-Flop with

Preset, Clear, and Complementary Outputs

General Description

This device contains two independent positive-edge-triggered J-K

flip-flops with complementary outputs. The J and

K

data is accepted by the flip-fl op on the r ising edge o f the

clock pulse. The triggering occur s at a voltage lev el and is

not directly related to t he transition time o f the rising ed ge

of the clock. The data on the J and K

inputs may be

changed while the cloc k is HIG H or LOW as lon g as set up

and hold times are no t violated. A low logic level on the

preset or clear inputs will set or reset the outputs regardless of the logic levels of the other inputs.

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

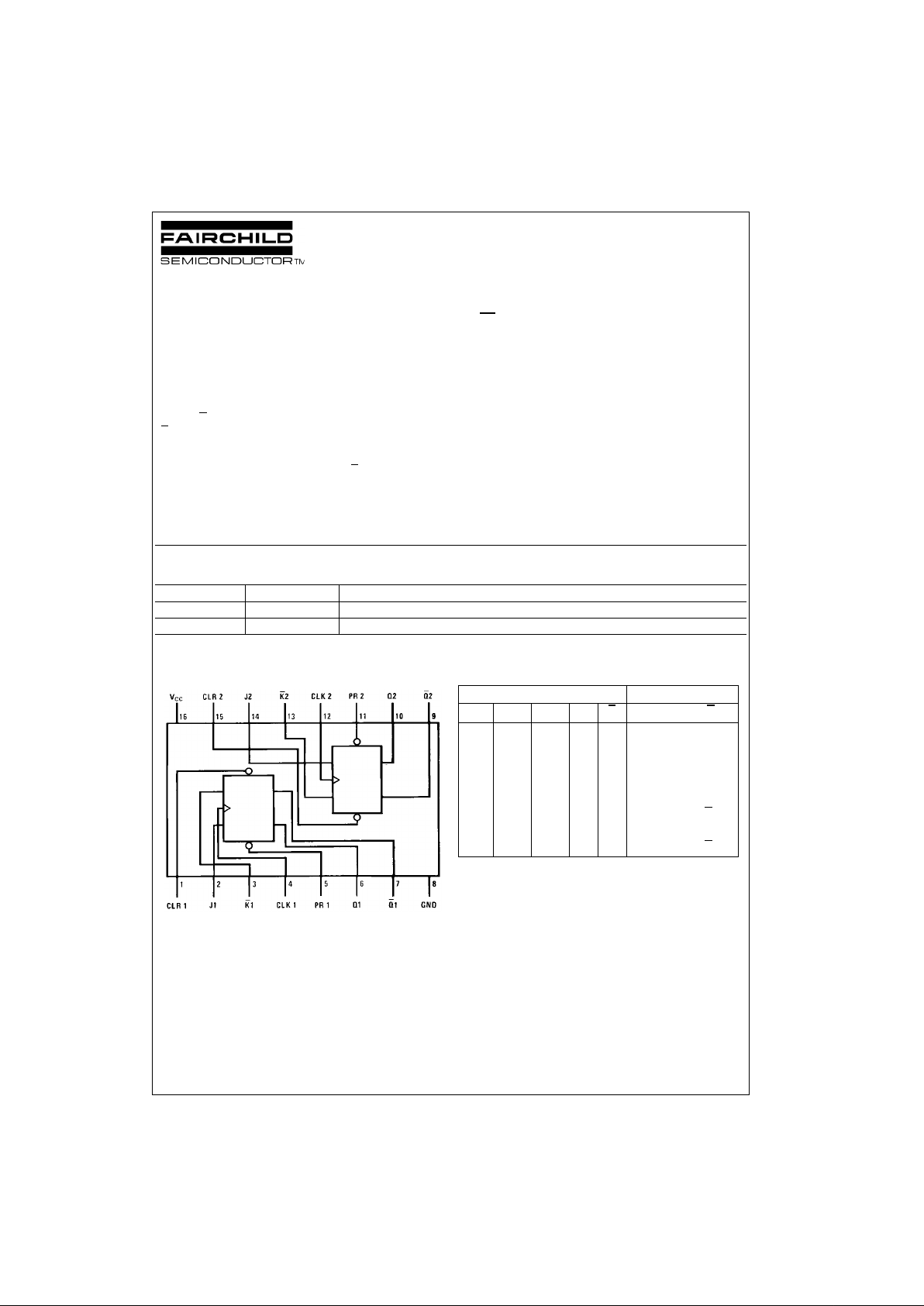

Connection Diagram Function Table

H = HIGH Logic Level

L = LOW Logic Level

X = Either LOW or HIGH Logic Level

↑ = Rising Edge of Pulse

Q0 = The out put logic lev el of Q be fore the in dica ted input con ditio ns were

established.

Toggle = Each output changes to the complement of its previous level on

each active transition of the clock pulse.

Note 1: This configuration i s no nst able; tha t is, i t will n ot pe rsis t whe n p reset and/or clear inputs return to their inactive (HIGH) state.

Order Number Package Number Package Description

DM74LS109AM M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

DM74LS109AN N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Inputs Outputs

PR CLR CLK J K

QQ

LHXXX H L

HLXXX L H

L L X X X H (Note 1) H (Note 1)

HH ↑ LL L H

HH ↑ H L Toggle

HH ↑ LH Q

0

Q

0

HH ↑ HH H L

HH LXX Q

0

Q

0

www.fairchildsemi.com 2

DM74LS109A

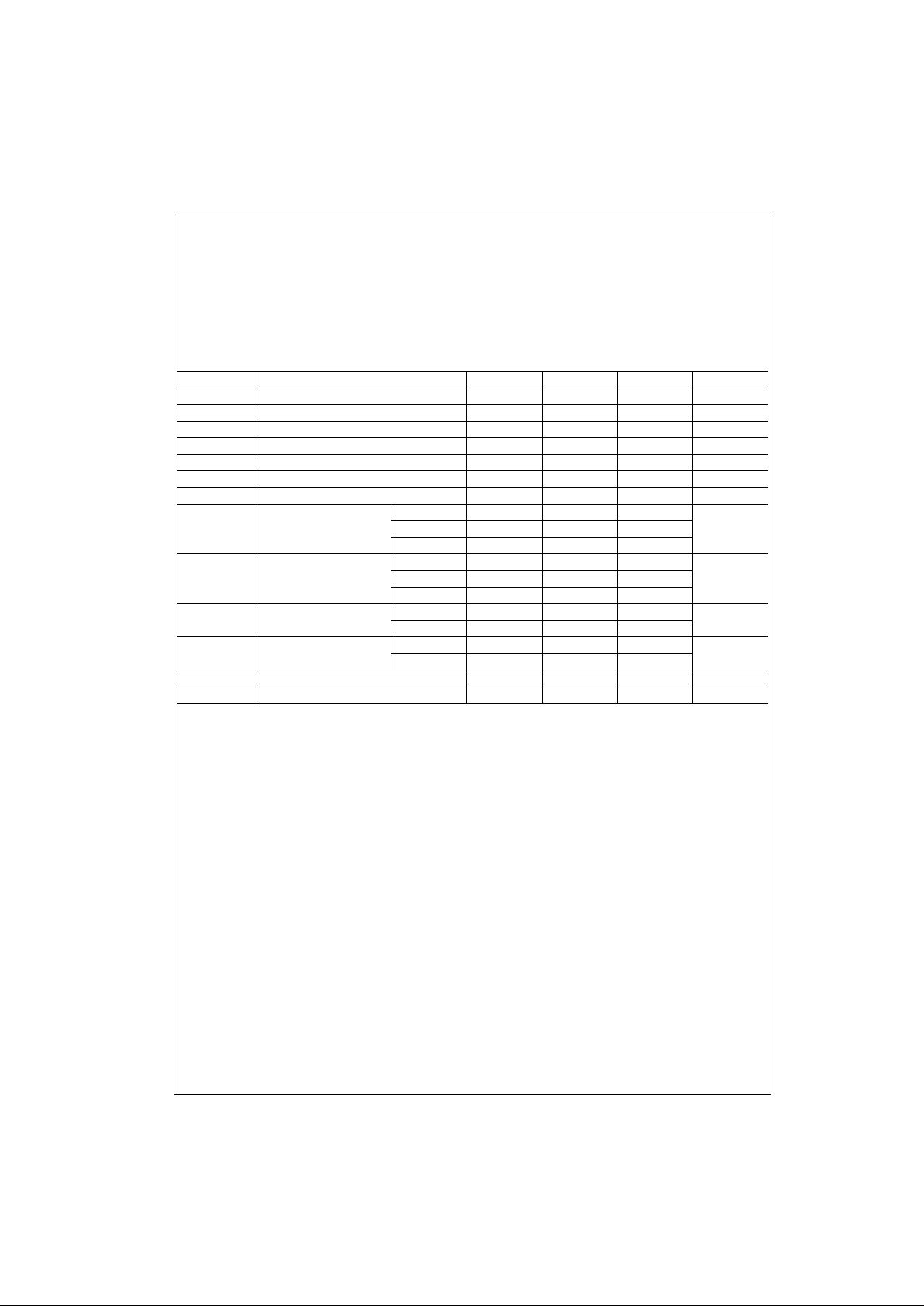

Absolute Maximum Ratings(Note 2)

Note 2: The “Absolute Maximum Ratin gs” are those v alues beyon d which

the safety of the dev ice cannot be guaranteed. T he device sh ould not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The “Recommend ed O peratin g Cond itions” t able w ill defin e the co ndition s

for actual device operation.

Recommended Operating Conditions

Note 3: CL = 15 pF, RL = 2 kΩ, TA = 25°C and VCC = 5V.

Note 4: C

L

= 50 pF, RL = 2 kΩ, TA = 25°C and VCC = 5V.

Note 5: The symbol (↑) indicates the rising edge of the clock pulse is used fo r ref erence.

Note 6: T

A

= 25°C and VCC = 5V.

Supply Voltage 7V

Input Voltage 7V

Operating Free Air Temperature Range 0°C to +70°C

Storage Temperature Range −65°C to +150°C

Symbol Parameter Min Nom Max Units

V

CC

Supply Voltage 4.75 5 5.25 V

V

IH

HIGH Level Input Voltage 2 V

V

IL

LOW Level Input Voltage 0.8 V

I

OH

HIGH Level Output Current −0.4 mA

I

OL

LOW Level Output Current 8 mA

f

CLK

Clock Frequency (Note 3) 0 25 MHz

f

CLK

Clock Frequency (Note 4) 0 20 MHz

t

W

Pulse Width Clock HIGH 18

(Note 3) Preset LOW 15 ns

Clear LOW 15

t

W

Pulse Width Clock HIGH 25

(Note 4) Preset LOW 20 ns

Clear LOW 20

t

SU

Setup Time Data HIGH 30↑

ns

(Note 3)(Note 5) Data LOW 20↑

t

SU

Setup Time Data HIGH 35↑

ns

(Note 5)(Note 4) Data LOW 25↑

t

H

Hold Time (Note 6) 0↑ ns

T

A

Free Air Operating Temperature 0 70 °C

Loading...

Loading...