Fairchild Semiconductor DM74ALS169BN, DM74ALS169BMX, DM74ALS169BM Datasheet

© 2000 Fairchild Semiconductor Corporation DS006207 www.fairchildsemi.com

April 1984

Revised April 2000

DM74ALS169B Synchronous Four-Bit Up/Down Counters

DM74ALS169B

Synchronous Four-Bit Up/Down Counters

General Description

These synchronous p resettable counters feature an internal carry look ahe ad for c ascading in high speed count ing

applications. The DM74ALS169B is a four-bit binary up/

down counter. The carry output is decoded to prevent

spikes during normal mode of counting operation. Synchronous operation is provide d so that outputs change coincident with each other when so instructed by count enable

inputs and internal gating. This mode of operation eliminates the output counti ng spikes wh ich are norm ally associated with asynchronous (ripple clock) counters. A

buffered clock input triggers th e four flip-flops o n the rising

(positive going) edge of clock input waveform.

These counters are fully programmable; that is, the outputs

may each be preset either HIGH or LOW. The load input

circuitry allows loading with carry-enable output of cascaded counters. As loading is synchr onous, setting up a

low level at the load input disables the counte r a nd causes

the outputs to agree with the data inputs after the next

clock pulse.

The carry look-ahead circuitr y permits cascading counters

for n-bit synchronous applications without additional gating.

Both count enable inputs (P

and T) must be LOW to count.

The direction of the co unt is determ ined b y the l evel of t he

up/down input. When the input is HIGH, the counter counts

UP; when LOW, it counts DOWN . Inpu t T is fed fo rward to

enable the carry outputs. The carry output thus enabled will

produce a low level o utput pulse with a dura tion approximately equal to the high p ortion of the Q

A

output when

counting UP, and approximately equal to the low portion of

the Q

A

when counting DOWN. This low level overflow carry

pulse can be used to enable successively cascaded

stages. Transitions at the enable P

or T inputs are allowed

regardless of the level of the clock input.

The control function s for thes e counters a re fully synchr o-

nous. Changes at control inpu ts (enab le P

, enable T, load,

up/down) which modify the opera ting mode have no effect

until clocking occurs. The func tion of the counte r (whether

enabled, disabled, loading or counting) will be dictated

solely by the conditions meeting the stable setup and hold

times.

Features

■ Switching specifications at 50 pF

■ Switching specifications guaranteed over full tempera-

ture and V

CC

range

■ Advanced oxide-isolated, ion-implanted Schottky TTL

process

■ Functionally and pin-for-pin compatible with Schottky

and low power Schottky TTL counterpart

■ Improved AC performa nce over S cho ttky a nd low p ower

Schottky counterparts

■ Synchronously programmable

■ Internal look ahead for fast counting

■ Carry out put for n-bit cascading

■ Synchronous counting

■ ESD inputs

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

Order Number Package Number Package Description

DM74ALS169BM M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

DM74ALS169BN N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

www.fairchildsemi.com 2

DM74ALS169B

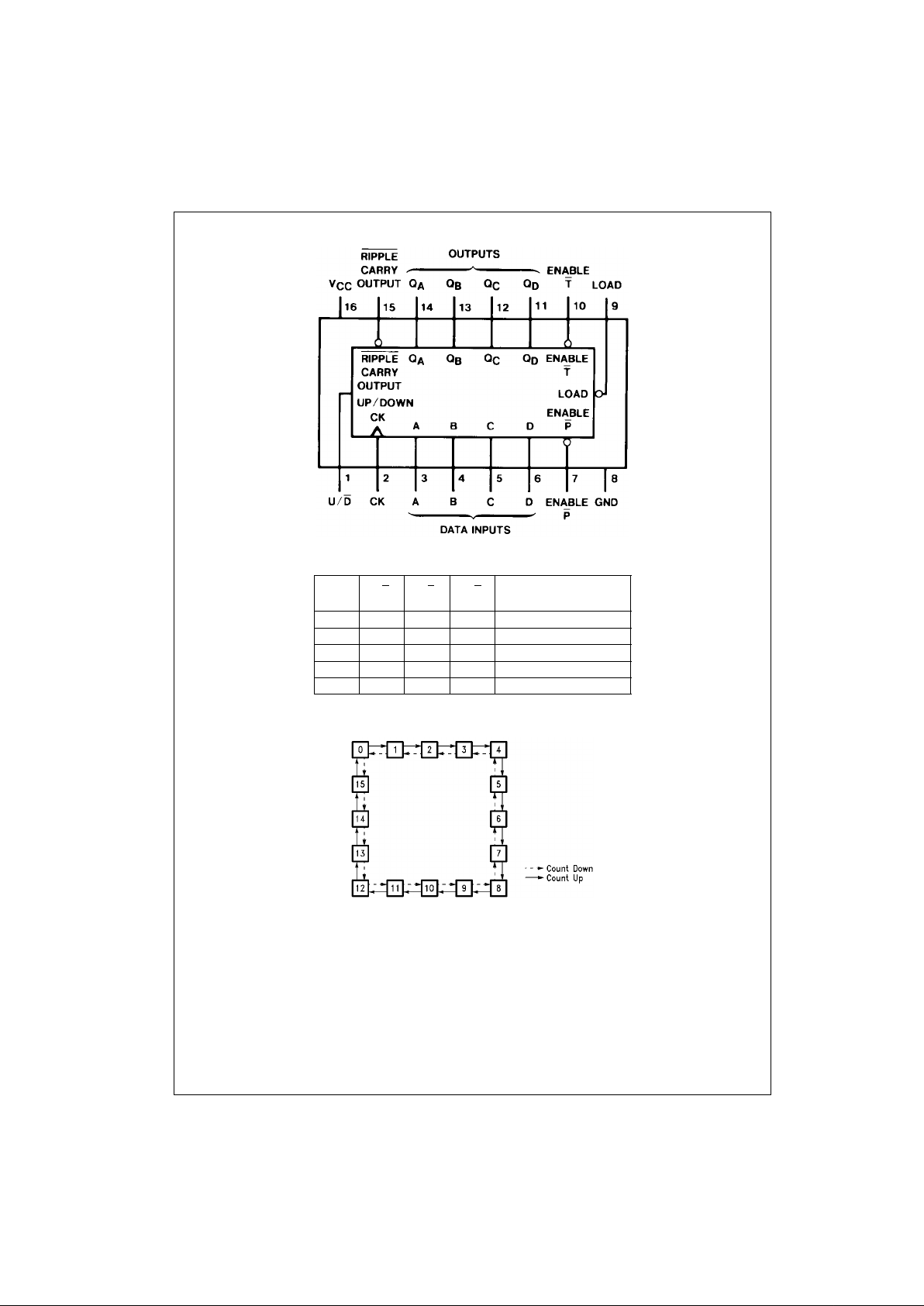

Connection Diagram

Mode Select Table

State Diagram

LOAD EP ET U/D

Action on Rising

Clock Edge

LXXXLoad (P

n

→ Qn)

H L L H Count Up (Increment)

H L L L Count Down (Decrement)

H H X X No Change (Hold)

H X H X No Change (Hold)

3 www.fairchildsemi.com

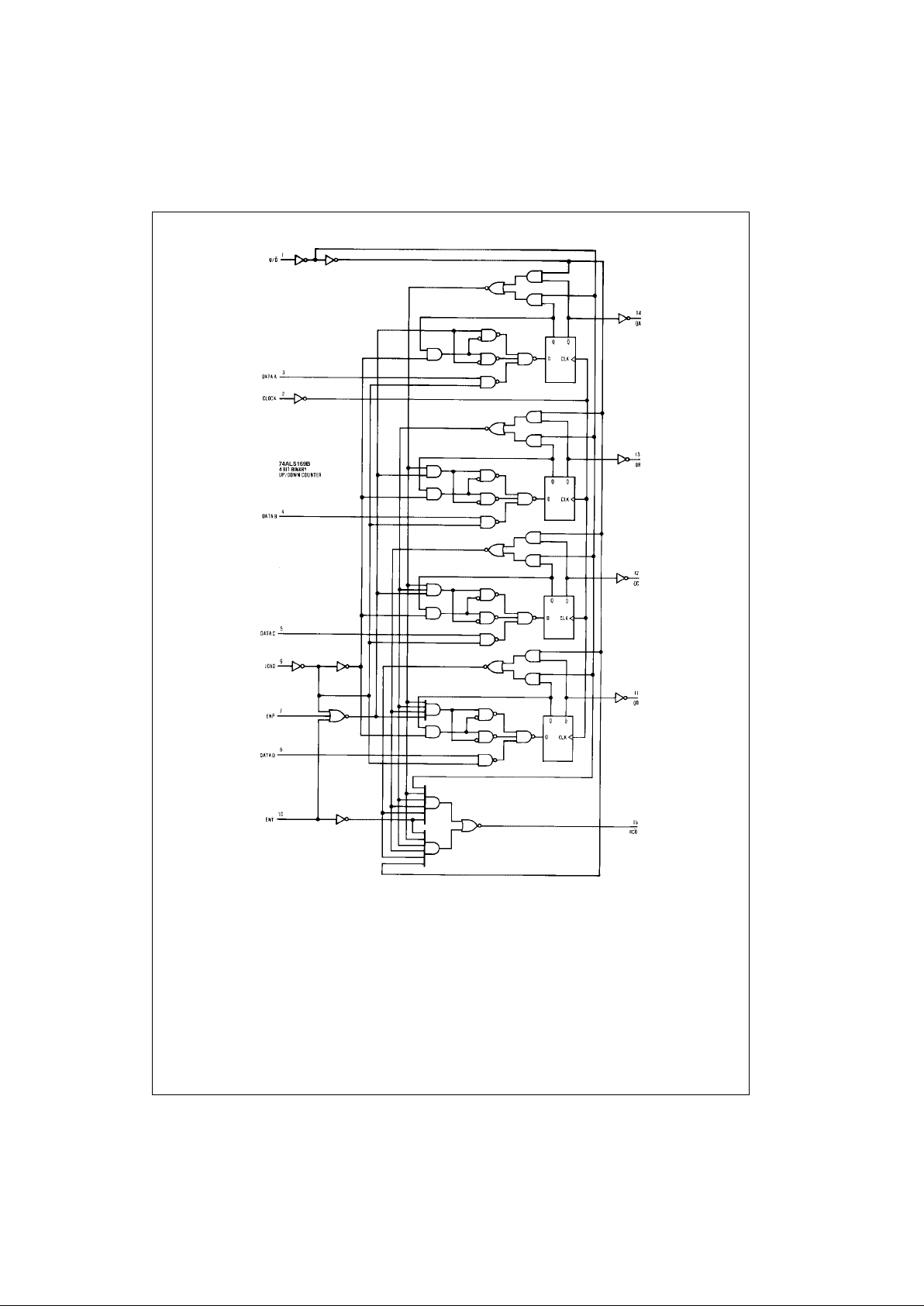

DM74ALS169B

Logic Diagram

Loading...

Loading...