Fairchild Semiconductor 74ACTQ563PC Datasheet

January 1990

Revised December 1998

74ACTQ563

Quiet Series Octal Latch with 3-STATE Outputs

74ACTQ563 Quiet Series Octal Latch wit h 3-STATE Outputs

General Description

The ACTQ563 is a high speed octal latch with buffered

common Latch Enable (LE) an d buffered common Output

Enable (OE

to the ACTQ573, but with inverted outp uts. The ACTQ563

utilizes Fairchild FACT Quiet Series technology to guarantee quiet output switching and improved dynamic threshold performance. FACT Quiet Series features GTO

output control and undershoot corrector in addition to a

split ground bus for superior performance.

) inputs. The ACTQ563 is function ally identical

Features

■ ICC and IOZ reduced by 50%

■ Guaranteed simultaneous switching noise level and

dynamic threshold performance

■ Guaranteed pin-to-pin skew AC performance

■ Improved latch-up immunity

■ Inputs and outputs on opposi te sides of package allow

easy interface with microprocessors

■ Outputs source/sink 24 mA

■ Faster prop delays than standard ACT563

■ Functionally iden tical to the ACTQ573 but w ith inverted

outputs

Ordering Code:

Order Number Package Number Package Description

74ACTQ563PC N20A 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

Device also available in Tape and Reel. Specify by appendin g s uf f ix let t er “X” to the ordering co de.

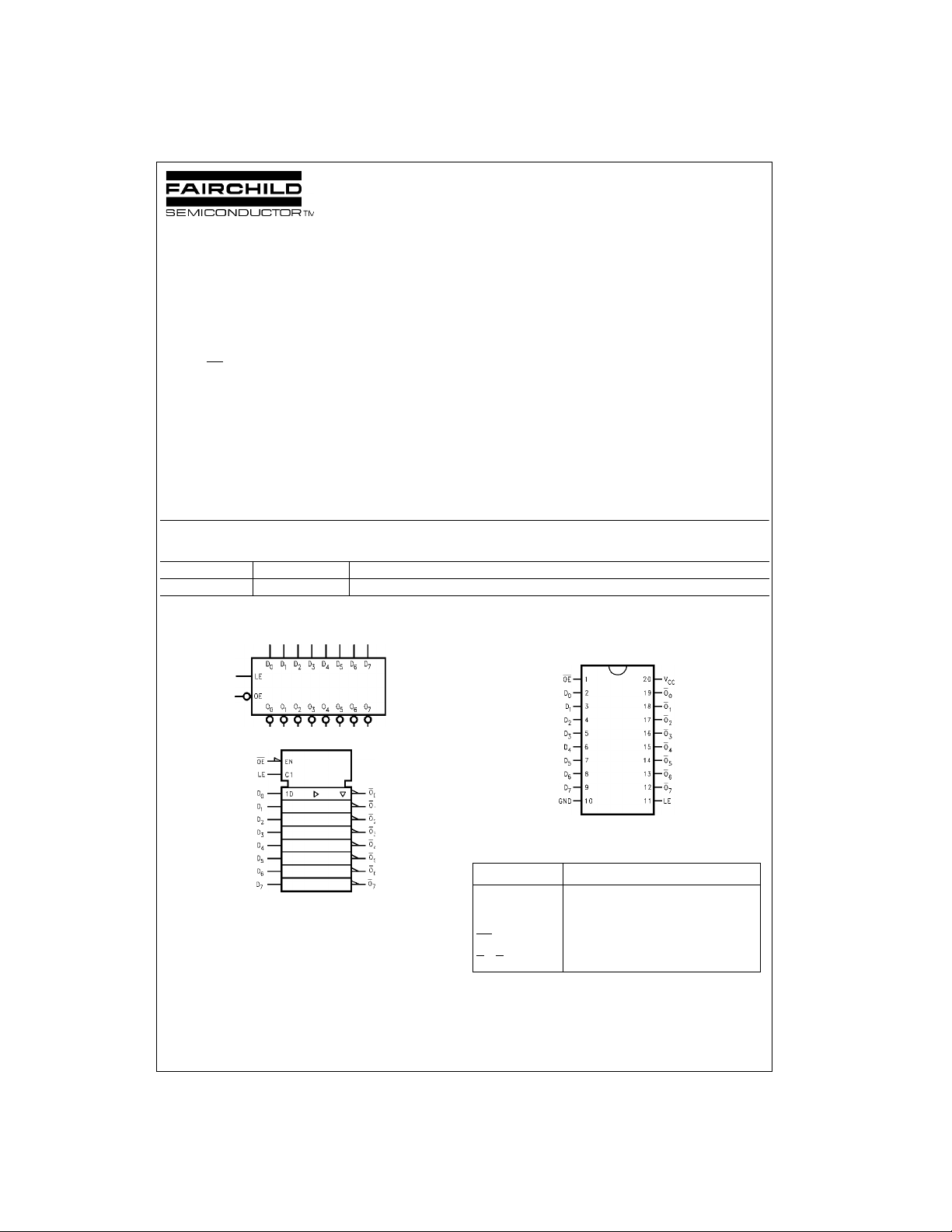

Logic Symbols

IEEE/IEC

Connection Diagram

Pin Assignment for DIP

Pin Descriptions

Pin Names Description

D

0–D7

LE Latch Enable Input

OE

O

0–O7

FACT, Quiet Series, FACT Quiet Series and GTO are trademark s of Fairchild Semiconductor Co rporation.

© 1999 Fairchild Semiconductor Corporation DS010631.prf www.fairchildsemi.com

Data Inputs

3-STATE Output Enable Input

3-STATE Latch Outputs

Functional Description

The ACTQ563 contains eig ht D-type lat ches with 3-STATE

complementar y o utp uts. Wh en the Latc h E nable (L E ) inp ut

is HIGH, data on the D

condition the latches are transparent, i.e., a latch output will

74ACTQ563

change state each time its D input changes. When LE is

LOW the latches store the information that was present on

inputs enters the latches. In this

n

Function Table

Inputs Internal Outputs Function

LE D Q O

OE

H X X X Z High-Z

H H L H Z High-Z

H H H L Z High-Z

H L X NC Z Latched

L H L H H Transparent

L H H L L Transparent

H = HIGH Voltage Level

L = LOW Voltage Lev el

X = Immaterial

Z = High Impedance

NC = No Change

L L X NC NC Latched

Logic Diagram

the D inputs a setup time preceding the HIGH-to-LOW transition of LE. The 3-STATE buffers are controlled by the

Output Enable (OE) input. When OE is LOW, the buffers

are in the bi-state m od e. When OE

in the high impedance mode but that does not interfere with

entering new data into the latches.

is HIGH the buffers are

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate p ropagation delays.

www.fairchildsemi.com 2

Absolute Maximum Ratings(Note 1)

Supply Voltage (VCC) −0.5V to +7.0V

DC Input Diode Current (I

= −0.5V −20 mA

V

I

= VCC + 0.5V +20 mA

V

I

DC Input Voltage (V

DC Output Diode Current (I

= −0.5V −20 mA

V

O

= VCC + 0.5V +20 mA

V

O

DC Output Voltage (V

DC Output Source

or Sink Current (I

or Ground Current

DC V

CC

per Output Pin (I

Storage Temperature (T

DC Latchup Source

)

IK

) −0.5V to VCC + 0.5V

I

O

CC

)

OK

) −0.5V to VCC + 0.5V

O

) ± 50 mA

or I

) ± 50 mA

GND

) −65°C to +150°C

STG

Junction Temperature (T

PDIP 140°C

Recommended Operating

Conditions

Supply Voltage (V

Input Voltage (V

Output Voltage (VO)0V to V

Operating Temperature (TA) −40°C to +85°C

Minimum Input Edge Rate ∆V/∆t 125 mV/ns

from 0.8V to 2.0V

V

IN

@ 4.5V, 5.5V

V

CC

Note 1: Absolute maximum ratings are those values beyond which damage

to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power

supply, temperature, and output/in put loading variables. Fairchild does n ot

recommend operat ion of FACT circuits outside databoo k specifications.

)

J

) 4.5V to 5.5V

CC

)0V to V

I

or Sink Current ± 300 mA

DC Electrical Characteristics

V

Symbol Parameter

V

Minimum HIGH Level 4.5 1.5 2.0 2.0 V V

IH

Input Voltage 5.5 1.5 2.0 2.0 or VCC − 0.1V

V

Maximum LOW Level 4.5 1.5 0.8 0.8 V V

IL

Input Voltage 5.5 1.5 0.8 0.8 or VCC − 0.1V

V

Minimum HIGH Level 4.5 4.49 4.4 4.4 V I

OH

Output Voltage 5.5 5.49 5.4 5.4

V

Maximum LOW Level 4.5 0.001 0.1 0.1 I

OL

Output Voltage 5.5 0.001 0.1 0.1

I

Maximum Input Leakage Current 5.5 ± 0.1 ± 1.0 µAVI = VCC, GND

IN

I

Maximum 3-STATE 5.5 ± 0.25 ± 2.5 µAVI = VIL, V

OZ

Leakage Current VO = VCC, GND

I

Maximum ICC/Input 5.5 0.6 1.5 mA VI = VCC − 2.1V

CCT

I

Minimum Dynamic 5.5 75 mA V

OLD

I

Output Current (Note 3) 5.5 −75 mA V

OHD

I

Maximum Quiescent Supply Current 5.5 4.0 40.0 µAVIN = VCC or GND

CC

V

Quiet Output 5.0 1.1 1.5 V Figure 1, Figure 2

OLP

Maximum Dynamic V

V

Quiet Output 5.0 −0.6 −1.2 V Figure 1, Figure 2

OLV

Minimum Dynamic V

V

Minimum HIGH Level

IHD

Dynamic Input Voltage

V

Maximum LOW Level

ILD

Dynamic Input Voltage

Note 2: All outputs loaded; thresholds on input associated with ou t put under test.

Note 3: Maximum test duration 2.0 ms, one output loaded at a time.

Note 4: DIP package.

Note 5: Max number of ou t puts defined as (n). Da ta inputs are driven 0V to 3V. One output @ GND.

OL

OL

CC

(V) Typ Guaranteed Limits

4.5 3.86 3.76 V IOH = −24 mA

5.5 4.86 4.76 IOH = − 24 mA (Note 2)

4.5 0.36 0.44 V IOL = 24 mA

5.5 0.36 0.44 IOL = 24 mA (Note 2)

5.0 1.9 2.2 V (Note 4)(Note 6)

5.0 1.2 0.8 V (Note 4)(Note 6)

TA = +25°CTA = −40°C to +85°C

Units Conditions

= 0.1V

OUT

= 0.1V

OUT

= − 50 µA

OUT

VIN = VIL or V

= 50 µA

OUT

VIN = VIL or V

IH

= 1.65V Max

OLD

= 3.85V Min

OHD

(Note 4)(Note 5)

(Note 4)(Note 5)

74ACTQ563

CC

CC

IH

IH

3 www.fairchildsemi.com

Loading...

Loading...