Fairchild Semiconductor 74ACT161SJX, 74ACT161SJ, 74ACT161SCX, 74ACT161SC, 74ACT161PC Datasheet

...

© 1999 Fairchild Semiconductor Corporation DS009931 www.fairchildsemi.com

November 1988

Revised November 1999

74AC161 • 74ACT161 Synchronous Presettable Binary Counter

74AC161 • 74ACT161

Synchronous Presettable Binary Counter

General Description

The AC/ACT161 are high -speed synchronous modulo-16

binary counters. They are synchronously presettable for

application in prog rammable dividers an d have two types

of Count Enable inputs plus a Terminal Count output for

versatility in forming synchronous multistage counters. The

AC/ACT161 has an asynchro nous Master Reset input that

overrides all other inputs and forces the outputs LOW.

Features

■ ICC reduced by 50%

■ Synchronous counting and loading

■ High-speed synchronous expan sion

■ Typical count rate of 125 MHz

■ Outputs source/sink 24 mA

■ ACT161 has TTL-compatible inputs

Ordering Code:

Device also available in Tape and Reel. Specify by appending su ffix le tter “X” to the ordering code.

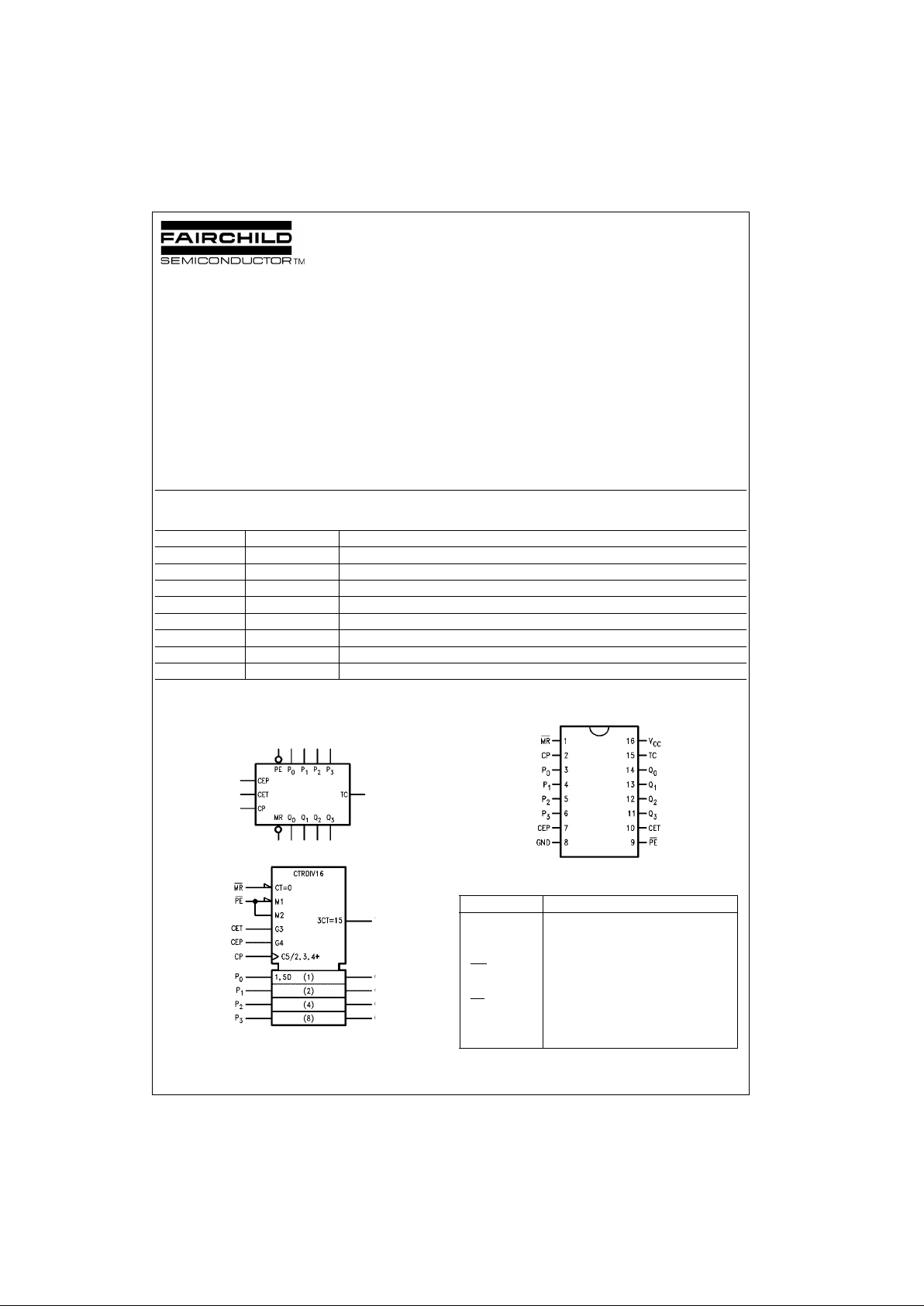

Logic Symbols

IEEE/IEC

Connection Diagram

Pin Descriptions

FACT is a trademark of Fairchild Semiconductor Corporation.

Order Number Package Number Package Description

74AC161SC M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body

74AC161SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74AC161MTC MTC16 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

74AC161PC N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

74ACT161SC M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150” Narrow Body

74ACT161SJ M16D 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

74ACT161MTC MTC16 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

74ACT161PC N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” Wide

Pin Names Description

CEP Count Enable Parallel Input

CET Count Enable Trickle Input

CP Clock Pulse Input

MR

Asynchronous Master Reset Input

P

0–P3

Parallel Data Inputs

PE

Parallel Enable Inputs

Q

0–Q3

Flip-Flop Outputs

TC Terminal Count Output

www.fairchildsemi.com 2

74AC161 • 74ACT161

Functional Description

The AC/ACT161 count in modulo-16 binary sequence.

From state 15 (HHHH) they increment to state 0 (LLLL).

The clock inputs of all flip-flops are driven in parallel

through a clock buffer. Thus all changes o f the Q outputs

(except due to Master Reset of the AC/ACT161) occur as a

result of, and synchron ous with, the LOW-to-HIGH transition of the CP input signal. The circu its have four fundamental modes of operation, in order of precedence:

asynchronous reset , parallel load, coun t-up and hold. Five

control inputs—Master Reset, Parallel Enable (PE

), Count

Enable Parallel (C EP) and Count Enable Trickle (CET)—

determine the mode of operation, as shown in the Mode

Select Table. A LOW signal on MR

overrides all other

inputs and asynchronousl y fo rces al l outp uts LOW. A LOW

signal on PE

overrides counting and allows information on

the Parallel Data (P

n

) inputs to be loaded in to the f lip-flo ps

on the next rising edge of CP. With PE

and MR HIGH, CEP

and CET permit c o un ti n g wh en b oth ar e H IGH . Co nv ers e l y,

a LOW signal on either CEP or CET inhibits counting.

The AC/ACT161 use D-type edge-triggere d flip-flops and

changing the PE

, CEP, and CET inputs when the CP is in

either state does not cause errors, provided that the recommended setup and hold times, with respect to the rising

edge of CP, are observe d.

The Terminal Count (TC) output is HIGH when CET is

HIGH and counter is in state 15. To implement synchronous multistage counters, the TC outputs can be used with

the CEP and CET inputs in two different ways.

Figure 1 shows the connect ions for simple ripple carry, in

which the clock period must be longer than the CP to TC

delay of the first stage, plus the cumulative CET to TC

delays of the intermediate stages, plus the CET to CP

setup time of the last stage. This total delay plus setup time

sets the upper limi t on clock frequency. For faster clock

rates, the carry lo okahead connectio ns shown in Figure 2

are recommended. In t hi s sche me th e ri p ple de l ay thr oug h

the intermediate s tages commences with the same clock

that causes the first stage to tick over fr om max to min in

the Up mode, or min to max in the Down mode, to start its

final cycle. Since this final c ycle requ ires 16 clo cks to com plete, there is plenty of time for the ripple to progress

through the intermediate stages. The critical timing that lim-

its the clock period is th e CP to TC

delay of the first stage

plus the CEP

to CP setup time of the last stage. The TC

output is subject to d ecoding spikes due to internal race

conditions and is th erefore n ot recomm ended fo r use as a

clock or asynchronous reset for flip-flops, registers or

counters.

Logic Equations: Count Enable = CEP • CET • PE

TC = Q0 • Q1 • Q2 • Q3 • CET

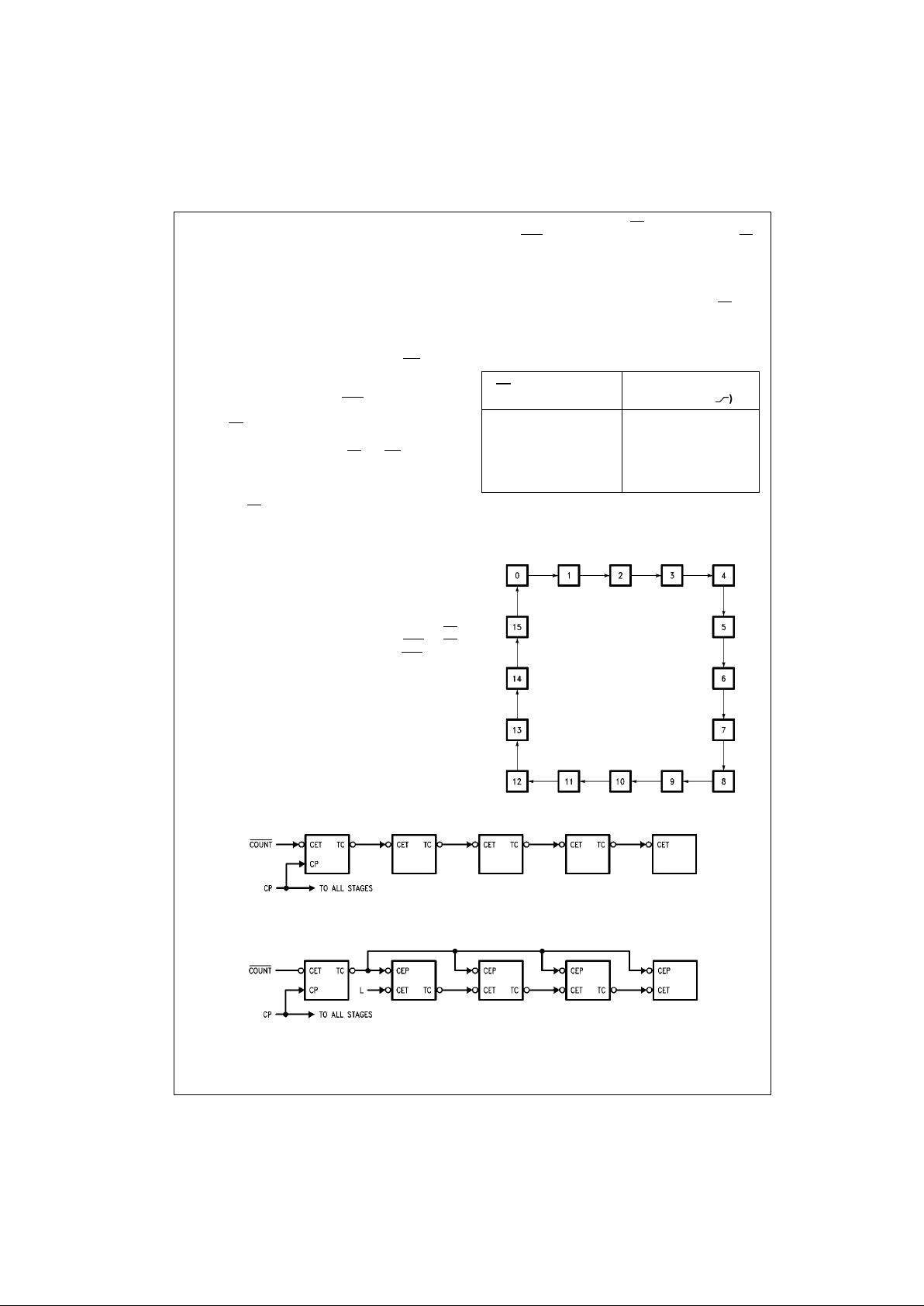

Mode Select Table

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

State Diagram

FIGURE 1. Multistage Counter with Ripple Carry

FIGURE 2. Multistage Counter with Lookahead Carry

PE

CET CEP

Action on the Rising

Clock Edge (

)

X X X Reset (Clear)

L X X Load (P

n→Qn

)

H H H Count (Increment)

H L X No Change (Hold)

H X L No Change (Hold)

3 www.fairchildsemi.com

74AC161 • 74ACT161

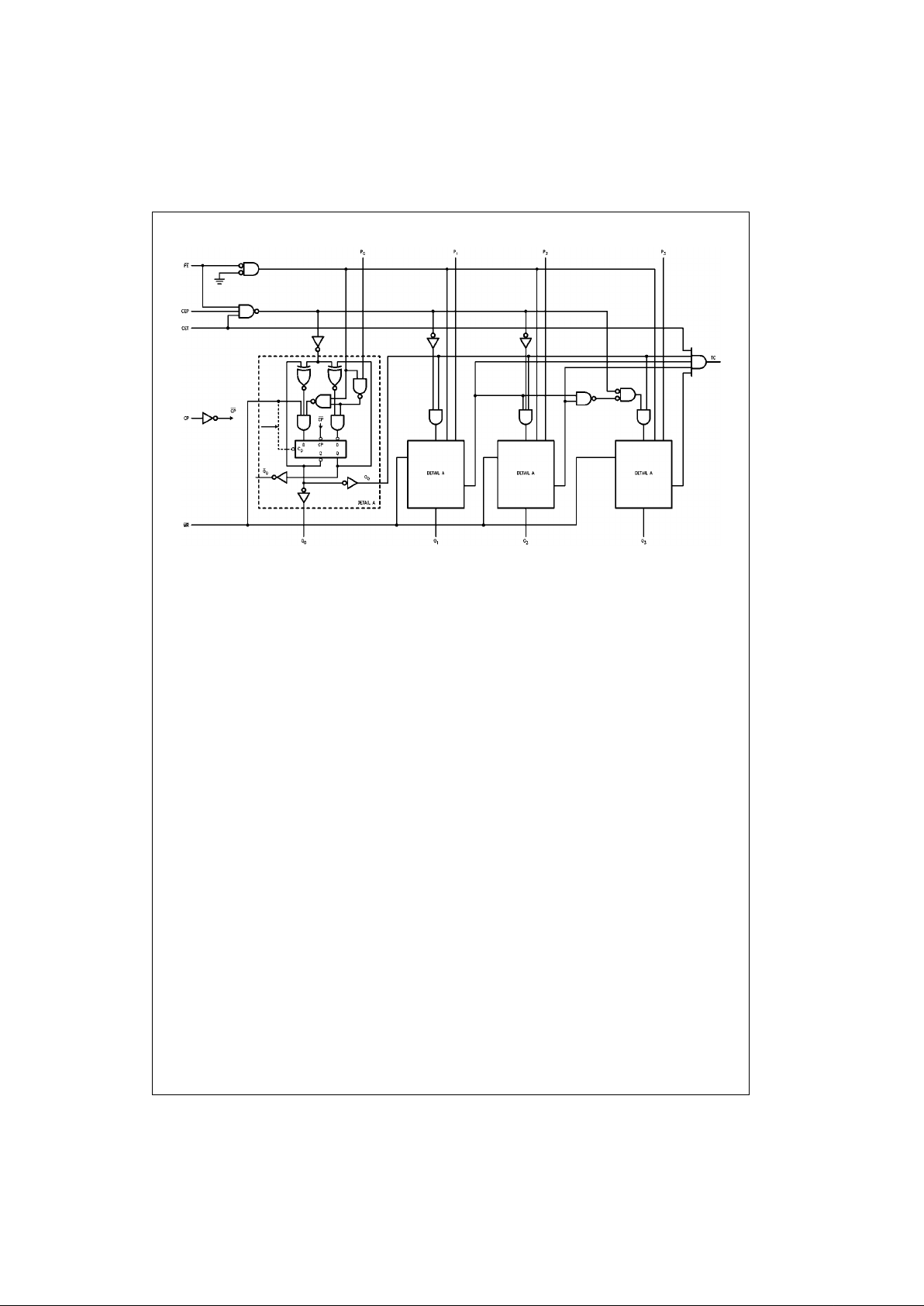

Block Diagram

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.fairchildsemi.com 4

74AC161 • 74ACT161

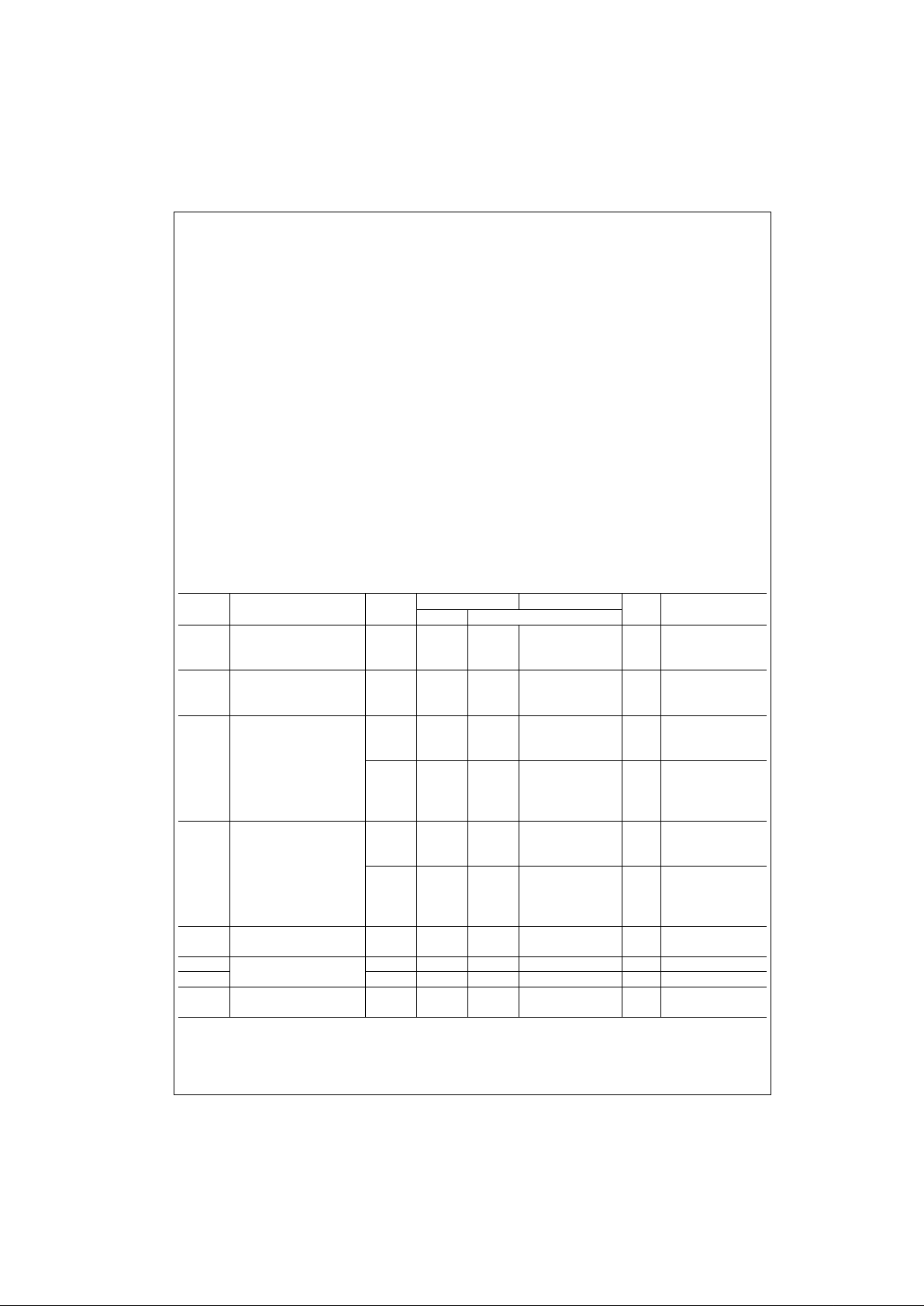

Absolute Maximum Ratings(Note 1) Recommended Operating

Conditions

Note 1: Absolute maximum ratings are those values beyond which damage

to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power

supply, temperature, and ou tput/inp ut loadi ng varia bles. Fairchild does no t

recommend operat ion of FACT circuits outside da t abook specifications.

DC Electrical Characteristics for AC

Note 2: All outputs loaded; thresholds on input assoc iat ed with output under tes t.

Note 3: Maximum test duratio n 2. 0 ms, one output loaded at a time.

Note 4: I

IN

and ICC @ 3.0V are guaranteed to be less than or equa l to th e respective limit @ 5.5V VCC.

Supply Voltage (VCC) −0.5V to +7.0V

DC Input Diode Current (I

IK

)

V

I

= −0.5V −20 mA

V

I

= VCC + 0.5V +20 mA

DC Input Voltage (V

I

) −0.5V to VCC + 0.5V

DC Output Diode Current (I

OK

)

V

O

= −0.5V −20 mA

V

O

= VCC + 0.5V +20 mA

DC Output Voltage (V

O

) −0.5V to VCC + 0.5V

DC Output Source

or Sink Current (I

O

) ±50 mA

DC V

CC

or Ground Current

per Output Pin (I

CC

or I

GND

) ±50 mA

Storage Temperature (T

STG

) −65°C to +150°C

Junction Temperature (T

J

)

PDIP 140°C

Supply Voltage (V

CC

)

AC 2.0V to 6.0V

ACT 4.5V to 5.5V

Input Voltage (V

I

) 0V to V

CC

Output Voltage (VO) 0V to V

CC

Operating Temperature (TA) −40°C to +85°C

Minimum Input Edge Rate (∆V/∆t)

AC Devices

V

IN

from 30% to 70% of V

CC

VCC @ 3.3V, 4.5V, 5.5V 125 mV/ns

Minimum Input Edge Rate (∆V/∆t)

ACT Devices

V

IN

from 0.8V to 2.0V

V

CC

@ 4.5V, 5.5V 125 mV/ns

Symbol Parameter

V

CC

TA = +25°C TA = −40°C to +85°C

Units Conditions

(V) Typ Guaranteed Limits

V

IH

Minimum HIGH Level 3.0 1.5 2.1 2.1 V

OUT

= 0.1V

Input Voltage 4.5 2.25 3.15 3.15 V or VCC − 0.1V

5.5 2.75 3.85 3.85

V

IL

Maximum LOW Level 3.0 1.5 0.9 0.9 V

OUT

= 0.1V

Input Voltage 4.5 2.25 1.35 1.35 V or VCC − 0.1V

5.5 2.75 1.65 1.65

V

OH

Minimum HIGH Level 3.0 2.99 2.9 2.9

Output Voltage 4.5 4.49 4.4 4.4 V I

OUT

= −50 µA

5.5 5.49 5.4 5.4

VIN = VIL or V

IH

3.0 2.56 2.46 IOH = −12 mA

4.5 3.86 3.76 V I

OH

= −24 mA

5.5 4.86 4.76 I

OH

= −24 mA (Note 2)

V

OL

Maximum LOW Level 3.0 0.002 0.1 0.1

Output Voltage 4.5 0.001 0.1 0.1 V I

OUT

= 50 µA

5.5 0.001 0.1 0.1

VIN = VIL or V

IH

3.0 0.36 0.44 IOL = 12 mA

4.5 0.36 0.44 V IOL = 24 mA

5.5 0.36 0.44 IOL = 24 mA (Note 2)

IIN Maximum Input

5.5 ±0.1 ±1.0 µAVI = VCC, GND

(Note 4) Leakage Current

I

OLD

Minimum Dynamic 5.5 75 mA V

OLD

= 1.65V Max

I

OHD

Output Current (Note 3) 5.5 −75 mA V

OHD

= 3.85V Min

ICC Maximum Quiescent

5.5 4.0 40.0 µA

VIN = V

CC

(Note 4) Supply Current or GND

Loading...

Loading...