Fairchild Semiconductor 100307QI, 100307QCX, 100307QC, 100307PC, 100307DC Datasheet

...

© 2000 Fairchild Semiconductor Corporation DS010582 www.fairchildsemi.com

August 1989

Revised August 2000

100307 Low Power Quint Exclusive OR/NOR Gate

100307

Low Power Quint Exclusive OR/NOR Gate

General Description

The 100307 is mon olithic quint exclu sive-OR/NOR gate.

The Function output is the w ire -O R of all fi ve ex cl usive -OR

outputs. All inputs have 50 k

Ω pull-down resistors.

Features

■ Low Power Operation

■ 2000V ESD protection

■ Pin/function compatible with 100107

■ Voltage compensated operating range

= −4.2V to −5.7V

■ Available to industrial grade temperature range

(PLCC package only)

Ordering Code:

Devices also availab le in Tape and Reel. Specify by appending th e s uffix let t er “X” to the ordering code.

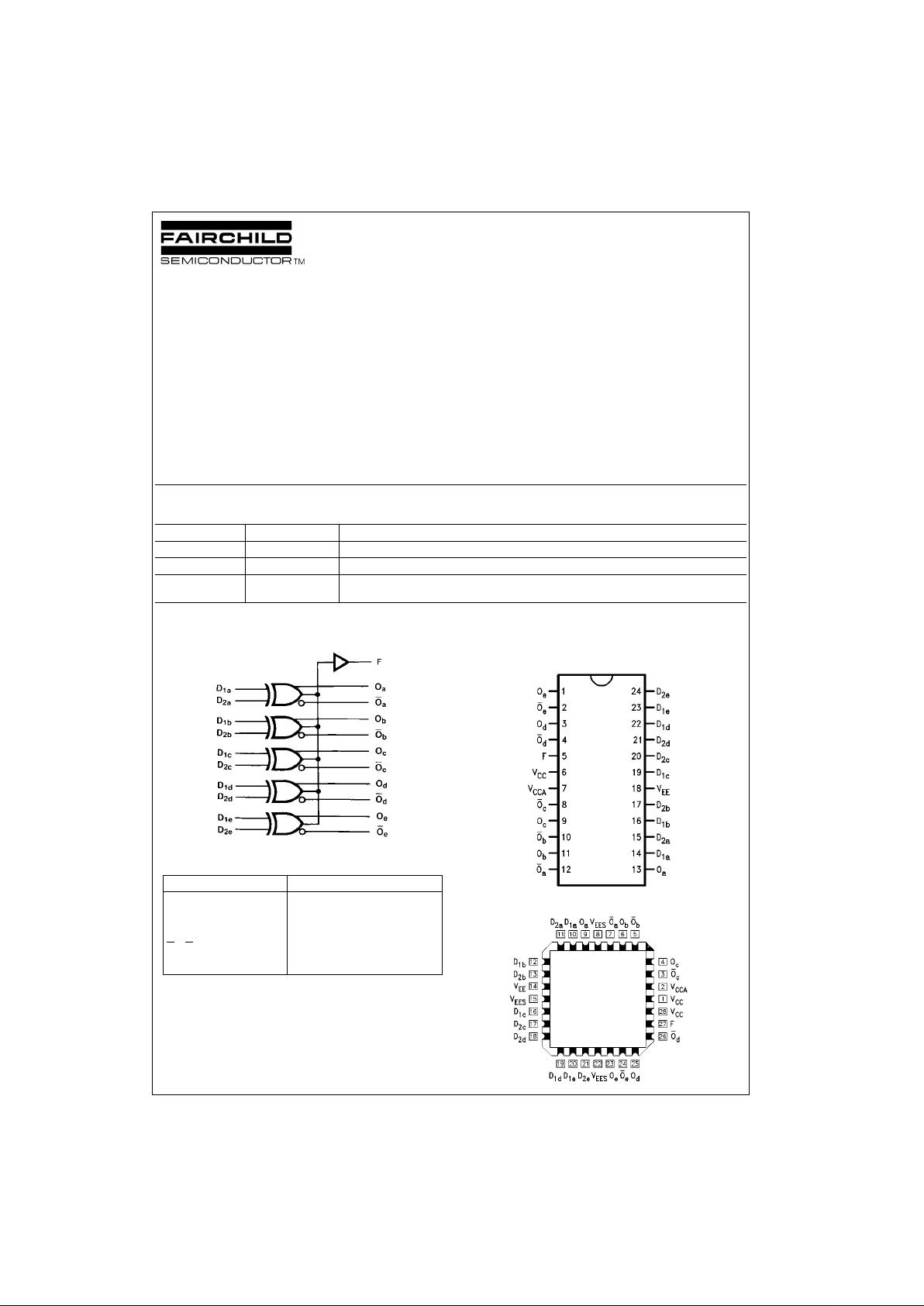

Logic Symbol

Pin Descriptions

Logic Equation

Connection Diagrams

24-Pin DIP

28-Pin PLCC

Order Number Package Number Package Description

1000307PC N24E 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.400 Wide

1000307QC V28A 28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square

1000307QI V28A 28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square

Industrial Temperature Range (

−40°C to +85°C)

Pin Names Description

D

na–Dne

Data Inputs

F Function Output

O

a–Oe

Data Outputs

O

a–Oe

Complementary

Data Outputs

F

= (D

1a

⊕ D2a) + (D1b ⊕ D2b) + (D1c ⊕ D2c) +

(D

1d

⊕ D

2d

) + (D1e ⊕ D2e).

www.fairchildsemi.com 2

100307

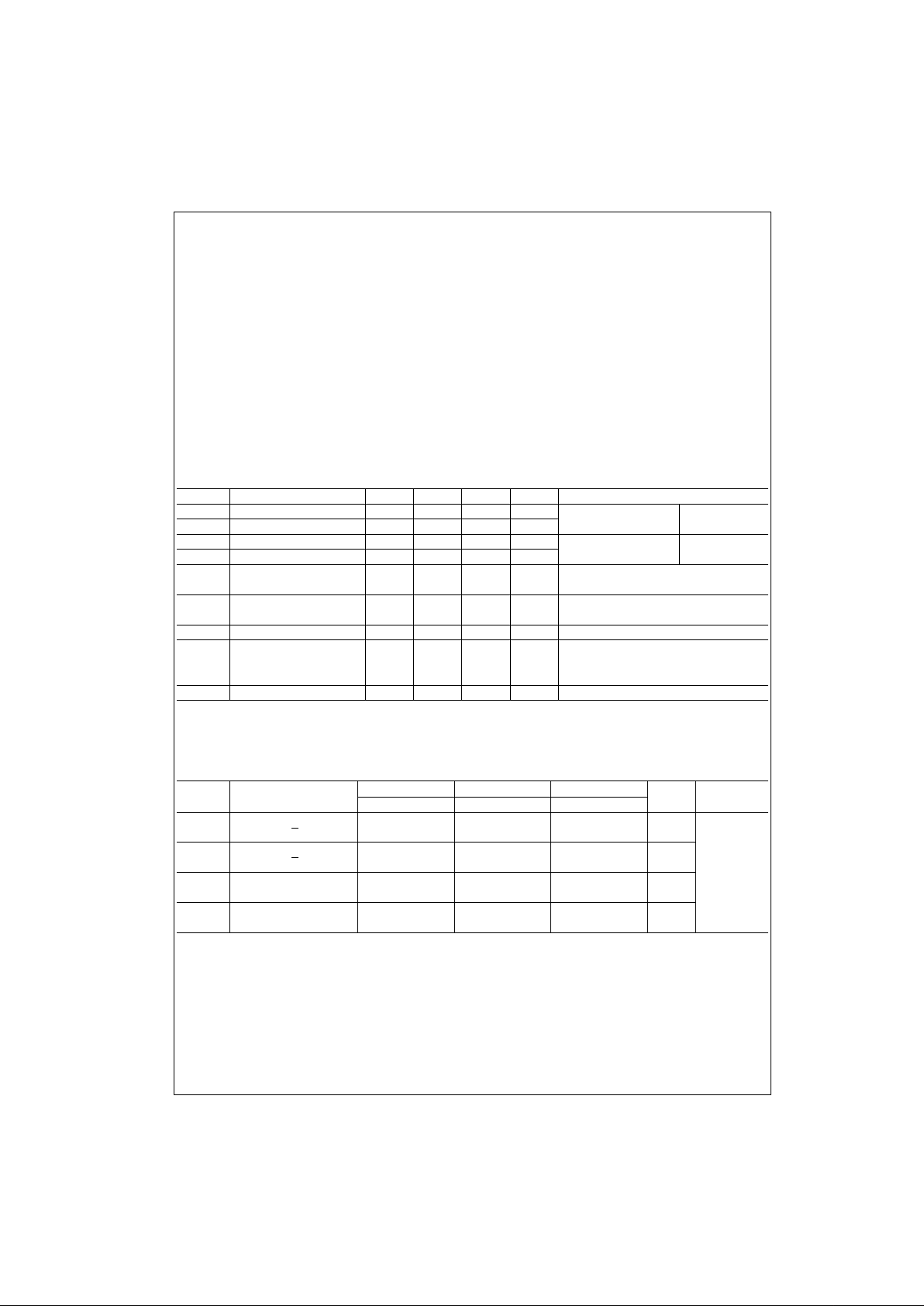

Absolute Maximum Ratings(Note 1) Recommended Operating

Conditions

Note 1: The “Absolute Maximum Ratings” are those values beyon d which

the safety of the dev ice cannot be guaranteed. T he device sh ould not be

operated at thes e limits. the parametric value s defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum rating.

The “Recomme nded O peratin g Cond itions ” table will defin e the condition s

for actual device operation.

Note 2: ESD testing conf orm s t o M I L-STD-883, Method 3015.

Commercial Version

DC Electrical Characteristics

(Note 3)

VEE = −4.2V to −5.7V, VCC = V

CCA

= GND, TC = 0°C to +85°C

Note 3: The specified limits represent the “worst case” value for the parameter. Since these values normally occur at the temperature extremes, additional

noise immunity and guardbanding can be achieved by decreasing the all owable syste m opera ti ng r ange s. Co ndi ti ons fo r t est ing shown in the ta ble s are chosen to guarantee operation under “worst case” conditions.

DIP AC Electrical Characteristics

VEE = −4.2V to −5.7V, VCC = V

CCA

= GND

Storage Temperature (T

STG

) −65°C to +150°C

Maximum Junction Temperature (T

J

) +150°C

V

EE

Pin Potential to Ground Pin −7.0V to +0.5V

Input Voltage (DC) V

EE

to +0.5V

Output Current (DC Output HIGH)

−50 mA

ESD (Note 2)

≥2000V

Case Temperature (T

C

)

Commercial 0

°C to +85°C

Industrial

−40°C to +85°C

Supply Voltage (V

EE

) −5.7V to −4.2V

Symbol Parameter Min Typ Max Units Conditions

V

OH

Output HIGH Voltage −1025 −955 −870 mV VIN =V

IH (Max)

Loading with

V

OL

Output LOW Voltage −1830 −1705 −1620 mV or V

IL (Min)

50Ω to −2.0V

V

OHC

Output HIGH Voltage −1035 mV VIN = V

IH (Min)

Loading with

V

OLC

Output LOW Voltage −1610 mV or V

IL (Max)

50Ω to −2.0V

V

IH

Input HIGH Voltage −1165 −870 mV Guaranteed HIGH Signal

for All Inputs

V

IL

Input LOW Voltage −1830 −1475 mV Guaranteed LOW Signal

for All Inputs

I

IL

Input LOW Current 0.50 µAVIN = V

IL (Min)

I

IH

Input HIGH Current

D2a–D

2e

250 µAVIN = VIH (Max)

D

1a–D1e

350

I

EE

Power Supply Current −69 −43 −30 mA Inputs Open

Symbol Parameter

TC = 0°CT

C

= +25°CT

C

= +85°C

Units Conditions

Min Max Min Max Min Max

t

PLH

Propagation Delay

0.55 1.90 0.55 1.80 0.55 1.90 ns

t

PHL

D2a–D2e to O, O

t

PLH

Propagation Delay

0.55 1.70 0.55 1.60 0.55 1.70 ns

t

PHL

D1a–D1e to O, O Figures 1, 2

t

PLH

Propagation Delay

1.15 2.75 1.15 2.75 1.15 3.00 ns

t

PHL

Data to F

t

TLH

Transition Time

0.35 1.20 0.35 1.20 0.35 1.20 ns

t

THL

20% to 80%, 80% to 20%

Loading...

Loading...