Page 1

MF302-13

IEEE1394 Controller

POWER SUPPLY IC

S1R77801F00A

S1F70000 Series

Technical Manual

Technical Manual

Page 2

NOTICE

No part of this material may be reproduced or duplicated in any from or by any means without the

written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material

without notics. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies

contained in this material or due to its application or use in any product or circuit and, further, there

is no repersesnation that this material is applicable to products requiring high level reliability, such as,

medical products. Moreover, no license to any intellectual property rights is granted by implication or

otherwise, and there is no representation or warranty that anything made in accordance with this

material will be free from any patent or copyright infringement of a third party. This material or

portions thereof may contain technology or the subject relating to strategic products under the control

of the Foreign Exchange and Foreign Trade Low of Japan and may require an export licenes from the

Ministry of International Trade and Industry or other approval from another government agency.

HD44103 is a registered trademark of Hitachi, Ltd.

All other product names mentioned herein are trademarks and/or registered trademarks of their

respective companies.

©SEIKO EPSON CORPORATION 2002, All rights reserved.

Page 3

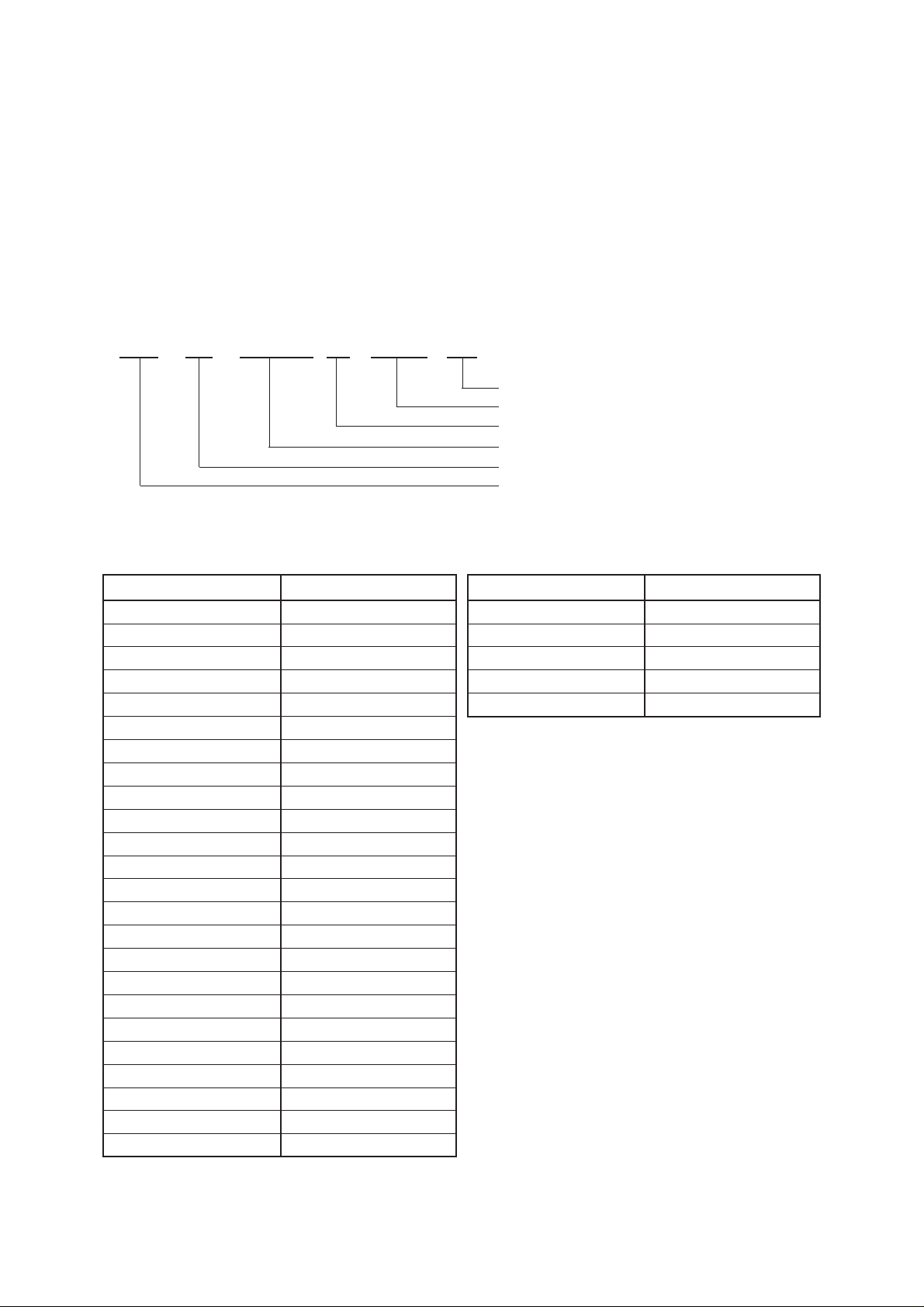

The information of the product number change

Starting April 1, 2001 the product number has been changed as listed belo w. To order , please use

the new product number. For further information, please contact Epson sales representative.

Configuration of product number

●DEVICES (Example : S1F70000D00B100)

S1 F 70000 D 00B1 00

Packing specification

Specifications

Shape (C:DIP, D:Bare chip, M:SOP, Y :SO T89)

Model number

Model name (F:Power supply ICs)

Product classification (S1:Semiconductors)

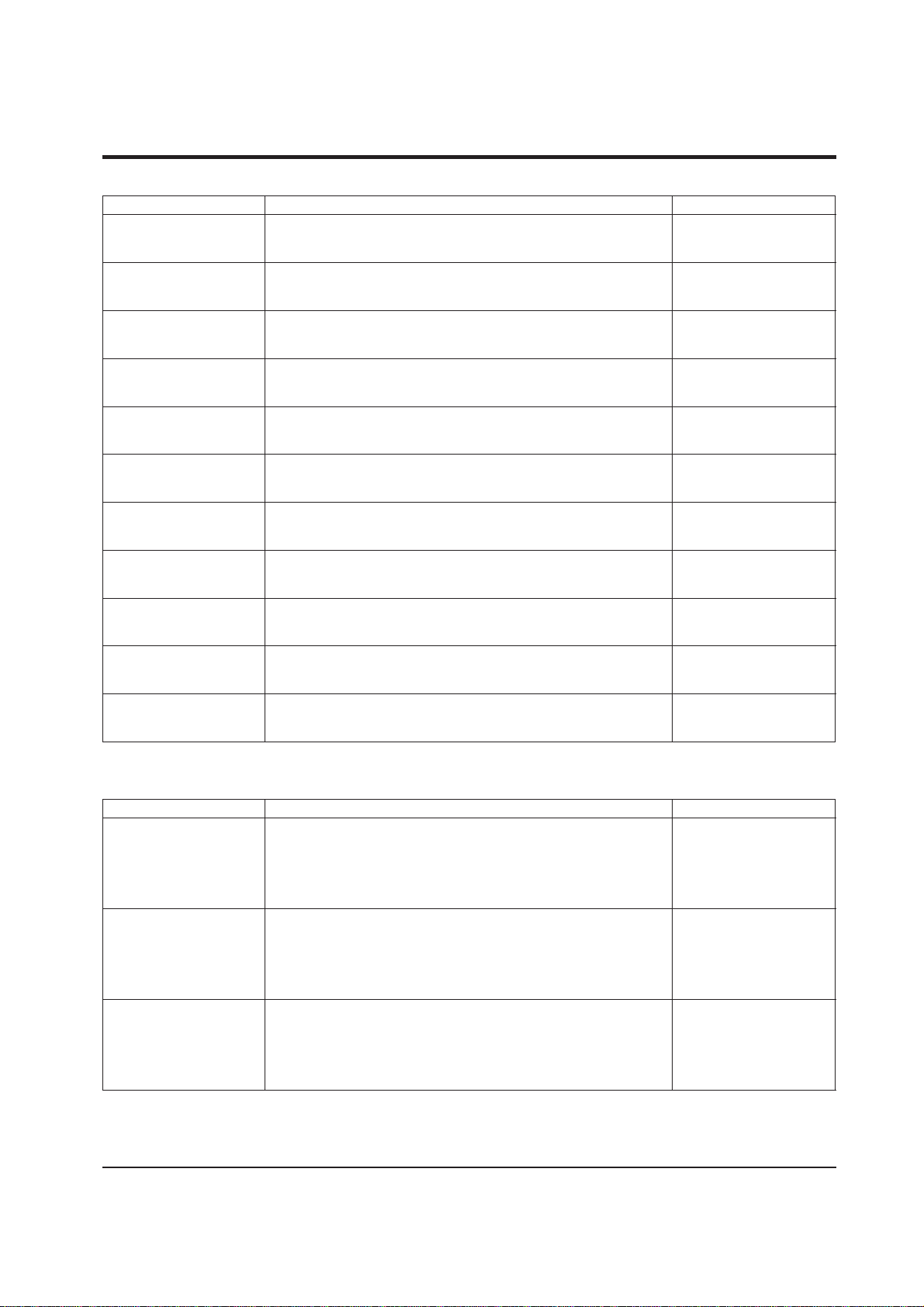

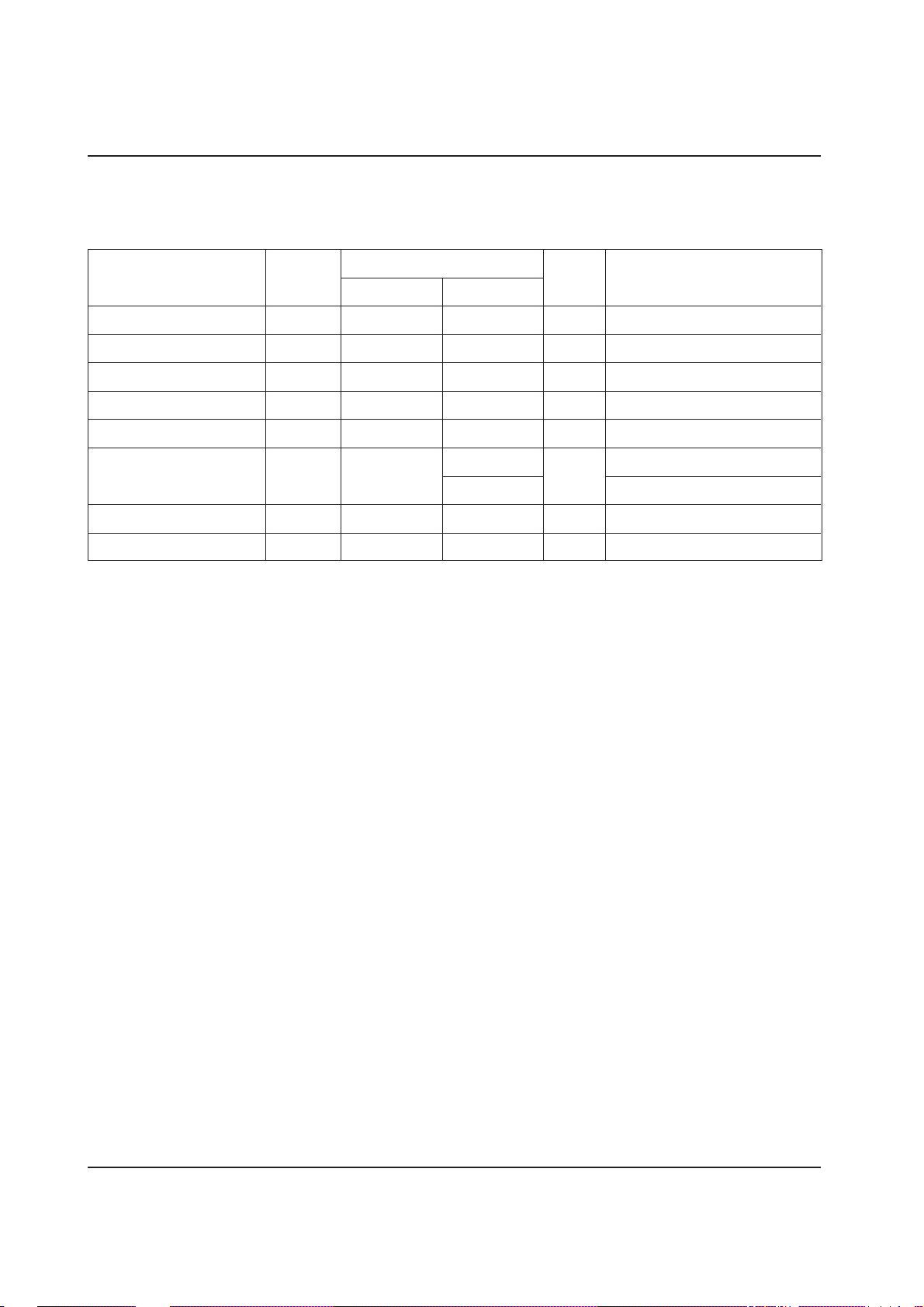

Comparison table between new and previous number

Previous number New number

SCI7660M0B S1F76600M0B0

SCI7660C0B S1F76600C0B0

SCI7662M0A S1F76620M0A0

SCI7662D0A S1F76620D0A0

SCI7661M0B S1F76610M0B0

SCI7661MBB S1F76610M2B0

SCI7661C0B S1F76610C0B0

SCI7654M0A S1F76540M0A0

SCI7654C0A S1F76540C0A0

SCI7664M0A S1F76640M0A0

SCI7664D0A S1F76640D0A0

SCI7810Y

SCI7910Y

SCI7631MLA S1F76310M1L0

SCI7631MBA S1F76310M1B0

SCI7631MKA S1F76310M1K0

SCI7631MAA S1F76310M1A0

SCI7638MHA S1F76380M1H0

SCI7638MLA S1F76380M1L0

SCI7633MBA S1F76330M1B0

SCI7110M0A S1F71100M0A0

SCI7120M0A S1F71200M0A0

SCI7120M0B S1F71200M0B0

B S1F78100Y2

*

A S1F79100Y1

*

*

*

Previous number New number

SCI7721Y

SCI7721Y

SCI7720Y

SCI7722Y

0

0

A S1F77210Y1

*

B S1F77210Y2

*

A S1F77200Y1

*

DB S1F77220Y2D0

*

*

*

0

0

0

Page 4

S1F70000 Series

Technical Manual

Page 5

Contents

Introduction .......................................................................................................................................................................... 1

Selection Guide.................................................................................................................................................................... 2

1. DC/DC Converter

S1F76600 Series

DESCRIPTION.......................................................................................................................................................... 1–1

FEATURES ............................................................................................................................................................... 1–1

APPLICATIONS ........................................................................................................................................................ 1–1

BLOCK DIAGRAM .................................................................................................................................................... 1–1

PIN ASSIGNMENTS ................................................................................................................................................. 1–1

PIN DESCRIPTIONS ................................................................................................................................................ 1–1

SPECIFICATIONS .................................................................................................................................................... 1–2

FUNCTIONAL DESCRIPTIONS ............................................................................................................................... 1–7

TYPICAL APPLICATIONS ........................................................................................................................................ 1–8

S1F76620 Series

DESCRIPTION........................................................................................................................................................ 1–10

FEATURES ............................................................................................................................................................. 1–10

BLOCK DIAGRAM .................................................................................................................................................. 1–10

PIN DESCRIPTIONS .............................................................................................................................................. 1–11

FUNCTIONAL DESCRIPTIONS ............................................................................................................................. 1–13

ELECTRICAL CHARACTERISTICS ....................................................................................................................... 1–14

EXAMPLE OF REFERENCE EXTERNAL CONNECTION ..................................................................................... 1–21

MEASUREMENT CIRCUIT..................................................................................................................................... 1–24

MECHANICAL DATA .............................................................................................................................................. 1–25

2. DC/DC Converter & Voltage Regulator

S1F76610 Series

DESCRIPTION.......................................................................................................................................................... 2–1

FEATURES ............................................................................................................................................................... 2–1

APPLICATIONS ........................................................................................................................................................ 2–1

BLOCK DIAGRAM .................................................................................................................................................... 2–1

PIN ASSIGNMENTS ................................................................................................................................................. 2–2

PIN DESCRIPTIONS ................................................................................................................................................ 2–2

SPECIFICATIONS .................................................................................................................................................... 2–3

FUNCTIONAL DESCRIPTIONS ............................................................................................................................. 2–11

TYPICAL APPLICATIONS ...................................................................................................................................... 2–12

S1F70000 Series EPSON i

Technical Manual

Page 6

Contents

S1F76540 Series

DESCRIPTION........................................................................................................................................................ 2–15

FEATURES ............................................................................................................................................................. 2–15

APPLICATIONS ...................................................................................................................................................... 2–15

BLOCK DIAGRAM .................................................................................................................................................. 2–16

PIN DESCRIPTIONS .............................................................................................................................................. 2–16

ELECTRICAL CHARACTERISTICS ....................................................................................................................... 2–19

FUNCTIONAL DESCRIPTIONS ............................................................................................................................. 2–22

CHARACTERISTICS GRAPH ................................................................................................................................ 2–29

APPLICATION CIRCUIT EXAMPLES .................................................................................................................... 2–30

S1F76640 Series

DESCRIPTION........................................................................................................................................................ 2–38

FEATURES ............................................................................................................................................................. 2–38

BLOCK DIAGRAM .................................................................................................................................................. 2–39

PIN ASSIGNMENTS ............................................................................................................................................... 2–40

PIN DESCRIPTIONS .............................................................................................................................................. 2–41

CHIP EXTERNAL SHAPE AND PAD CENTER COORDINATES .......................................................................... 2–42

FUNCTIONAL DESCRIPTIONS ............................................................................................................................. 2–43

ELECTRICAL CHARACTERISTICS ....................................................................................................................... 2–46

CHARACTERISTICS GRAPH ................................................................................................................................ 2–51

MECHANICAL DATA .............................................................................................................................................. 2–56

APPLICATION EXAMPLE ...................................................................................................................................... 2–57

3. Voltage Regulator

S1F78100Y Series

DESCRIPTION.......................................................................................................................................................... 3–1

FEATURES ............................................................................................................................................................... 3–1

BLOCK DIAGRAM .................................................................................................................................................... 3–1

PIN DESCRIPTIONS ................................................................................................................................................ 3–2

PIN ASSIGNMENTS ................................................................................................................................................. 3–2

FUNCTIONAL DESCRIPTIONS ............................................................................................................................... 3–3

LINEUP ..................................................................................................................................................................... 3–4

ABSOLUTE MAXIMUM RATINGS............................................................................................................................ 3–5

RECOMMENDED OPERATING CONDITIONS ....................................................................................................... 3–5

ELECTRICAL CHARACTERISTICS ......................................................................................................................... 3–6

EXAMPLES OF REFERENCE EXTERNAL CONNECTION .................................................................................. 3–14

MECHANICAL DATA .............................................................................................................................................. 3–14

ii EPSON S1F70000 Series

Technical Manual

Page 7

Contents

CHARACTERISTICS GRAPH ................................................................................................................................ 3–15

S1F79100Y Series

DESCRIPTION........................................................................................................................................................ 3–21

FEATURES ............................................................................................................................................................. 3–21

APPLICATIONS ...................................................................................................................................................... 3–21

LINEUP ................................................................................................................................................................... 3–21

BLOCK DIAGRAM .................................................................................................................................................. 3–21

PIN ASSIGNMENTS ............................................................................................................................................... 3–21

PIN DESCRIPTIONS .............................................................................................................................................. 3–22

SPECIFICATIONS .................................................................................................................................................. 3–22

PACKAGE MARKINGS........................................................................................................................................... 3–35

FUNCTIONAL DESCRIPTIONS ............................................................................................................................. 3–35

TYPICAL APPLICATIONS ...................................................................................................................................... 3–36

4. DC/DC Switching Regulators

S1F76300 Series

S1F76310, S1F76380 Series

DESCRIPTION ................................................................................................................................................ 4–1

FEATURES ..................................................................................................................................................... 4–1

APPLICATIONS .............................................................................................................................................. 4–1

LINEUP............................................................................................................................................................ 4–1

BLOCK DIAGRAMS ........................................................................................................................................ 4–2

PIN ASSIGNMENTS ....................................................................................................................................... 4–3

PIN DESCRIPTIONS....................................................................................................................................... 4–3

SPECIFICATIONS........................................................................................................................................... 4–4

PACKAGE MARKINGS ................................................................................................................................. 4–13

FUNCTIONAL DESCRIPTIONS.................................................................................................................... 4–13

TYPICAL APPLICATIONS ............................................................................................................................ 4–15

S1F76330 Series

DESCRIPTION .............................................................................................................................................. 4–22

FEATURES ................................................................................................................................................... 4–22

APPLICATIONS ............................................................................................................................................ 4–22

LINEUP.......................................................................................................................................................... 4–22

BLOCK DIAGRAMS ...................................................................................................................................... 4–23

PIN ASSIGNMENTS ..................................................................................................................................... 4–23

PIN DESCRIPTIONS..................................................................................................................................... 4–23

SPECIFICATIONS......................................................................................................................................... 4–24

S1F70000 Series EPSON iii

Technical Manual

Page 8

Contents

PACKAGE MARKINGS ................................................................................................................................. 4–26

FUNCTIONAL DESCRIPTIONS....................................................................................................................4–27

TYPICAL APPLICATIONS ............................................................................................................................ 4–28

S1F71100 Series

DESCRIPTION........................................................................................................................................................ 4–34

FEATURES ............................................................................................................................................................. 4–34

BLOCK DIAGRAM .................................................................................................................................................. 4–34

PIN ASSIGNMENTS ............................................................................................................................................... 4–35

PIN DESCRIPTIONS .............................................................................................................................................. 4–35

FUNCTIONAL DESCRIPTIONS ............................................................................................................................. 4–36

ABSOLUTE MAXIMUM RATINGS.......................................................................................................................... 4–37

ELECTRICAL CHARACTERISTICS ....................................................................................................................... 4–38

EXAMPLE OF EXTERNAL CONNECTION OF REFERENCE CIRCUIT ............................................................... 4–39

MECHANICAL DATA .............................................................................................................................................. 4–40

S1F71200 Series

DESCRIPTION........................................................................................................................................................ 4–41

FEATURES ............................................................................................................................................................. 4–41

BLOCK DIAGRAM .................................................................................................................................................. 4–42

PIN ASSIGNMENTS ............................................................................................................................................... 4–43

PIN DESCRIPTIONS .............................................................................................................................................. 4–44

FUNCTIONAL DESCRIPTIONS ............................................................................................................................. 4–45

ABSOLUTE MAXIMUM RATINGS.......................................................................................................................... 4–47

ELECTRICAL CHARACTERISTICS ....................................................................................................................... 4–48

EXAMPLE OF EXTERNAL CONNECTION OF REFERENCE CIRCUIT ............................................................... 4–52

MECHANICAL DATA .............................................................................................................................................. 4–54

iv EPSON S1F70000 Series

Technical Manual

Page 9

Contents

5.Voltage Detector

S1F77200Y Series

DESCRIPTION..........................................................................................................................................................5–1

FEATURES...............................................................................................................................................................5–1

LINEUP.....................................................................................................................................................................5–2

BLOCK DIAGRAM....................................................................................................................................................5–3

PIN DESCRIPTIONS................................................................................................................................................5–4

FUNCTIONAL DESCRIPTIONS...............................................................................................................................5–4

ABSOLUTE MAXIMUM RATINGS............................................................................................................................5–5

ELECTRIC CHARACTERISTICS.............................................................................................................................5–6

EXAMPLES OF EXTERNAL CONNECTION..........................................................................................................5–19

SAMPLE CIRCUITS (S1F77210Y Series)..............................................................................................................5–20

SAMPLE CIRCUITS (S1F77200Y Series)..............................................................................................................5–21

PRECAUTIONS......................................................................................................................................................5–22

6.Appendix

ABSOLUTE MAXIMUM RATINGS............................................................................................................................6–1

RECOMMENDER OPERATING CONDITIONS.......................................................................................................6–1

ELECTRICAL CHARACTERISTICS.........................................................................................................................6–1

POWER DISSIPATION CONDITIONS.....................................................................................................................6–1

PARAMETER SUMMARY........................................................................................................................................6–2

MECHANICAL DATA................................................................................................................................................6–4

EMBOSS CARRIER TAPING STANDARD (SOT89-3pin)

TAPING INFORMATION...........................................................................................................................................6–6

REEL SPECIFICATIONS..........................................................................................................................................6–7

DEVICE POSITIONING............................................................................................................................................6–7

EMBOSS CARRIER TAPING STANDARD (SOP3-8pin)

TAPING INFORMATION...........................................................................................................................................6–8

REEL SPECIFICATIONS..........................................................................................................................................6–9

DEVICE POSITIONING............................................................................................................................................6–9

EMBOSS CARRIER TAPING STANDARD (SOP5-14pin)

TAPING INFORMATION.........................................................................................................................................6–11

REEL SPECIFICATIONS........................................................................................................................................6–12

DEVICE POSITIONING..........................................................................................................................................6–12

S1F70000 Series EPSON v

Technical Manual

Page 10

Contents

EMBOSS CARRIER TAPING STANDARD (SOP2-24pin)

TAPING INFORMATION.........................................................................................................................................6–14

REEL SPECIFICATIONS........................................................................................................................................6–16

DEVICE POSITIONING..........................................................................................................................................6–16

vi EPSON S1F70000 Series

Technical Manual

Page 11

Introduction

This book describes SEIKO EPSON's full lineup of

power supply ICs and includes a complete set of

product specifications. Also included are sections on

quality assurance and packaging.

We suggest that you use the selector guide beginning

on the following page to choose the IC or IC series that

most closely matches your application. Then you can

use the detailed product descriptions in subsequent

sections to confirm device specifications and characteristics.

Please contact your local SEIKO EPSON sales

representative for further information or assistance on

these or other products.

S1F70000 Series EPSON 1

Technical Manual

Page 12

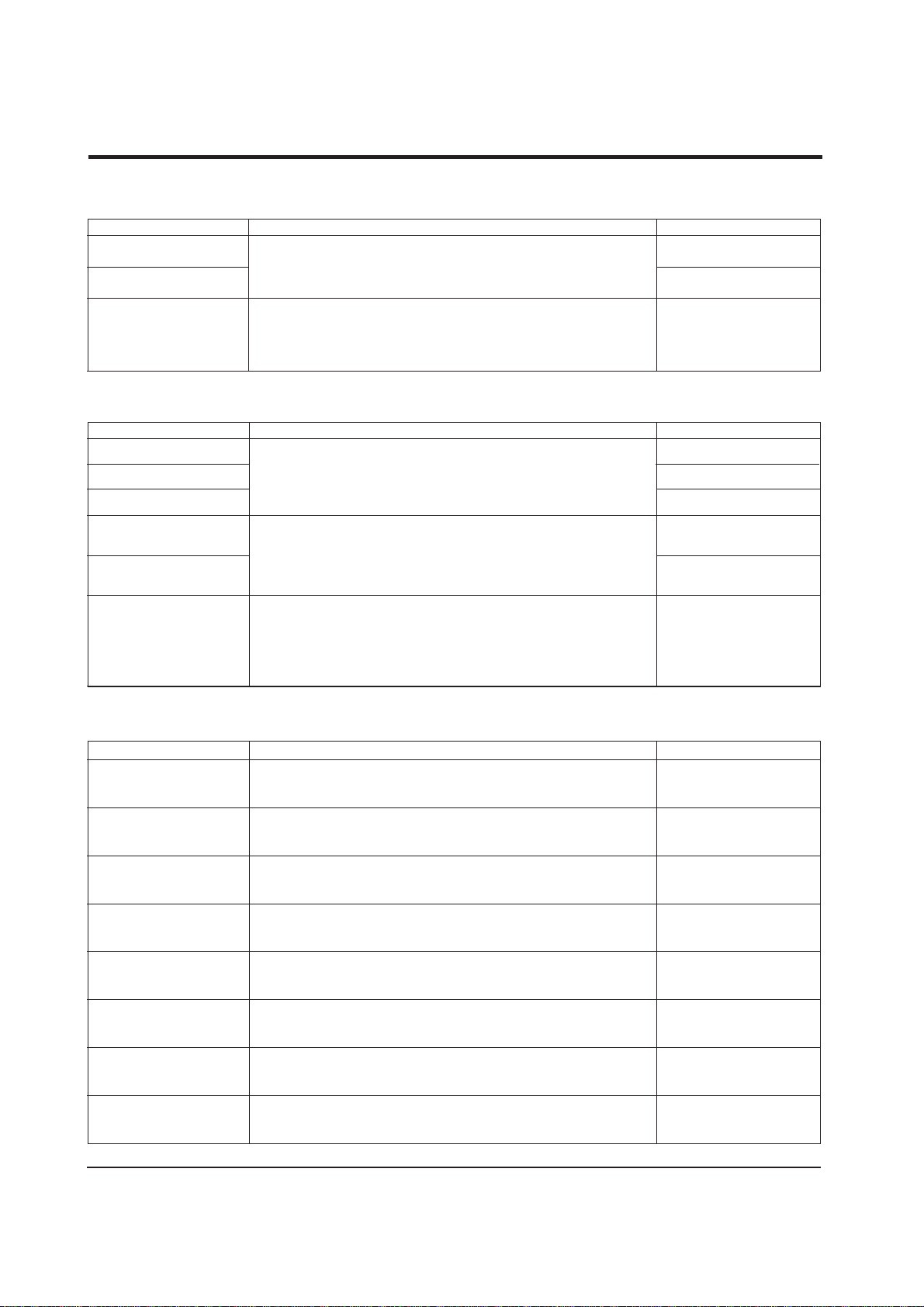

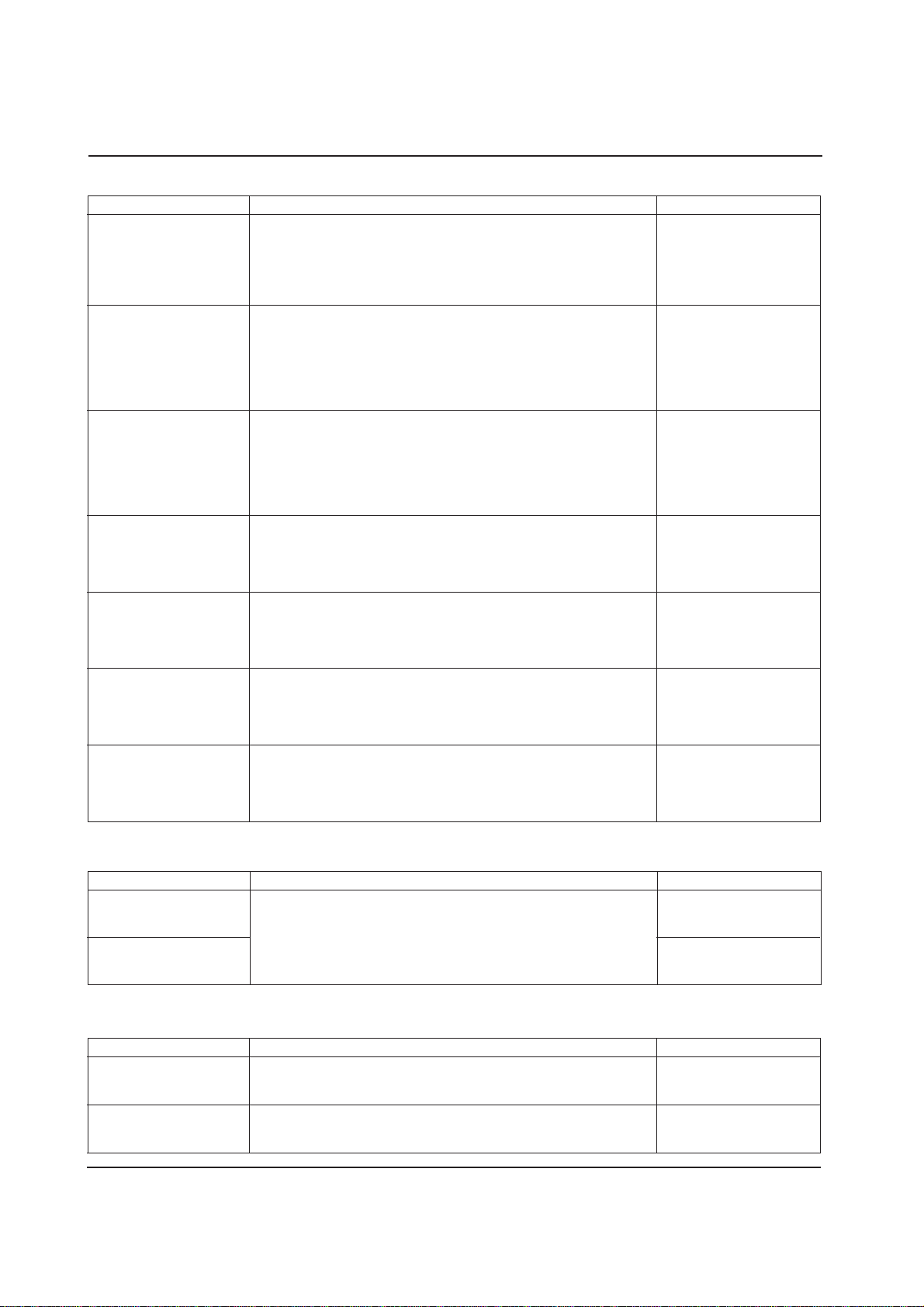

Selection Guide

DC/DC Converter

Product Features Package

S1F76600M0B0

S1F76600C0B0

S1F76620M0A0

• Supply voltage conversion IC.

• It effectively converts input voltage V

• Output current : Max. 30mA at –5V

• Power conversion efficiency: Typ. 95%

• Supply voltage conversion IC.

• It effectively converts input voltage V

• Output current : Max. 30mA at 5V

• Power conversion efficiency: Typ. 95%

DD into –VDD or 2VDD

DD into –VDD or 2VDD

DC/DC Converter and Voltage Regulator

Product Features Package

S1F76610M0B0

S1F76610M2B0 • Output current : Max. 20mA at –5V SSOP2-16pin

S1F76610C0B0

S1F76540M0A0

S1F76540C0A0

S1F76640M0A0 • Output current : Max. 20mA at 5V SSOP2-16pin

• On–chip voltage regulator.

• It effectively converts input voltage V

• Power conversion efficiency: Typ. 95%

• Three temperature gradients for LCD panel power.

• On–chip voltage regulator.

• It effectively converts input voltage V

• Low current Consumption : Typ. 130

• Power conversion efficiency: Typ. 95%

• Three temperature gradients for LCD panel power.

• On–chip voltage regulator.

• It effectively converts input voltage V

• Power conversion efficiency: Typ. 95%

• Three temperature gradients for LCD panel power.

DD into –VDD/–2VDD or 2VDD/3VDD

DD into –2VDD/–3VDD/–4VDD.

µ

A at –5V, 4–time boosting

DD into 2VDD/3VDD/4VDD.

SOP4-8pin

DIP-8pin

SOP4-8pin

SOP5-14pin

DIP-14pin

SSOP2-16pin

DIP-16pin

Voltage regulator

Product Features Package

• 6.00V positive output voltage regulator.

S1F78100Y2A0 • Low operating current (Typ. 3.0

• Input voltage stability (Typ. 0.1%/V).

• 5.00V positive output voltage regulator.

S1F78100Y2B0 • Low operating current (Typ. 3.0

• Input voltage stability (Typ. 0.1%/V).

• 4.50V positive output voltage regulator.

S1F78100Y2M0 • Low operating current (Typ. 3.0

• Input voltage stability (Typ. 0.1%/V).

• 4.00V positive output voltage regulator.

S1F78100Y2P0 • Low operating current (Typ. 3.0

• Input voltage stability (Typ. 0.1%/V).

• 3.90V positive output voltage regulator.

S1F78100Y2K0 • Low operating current (Typ. 3.0

• Input voltage stability (Typ. 0.1%/V).

• 3.50V positive output voltage regulator.

S1F78100Y2N0 • Low operating current (Typ. 3.0

• Input voltage stability (Typ. 0.1%/V).

• 3.30V positive output voltage regulator.

S1F78100Y2T0 • Low operating current (Typ. 3.0

• Input voltage stability (Typ. 0.1%/V).

• 3.20V positive output voltage regulator.

S1F78100Y2C0 • Low operating current (Typ. 3.0

• Input voltage stability (Typ. 0.1%/V).

µ

A). SOT89-3pin

µ

A). SOT89-3pin

µ

A). SOT89-3pin

µ

A). SOT89-3pin

µ

A). SOT89-3pin

µ

A). SOT89-3pin

µ

A). SOT89-3pin

µ

A). SOT89-3pin

2 EPSON S1F70000 Series

Technical Manual

Page 13

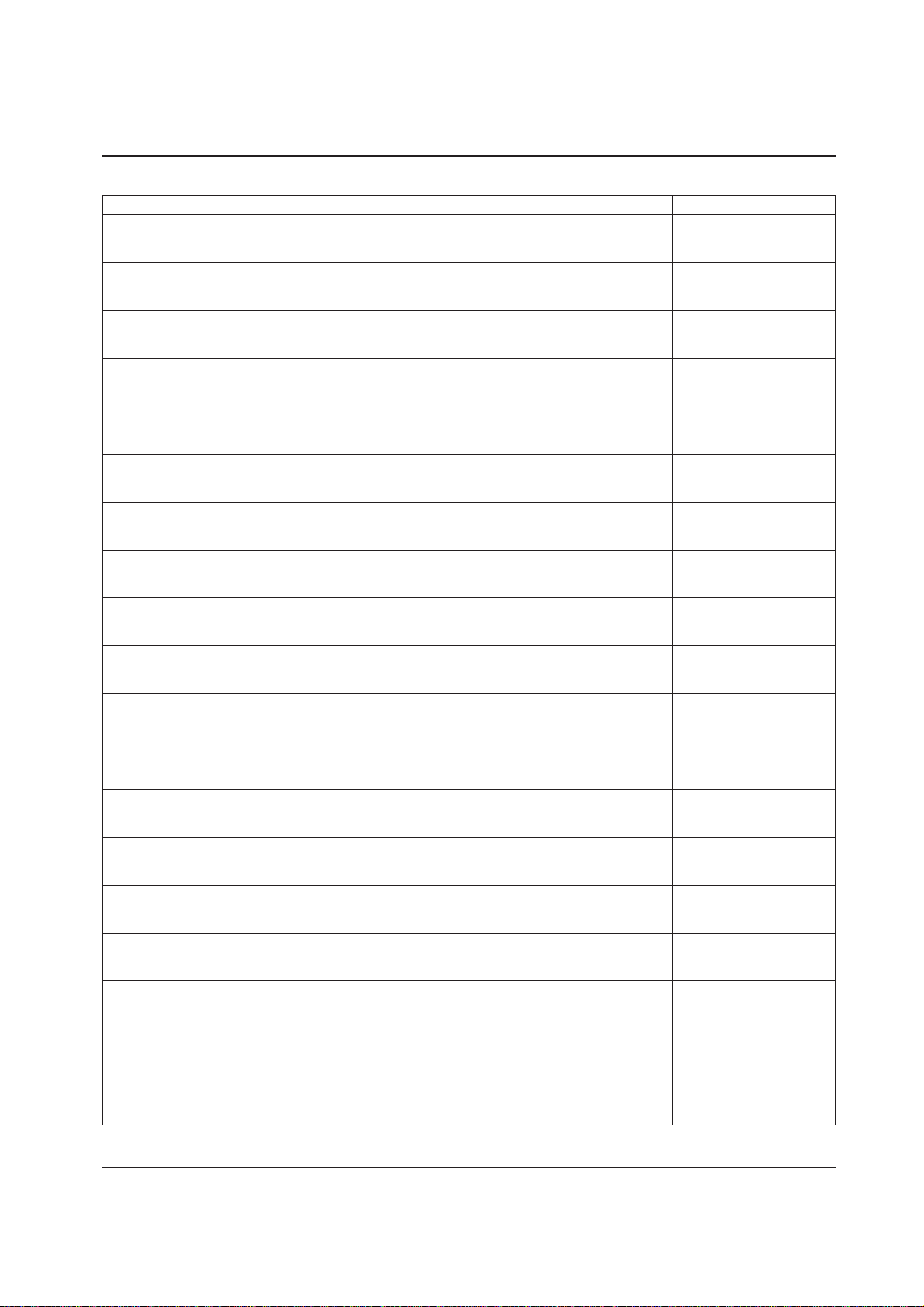

Selection Guide

Product Features Package

• 3.00V positive output voltage regulator.

S1F78100Y2D0 • Low operating current (Typ. 3.0

• Input voltage stability (Typ. 0.1%/V).

• 2.80V positive output voltage regulator.

S1F78100Y2R0 • Low operating current (Typ. 3.0

• Input voltage stability (Typ. 0.1%/V).

• 2.60V positive output voltage regulator.

S1F78100Y2L0 • Low operating current (Typ. 3.0

• Input voltage stability (Typ. 0.1%/V).

• 2.20V positive output voltage regulator.

S1F78100Y2F0 • Low operating current (Typ. 3.0

• Input voltage stability (Typ. 0.1%/V).

• 1.80V positive output voltage regulator.

S1F78100Y2G0 • Low operating current (Typ. 3.0

• Input voltage stability (Typ. 0.1%/V).

• 1.50V positive output voltage regulator.

S1F78100Y2H0 • Low operating current (Typ. 3.0

• Input voltage stability (Typ. 0.1%/V).

• –5.00V negative output voltage regulator.

S1F79100Y1B0 • Low operating current (Typ. 4.0

• Input voltage stability (Typ. 0.1%/V).

• –4.00V negative output voltage regulator.

S1F79100Y1P0 • Low operating current (Typ. 4.0

• Input voltage stability (Typ. 0.1%/V).

• –3.00V negative output voltage regulator.

S1F79100Y1D0 • Low operating current (Typ. 4.0

• Input voltage stability (Typ. 0.1%/V).

• –1.80V negative output voltage regulator.

S1F79100Y1G0 • Low operating current (Typ. 4.0

• Input voltage stability (Typ. 0.1%/V).

• –1.50V negative output voltage regulator.

S1F79100Y1H0 • Low operating current (Typ. 4.0

• Input voltage stability (Typ. 0.1%/V).

µ

A). SOT89-3pin

µ

A). SOT89-3pin

µ

A). SOT89-3pin

µ

A). SOT89-3pin

µ

A). SOT89-3pin

µ

A). SOT89-3pin

µ

A). SOT89-3pin

µ

A). SOT89-3pin

µ

A). SOT89-3pin

µ

A). SOT89-3pin

µ

A). SOT89-3pin

DC/DC Switching Regulator

Product Features Package

• Step-up switching regulator (from 1.5V to 5.0V).

• Low operating voltage (Min. 0.9V).

S1F76310M1A0

S1F76310M1K0

S1F76310M1B0

S1F70000 Series EPSON 3

Technical Manual

• Low operating current (Typ. 10

• High precision voltage detection function and battery backup function.

• Built-in CR oscillator circuit.

• Power-on clear function.

• Step-up switching regulator (from 1.5V to 3.5V).

• Low operating voltage (Min. 0.9V).

• Low operating current (Typ. 8

• High precision voltage detection function and battery backup function.

• Built-in CR oscillator circuit.

• Power-on clear function.

• Step-up switching regulator (from 1.5V to 3.0V).

• Low operating voltage (Min. 0.9V).

• Low operating current (Typ. 8

• High precision voltage detection function and battery backup function.

• Built-in CR oscillator circuit.

• Power-on clear function.

µ

A).

µ

A).

µ

A).

SOP3-8pin

SOP3-8pin

SOP3-8pin

Page 14

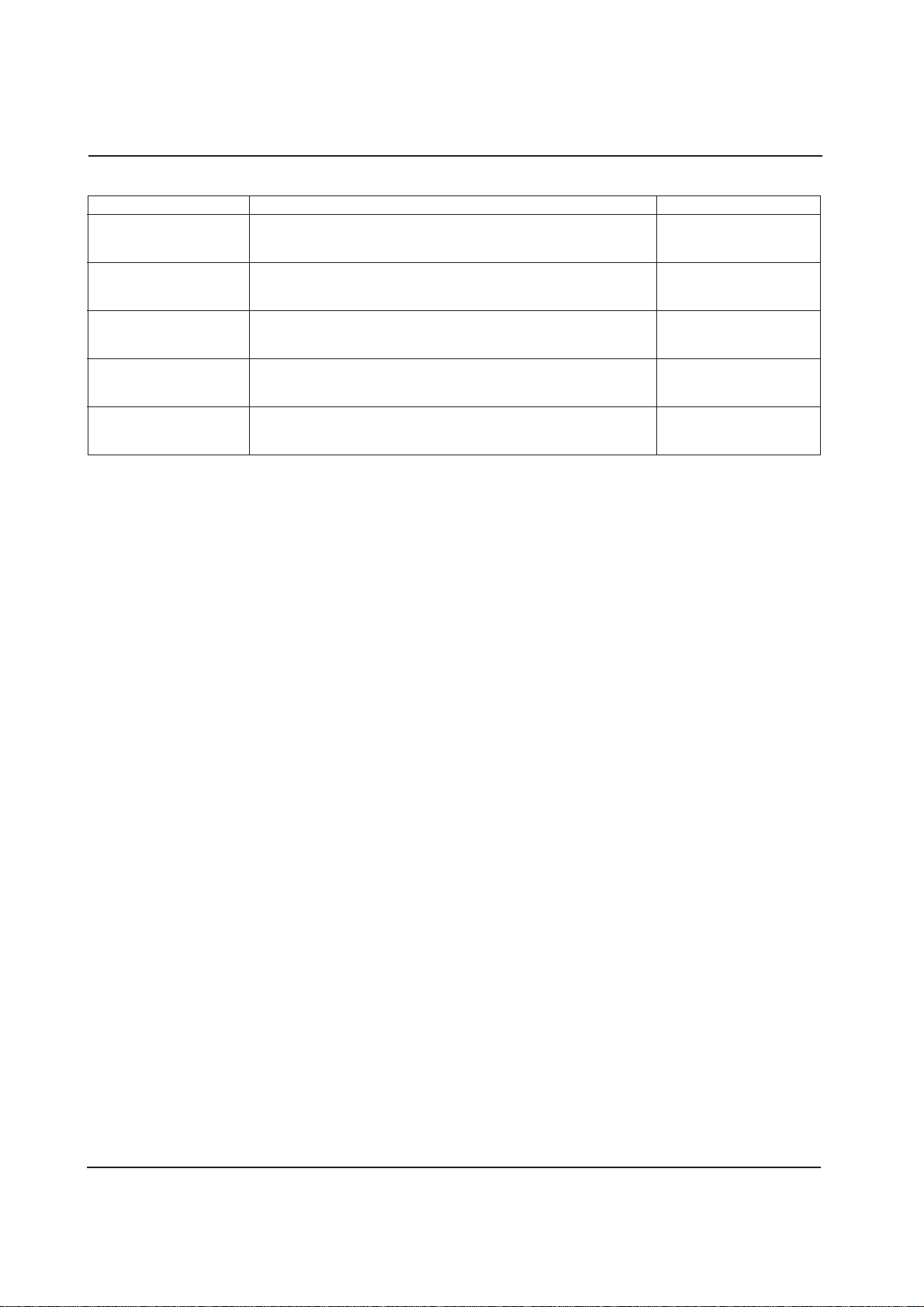

Selection Guide

Product Features Package

• Step-up switching regulator (from 1.5V to 2.4V).

• Low operating voltage (Min. 0.9V).

S1F76310M1L0

S1F76380M1H0 • Built-in CR oscillator circuit. SOP3-8pin

S1F76380M1L0 • Built-in CR oscillator circuit. SOP3-8pin

S1F76330M1B0 • Low operating current. (Typ. 5

S1F71100M0A0 • Frequency fixing (200kHz) PWM. SOP4-8pin

S1F71200M0A0 • Frequency fixing (200kHz) PWM. SSOP2-16pin

S1F71100M0B0 • Frequency fixing (200kHz) PWM. SSOP2-16pin

• Low operating current (Typ. 7

• High precision voltage detection function and battery backup function.

• Built-in CR oscillator circuit.

• Power-on clear function.

• Step-up switching regulator (from 1.5V to 2.2V).

• Low operating voltage (Min. 0.9V).

• Low operating current. (Typ. 7

• High precision voltage detection.

• Output voltage response compensation.

• Temperature characteristics of output voltage for LCD panel (-4.5mV/C).

• Step-up switching regulator (from 1.5V to 2.4V).

• Low operating voltage (Min. 0.9V).

• Low operating current. (Typ. 7

• High precision voltage detection.

• Output voltage response compensation.

• Temperature characteristics of output voltage for LCD panel (-4.0mV/C).

• Step-up switching regulator (from 1.5V to 3.0V).

• Low operating voltage (Min. 0.9V).

• Built-in crystal oscillator circuit.

• Equipped with crystal oscillator output pin.

• Step-down switching regulator (from 3.3V ~ 12.0V to 3.3V).

• Power off current : 1

• Soft start function.

• Overcurrent protection function, Low-voltage protection function.

• Step-up/down switching regulator (from 2.5V ~ 12.0V to 5.0V).

• Power off current : 1

• Soft start function.

• Overcurrent protection function.

• Step-up/down switching regulator (from 2.5V ~ 12.0V to 3.3V).

• Power off current : 1

• Soft start function.

• Overcurrent protection function.

µ

A).

µ

A).

µ

A).

µ

A). SOP3-8pin

µ

A

µ

A

µ

A

SOP3-8pin

Voltage Detector

Product Features Package

S1F77210Y1L0 • Output format: COMS. SOP89-3pin

S1F77210Y1K0 • Output format: COMS. SOP89-3pin

4 EPSON S1F70000 Series

• Voltage detection (Typ. 5.00V).

• Low operating power (Typ. 2.0 µA, VDD = 6.0V).

• Voltage detection (Typ. 4.80V).

• Low operating power (Typ. 2.0 µA, VDD = 5.0V).

Technical Manual

Page 15

Selection Guide

Product Features Package

S1F77210Y120 • Output format: COMS. SOP89-3pin

S1F77210Y1J0 • Output format: COMS. SOP89-3pin

S1F77210Y1M0 • Output format: COMS. SOP89-3pin

S1F77210Y1T0 • Output format: COMS. SOP89-3pin

S1F77210Y130 • Output format: COMS. SOP89-3pin

S1F77210Y1H0 • Output format: COMS. SOP89-3pin

S1F77210Y1G0 • Output format: COMS. SOP89-3pin

S1F77210Y1R0 • Output format: COMS. SOP89-3pin

S1F77210Y1F0 • Output format: COMS. SOP89-3pin

S1F77210Y1E0 • Output format: COMS. SOP89-3pin

S1F77210Y1S0 • Output format: COMS. SOP89-3pin

S1F77210Y1P0 • Output format: COMS. SOP89-3pin

S1F77210Y1C0 • Output format: COMS. SOP89-3pin

S1F77210Y2F0 • Output format: COMS. SOP89-3pin

S1F77210Y2C0 • Output format: COMS. SOP89-3pin

S1F77200Y1T0 • Output format: N-ch open drain. SOP89-3pin

S1F77200Y1F0 • Output format: N-ch open drain. SOP89-3pin

S1F77200Y1C0 • Output format: N-ch open drain. SOP89-3pin

S1F77200Y1N0 • Output format: N-ch open drain. SOP89-3pin

• Voltage detection (Typ. 4.60V).

• Low operating power (Typ. 2.0 µA, VDD = 5.0V).

• Voltage detection (Typ. 4.40V).

• Low operating power (Typ. 2.0 µA, VDD = 5.0V).

• Voltage detection (Typ. 4.20V).

• Low operating power (Typ. 2.0 µA, VDD = 5.0V).

• Voltage detection (Typ. 4.00V).

• Low operating power (Typ. 2.0 µA, VDD = 5.0V).

• Voltage detection (Typ. 3.50V).

• Low operating power (Typ. 2.0 µA, VDD = 4.0V).

• Voltage detection (Typ. 3.20V).

• Low operating power (Typ. 2.0 µA, VDD = 4.0V).

• Voltage detection (Typ. 3.00V).

• Low operating power (Typ. 2.0 µA, VDD = 4.0V).

• Voltage detection (Typ. 2.80V).

• Low operating power (Typ. 2.0 µA, VDD = 3.0V).

• Voltage detection (Typ. 2.65V).

• Low operating power (Typ. 2.0 µA, VDD = 3.0V).

• Voltage detection (Typ. 2.55V).

• Low operating power (Typ. 2.0 µA, VDD = 3.0V).

• Voltage detection (Typ. 2.35V).

• Low operating power (Typ. 2.0 µA, VDD = 3.0V).

• Voltage detection (Typ. 2.25V).

• Low operating power (Typ. 2.0 µA, VDD = 3.0V).

• Voltage detection (Typ. 2.15V).

• Low operating power (Typ. 2.0 µA, VDD = 3.0V).

• Voltage detection (Typ. 2.65V).

• Low operating power (Typ. 2.0 µA, VDD = 3.0V).

• Voltage detection (Typ. 2.15V).

• Low operating power (Typ. 2.0 µA, VDD = 3.0V).

• Voltage detection (Typ. 4.00V).

• Low operating power (Typ. 2.0 µA, VDD = 5.0V).

• Voltage detection (Typ. 2.65V).

• Low operating power (Typ. 2.0 µA, VDD = 3.0V).

• Voltage detection (Typ. 2.15V).

• Low operating power (Typ. 2.0 µA, VDD = 3.0V).

• Voltage detection (Typ. 1.90V).

• Low operating power (Typ. 2.0

µ

A, VDD = 3.0V).

S1F70000 Series EPSON 5

Technical Manual

Page 16

Selection Guide

Product Features Package

S1F77200Y1B0 • Output format: N-ch open drain. SOP89-3pin

S1F77200Y1Y0 • Output format: N-ch open drain. SOP89-3pin

S1F77200Y1A0 • Output format: N-ch open drain. SOP89-3pin

S1F77200Y1V0 • Output format: N-ch open drain. SOP89-3pin

S1F77220Y2D0 • Output format: P-ch open drain. SOP89-3pin

• Voltage detection (Typ. 1.15V).

• Low operating power (Typ. 1.5 µA, VDD = 1.5V).

• Voltage detection (Typ. 1.10V).

• Low operating power (Typ. 1.5 µA, VDD = 1.5V).

• Voltage detection (Typ. 1.05V).

• Low operating power (Typ. 1.5 µA, VDD = 1.5V).

• Voltage detection (Typ. 0.95V).

• Low operating power (Typ. 1.5 µA, VDD = 1.5V).

• Voltage detection (Typ. 1.25V).

• Low operating power (Typ. 1.5

µ

A, VDD = 1.5V).

6 EPSON S1F70000 Series

Technical Manual

Page 17

1. DC/DC Converter

Page 18

S1F76600 Series

S1F76600 Series CMOS DC/DC Converter (Voltage Doubler)

DESCRIPTION

The S1F76600 Series is a highly efficient CMOS DC/

DC converter for doubling an input voltage (from

–1.5V to –8V). This power-saving IC allows portable

computers and similar hand-held equipment to operate

from a single power supply, even when they incorporate

LSIs that operate at voltages different from those of

logic circuits, for example, LCD drivers and analog

LSIs.

The S1F76600C0B0 is available in 8-pin plastic DIPs,

and the S1F76600M0B0, in 8-pin plastic SOPs.

FEATURES

• 95% (Typ.) conversion efficiency

• Two output voltages, V

O, relative to VDD and VI

• 30mA maximum output current at 5V

• Connecting-in-series configuration obtains a higher

output voltage (V

1=–5V, V0=–15V at two-in-series).

• Low operating voltage

• On-chip CR oscillator

• 8-pin plastic DIP and 8-pin plastic SOP

APPLICATIONS

• Fixed-voltage power supplies for battery-operated

equipment

• Power supplies for pagers, memory cards, calculators

and similar hand-held equipment

• Fixed-voltage power supplies for medical equipment

• Fixed-voltage power supplies for communications

equipment

• Uninterruptable power supplies

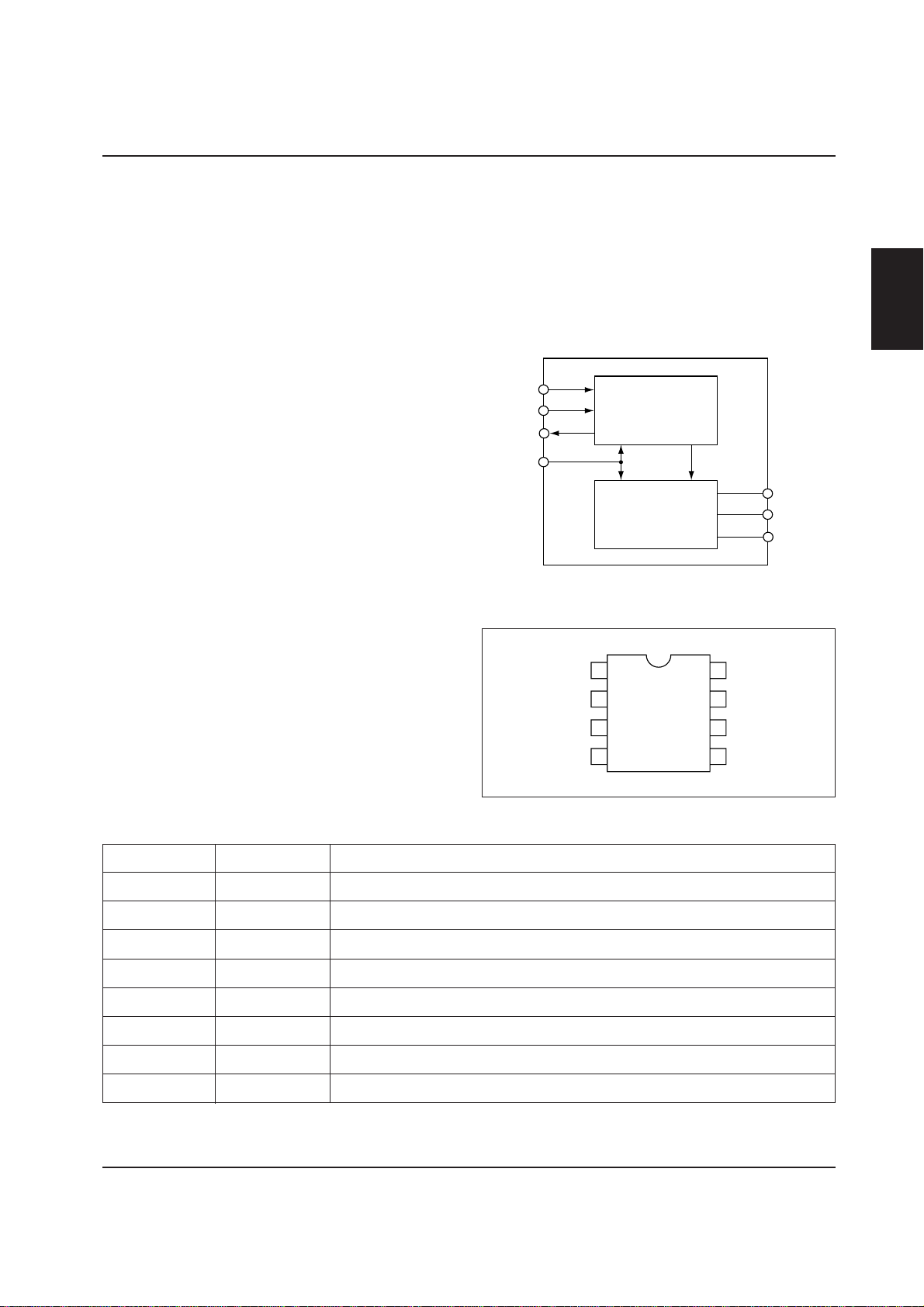

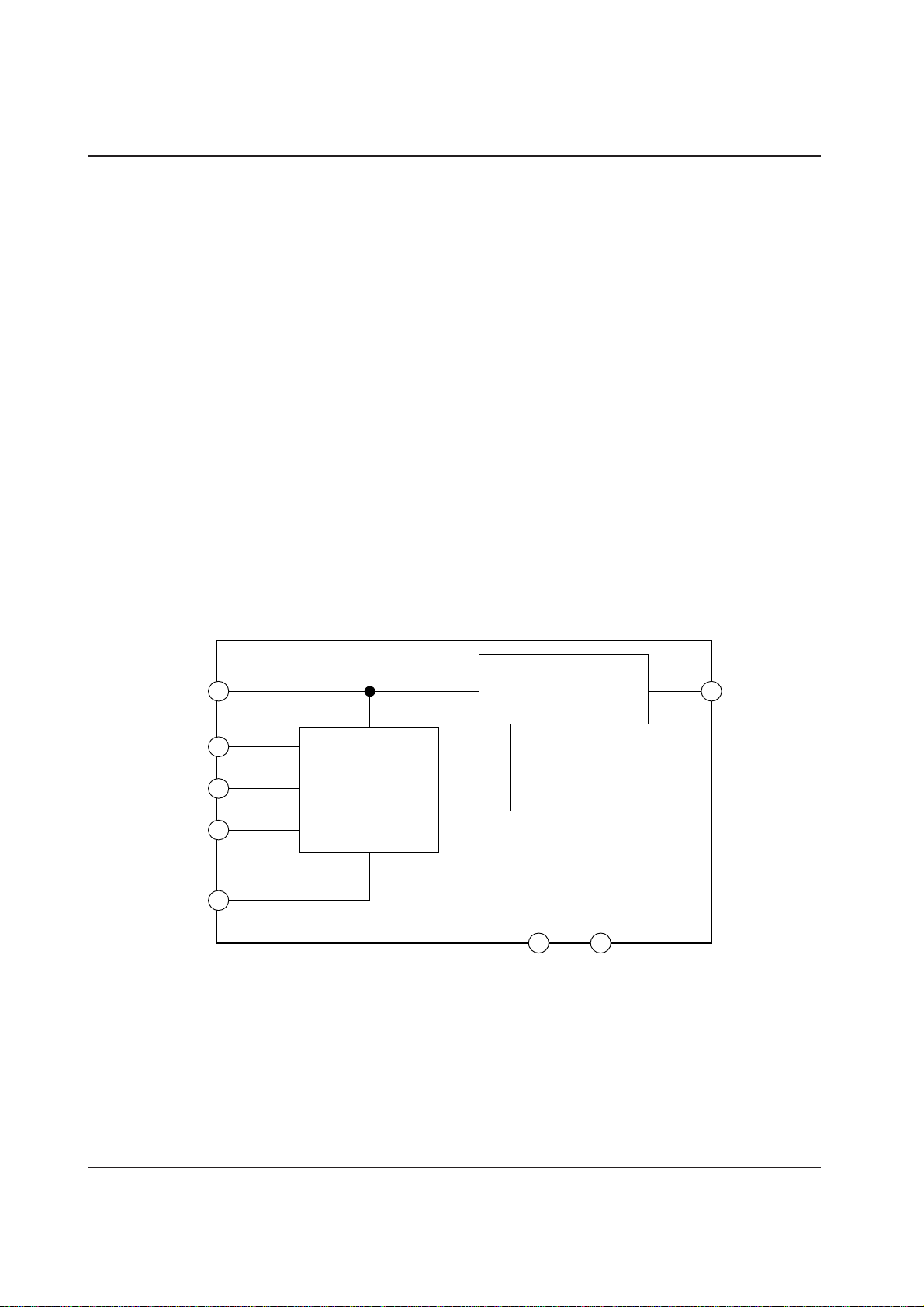

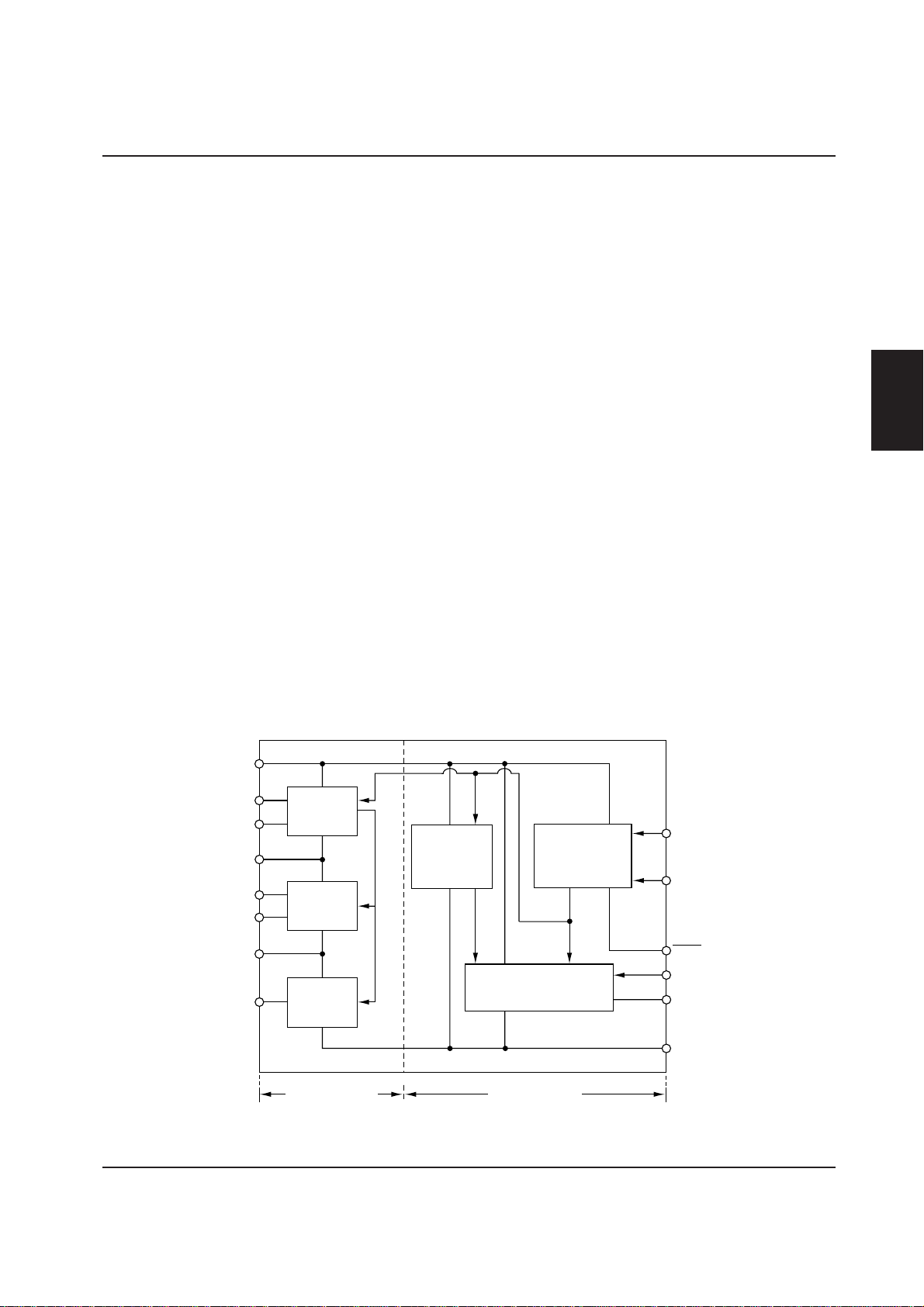

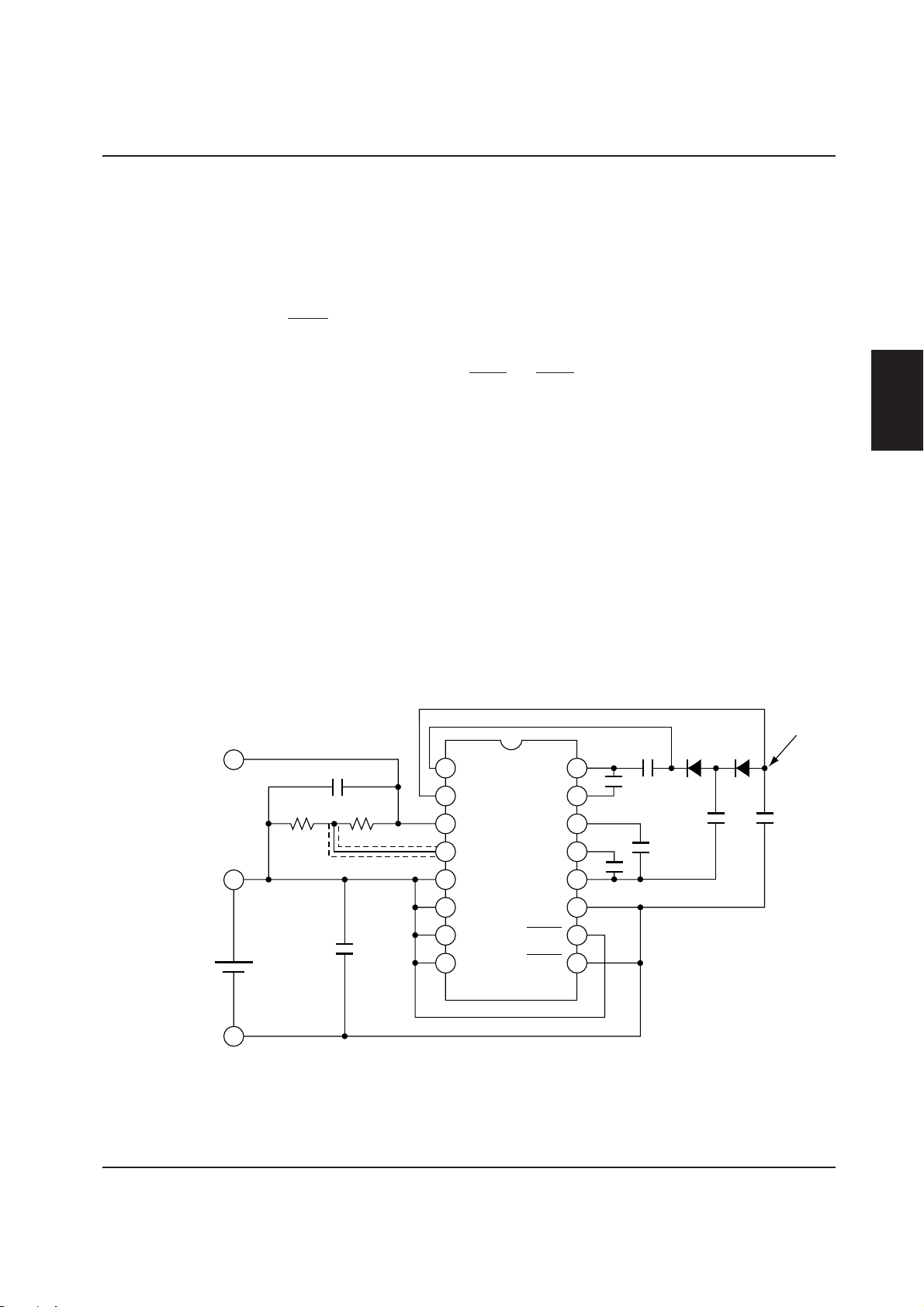

BLOCK DIAGRAM

V

DD

OSC1

OSC2

V

I

CR oscillator

Voltage converter

CAP1+

CAP1–

V

O

PIN ASSIGNMENTS

NC

OSC2

OSC1

DD

V

1

2

S1F76600M0B0

3

4

/C0B0

8

7

6

5

V

I

V

O

CAP1–

CAP1+

Series

S1F76600

PIN DESCRIPTIONS

Pin No. Pin name Description

1 NC No connection

2 OSC2 Resistor connection. Open when using external clock

3 OSC1 Resistor connection. Clock input when using external clock

4VDD Positive supply (system VCC)

5 CAP1+ Positive charge-pump connection

6 CAP1– Negative charge-pump connection

7VO ×2 multiplier output

8VI Negative supply (system ground)

S1F70000 Series EPSON 1–1

Technical Manual

Page 19

S1F76600 Series

SPECIFICATIONS

Absolute Maximum Ratings

Parameter Symbol Rating Unit

Input voltage range VI –10.0 to 0.5 V

Output voltage range VO Min. –20.0 V

Power dissipation PD

300 (DIP)

mW

150 (SOP)

Operating temperature range Topr –40 to +85 ˚C

Storage temperature range

Soldering temperature(for 10s). See note.

Tstg –65 to +150 ˚C

Tsol 260 ˚C

Note:

Temperatures during reflow soldering must remain within the limits set out in LSI Device Precautions.

Never use solder dip to mount S1F70000 series power supply devices.

Recommended Operating Conditions

V

DD = 0V, Ta = –40 to +85˚C unless otherwise noted

Parameter Symbol Condition Rating Unit

Min. Typ. Max.

ROSC = 1MΩ,

C1/C2≤1/20, C2≥10µF, — — –1.5

Oscillator startup voltage V

STA Ta = –20 to +85˚C V

See note 1.

ROSC = 1MΩ — — –2.2

Oscillator shutdown voltage

VSTP ROSC = 1MΩ –1.5 — — V

Load resistance RL

RL min

See note 2.

——Ω

Output current IO — — 30.0 mA

Clock frequency fOSC 10.0 — 30.0 kHz

CR oscillator network

resistance

R

OSC 680 — 2,000 kΩ

Capacitance C1, C2 3.3 — — µF

Notes:

1. The recommended circuit configuration for low-voltage operation (when V

I is between –1.2V and

–2.2V) is shown in the following figure. Note that diode D1 should have a maximum forward voltage of

0.6V with 1.0mA forward current.

2. R

L min can be varied depending on the input voltage.

1–2 EPSON S1F70000 Series

Technical Manual

Page 20

S1F76600 Series

3. RL min is a function of VI.

5

4

3

2

1

Minimum load resistance (kΩ)

0

1MΩ

1.0

V

1

2

3

4

STA1

Battery

1.5 2.0

Input voltage (V)

V

STA2

8

7

6

5

3.0

+

C2

22µF

C1

+

10µF

4.0 5.0 6.0

C

R

L

L

D1

Series

S1F76600

Electrical Characteristics

VDD = 0V, Ta = –40 to +85˚C unless otherwise noted

Parameter Symbol Condition Rating Unit

Min. Typ. Max.

Input voltage VI –8.0 — –1.5 V

Output voltage VO –16.0 — — V

Multiplier current IOPR

RL = ∞, ROSC = 1MΩ

V

I = –5V

—2030µA

Quiescent current IQ RL =∞, VI = –8V — — 2.0 µA

Clock frequency fOSC

ROSC = 1MΩ, VI = –5V

16 20 24 kHz

Output impedance RO IO = 10mA, VI = –5V — 75 100 Ω

Multiplication efficiency Peff IO = 5mA, VI = –5V 90 95 — %

OSC1 Input leakage current

S1F70000 Series EPSON 1–3

Technical Manual

ILKI VI = –8V — — 2.0 µA

Page 21

S1F76600 Series

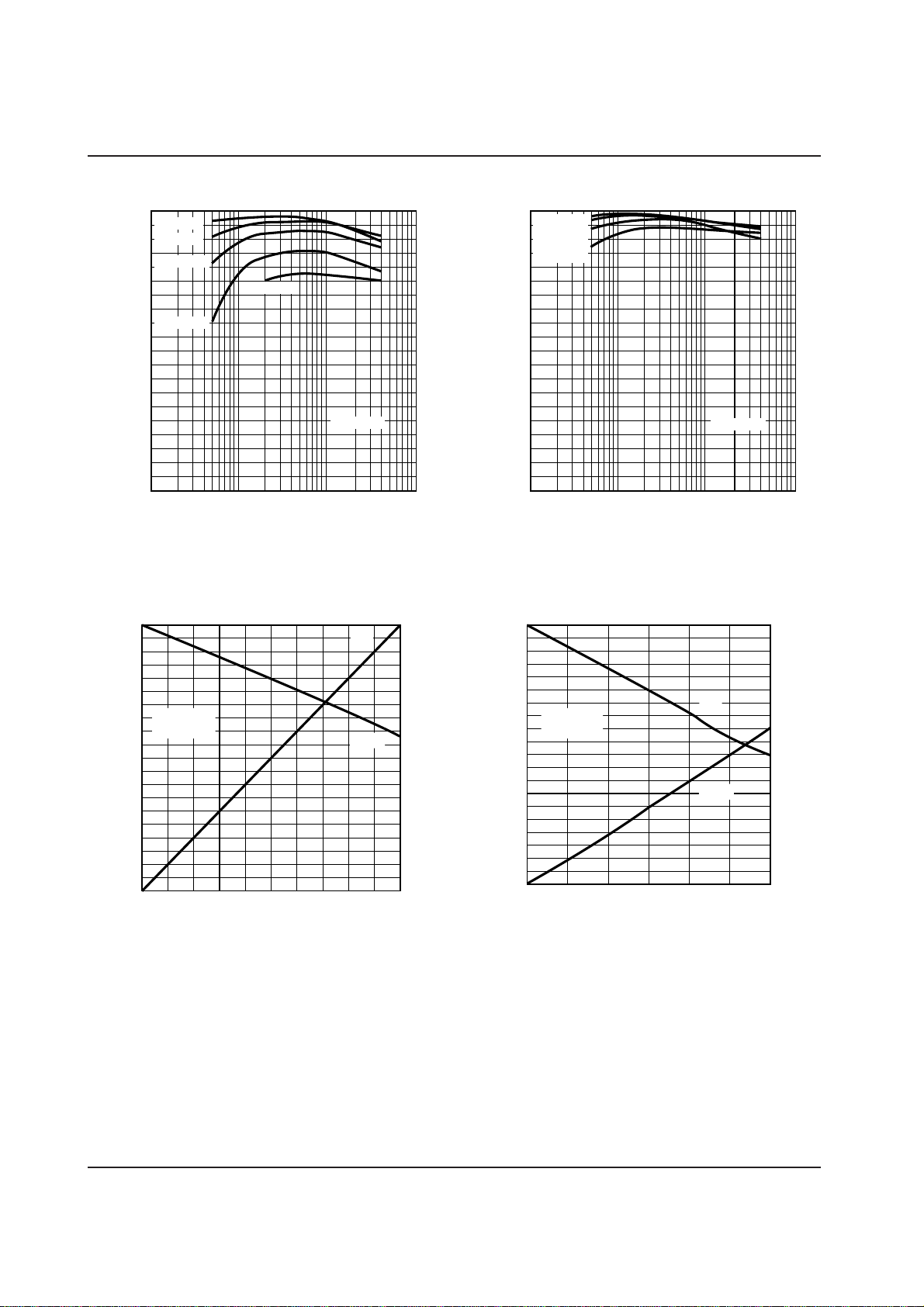

Typical Performance Characteristics

1000

Ta = 25°C

26

25

24

23

22

21

20

19

VI = –5.0V

I

= –3.0V

V

100

I = –5V

V

VI = –3V

V

I = –2V

18

I

= –2.0V

V

fOSC [kHz]

10

17

16

fOSC [kHz]

15

14

13

12

11

10

9

1

10 100 1000 10000

ROSC [kΩ]

8

–40 –20 0 20 40

Ta [°C]

60 80 100

(1) Clock frequency vs. External resistance (2) Clock frequency vs. Ambient temperature

50

f

OSC

45

= 40kHz

40

Ta = 25°C

35

f

OSC

=

20kHz

30

[µA]

25

f

OSC

OPR

l

20

=

10kHz

15

10

5

0

–7 –6 –5 –4 –3 –2 –1 0

VI [V]

0

Ta = 25˚C

I

= –5.0V

V

–5

[V]

O

V

–10

–15

0 1020304050

IO [mA]

(3) Multiplier current vs. Input voltage (4) Output voltage vs. Output current

1–4 EPSON S1F70000 Series

Technical Manual

Page 22

S1F76600 Series

0

Ta = 25°C

V

I

= –3.0V

0

–1

Ta = 25°C

V

I

= –2.0V

–2

[V]

–3

[V]

O

V

–5

O

V

–4

–5

–10

0102030

IO [mA]

–6

0 23456789101

IO [mA]

(5) Output voltage vs. Output current (6) Output voltage vs. Output current

300

Ta = 25°C

O = 7mA

I

300

Ta = 25°C

O = 10mA

I

Series

S1F76600

200

RO [Ω]

100

0

–7 –6 –5 –4 –3 –2 –1 0

VI [V]

200

RO [Ω]

100

0

–7 –6 –5 –4 –3 –2 –1 0

VI [V]

(7) Output impedance vs. Input voltage (8) Output impedance vs. Input voltage

S1F70000 Series EPSON 1–5

Technical Manual

Page 23

S1F76600 Series

100

IO = 2mA

IO = 5mA

90

IO = 10mA

80

70

60

IO = 20mA

IO = 30mA

50

Peff [%]

40

30

20

10

0

1 10 100 1000

fOSC [kHz]

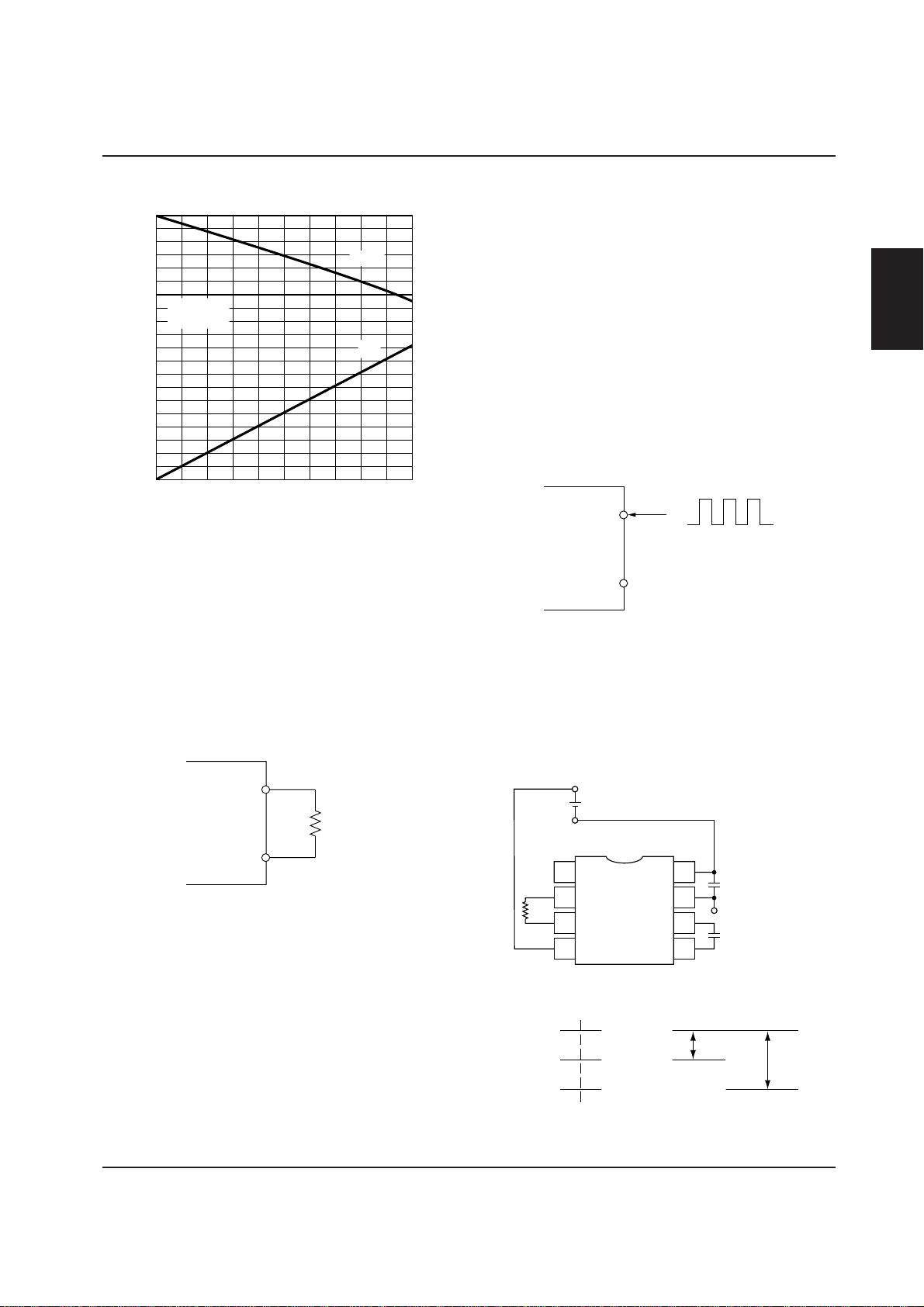

(9) Multiplication efficiency vs. (10) Multiplication efficiency vs.

Clock frequency Clock frequency

100

90

80

70

Ta = 25°C

V

I

60

50

Peff [%]

40

30

20

10

= –5.0V

0

0

10 20 30 40 50

IO [mA]

VI = –5.0V

I

I

Peff

100

90

80

70

60

50

40

30

20

10

0

[mA]

I

I

100

IO = 0.5mA

I

O

= 1.0mA

90

IO = 2.0mA

I

O

= 4.0mA

80

70

60

50

Peff [%]

40

30

20

VI = –3.0V

10

0

1 10 100 1000

f

OSC

[kHz]

100

90

80

I

70

60

Ta = 25°C

V

I

= –3.0V

I

50

40

Peff [%]

Peff

30

20

10

0

0 5 10 15 20 25 30

IO [mA]

100

90

80

70

60

50

40

30

20

10

0

[mA]

I

I

(11) Multiplication efficiency/input current (12) Multiplication efficiency/input current

vs. Output current vs. Output current

1–6 EPSON S1F70000 Series

Technical Manual

Page 24

S1F76600 Series

100

90

80

70

Ta = 25°C

V

I = –2.0V

60

50

Peff [%]

40

30

20

10

0

012345678910

IO [mA]

Peff

II

40

36

32

28

24

20

16

12

8

4

0

(13) Multiplication efficiency/input current

vs. Output current

FUNCTIONAL DESCRIPTIONS

CR Oscillator

S1F76600 has a built-in CR oscillator as the internal oscillator, and an external oscillation resistor R

nected between the pins OSC1 and OSC2 before operation.

OSC is con-

far as the

straight portion (500kΩ < R

R

OSC = A • (1/fOSC)

(A : Constant, When GND is 0V and V

approximately 2.0 × 10

So, the R

I [mA]

I

(Recommended oscillation frequency : 10kHz to 30kHz

(R

OSC value can be obtained from this formula.

OSC : 2MΩ to 680kΩ))

OSC < 2MΩ) is concerned:

10

(I/F).)

DD is 5V, A is

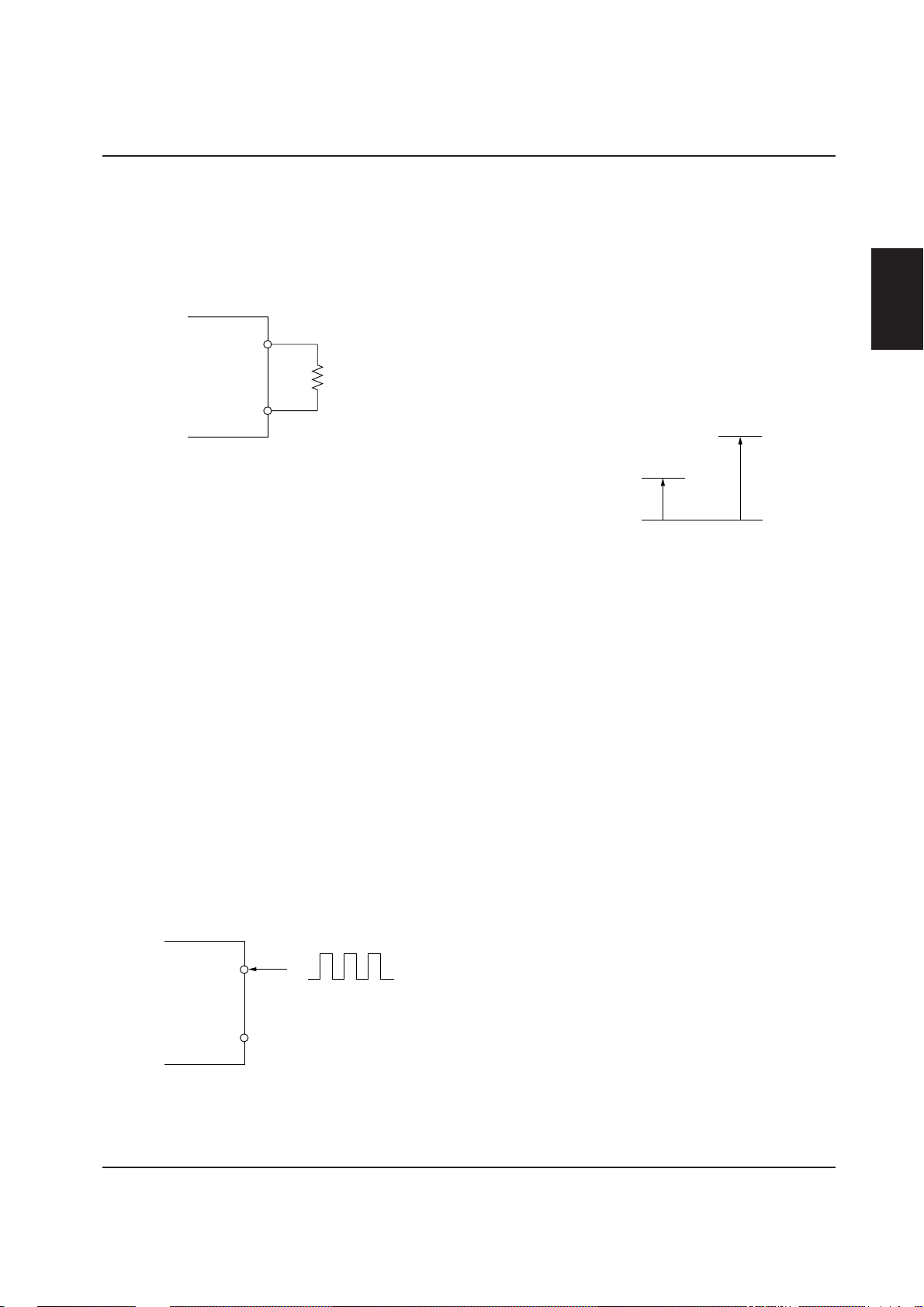

When the external clock operates, make the pin OSC2

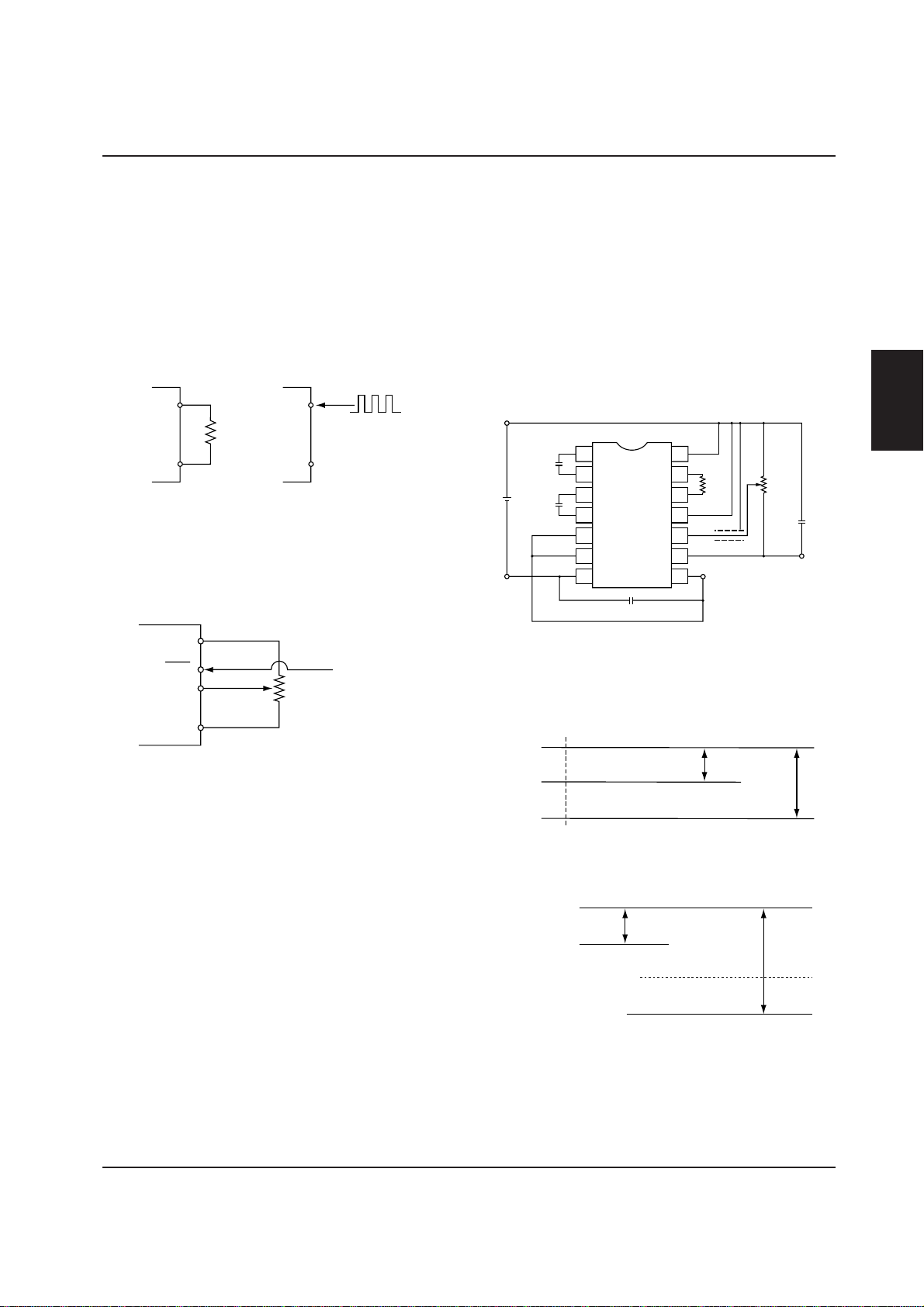

open as shown below and input the 50% duty of the external clock from the pin OSC1.

OSC1

External clock

OSC2

Open

Voltage Multiplier

The voltage multiplier uses the clock signal from the

oscillator to double the input voltage. This requires two

external capacitors—a charge-pump capacitor, C1, between CAP1+ and CAP1–, and a smoothing capacitor,

C2, between V

I and VO.

Series

S1F76600

= 0 V

V

OSC1

(Note 1)

OSC

R

V

= –5 V

I

DD

5 V

OSC2

8

+

C2

10µF

7

6

5

+

= –10V (2VI)

V

O1

C1

10µF

Note 1

Since the oscillation frequency varies with wiring ca-

1

2

1MΩ

3

4

pacitance, make the cables between the terminals OSC1

and OSC2 and R

When setting the external resistor R

able for f

OSC that brings about the maximum efficiency

from characteristics graph (9) and (10). The relations

between R

expressed approximately with the following formula as

S1F70000 Series EPSON 1–7

Technical Manual

OSC as short as possible.

OSC, find ROSC suit-

OSC and fOSC in characteristics graph (1) are

Doubled potential levels

V

CC

(+5V)

GND

(–5V)

DD

= 0 V

V

I

= –5 V

V

VO = (2VI) = –10 V

Page 25

S1F76600 Series

TYPICAL APPLICATIONS

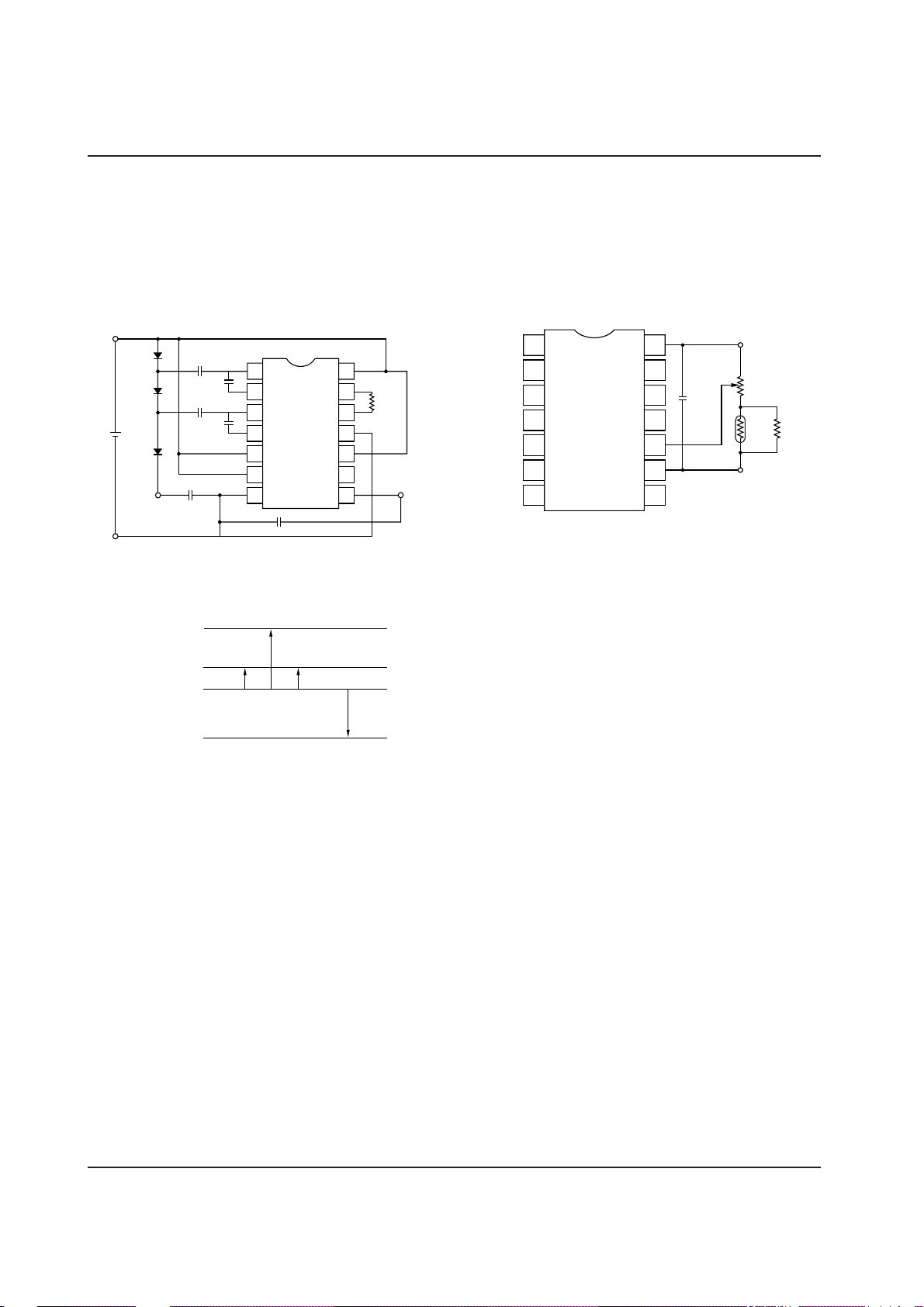

Parallel Connection

Connecting two or more chips in parallel reduces the

output impedance by 1/n, where n is the number of devices used.

V

= 0 V

DD

V

= –5 V

I

5 V

1

2

1MΩ

3

4

8

+

C2

10µF

7

6

C1

+

10µF

5

Serial Connection

Connecting two or more chips in series obtains a higher

output voltage than can be obtained using a parallel

V

= 0 V

DD

= –5 V

V

I

1MΩ

5 V

1

2

3

4

8

+

C2

10µF

7

6

C1

+

10µF

5

1

2

1MΩ

3

4

8

7

6

C1

+

10µF

5

= –10 V

V

O

connection, however, this also raises the output impedance.

' = VI = –5

V

DD

1

2

1MΩ

3

4

8

+

C2

10µF

7

6

C1

+

10µF

5

V

= –10 V = VI'

V

O

' = –15 V

O

Potential levels

V

DD

(0 V)

I

(–5 V)

V

O

(–10 V)

V

Primary stage Secondary stage

VDD'

I

V

'

O

' (–15 V)

V

1–8 EPSON S1F70000 Series

Technical Manual

Page 26

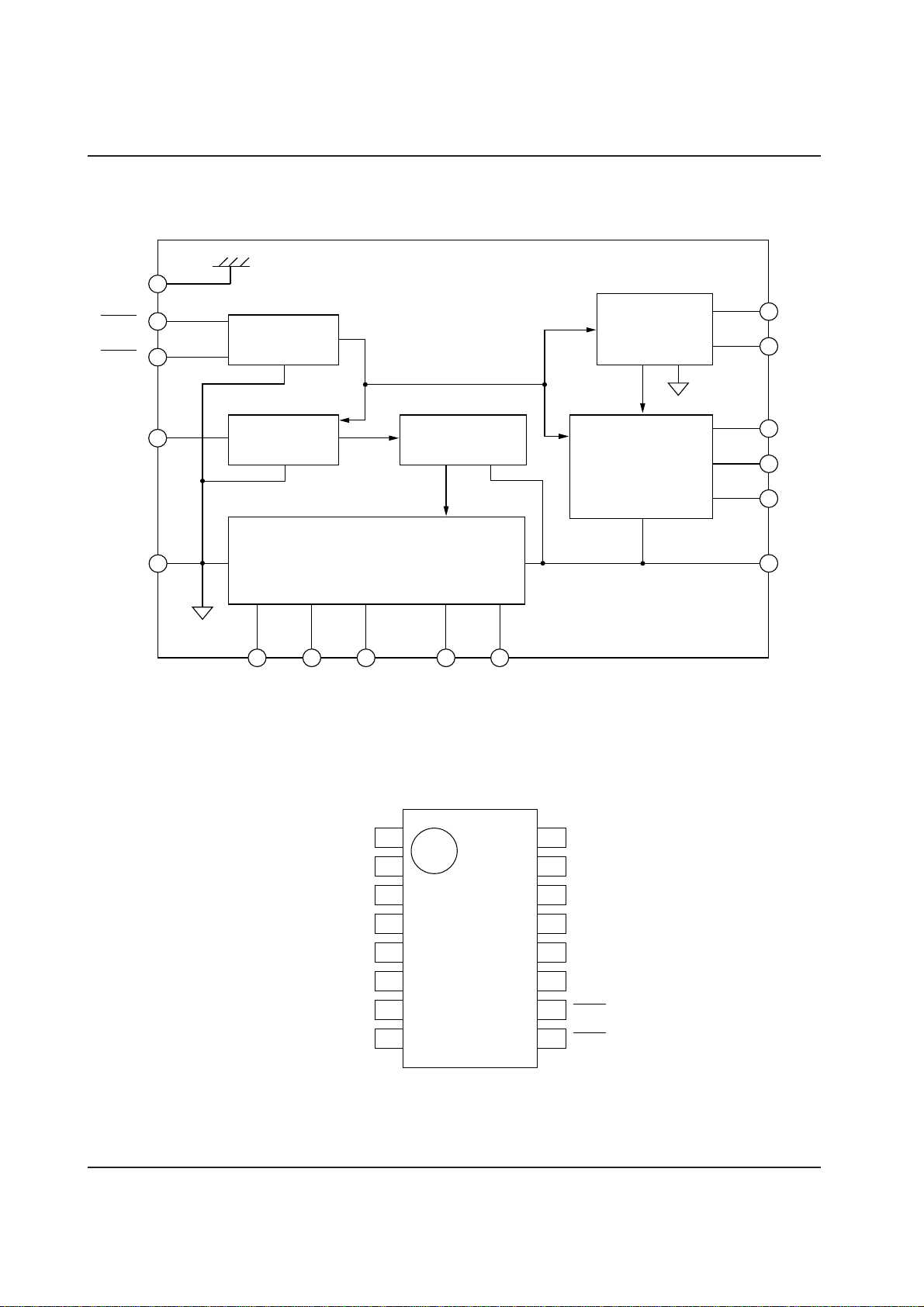

Positive Voltage Conversion

Diodes can be added to a circuit connected in parallel to

make a negative voltage positive.

= 0 V

V

DD

V

= –5 V

I

1MΩ

5 V

V

1

2

3

4

8

7

6

5

Simultaneous Voltage Conversion

Combining a multiplier circuit with a positive voltage

conversion circuit generates both –10 and 3.8 V outputs

from a single input.

' = 3.8 V

O

C2

+

10µF

C1

+

10µF

Potential levels

V

O2

= 3.8 V

S1F76600 Series

Series

S1F76600

= –5 V

V

I

1MΩ

1

2

3

4

VDD = 0 V

5 V

V

DD

= 0 V

I

= –5 V

V

O1

= –10 V

V

V

= 3.8 V

O2

C2

10µF

V

O1

C1

10µF

C4

10µF

= –10 V

C3

10µF

++

+

8

7

6

+

5

S1F70000 Series EPSON 1–9

Technical Manual

Page 27

S1F76620 Series

S1F76620 Series CMOS DC/DC Converter (Voltage Doubler)

DESCRIPTION

S1F76620 is a high efficiency and low power consumption CMOS DC/DC converter. It enables to obtain 2

times step-up output (3.0 to 16V) from input voltage

(1.5 to 8V). Also, S1F76620 enable to drive ICs (liquid

crystal driver, analog IC, etc.), which require another

power supply in addition to logic main power supply,

with a single power supply, and it is suitable for micro

power IC of hand-held computers, handy devices, etc.

due to its small power consumption.

BLOCK DIAGRAM

V

DD

FEATURES

(1) High efficiency and low power consumption

CMOS DC/DC converter

(2) Easy voltage conversion from input voltage V

to positive potential side or negative potential side

• Input V

2V

DD (5V) to output –VDD (–5V),

DD (10V)

(3) Output current : Max. 30mA

(V

DD = 5V)

(4) Power conversion efficiency : Typ. 95%

(5) Possibility of series connection

(In 2-piece use, V

DD = 5V, VO = 15V)

(6) Low voltage operation : Suitable for

battery drive

(7) Built-in CR oscillator

(8) SOP4-8pin······························ S1F76620M0A0

Bare Chip ······························· S1F76620D0A0

Voltage conversion circuit

DD (5V)

V

O

OSC1

OSC2

P

OFF

GND

CR oscillator

CAP1+ CAP1–

1–10 EPSON S1F70000 Series

Technical Manual

Page 28

PIN DESCRIPTIONS

Pin Assignments

S1F76620 Series

Pin descriptions

Pin No.

1

2

3

Pin name

POFF

GND (VSS)

OSC1

POFF

GND

OSC1

OSC2

1

2

3

4

8

7

6

5

O

V

CAP1+

CAP1–

V

DD

Pin Assignments of SOP4-8pin

Description

Input pin for power off control.

Power pin. (Minus side, System GND)

Oscillation resistor connection pin. Works as the clock input pin when the

external clock operates.

Series

S1F76620

4

5

6

7

8

S1F70000 Series EPSON 1–11

Technical Manual

OSC2

VDD

CAP1–

CAP1+

VO

Oscillation resistor connection pin. Opens when the external clock operates.

Power pin. (Plus side, System VCC)

Pump up capacitor minus side connection pin for 2 times step-up.

Pump up capacitor plus side connection pin for 2 times step-up.

Output pin at the time of 2 times step-up.

Page 29

S1F76620 Series

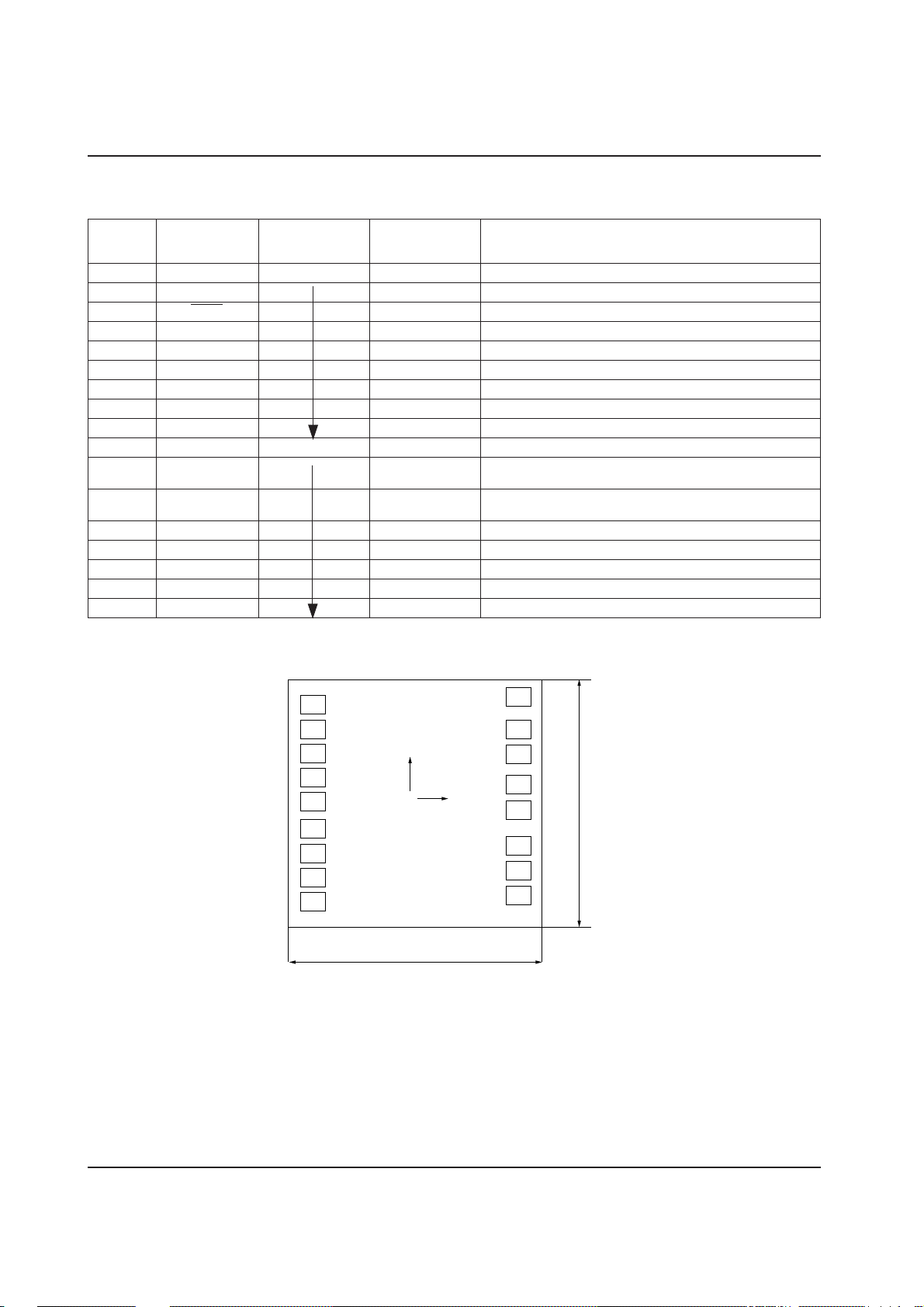

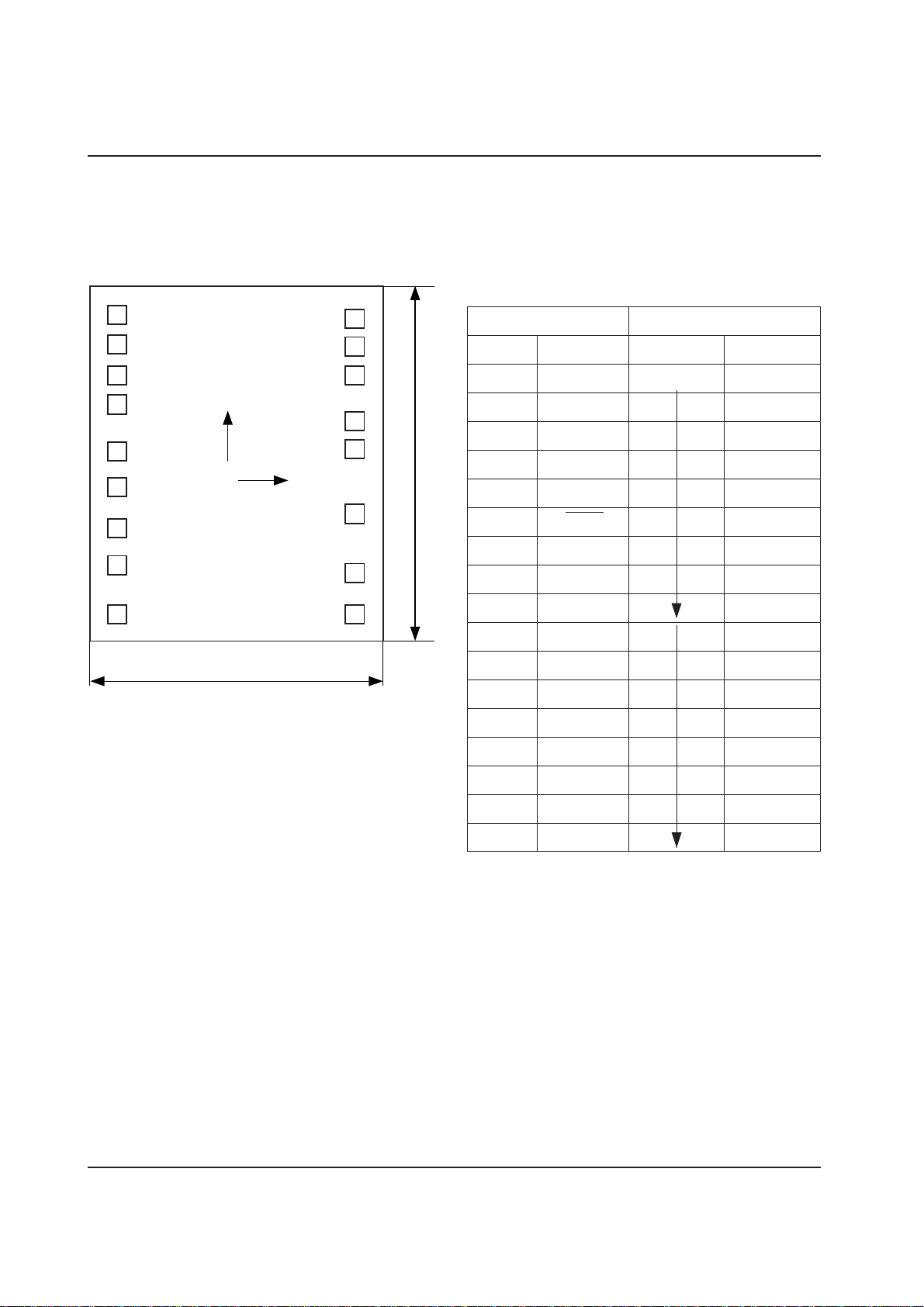

Pad Center Coordinates (S1F76620D0A0)

Pad No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

Pad name

(NC)

(NC)

POFF

(NC)

(NC)

(NC)

GND (VSS)

OSC1

OSC2

VDD

CAP1–

CAP1+

(NC)

VO

(NC)

(NC)

(NC)

Pad center

coordinates

µm)

X (

–984

984

coordinates

Pad center

µm)

Y (

1096

788

580

390

96

–218

–510

–802

–1094

–1134

–892

–514

182

372

750

942

1134

Description

—

—

Input pin for power off control

—

—

—

Power input pin (Minus side)

Oscillation resistor connection pin

Oscillation resistor connection pin

Power input pin (Plus side)

Pump up capacitor minus side connection pin for 2

times step-up

Pump up capacitor plus side connection pin for 2

times step-up

—

2 times step-up output pin

—

—

—

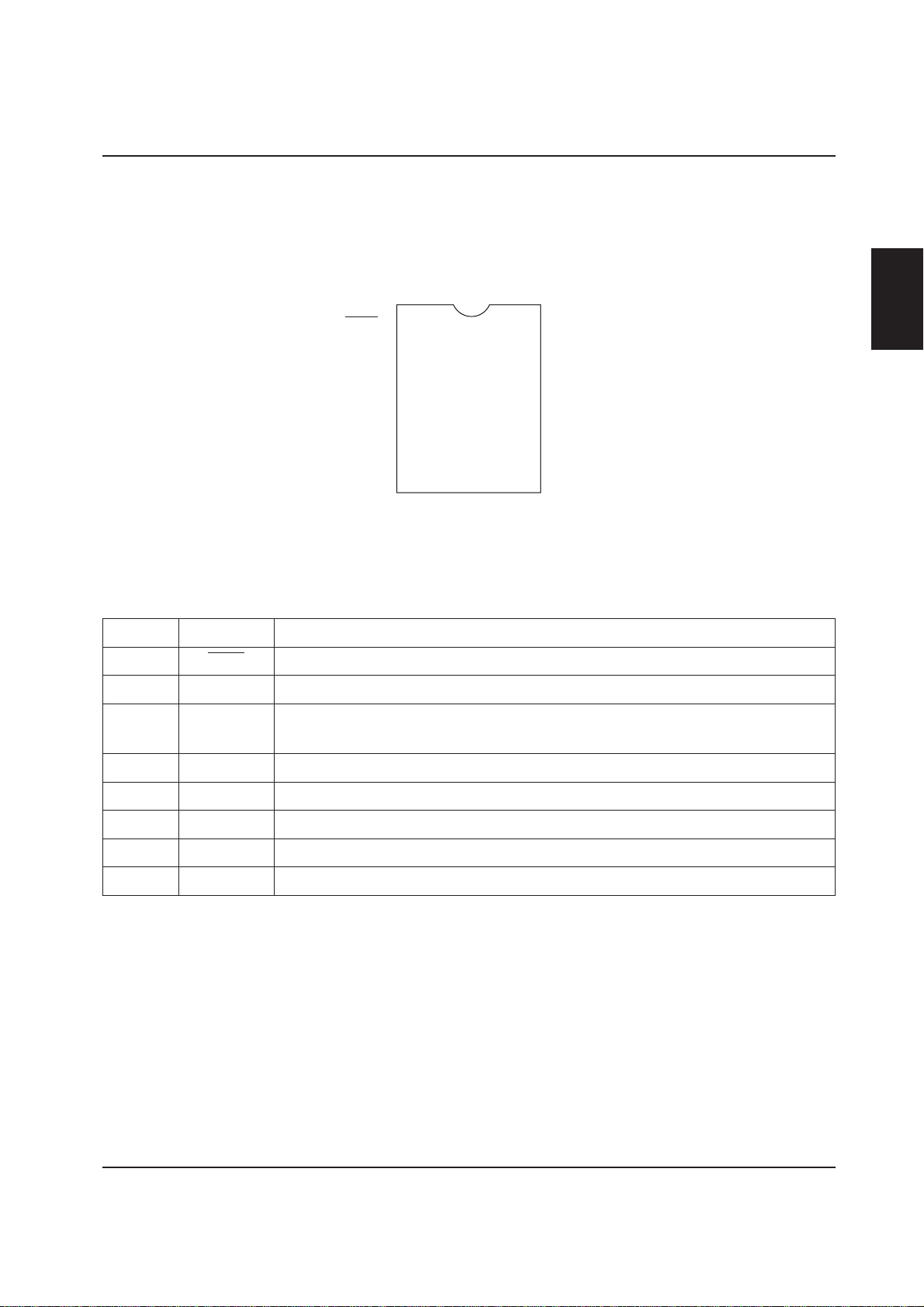

Chip External Shape

Y

+

(0,0)

2.30mm

Pad Assignment

Pad aperture : 100µm × 100µm Chip thickness : 400µm

Note

Do not bond the NC pad.

X

2.60mm

1–12 EPSON S1F70000 Series

Technical Manual

Page 30

FUNCTIONAL DESCRIPTIONS

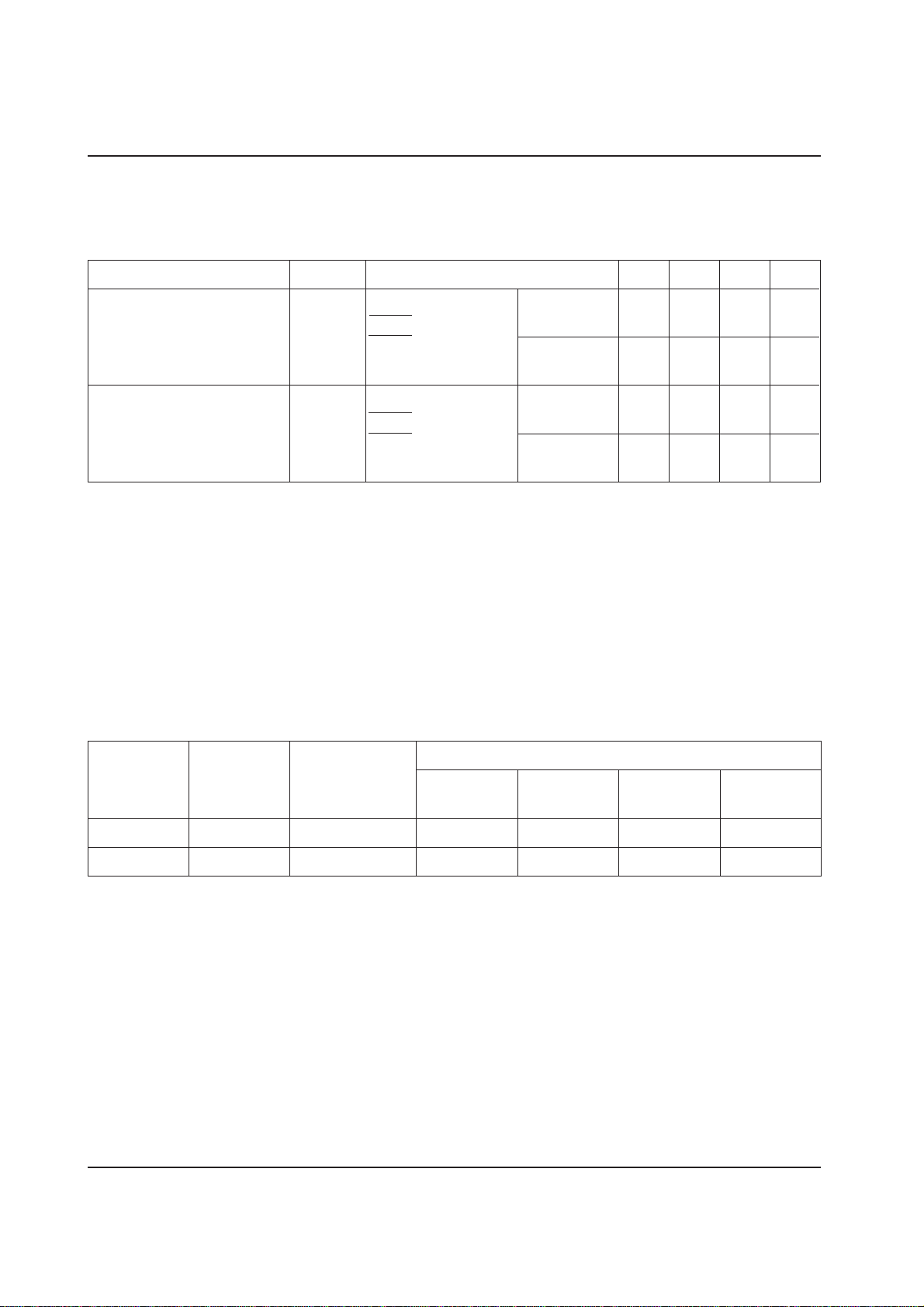

CR Oscillator

S1F76620 has a built-in CR oscillator as the internal oscillator, and an external oscillation resistor R

nected between the pins OSC1 and OSC2 before operation.

OSC1

OSC2

(Note 1)

R

OSC is con-

OSC

S1F76620 Series

Voltage Conversion Circuit

The voltage conversion circuit uses clocks generated in

the CR oscillator to double the input supply voltage

V

DD.

In case of 2 times step-up, 2 times voltage (2V

the input voltage is obtained from the V

pump up capacitor is connected between CAP1+ and

CAP2– and a smoothing capacitor is connected between V

When GND is 0 and V

DD and VO outside.

DD is 5, the relations between

input/output and voltage are as shown below:

CAP1=2VDD=10V

DD) of

O pin when a

Series

S1F76620

Note 1

Since the oscillation frequency varies with wiring capacitance, make the cables between the terminals OSC1

and OSC2 and R

When setting the external resistor R

able for f

OSC that brings about the maximum efficiency

OSC as short as possible.

OSC, find ROSC suit-

from characteristics graph (9) and (10). The relations

between R

OSC and fOSC in characteristics graph (1) are

expressed approximately with the following formula as

far as the

straight portion (500kΩ < R

R

OSC = A • (1/fOSC)

(A : Constant, When GND is 0V and V

approximately 2.0 × 10

So, the R

OSC value can be obtained from this formula.

OSC < 2MΩ) is concerned:

10

(I/F).)

DD is 5V, A is

(Recommended oscillation frequency : 10kHz to 30kHz

(R

OSC : 2MΩ to 680kΩ))

When the external clock operates, make the pin OSC2

open as shown below and input the 50% duty of the ex-

ternal clock from the pin OSC1.

V

DD

=5V

G

ND

=0V

OSC1

External clock

OSC2

S1F70000 Series EPSON 1–13

Technical Manual

Open

Page 31

S1F76620 Series

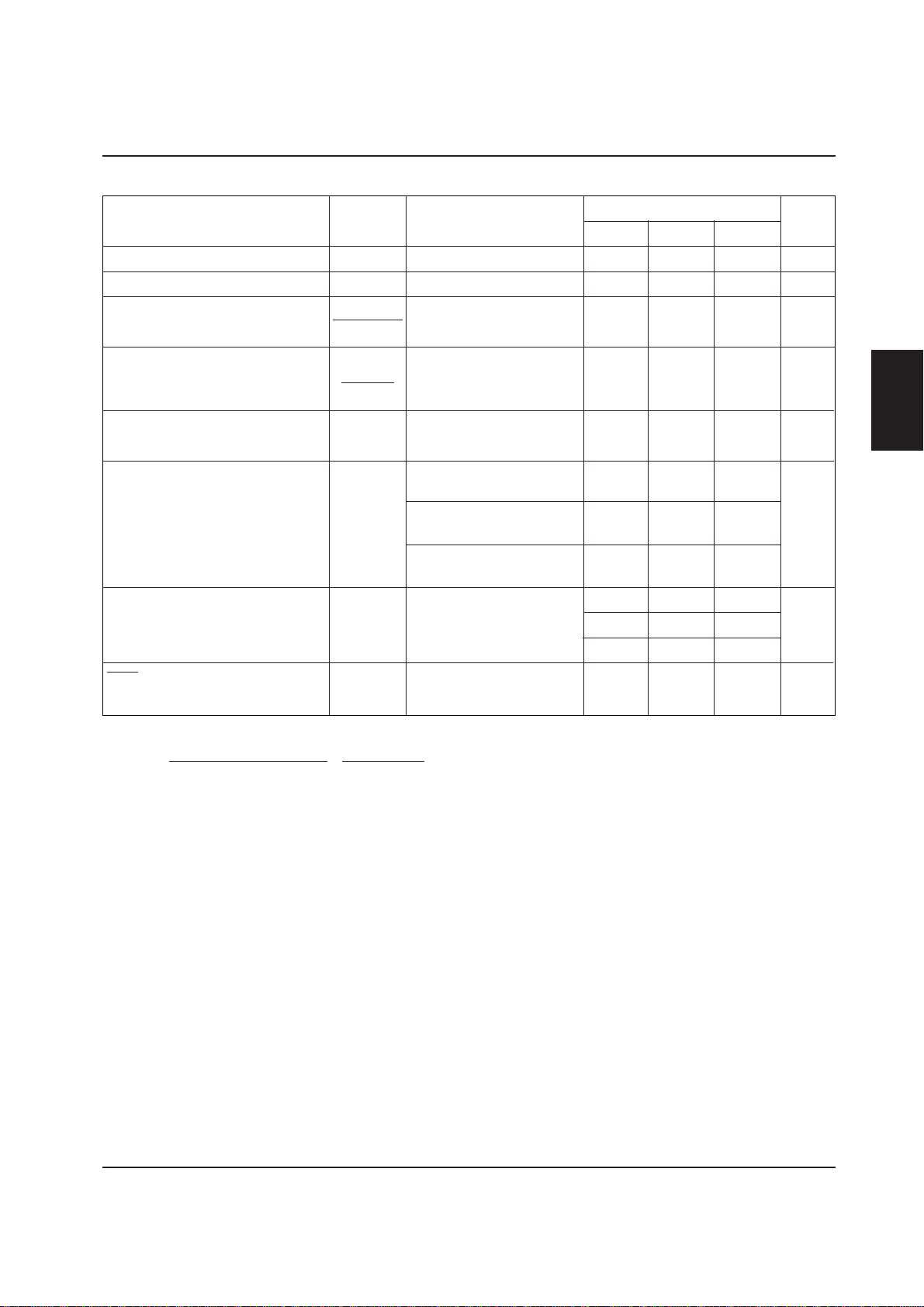

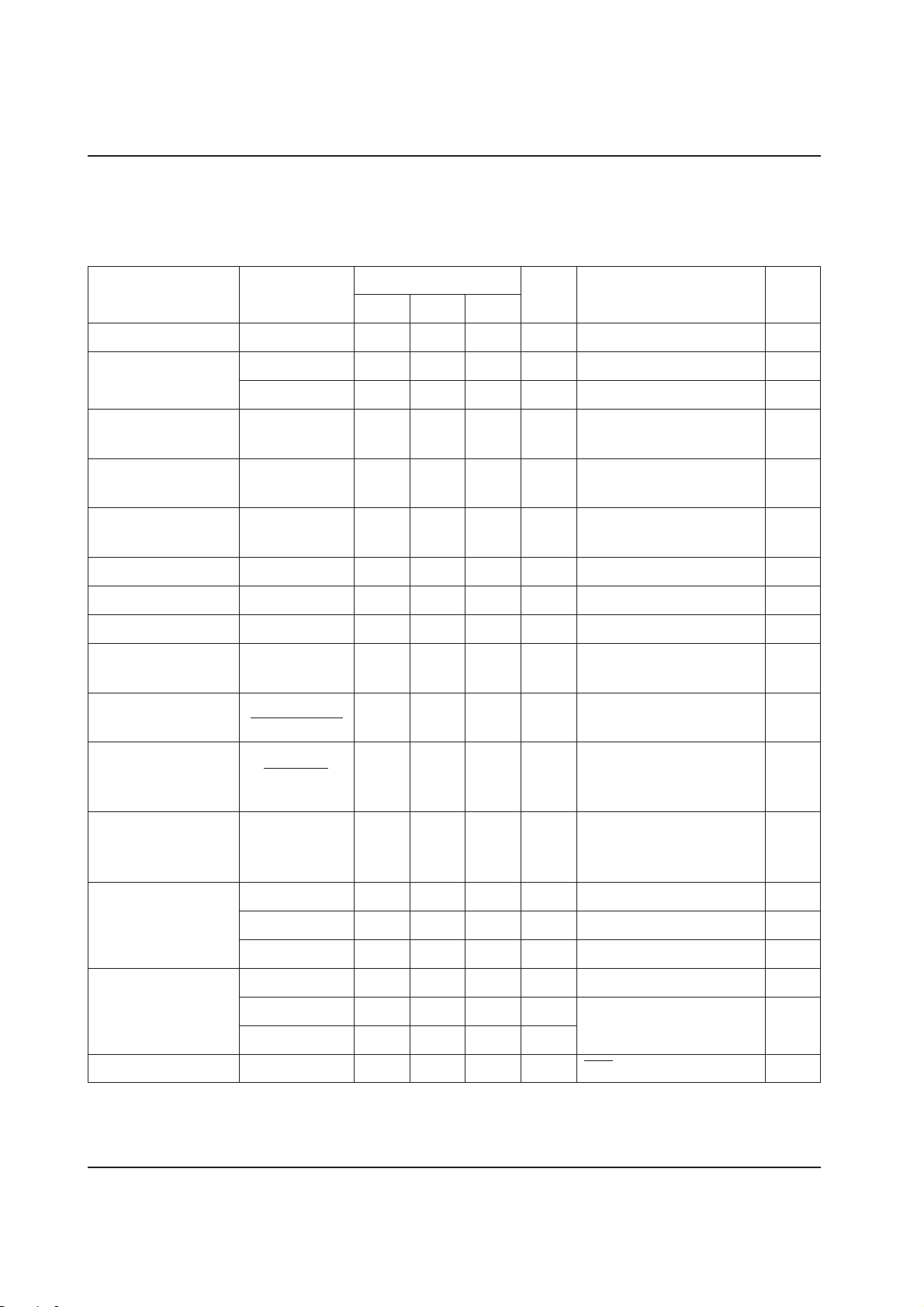

ELECTRICAL CHARACTERISTICS

Absolute Maximum Ratings

(Ta = –40 to +85°C)

Parameter

Input supply voltage

Input pin voltage

Output voltage

Output supply voltage

Output pin voltage

Allowable loss

Operating temperature

Storage temperature

Note 1

Under the conditions exceeding the above absolute maximum ratings, the IC may result in a permanent destruction.

An operation for a long period under the conditions of the above absolute maximum ratings may deteriorate the

reliability remarkably.

Note 2

All voltage values are based on GND being 0V.

Symbol

VIN

VI

VO

VCAP+

VCAP–

PD

Topr

Tstg

Min.

–0.5

–0.5

—

–0.5

–0.5

—

–40

–65

Rating

Max.

10.0

VDD + 0.5

20

VDD + 0.5

VO + 0.5

300

150

85

150

Unit

V

V

V

V

V

mW

°C

°C

Remarks

—

OSC1, OSC2

—

CAP+

CAP–

DIP-8pin

SOP-8pin

—

—

1–14 EPSON S1F70000 Series

Technical Manual

Page 32

Recommended Operating Conditions

S1F76620 Series

(Ta = –40 to +85°C)

Parameter

Symbol

Min.

Max.

Unit

ROSC = 1MΩ

Rating

Step-up start operation

Step-up stop voltage

VSTA1

VSTA2

VSTP

1.5

2.2

—

—

—

1.5

V

V

V

C

See note 2.

ROSC = 1MΩ

ROSC = 1MΩ

RLmin

Output load resistance

Output load current

Oscillation frequency

RL

IO

fOSC

See note 3.

—

10

—

30

30

Ω

mA

kHz

External resistor for

oscillation

Step-up capacitor

ROSC

C1, C2

680

3.3

2000

—

kΩ

µF

Note 1

All voltages are based on the GND being 0V.

Note 2

The figure below shows the recommended circuit for operation with low voltages (V

Remarks

2 ≥ 10µF CL/C2 ≥ 1/20

—

—

—

—

—

DD = 1.5 to 2.2V):

Series

S1F76620

C

*D

L

1

R

L

1

P

OFF

2

GND

3

OSC1

4

OSC2

* (DI (VF (IF=1mA) is recommended to be not more than 0.6V.)

CAP1+

CAP1–

8

O

V

7

6

5

V

DD

+

C

1

+

–

–

C

2

Recommended Circuit

Note 3

Lmin varies with input voltage. See Characteristics Graph (15).

R

S1F70000 Series EPSON 1–15

Technical Manual

Page 33

S1F76620 Series

Electrical Characteristics

(V

DD = 5V, Ta = –40 to +85°C)

Parameter

Symbol

Min.

Input supply voltage

Output voltage

VDD

VO

1.8

—

Step-up circuit current

consumption

Static current

Oscillation frequency

Output impedance

IOPR

IQ

fOSC

RO

—

—

16

—

Step-up power conversion efficiency

Input leak current

Peff

ILKI

90

—

Note 1

All voltage values are based on GND being 0V.

Rating

Typ.

—

—

35

—

20

85

95

—

Max.

8.0

16.0

50

1.0

24

130

—

1.0

Unit

V

V

µA

µA

kHz

Ω

%

µA

Remarks

—

—

ROSC = 1MΩ

—

ROSC = 1MΩ

IO = 10mA

IO = 5mA

OSC1 pin

1–16 EPSON S1F70000 Series

Technical Manual

Page 34

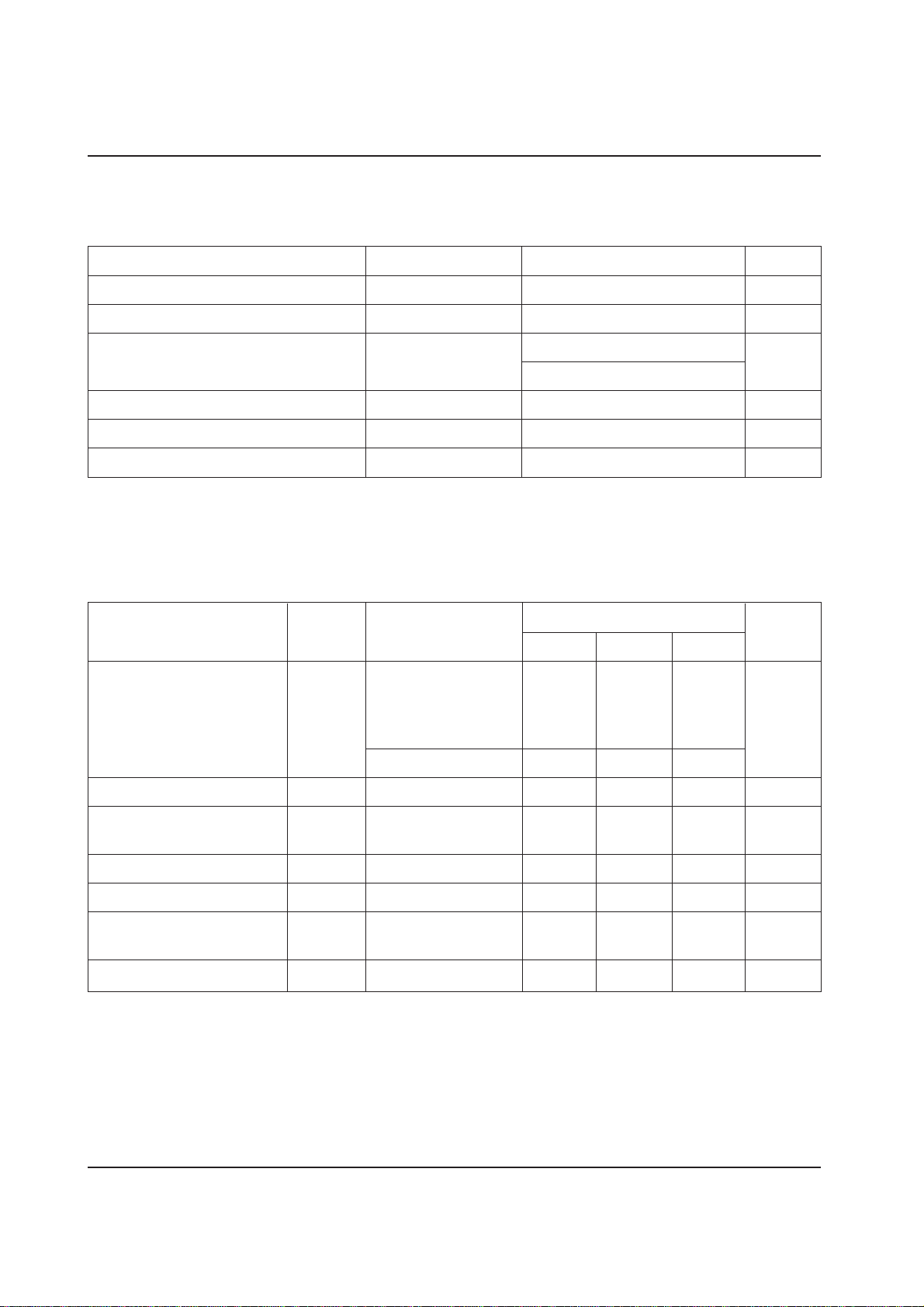

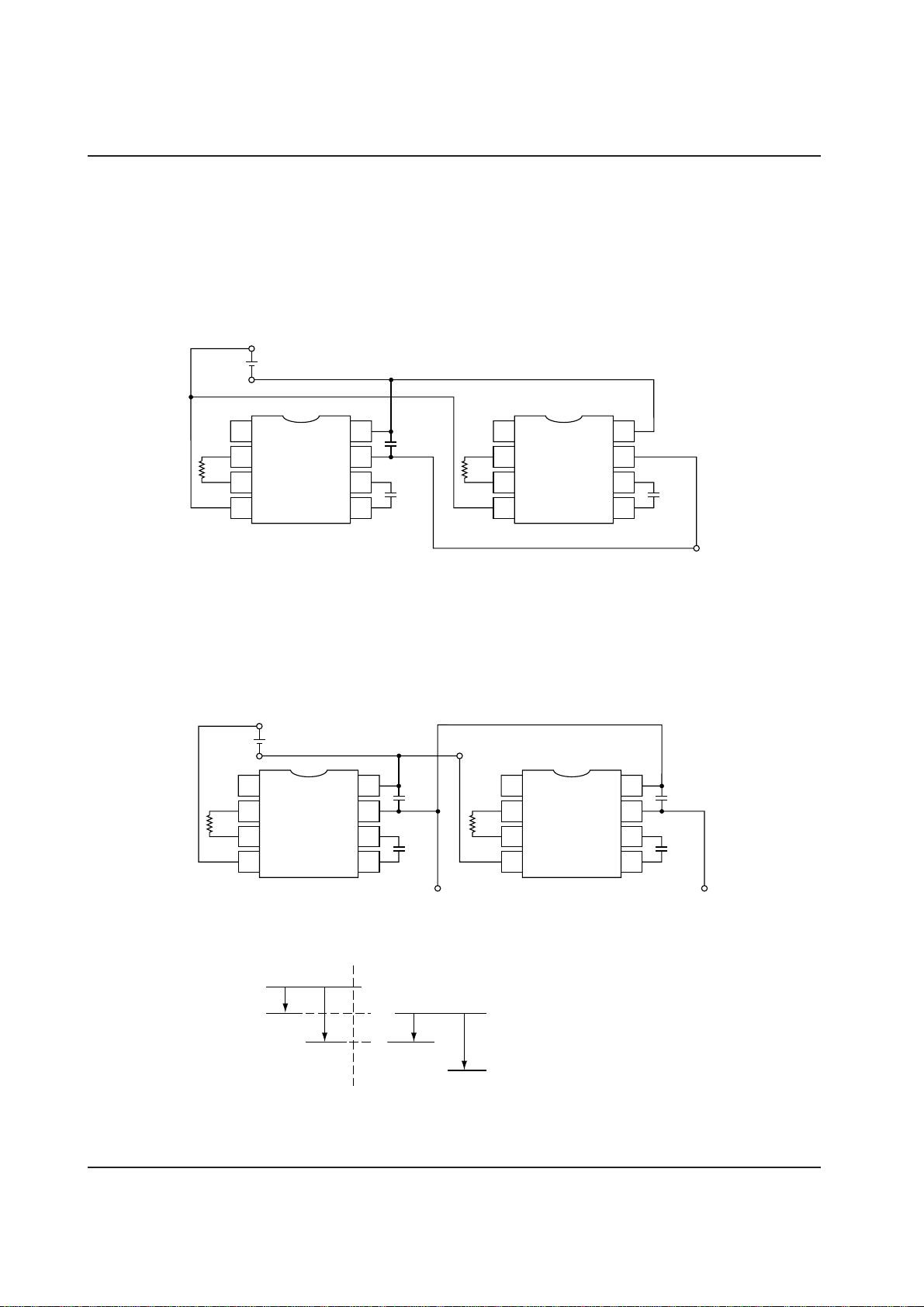

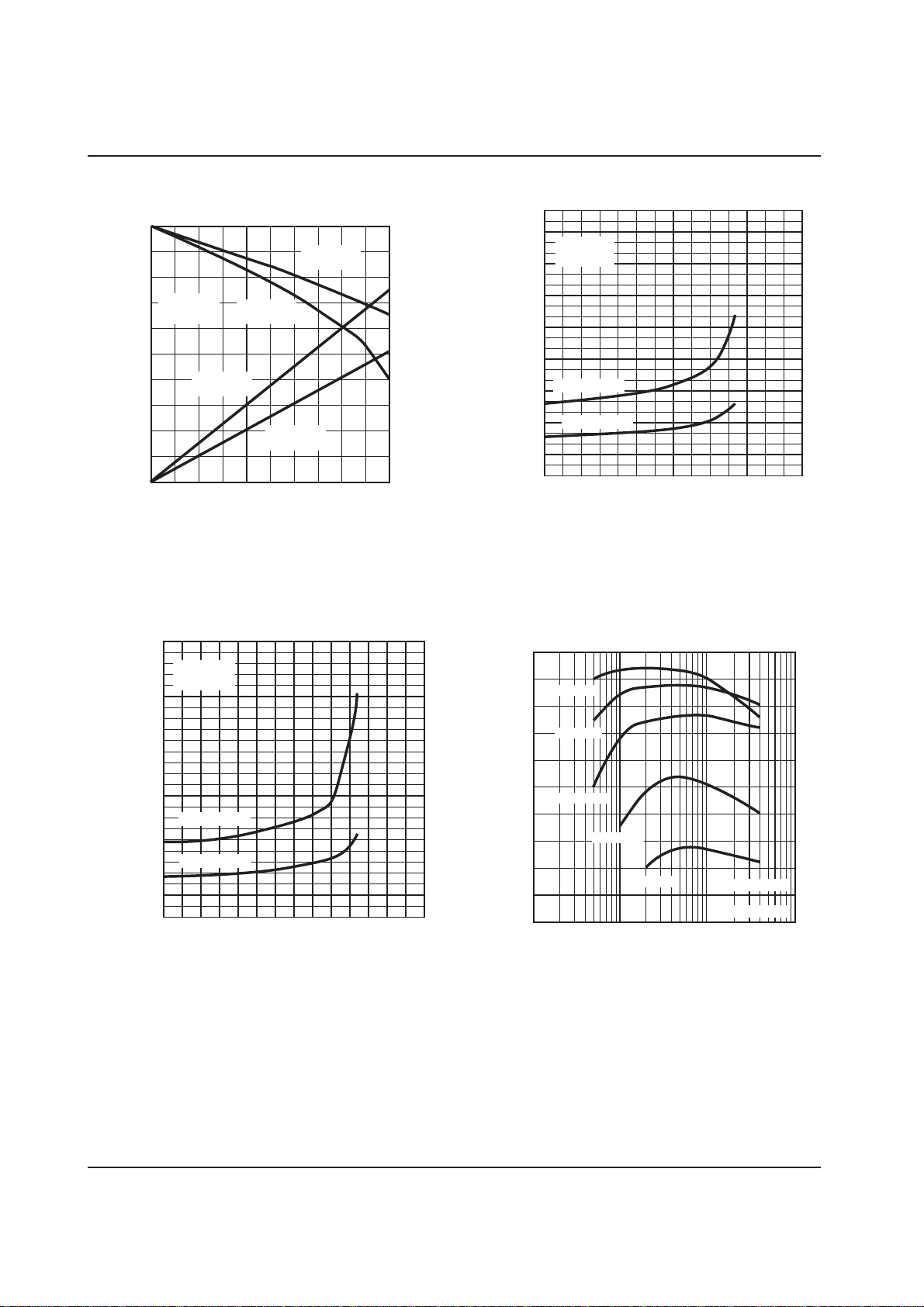

Characteristics Graph

S1F76620 Series

1000

Ta=25°C

VDD=5V

100

[kHz]

VDD=3V

OSC

f

10

VDD=2V

1

10 100 1000 10000

OSC

[kΩ]

R

(1) Oscillation frequency vs.

External resistance for oscillation

100

80

60

[µA]

40

OPR1

I

20

0

Ta=25°C

C

1=C2

=10µF

f

OSC

=40kHz

f

OSC

=20kHz

f

OSC

=10kHz

0123456

VDD[V]

30

28

26

24

22

20

[kHz]

OSC

18

f

VDD=5V

16

14

12

VDD=2V

VDD=3V

10

–40 –20 0 20 40 60 80 100

Ta[°C]

(2) Oscillation frequency vs. Temperature

10

9

8

7

6

[V]

5

O

V

4

3

Ta=25°C

2

V

DD

1

0

0 5 10 15 20 25 30

1=C2

C

=5V

=10µF

IO [mA]

Series

S1F76620

(3) Step-up circuit current consumption vs.

(4) Output voltage (V

O) vs. Output current 1

Input current

S1F70000 Series EPSON 1–17

Technical Manual

Page 35

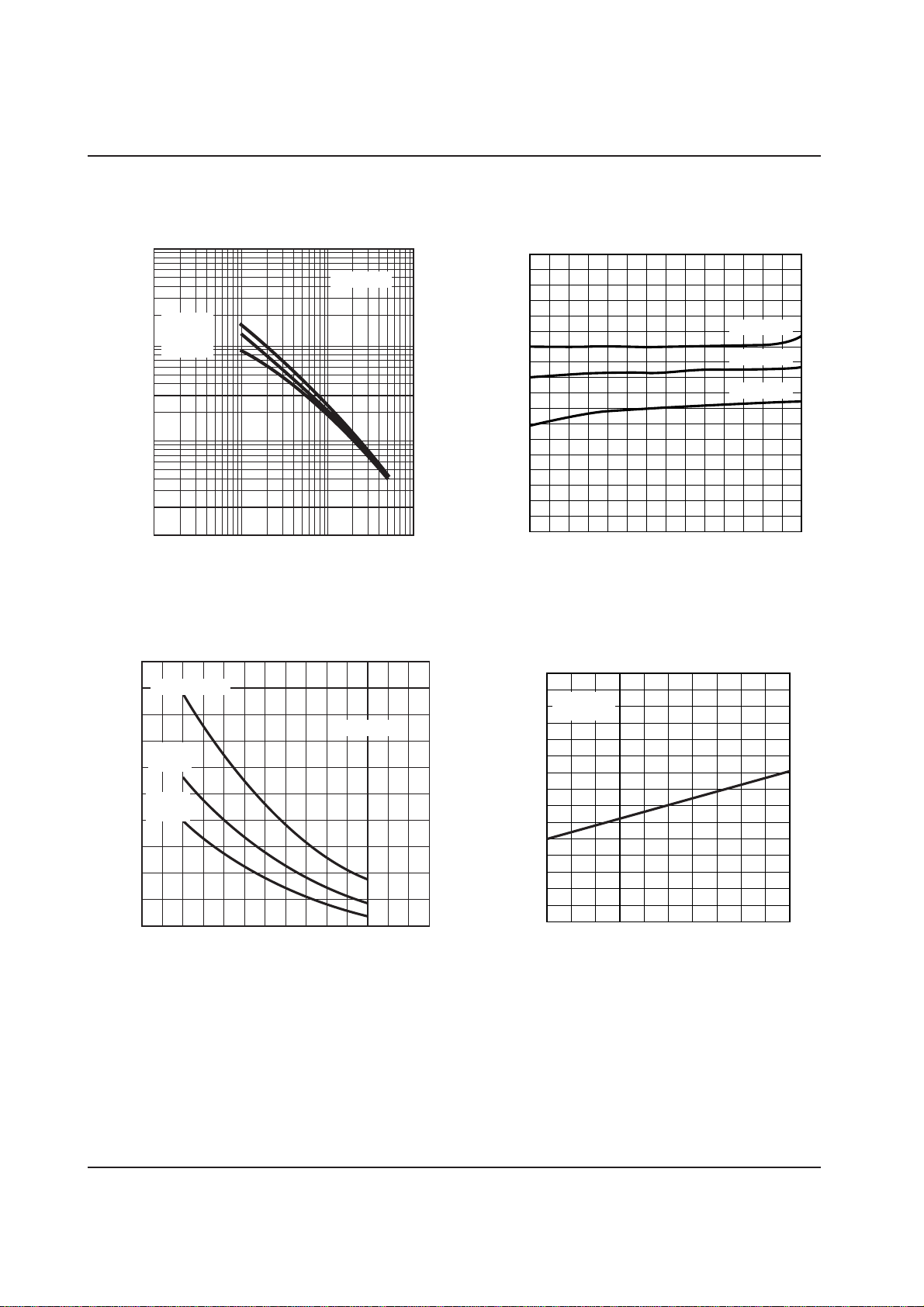

S1F76620 Series

6

4

5

3

4

[V]

O

V

3

[V]

O

V

2

2

Ta=25°C

1

V

DD

=3V

C

1=C2

=10µF

0

0 5 10 15 20

1

Ta=25°C

V

DD

=2V

C

1=C2

=10µF

0

012345678910

IO [mA] IO [mA]

(5) Output voltage (VO) vs. Output current 2 (6) Output voltage (VO) vs. Output current 3

300

250

300

250

Ta=25°C

I

O

=10mA

200

[Ω]

150

O

R

100

50

Ta=25°C

O

=5mA

I

0

0123456

DD

[V]

V

200

[Ω]

150

O

R

100

50

0

0123456

DD

[V]

V

(7) Output impedance vs. Input current 1 (8) Output impedance vs. Input voltage 2

1–18 EPSON S1F70000 Series

Technical Manual

Page 36

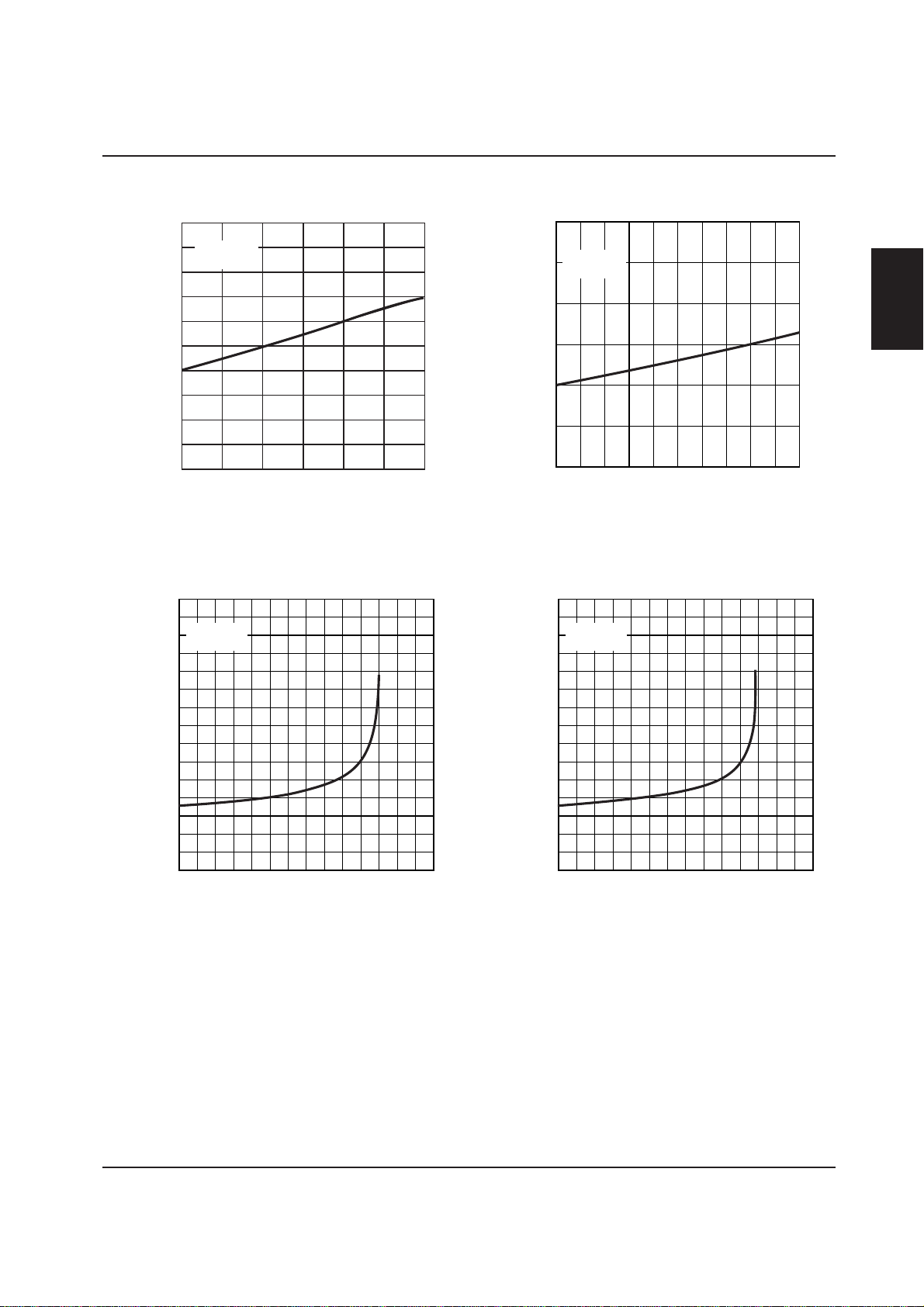

S1F76620 Series

100

90

80

70

60

50

Peff[%]

40

30

20

10

Ta=25°C

V

DD=5V

C1=C2=10µF

0

0 102030

I

O [mA]

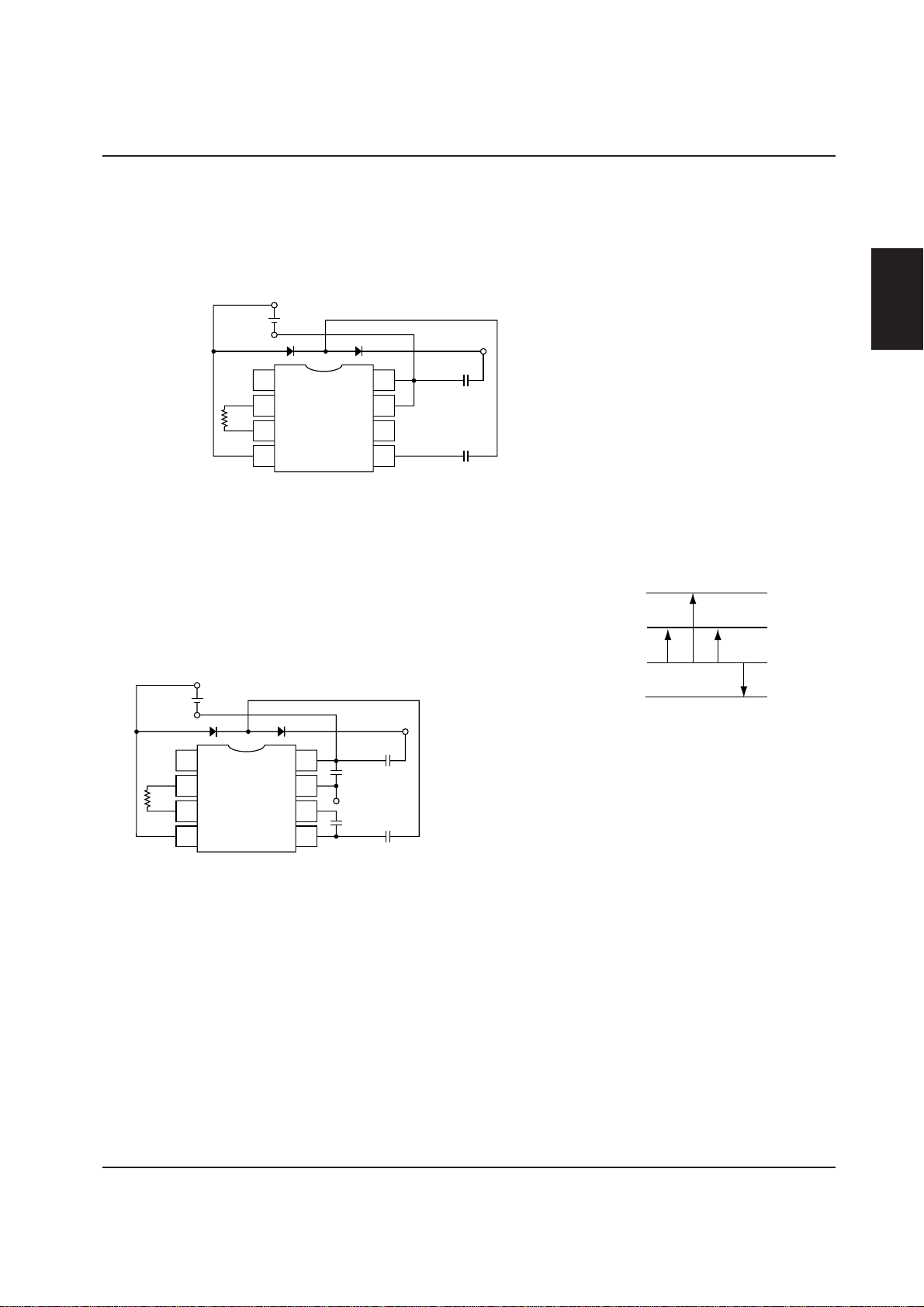

(9) Step-up power conversion efficiency vs.

Output current 1

Input current vs. Output current 1

100

90

80

70

60

50

Peff[%]

40

30

20

10

0

Ta=25°C

V

DD

=5V

C1=C2=10µF

012345678910

O

[mA]

50

40

30

20

10

0

150

120

90

60

30

0

DD[mA]

I

[mA]

DD

I

100

90

80

70

60

50

Peff[%]

40

30

20

10

Ta=25°C

V

DD=3V

C1=C2=10µF

0

0 5 10 15 20

I

O [mA]

(10) Step-up power conversion efficiency vs.

Output current 2

Input current vs. Output current 2

100

90

80

Peff[%]

70

60

50

1 10 100 1000

IO =5mA

IO =2mA

IO =20mA

focs[kHz]I

IO =10mA

Ta=25°C

V

DD

=5V

1=C2

=10µF

C

100

90

80

70

60

50

40

30

20

10

Series

S1F76620

DD[mA]

I

0

(11) Step-up power conversion efficiency vs.

Output current 3

. (12) Step-up power conversion efficiency vs.

Oscillation frequency 1

Input current vs. Output current 3

S1F70000 Series EPSON 1–19

Technical Manual

Page 37

S1F76620 Series

100

90

80

IO =1mA

IO =5mA

Peff[%]

70

60

IO =2mA

IO =10mA

Ta=25°C

V

C

DD

=3V

1=C2

=10µF

50

1 10 100 1000

focs[kHz]

(13) Step-up power conversion efficiency vs.

Oscillation frequency 2

1.7

1.6

[V]

STA1

V

1.5

1.4

1.3

1.2

Ta=25°C

C

1=C2

=10µF

OSC

=1MΩ

R

100

90

IO =0.5mA

80

IO =1mA

IO =2mA

Peff[%]

70

60

IO =5mA

Ta=25°C

V

DD

=2V

1=C2

=10µF

C

50

1 10 100 1000

focs[kHz]

(14) Step-up power conversion efficiency vs.

Oscillation frequency 3

1.1

1.0

0.9

100 1000 10000 100000

R

L

[Ω]

(15) Step-up start voltage (1) vs. Load resistance

1–20 EPSON S1F70000 Series

Technical Manual

Page 38

EXAMPLE OF REFERENCE EXTERNAL CONNECTION

2 Times Step-up

2 times step-up output of V

O (2 × VDD) is obtained from the circuit shown in Figure 1.

S1F76620 Series

1

POFF

2

GND

3

4

OSC1

OSC2

VI

Figure 1 2 Time Step-up Operation

Parallel Connection

It is possible to make the output impedance (R

O) small when several pieces of the circuit shown in Figure 1 are

connected. Parallel connection of n circuits reduces R

C

2 can be commonly used.

1

P

OFF

2

GND

V

I

3

OSC1

CAP1+

CAP1–

8

O

V

7

6

OFF

•

2 VI

V

CAP1+

8

O

7

+

8

O

V

CAP1+

CAP1–

O to 1/n approximately. One piece of the smoothing capacitor

7

6

5

V

DD

+

+

–

–

1

P

2

GND

_

3

OSC1

CAP1–

6

+

4

+

_

OSC2

5

V

DD

_

Series

S1F76620

4

OSC2

5

V

DD

Figure 2 Parallel Connection

S1F70000 Series EPSON 1–21

Technical Manual

Page 39

S1F76620 Series

Series Connection

When S1F76620 is connected in series (V

stage respectively), the output voltage can be increased more. But the series connection makes the output impedance

high. Figure 3 shows an example of the series connection to get V

DD and VO in the previous stage are connected to GND and VDD in the next

O = 15V from VDD = 5V.

• •

V o=2 V

I

1

P

OFF

2

GND

1

P

OFF

2

GND

V

I

3

4

OSC1

OSC2

CAP1+

CAP1–

8

V

O

3

OSC1

7

6

5

DD

V

+

4

+

–

OSC2

–

CAP1+

CAP1–

8

V

O

7

6

5

DD

V

+

–

V o'=3 V

+

–

I

Figure 3 Series Connection

DD(5V)

V

V

O=10V

First stage Next stage

VDD'

GND'

V

O'=15V

GND(0V)

Figure 4 Power Supply Relations in Series Connection (1)

Note

When the input voltage in the next stage is as per the specification (V

output in the first stage (V

V

DD

GND(0V)

O-VDD) can be used as the input in the next stage (VDD-GND). (See Figure 5.)

First stage

O

=4V

V

Next stage

(2V)

DD-GND ≤ 8V) in a series connection, the

V

O

'=8V

VDD'

GND'

Figure 5 Power Supply Relations in Series Connection (2)

1–22 EPSON S1F70000 Series

Technical Manual

Page 40

S1F76620 Series

Negative Voltage Conversion

S1F76620 can boost input voltage to twice on the positive potential side by using the circuit shown in Figure 6. But

the output voltage drops by the forward voltage V

shown in Figure 6 for example, V

O is calculated as follows: VO = –5V + 2 × 0.6V = –3.8V.

F of the diode. When GND is 0V, VDD is 5V and VF is 0.6V as

1

P

OFF

O

V

+–

8

Series

S1F76620

2

3

4

GND

OSC1

OSC2

CAP1+

CAP1–

7

+–

6

5

DD

V

VO'

Figure 6 Negative Voltage Conversion

Negative Voltage Conversion + Positive Voltage Conversion

When the 3 times step-up operation shown in Figure 1 and the positive voltage conversion in Figure 6 are combined,

the circuit shown in Figure 7 can be formed and 10V and –3.8V can be obtained from the input 5V. However, the

output impedance is higher than in case of connection of either one only (the negative voltage conversion or the

positive voltage conversion).

V

1

2

3

P

OFF

GND

OSC1

V

CAP1+

CAP1–

O1

8

O

7

+

+

–

–

6

Potential Relations Diagram

2 V

I

V

DD

V

I

V

SS

–VI+2 V

•

F

4

OSC2

5

DD

V

V

O2

V

O2

Figure 7 Negative Voltage Conversion + Positive Voltage Conversion

S1F70000 Series EPSON 1–23

Technical Manual

Page 41

S1F76620 Series

MEASUREMENT CIRCUIT

V

O

I

O

A

R

L

1

P

OFF

8

O

V

V

2

3

4

GND

OSC1

OSC2

V

I

OPR

A

R

OSC

V

I

CAP1+

CAP1–

7

6

5

V

DD

+

C

1

+

2

–

C

–

1–24 EPSON S1F70000 Series

Technical Manual

Page 42

MECHANICAL DATA

S1F76620 Series

S1F76620M0A0 SOP4-8pin

D

85

E

HE

θ2

2

A

A

1

A

θ3

Max.

5.2

—

0.45

0.25

Symbol

E

D1

A

A1

A2

e

b

C

INDEX

14

e

b

Dimension in Milimeters

Min.

4.8

—

Nom.

5

—

1.75

0.15

1.6

1.27

0.25

0.05

0.35

0.15

θ

L

0.55

L1

L2

HE

D

6.4

4.8

6.8

5

7.2

5.2

θ2

θ3

R

R1

* for reference

Note

This drawing is subject to change without notice for improvement.

θ

Min.

(0.189)

—

(0.010)

(0.002)

(0.252)

(0.189)

R

1

R

C

L

2

L

L

1

Dimension in Inches*

Nom.

(0.197)

—

(0.069)

(0.006)

(0.063)

(0.050)

(0.014)

(0.006)

(0.022)

(0.268)

(0.197)

Reference

Max.

(0.204)

—

(0.017)

(0.009)

(0.283)

(0.204)

Series

S1F76620

S1F70000 Series EPSON 1–25

Technical Manual

Page 43

2. DC/DC Converter & Voltage Regulator

Page 44

S1F76610 Series

S1F76610 Series CMOS DC/DC Converter (Voltage

Doubler / Tripler) & Voltage Regulator

DESCRIPTION

The S1F76610 Series is a highly effecient CMOS DC/

DC converter for doubling or tripling an input voltage.

It incorporates an on-chip voltage regulator to ensure