Page 1

查询S1D13503供应商查询S1D13503供应商

S1D13503 Graphics LCD Controller

S1D13503

TECHNICAL MANUAL

Issue Date: 01/01/30

Document Number: X18A-Q-001-07

Copyright © 1997, 2001 Epson Research and Development, Inc. All Rights Reserved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in

evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any

representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain

material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other trademarks are the property of their respective owners.

Page 2

Page ii

Epson Research and Development

Vancouver Design Center

THIS PAGE LEFT BLANK

S1D13503 Issue Date : 01/01/30

Page 3

Epson Research and Development

Vancouver Design Center

CUSTOMER SUPPORT INFORMATION

Comprehensive Support Tools

Seiko Epson Corp. provides to the system designer and computer OEM manufacturer a complete set of resources and tools

for the development of graphics systems.

Evaluation / Demonstration Board

• Assembled and fully tested graphics evaluation board with installation guide and schematics

• To borrow an evaluation board, please contact your local Seiko Epson Corp. sales representative

VGA Chip Documentation

• Technical manual includes Data Sheet, Application Notes, and Programmer’s Reference

Software

Page iii

•Video BIOS

• OEM Utilities

• User Utilities

• Evaluation Software

• To obtain these programs, contact Application Engineering Support

Application Engineering Support

Engineering and Sales Support is provided by:

Japan

Seiko Epson Corporation

Electronic Devices Marketing Division

421-8, Hino, Hino-shi

Tokyo 191-8501, Japan

Tel: 042-587-5812

Fax: 042-587-5564

http://www.epson.co.jp

Hong Kong

Epson Hong Kong Ltd.

20/F., Harbour Centre

25 Harbour Road

Wanchai, Hong Kong

Tel: 2585-4600

Fax: 2827-4346

North America

Epson Electronics America, Inc.

150 River Oaks Parkway

San Jose, CA 95134, USA

Tel: (408) 922-0200

Fax: (408) 922-0238

http://www.eea.epson.com

Europe

Epson Europe Electronics GmbH

Riesstrasse 15

80992 Munich, Germany

Tel: 089-14005-0

Fax: 089-14005-110

Taiwan, R.O.C.

Epson Taiwan Technology

& Trading Ltd.

10F, No. 287

Nanking East Road

Sec. 3, Taipei, Taiwan, R.O.C.

Tel: 02-2717-7360

Fax: 02-2712-9164

Singapore

Epson Singapore Pte., Ltd.

No. 1

Temasek Avenue #36-00

Millenia Tower

Singapore, 039192

Tel: 337-7911

Fax: 334-2716

Issue Date: 01/01/30 S1D13503

Page 4

Page iv

Epson Research and Development

Vancouver Design Center

THIS PAGE LEFT BLANK

S1D13503 Issue Date : 01/01/30

Page 5

Epson Research and Development

Vancouver Design Center

INTRODUCTION

S1D13503 Graphics LCD Controller Data Sheet

SPECIFICATION

S1D13503 Hardware Functional Specification

PROGRAMMER’S REFERENCE

S1D13503 Programming Notes and Examples

UTILITIES

13503SHOW.EXE Display Utility

13503VIRT.EXE Display Utility

13503BIOS.COM Display Utility

13503MODE.EXE Display Utility

13503PD.EXE Power Down Utility

13503READ.EXE Diagnostic Utility

Page v

TABLE OF CONTENTS

EVALUATION

S5U13503B00C Rev 1 Evaluation Board User Manual

APPLICATION NOTES

Power Consumption

ISA Bus Interface Considerations

MC68340 Interface Considerations

LCD Panel Options/Memory Requirem ent s

S1D13503/S1D13502 Feature Comparison

Issue Date: 01/01/30 S1D13503

Page 6

Page vi

Epson Research and Development

Vancouver Design Center

THIS PAGE LEFT BLANK

S1D13503 Issue Date : 01/01/30

Page 7

GRAPHICS

S1D13503

January 2001

S1D13503 GRAPHICS LCD CONTROLLER

■

DESCRIPTION

The S1D13503 is a dot matrix graphic LCD controller supporting resolutions up to 1024x1024. It is

capable of displaying a maximum of 256 simultaneous colors out of a possible 4096 or 16 gray shades.

Design flexibility allows the S1D13503 to interface to either an MC68000 family microprocessor or an

8/16-bit MPU/bus with minimum external logic. The Static RAM (SRAM) interface used for the display

buffer is optimized for speed and performance, supporting up to 128K bytes.

Two power save modes , combine d with operat ing volta ges of 2.7 vol ts throu gh 5.5 volt s, all ow for a wi de

range of applications while providing min imum power consumption.

■

FEATURES

CPU Interface

Pin compatible with the S1D13502.

•

16-bit 16 MHz MC68xxx MPU interface.

•

8/16-bit MPU interface controlled by a READY

•

(or WAIT#) signal.

Option to use built-in index register or direct-map-

•

ping to access one of sixteen internal registers.

Memory Int e rface

8/16-bit SRAM interface configurations:

•

128K bytes using one 64Kx16 SRAMs.

128K bytes using two 64Kx8 SRAMs.

64K bytes using two 32Kx8 SRAMs.

40K bytes using one 8Kx8 and one 32Kx8

SRAM.

32K bytes using one 32Kx8 SRAM.

16K bytes using two 8Kx8 SRAMs.

8K bytes using one 8Kx8 SRAM.

Display Modes

Black-and-white display.

•

2/4 bits-per-pixel, 4/16-level gray-scale display.

•

2/4/8 bits-per-pixel, 4/16/256-level color display.

•

Display Support

Single-panel, singl e- dr ive pas si v e disp la y.

•

Dual-panel, dual-drive passive display.

Maximum number of vertical lines:

•

1,024 lines (single-panel, single-drive display).

2,048 lines (dual-panel, dual-drive display).

Split screen display support allowing two different

•

images to be simultaneously displayed.

Virtual display support (displays images larger than

•

the panel size through the use of panning).

Clock Source

2-terminal crystal or external oscillator.

•

Power Down Modes

Low power consumption.

•

Two software power-save modes.

•

Package

QFP5-100-S2 package (F00A).

•

QFP15-100-STD package (F01A).

•

X18A-C-002-03

1

Page 8

GRAPHICS

S1D13503

■

SYSTEM BLOCK DIAGRAM

CLOCK

CPU

Control

Clock

S1D13503

SRAM

Digital Out

CONTACT YOUR SALES REPRESENTATIVE FOR THESE

COMPREHENSIVE DESIGN TOOLS:

• S1D13503 Technical Manual

• S5U13503 Evaluation Boards

• CPU Independent Software Utilities

Japan

Seiko Epson Corporation

Electronic Devices Marketing Division

421-8, Hino, Hino-shi

Tokyo 191-8501, Japan

Tel: 042-587-5812

Fax: 042-587-5564

http://www.epson.co.jp

Hong Kong

Epson Hong Kong Ltd.

20/F., Harbour Centre

25 Harbour Road

Wanchai, Hong Kong

Tel: 2585-4600

Fax: 2827-4346

North America

Epson Electronics America, Inc.

150 River Oaks Parkway

San Jose, CA 95134, USA

Tel: (408) 922-0200

Fax: (408) 922-0238

http://www.eea.epson.com

Europe

Epson Europe Electronics GmbH

Riesstrasse 15

80992 Munich, Germany

Tel: 089-14005-0

Fax: 089-14005-110

Flat Panel

QFP5-100-S2

(S1D13503F00A)

Taiwan

Epson Taiwan Technology

& Trading Ltd.

10F, No. 287

Nanking East Road

Sec. 3, Taipei, Taiwan

Tel: 02-2717-7360

Fax: 02-2712-9164

Singapore

Epson Singapore Pte., Ltd.

No. 1

Temasek Avenue #36-00

Millenia Tower

Singapore, 039192

Tel: 337-7911

Fax: 334-2716

QFP15-100-STD

(S1D13503F01A)

Copyright ©1997, 2001 Epson Research and Development, Inc. All rights reserved. VDC

Information in this document is subjec t to change without not ice . You may downlo ad and use thi s docum ent, bu t only for you r ow n use in eva luating S eiko E pson/

EPSON products. You may not modify the document. Epson Research and Develo pment, Inc. disclaims any repr esentati on that the contents of this document are

accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. Microsoft and Windows are registered trademarks of Microsoft Corporation.

2

X18A-C-002-03

Page 9

S1D13503 Dot Matrix Graphics Color LCD Controller

Hardware Functional Specification

Document Number: X18A-A-001-08

Copyright © 1997, 2001Epson Research and Development, Inc. All Rights Reser ved.

Information in this document is subject to change without notice. You may download and use this document, but only for your own use in

evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any

representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain

material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other trademarks are the property of their respective owners.

Page 10

Page 2 Epson Resear ch and Development

Vancouver Design Center

THIS PAGE LEFT BLANK

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 11

Epson Research and Development Page 3

Vancouver Design Center

Table of Contents

1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.1 Scope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.2 Overview Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

2 FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.1 Technology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.2 System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.3 Display Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.4 Display Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.5 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3 TYPICAL SYSTEM BLOCK DIAGRAMS . . . . . . . . . . . . . . . . . . . . . . 12

3.1 16-Bit MC68000 MPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.2 MPU with READY (or WAIT#) signal . . . . . . . . . . . . . . . . . . . . . . 13

3.3 ISA Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.4 Internal Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.5 Functional Block Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.5.1 Bus Signal Translation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.5.2 Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.5.3 Sequence Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.5.4 LCD Panel Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.5.5 Look-Up Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.5.6 Port Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.5.7 Memory Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.5.8 Data Bus Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.5.9 Address Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.5.10 MPU / CRT Selector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.5.11 Display Data Formatter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.5.12 Clock Inputs / Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.5.13 SRAM Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

4 PINOUT DIAGRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5 PIN DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

5.1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

5.2 Summary of Configuration Options . . . . . . . . . . . . . . . . . . . . . . . . 26

6 D.C. CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

7 A.C. CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

7.1 Bus Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

7.1.1 MC68000 Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

7.1.2 Non-MC68000, MPU/Bus With READY (or WAIT#) Signal . . . . . . . . . . . . . . . 33

7.2 Clock Input Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

7.2.1 Recommended Clock Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 12

Page 4 Epson Resear ch and Development

Vancouver Design Center

7.3 Display Memory Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . 39

7.3.1 Write Data to Display Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

7.3.2 Read Data From Display Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

7.4 LCD Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

7.4.1 LCD Interface Timing - 4-Bit Single, 8-Bit Single/Dual Monochrome Panels . . . . . . . 41

7.4.2 LCD Interface Timing - 4-Bit Single Color Panel . . . . . . . . . . . . . . . . . . . . . . 44

7.4.3 LCD Interface Timing - 8-Bit Single Color Panels Format 2/8-Bit Dual Color Panels . . . 46

7.4.4 LCD Interface Timing - 16-Bit Single/Dual Color Panels . . . . . . . . . . . . . . . . . . 48

7.4.5 LCD Interface Timing - 8-Bit Single Color Panels Format 1 . . . . . . . . . . . . . . . . 50

7.4.6 LCD Interface Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

8 HARDWARE REGISTER INTERFACE . . . . . . . . . . . . . . . . . . . . . . . .61

8.1 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

8.2 Look-Up Table Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . 72

8.2.1 Gray Shade Display Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

8.2.2 Color Display Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

8.3 Power Save Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

8.3.1 Power Save Mode 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

8.3.2 Power Save Mode 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

8.3.3 Power Save Mode Function Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

8.3.4 Pin States in Power Save Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

9 DISPLAY MEMORY INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . .79

9.1 SRAM Configurations Supported . . . . . . . . . . . . . . . . . . . . . . . . 79

9.1.1 8-Bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

9.1.2 16-bit Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

9.2 SRAM Access Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

9.2.1 8-bit Display Memory Interface: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

9.2.2 16-bit Display Memory Interface: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

9.3 Frame Rate Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

9.3.1 For single panel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

9.3.2 For dual panel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

9.4 Memory Size Calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

9.5 Memory Size Requirement . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

10 MECHANICAL DATA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 13

Epson Research and Development Page 5

Vancouver Design Center

List of Tables

Table 4-1: PAD Coordinates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Table 5-1: Bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Table 5-2: Display Memory Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Table 5-3: LCD Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Table 5-4: Clock Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 5-5: Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Table 5-6: Summary of Power On / Reset Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

Table 5-7: I/O and Memory Addressing Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 6

Table 6-1: Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Table 6-2: Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Table 6-3: Input Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Table 6-4: Output Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Table 7-1: IOW# Timing (MC68000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Table 7-2: IOR# Timing (MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Table 7-3: MEMW# Timing (MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 1

Table 7-4: MEMR# Timing (MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

Table 7-5: IOW# Timing (Non-MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Table 7-6: IOR# Timing (Non-MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Table 7-7: MEMW# Timing (Non-MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Table 7-8: MEMR# Timing (Non-MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

Table 7-9: Clock Input Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 7

Table 7-10: Write Data to Display Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Table 7-11: Read Data From Display Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Table 7-12: LCD Interface Timing - 4-Bit Single and 8-Bit Single/Dual Monochrome Panel . . . . . . . . . . . 42

Table 7-13: LCD Interface Timing - 4-Bit Single Color Panel. . . . . . . . . . . . . . . . . . . . . . . . . . . .45

Table 7-14: LCD Interface Timing - 8-Bit Single Color Panels Format 2/8-Bit Dual Color Panels. . . . . . . . .47

Table 7-15: LCD Interface Timing - 16-Bit Single/Dual Color Panels . . . . . . . . . . . . . . . . . . . . . . .49

Table 7-16: LCD Interface Timing - 8-Bit Single Color Panels Format 1 . . . . . . . . . . . . . . . . . . . . . .51

Table 8-1: Gray Shade/Color Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

Table 8-2: LCD Data Width. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

Table 8-3: Maximum Value of Line Byte Count Register - 8-Bit Display Memory Interface . . . . . . . . . . .64

Table 8-4: Maximum Value of Line Byte Count Register - 16-Bit Display Memory Interface . . . . . . . . . .64

Table 8-5: Power Save Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

Table 8-6: ID Bit Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

Table 8-7: Look-Up Table Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

Table 8-8: Look-Up Table Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 2

Table 8-9: Power Save Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77

Table 8-10: Power Save Mode Function Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

Table 8-11: Pin States in Power Save Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

Table 9-1: 8-Bit Display Memory Interface SRAM Access Time . . . . . . . . . . . . . . . . . . . . . . . . .8 3

Table 9-2: 16-Bit Display Memory Interface SRAM Access Time. . . . . . . . . . . . . . . . . . . . . . . . .83

Table 9-3: Memory Size Requirement: Number of Horizontal Pixels = 640 . . . . . . . . . . . . . . . . . . . .85

Table 9-4: Memory Size Requirement: Number of Horizontal Pixels = 480 . . . . . . . . . . . . . . . . . . . .86

Table 9-5: Memory Size Requirement: Number of Horizontal Pixels = 320 . . . . . . . . . . . . . . . . . . . .86

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 14

Page 6 Epson Resear ch and Development

Vancouver Design Center

THIS PAGE LEFT BLANK

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 15

Epson Research and Development Page 7

Vancouver Design Center

List of Figures

Figure 1: 16-Bit 68000 Series . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Figure 2: 8-Bit Mode, Example: Z80 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Figure 3: 16-Bit Mode, Example: i8086 (maximum mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Figure 4: 8-Bit Mode (ISA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Figure 5: 16-Bit Mode (ISA). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Figure 6: Internal Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Figure 7: S1D13503 Pinout Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Figure 8: S1D13503 Pinout Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Figure 9: S1D13503 Pad Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 9

Figure 10: IOW# Timing (MC68000). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Figure 11: IOR# Timing (MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Figure 12: MEMW# Timing (MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

Figure 13: MEMR# Timing (MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

Figure 14: IOW# Timing (Non-MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Figure 15: IOR# Timing (Non-MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

Figure 16: MEMW# Timing (Non-MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

Figure 17: MEMR# Timing (Non-MC68000) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36

Figure 18: Clock Input Requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

Figure 19: Recommended Clock Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

Figure 20: Write Data to Display Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Figure 21: Read Data From Display Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Figure 22: LCD Interface Timing - Monochrome Panel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 1

Figure 23: LCD Interface Timing - 4-Bit Single Color Panel. . . . . . . . . . . . . . . . . . . . . . . . . . . .44

Figure 24: LCD Interface Timing - 8-Bit Single Color Panels Format 2/8-Bit Dual Color Panels. . . . . . . . .46

Figure 25: LCD Interface Timing - 16-Bit Single/Dual Color Panels . . . . . . . . . . . . . . . . . . . . . . .4 8

Figure 26: LCD Interface Timing - 8-Bit Single Color Panels Format 1 . . . . . . . . . . . . . . . . . . . . . .50

Figure 27: 4-Bit Single Monochrome Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

Figure 28: 8-Bit Single Monochrome Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

Figure 29: 8-Bit Dual Monochrome Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

Figure 30: 4-Bit Single Color Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

Figure 31: 8-Bit Single Color Panel Timing - Format 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .56

Figure 32: 8-Bit Single Color Panel Timing - Format 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

Figure 33: 8-Bit Dual Color Panel Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

Figure 34: External Circuit Required for 16-Bit Panel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

Figure 35: 16-Bit Single Color Panel Timing with External Circuit . . . . . . . . . . . . . . . . . . . . . . . .59

Figure 36: 16-Bit Dual Color Panel Timing with External Circuit . . . . . . . . . . . . . . . . . . . . . . . . .60

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 16

Page 8 Epson Resear ch and Development

Vancouver Design Center

Figure 37: 4-Level Gray-Shade Mode Look-Up Table Architecture . . . . . . . . . . . . . . . . . . . . . . . 72

Figure 38: 16-Level Gray-Shade Mode Look-Up Table Architecture . . . . . . . . . . . . . . . . . . . . . . . 73

Figure 39: 4-Level Color Mode Look-Up Table Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 40: 16-Level Color Mode Look-Up Table Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 41: 256-Level Color Mode Look-Up Table Architecture . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure 42: 8-Bit Mode - 8K bytes SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Figure 43: 8-Bit Mode - 16K bytes SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Figure 44: 8-Bit Mode - 32K bytes SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Figure 45: 8-Bit Mode - 40K bytes SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Figure 46: 8-Bit Mode - 64K bytes SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Figure 47: 16-Bit Mode - 16K bytes SRAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Figure 48: 16-Bit Mode - 64K bytes SRAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Figure 49: 16-Bit Mode - 128K bytes SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Figure 50: Mechanical Drawing QFP5-100-S2 (S1D13503) . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Figure 51: Mechanical Drawing QFP15-100-STD (S1D13503). . . . . . . . . . . . . . . . . . . . . . . . . . 88

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 17

Epson Research and Development Page 9

Vancouver Design Center

1 INTRODUCTION

1.1 Scope

This is the Functional Specification for the S1D13503 Dot Matrix Graphic Color LCD Controller. Included in this

document are timing diagrams, AC and DC characteristics, register descriptions, and power managem ent descriptions. This

document is intended for two audiences, Video Subsystem Designers and Software Developers.

1.2 Overview Description

This device is designed for products where low cost, low power consumption, and low component count are the major

design considerations. This chip operates f rom 2.7 Volts to 5.5 Volts and up t o 25MHz to suit d ifferent power consump tion,

speed and cost requirements. The S1D13503 offers a flexible microprocessor interface, and is pin compatible with the

S1D13502 within the same package types (e.g. the 13503D0A is pin compatible with the 13502; the 13503 is pin

compatible with the 13502).

The S1D13503 is capable of displaying a maximum of 16 levels of gray shade or 256 simultaneous colors. In gray shade

modes, a 16x4 Look-Up Table is provid ed to allow remapping of the 16 possible gray s hades displayed on the LCD panel.

In color modes, three 16x4 Look-Up Tables are prov ided to allo w remappin g of the 4096 pos sibl e colors display ed on the

LCD panel. The S1D13503S1D13503 can interface to an MC68000 family microprocessor or an 8/16-bit MPU/Bus with

minimum external “glue” logic. This device can directly control up to 128K bytes of static RAM with a 16-bit data path,

or up to 64K bytes with an 8-bit data path.

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 18

Page 10 Epson Resear ch and Development

Vancouver Design Center

2 FEATURES

2.1 Technology

• low power CMOS

• 2.7 to 5.5 volt operation

• 100 pin QFP5-S2 surface mount package

• 100 pin QFP15-STD surface mount package

2.2 System

• maximum 25 MHz input clock (or pixel clock)

• 2-terminal crystal input for internal oscillator or direct connection to external clock source

• maximum 16 MHz, 16-bit MC68000 MPU interface

• 8-bit or 16-bit MPU/Bus interface with memory accesses controlled by a READY (or WAIT#) signal

• option to use built-in index register or direct-mapping to access one of sixteen internal registers

• 8-bit or 16-bit SRAM data bus interface configurations

• display memory configurations :

• 128k bytes using one 64Kx16 SRAM

• 128k bytes using two 64Kx8 SRAMs

• 64k bytes using two 32Kx8 SRAMs

• 40k bytes using one 8Kx8 and one 32Kx8 SRAM

• 32k bytes using one 32Kx8 SRAM

• 16k bytes using two 8Kx8 SRAMs

• 8k bytes using one 8Kx8 SRAM

2.3 Display Modes

• 1 bit-per-pixel, black-and-white display mode

• 2/4 bits-per-pixel, 4/16 level gray shade display modes

• 2/4/8 bits-per-pixel, 4/16/256 level color display modes

• one 16x4 Look-Up Table provided for gray shade display modes

• three 16x4 Look-Up Tables provided for color display modes

• maximum 16 shades of gray

• maximum 256 simultaneous colors from a possible 4096 colors

• split screen display mode (see AUX[0A])

• virtual display mode (see AUX[0D])

Note

256 color display mode support requires a 16-bit display memory interface

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 19

Epson Research and Development Page 11

Vancouver Design Center

2.4 Display Support

• example resolutions:

• 1024 x 768 black-and-white

• 640 x 480 with 4 colors/grays

• 640 x 400 with 16 colors/grays

• 320 x 240 with 256 colors

• passive monochrome LCD panels:

• 4-bit single (4-bit data transfer)

• 8-bit single (8-bit data transfer)

• 8-bit dual (4-bit data transfer for each half panel)

• passive color LCD panels:

• 4-bit single (4-bit data transfer)

• 8-bit single (8-bit data transfer)

• 8-bit dual (4-bit data transfer for each half panel)

• 16-bit single (8-bit data transfer with external circuit)

• 16-bit dual (8-bit data transfer with external circuit)

See Section 9.5 on page 85 for complete details

2.5 Power Management

• two software power-save modes

• low power consumption

• panel power control switch (see AUX[01] bit 4)

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 20

Page 12 Epson Resear ch and Development

Vancouver Design Center

3 TYPICAL SYSTEM BLOCK DIAGRAMS

The following figures show typical system implementations of the S1D13503. All of the following block diagrams are

shown without SRAM or LCD display. Refer to the interface specific Application Notes for complete details.

3.1 16-Bit MC68 000 MPU

MC68000

A20 to A23

FC0 to FC1

A1 to A19 AB1 to AB19

D0 to D15

DTACK#

UDS#

LDS#

AS#

R/W#

A14 to A16

A10 to A19

Decoder

Decoder

S1D13503

MEMCS#

IOCS#

DB0 to DB15

READY

AB0

BHE#

IOR#

IOW#

Figure 1: 16-Bit 68000 Series

(example implementation only - actual may vary)

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 21

Epson Research and Development Page 13

Vancouver Design Center

3.2 MPU with READY (or WAIT#) signal

RDY

CLK

READY

RESET#

8284A

Z80

MREQ#

MI#

IORQ#

A0 to A15

D0 to D7

WAIT#

WR#

RD#

RESET#

8086

(Maximum mode)

CLK

READY

RESET#

A16 to A19

AD0 to AD15

Decoder

A10 to A15

Decoder

Figure 2: 8-Bit Mode, Example: Z80

(example implementation only - actual may vary)

8288

CLK

S2#

S1#

S0#

A16

BHE#

S2#

S1#

S0#

DEN

DT/R

ALE

Decoder

M/IO#

BHE#

A0 to A16

STB

MRDC#

AMWC#

IORC#

AIOWC#

S1D13503

MEMCS#

IOCS#

AB0 to AB15

DB0 to DB7

READY

MEMW#

MEMR#

IOR#

IOW#

RESET

S1D13503

MEMR#

MEMW#

IOR#

IOW#

AB16 to AB19

AB0 to AB15

BHE#

MEMCS#

IOCS#

D0 to D15

T

OE

Transceiver

DB0 to DB15

RESET

READY

Figure 3: 16-Bit Mode, Example: i8086 (maximum mode)

(example implementation only - actual may vary)

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 22

Page 14 Epson Resear ch and Development

Vancouver Design Center

3.3 ISA Bus

8-Bit ISA Bus

REFRESH

SMEMW#

SMEMR#

IOCHRDY

SD0 to SD7

SA0 to SA19

AEN

IOW#

IOR#

RESET#

0WS#

SA16 to SA13

SA10 to SA15

Decoder

Decoder

optional

Decoder

Figure 4: 8-Bit Mode (ISA)

(example implementation only - actual may vary)

S1D13503

MEMCS#

MEMW#

MEMR#

READY

DB0 to DB7

AB0 to AB19

IOCS#

IOW#

IOR#

RESET

SA(1 or 4) through SA9

16-bit ISA Bus

REFRESH

SMEMW#

SMEMR#

IOCHRDY

SD0 to SD15

SA0 to SA19

IOW#

IOR#

SBHE#

RESET#

IOCS16#

LA17 to LA23

MEMCS16#

SA16 to SA14

AEN

Decoder

SA10 to SA15

(example implementation only - actual may vary)

Decoder

Decoder

Decoder

Figure 5: 16-Bit Mode (ISA)

S1D13503

MEMCS#

MEMW#

MEMR#

READY

DB0 to DB15

AB0 to AB19

IOCS#

IOW#

IOR#

BHE#

RESET

SA(1 or 4) through SA9

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 23

Epson Research and Development Page 15

Vancouver Design Center

3.4 Internal Block Diagram

Control Re gi sters

IOR#, IOW#, IOCS#,

MEMCS#, MEMR#,

MEMW#, BHE#,

AB[19:0]

READY

DB[15:0]

Bus

Signal

Translation

Port

Decoder

Memory

Decoder

Data Bus

Conversion

Timing Generator

Power Save

Oscillator

Sequence

Controller

Address

Generator

MPU/CRT

Selector

Display

Data

Formatter

SRAM Interface

Lookup

Table

LCD

Panel

Interface

LCDENB

UD[3:0]

LD[3:0]

LP, YD,

XSCL,

WF(XSCL2)

OSC1

OSC2

VOE#

VA[15:0]

VCS0#, VCS1#

VD[15:0]

VWE#

Figure 6: Internal Block Diagram

3.5 Functional Block Descriptions

3.5.1 Bus Signal Translation

According to configuration setting VD2, Bus Signal Translation translates MC68000 type MPU signals, or READY type

MPU signals to internal bus interface signals.

3.5.2 Control Regist ers

The Control Register contains 16 internal control and configuration registers. These registers can be accessed by either

direct-mapping or by using the built-in internal index register.

3.5.3 Sequence Controller

The Sequence Controller generates horizont al and vertical dis play timings accordin g to the con figuration regist ers settings.

3.5.4 LCD Pa nel Int erfac e

The LCD Panel Interface performs frame rate modulation and output data pattern formatting for both passive monochrome

and passive color LCD panels.

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 24

Page 16 Epson Resear ch and Development

Vancouver Design Center

3.5.5 Look-Up Table

The Look-Up Table contains three 16x4-bit wide pale ttes. In gray s hade modes , the “g reen” p alette can be configured for

the re-mapping of 16 possible shades of gray. In color modes, all three palettes can be configured for the re-mapping of

4096 possible colors.

3.5.6 Port Decoder

According to configuration settings VD1, VD12 - VD4, IOCS# and address lines AB9-1, the Port Decoder validates a given

I/O cycle.

3.5.7 Memory Decoder

According to configuration settings VD15 - VD13, MEMCS# and address lines AB19-17, the Memo ry Decoder validates

a given memory cycle.

3.5.8 Data Bus Conversion

According to configuration setting VD0, Data Bus Conversion maps the external data bus, either 8-b it or 1 6-b it, into th e

internal odd and even data bus.

3.5.9 Address Generator

The Address Generator generates display refresh addresses to be used to access display memory.

3.5.10 MPU / CRT Selector

The MPU / CRT Selector grants access to the display memory from either the MPU or the display refresh circuitry.

3.5.11 Display Data Formatter

The Display Data Formatter reads in the display data from the display memory and outputs th e correct format for all

supported gray shade and color selections.

3.5.12 Clock Inputs / Timing

Clock Inputs / Timing generates the internal master clock according to gray-level / color selected and display memory

interface. The master clock (MCLK) can be:

- MCLK = input clock

- MCLK = 1/2 input clock

- MCLK = 1/4 input clock.

Pixel clock = input clock = f

OSC.

3.5.13 SRAM Interface

The SRAM Interface generates the necessary signals to interface to the Display Memory (SRAM).

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 25

Epson Research and Development Page 17

Vancouver Design Center

4 PINOUT DIAGRAM

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

XSCL

LCDENB

VOE#

IOCS#

IOW#

IOR#

MEMCS#

MEMW#

MEMR#

READY

BHE#

OSC1

OSC2

DB0

DB1

DB2

DB3

DB4

DB5

DB6

8079787776757473727170696867666564636261605958575655545352

WF/XSCL2*

LPYDLD0

LD1

LD2

LD3

UD2

UD0

UD1

UD3

VCS1#

VCS0#

VWE#

VA15

VA14

VA13

VA12

VA11

VD15

VD14

VD13

VD12

VD11

VD10

VD9

VD8

V

DDVSS

S1D13503F00A

DB10

DB12

DB13

DB7

V

SS

123

DD

DB15

DB8

V

4

DB11

DB9

5

6

7

DB14

AB0

AB1

AB2

AB3

AB4

AB5

AB6

AB7

101112131415161718192021222324252627282930

8

9

AB10

AB12

AB13

AB14

AB15

AB8

AB11

AB9

AB16

51

VD7

50

VD6

49

VD5

48

VD4

47

VD3

46

VD2

45

VD1

44

VD0

43

VA10

42

VA9

41

VA8

40

VA7

39

VA6

38

VA5

37

VA4

36

VA3

35

VA2

34

VA1

33

VA0

AB19

32

31

RESET

AB17

AB18

Figure 7: S1D13503F00A Pinout Diagram

Package type: 100 pin surface mount QFP5-S2.

Note

* Pin 80 = WF in all display modes except format 1 for 8-bit single color panel.

* Pin 80 = XSCL2 in format 1 for 8-bit single color panel.

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 26

Page 18 Epson Resear ch and Development

Vancouver Design Center

75747372717069686766656463626160595857565554535251

YD

LD0

LD1

LD2

LD3

UD0

UD1

UD2

UD3

VCS1#

VCS0#

VWE#

VA1 5

VA1 4

VA1 3

VA1 2

VA1 1

VD15

VD14

VD13

VD12

VD11

VD10

VD9

VD8

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

LP

WF/XSCL2*

XSCL

LCDENB

VOE#

IOCS#

IOW#

IOR#

MEMCS#

MEMW#

MEMR#

READY

BHE#

OSC1

OSC2

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

VSS

V

DD

DB8

DB9

1

50

V

DD

49

V

SS

48

VD7

47

VD6

46

VD5

45

VD4

44

VD3

43

VD2

42

VD1

41

VD0

40

VA1 0

39

VA9

38

AB15

RESET

AB19

AB18

AB16

AB17

25

VA8

VA7

VA6

VA5

VA4

VA3

VA2

VA1

VA0

37

36

35

34

33

32

31

30

29

28

27

26

S1D13503F01A

DB10

DB12

DB13

DB15

DB11

2

3

456

DB14

AB0

AB1

AB2

AB3

AB4

AB5

AB6

AB7

7

101112131415161718192021222324

8

9

AB10

AB8

AB11

AB9

AB14

AB12

AB13

Figure 8: S1D13503F01A Pinout Diagram

Package type: 100 pin surface mount QFP15-STD.

Note

* Pin 77 = WF in all display modes except format 1 for 8-bit single color panel.

* Pin 77 = XSCL2 in format 1 for 8-bit single color panel.

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 27

Epson Research and Development Page 19

Vancouver Design Center

VCS1#

VCS0#

LP

YD

LD0

LD1

LD2

LD3

UD0

UD1

UD2

UD3

VWE#

VA1 5

VA1 4

VA1 3

VA1 2

VD15

VD14

VD13

VD12

VD11

VA1 1

VD10

VD9

VD8

V

V

DD

SS

Dummy Pad

WF/XSCL2*

XSCL

LCDENB

VOE#

IOCS#

IOW#

IOR#

MEMCS#

MEMW#

MEMR#

READY

BHE#

OSC1

OSC2

DB0

DB1

DB2

DB3

DB4

DB5

DB6

100

110

120

90

S1D13503D00A

7080

60

50

40

VD7

VD6

VD5

VD4

VD3

VD2

VD1

VD0

VA1 0

VA9

VA8

VA7

VA6

VA5

VA4

VA3

VA2

VA1

VA0

RESET

AB19

DB7

Dummy Pad

110 20

V

V

SS

Chip Size

Chip Thickness

Pad Size

Pad Pitch

DD

DB8

DB9

DB10

DB12

DB13

DB15

AB0

AB1

AB2

AB3

AB4

AB5

AB6

AB7

AB8

AB9

DB11

=

=

=

=

DB14

5.030 mm x 5.030 mm

0.400 mm

0.090 mm x 0.090 mm

0.126 mm (Min.)

AB10

AB11

30

AB12

AB13

AB14

AB15

AB16

AB18

AB17

Figure 9: S1D13503D00A Pad Diagram

Note

* Pad 97 = WF in all display modes except format 1 for 8-bit single color panel.

* Pad 97 = XSCL2 in format 1 for 8-bit single color panel.

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 28

Page 20 Epson Resear ch and Development

Vancouver Design Center

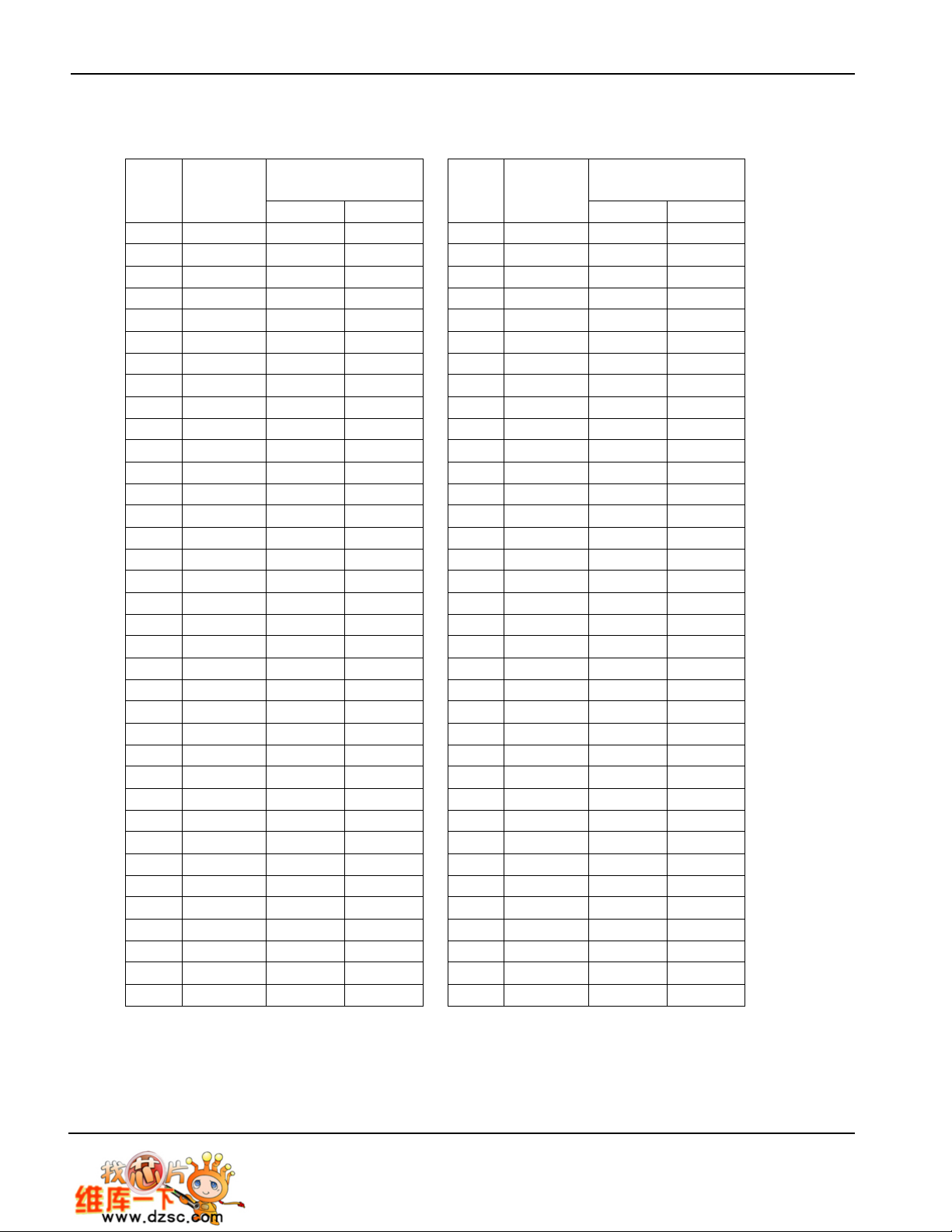

Table 4-1: PAD Coordinates

Pad

No.

1 VSS -2.165 -2.390 37 RESET 2.390 -1.535

2 --- -2.000 -2.390 38 VA0 2.390 -1.388

3 VDD -1.840 -2.390 39 VA1 2.390 -1.246

4 DB8 -1.685 -2.390 40 VA2 2.390 -1.106

5 DB9 -1.535 -2.390 41 --- 2.390 -0.969

6 DB10 -1.388 -2.390 42 VA3 2.390 -0.835

7 DB11 -1.246 -2.390 43 VA4 2.390 -0.703

8 DB12 -1.106 -2.390 44 --- 2.390 -0.573

9 DB13 -0.969 -2.390 45 VA5 2.390 -0.444

10 DB14 -0.835 -2.390 46 VA6 2.390 -0.317

11 DB15 -0.703 -2.390 47 --- 2.390 -0.190

12 --- -0.573 -2.390 48 VA7 2.390 -0.063

13 AB0 -0.444 -2.390 49 VA8 2.390 0.063

14 AB1 -0.317 -2.390 50 --- 2.390 0.190

15 AB2 -0.190 -2.390 51 VA9 2.390 0.317

16 AB3 -0.063 -2.390 52 VA10 2.390 0.444

17 AB4 0.063 -2.390 53 --- 2.390 0.573

18 AB5 0.190 -2.390 54 VD0 2.390 0.703

19 AB6 0.317 -2.390 55 VD1 2.390 0.835

20 AB7 0.444 -2.390 56 --- 2.390 0.969

21 --- 0.573 -2.390 57 VD2 2.390 1.106

22 AB8 0.703 -2.390 58 VD3 2.390 1.246

23 AB9 0.835 -2.390 59 VD4 2.390 1.388

24 AB10 0.969 -2.390 60 VD5 2.390 1.535

25 AB11 1.106 -2.390 61 VD6 2.390 1.685

26 AB12 1.246 -2.390 62 --- 2.390 1.840

27 AB13 1.388 -2.390 63 --- 2.390 2.000

28 AB14 1.535 -2.390 64 VD7 2.390 2.165

29 AB15 1.685 -2.390 65 VSS 2.165 2.390

30 AB16 1.840 -2.390 66 --- 2.000 2.390

31 --- 2.000 -2.390 67 VDD 1.840 2.390

32 AB17 2.165 -2.390 68 VD8 1.685 2.390

33 AB18 2.390 -2.340 69 VD9 1.535 2.390

34 --- 2.390 -2.000 70 VD10 1 .388 2.390

35 --- 2.390 -1.840 71 VD11 1 .246 2.390

36 AB19 2.390 -1.685 72 VD12 1.106 2.390

Pin

Name

Pad Center

Coordinate

XY XY

Pad

No.

Pin

Name

Pad Center

Coordinate

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 29

Epson Research and Development Page 21

Vancouver Design Center

Table 4-1: PAD Coordinates

Pad

No.

73 VD13 0.969 2.390 102 VOE# -2.390 1.388

74 VD14 0.835 2.390 103 IOCS# -2.390 1.246

75 VD15 0.703 2.390 104 IOW# -2.390 1.106

76 --- 0.573 2.390 105 --- -2.390 0.969

77 VA11 0.444 2.390 106 IOR# -2.390 0.835

78 VA12 0.317 2.390 107 MEMCS# -2.390 0.703

79 VA13 0.190 2.390 108 --- -2.390 0.573

80 VA14 0.063 2.390 109 MEMW# -2.390 0.444

81 VA15 -0.063 2.390 110 MEMR# -2.390 0.317

82 VWE# -0.190 2.390 111 --- -2.390 0.190

83 VCS0# -0.317 2.390 112 READY -2.390 0.063

84 VCS1# -0.444 2.390 113 BHE# -2.390 -0.063

85 --- -0.573 2.390 114 --- -2.390 -0.190

86 UD3 -0.703 2.390 115 OSC1 -2.390 -0.317

87 UD2 -0.835 2.390 116 OSC2 -2.390 -0.444

88 UD1 -0.969 2.390 117 --- -2.390 -0.573

89 UD0 -1.106 2.390 118 DB0 -2.390 -0.703

90 LD3 -1.246 2.390 119 DB1 -2.390 -0.835

91 LD2 -1.388 2.390 120 --- -2.390 -0.969

92 LD1 -1.535 2.390 121 DB2 -2.390 -1.106

93 LD0 -1.685 2.390 122 DB3 -2.390 -1.246

94 YD -1.840 2.390 123 DB4 -2.390 -1.388

95 --- -2.000 2.390 124 DB5 -2.390 -1.535

96 LP -2.340 2.390 125 DB6 -2.390 -1.685

97 WF/XSCL2 -2.390 2.165 126 --- -2.390 -1.840

98 --- -2.390 2.000 127 --- -2.390 -2.000

99 --- -2.390 1.840 128 DB7 -2.390 -2.165

100 XSCL -2.390 1.685 129 Dummy Pad 2.390 2.390

101 LCDENB -2.390 1.535 130 Dummy Pad -2.390 -2.390

Pin

Name

Pad Center

Coordinate

XY XY

Pad

No.

Pin

Name

Pad Center

Coordinate

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 30

Page 22 Epson Resear ch and Development

Vancouver Design Center

5 PIN DESCRIPTION

5.1 Description

Key:

I=Input

O=Output

I/O = Bidirectional (Input/Output)

P=Power pin

COx = CMOS level output driver, x denotes driver type (see Table 6-4, “Output Specifications,” on page 28)

COxS = CMOS level output d river with s lew rate cont rol for n oise redu ction, x d enotes dr iver typ e (see Table 6-4,

“Output Spec ifications,” on page 28)

TSx = Tri-state CMOS level output driver, x denotes driver type (see Table 6-4, “Output Specifications,” on

page 28)

TSxD2 = Tri-state CMOS level output driver with pull down resistor (typical values of 100KΩ/200ΚΩ at 5V/3.0V

respectively), x denotes driver type (see Table 6-4, “Output Specifications,” on page 28)

TTL = TTL level input (V

= 5.0V, see Table 6-3, “Input Specifications,” on page 27)

DD

TTLS = TTL level input with hysteresis

Table 5-1: Bus Interface

Pin Name Type

F00A

Pin #

F01A

Pin #

D00A

Pad #

Driver Description

118119,

121125,

128,

TS2

These pins are connected to the system data bus. In 8-bit bus

mode, DB8-DB15 must be tied to V

DD

.

DB0DB15

I/O

94 100, 1,

4 -11

91 - 98,

1 - 8

4-11

In MC68000 MPU interface, this pin is connected to the Upper

AB0 I 12 9 13 TTLS

Data Strobe (UDS#) pin of MC68000. In other MPU/Bus

interfaces, this pin is connected to the system address bus.

14-20,

AB1AB19

I 13 - 31 10 - 28

22-30,

32-33,

TTL These pins are connected to the system address bus.

36

In MC68000 MPU interface, this pin is connected to the Lower

BHE# I 91 88 113 TTLS

Data Strobe (LDS#) pin of MC68000. In other MPU/Bus

interfaces, this pin is the Byte High Enable input for use with

16-bit system. In 8-bit bus mode tie the BHE# input to V

IOCS# I 84 81 103 TTLS Active low input to select one of sixteen internal registers.

DD

.

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 31

Epson Research and Development Page 23

Vancouver Design Center

Table 5-1: Bus Interface

Pin Name Type

F00A

Pin #

F01A

Pin #

D00A

Pad #

Driver Description

In MC68000 MPU interface, this pin is connected to the R/W#

pin of MC68000. This input pin defines whether the data

IOW# I 85 82 104 TTLS

transfer is a read (active high) or write (active low) cycle. In

other MPU/Bus interfaces, this is the active low input to write

data into an internal register.

In MC68000 MPU interface, this pin is connected to the AS#

IOR# I 86 83 106 TTLS

pin of MC68000. This input pin indicates a val i d address is

available on the address bus. In other MPU/Bus interfaces, this

is the active low input to read data from an internal register.

MEMCS# I 87 84 107 TTLS Active low input to indicate a memory cycle.

MEMW# I 88 85 109 TTLS

MEMR# I 89 86 110 TTLS

Active low input to indicate a memory write cycle. This pin

should be tied to V

in an MC68000 MPU interface.

DD

Active low input to indicate a memory read cycle. This pin

should be tied to V

in an MC68000 MPU interface.

DD

For MC68000 MPU interface, this pin is connected to the

DTACK# pin of MC68000 and is driven low when the data

transfer is complete. In other MPU/Bus interfaces, this output

READYO9087112TS3

is driven low to force the system to insert wait states when

needed.

READY is placed in a high impedance (Hi-Z) state after the

transfer is completed.

RESET I 32 29 37 TTLS Active high input to force all signals to their inactive states.

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 32

Page 24 Epson Resear ch and Development

Vancouver Design Center

Table 5-2: Display Memory Interface

Pin

Name

VD0VD15

VA0VA15

VCS1# O 69 66 84 CO1

VCS0# O 68 65 83 CO1

VWE#O676482CO1

VOE#O8380102CO1

Type

I/O

O

F00A

Pin #

44 - 51,

54 - 61

33 - 43,

62 - 66

F01A

Pin #

41 - 48,

51 - 58

30 - 40

59 - 63

D00A

Pad #

54-55,

57-61,

64,

68-75

38-40,

42-43,

45-46,

48-49,

51-52,

77-81

Driver Description

These pins are connected to the display memory data bus. For 16bit interface, VD0-VD7 are connected to the display memory data

bus of even byte addresses and VD8-VD15 are connected to the

display memory data bus of odd byt e addresses . The out put drivers

of these pins are placed in a high impedance state when RESET is

TS1D2

CO1 These pins are connected to the display memory address bus.

high.

On the falling edge of RESET, the values of VD0-VD15 are

latched into the chip to configure various hardware options (see

Section Table 5-6: on page 26).

VD0-VD15 each have an internal pull-down resistor (see Section

Table 6-3: on page 27).

Active low chip-select output to the second or odd byte address

SRAM. See Display Memory Interface section for details.

Active low chip-select output to the first or even byte address

SRAM. See Display Memory Interface section for details.

Active low output used for writing data to the display memory.

This pin is connected to the WE# input of the SRAMs.

Active low output to enable reading of data from the display

memory. This pin is connected to the OE# input of the SRAMs.

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 33

Epson Research and Development Page 25

Vancouver Design Center

Table 5-3: LCD Interface

TM

Pin Name

UD3-UD0

LD3-LD0

FPDI-1

Pin Name

UD3-UD0

UD3-LD0

a

XSCL FPSHIFT O 81 78 100 CO3

Type

O

F00A

Pin #

70 - 73

74 - 77

F01A

Pin #

67 - 70

71 - 74

D00A

Pad #

86 - 89

90 - 93

Driver Description

Panel display data bus. The data format depends on the

CO3S

specific panel connected. For 4-bit single p anels, LD3-LD0

are driven low (0 state).

Display data shift clock. Data is shifted into the LCD

X-drivers on the falling edge of this signal.

Display data latch clock. The falling edge of this signal is

LP F PLINE O 79 76 96 CO3

used to latch a row of display data in the LCD X-drivers

and to turn on the Y driver (row driver).

For format 1 of 8-bit single color panels this is the second

shift clock.

WF/

XSCL2

MOD

FPSHIFT2

O80 77 97 CO3

For all other modes, this is the LCD backplane BIAS

signal. This output toggles once every frame, or as

programmed in AUX[05] bits 7-2.

Vertical scanning start pulse. A logic ‘1’ on this signal,

YD FPFRAME O 78 75 94 CO3

sampled by the LCD module on the falling edge of LP, is

used by the panel Y driver (row driver) to indicate the start

of the vertical frame.

LCDENB

a

VESA Flat Panel Display Interface Standard (FPDI-1TM)

-----

O82 79 101 CO2

LCD enable signal output. It can be used externally to turn

off the panel supply voltage and backlight.

Table 5-4: Clock Inputs

Pin

Name

Type

F00A

Pin #

F01A

Pin #

D00A

Pad #

Driver Description

This pin, along with OSC2, is the 2-terminal crystal interface when

OSC1I9289115*

using a 2-terminal crystal as the clock input. If an external

oscillator is used as a clock source, then this pin is the clock input.

This pin, along with OSC1, is the 2-terminal crystal interface when

OSC2O9390116*

using a 2-terminal crystal as the clock input. If an external

oscillator is used as a clock source this pin should be left

unconnected.

Table 5-5: Power Supply

Pin Name Type F00A Pin # F01A Pin # D00A Pad # Driver Descripti on

V

DD

V

SS

P 3, 53 50, 100 3, 67 P Voltage supply

P 2, 52 49, 99 1, 65 P Voltage ground

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 34

Page 26 Epson Resear ch and Development

Vancouver Design Center

5.2 Summary of Configuration Options

The S1D13503 requires some configuration information on power-up. This information is provided through the SRAM

data lines VD[0...15]. The state of these pins are read on the falling edge of RESET and used to configure the following

options:

Table 5-6: Summary of Power On / Reset Options

Pin Name value on this pin at falling edge of RESET is used to configure: (1/0)

1 0

VD0 16-bit host bus interface 8-bit host bus interface

VD1 Use direct-mapping for I/O accesses Use internal index register for I/O accesses

VD2 MC68000 MPU interface

VD3

VD12-VD4

Swap of high and low data bytes in 16-bit bus

interface

Select I/O mapping address bits [9:1].

These nine bits are latched on power-up and are compared to the MPU address bits [9-1]. A

valid I/O cycle combined with a valid address will enable the internal I/O decoder. Therefore,

both types of I/O mapping are limited to even address boundaries to determine either the

absolute or indexed I/O address of the first register. Note that a “valid I/O cycle” includes

IOCS# being toggled low.

Select memory mapping address bits [3:1]

MPU / Bus interface with memory accesses

controlled by a READY (WAIT#) signal

No byte swap of high and low data bytes in

16-bit bus interface

These three bits are latched on power-up and are compared to the MPU address bits [1 9-1 7]. A

valid memory cycle combined with a valid address will enable the internal memory decoder.

As only the three most significant bits of the address are compared, the maximum amount of

VD15-VD13

Note

The S1D13503 has internal pulldown r esistors on these pins and theref ore will be pulled down

and read on a logic “0” after RESET. If pullup resistors are required refer to Table 6-3, “Input

Specifications,” on page 27 for pulldown resistor values.

Example: If an ISA bus (no byte swap) with memory segment “A” and I/O location 300h are used, the corresponding

settings of VD15-VD0 would be:

Pin Name

VD00011

VD10 101

VD20000

VD30000

VD12-VD4 11 0000 000 11 0000 xxx 11 0000 000 11 0000 xxx

VD15-VD13 101 101 101 101

memory supported is 128K bytes. Note that a “valid memory cycle” includes MEMCS# being

toggled low.

When using 128K byte memo ry it m us t be m apped at an even address such that all 128K bytes

is available without a change in state on A17, as this would invalidate the internal compare

logic.

Table 5-7: I/O and Memory Addressing Example

8-Bit ISA Bus 16-Bit ISA Bus

Index

Register

Direct Mapping

Index

Register

Direct Mapping

Where x = don’t care; 1 = connected to pull-up resistor; 0 = no pull-up resistor

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 35

Epson Research and Development Page 27

Vancouver Design Center

6 D.C. CHARACTERISTICS

Table 6-1: Absolute Maximum Ratings

Symbol Parameter Rating Units

-0.3 to + 6.0 V

-0.3 to V

-0.3 to V

+ 0.5 V

DD

+ 0.5 V

DD

-65 to 150 ° C

260 for 10 sec. max at lead ° C

= 0 V 2.7 3.0/3.3/5.0 5.5 V

V

SS

= 6 MHz

f

OSC

256 colors

V

SS

-- V

4.5/5.0/11 mA

-40 25 85 ° C

f

= 6 MHz

OSC

256 colors

13.5/16.5/55 mW

DD

V

V

T

T

V

V

DD

IN

OUT

STG

SOL

Supply Voltage

Input Voltage

Output Voltage

Storage Temperature

Solder Temperature/Time

Table 6-2: Recommended Operating Conditions

Symbol Parameter Condition Min Typ Max Units

V

I

T

P

V

OPR

OPR

TYP

Supply Voltage

DD

Input Voltage

IN

Operatin g Current

Operating Temperature

Typical Active Power Consumption

Table 6-3: Input Specifications

Symbol Parameter Condition Min Typ Max Units

VDD = 4.5V

V

IL

V

IH

Low Level Input Voltage

High Level Input Voltage

V

= 3.0V

DD

V

= 2.7V

DD

VDD = 5.5V

V

= 3.6V

DD

V

= 3.3V

DD

2.0

1.3

1.2

VDD = 5.0

V

T+

V

T-

V

H

I

IZ

Positive-going Threshold

Negative-going Threshold

Hysteresis Voltage

Input Leakage Current

V

= 3.3

DD

V

= 3.0

DD

VDD = 5.0

V

= 3.3

DD

V

= 3.0

DD

VDD = 5.0

V

= 3.3

DD

V

= 3.0

DD

0.6

0.5

0.4

0.1

0.1

0.1

-- -1 1

0.8

0.4

0.3

2.4

1.4

1.3

V

V

V

V

V

µA

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 36

Page 28 Epson Resear ch and Development

Vancouver Design Center

Table 6-3: Input Specifications (Continued)

Symbol Parameter Condition Min Typ Max Units

C

IN

R

PD

R

PD

R

PD

Input Pin Capacitance

Pull Down Resistance

Pull Down Resistance

Pull Down Resistance

f =1 MHz,

V

= 0V

DD

VDD = 5.0V

V

= V

I

DD

VDD = 3.3V

V

= V

I

DD

VDD = 3.0V

V

= V

I

DD

12 pF

50 100 200 kΩ

90 180 360 kΩ

100 200 400 kΩ

Table 6-4: Output Specifications

Symbol Parameter Condition Min Typ Max Units

Low Level Output Voltage

V

(5.0V)

OL

Type 1 - TS1D2, CO1

Type 2 - TS2, CO2

Type 3 - TS3, CO3, CO3S

Low Level Output Voltage

V

(3.3V)

OL

Type 1 - TS1D2, CO1

Type 2 - TS2, CO2

Type 3 - TS3, CO3, CO3S

Low Level Output Voltage

VDD = Min

I

= 4 mA

OL

I

= 8 mA

OL

I

= 12 mA

OL

VDD = Min

I

= 2 mA

OL

I

= 4 mA

OL

I

= 6 mA

OL

VDD = Min

0.4 V

0.3 V

I

V

(3.0V)

OL

Type 1 - TS1D2, CO1

Type 2 - TS2, CO2

Type 3 - TS3, CO3, CO3S

High Level Output Volt age

V

(5.0V)

OH

Type 1 - TS1D2, CO1

Type 2 - TS2, CO2

Type 3 - TS3, CO3, CO3S

Low Level Output Voltage

V

(3.3V)

OH

Type 1 - TS1D2, CO1

Type 2 - TS2, CO2

Type 3 - TS3, CO3, CO3S

High Level Output Volt age

V

(3.0V)

OH

Type 1 - TS1D2, CO1

Type 2 - TS2, CO2

Type 3 - TS3, CO3, CO3S

C

C

I

OZ

OUT

BID

Output Leakage Current

Output Pin Capacitance

Bidirectional Pin Capacitance

= 1.8 mA

OL

I

= 3.5 mA

OL

I

= 5 mA

OL

VDD = Min

I

= -4 mA

OH

I

= -8mA

OH

I

= -12 mA

OH

VDD-0.4 V

VDD = Min

I

= -2 mA

OL

I

OL

I

OL

= -4 mA

= -6 mA

VDD-0.3 V

VDD = Min

I

= -1.8 mA

OH

I

= -3.5 mA

OH

I

= -5 mA

OH

VDD-0.3 V

-- -1 1

f =1 MHz,

V

= 0V

DD

f =1 MHz,

V

= 0V

DD

0.3 V

µA

12 pF

12 pF

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 37

Epson Research and Development Page 29

Vancouver Design Center

7 A.C. CHARACTERISTICS

Conditions : VDD = 3.0V ± 10%, VDD = 3.3V ± 10%, or VDD = 5.0V ± 10% TA = -40 °C to 85 °C

T

and T

rise

C

= 80pF (Bus/MPU Interface)

L

C

= 100pF (LCD Panel Interface)

L

C

= 20pF (Display Memory Interface)

L

7.1 Bus Interface Timing

7.1.1 MC68000 Interfac e Timing

Note

All input timing parameters are based on a maximum 16MHz MPU clock.

IOW # Timing

for all inputs must be < 5 nsec (10% ~ 90%)

fall

AB[9:1]

IOCS#

AS#

R/W

UDS#/LDS#

DTACK#

DB[15:0]

t1

INVALID

Hi-Z

t5

VALID

Hi-Z

t2

t3

t4

t6

t7

VALID

Hi-Z

t8

Hi-Z

Figure 10: IOW# Timing (MC68000)

Table 7-1: IOW# Timing (MC68000)

3V/3.3V 5V

Symbol Parameter Min Max Min Max Units

t1

AB[9:1] valid before AS# falling edge

t2

AB[9:1] hold from AS# rising edge

t3

IOCS# hold from AS# rising edge

t4

UDS#/LDS# valid before AS# rising edge

t5

UDS#/LDS# falling edge to DTACK# falling edge

t6

AS# rising edge to DTACK# hi-z delay

t7

DB[15:0] setup to AS# rising edge

t8

DB[15:0] hold from AS# rising edge

10 0 ns

20 10 ns

00ns

30 20 ns

40 25 ns

40 25 ns

20 10 ns

20 10 ns

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 38

Page 30 Epson Resear ch and Development

Vancouver Design Center

IOR# Timing

AB[9:1]

IOCS#

AS#

UDS#/LDS#

R/W#

DTACK#

DB[15:0]

INVALID

Hi-Z

Hi-Z

VALID

t2b

t1

t3

t5

VALID

t2a

t4

Hi-Z

t6

Hi-Z

t7

Figure 11: IOR# Timing (MC68000)

Table 7-2: IOR# Timing (MC68000)

3V/3.3V 5V

Symbol Parameter Min Max Min Max Units

t1

AB[9:1] and IOCS# valid before AS# falling edge

t2

AB[9:1] and IOCS# hold from AS# rising edge

t3

AS# falling edge to DTACK# falling edge

t4

AS# rising edge to DTACK# hi-z delay

t5

AS# falling edge to DB[15:0] valid

t6

DB[15:0] hold from AS# rising edge

t7

AS# rising edge to DB[15:0] hi-z delay

10 0 ns

20 10 ns

40 25 ns

40 25 ns

60 40 ns

20 15 ns

35 25 ns

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 39

Epson Research and Development Page 31

Vancouver Design Center

MEMW# Timing

AB[19:1]

MEMCS#

AS#

UDS#/LDS#

R/W#

DTACK#

DB[15:0]

INVALID

Hi-Z

Hi-Z

t1

t5

VALID

t2

t4

t3

t6

VALID

Hi-Z

Hi-Z

Figure 12: MEMW# Timing (MC68000)

Table 7-3: MEMW# Timing (MC68000)

3V/3.3V 5V

Symbol Parameter Min Max Min Max Units

t1

AB[19:1] and MEMCS# valid before AS# falling edge

t2

AB[19:1] and MEMCS# hold from AS# rising edge

t3

AS# falling edge to DTACK# falling edge

t4

AS# rising edge to DTACK hi-z delay

t5

AS# falling edge to DB[15:0] valid

t6

DB[15:0] hold from AS# rising edge

00ns

00ns

3.5 *

MCLK

+ 20

3.5 *

MCLK

+ 10

40 25 ns

MCLK

-40

MCLK

-20

00ns

ns

ns

Where MCLK period = 1/f

OSC

, or 2/f

OSC

, or 4/f

depending on which disp lay mod e the chi p is in. (s ee s ectio n 9.2 and

OSC

9.3)

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 40

Page 32 Epson Resear ch and Development

Vancouver Design Center

MEMR# Timing

AB[19:1]

MEMCS#

AS#

UDS#/LDS#

R/W#

DTACK#

DB[15:0]

t1

INVALID

Hi-Z

Hi-Z

VALID

t2

t4

t3

t5

VALID

Hi-Z

t6

t7

Figure 13: MEMR# Timing (MC68000)

Table 7-4: MEMR# Timing (MC68000)

3V/3.3V 5V

Symbol Parameter Min Max Min Max Units

t1

AB[19:1] and MEMCS# valid before AS# falling edge

t2

AB[19:1] and MEMCS# hold from AS# rising edge

t3

AS# falling edge to DTACK# falling edge

t4

AS# rising edge to DTACK# hi-z delay

t5

DTACK# falling edge to DB[15:0] valid

t6

DB[15:0] hold from AS# rising edge

t7

AS# rising edge to DB[15:0] hi-z delay

00ns

00ns

3.5 *

MCLK

+ 20

3.5 *

MCLK

+ 10

40 15 ns

20 15 ns

25 15 ns

40 30 ns

Hi-Z

ns

Where MCLK period = 1/f

OSC

, or 2/f

OSC

, or 4/f

depending on which disp lay mod e the chi p is in. (s ee s ectio n 9.2 and

OSC

9.3)

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 41

Epson Research and Development Page 33

Vancouver Design Center

7.1.2 Non-MC68000, MPU/Bus With READY (or WAIT#) Signal

IOW # Timing

AB[9:0]

BHE#

IOCS#

t1

IOW#

DB[15:0]

VALID

Hi-Z

t5

VALID

t2

t4t3

Hi-Z

Figure 14: IOW# Timing (Non-MC68000)

Table 7-5: IOW# Timing (Non-MC68000)

3V/3.3V 5V

Symbol Parameter Min Max Min Max Units

AB[9:0], BHE# and IOCS# valid before IOW# falling

t1

edge

t2

AB[9:0], BHE# and IOCS# hold from IOW# rising edge

t3

DB[15:0] setup to IOW# rising edge

t4

DB[15:0] hold from IOW# rising edge

t5

Pulse width of IOW#

10 0 ns

20 10 ns

20 10 ns

20 10 ns

30 20 ns

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 42

Page 34 Epson Resear ch and Development

Vancouver Design Center

IOR# Timing

AB[9:0]

BHE#

IOCS#

IOR#

DB[15:0]

t1

Hi-Z

t3

VALID

t2

t4

VALID

t5

Figure 15: IOR# Timing (Non-MC68000)

Table 7-6: IO R# Timing (Non-MC68000)

3V/3.3V 5V

Symbol Parameter Min Max Min Max Units

AB[9:0], BHE# and IOCS# valid before IOR# falling

t1

edge

t2

AB[9:0], BHE# and IOCS# hold from IOR# rising edge

t3

IOR# falling edge to DB[15:0] valid

t4

DB[15:0] hold from IOR# rising edge

t5

IOR# rising edge to DB[15:0] hi-z delay

10 0 ns

20 10 ns

60 40 ns

20 15 ns

35 25 ns

Hi-Z

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 43

Epson Research and Development Page 35

Vancouver Design Center

MEMW# Timing

AB[19:0]

BHE#

MEMCS#

MEMW#

READY

DB[15:0]

t1

t3 t6

Hi-Z

VALID

t2

Hi-Z

t5

Hi-Z

t4

VALID

Hi-Z

Figure 16: MEMW# Timing (Non-MC68000)

Table 7-7: MEMW# Timing (Non-MC68000)

3V/3.3V 5V

Symbol Parameter Min Max Min Max Units

AB[19:0], BHE# and MEMCS# valid before MEMW#

t1

falling edge

AB[19:0], BHE# and ME MCS# hold fr om MEMW#

t2

rising edge

t3

MEMW# falling edge to READY falling edge

t4

MEMW# falling edge to DB[15:0] valid

t5

DB[15:0] hold from MEMW# rising edge

t6

READY negated pulse width

00ns

00ns

30 20 ns

MCLK

-40

MCLK

-20

ns

00ns

3.5*

MCLK

+ 20

3.5*

MCLK

+ 10

ns

Where MCLK period = 1/f

OSC

, or 2/f

OSC

, or 4/f

depending on which disp lay mod e the chi p is in. (s ee s ectio n 9.2 and

OSC

9.3)

Hardware Functional Specification S1D13503

Issue Date: 01/01/29 X18A-A-001-08

Page 44

Page 36 Epson Resear ch and Development

Vancouver Design Center

MEMR# Timing

AB[19:0]

BHE#

MEMCS#

MEMR#

READY

DB[15:0]

t1

t3 t7

Hi-Z

VALID

Hi-Z

t2

Hi-Z

t6

t5

VALID

t4

Figure 17: MEMR# Timing (Non-MC68000)

Table 7-8: MEMR# Timing (Non-MC68000)

3V/3.3V 5V

Symbol Parameter Min Max Min Max Units

AB[19:0], BHE# and MEMCS# valid before MEMR#

t1

falling edge

AB[19:0], BHE# and ME MCS# hold fr om MEMR#

t2

rising edge

t3

MEMR# falling edge to READY falling edge

t4

READY rising edge to DB[15:0] valid

t5

DB[15:0] hold from MEMR# rising edge

t6

MEMR# rising edge to DB[15:0] hi-z delay

t7

READY negated pulse width

00ns

00ns

30 20 ns

15 10 ns

20 10 ns

30 20 ns

3.5*

MCLK

+ 20

3.5*

MCLK

+ 10

Hi-Z

ns

Where MCLK period = 1/f

OSC

, or 2/f

OSC

, or 4/f

depending on which display mode the chip is in. (See sect ion 9.2 and

OSC

9.3.)

S1D13503 Hardware Functional Specification

X18A-A-001-08 Issue Date : 01/01/29

Page 45

Epson Research and Development Page 37

Vancouver Design Center

7.2 Clock Input Requirements