Page 1

EPSONIMPACTDOT PRINTER

DLQ-3000

(upgrade model)

SERVICE MANUAL

EPSON

4006094

Page 2

PREFACE

This document provides supplementary information to describe the new DLQ-3000 (Minerva+), which is a

follow-on version of the DLQ-3000 (Minerva). Therefore, you must refer to this information in conjunction with

DLQ-3000 (Minerva) Service Manual for details on any subjects common to both printers.

-i-

Page 3

REVISION SHEET

Revision Issue Date Revision Page

A March 15, 1996 - 1st issue

-ii-

Page 4

DLQ-3000 (MINERVA+) Product Description

1.1 FEATURES

Minerva+ is a 24-pin serial dot-matrix and flat-bed type impact printer. As this printer follows on DLQ-3000

(MINERVA+), the main future is almost same as DLQ-3000 (MINERVA).

The main features are ;

❏ Two built-in and one optional I/F

Bi-Directional Parallel Interface (IEEE-1284 nibble mode)

Serial Interface

Type-B Interface (Option)

The exterior view of DLQ-3000 (MINERVA+) is the same as DLQ-3000 (MINERVA).

Rev.A 1-1

Page 5

Product Description DLQ-3000 (MINERVA+)

1.2 INTERFACE OVERVIEW

The printer provides an 8-bit Bi-directional parallel interface and serial interface as standard. Moreover, it is

possible to interface to various computers using the optional type-B interface board. This section describes

the specifications of the standard interfaces.

1.2.1 Parallel Interface Specifications

1.2.1.1 Forward Channel

Transmission mode: 8-bit parallel, IEEE-1284 compatible mode

Synchronization: By

Handshaking: By BUSY and

STROBE pulse

ACKNLG signal

Signal level: TTL-compatible level, IEEE-1284 level 1 device

Adaptable connector: 57-30360 (Amphenol) or equivalent

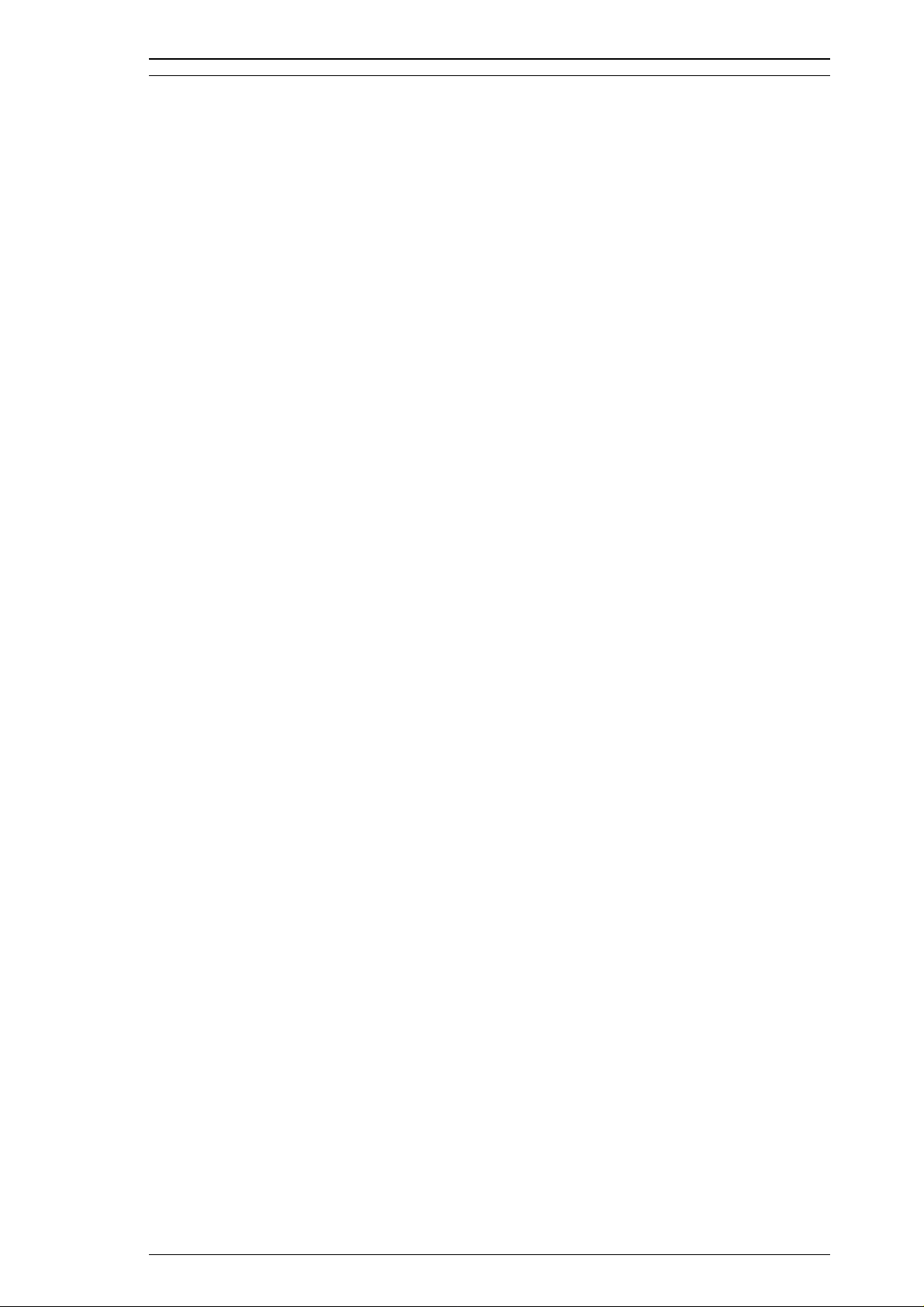

Data transmission timing: See Figure 1-1.

Note: Transition time (rise time and fall time) of every input signal must be less than 200 ns and

every output signal must be less than 120 ns.

The BUSY signal is at a HIGH level before either -ERROR signal is at a LOW level or the PE signal is at a

HIGH level until all these signals return to their inactive state. The BUSY signal is at a HIGH level in the

following cases:

- During data reception (see the figure above)

- When the input buffer is full

- When the

INIT input signal is active

- During initialization

- When the ERROR signal is active

- In the self-test mode

- In the SelecType

- When the parallel interface is not selected.

The

ERROR signal is at a LOW level when the printer is in one of the following conditions:

- Printer hardware error (fatal error)

- A paper-out error

- Release lever operation error

PE signal is at a HIGH level during paper out error.

DATA

-STORBE

BUSY

-ACKNLG

500 ns (min.) 500 ns (min.)

0 (min.) 500 ns (max.)

DATA (n)

500 ns (min.)

Figure 1-1. Data Transmission Timing

DATA (n+1)

0 (min.)

0 (min.)

500 ns ~10 µs

1-2 Rev.A

Page 6

DLQ-3000 (MINERVA+) Product Description

Table 1-1 shows the connector pin assignments and signal functions for the 8-bit parallel interface.

Table 1-1. Signal and Connector Pin Assignments for Parallel Interface

(Forward Channel)

Pin No. Signal Name

1

2-9 DATA1-8 20-27 In

10

11 BUSY 29 Out

12 PE 30 Out

13 SLCT - Out

14

STROBE 19 In

ACKNLG 28 Out

AFXT - In

Return

GND Pin

I/O Description

Strobe pulse. Input data is latched at the falling

edge of this signal.

Parallel input data to the printer.

Active-HIGH input.

LSB: DATA1

MSB: DATA8

Indicates that data has been received and the

printer is ready to accept more data.

A HIGH level means the printer cannot accept

further data.

A HIGH level means a paper-out error. Always

the logical opposite of the ERROR signal.

Always at a HIGH level (pulled up to +5 V

through a 1K-ohm resistor).

Auto feed execution means that a line feed is

automatically performed upon input of a CR

code. Checked when the printer is initialized.

Active-LOW signal.

31

32

36

18,35 Logic H - Out

17 Chassis GND - - Chassis GND

16,19-30,

33

15,34 NC - - Not used. Not connected.

INIT 16 In

ERROR - Out A LOW level means that an error has occurred.

SLIN 30 In Not used.

GND - - Signal GND

Initialize printer. Minimum 50 µs pulse is

necessary. Active-LOW signal.

Pulled up to +5V and shorted to +5V via Schottky

diode, making these signals appear low to the

host when the printer is turned off.

Note: In/Out refers to the direction of signal flow as viewed from the printer.

Rev.A 1-3

Page 7

Product Description DLQ-3000 (MINERVA+)

1.2.1.2 Reverse Channel

Transmission mode: 8-bit parallel, IEEE-1284 nibble mode

Synchronization: Refer to the IEEE-1284 specification

Handshaking: Refer to the IEEE-1284 specification

Signal level: IEEE-1284 level 1 device

Data transmission timing: Refer to the IEEE-1284 specification

Extensibility request: the printer responds to the extensibility request in the affirmative, when the

request is 00H or 04H, which mean;

00H: Request nibble mode of reverse channel transfer

04H: Request device ID in nibble mode of reverse channel

Transfer Device ID:

Table 1-2. Transfer ID

ESC/P2 IBM 2391 Plus

[00H][33H]

MFG:EPSON;

CMD:ESCPL2-00;

MDL:DLQ-3000;

CLS:PRINTER;

[00H][34H]

MFG:EPSON;

CMD:PRPXL24-01;

MDL:DLQ-3000;

CLS:PRINTER;

1-4 Rev.A

Page 8

DLQ-3000 (MINERVA+) Product Description

Table 1-3 shows the connector pin assignments and signal functions for the 8-bit parallel interface.

Table 1-3. Signal and Connector Pin Assignments for Parallel Interface

(Reverse Channel)

Pin No. Signal Name

1 Host Clk

2-9 DATA 1-8 20-27 In

10 Ptr Clk 28 Out Printer clock signal

11

12

13

14 Host Busy 30 In Host busy signal

31

32

PtrBusy /

Data Bit -3,7

Ack Data Req /

Data Bit -2,6

Xflag /

Data Bit -1,5

INIT 30 In Not used.

Data Avail /

Data Bit -0,4

Return

GND Pin

19 In Host clock signal.

29 Out

28 Out

28 Out

29 Out

I/O Description

Parallel input data to the printer.

Active-HIGH input.

LSB: DATA1

MSB: DATA8

Printer BUSY signal and reverse channel

transfer data bit 3 or 7.

Acknowledge data request signal and reverse

channel transfer data bit 2 or 6.

Xflag signal and reverse channel transfer data

bit 1 or 5.

Data available signal and reverse channel

transfer data bit 0 or 4.

36 1284-Active 30 In 1284 active signal

18 Logic H - Out

35 +5V - Out

17 Chassis - - Chassis GND

16,19-30

,33

15,34 NC - - Not used. Not connected.

GND - - Signal GND

A high signal indicates that all other signals

source by the peripheral are in a valid state.

This line is pulled up to +5V through 3.3K Ω

resister.

Note: In/Out refers to the direction of signal flow as viewed from the printer.

Rev.A 1-5

Page 9

Product Description DLQ-3000 (MINERVA+)

1.5 MAIN COMPONENTS

The main components of the DLQ-3000 are designed for easy removal and repair. The main components are

:

■ BOARD ASSY., C124 MAIN-B : control board

■ BOARD ASSY., C124 PSB/PSE : power supply board(100 ~ 120V/220 ~ 240V)

■ C124 SUB board

■ M-5L60 Printer Mechanism

■ Control Panel

■ Housing

1.5.1 BOARD ASSY., C124 MAIN-B

The main board consists of a µPD70433, an E05A88, Program (256 KB Flash memory), CG (8M for Japan /

4 M for other countries), D-RAMs (256 MB), Bi-Directional Interface circuit, etc.

1.5.2 BOARD ASSY., C124 PSB/PSE

This Power supply board consists of two transformers, two switching FETs, a switching regulator IC, diode

bridge, etc. This board has ratings for input AC voltages.

1.5.3 Printer Mechanism

This printer mechanism consists of a 24-pin impact dot head, PF motor , CR motor, color ribbon shift motor,

HP/PG sensor, paper width/paper end sensor, etc.

1.4.5 Housing Assembly

This printer Housing consists of the COVER ASSY.,PRINTER, the HOUSING ASSY.,UPPER, the

HOUSING ASSY.,LOWER and FRAME ASSY.,BOTTOM.

1-6 Rev.A

Page 10

DLQ-3000 (MINERVA+) Service Manual Appendix

A.1 CONNECTOR SUMMARY

This section describes the component connection and detailed pin assignments of each connector of the units.

Figure A-1 shows the component connections of the DLQ-3000, and Table A-1 lists the connector

assignments and reference tables.

C124PSB/PSE

AC

Fan motor

PAR ALL EL I/F

SERIAL I/F

TYPE-B I/F

Panel

Cover Open Sensor

temp .

CN10 -1 2

CN 15,16

CN9

CN7

CN8

CN6

CN13

CN14

CN1

CN2

CN3

CN4

CN5

Printer MechanismC124 MAIN-B

Printhead

CS Motor

Film Ribbon Se nsor

Color Ribbo n Sensor

PEWSensor Assembly

CR Motor Asse mbly

PF Motor Assemb ly

LOAD Sensor Assembly

External Fan

PF Sensor

HP Sensor

Figure A-1. Cable Connection

Rev.A A-1

Page 11

Appendix DLQ-3000 (MINERVA+) Service Manual

Table A-2 through appendix lists connector pin assignments.

Table A-1. Connector Assignment

Board

BOARD

ASSY.,C124

MAIN-B

Connector

CN 1 20 Printhead drive signal output

CN 2 20 Printhead drive signal output

CN 3 14 CS motor, Color ribbon / film ribbon / CS home sensor

CN 4 11 CR motor, PF motor output

CN 5 13 PG/ REL/COVER OPEN/LOAD sensor, External fan motor

CN 6 36 Type -B I/F

CN 7 36 Bi-Directional parallel I/F

CN 8 25 Serial I/F

CN 9 2 Power supply board fan motor

CN 10 4 Power supply input (+5V)

CN 11 6 Power supply input (+35V)

CN 12 6 Power supply input (+35V)

CN 13 10 Control panel

CN 14 2 CR motor common (cover open sensor)

CN 15 2 Power supply board temp.

Pin Description

C124 SUB

BOARD

BOARD

ASSY., C124

PSB / PSE

CN 16 2 Power supply board temp.

CN 4 From CN1 to Printhead output signal

CN 5 From CN2 to Printhead output signal

CN 6

CN 1 2 AC input line

CN 2 10 DC output ( +5V, +35V )

CN 3 6 DC output ( +35V )

From CN3 to CS motor, Color ribbon / film ribbon / CS

home sensor

A-2 Rev.A

Page 12

DLQ-3000 (MINERVA+) Service Manual Appendix

Table A-2. Connector Pin Assignment - CN7

Pin I/O Name Description (Forward / Reverse)

1I

2 - 9 I DATA 0-7 Parallel data bit 0 to 7

10 O

11 O

12 O

13 O

14 I

15 - NC Not used and not connected.

16 - GND Signal Ground

STOBE / Host

Clk

ACKNLG /

PtrClk

BUSY /

PtrBusy, Data

Bit-3,7

PE /

AckDataReq,

Data Bit-2,6

SLCT / Xflag,

Data Bit-1,5

AFXT / Host

Busy

Data strobe / Host clock signal

Acknowledge / Printer clock signal

Printer busy and reverse channel transfer data bit 3 or 7

Paper out / Acknowledge data request and reverse channel

transfer data bit 2 or 6

Always HIGH at printer power on / Xflag and reverse

channel transfer data bit 1 or 5

Not used / Host busy signal

17 - Chassis GND Chassis ground

18 O Logic-H

19-30 - GND Signal Ground

31 I

32 O

33 - GND Signal Ground

34 - NC Not used and not connected.

35 O +5V Pulled up 5V

36 I

INIT / INIT Initialize signal / Not used

ERROR / data

avail, data

bit-0,4

SLIN /

1284-Active

Pulled up 5V / A HIGH signal indicates that all other signals

soursed by the peripheral are in valid state.

Error signal / Data available and reverse channel data bit 0,4

Not used. / 1284-active signal

Note: The signal direction I/O are viewed from the connector on the board.

Rev.A A-3

Page 13

DLQ-3000 (MINERVA+) Service Manual Appendix

CN1

Head Conn 1

from mainboard

CN2

Head Conn 2

from mainboard

COM14 20

COM10/18 13

COM6/22 2

COM2 14

COM23 10

COM3/19 4

COM7/15 6

COM11 3

HD2 17

HD3 9

HD6 15

HD7 19

HD10 16

HD11 11

HD14 12

HD15 1

HD18 18

HD19 8

HD22 7

HD23 5

COM12/16 10

COM8/20 15

COM4/24 11

COM1/21 1

COM5/17 7

COM9/13 2

HD1 13

HD4 17

HD5 3

HD8 18

HD9 5

HD12 12

HD13 4

HD16 16

HD17 5

HD20 9

HD21 8

HD24 14

TENP 19

TEMP 20

20 COM14

13 COM10/18

2 COM6/22

14 COM2

10 COM23

4 COM3/19

6 COM7/15

3 COM11

17 HD2

9 HD3

15 HD6

19 HD7

16 HD10

11 HD11

12 HD14

1 HD15

18 HD18

8 HD19

7 HD22

5 HD23

10 COM12/16

15 COM8/20

11 COM4/24

1 C O M1/2 1

7 C O M5/1 7

2 C O M9/1 3

13 HD1

17 HD4

3 HD5

18 HD8

5 HD9

12 HD12

4 HD1 3

6 HD1 6

5 HD1 7

9 HD2 0

8 HD2 1

14 HD24

19 TEMP

20 TEMP

CN 4

Head conn 1

to Hea d

CN 5

Head conn 2

to H ea d

CN1

Head Conn 1

from mainboard

+5V 1

PEWR/L 5

PWLCOM 6

PWRCOM 2

RFCOM 7

RFA 11

RF_A 9

RFB 10

RF_B 8

CSHOME 3

GND 4

COLOR 13

FILM 14

GND 12

1 +5v

5 PEWR/L

5 PWLCOM

2 PWRCOM

7 RFCOM

11 R FA

9 RF_ A

10 R FB

8 RF_ B

3 CSHOME

4 G N D

13 COLOR

14 FILM

12 GND

CN 4

Head conn 1

to He ad

Figure A-4. C124 MAIN SUB Board Circuit Diagram

Rev.A A-9

Page 14

Appendix DLQ-3000 (MINERVA+) Service Manual

A

A

0

.

5

.

1

1

/

/

B

.

V

V

L

5

G

+

0

8

7

9

2

1

N

C

u

V

4

0

0

5

0

2

3

1

1

0

0

W

2

5

C

.

2

1

D

0

R

S

5

1

1

4

8

R

5

0

5

2

0

1

C

-

5

-

L

R

1

1

E

0

D

2

P

L

1

9

5

6

1

4

0

1

Q

1

2

A

6

1

R

L

5

1

5

A

K

0

1

6

0

6

D

1

S

1

R

9

5

1

R

8

5

1

R

9

Z

Z

1

0

H

1

1

1

2

K

K

5

5

1

3

.

7

1

.

1

4

4

8

4

8

1

5

1

1

6

R

1

4

K

p

5

0

9

0

9

1

4

0

6

5

L

1

C

5

1

I

T

C

1

0

1

T

7

1

3

1

R

1

0

1

B

1

D

6

0

5

2

V

B

R

5

4

k

0

1

6

6

1

1

1

1

R

R

1

5

1

B

2

5

1

R

W

0

2

1

5

1

R

E

E

C

V

O

-

R

+

8

/

2

2

6

0

0

2

5

1

0

X

6

7

1

3

A

1

4

R

Q

K

6

3

.

8

6

1

1

2

2

C

C

C

I

O

I

2

2

W

2

/

2

2

.

0

3

3

1

7

C

G

R

D

6

N

T

5

R

T

C

4

T

C

3

D

I

-

F

B

2

I

1

1

1

+

K

0

6

7

0

6

6

2

1

1

R

R

4

0

0

2

2

8

5

A

1

R

D

E

4

3

1

1

6

4

5

W

1

/

K

0

8

0

1

1

1

R

1

0

1

B

V

K

2

5

.

1

1

1

/

C

p

0

0

3

3

V

0

0

1

2

1

/

1

u

C

0

6

5

W

5

1

2

.

0

3

1

2

Y

R

T

*

W

5

2

2

R

.

F

2

T

2

4

B

h

5

p

c

3

G

+

3

5

2

4

6

1

u

1

1

.

8

0

1

C

2

-

3

5

1

D

Z

2

8

K

1

2

R

K

K

6

2

.

2

3

.

7

7

5

1

1

1

R

R

k

5

K

1

0

.

0

7

7

1

1

1

1

R

R

V

K

3

5

1

5

0

1

1

A

u

1

0

.

0

8

5

1

C

K

3

Q

0

1

P

0

1

1

5

1

F

2

D

1

3

0

1

3

W

1

/

0

1

0

1

1

3

R

F

u

1

3

.

1

0

1

C

1

5

0

5

1

8

*

1

Q

K

p

0

0

2

1

p

2

3

0

C

0

2

2

8

C

A

7

4

Z

G

2

1

M

S

2

C

Q

V

0

2

5

/

X

u

2

0

5

0

1

3

C

3

1

5

1

C

2

9

1

4

0

0

2

8

A

1

R

3

E

1

D

1

7

4

0

0

2

8

A

R

E

6

1

1

C

u

2

2

.

0

1

1

1

k

R

0

7

3

1

.

1

5

D

3

4

1

1

0

0

R

1

1

Q

5

1

1

R

2

8

0

0

4

1

4

C

Q

4

1

1

V

C

K

2

.

1

/

p

0

0

3

3

0

A

7

4

2

1

1

0

R

0

7

6

7

2

1

2

1

R

0

2

1

2

0

S

1

p

S

K

0

D

1

0

0

9

1

7

1

1

4

R

K

7

1

.

2

4

1

R

p

0

0

4

3

C

3

p

0

0

3

3

C

3

K

3

7

0

4

5

.

.

1

7

7

6

2

1

1

/

R

R

u

0

7

4

7

5

1

C

3

5

4

8

8

8

2

2

1

1

1

-

-

D

D

D

A

A

6

Z

Z

6

Z

S

S

Z

Z

H

H

0

6

0

5

3

1

R

7

5

1

1

1

2

u

V

0

5

0

2

2

1

1

1

C

1

1

0

1

1

3

4

C

I

M

J

N

K

4

0

.

2

2

1

R

4

2

1

L

R

2

1

1

0

1

C

P

4

3

1

2

V

3

6

1

/

U

0

0

7

2

1

2

1

C

W

3

/

0

3

2

.

1

0

1

R

C

0

3

5

u

8

8

D

8

6

.

1

1

F

0

1

C

L

E

3

B

7

B

A

S

2

Z

S

5

J

H

1

9

D

3

Z

D

R

S

E

4

1

1

5

C

5

T

1

D

Q

4

5

5

1

8

1

1

Q

C

2

8

2

2

1

-

-

D

A

A

Z

6

2

6

-

1

S

S

8

A

Z

Z

6

1

H

H

D

S

Z

Z

H

1

5

2

-

1

A

D

6

Z

S

Z

H

0

1

2

8

1

1

S

0

1

5

1

1

2

5

P

L

T

3

0

1

D

2

3

1

R

4

2

1

R

8

D

S

6

1

1

R

2

1

2

0

1

C

P

6

5

4

0

0

2

8

A

4

R

0

E

0

2

8

A

1

3

R

2

0

3

E

1

2

2

D

R

3

9

2

4

3

1

0

-

R

3

4

B

4

R

0

E

1

D

W

2

/

0

2

2

6

2

1

R

V

K

5

0

2

9

1

3

/

1

A

R

0

1

1

F

0

0

0

2

2

1

1

9

1

5

6

S

S

4

4

1

S

S

5

5

1

R

1

1

2

D

D

k

0

1

G

1

4

1

5

0

P

2

L

T

T

4

u

1

8

0

.

1

1

0

C

K

7

5

2

2

1

R

4

0

3

4

B

4

R

0

E

2

D

W

1

/

K

0

0

1

2

N

1

N

C

1

L

6

5

1

C

4

2

5

-

1

A

6

D

Z

S

0

Z

2

H

1

4

S

K

5

3

S

0

1

5

5

K

1

2

R

5

1

2

1

D

R

5

4

5

0

1

0

C

2

8

A

2

R

5

E

2

D

4

1

7

5

4

6

W

2

/

2

2

1

.

3

0

2

R

W

1

/

k

0

8

0

1

1

2

R

V

0

0

1

2

1

/

2

u

C

0

6

5

A

5

.

1

/

A

A

.

V

p

h

5

c

G

3

+

1

6

5

3

4

2

3

N

C

K

K

6

2

.

2

3

.

7

7

5

1

2

2

R

R

k

5

.

1

K

0

0

7

7

1

2

2

1

R

R

3

5

5

1

2

0

1

Q

A

V

6

1

/

u

3

3

V

0

2

5

/

X

u

Q

0

1

P

F

0

1

1

F

u

5

1

2

.

1

0

D

3

1

1

1

2

R

3

1

2

C

1

5

0

5

2

*

8

1

1

Q

0

K

2

B

V

K

5

2

.

1

2

1

/

C

p

0

0

3

3

2

0

5

0

2

3

C

3

1

2

5

2

3

C

9

2

0

1

1

4

0

0

-

3

2

8

A

1

R

3

E

2

D

W

4

1

0

1

/

0

0

0

-

3

2

2

1

0

5

D

3

8

2

1

3

0

A

0

R

1

2

R

E

A

Q

F

u

1

0

.

5

7

0

6

1

2

1

2

2

R

R

2

8

0

0

4

2

4

Q

C

0

2

1

2

S

0

S

2

1

D

p

0

0

4

7

1

4

2

V

C

K

2

.

1

/

p

6

0

1

0

2

3

C

3

1

1

1

0

2

C

P

1

2

1

7

u

1

V

0

2

5

0

k

2

2

R

1

1

7

.

2

4

C

2

1

3

1

0

1

3

7

4

0

4

1

2

2

M

2

C

J

I

R

0

N

7

2

K

0

9

1

1

2

R

1

2

2

R

W

3

/

0

3

2

.

1

0

2

R

K

K

4

7

0

.

.

2

2

4

2

R

)

1

5

2

D

,

1

5

1

D

,

1

0

2

Q

,

1

0

)

1

1

Q

,

8

1

1

0

d

C

1

(

e

t

Y

n

T

(

u

o

k

n

i

m

s

t

t

a

e

o

H

N

0

1

2

0

8

1

6

0

2

S

5

3

D

2

S

1

R

7

0

5

1

2

5

R

2

1

1

1

2

5

P

L

4

3

T

Figure A-5. C124 PSB Board Circuit Diagram

A-10 Rev.A

Page 15

DLQ-3000 (MINERVA+) Service Manual Appendix

A

A

0

5

.

.

1

1

/

/

B

V

V

L

.

5

h

5

3

G

+

0

7

9

8

1

2

N

C

u

V

0

4

0

0

5

1

0

1

1

C

4

3

2

5

2

D

1

W

.

S

2

R

0

5

R

1

1

2

5

5

8

-

5

1

1

C

1

L

0

R

D

2

E

P

L

1

9

6

5

4

1

1

1

0

Q

6

A

2

1

R

5

L

5

1

K

0

1

A

0

6

6

D

1

1

S

Z

R

Z

9

H

1

0

1

1

2

1

K

K

3

1

5

5

1

.

9

7

4

1

8

4

.

5

1

4

8

1

R

1

5

R

6

1

4

p

1

K

9

0

5

8

9

0

4

6

1

5

5

0

L

5

1

1

1

C

T

I

C

R

1

0

1

T

7

1

3

1

R

0

6

A

1

B

0

S

1

5

B

D

D

1

5

6

6

k

0

1

1

1

0

R

R

1

4

0

0

1

-

5

1

B

2

5

1

R

W

1

2

2

/

5

X

1

R

E

E

C

V

O

-

R

+

0

0

8

2

7

0

2

6

0

5

4

6

1

3

1

1

A

R

Q

K

6

3

.

8

6

1

1

2

2

C

C

C

I

O

I

2

2

W

2

/

2

2

.

0

3

3

C

7

1

G

D

R

6

N

T

R

5

T

C

4

C

D

T

3

I

-

F

B

2

I

1

1

1

+

K

0

7

6

0

6

6

2

1

1

R

R

4

0

0

2

2

8

5

A

1

R

D

E

4

3

1

1

6

5

4

W

W

1

1

/

/

K

K

0

8

2

1

R

1

3

C

0

8

1

0

0

1

1

1

R

1

0

1

B

5

1

1

C

V

0

1

0

1

4

/

1

u

C

0

5

1

p

0

0

7

4

7

4

W

.

R

5

4

1

0

3

1

*

7

R

Y

W

.

T

5

4

2

W

7

R

.

5

4

F

2

T

4

B

c

+

p

G

5

6

3

4

1

2

u

1

1

.

8

0

1

C

2

-

3

B

5

1

D

Z

2

8

K

1

2

R

K

K

6

2

3

2

.

.

7

7

5

1

1

1

R

R

k

5

K

1

0

.

0

7

7

1

1

1

1

R

R

5

3

1

0

5

1

1

A

u

1

0

.

8

0

5

1

C

K

3

Q

0

1

P

1

0

5

1

1

2

F

D

1

0

1

3

W

1

/

1

0

1

0

1

3

R

F

u

3

1

.

1

0

1

C

1

2

9

0

6

1

1

Q

K

*

V

V

K

K

2

2

6

.

.

1

1

1

/

1

/

p

C

p

0

0

0

0

3

3

3

3

p

0

0

8

7

4

C

A

7

4

Z

J

8

M

S

2

C

Q

2

V

X

0

2

5

/

5

1

u

C

0

0

3

1

5

3

1

C

3

9

2

1

4

0

0

-

2

8

1

A

3

R

1

E

D

7

1

1

u

2

1

0

1

1

4

0

0

0

1

-

D

5

3

2

1

8

0

0

A

1

1

R

A

Q

E

0

5

7

1

2

1

R

2

8

0

0

4

1

4

Q

C

2

0

1

D

p

4

0

1

0

1

7

4

C

p

0

0

9

7

C

4

4

u

C

2

2

.

0

3

C

0

1

R

k

1

C

7

3

.

1

1

4

1

R

0

4

3

1

7

1

2

1

0

R

1

C

I

0

6

7

1

2

1

R

0

2

1

S

S

1

K

0

9

1

1

1

R

K

K

7

4

1

0

.

.

2

2

4

2

1

1

R

R

p

0

0

4

7

4

p

2

0

0

7

4

1

L

K

K

0

7

V

4

5

.

1

7

7

3

2

.

1

1

6

R

R

/

u

0

7

7

5

4

1

C

3

5

4

8

8

8

2

2

2

1

1

1

-

-

-

D

D

D

A

A

A

Z

Z

6

6

Z

6

S

S

S

Z

Z

Z

H

H

H

0

6

0

5

3

1

R

7

5

1

R

1

1

1

1

0

1

C

5

P

2

1

V

5

2

2

V

1

3

4

M

J

N

2

1

1

R

3

Z

0

5

8

D

8

1

F

L

E

6

1

/

u

0

7

0

1

2

1

2

C

W

3

/

8

6

.

0

u

8

1

6

.

1

0

C

3

7

B

S

Z

A

2

5

S

H

1

J

9

D

3

Z

D

R

S

E

4

1

5

1

5

C

1

T

Q

D

4

5

5

1

1

8

1

Q

C

6

5

2

8

2

1

2

-

-

D

1

A

A

Z

8

6

6

1

S

S

D

Z

Z

Z

H

H

2

-

1

A

5

6

1

S

D

Z

Z

H

1

0

2

8

1

1

0

S

D

1

S

5

1

2

)

2

F

2

4

L

0

3

-

1

6

B

C

P

P

L

G

4

6

-

T

4

D

(

4

0

0

-

2

3

8

0

4

A

1

0

R

0

D

-

E

2

8

1

3

2

2

A

0

3

3

1

R

2

1

2

E

D

R

R

3

9

2

3

1

5

0

R

-

8

3

4

B

0

R

1

E

D

W

2

/

4

6

2

0

2

1

2

1

R

2

R

7

2

1

R

W

5

.

V

0

/

0

5

K

1

2

0

/

R

9

H

3

A

1

5

F

T

0

0

2

2

0

1

1

1

9

4

S

S

4

5

6

5

S

5

1

R

k

8

0

6

1

1

R

1

2

5

8

1

1

C

5

2

1

R

W

1

/

K

0

0

1

W

1

/

K

0

0

1

S

1

1

2

1

D

D

)

2

F

L

4

D

(

J

1

7

0

4

2

6

T

P

4

L

7

T

u

1

0

.

0

K

0

1

2

1

1

3

2

R

5

0

8

3

4

B

0

R

2

E

D

N

1

N

C

L

1

C

4

5

1

D

Z

0

2

3

5

4

1

5

5

5

S

1

1

1

K

S

D

R

2

R

1

5

5

1

4

C

0

0

-

2

8

A

2

R

5

E

2

D

4

1

6

4

5

W

2

/

2

2

.

0

W

1

/

8

K

2

0

2

0

R

1

V

0

0

1

4

1

/

2

u

C

0

5

1

A

5

.

1

/

V

A

A

.

5

p

h

3

c

G

+

5

6

3

4

2

1

3

N

C

3

2

K

K

7

7

6

2

2

2

.

.

R

R

5

1

0

k

1

7

K

5

7

2

0

.

2

1

R

1

R

3

5

5

1

2

0

1

Q

A

V

6

1

/

u

3

3

2

A

6

S

Z

H

K

Q

0

0

2

1

P

0

F

1

1

F

u

5

1

2

.

2

D

0

3

1

0

3

1

1

3

W

4

1

/

0

0

0

1

-

1

0

2

2

3

8

R

A

R

F

E

u

3

1

.

1

0

2

W

2

C

1

0

/

2

K

8

Q

1

0

2

0

R

1

2

1

9

0

6

1

*

2

0

1

2

K

Q

B

V

V

K

K

2

2

5

6

.

.

1

1

1

1

2

2

/

/

C

C

p

p

0

0

0

0

3

3

3

3

)

1

5

2

D

,

1

5

1

D

,

1

0

2

Q

,

1

0

1

Q

,

1

0

1

Y

T

(

k

n

i

s

t

a

e

H

2

V

X

0

5

/

2

u

5

2

0

0

C

3

3

1

5

2

C

9

2

1

4

0

0

-

2

8

A

1

R

3

E

2

D

1

0

2

D

3

0

2

Q

8

0

4

4

C

)

1

8

1

C

(

d

e

t

n

u

o

m

t

o

N

1

7

1

u

2

V

2

0

1

3

1

2

R

5

1

0

1

A

0

5

7

1

2

2

R

0

2

2

1

0

S

2

S

D

1

p

0

4

0

1

2

7

4

C

5

R

0

2

k

2

1

C

7

.

4

1

0

1

7

4

0

1

2

2

6

2

0

1

C

I

R

7

2

2

R

K

0

1

9

1

2

R

K

K

4

7

1

0

.

.

2

2

2

4

2

2

R

R

0

6

0

5

3

2

1

0

R

2

8

2

1

0

7

S

D

1

5

S

5

2

1

R

)

1

1

1

2

2

3

1

3

4

M

J

N

W

3

/

8

2

6

.

1

2

0

R

2

F

1

2

L

4

-

1

3

0

B

6

2

P

G

C

L

-

T

P

4

D

4

5

(

Figure A-6. C124 PSE Board Circuit Diagram

Rev.A A-11

Page 16

EPSON

Loading...

Loading...