Page 1

A

3A ULTRA LOW DROPOUT LINEAR REGULATOR WITH ENABLE

Description

The AP7175 is a 3.0A ultra low-dropout (LDO) linear regulator that

features an enable input and a power-good output.

The enable input and power-good output allow users to configure

power management solutions that can meet the sequencing

requirements of FPGAs, DSPs, and other applications with different

start-up and power-down requirements.

The AP7175 features two supply inputs, for power conversion supply

and control. With the separation of the control and the power input

very low dropout voltages can be reached and power dissipation is

reduced.

A precision reference and feedback control deliver 1.5% accuracy

over load, line, and operating temperature ranges.

The AP7175 is available in SO-8EP and MSOP-8EP package with an

NEW PRODUCT

exposed PAD to reduce the junction to case resistance and extend

the temperature range it can be used in.

Features

• VIN Range: 1.2V to 3.65V V

• Adjustable output voltage

• Continuous Output Current I

• Fast transient response

• Power on reset monitoring on V

• Internal Softstart

• Stable with Low ESR MLCC capacitors

• Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

• Halogen and Antimony Free. “Green” Device (Note 3)

Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

2. See http://www.diodes.com for more information about Diodes Incorporated’s definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. Halogen- and Antimony-free "Green” products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and

<1000ppm antimony compounds.

3.0V to 5.5V

CNTL

= 3A

OUT

CNTL

and VIN

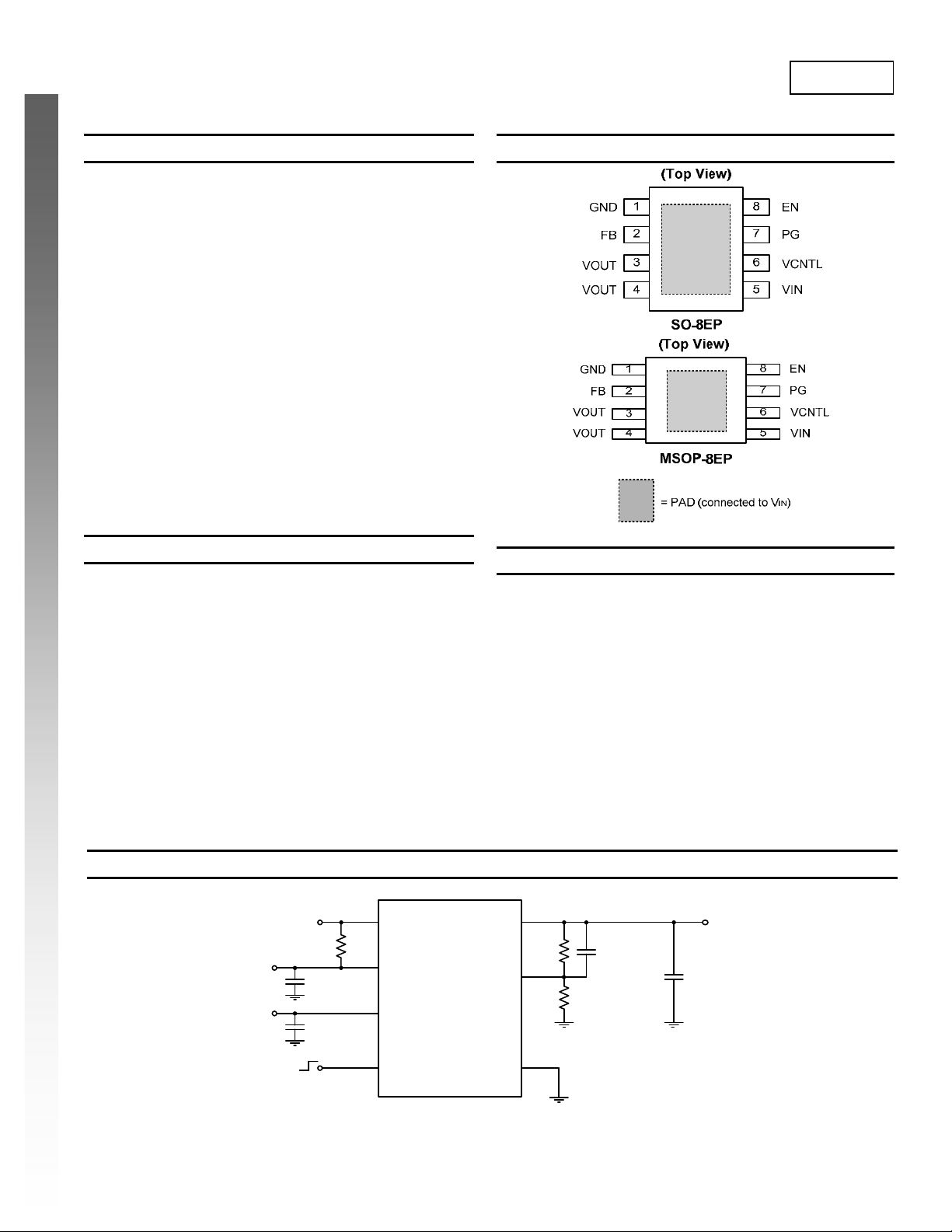

Pin Assignments

Applications

• Notebook

• PC

• Netbook

• Wireless Communication

• Server

• Motherboard

• Dongle

• Front Side Bus VTT (1.2V/3.3A)

P7175

Typical Applications Circuit

R3

5.1K

C

CNTL

1uF

C

IN

10uF

ON

OFF

AP7175

Document number: DS35606 Rev. 3 - 2

PG

VCNTL

VIN

EN

AP7175

VOUT

FB

GND

R1

12K

R2

24K

Figure 1. Typical Application Circuit

1 of 14

www.diodes.com

C1

*Optional

C

OUT

10uF

December 2012

© Diodes Incorporated

Page 2

A

Pin Descriptions

Pin Number

SO-8EP MSOP-8EP

3/4 3/4

5 5

6 6

NEW PRODUCT

Pin

Name

GND 1 1 Ground

FB 2 2

V

OUT

VIN

V

CNTL

PG 7 7

EN 8 8

PAD EP EP

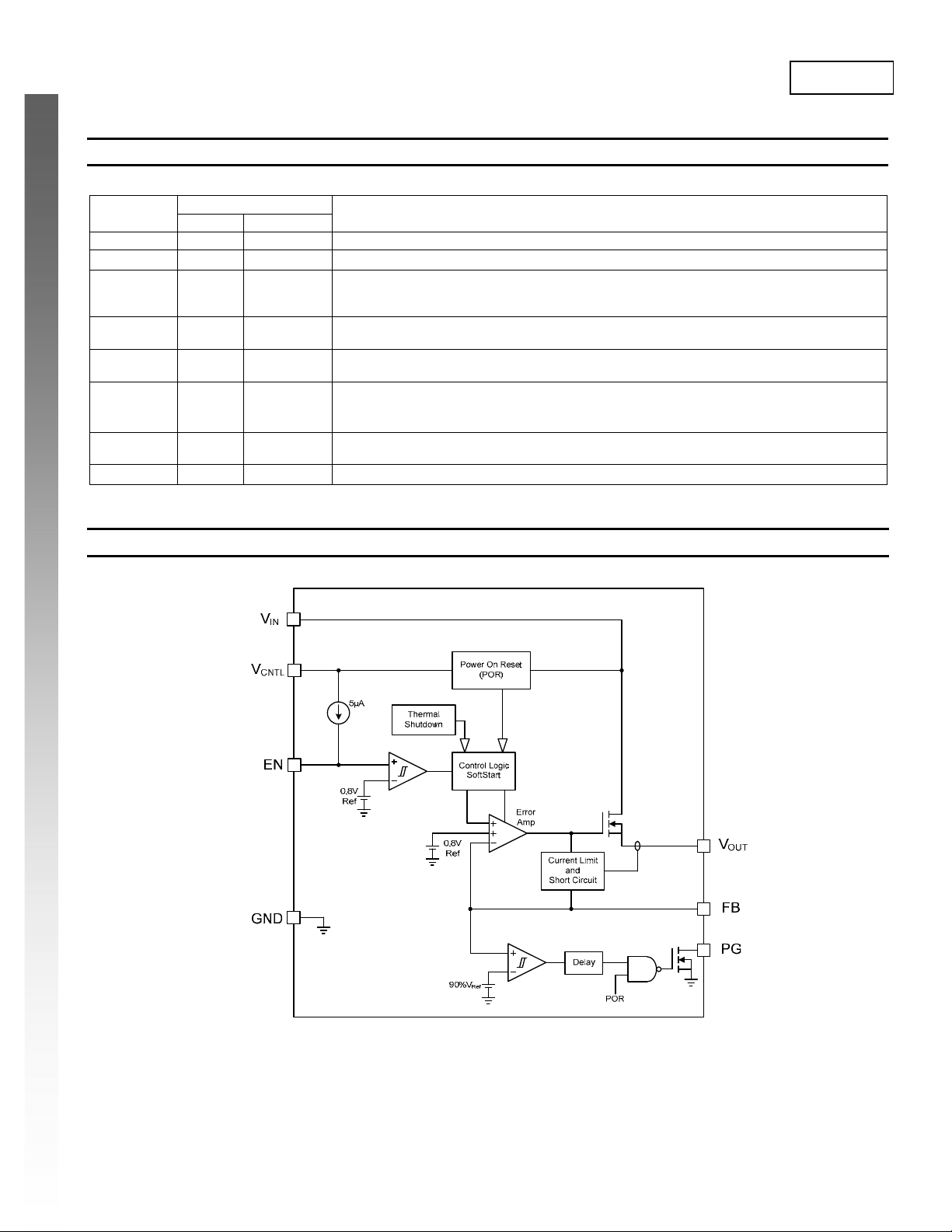

Functional Block Diagram

P7175

Function

Feedback to set the output voltage via an external resistor divider between V

Power Output Pin. Connect at least 10µF capacitor to this pin to improve transient response and

required for stability. When the part is disabled the output is discharged via an internal pull-low

MOSFET.

Power Input Pin for current supply. Connect a decoupling capacitor (10µF) as close as possible to

the pin for noise filtering.

BIAS supply for the controller, recommended 5V. Connect a decoupling capacitor (1µF) as close

as possible to the pin for noise filtering.

Power Good output open drain to indicate the status of V

pulled low when the voltage is outside the limits, during thermal shutdown and if either V

go below their thresholds.

Enable pin. Driving this pin low will disable the part. When left floating an internal current source will

pull this pin high and enable it.

Exposed pad connect this to V

for good thermal conductivity.

IN

via monitoring the FB pin. This pin is

OUT

and GND.

OUT

CNTL

or VIN

AP7175

Document number: DS35606 Rev. 3 - 2

2 of 14

www.diodes.com

December 2012

© Diodes Incorporated

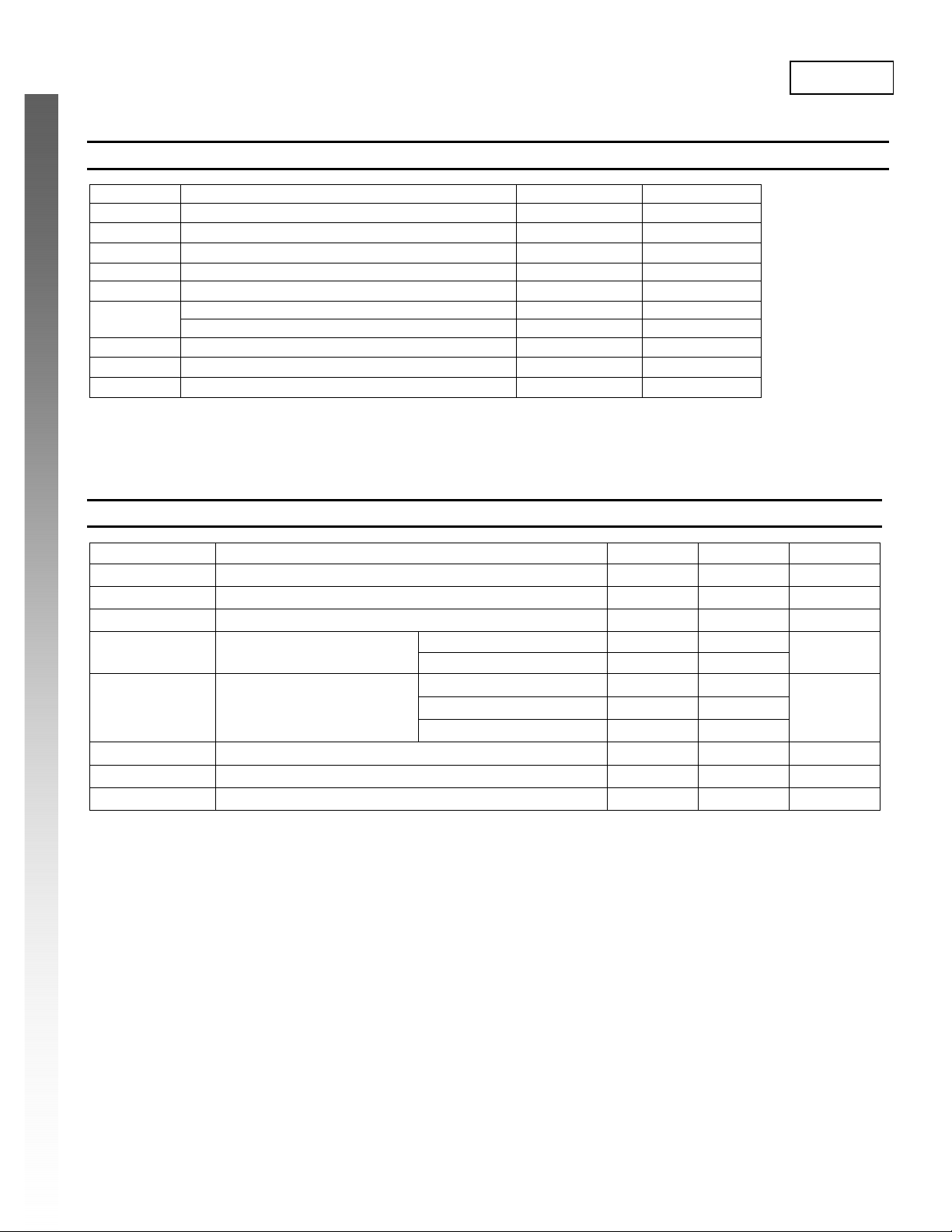

Page 3

A

Absolute Maximum Ratings (Note 4) (@T

= +25°C, unless otherwise specified.)

A

Symbol Parameter Rating Unit

VIN V

V

V

CNTL

V

V

OUT

Supply Voltage (VIN to GND)

IN

CNTL

OUT

Supply Voltage (V

CNTL

to GND)

to GND Voltage -0.3 to VIN +0.3

-0.3 to +4.0 V

-0.3 to +7.0 V

V

PG to GND Voltage -0.3 to +7.0 V

EN, FB to GND Voltage

PD

TJ

T

STG

T

SDR

Note: 4. Stresses greater than the 'Absolute Maximum Ratings' specified above, may cause permanent damage to the device. These are stress ratings only;

functional operation of the device at these or any other conditions exceeding those indicated in this specification is not implied. Device reliability may

be affected by exposure to absolute maximum rating conditions for extended periods of time.

Power Dissipation (SO-8EP) 1.7 W

Power Dissipation (MSOP-8EP) 1.5

Maximum Junction Temperature 150 °C

Storage Temperature -65 to +150 °C

Maximum Lead Soldering Temperature, 10 Seconds 260 °C

-0.3 to V

CNTL

+0.3

V

NEW PRODUCT

Recommended Operating Conditions (@T

= +25°C, unless otherwise specified.)

A

Symbol Parameter Min Max Unit

V

V

CNTL

VIN V

V

V

OUT

I

V

OUT

C

V

OUT

E

ESR of V

SRCOUT

TA

TJ

CNTL

IN

OUT

OUT

OUT

Ambient Temperature -40 +85 °C

Junction Temperature -40 +125

Supply Voltage

Supply Voltage

Output Voltage (when V

Output Current

Output Capacitance

Output Capacitor

OUT

CNTL-VOUT

>1.9V)

Continuous Current 0 3

Peak Current 0 4

I

= 3A at 25% nominal V

OUT

I

= 2A at 25% nominal V

OUT

I

= 1A at 25% nominal V

OUT

OUT

OUT

OUT

3.0 5.5 V

1.2 3.65 V

0.8

8 1100

8 1700

8 2400

VIN - V

DROP

0 200 m

AP7175

Document number: DS35606 Rev. 3 - 2

3 of 14

www.diodes.com

P7175

V

A

µF

°C

December 2012

© Diodes Incorporated

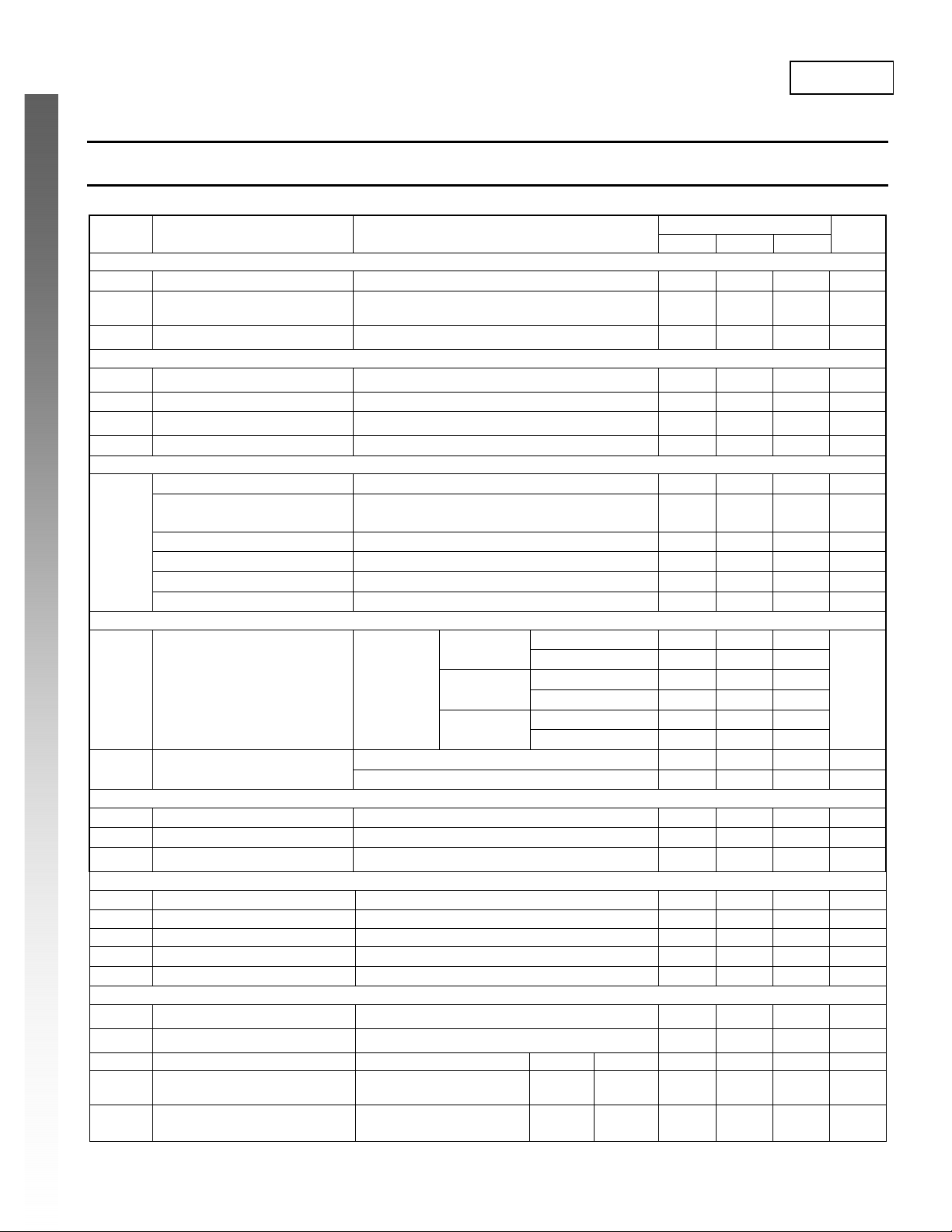

Page 4

A

Electrical Characteristics

(V

= 5V, VIN = 1.8V, V

CNTL

= 1.2V and TA = -40 to +85°C, @TA = +25°C, unless otherwise specified.)

OUT

Symbol Parameter Test Conditions

Min Typ Max

SUPPLY CURRENT

IV

CNTL

ISD

V

Supply Current EN = V

CNTL

V

Supply Current at

CNTL

Shutdown

, I

CNTL

EN = GND — 15 30 µA

VIN Supply Current at Shutdown EN = GND, VIN=3.65V

OUT

=0A

— 1.0 1.5 mA

— — 1 µA

POWER-ON-RESET (POR)

2.5 2.7 2.95 V

— 0.4 — V

0.8 0.9 1.0 V

— 0.5 — V

— 0.8 — V

-1.5 — +1.5 %

— 0.06 0.25 %

-0.15 — +0.15 %/V

— 10 —

-100 — 100 nA

NEW PRODUCT

Rising V

V

POR Hysteresis

CNTL

Rising V

VIN POR Hysteresis

OUTPUT VOLTAGE

Reference Voltage

Output Voltage Accuracy

REF

Load Regulation

V

Line Regulation

V

Pull-low Resistance V

OUT

FB Input Current

POR Threshold

CNTL

POR Threshold

IN

FB = V

V

CNTL

T

J

I

OUT

I

OUT

CNTL

V

FB

OUT

=3.0 ~ 5.5V, I

= -40 to +125°C

=0A to 3A

=10mA, V

= 3.3V, VEN = 0V, V

= 0.8V

OUT

= 3.0 to 5.5V

CNTL

= 0 to 3A,

< 0.8V

OUT

DROPOUT VOLTAGE

= +25°C

T

J

TJ = -40 to +125°C

= +25°C

T

J

TJ = -40 to +125°C

= +25°C

T

J

TJ = -40 to +125°C

NOMiNAL

4.5 5.7 6.7 A

4.2 A

V

DROP

I

LIM

-to-V

V

IN

(Note 5)

Current-Limit Level

Dropout Voltage

OUT

V

OUT

= 5.0V,

V

CNTL

= 3A

I

OUT

= +25°C, V

T

J

OUT

V

OUT

V

OUT

TJ = -40 to +125°C

= 2.5V

= 1.8V

= 1.2V

= 80% V

PROTECTIONS

I

SHORT

TSD

Short Current-Limit Level

Thermal Shutdown Temperature

V

< 0.2V

FB

TJ rising

— 1.1 — A

— 170 °C

Thermal Shutdown Hysteresis — 50 — °C

ENABLE AND SOFT-START

EN Logic High Threshold Voltage

V

EN

rising

0.5 0.8 1.1 V

EN Hysteresis 0.1 — V

EN Pull-High Current EN = GND — 5 — uA

TSS

Soft-Start Interval 0.3 0.6 1.2 ms

Turn On Delay

From being enabled to V

rising 10%

OUT

200 350 500 us

POWER-GOOD AND DELAY

V

THPG

Rising PG Threshold Voltage

VFB rising

90 92 95 %

PG Threshold Hysteresis — 8 — %

PG Pull-low Voltage PG sinks 5mA — 0.25 0.4 V

V

< falling PG voltage

PG Debounce Interval

PG Delay Time

Note: 5. Dropout voltage is the voltage difference betw een the inut and the output at which the output voltage drops 2% below its nominal value.

FB

threshold

From V

= V

FB

edge of the V

to rising

THPG

PG

— 10 — µs

1 2 4 ms

AP7175

Document number: DS35606 Rev. 3 - 2

4 of 14

www.diodes.com

AP7175

0.26 0.31

0.42

0.24 0.29

0.40

0.23 0.28

0.38

December 2012

© Diodes Incorporated

P7175

Unit

V

Page 5

A

P7175

Electrical Characteristics (cont.)

(V

= 5V, VIN = 1.8V, V

CNTL

Symbol Parameter Test Conditions

THERMAL CHARACTERISTIC

Notes: 6. Device mounted on 2"*2" FR-4 substrate PC board, 2oz copper, with minimum recommended pad on top layer and thermal vias to bottom layer ground

plane.

7. Device mounted on 2"*2" FR-4 substrate PC board, 2oz copper,with minimum recommended pad layout.

Thermal Resistance Junction-to-Ambient

JA

Thermal Resistance Junction-to-Ambient

JC

= 1.2V and TA = -40 to +85°C, @TA = +25°C, unless otherwise specified.)

OUT

SO-8EP (Note 6) 70

MSOP-8EP (Note 7) 80

SO-8EP (Note 6) 30

MSOP-8EP (Note 7) 30

AP7175

Min Typ Max

Unit

°C/W

°C/W

°C/W

°C/W

Typical Characteristics

NEW PRODUCT

AP7175

Document number: DS35606 Rev. 3 - 2

5 of 14

www.diodes.com

December 2012

© Diodes Incorporated

Page 6

A

Typical Characteristics (cont.)

P7175

NEW PRODUCT

AP7175

Document number: DS35606 Rev. 3 - 2

6 of 14

www.diodes.com

December 2012

© Diodes Incorporated

Page 7

A

C

OU

v

C

OU

OU

OU

OU

OU

P7175

Operating Waveforms (@ V

NEW PRODUCT

C

=10µF, CIN=10µF, RL=0.4

OUT

CH1: V

CNTL

CH2: VIN, 1V/Div, DC

CH3: V

CH4: V

TIME: 2ms/Div

, 1V/Div, DC

OUT

, 5V/Div, DC

POK

Load Transient Response

Power On

, 5V/Div, DC

= 5V, VIN = 1.8V, V

CNTL

V

V

V

V

POK

NTL

= 1.2V, TA = +25°C, unless otherwise specified.)

OUT

Power Off

V

NTL

V

IN

T

C

=10µF, CIN=10µF, RL=0.4

OUT

CH1: V

CH2: VIN, 1V/Div, DC

CH3: V

CH4: V

TIME: 2ms/Di

, 5V/Div, DC

CNTL

, 1V/Div, DC

OUT

, 5V/Div, DC

POK

IN

V

T

V

POK

Over Current Protection

V

T

V

T

I

T

I

T

I

= 10mA to 3A to10mA (rise / fall time =1µs)

OUT

C

= 10µF, C

OUT

CH1: V

CH2: I

TIME: 50µs/Div

, 50mV/Div, AC

OUT

, 1A/Div, DC

OUT

= 10µF

IN

C

= 10µF, C

OUT

CH1: V

CH2: I

TIME: 0.2ms/Div

, 0.5V/Div, DC

OUT

, 2A/Div, DC

OUT

= 10µF, I

IN

= 2A to 5.6A

OUT

AP7175

Document number: DS35606 Rev. 3 - 2

7 of 14

www.diodes.com

December 2012

© Diodes Incorporated

Page 8

A

v

P7175

Operating Waveforms (cont.) (@ V

VEN

C

NEW PRODUCT

= 10µF, C

OUT

CH1: VEN, 5V/Div, DC

CH2: V

OUT

CH3: V

POK

CH4: I

OUT

TIME: 4µs/Div

= 10µF, RL = 0.4

IN

, 1V/Div, DC

, 5V/Div, DC

, 2A/Div, DC

= 5V, VIN = 1.8V, V

CNTL

= 1.2V, TA = +25°C, unless otherwise specified.)

OUT

Enable

VEN

V

OUT

V

POK

I

OUT

V

OUT

I

OUT

C

= 10µF, C

OUT

CH1: VEN, 5V/Div, DC

CH2: V

OUT

CH3: V

POK

CH4: I

OUT

TIME: 1ms/Di

= 10µF, RL = 0.4

IN

, 1V/Div, DC

, 5V/Div, DC

, 2A/Div, DC

V

POK

AP7175

Document number: DS35606 Rev. 3 - 2

8 of 14

www.diodes.com

December 2012

© Diodes Incorporated

Page 9

A

Application Information

Power Good and Delay

AP7175 monitors the feedback voltage VFB on the FB pin. An internal delay timer is started after the PG voltage threshold (V

is reached. At the end of the delay time an internal NMOS of the PG is turned off to indicate that the power at the output is good (PG). This

monitoring function is continued during operation and if V

typical 10µs to avoid oscillating of the PG signal.

falls 8% (typ) below V

FB

, the NMOS of the PG is turned on after a delay time of

THPG

Power On Reset

AP7175 monitors both supply voltages, V

exceed their POR threshold during power on. During operation the POR component continues to monitor the supply voltage and pulls the PG low

to indicate an out of regulation supply. This function will engage without regard to the status of the output.

and VIN to ensure operation as intended. A Soft-Start process is initiated after both voltages

CNTL

Soft-Start

AP7175 incorporates an internal Soft-Start function. The output voltage rise is controlled to limit the current surge during start-up. The typical

Soft-Start time is 0.6ms.

Current-Limit Protection

AP7175 monitors the current flow through the NMOS and limits the maximum current to avoid damage to the load and AP7175 during overload

NEW PRODUCT

conditions.

Short Circuit Current-Limit Protection

AP7175 incorporates a current limit function to reduce the maximum current to 1.1A (typ) when t he voltage at FB falls below 0.2V (t yp) during an

overload or short circuit situation.

During start-up period, this function is disabled to ensure successful heavy load start-up.

Enable Control

If the enable pin (EN) is left open, an internal current source of ~5µA pulls the pin up and enables the AP7175. This will reduce the bill of material

saving an external pull up resistor. Driving the enable pin low disables the device. Driving the pin high subsequently initiates a new Soft-Start

cycle.

Output Voltage Regulation

Output Voltage is set by resistor divider from V

voltage and the NMOS pass element regulates the output voltage while delivering current from V

via FB pin to GND. Internally VFB is compared to a 0.8V temperature compensated reference

OUT

to V

OUT

.

IN

Setting the Output Voltage

A resistor divider connected to FB pin programs the output voltage.

1R

⎛

⎜

VV

REFOUT

⎝

⎞

1*

+=

V

⎟

2R

⎠

THPG

P7175

) on the FB pin

R1 is connected from V

stability, a bypass capacitor can be connected in parallel with R1. (optional in typical application circuit)

to FB with Kelvin sensing connection. R2 is connected from FB to GND. To improve load transient response and

OUT

Power Sequencing

AP7175 requires no specific sequencing between VIN and V

without the presence of V

. Conduction through internal parasitic diode (from V

IN

. However, care should be taken to avoid forcing V

CNTL

to VIN) could damage AP7175.

OUT

for prolonged times

OUT

Thermal Shutdown

The PCB layout and power requirements for AP7175 under normal operation condition should allow enough cooling to restrict the junction

temperature to +125°C. The packages for AP7175 have an exposed PAD to support this. These packages provide better connection to the PCB

and thermal performance. Refer to the layout considerations.

If AP7175 junction temperature reaches +170°C a thermal protection block disables the NMOS pass element and lets the pa rt cool down. After

its junction temperature drops by 50°C (typ), a new Soft-Start cycle will be initiated. A new thermal protection will start, if the load or ambient

conditions continue to raise the junction temperature to +170°C. This cycle will repeat until normal operation temperature is maintained again.

AP7175

Document number: DS35606 Rev. 3 - 2

9 of 14

www.diodes.com

December 2012

© Diodes Incorporated

Page 10

A

Application Information (cont.)

Output Capacitor

An output capacitor (C

capacitance drives the selection. Care needs to be taken to cover the entire operating temperature range.

The output capacitor can be an Ultra-Low-ESR ceramic chip capacitor or a low ESR bulk capacitor like a solid tantalum, POSCap or aluminum

electrolytic capacitor.

is used to improve the output stability and reduces the changes of the output voltage during load transitions. The slew rate of the current

C

OUT

sensed via the FB pin in AP7175 is reduced. If the application has large load variations, it is recommended to utilize low-ESR bulk capacitors.

It is recommended to place ceramic capacitors as close as possible to the load and the ground pin and care should be taken to reduce the

impedance in the layout.

Input Capacitor

To prevent the input voltage from dropping during load steps it is recommended to utilize an input capacitor (CIN). As with the output capacitor

the following are acceptable, Ultra-Low-ESR ceramic chip capacitor or low ESR bulk capacitor like a solid tantalum, POSCap or aluminum

electrolytic capacitor. Typically it is recommended to utilize an capacitance of at least 10µF to avoid output voltage drop due to reduced inpu t

voltage. The value can be lower if V

NEW PRODUCT

Layout Considerations

For good ground loop and stability, the input and output capacitors should be located close to the input, output, and ground pi ns of the device.

No other application circuit is connected within the loop. Avoid using vias within ground loop. If vias must be used, multiple vias should be used

to reduce via inductance.

The regulator ground pin should be connected to the external circuit ground to reduce voltage drop caused by trace i mpedance. Grou nd plane is

generally used to reduce trace impedance.

Wide trace should be used for large current paths from V

Place the R1, R2, and C1(optional) near the LDO as close as possible to avoid noise coupling.

R2 is placed close to device ground. Connect the ground of the R2 to the GND pin by using a dedicated trace.

Connect the pin of the R1 directly to the load for Kelvin sensing.

No high current should flow through the ground trace of feedback loop and affect reference voltage stability.

For the packages with exposed pads, heat sinking is accomplished using the heat spreading capability of the PCB and its copper traces.

Suitable PCB area on the top layer and thermal vias(0.3mm drill size with 1mm spacing, 4~8 vias at least) to the Vin power plane can help to

reduce device temperature greatly.

Reference Layout Plots

) is needed to improve transient response and maintain stability. The ESR (equivalent series resistance) and

OUT

changes are not critical for the application.

IN

to V

IN

, and load circuit.

OUT

Top Layer Bottom Layer

P7175

Vin

Vcntl

GND

Ccntl

Cin

PG

EN

AP7175

Document number: DS35606 Rev. 3 - 2

Cout

FB

1

R2

Vout

Vin

GND

R1

PG

GND

C1

EN

10 of 14

www.diodes.com

December 2012

© Diodes Incorporated

Page 11

A

Ordering Information

P7175

Part Number Package Code Packaging

AP7175SP-13 SP SO-8EP 2500/Tape & Reel -13

AP7175MP-13 MP MSOP-8EP 2500/Tape & Reel -13

NEW PRODUCT

Marking Information

(1) SO-8EP

(2) MSOP-8EP

13” Tape and Reel

Quantity Part Number Suffix

AP7175

Document number: DS35606 Rev. 3 - 2

11 of 14

www.diodes.com

December 2012

© Diodes Incorporated

Page 12

A

Package Outline Dimensions (All dimensions in mm.)

Please see AP02002 at http://www.diodes.com/datasheets/ap02002.pdf for latest version.

(1) SO-8EP

85

E1

Exposed Pad

14

F

NEW PRODUCT

9° (All si de s)

e

D

A1

b

4° ± 3°

A

7

°

Bottom View

N

E

45

°

E0

Q

L

(2) MSOP-8EP

D

x

E

y

1

A

e

A1

D

AP7175

Document number: DS35606 Rev. 3 - 2

8Xb

A2

E2

A3

D1

E3

E1

Gauge Plane

Seating Plane

See Detail C

www.diodes.com

0.25

4

X

1

c

0

°

Detail C

12 of 14

H

C

Gauge Plane

Seating Plane

4

X

P7175

SO-8EP (SOP-8L-EP)

Dim Min Max Typ

A 1.40 1.50 1.45

A1 0.00 0.13 -

b 0.30 0.50 0.40

C 0.15 0.25 0.20

D 4.85 4.95 4.90

E 3.80 3.90 3.85

E0 3.85 3.95 3.90

E1 5.90 6.10 6.00

e - - 1.27

F 2.75 3.35 3.05

H 2.11 2.71 2.41

L 0.62 0.82 0.72

N - - 0.35

Q 0.60 0.70 0.65

All Dimensions in mm

MSOP-8EP

Dim Min Max Typ

A - 1.10 -

A1 0.05 0.15 0.10

1

0

°

a

L

A2 0.75 0.95 0.86

A3 0.29 0.49 0.39

b 0.22 0.38 0.30

c 0.08 0.23 0.15

D 2.90 3.10 3.00

D1 1.60 2.00 1.80

E 4.70 5.10 4.90

E1 2.90 3.10 3.00

E2 1.30 1.70 1.50

E3 2.85 3.05 2.95

e - - 0.65

L 0.40 0.80 0.60

a 0° 8° 4°

x - - 0.750

y - - 0.750

All Dimensions in mm

December 2012

© Diodes Incorporated

Page 13

A

Suggested Pad Layout

Please see AP02001 at http://www.diodes.com/datasheets/ap02001.pdf for the latest version.

(1) SO-8EP

X2

NEW PRODUCT

(2) MSOP-8EP

AP7175

Document number: DS35606 Rev. 3 - 2

Y2

X C

G

Y2

X1

Y1

X1

Y

C

X

Y

Y1

13 of 14

www.diodes.com

Dimensions

C 1.270

X 0.802

X1 3.502

X2 4.612

Y 1.505

Y1 2.613

Y2 6.500

Dimensions

C 0.650

G 0.450

X 0.450

X1 2.000

Y 1.350

Y1 1.700

Y2 5.300

Value

(in mm)

Value

(in mm)

P7175

December 2012

© Diodes Incorporated

Page 14

A

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT,

INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE

(AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes

without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the

application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or

trademark rights, nor the rights of others. Any Customer or user of this document o r products described herein in such applica tions shall assume

all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated

website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorize d application, Customers shall indemnify and

hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or

indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings

NEW PRODUCT

noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Onl y the English version of this document is the

final and determinative format released by Diodes Incorporated.

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express

written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

labeling can be reasonably expected to result in significant injury to the user.

B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the

failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and

acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any

use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related

information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its

representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2012, Diodes Incorporated

www.diodes.com

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the

IMPORTANT NOTICE

LIFE SUPPORT

P7175

AP7175

Document number: DS35606 Rev. 3 - 2

14 of 14

www.diodes.com

December 2012

© Diodes Incorporated

Loading...

Loading...