AP2142A/ AP2152A

0.5A DUAL CHANNEL CURRENT-LIMITED

POWER SWITCH WITH OUTPUT DISCHARGE

Description

The AP2142A and AP2152A are dual channel current-limited

integrated high-side power switches optimized for Universal Serial

Bus (USB) and other hot-swap applications. The family of devices

complies with USB standards and available with both polarities of

enable input.

The devices have fast short-circuit response time for improved overall

system robustness, and have integrated output discharge function to

ensure completely controlled discharging of the output voltage

capacitor. They provide a complete protection solution for application

subject to heavy capacitive loads and the prospect of short circuit,

and offer reverse current blocking, over-current, over-temperature

and short-circuit protection, as well as controlled rise time and undervoltage lockout functionality. A 7ms deglitch capability on the opendrain flag output prevents false over-current reporting and does not

require any external components.

All devices are available in SO-8, MSOP-8EP and U-DFN3030-8

packages.

Features

Dual Channel Current-Limited Power Switch with Output

Discharge

Fast Short-Circuit Response Time: 2µs

0.7A Accurate Current Limiting

Reverse Current Blocking

85m On-Resistance

Input Voltage Range: 2.7V – 5.5V

Built-In Soft-Start with 0.6ms Typical Rise Time

Short Circuit and Thermal Protection

Fault Report (FLG) with Blanking Time (7ms typ)

ESD protection: 2kV HBM, 300V MM

Active High (AP2152A) or Active Low (AP2142A) Enable

Ambient Temperature Range: -40°C to +85°C

SO-8, MSOP-8EP and DFN3030E-8 (Exposed Pad): Available

in “Green” Molding Compound (No Br, Sb)

Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

Halogen and Antimony Free. “Green” Device (Note 3)

UL Recognized, File Number E322375

IEC60950-1 CB Scheme Certified

Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

2. See http://www.diodes.com/quality/lead_free.html for more information about Diodes Incorporated’s definitions of Halogen- and Antimony-free, "Green"

and Lead-free.

3. Halogen- and Antimony-free "Green” products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and

<1000ppm antimony compounds.

AP2142A/ AP2152A

Document number: DS32191 Rev. 3 - 2

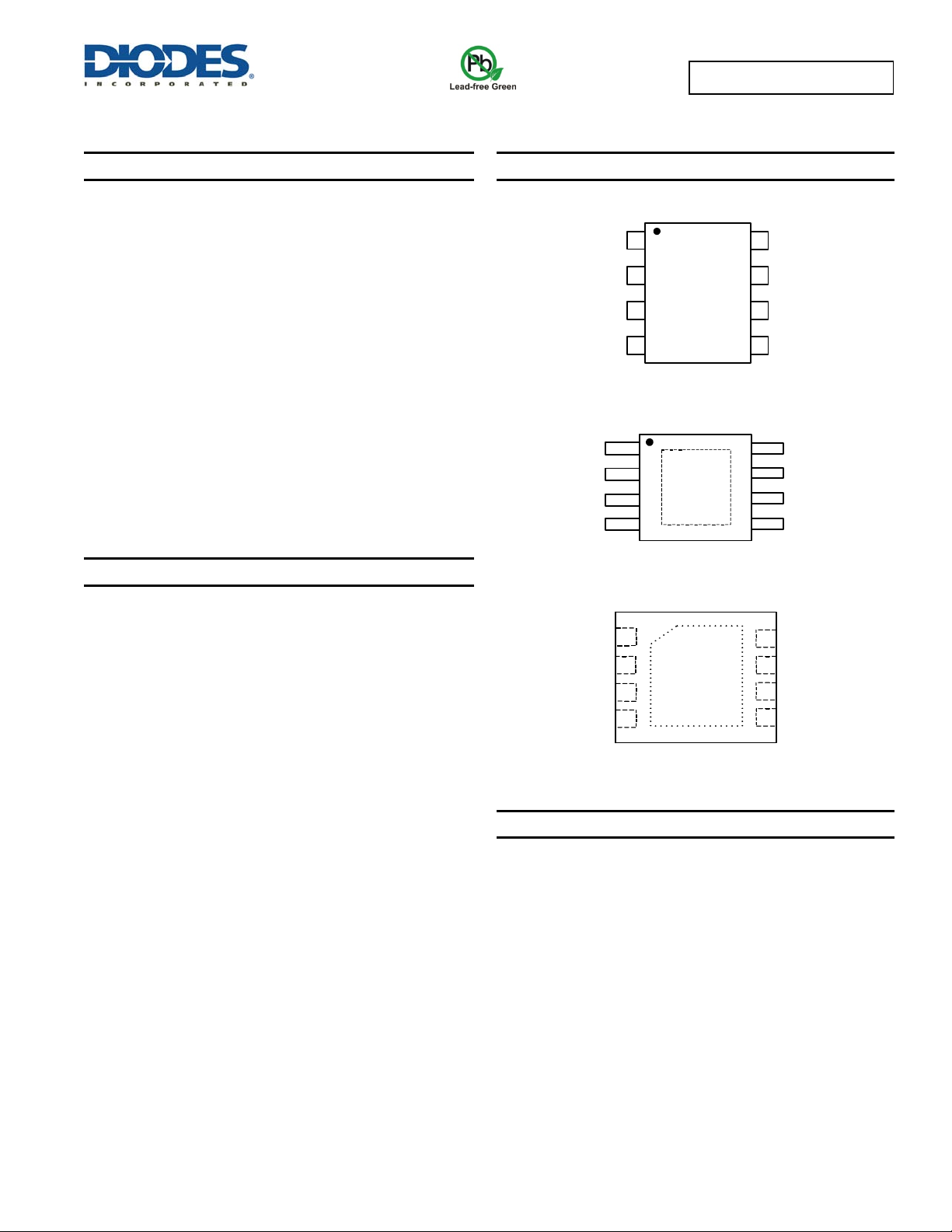

Pin Assignments

Applications

LCD TVs & Monitors

Set-Top-Boxes, Residential Gateways

Laptops, Desktops, Servers,

Printers, Docking Stations, HUBs

1 of 16

www.diodes.com

GND

IN

EN1

EN2

GND

EN1

EN2

GND

IN

EN1

EN2

IN

1

2

3

4

1

2

3

4

1

2

3

4

( Top View )

SO-8

( Top View )

MSOP-8EP

( Top View )

U-DFN3030-8

8

7

6

5

OUT1

OUT2

FLG2

8

7

6

5

8

7

6

5

FLG1

FLG1

OUT1

OUT2

FLG1

OUT1

OUT2

FLG2

FLG2

March 2013

© Diodes Incorporated

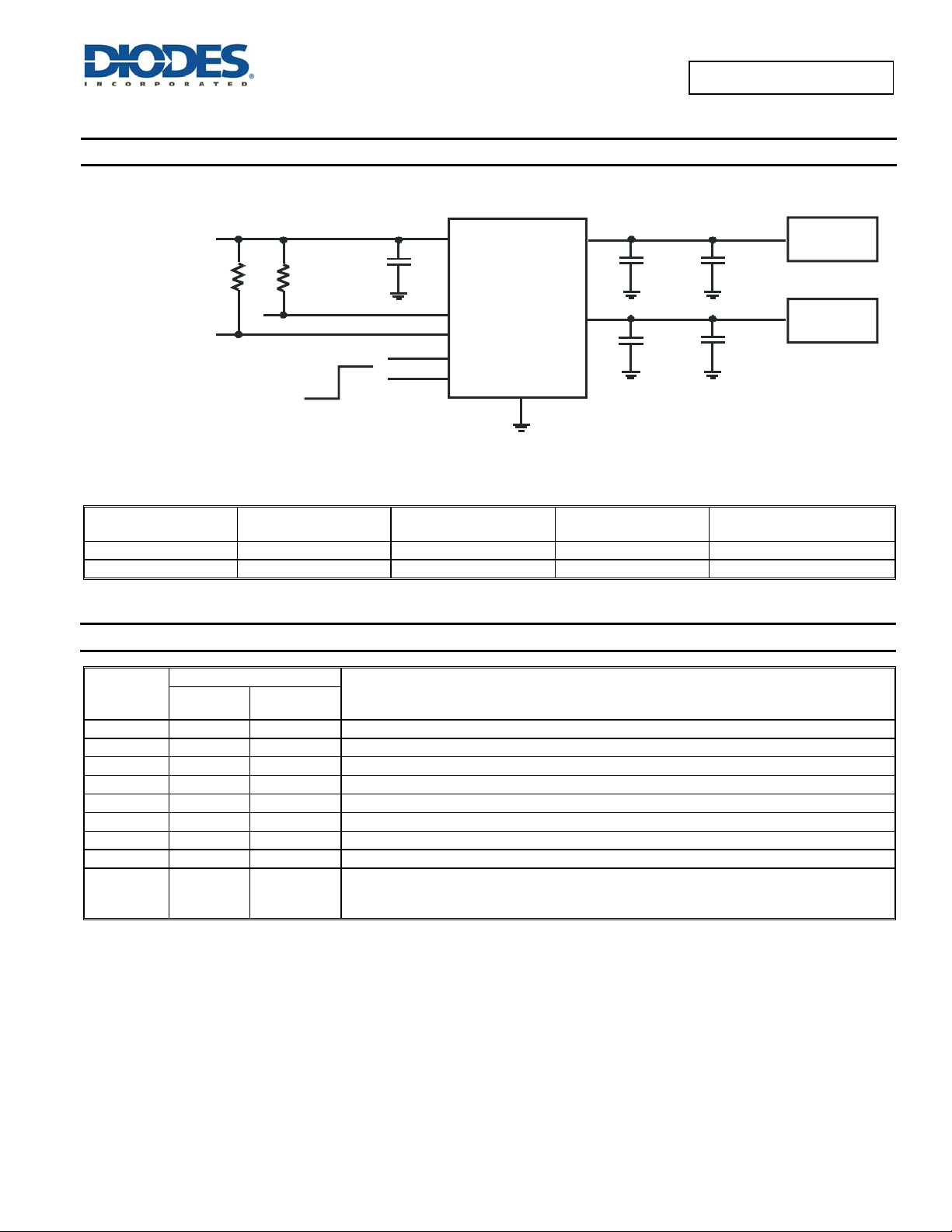

Typical Applications Circuit

AP2152 A Enabl e Active Hi gh

AP2142A/ AP2152A

Power Supply

2.7V to 5.5V

10 k

10 k

ON

OFF

1uF

IN

FLG 1

FLG 2

EN1

EN2

GND

OUT 1

OUT 2

1uF

1uF

4.7uF*

4.7uF*

Note: * USB 2.0 r equire s 120uF per hub

Available Options

Part Number Channel

AP2142A 2 Active Low 0.7A 0.5A

AP2152A 2 Active High 0.7A 0.5A

Enable Pin

(EN)

Current Limit

(typ)

Recommended Maximum

Continuous Load Current

Pin Descriptions

Pin Number

Pin Name

GND 1 1 Ground

IN

EN1 3 3 Switch 1 enable input, active low (AP2142A) or a ctive high (AP2152 A)

EN2 4 4 Switch 2 enable input, active low (AP2142A) or a ctive high (AP2152 A)

FLG2 5 5 Switch 2 over-current and over-temperature fault re port; open-dra in flag is act ive low w hen triggered

OUT2

OUT1

FLG1 8 8 Switch 1 over-current and over-temperature fault re port; open-dra in flag is act ive low w hen triggered

Exposed Pad - Exposed Pad

SO-8

2 2 Voltage input pin

6 6 Switch 2 voltage output pin

7 7 Switch 1 voltage output pin

AP2142A/ AP2152A

Document number: DS32191 Rev. 3 - 2

MSOP-8EP

U-DFN3030-8

Exposed Pad:

It should be connected to GND and thermal mass for enhanced thermal impedance.

It should not be used as electrical ground conduction path.

2 of 16

www.diodes.com

Function

Load

Load

March 2013

© Diodes Incorporated

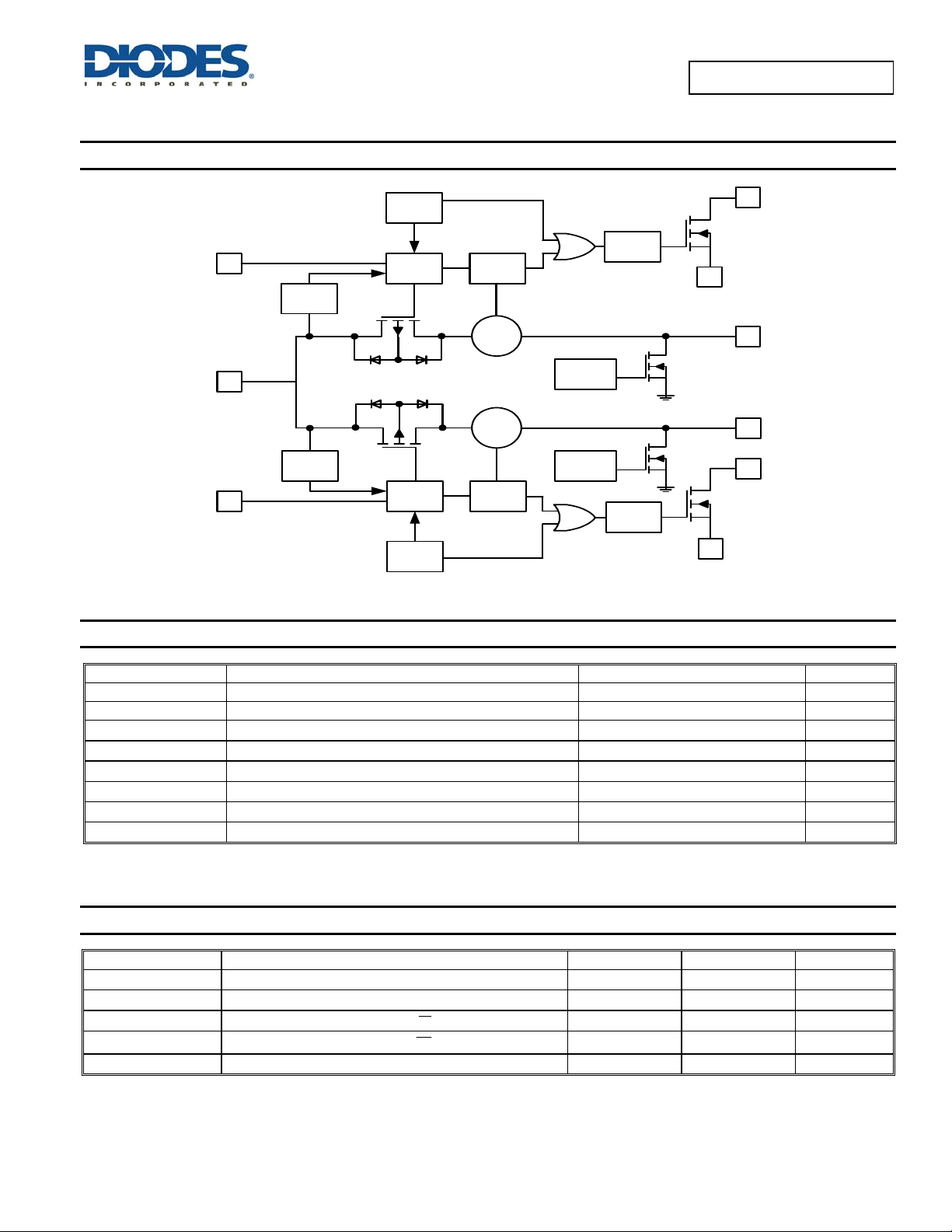

Functional Block Diagram

AP2142A , AP2152A

EN1

UVLO

Thermal

Sense

Driver

Current

Limit

AP2142A/ AP2152A

FLG1

Deglitch

GND

Current

Sense

Discharge

Control

Discharge

Control

Deglitch

GND

EN2

IN

Current

Sense

UVLO

Driver

Thermal

Sense

Current

Limit

Absolute Maximum Ratings (@T

= +25°C, unless otherwise specified.)

A

Symbol Parameter Ratings Unit

ESD HBM Human Body Model ESD Protection 2 kV

ESD MM Machine Model ESD Protection 300 V

VIN

V

OUT

V

EN , VFLG

T

I

LOAD

J(MAX)

TST

Note: 4. UL Recognized Rating from -30°C to +70°C (Diodes qualified TST from -65°C to +150°C)

Input Voltage 6.5 V

Output Voltage

VIN +0.3

Enable Voltage 6.5 V

Maximum Continuous Load Current Internal Limited A

Maximum Junction Temperature 150 °C

Storage Temperature Range (Note 4) -65 to +150 °C

Recommended Operating Conditions (@T

= +25°C, unless otherwise specified.)

A

Symbol Parameter Min Max Unit

VIN

I

OUT

VIH

VIL

TA

Input Voltage 2.7 5.5 V

Output Current 0 500 mA

High-Level Input Voltage on EN or

Low-Level Input Voltage on EN or

EN

EN

2

0 0.8 V

V

IN

Operating Ambient Temperature Range -40 +85 °C

AP2142A/ AP2152A

Document number: DS32191 Rev. 3 - 2

3 of 16

www.diodes.com

OUT1

OUT2

FLG2

© Diodes Incorporated

V

V

March 2013

AP2142A/ AP2152A

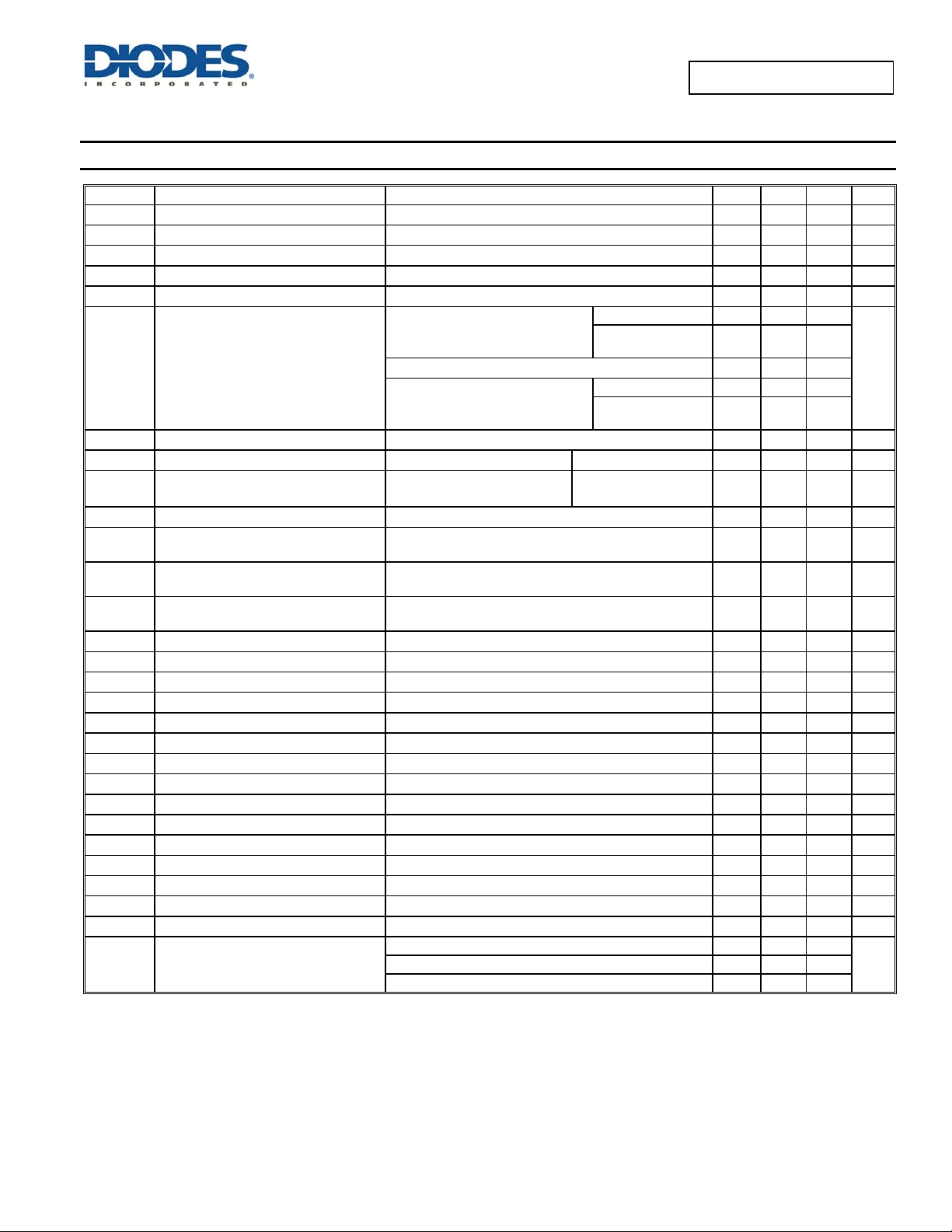

Electrical Characteristics (@T

= +25°C, VIN = +5.0V, unless otherwise specified.)

A

Symbol Parameter Test Conditions (Note 5) Min Typ Max Unit

Input UVLO 1.6 2.0 2.4 V

UVLO

Input Shutdown Current

Input Quiescent Current, Dual

I

Q

Disabled, I

Enabled, I

OUT

OUT

= 0

= 0

0.1 1 µA

115 180 µA

Input Leakage Current Disabled, OUT grounded 1 µA

Reverse Leakage Current

REV

Switch On-Resistance

Over-Load Current Limit

Ganged Over-Load Current Limit

Current Limiting Trigger Threshold

Trig

Ganged Current Limiting Trigger

Threshold

Short-Circuit Current per Channel

IOS

Ganged Short-Circuit Current

Short-Circuit Response Time

EN Input Logic Low Voltage

V

IL

EN Input Logic High Voltage

V

IH

EN Input Leakage

Output Leakage Current

Output Turn-On Rise Time

TR

Output Turn-Off Fall Time

TF

Output Turn-On Delay Time

Output Turn-Off Delay Time

FLG Output FET On-Resistance

FLG

FLG Off Current

FOH

FLG Blanking Time

Blank

Discharge Resistance (Note 6)

DIS

Thermal Shutdown Threshold

Thermal Shutdown Hysteresis 25

HYS

Disabled, VIN = 0V, V

V

= 5V, I

IN

= +25°C

T

A

VIN = 5V, I

VIN = 3.3V, I

= +25°C

T

A

= 3.3V, I

V

IN

VIN = 5V, V

= 5V, V

V

IN

= 0.5A,

OUT

= 0.5A, -40°C TA +85°C

OUT

= 0.5A,

OUT

= 0.5A, -40°C TA +85°C

OUT

= 4V, CL = 4.7µF -40°C TA +85°C

OUT

= 4V, OUT1 &

OUT

OUT2 tied together, C

= 5V, I

OUT

= 4.7µF

L

at VIN

REV

SO-8 90 110

MSOP-8EP,

U-DFN3030-8

SO-8 110 130

MSOP-8EP,

U-DFN3030-8

-40°C T

+85°C

A

Output Current Slew rate (<100A/s), CL = 4.7µF

OUT1 & OUT2 tied together, Output Current Slew rate

(<100A/s), C

= 4.7µF

L

OUTx connected to ground, device enabled into short

circuit, C

= 4.7µF

L

OUT1 & OUT2 connected to ground, device enabled into

short-circuit, C

V

= 0V to I

OUT

= 2.7V to 5.5V

V

IN

V

= 2.7V to 5.5V

IN

= 0V to 5.5V

V

EN

Disabled, V

CL = 1µF, R

CL = 1µF, R

CL = 100µF, R

CL = 100µF, R

I

= 10mA

FLG

= 5V

V

FLG

OUT

LOAD

LOAD

= 4.7µF

L

= I

OUT

= 0V

= 10

= 10

LOAD

LOAD

(output shorted to ground)

LIMIT

= 10

= 10

CL =4.7µF

V

= 5V, disabled, I

IN

Enabled, R

LOAD

=1k

OUT

=1mA

0.01 0.1 µA

85 105

135

105 125

170

0.55 0.7 0.85 A

1.1 1.4 1.7 A

1.0 A

1.0 A

0.7 A

1.1 1.4 1.7 A

2 µs

0.8 V

2 V

1 µA

0.5 1 µA

0.6 1.5 ms

0.05 0.3 ms

0.2 0.5 ms

0.1 0.3 ms

20 40

0.01 1 µA

4 7 15 ms

100

140

V

I

SHDN

I

LEAK

I

R

DS(ON)

I

LIMIT

I

LIMIT_G

I

I

Trig_G

I

OS_G

T

SHORT

I

SINK

I

LEAK-O

T

D(ON)

T

D(OFF)

R

I

T

R

T

SHDN

T

SO-8 (Note 7) 115

Thermal Resistance Junction-to-Ambient

JA

MSOP-8EP (Note 8) 75

°C/W

U-DFN3030-8 (Note 8) 60

Notes: 5. Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately.

6. The discharge function is active when the device is disabled (when enable is de-asserted or during power-up / power-down when V

discharge function offers a resistive discharge path for the external storage capacitor for limited time.

7. Test condition for SO-8: Device mounted on FR-4 substrate PCB with minimum recommended pad layout.

8. Test condition for MSOP-8EP and U-DFN3030-8: Device mounted on 2” x 2” FR-4 substrate PCB, 2oz copper, with minimum recommended pad on top

layer and thermal vias to bottom layer ground plane.

< V

). The

IN

UVLO

AP2142A/ AP2152A

Document number: DS32191 Rev. 3 - 2

4 of 16

www.diodes.com

March 2013

© Diodes Incorporated

m

C

C

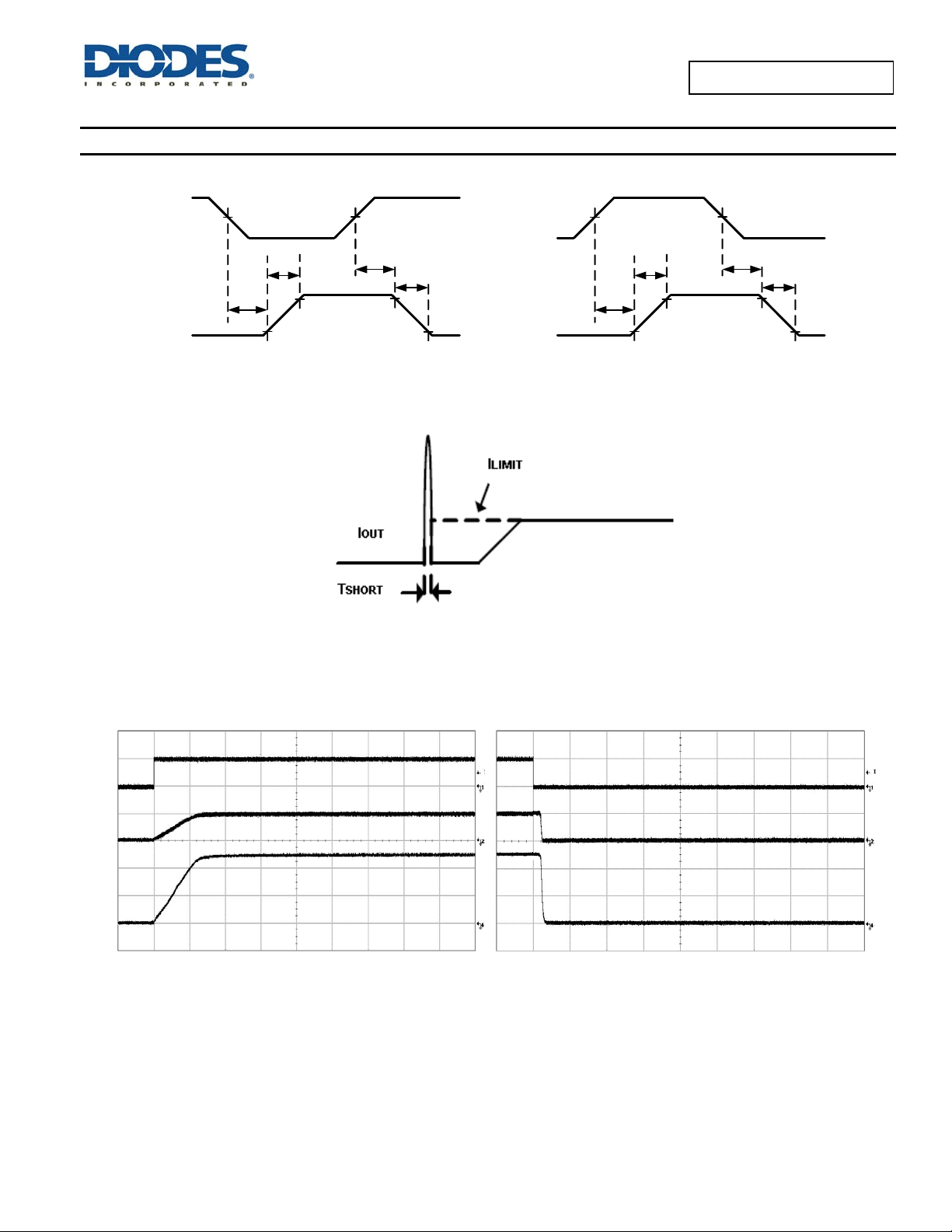

Typical Performance Characteristics

AP2142A/ AP2152A

V

EN

V

OUT

50%

T

D(ON)

T

10%

50%

T

R

90%

D(OFF)

90%

10%

T

F

V

EN

50%

T

T

D(ON)

V

OUT

10%

50%

T

R

90%

D(OFF)

90%

10%

T

F

Figure 1 Voltage Waveforms: AP2142A (left), AP2152A (right)

Figure 2 Response Time to Short Circuit Waveform

All Enable Plots are for AP2152A Active High

Turn-On Delay and Rise Time

Turn-Off Delay and Fall Time

EN

5V/div

Iin

500mA/div

Vout

2V/div

AP2142A/ AP2152A

Document number: DS32191 Rev. 3 - 2

500µs/div

CL=1µF

TA= +25°C

RL=10

5 of 16

www.diodes.com

EN

5V/div

Iin

500mA/div

Vout

2V/div

500µs/div

CL=1µF

TA= +25°C

R

=10

L

March 2013

© Diodes Incorporated

Loading...

Loading...