Page 1

SERVICE MANUAL

For Europe model

Ver. 1

MODEL

AV SURROUND RECEIVER

AVR-1306

注 意

サービスをおこなう前に、このサービスマニュアルを

必ずお読みください。本機は、火災、感電、けがなど

に対する安全性を確保するために、さまざまな配慮を

おこなっており、また法的には「電気用品安全法」に

もとづき、所定の許可を得て製造されております。

従ってサービスをおこなう際は、これらの安全性が維

持されるよう、このサービスマニュアルに記載されて

いる注意事項を必ずお守りください。

●

For purposes of improvement, specifications and

design are subject to change without notice.

●

Please use this service manual with referring to the

operating instructions without fail.

●

Some illustrations using in this service manual are

slightly different from the actual set.

Denon Brand Company, D&M Holdings Inc.

●

●

●

●

TOKYO, JAPAN

本機の仕様は性能改良のため、予告なく変更すること

があります。

補修用性能部品の保有期間は、製造打切後8年です。

修理の際は、必ず取扱説明書を参照の上、作業を行っ

てください。

本文中に使用しているイラストは、説明の都合上現物

と多少異なる場合があります。

X0260V.01 DE/CDM 0509

Page 2

AVR-1306

SAFETY PRECAUTIONS

The following check should be performed for the continued protection of the customer and service technician.

LEAKAGE CURRENT CHECK

Before returning the unit to the customer, make sure you make either (1) a leakage current check or (2) a line to chassis

resistance check. If the leakage current exceeds 0.5 milliamps, or if the resistance from chassis to either side of the

power cord is less than 460 kohms, the unit is defective.

500V

1M

(1)

(2)

(1)

(2)

2

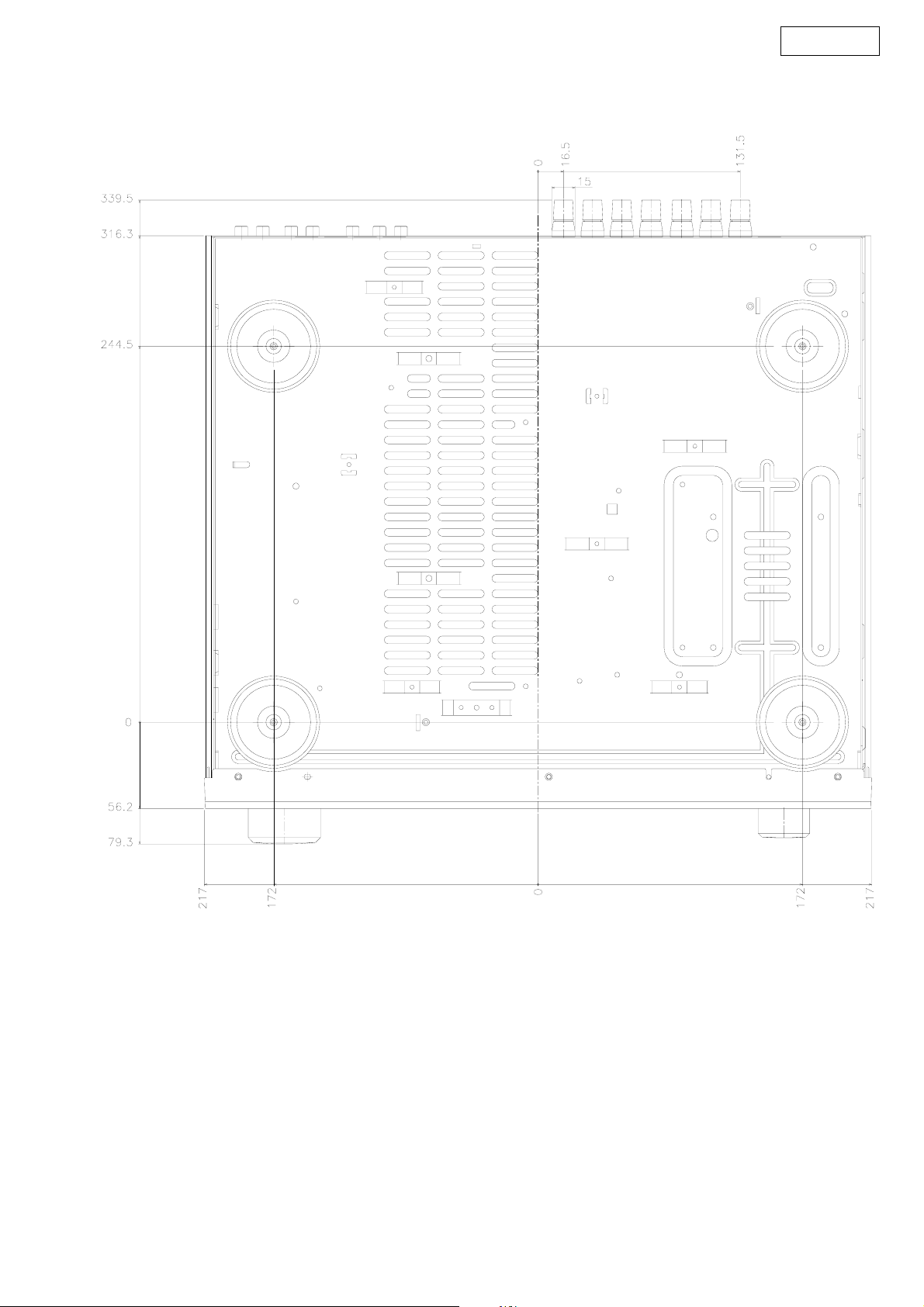

Page 3

DIMENSION

AVR-1306

3

Page 4

AVR-1306

CAUTION IN SERVICING

Initializing AV SURROUND RECEIVER

AV SURROUND RECEIVER initialization should be performed

when the µcom, peripheral parts of µcom, and Digital P.W.B. are

replaced.

1. Switch off the unit.

2. Hold the following SPEAKERS-A button and SPEAKERS-B

button, and switch on the unit.

3. Check that the entire display is flashing with an interval of

about 1 second, and release your fingers from the 2 buttons

and the microprocessor will be initialized.

Note:・If step 3 does not work, start over from step 1.

・ All user settings will be lost and this factory setting will

be recovered when this initialization mode.

So make sure to memorize your setting for restoring

after the initialization.

サービス時の注意事項

AVサラウンドアンプの初期化について

マイコンやマイコン周辺部品、Digital 基板等を交換した場合

は、AV サラウンドアンプの初期化を行って下さい。

1. オン/オフボタンを OFF にします。

2. SPEAKERS-A ボタンと SPEAKERS-B ボタンを同時に押しな

がら、オン/オフボタンを押して ON にします。

3. ディスプレイ表示が約 1秒間隔で点滅するのを確認後、2

つのボタンから指を離します。

*マイコンが初期化されます。

注意 :・上記 3 の状態にならない場合は、もう一度操作 1 か

らやり直してください。

・初期化を行うとお客様が設定した内容が工場出荷状

態に戻りますので、あらかじめ設定内容を控えてお

き初期化後再設定してください。

4

Page 5

AVR-1306

ADJUSTMENT

Audio Section

Idling Current

Required measurement equipment: DC Voltmeter

1. Preparation

(1) Avoid direct blow from an air conditioner or an electric

fan, and adjust the unit at normal room temperature 15 °C

~ 30 °C (59 °F ~ 86 °F).

(2) Presetting

• POWER (Power source switch) OFF

• SPEAKER (Speaker terminal) No load

(Do not connect speaker, dummy resistor, etc.)

2. Adjustment

(1) Remove top cover and set VR101, VR102, VR103,

VR104, VR105, on Amp. unit, Unit at fully counterclockwise ( ) position.

(2) Connect DC Voltmeter to test points (FRONT-Lch:

TP104, FRONT-Rch: TP105, CENTER ch: TP103, SURROUND-Lch: TP101, SURROUND-Rch: TP102).

(3) Connect power cord to AC Line, and turn power switch

"ON".

(4) Presetting.

MASTER VOLUME : "---" counterclockwise ( min.)

MODE : 5CH STEREO

FUNCTION : CD

(5) Within 2 minutes after the power on, turn VR101 clock-

wise ( ) to adjust the TEST POINT voltage to 1.5 mV

± 0.5 mV DC.

(6) After 10 minutes from the preset above, turn VR101 to

set the voltage to 2.5 mV ± 0.5 mV DC.

(7) Adjust the Variable Resistors of other channels in the

same way.

調整

オーディオセクション

アイドリング電流の調整

調整に必要な測定器 : DCVoltmeter

1. 準備

(1) セットをクーラ、扇風機のそばなど風通しの良い場所

を避け、通常の使用状態に置きます。セットの周囲温

度は 15〜30 ℃、湿度は常湿とします。

(2) プリセット

・電源スイッチ OFF

・スピーカ端子 無負荷

( スピーカ・ダミー抵抗器などを接続しない。)

2. 調整

(1) 上カバーをはずし、パワーアンプ基板の VR101,VR102,

VR103,VR104,VR105 を反時計方向 ( )に回し切った

状態にセットします。

(2) テストポイント (FRONT-Lch:TP104,FRONT-Rch:

TP105,CENTERch:TP103,SURROUND-Lch:TP101,

SURROUND-Rch:TP102) に DCVoltmeterを接続します。

(3) 電源コードを AC100V(95〜105Vの範囲でも可)に接

続し、電源スイッチを "ON"にします。

(4) ON後、次のようにセットします。

・MASTERVOLUME(音量調節つまみ)→反時計方向

( )に回す、最小の状態にする。

・SPEAKER(スピーカ端子)→無負荷(スピーカ、

ダミー抵抗器などを接続しない。)

MODE:5CHSTEREO

FUNCTION:CD

(5) 2分以内に VR101を時計方向 ( ) に回しテストポイ

ントの電圧を次のように調整します。

1.5mV ±0.5mVDC

(6) 予備調整から 10分後 VR101を回し、次のように電圧を

設定します。

2.5mV± 0.5mVDC

(7) 同じ方法で各チャネルの可変抵抗を調整します。

DC Voltmeter

F Lch

S Lch

C ch

S Rch

F Rch

VR104

TP104

VR101

TP101

VR103,TP103

VR102,TP102

VR105

TP105

5

Page 6

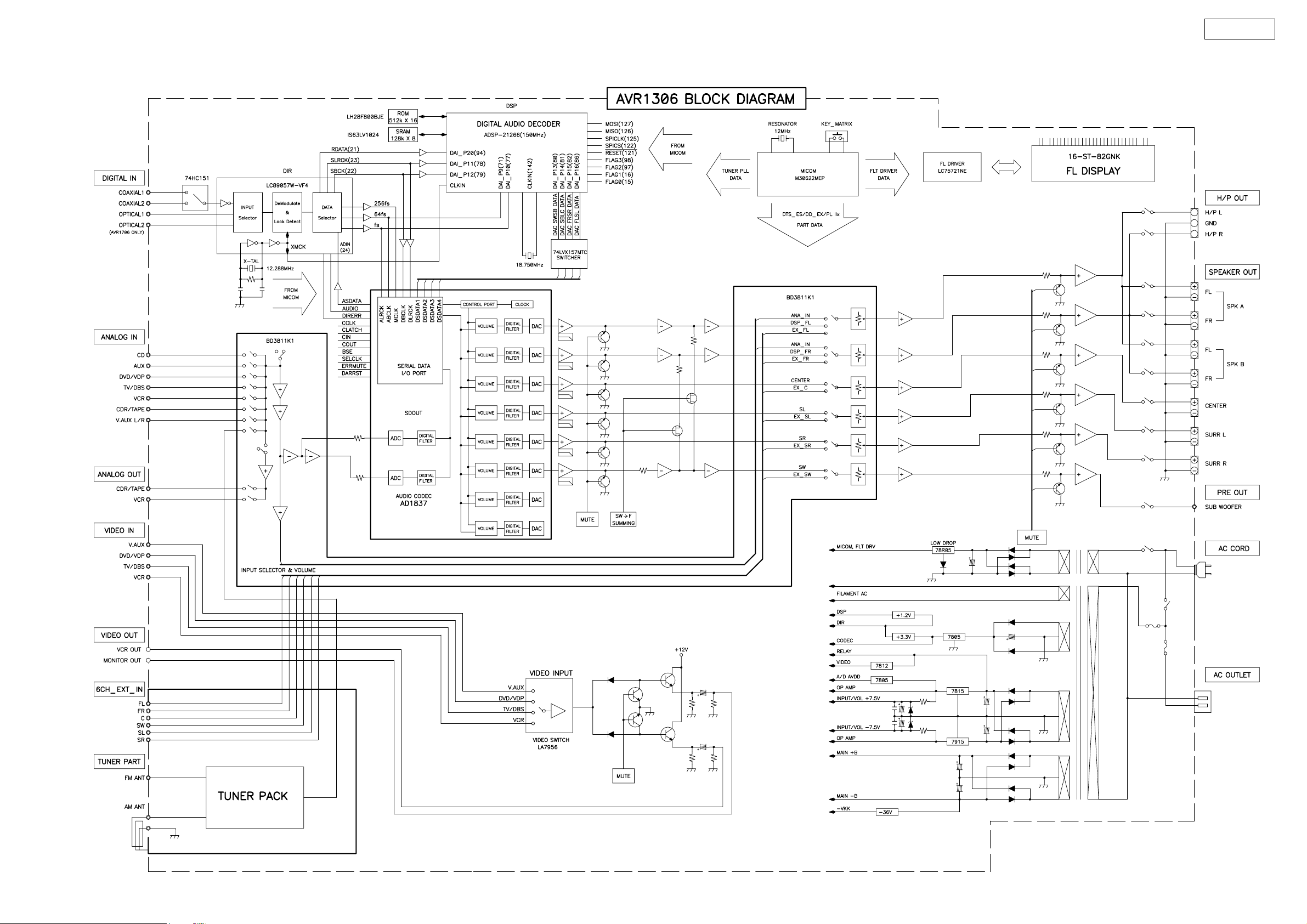

BLOCK DIAGRAM

AVR-1306

6

Page 7

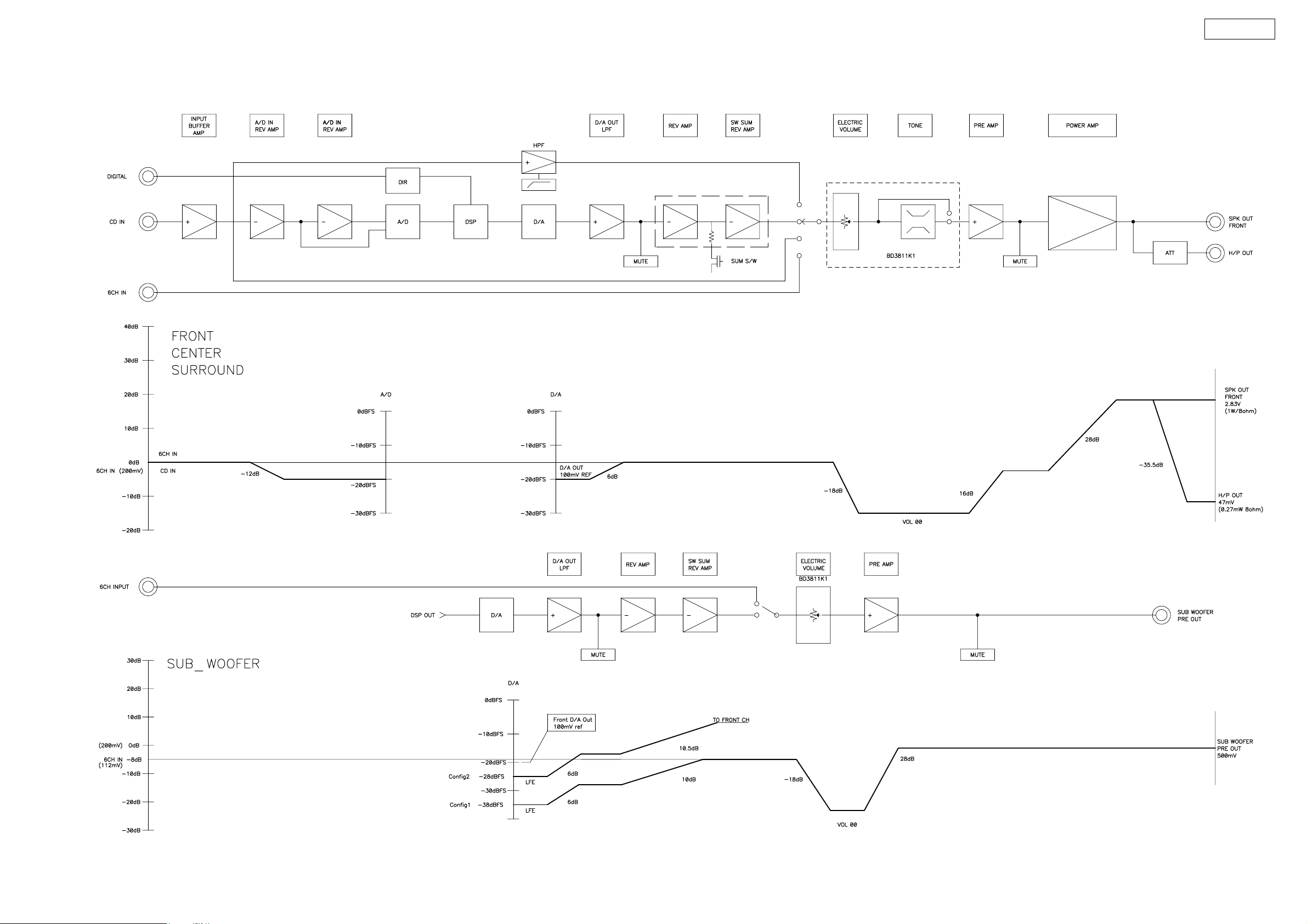

LEVEL DIAGRAM

AVR-1306

7

Page 8

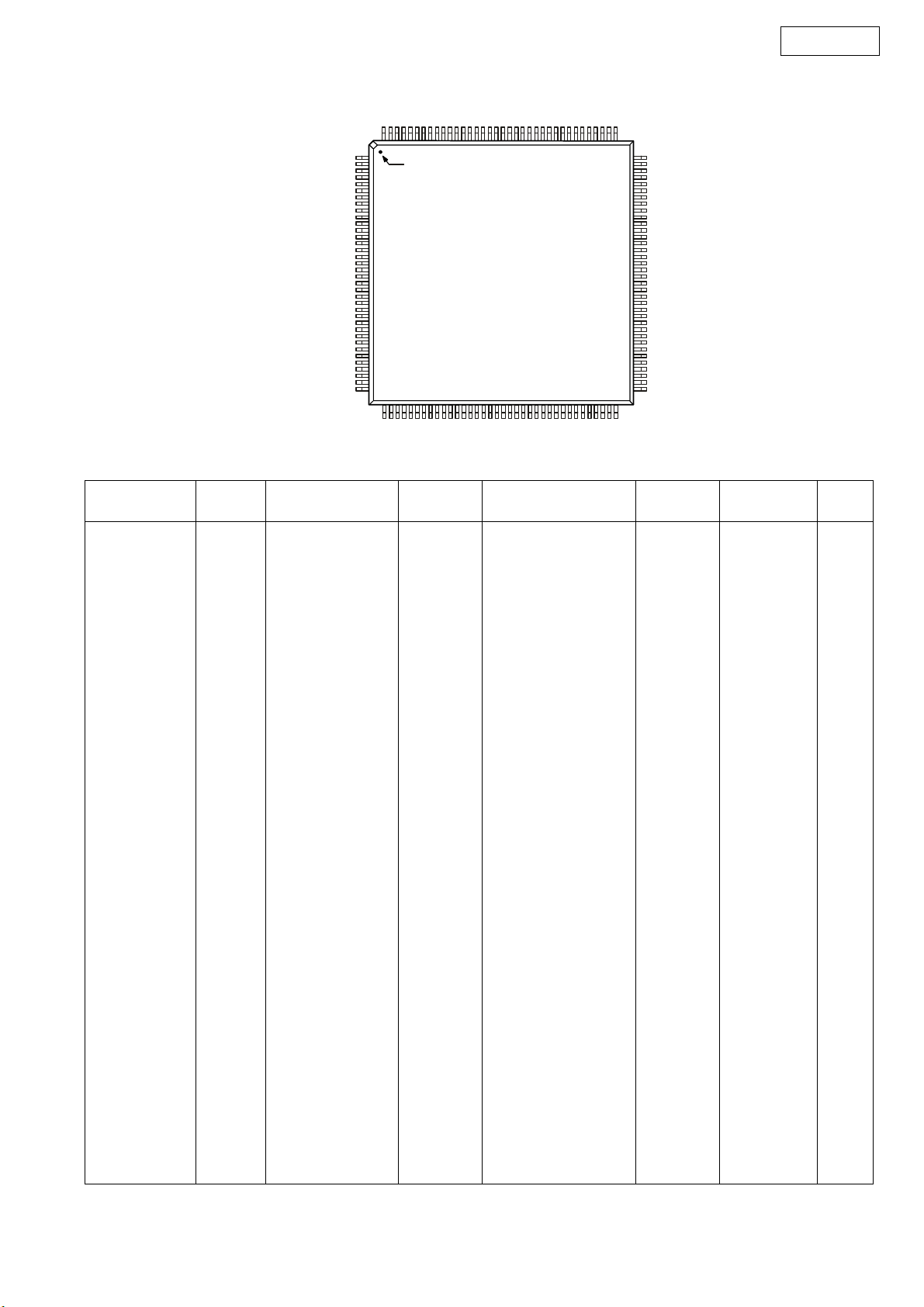

SEMICONDUCTORS

Only major semiconductors are shown, general semiconductors etc. are omitted to list.

主な半導体を記載しています。汎用の半導体は記載を省略しています。

1. IC’s

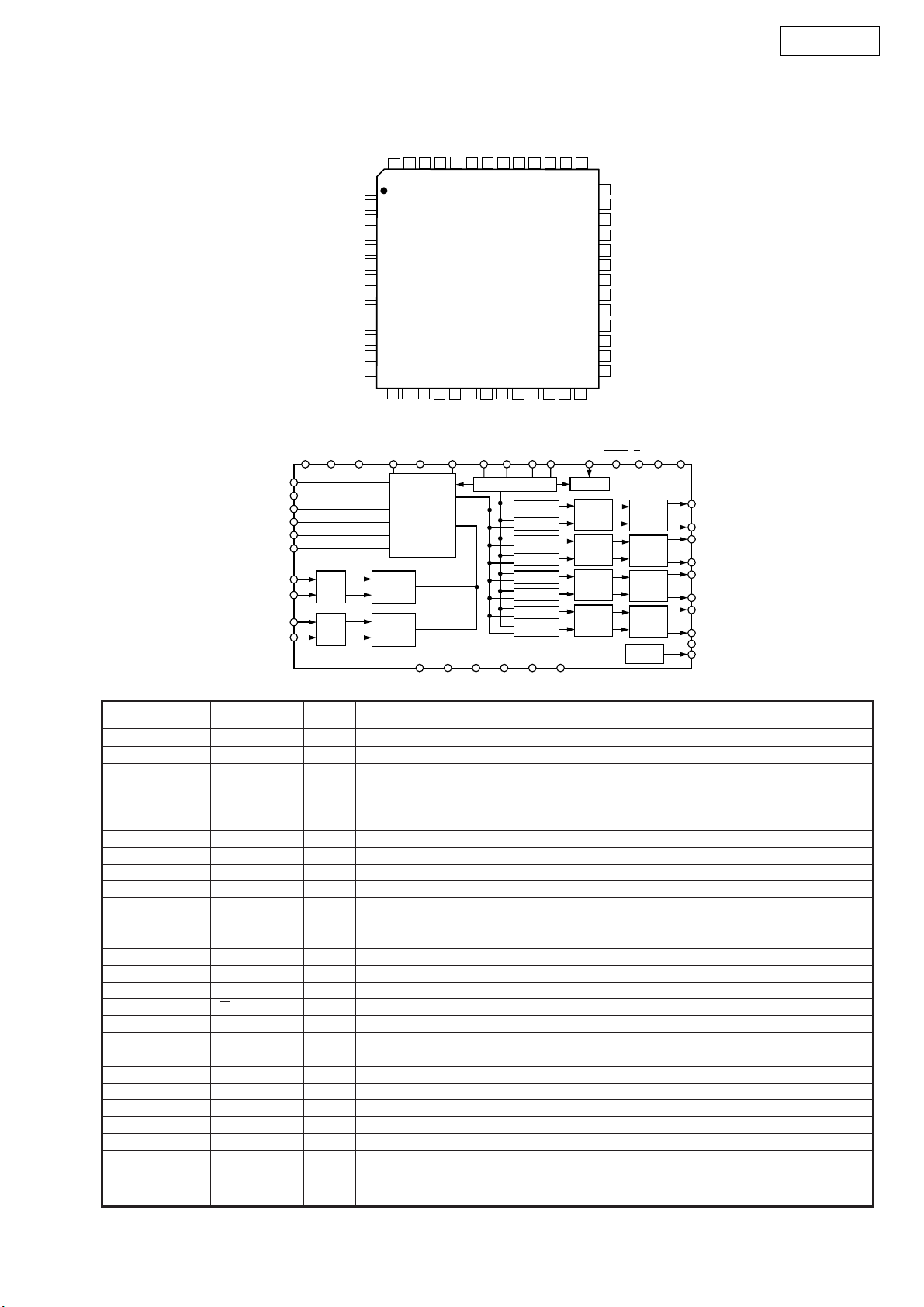

M30622MEP (IC201)

DDVSS

PK1/TX

PK2/TEX

PI1/RMC

PI2/NMI

PI3/TO0/ADJ

PI4/INT1/CS1

PC6

PC7

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7NCV

PI5/SCK1

AVR-1306

PC5

PC4

PC3

PC2

PC1

PC0

PB7/SI2

PB6/SO2

PB5/SCK2

PB4/TO2

PB3

PB2

PB1

PB0

PJ7

PJ6

PJ5

PJ4

PJ3

PJ2

PJ1

PJ0

PD7

PD6

PD5

PD4

PD3

PD2

PD1

PD0

999897969594939291

100

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32333435363738394041424344454647484950

PH7

PH6

PH5

PH4

PH3

PH2

908988878685848382

TOP VIEW

SS

V

PH1

PH0

RST

XTAL

PK7/TO1

EXTAL

PK5/SI0

PK6/CS0

PK4/SO0

PF7/AN11

PK3/SCK0

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

PF5/AN9

PF6/AN10

PI6/SO1

PI7/SI1

PE0/INT0

PE1/INT2

PE2/PWM0

PE3/PWM1

PE4

PE5

PE6

PE7

PG0/TxD

PG1/RxD

PG2/EC0

PG3/EC1

PG4/EC2

PG5/INT3

PG6/INT4

PG7/CINT

AN0

AN1

AN2

AN3

PF0/AN4

PF1/AN5

PF2/AN6

PF3/AN7

AV

DD

AV

REF

AV

SS

PF4/AN8

M30622MEP Terminal Function

PIN

No.

1 SW_SUM O SW SUMMING CONTROL

2 4094_CLK O BU4094(IC551~2) CLOCK

3 2090_CLK(VIDEO)/SEL2/G O LA7956(IC601) S2 CONTROL

4 2090_DATA/SEL1/F O LA7956(IC601) S1 CONTROL

5 2090_DATA2/VIDEO_MUTE O VIDEO MUTE CONTROL

6 RMC I REMOCON SIGNAL DATA INPUT

7 1837_SDIN I AD1837(IC808) COUT SERIAL DATA INPUT

8 BYTE GND GND

9 CNVSS - UP GRADE PIN (TP301 CNVSS)

10 2090_DATA/4094_DATA O BU2090(IC302) DATA/BU4094(IC551~2) DATA

11 FLD_RST/4094_EN O LC75721(IC301) RESET CONTROL/BU4094(IC551~2) OUT_ENABLE CONTROL

12 RESET I u-COM RESET SIGNAL INPUT

13 X-OUT O OSILATOR CONNECTION

14 Vss GND GND

15 X-IN I OSILATOR CONNECTION

16 Vcc1(+5V) 5V POWER 5V

17 NC I PULL UP

18 FLAG0 I EPROM chip select control for DSP

PIN NAME I/O FUNCTION

8

Page 9

AVR-1306

PIN

No.

19 89057_INT I LC89057(IC807) INT SIGNAL INPUT

20 PROTECTION I PROTECTION SIGNAL INPUT

21 FLD/2090_CLK O BU2090(IC302) CLOCK/ LC75721(IC301) CLOCK

22 FLD_DATA O LC75721(IC301) DATA

23 FLD_CE O LC75721(IC301) CHIP ENABLE

24 9273_STB/CDR_TAPE_MUTE O TC9273-004(IC703) STB

25 9273/9164_DATA O TC9273-004(IC703) DATA

26 9273/9164_CLK O TC9273-004(IC703) CLOCK

27 9164_STB I/O OPEN

28 9274_STB/MIC_RLY O AVR1706: MIC RELAY (RLY702) CONTROL

29 90A69/1270_CLK O TC90A69(IC609) SCLOCK/TA1270BF(IC606) SCLOCK

30 90A69/1270_DATA I/O TC90A69(IC609) SDATA/TA1270BF(IC606) SDATA

31 RS232C_TX O UP GRADE PIN(TP301) TXD

32 RS232C_RX I UP GRADE PIN(TP301) RXD

33 9274_DATA O OPEN

34 9274_CLK O OPEN

35 PLL_DATA_IN I TUNER DATA IN

36 PLL_DATA_OUT O TUNER DATA OUT

37 PLL_CLK O TUNER PLL CLOCK

38 PLL_CE O TUNER PLL CHIP ENABEL

39 TUNED I TUNED SIGNAL INPUT

40 STEREO I STEREO SIGNAL INPUT

41 EPM(UP_GRADE) I UP GRADE PIN (TP301 EPM)

42 VOL_UP I MASTER VOLUME ENCODER(VEC301)

43 VOL_DOWN I MASTER VOLUME ENCODER(VEC301)

44 SEL_UP I SELECT ENCONDER(VEC302)

45 SEL_DOWN I SELECT ENCONDER(VEC302)

46 CE(UP_GRADE) I UP GRADE PIN (TP301 CE)

47 PWR_DOWN I POWER DOWN CONTROL INPUT

48 RDS_DATA I TDA7330BD(IC202) RDDR SIGNAL INPUT

49 ERR_MUTE O ERROR MUTE

50 BSE O DIGITAL SIGNAL MUTE

51 89057_ENPHA I LC89057(IC807) PRE EMPHASIS INFOMATION SIGNAL INPUT

52 SHARC_SDIN I SHARC(IC804) SERIAL DATA INPUT

53 89057_SD_IN I LC89057(IC807) D0 SIGNAL INPUT

54 EEPROM_RST O FLASH ROM(IC805) RESET

55 89057_RST O LC89057(IC807) RESET

56 SHARC_CE O SHARC(IC804) CHIP ENABEL

57 SHARC_SDOUT O CHARC(IC804) SERIAL DATA OUT

58 89057_CE O LC89057(IC807) CHIP ENABLE

59 89057/1837_SDOUT O LC89057(IC807) D1 SIGNAL / AD1837(IC808) CIN SIGNAL

60 89057/1837_SCLK O LC89057(IC807) CLOCK/ AD1837(IC808) CCLOCK

61 1837_RST O AD1837(IC808) RESET SIGNAL OUT (TO IC821)

62 Vcc2(+5V) 5V POWER 5V

63 SHARC_SCLK O SHARC(IC804) SPICLK

64 Vss GND GND

65 SHARC_RST O SHARC(IC804) RESET SIGNAL

66 1837_CE O AD1837(IC808) CLATCH

67 FLAG3 I Special flag for ROM updata

68 FLAG2 I DSP operation check flag

69 FLAG1 I NON USE

70 H/P_DET I HEAD PHONE DETECT

71 FUNC_UP I FUNCTION ENCODER (VEC303)

72 FUNC_DOWN I FUNCTION ENCODER (VEC303)

73 RDS_CLK O TDA7332BD(IC202) CLOCK FOR RDS

PIN NAME I/O FUNCTION

9

Page 10

AVR-1306

PIN

No.

74 POWER_KEY I POWER SWICH SIGNAL INPUT

75 MIC_DET I MIC DETECTION

76 POWER_RELAY O FRONT PANEL POWER CONTROL

77 STBY_LED(RED) O STBY LED RED CONTROL

78 VCR_MUTE/9427_STB O NON USE

79 3811/94A27_CLK O BD3811K1(IC701) CLOCK/BD3812F (IC702) CLOCK

80 3811/94A27_DATA O BD3811K1(IC701) DATA/BD3812F(IC702) DATA

81 MUTE_POWER O MUTE POWER CONTROL

82 4094_STB(RLY) O BU4094(IC552) STB

83 4094_STB(RLY_MUTE) O OPEN

84 4094_STB(MUTE) O BU4094(IC551) STB

85 S-MON_DET/J I S-MONITOR DETECT

86 COMP_VIDEO_DET I COMPONENT SIGNAL INPUT DETECT

87 C_VIDEO_DET I CONPOSIT SIGNAL INPUT DETECT

88 S_VIDEO_DET I S VIDEO SIGNAL INPUT DETECT

89 RS232C_SW O OPEN

90 KEY_IN1 I KEY1 SIGNAL INPUT

91 KEY_IN2 I KEY2 SIGNAL INPUT

92 KEY_IN3 I KEY3 SIGNAL INPUT

93 SET_OPTION I MODEL OPTION SELECT

94 STEP_OPTION I AREA OPTION SELECT

95 74HC151_SW O TC74HC151(IC827) A CONTROL COAXIAL SIGNAL SELECT

96 AVss GND GND

97 SEL_CLK O SEL_CLK

98 VREF(+5V) 5V VREF

99 AVcc(+5V) 5V POWER 5V

100 74781_CE O OPEN

PIN NAME I/O FUNCTION

10

Page 11

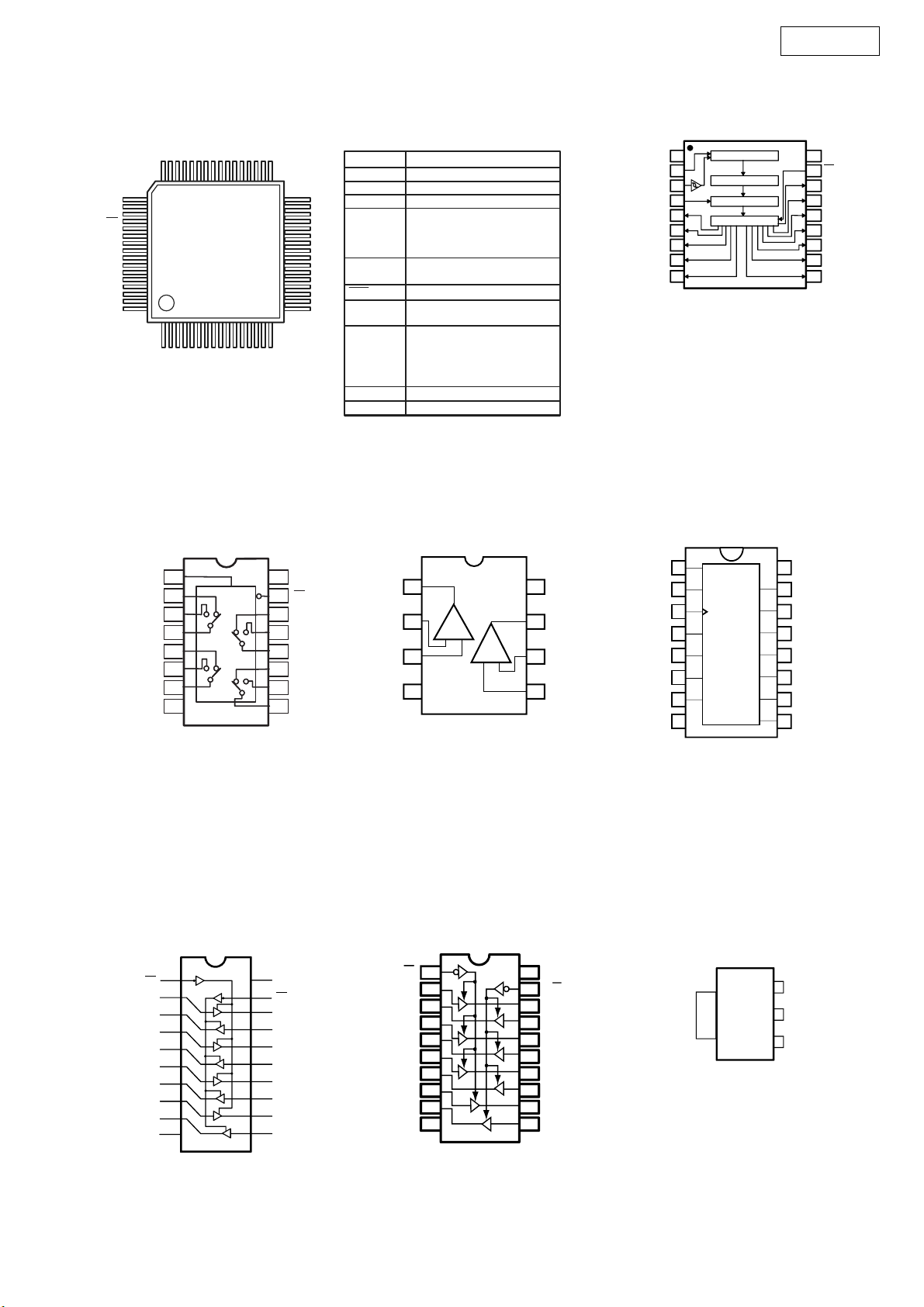

ADSP-21266SKSTZ-1B (IC804)

AVR-1306

144

1

PIN 1 INDICATOR

109

108

TOP VIEW

36

37

73

72

ADSP-21266SKSTZ-2B Terminal Function

LQFP

Pin Name

V

DDINT

Pin # Pin Name

1V

DDINT

CLKCFG0 2 GND 38 GND 74 V

CLKCFG1 3 RD 39 V

BOOTCFG0 4 ALE 40 GND 76 V

LQFP

Pin # Pin Name

37 V

DDEXT

DDINT

LQFP

Pin # Pin Name

73 GND 109

DDINT

75 GND 111

DDINT

BOOTCFG1 5 AD15 41 DAI_P10 (SD2B) 77 GND 113

GND 6 AD14 42 DAI_P11 (SD3A) 78 V

V

DDEXT

7 AD13 43 DAI_P12 (SD3B) 79 GND 115

GND 8 GND 44 DAI_P13 (SCLK23) 80 V

V

DDINT

9V

DDEXT

45 DAI_P14 (SFS23) 81 GND 117

GND 10 AD12 46 DAI_P15 (SD4A) 82 V

V

DDINT

11 V

DDINT

47 V

DDINT

83 GND 119

GND 12 GND 48 GND 84 V

V

DDINT

13 AD11 49 GND 85 RESET 121

DDINT

DDEXT

DDINT

DDINT

GND 14 AD10 50 DAI_P16 (SD4B) 86 SPIDS 122

FLAG0 15 AD9 51 DAI_P17 (SD5A) 87 GND 123

FLAG1 16 AD8 52 DAI_P18 (SD5B) 88 V

DDINT

AD7 17 DAI_P1 (SD0A) 53 DAI_P19 (SCLK45) 89 SPICLK 125

GND 18 V

V

DDINT

19 GND 55 GND 91 MOSI 127

DDINT

54 V

DDINT

90 MISO 126

GND 20 DAI_P2 (SD0B) 56 GND 92 GND 128

V

DDEXT

GND 22 GND 58 DAI_P20 (SFS45) 94 V

V

DDINT

AD6 24 V

21 DAI_P3 (SCLK0) 57 V

23 V

DDEXT

DDINT

59 GND 95 A

60 V

DDEXT

DDINT

93 V

96 A

DDINT

DDEXT

VDD

VSS

AD5 25 GND 61 FLAG2 97 GND 133

AD4 26 DAI_P4 (SFS0) 62 FLAG3 98 CLKOUT 134

V

DDINT

27 DAI_P5 (SD1A) 63 V

DDINT

99 EMU 135

GND 28 DAI_P6 (SD1B) 64 GND 100 TDO 136

AD3 29 DAI_P7 (SCLK1) 65 V

AD2 30 V

V

DDEXT

31 GND 67 V

GND 32 V

DDINT

DDINT

66 GND 102 TRST 138

68 GND 104 TMS 140

AD1 33 GND 69 V

DDINT

DDINT

DDINT

101 TDI 137

103 TCK 139

105 GND 141

AD0 34 DAI_P8 (SFS1) 70 GND 106 CLKIN 142

WR 35 DAI_P9 (SD2A) 71 V

V

DDINT

36 V

DDINT

72 V

DDINT

DDINT

107 XTAL 143

108 V

DDEXT

LQFP

Pin #

110

112

114

116

118

120

124

129

130

131

132

144

11

Page 12

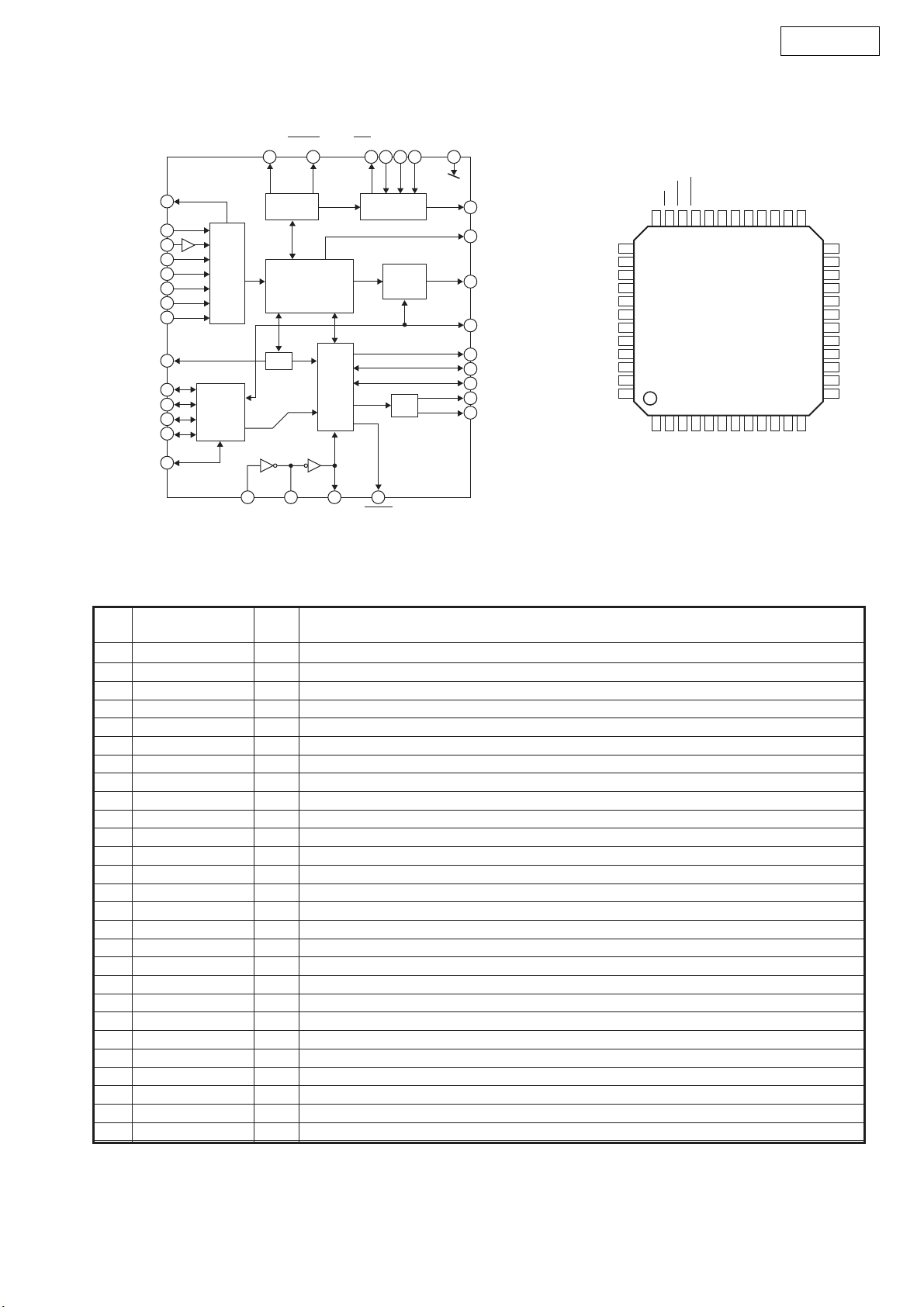

LC89057W (IC807)

AVR-1306

RXOUT

RX0

RX1

RX2

RX3

RX4

RX5/VI

RX6/UI

LPF

TMCK/PIO0

TBCK/PIO1

TLRCK/PIO2

TDATA/PIO3

TXO/PIOEN

10

13

44

45

46

47

48

1

2

3

4

5

8

9

EMPHA/UO33AUDIO/VO35INT40CL39CE38DI

32

Clock

Selector

27

Microcontroller

Input

Selector

Modulation

or

Parallel Port

29

XIN

C bit, U bit

Demodulation

&

Lock Detect

PLL

28

XOUT

XMCK34CKST

I/F

Data

Selector

I/N

XMODE

41

37

36

21

24

16

17

20

22

23

DO

RERR

RD ATA

SDIN

RMCK

RBCK

RLRCK

SBCK

SLRCK

36 RERR1RXOUT

35 INT2RX0

34 CKST3RX1

TOP VIEW

33 AUDIO/VO4RX2

32 EMPHA/UO5RX3

31 DGND6DGND

30 DVDD7DVDD

29 XIN8RX4

28 XOUT9RX5/VI

27 XMCK10RX6/UI

26 DVDD11DVDD

25 DGND12DGND

24 SDIN37DO

23 SLRCK38DI

22 SBCK39CE

21 RDATA40CL

20 RLRCK41XMODE

19 DVDD42DGND

18 DGND43DVDD

17 RBCK44TMCK/PIO0

16 RMCK45TBCK/PIO1

15 AGND46TLRCK/PIO2

14 AVDD47TDATA/PIO3

13 LPF48TXO/PIOEN

LC89057W Terminal Function

Pin

No.

1 RXOUT O Input bi-phase select data output terminal

2 RX0 I TTL compatible digital data input terminal

3 RX1 I Coaxial compatible amp built-in digital data input terminal

4 RX2 I TTL compatible digital data input terminal

5 RX3 I TTL compatible digital data input terminal

6 DGND — Digital GND

7 DVDD — Digital power

8 RX4 I TTL compatible digital data input terminal

9 RX5/VI I TTL compatible digital data/Validity flag input terminal for modulation

10 RX6/UI I TTL compatible digital data/User data input terminal for modulation

11 DVDD — Digital power for PLL

12 DGND — Digital GND for PLL

13 LPF O PLL loop filter connecting terminal

14 AVDD — Analog power for PLL

15 AGND — Analog GND for PLL

16 RMCK O RMCK clock output terminal (256fs, 512fs, XIN, VCO)

17 RBCK O/I RBCK clock in/output terminal (64fs)

18 DGND — Digital GND

19 DVDD — Digital power

20 RLRCK O/I RLRCK clock in/output terminal (fs)

21 RDATA O Serial audio data output terminal

22 SBCK O SBCK clock output terminal (32fs, 64fs, 128fs)

23 SLRCK O SLRCK clock output terminal (fs/2, fs, 2fs)

24 SDIN I Serial audio data input terminal

25 DGND — Digital GND

26 DVDD — Digital power

27 XMCK O Osc. amp output terminal

Pin Name

I/O

Function

12

Page 13

AVR-1306

Pin

No.

Pin Name I/O

Function

28 XOUT O X’tal osc. connecting output terminal

29 XIN I X’tal osc. connection, external clock input terminal (24.576MHz or 12.288MHz)

30 DVDD — Digital power

31 DGND — Digital GND

32 EMPHA/UO I/O Emphasis information/U-data output/Chip address setting terminal

33 AUDIO/VO I/O Non-PCM detect/V-flag output/ Chip address setting terminal

34 CKST I/O Clock switch transition period output/Demodulation master or slave function switching terminal

35 INT I/O Interrupt output for µcom (Interrupt factor selectable)/Modulation or general I/O switching terminal

36 RERR O PLL lock error, data error flag output

37 DO O µcom I/F, read out data output terminal (3-state)

38 DI I µcom I/F, write data input terminal

39 CE I µcom I/F, chip enable input terminal

40 CL I µcom I/F, clock input terminal

41 XMODE I System reset input terminal

42 DGND — Digital GND

43 DVDD — Digital power

44 TMCK/PIO0 I/O 256fs system clock input for modulation/General I/O in/output terminal

45 TBCK/PIO1 I/O 64fs bit clock input for modulation/General I/O in/output terminal

46 TLRCK/PIO2 I/O fs clock input for modulation/General I/O in/output terminal

47 TDATA/PIO3 I/O Serial audio data input for modulation/General I/O in/output terminal

48 TXO/PIOEN O/I Modulation data output/ General I/O enable input terminal

* For latch-up countermeasure, perform each power supply ON/OFF in the same timing.

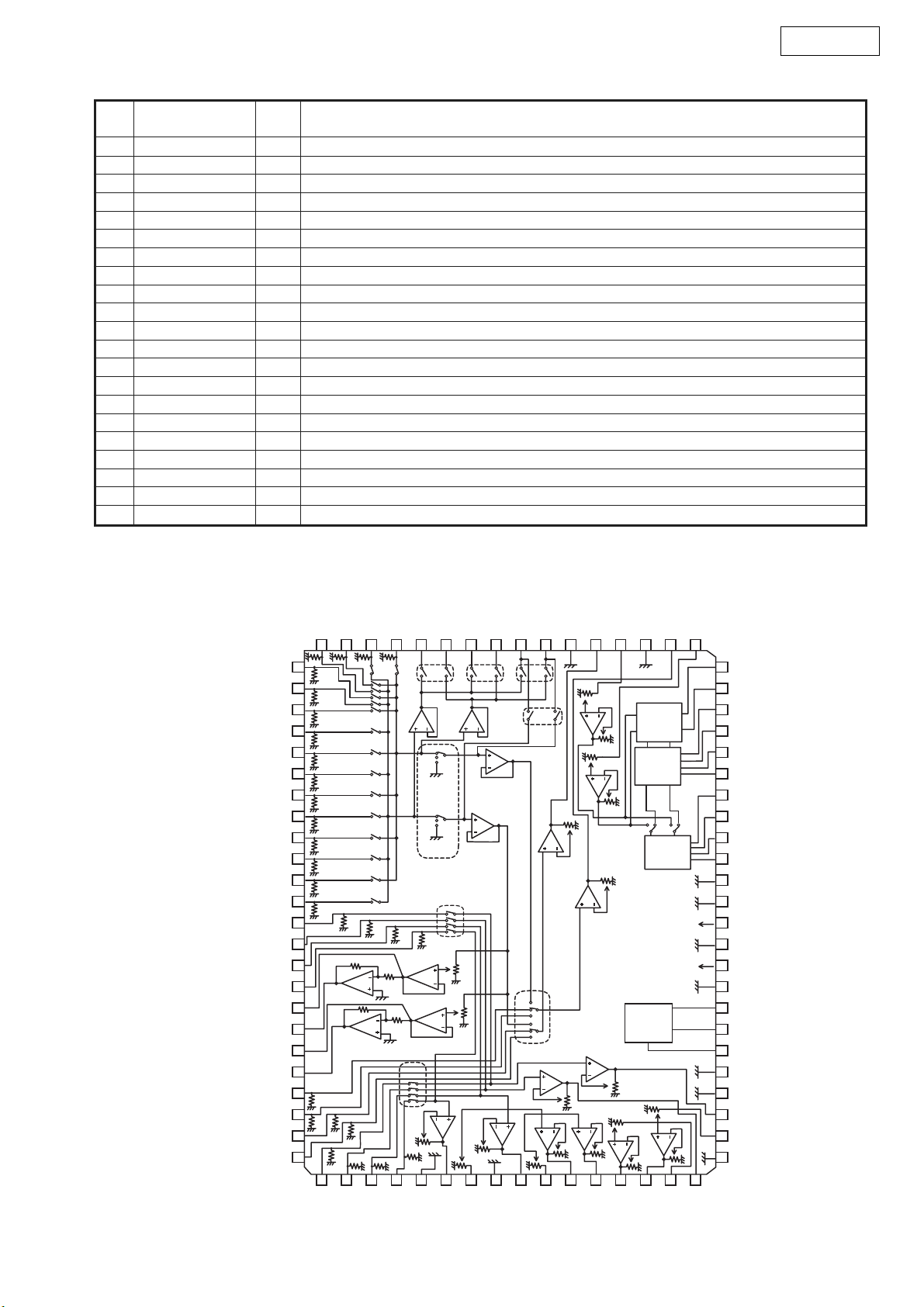

BD3811K1 (IC701)

IN31

IN32

IN41

IN42

IN51

IN52

IN61

IN62

IN71

IN72

IN81

IN82

INDVDSR

INDVDSL

INDVDC

INDVDSW

OUT2(+)

OUT2(-)

OUT1(+)

OUT1(-)

IN1DSP

IN1MIX

IN2DSP

IN2MIX

IN22

IN21

IN12

IN11

ROUT32

ROUT31

ROUT22

ROUT21

ROUT12

ROUT11

AGND10

GOUT2

OUTC

VIN2

LOGIC

OUTSL

80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25 26

INDSPSR

5.1ch Mode SW2 DSP

27 28 29 30 31 32 33 34 35 36 37 38 39 40

INDSPC

INDSPSL

5.1ch Mode SW2 DVD

AGND1

INDSPSW

GOUTSW

VINSW

AGND2

5.1ch Mode SW1

VINC

GOUTC

OUTSW

AGND9

TREBLE

BASS

BASS

BOOST

OUTSR

GOUT1

VINSL

VIN1

GOUTSL

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

TNF2

TNF1

BNF11

BNF21

BNF12

BNF22

BBNF2

OUT2

BBNF1

OUT1

AGND8

AGND7

VCC

AGND6

VEE

AGND5

MUTE

CL

DA

DGND

AGND4

GOUTSR

VINSR

AGND3

13

Page 14

AD1837 (IC808)

AVR-1306

DSDATA2

DSDATA1

NC

AGND

MCLKASDATAABCLKALRCLKODVDDDVDD DVDD

CLOCK

DIGITAL

FILTER

DIGITAL

FILTER

DIGITAL

FILTER

DIGITAL

FILTER

DGND

DVDD

39

38

DBCLK

37

DLRCLK

M/S

36

AGND

35

34

OUTR4

33

NC

32

OUTL4

31

NC

30

AGND

29

AVDD

28

OUTR3

NC

27

OUTL3

PD/RST M/S AVDD AVDD

DAC

DAC

DAC

DAC

V

DescriptionPin No.

Σ-∆

Σ-∆

Σ-∆

Σ-∆

REF

OUTL1

OUTR1

OUTL2

OUTR2

OUTL3

OUTR3

OUTL4

OUTR4

FILTD

FILTR

DLRCLK

DBCLK

DSDATA1

DSDATA2

DSDATA3

DSDATA4

ADCLP

ADCLN

ADCRP

ADCRN

AD1837 Terminal Function

Pin Name

CLATCH

PD/RST

OUTR1

Σ-∆

ADC

Σ-∆

ADC

AD1837

Input/

Output

DVDD

CIN

AGND

NC

OUTL1

NC

AGND

AVDD

NC

OUTL2

DGND

CCLK

COUT

ASDATA

ODVDD

MCLK

ALRCLK

ABCLK

50 494847 46 45 44 43 42 41 40

51

52

1

2

3

4

5

6

7

8

9

10

11

12

13

14 15 16 17 18 19 20 21 22 23 24 25 26

NC

OUTR2

SERIAL DATA

I/O PORT

DIGITAL

FILTER

DIGITAL

FILTER

TOP VIEW

FILTD

FILTR

AGND

DGND AGND AGND AGND AGNDDGND

AVDD

DSDATA4

ADCLP

ADCLN

ADCRN

CINCLATCHCCLK COUT

CONTROL PORT

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

DSDATA3

ADCRP

1,39 DVDD Digital Power Supply. Connect to digital 5V supply.

2 CLATCH I Latch Input for Control Data

33 CIN I Serial Control Input

4 PD/RST I Power-Down/Reset

5,10,16,24,30,35 AGND Analog Ground

6,12,25,31 NC Not connected

7,13,26,32 OUTLx O DACx Left Channel Output

8,14,27,33 NC Not connected

9,15,28,34 OUTRx O DACx Right Channel Output

11,19,29 AVDD Analog Power Supply. Connect to analog 5V supply.

17 FILTD Filter Capacitor Connection. Recommend 10µF/100nF.

18 FILTR Reference Filter Capacitor Connection. Recommended 10µF/100nF.

20 ADCLN I ADC Left Channel Negative Input

21 ADCLP I ADC Left Channel Positive Input

22 ADCRN I ADC Right Channel Negative Input

23 ADCRP I ADC Right Channel Positive Input

36 M/S I ADC Master/Slave Select

37 DLRCLK I/O DAC LR Clock

38 DBCLK I/O DAC Bit Clock

40,52 DGND Digital Ground

41-44 DSDATAx I DACx Input Data (Left and Right Supply)

45 ABCLK I/O ADC Bit Clock

46 ALRCLK I/O ADC LR Clock

47 MCLK I Master Clock Input

48 ADVDD Digital Output Driver Power Supply

49 ASDATA O ADC Serial Data Output

50 COUT O Output for Control Data

51 CCLK I Control Clock Input for Control Data

14

Page 15

LC75721E (IC301) BU2090 (IC302)

2

SERIAL

IN

STROBE

Q

1

Q2

Q3

Q4

CLOCK

3

4

5

6

7

8

15

14

13

12

11

10

9

V

SS

1

OUTPUT

ENABLE

V

DD

Q6

Q7

Q8

Q'S

Q5

QS

16

AVR-1306

G7 G8G9

48 33

49

DI

CL

CE

RES

DD

V

OSCI

OSCO

Vss

TEST

FL

V

G1

G2

G3

G4

G5

G6

64

AM 1

AM 2

AM 3

G10

G11

AA8/G12

AA7/G13

AA6/G14

AA5/G15

AA4/G16

AA3

AA2

AA1

AM35

AM34

AM33

161

AM 4

AM 5

AM 6

AM 7

AM 8

AM 9

AM 10

AM 11

AM 12

AM 13

AM 14

AM 15

AM 16

LC75721E Terminal Function

Symbol

32

17

AM 17

AM 18

AM 19

AM 20

AM 21

AM 22

AM 23

AM 24

AM 25

AM 26

AM 27

AM 28

AM 29

AM 30

AM 31

AM 32

V

DD

Vss

V

FL

DI

CL

CE

OSCI

OSCO

RES

AM1~AM35

AA1~AA3

AA4/G16

AA5/G15

AA6/G14

AA7/G13

AA8/G12

Power terminal +5V

Power terminal GND

Power terminal FL drive

Serial data transfer terminal

DI: Data

CL: Clock

CE: Chip enable

External CR connecting terminal

System reset terminal

Anode output terminal

Anode/Grid output terminal

Function

VSS

DATA

CLOCK

LCK

1

CONTROL CIRCUIT

2

12-bi t SHIFT REGI STER

3

4

5

6

7

8

9

12- bit STRAGE REGI STER

OUTPUT BUFF ER (OPE N DRAI N)

Q0

Q1

Q2

Q4

18

17

16

15

14

13

12

11Q3

10

G1~G11 Grid output terminal

TEST LSI test terminal

74LVX157 (IC816) BA4510F (IC815A,816A) BU4094BC (IC551,552)

SE

LECT

1A

1B

1Y

2A

2B

2Y

GND

1

2

SEL

3

4

5

5

6

7

8

16

15

14

13

12

11

10

Vcc

OUT1

1

VCC

8

ST

4A

4B

4Y

– IN1

+ IN1

2

1ch

+

–

3

2ch

+

–

OUT2

7

– IN2

6

3A

3B

9

3Y

EE

V

4

+ IN2

5

VDD

OE

Q11

Q10

Q9

Q8

Q7

Q6

Q5

MM74LCX244 (IC809-811) MM74HCT244 (IC812) FAN1117-1.2 (IC824)

RC1117-3.3 (IC823)

TOP VIEW

1

OE

2

I0

3

O4

4

I1

5

O5

6

I2

7

O6

8

I3

912

O7 O3

10 11

GND

20

VCC

19

OE2

18

O0

17

I4

16

O1

15

I5

14

O2

13

I6

I7

1G

1A

2Y

1A

2Y

1A

2Y

1A

2Y

GND

0

0

1

1

2

2

3

3

20 1

V

CC

19 2

2G

0

18 3

1Y

0

17 4

2A

1

16 5

1Y

1

15 6

2A

2

14 7

1Y

2

13 8

2A

3

12 9

1Y

3

11 10

2A

V

15

OUT

FRONT VIEW

2

3

2

1

IN

OUT

ADJ/GND

Page 16

AVR-1306

1A

1Y

2A

2Y

3A

3Y

GND

1

2

3

4

5

6

7

14

13

12

11

10

9

8

Vcc

6A

6Y

5A

5Y

4A

4Y

LH28F800BJE (IC805)

SN74LV573APW (IC818,819) SN74LV14APW (IC829)

Vcc

OE

D0

D1

D2

D3

D4

D5

D6

D7

GND

1

2

3

4

5

6

7

8

9

10

20

Q0

19

Q1

18

Q2

17

Q3

16

Q4

15

Q5

14

13

Q6

12

Q7

11

LE

OE

11

E

1

D1 D2

D0

234

D

D

D

Q

L

Q0 Q1

L

Q

Q

L

L

1819

17

Q2

D3 D4 D5 D6

567

D

D

Q

Q

L

L

16

Q3

89

D

Q

L

Q4 Q5 Q6 Q7

D7

D

D

Q

Q

L

L

12131415

SN74LVC139APWR (IC820) MM74HCT00MT (IC814,815)

FUNCTION TABLE

1G

1A

1B

1Y0

1Y1

1Y2

1Y3

GND

(each decoder/demultiplexer)

1

16

V

2

3

4

5

6

7

8

CC

15

2G

14

2A

13

2B

12

2Y0

11

2Y1

10

2Y2

9

2Y3

INPUTS

SELECT

G

G

B A Y3 Y2 Y1 Y0

L L L H H H L

L L HHHLH

L H LHLHH

L H HLHHH

H X X H H H H

OUTPUTS

OUTPUTS

GND

1A

1B

1Y

2A

2B

2Y

1

2

3

4

5

6

7

Vcc

14

4B

13

4A

12

4Y

11

3B

10

9

3A

3Y

8

IC63LV1024-10T (IC817)

16

Page 17

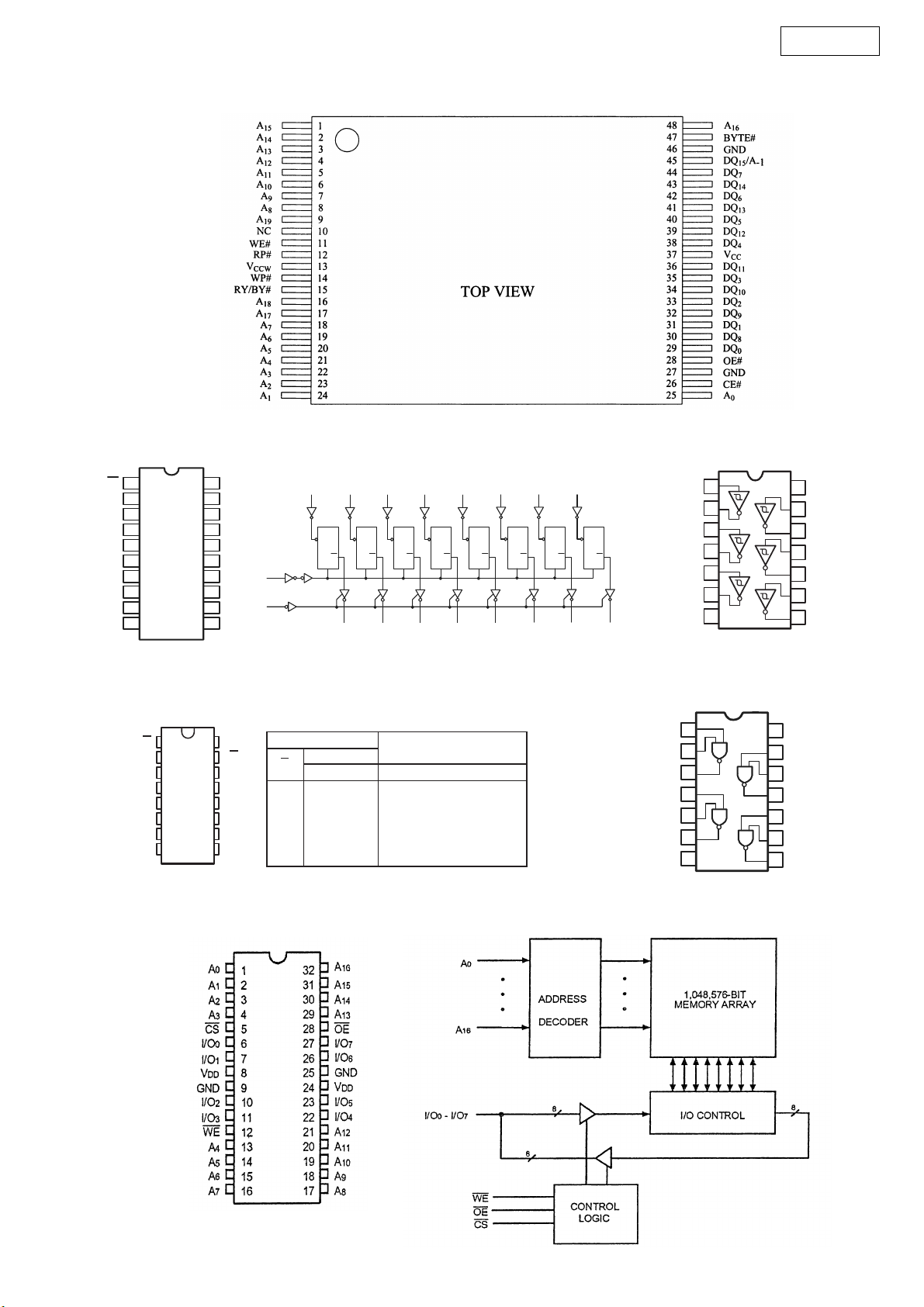

2. FL DISPLAY

16-ST-82GNK (FL301)

AVR-1306

59

TUNED

STEREO

RDS

CH

G16

TUNED

RDS

CH

G15 G13

STEREO

AUTO

Pin Assignment

AUTO

G14

ZONE2

REC

ZONE2

REC

PHONO

VCR

G12

PHONO

VCR

G11

CD

-

1

G10

CD

-

TUNER

-2-

TUNER

-2-

1

AUX

3 V.AUX

G9

3

G8

DVD /

CDR

G7

AUX

V.AUX

VDP TV

TAPE

/

G6

DVD /

CDR

G5

/

-1-

G4

VDP

TAPE

/

2

DBS

DIGITAL

G3

TV

-1-

PRO LOGICII

DIGITAL

ANALOG

G2

DBS

/

2

DIGITAL

1

G1

PRO LOGIC

DIGITAL

ANALOG

G1

S38

S13

S14

S15

S12

S9

S10

S11

S1

S6

S2

S7

S5

S3

S4

G2~G16

S3

S8

S13

S18

S23

S28

S33

S4

S9

S14

S19

S24

S29

S34

S5

S10

S15

S20

S25

S30

S35

S2

S1

S7

S6

S12

S11

S17

S16

S22

II

S21

S26

S31

S27

S32

PIN NO.

CONNECTION

PIN NO.

CONNECTION

PIN NO.

CONNECTION

12345

F1 F1

21 22

S18

NP

23 24 25

S19 S20 S21 S22 S23 S24 S25 S26 S27 S28 S29 S30 S31 S32 S33 S34 S35 S36 S37

41 42 43 44 45

S38

G16 G15 G14 G13 G12 G11 G10 G9 G8 G7 G6 G5 G4 G3 G2 G1 F2 F2

Anode & Grid Assignment

G1

G2~G16

S1

S2

S3

S4

S5

S6

S7

S8

S9

TV

VDP

2

-

1

TAPE

S36

S37

S38

S1

S2

S3

S4

S5

S6

S7

S1

S2

S3

S4

S5

S6

S7

S8

S9

S9

G1 G2 G3 G4 G5 G6 G7 G8 G9 G10 G11 G12 G13 G14 G15

/

-

S38

DBS

6

S1 S2 S3

26

46

S10

S11

S12

S13

S14

S15

S10

S11

S12

S13

S14

S15

S16

S17

S18

DIGITAL

PRO LOGIC

/(DVD)

/(CDR)

CDR

7 8 9 10 11 12 13 14 15 16 17 18 19

S5 S6 S7 S8 S9 S10 S11 S12 S13 S14 S15

S4

27 28 29 30 31 32 33 34

35 36 37 38

47 48 49 50 51 52 53 54 55 56 57

G1

G2~G16

AUXDVD

V.AUX

S13

II

S10

S11

S12

S14

S15

S16

S17

S18

S19

S20

S21

S22

S23

S24

S25

S26

S27

TUNER

-

2

-

3

CD

-

G1

G2~G16

S19

S20

S21

S22

S23

S24

S25

S26

S28

S29

S30

S31

S32

S33

S34

S35

S27

PHONO

1

VCR

REC

ZONE2

20

S16 S17

39 40

58 59

F1, F2 : Filament

G1~G16 : Grid

S1~S38 : Anode

G1

G2~G16

S28

S29

S30

S31

S32

S33

S34

S35

G16

STEREO

AUTO

TUNED

RDS

CH

17

Page 18

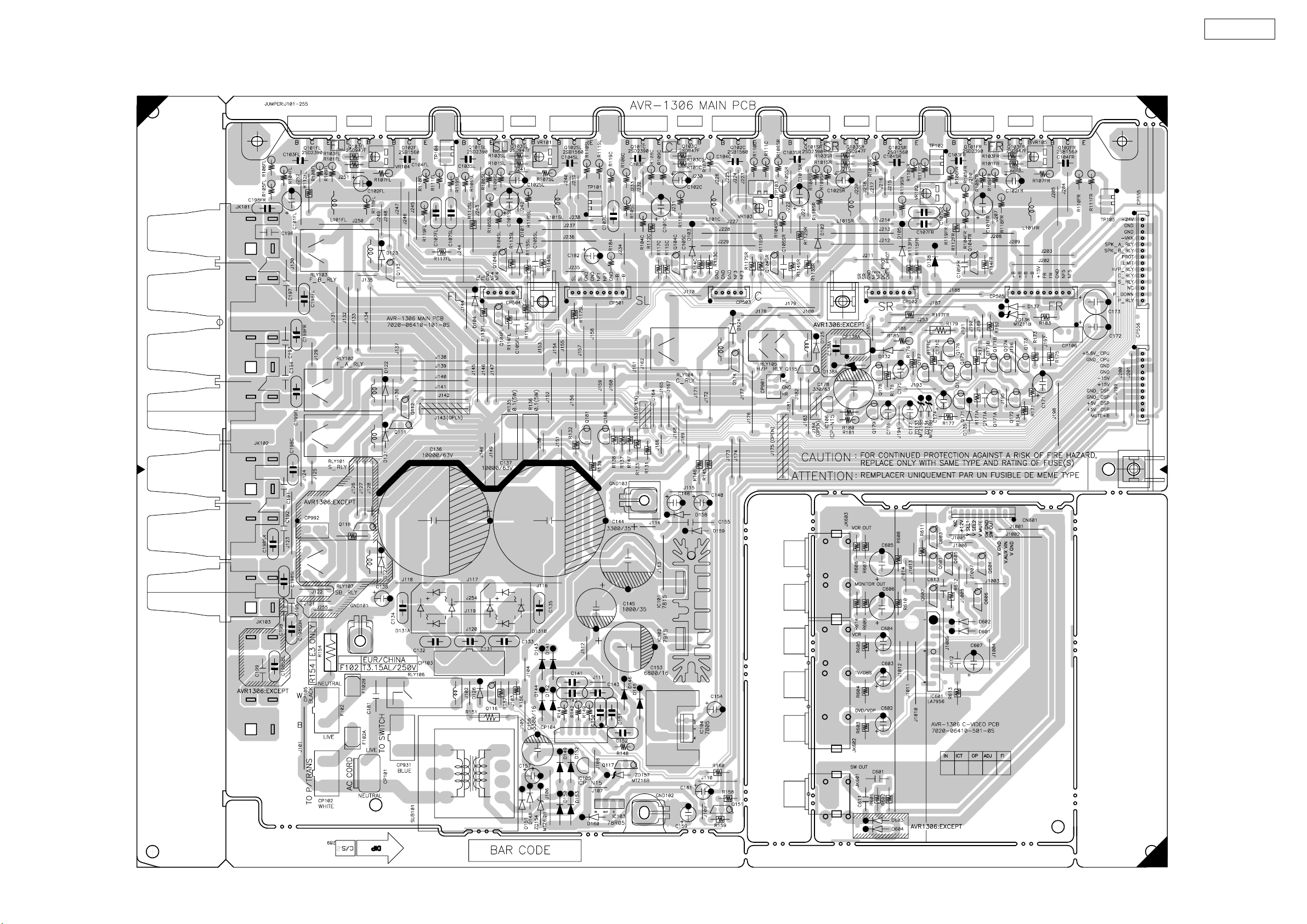

PRINTED WIRING BOARDS

MAIN P.W.B. UNIT

AVR-1306

18

COMPONENT SIDE

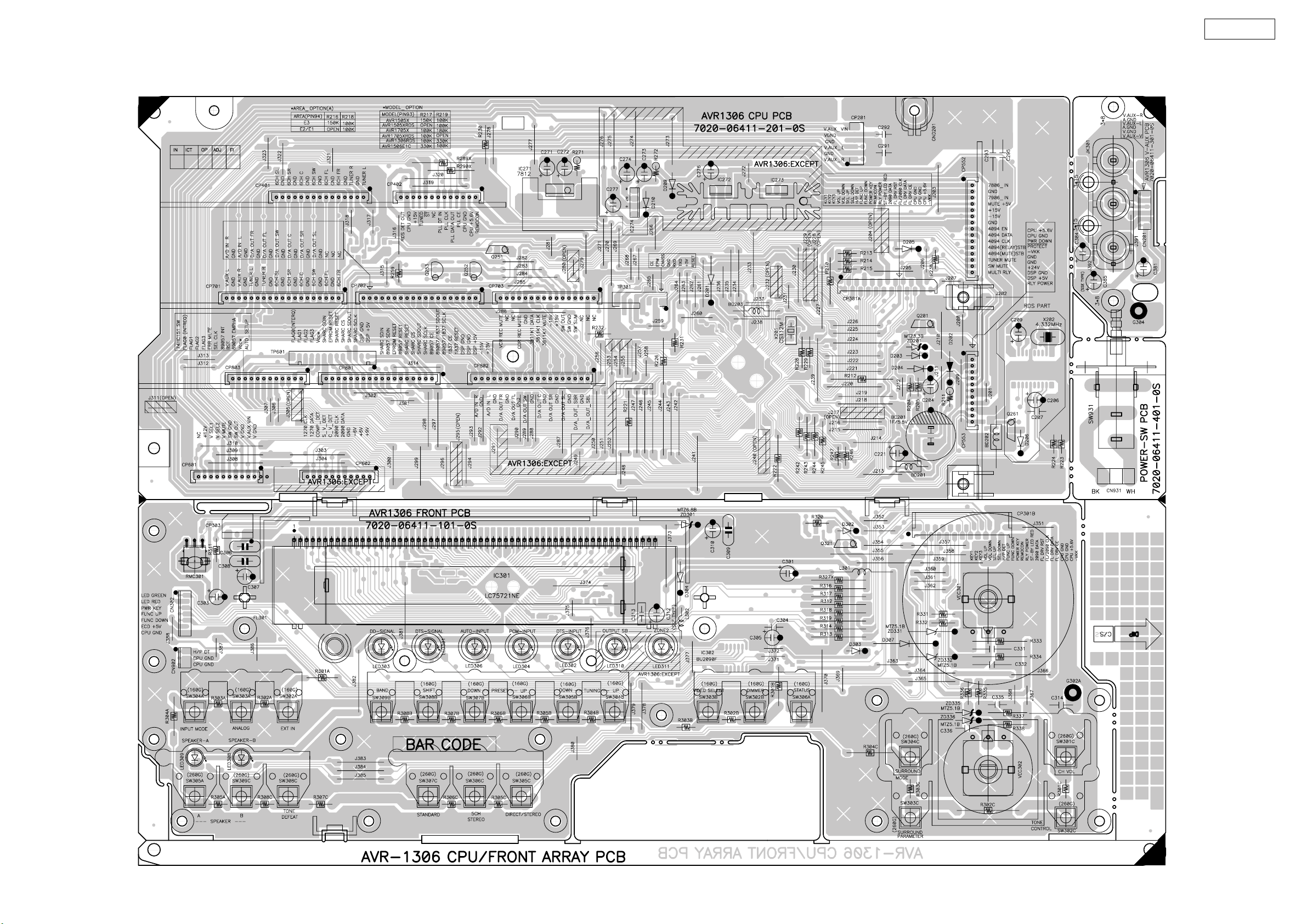

Page 19

FRONT P.W.B. UNIT

AVR-1306

19

COMPONENT SIDE

Page 20

AVR-1306

20

FOIL SIDE

Page 21

CNT P.W.B. UNIT

AVR-1306

21

COMPONENT SIDE

Page 22

AVR-1306

22

FOIL SIDE

Page 23

INPUT P.W.B. UNIT

AVR-1306

COMPONENT SIDE

23

FOIL SIDE

Page 24

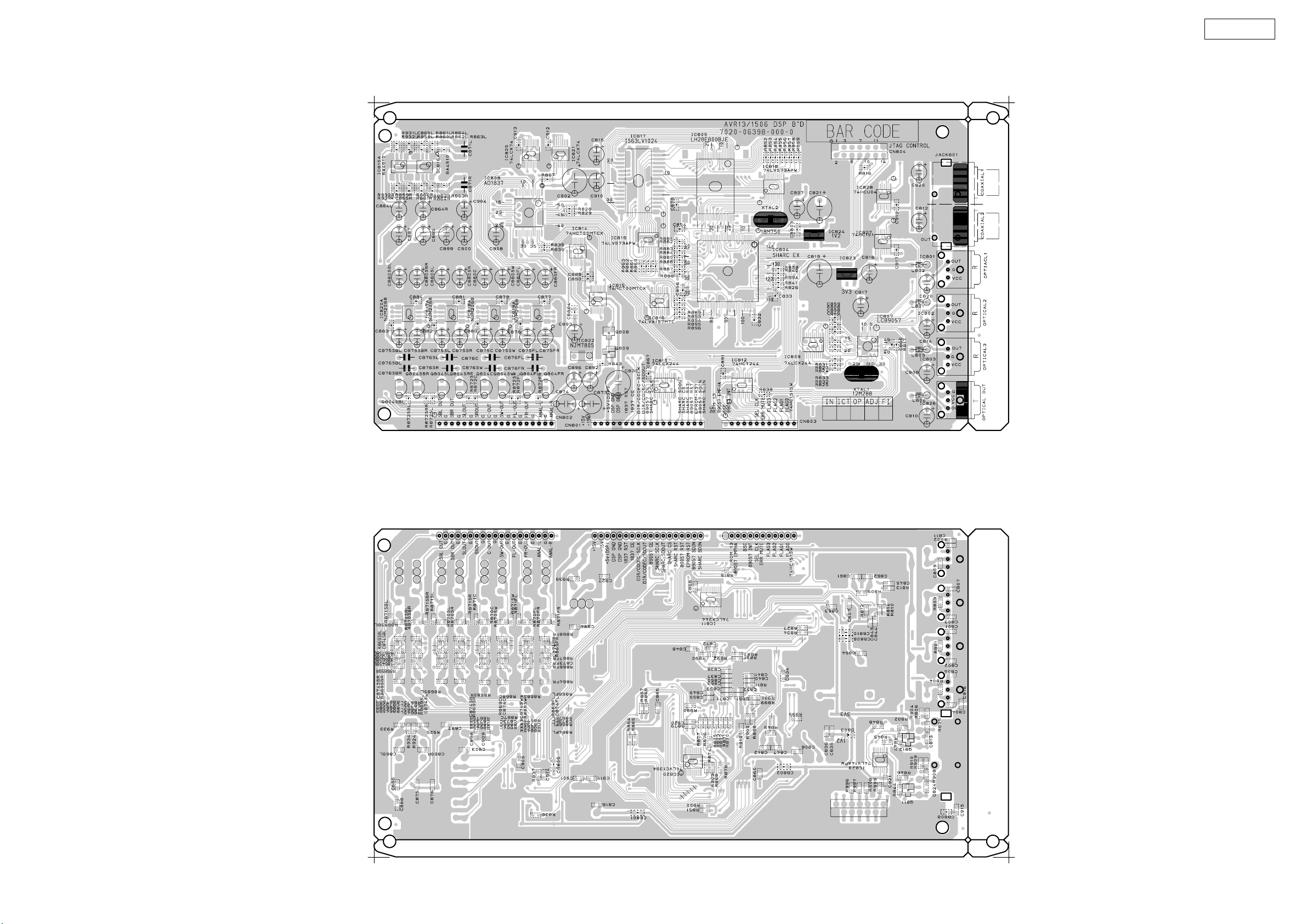

DSP P.W.B. UNIT

AVR-1306

COMPONENT SIDE

24

FOIL SIDE

Page 25

AVR-1306

NOTE FOR PARTS LIST

• Part indicated with the mark "nsp" are not always in stock and possibly to

take a long period of time for supplying, or in some case supplying of part

may be refused.

• When ordering of part, clearly indicate "1" and "I" (i) to avoid mis-

supplying.

• Ordering part without stating its part number can not be supplied.

• Part indicated with the mark " ★ " is not illustrated in the exploded view.

• Not including Carbon Film Resister ±5%, 1/4W Type in the P.W.Board

parts list. (Refer to the Schematic Diagram for those parts.)

• Not including Carbon Chip Resister 1/16W Type in the P.W.Board parts

list. (Refer to the Schematic Diagram for those parts.)

WARNING:

Parts marked with this symbol ! have critical characteristics.

Use ONLY replacement parts recommended by the manufacturer.

ll

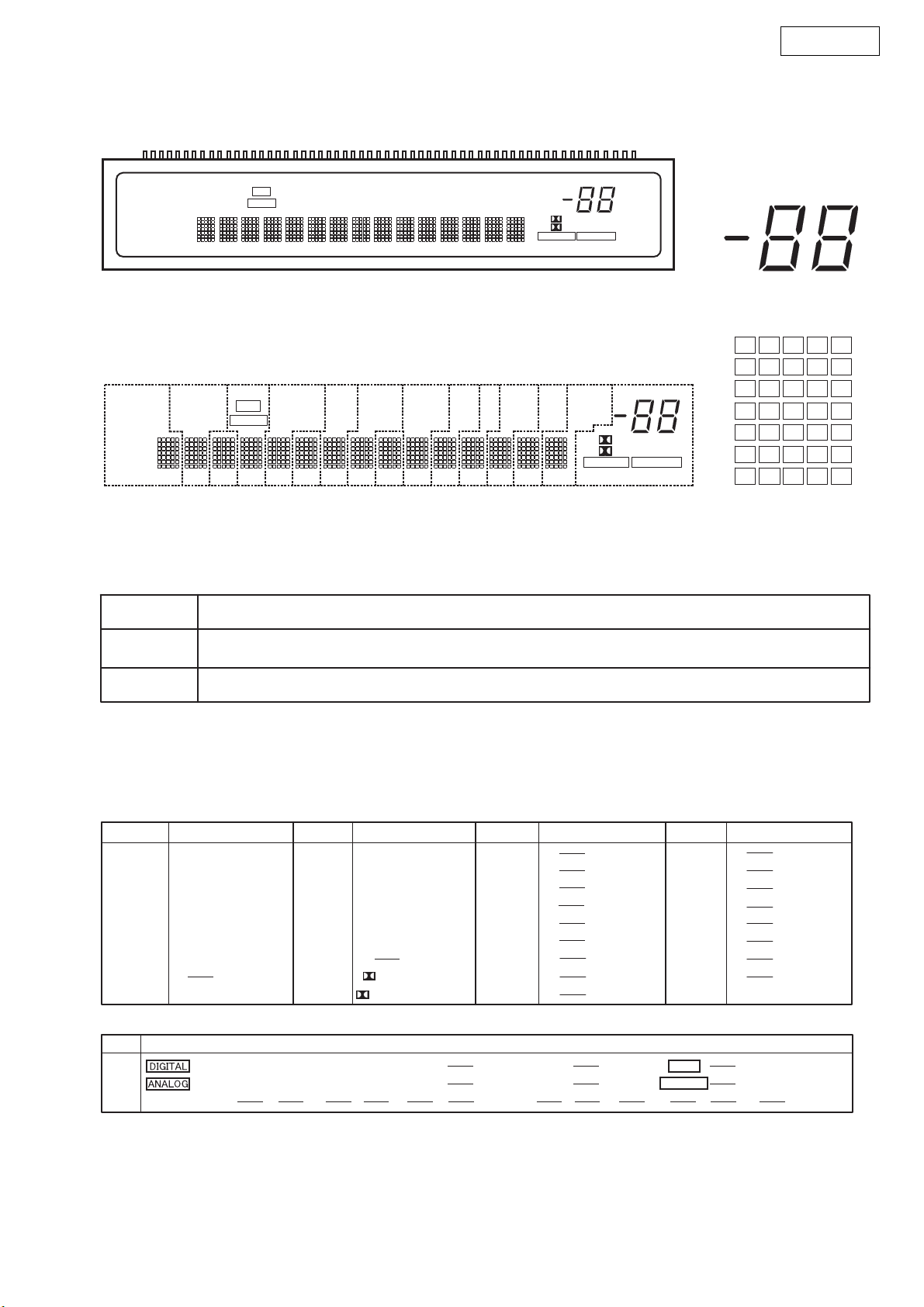

Resistors

l

ll

Ex.: RN 14K 2E 182 G FR

Type Shape Power Resist- Allowable Others

and per- ance error

formance

RD : Carbon 2B : 1/8W F : ±1% P : Pulse-resistant type

RC : Composition 2E : 1/4W G : ±2% NL : Low noise type

RS : Metal oxide film 2H : 1/2W J : ±5% NB : Non-burning type

RW : Winding 3A : 1W K : ±10% FR : Fuse-resistor

RN : Metal film 3D : 2W M : ±20% F : Lead wire forming

RK : Metal mixture 3F : 3W

] Resistance

1 8 2 ⇒ 1800 ohm = 1.8 kohm

s

s

• Units: ohm

1 R 2 ⇒ 1.2 ohm

s

s

• Units: ohm

3H : 5W

Indicates number of zeros after effective number.

2-digit effective number.

1-digit effective number.

2-digit effective number, decimal point indicated by R.

部品表について

1.nsp 印の部品は常時在庫していませんので供給に長時間を要すること

があります。

場合によっては、供給をお断りすることがあります。

2.部品を発注する際は特に数字の " 1 " と英字の "I" との区別をはっき

り記入してください。

3.部品番号を表示していない部品は供給できません。

4.!印の部品は安全上重要な部品です。交換するときは、安全および性

能維持のため必ず指定の部品をご使用ください。

5.★印のついている部品は分解図中には記載していません。

6.カーボン抵抗器± 5%、1/4W 型は記載していません。定数は回路図を

参照願います。

7.カーボンチップ抵抗器 1/16W 型は記載していません。定数は回路図を

参照願います。

8.部品表の抵抗器、コンデンサの品名記号の読み方は表を参照してくだ

さい。

RN 14K 2E 182 G FR

RD : 2B : 1/8 W F : ±1% P :

RC : 2E : 1/4 W G : ±2% NL :

RS : 2H : 1/2 W J : ±5% NB :

RW : 3A : 1 W K : ±10% FR :

RN : 3D : 2 W M : ±20% F :

RK : 3F : 3 W

∗

18 2

1R 2

3H : 5 W

1800

Ö

2

1.2

Ö

1

2 R

=1.8k

0

ll

l Capacitors

ll

Ex.: CE 04W 1H 2R2 M BP

Type Shape Dielectric Capacity Allowable Others

and per- strength error

formance

CE : Aluminum foil 0J : 6.3V F : ±1% HS : High stability type

electrolytic

CA : Aluminum solid 1A : 10V G : ±2% BP : Non-polar type

electrolytic

CS : Tantalum electrolytic 1C : 16V J : ±5% HR : Ripple-resistant type

CQ : Film 1E : 25V K : ±10% DL : For change and discharge

CK : Ceramic 1V : 35V M : ±20% HF : For assuring high

CC : Ceramic 1H : 50V Z : +80% U : UL part

CP : Oil 2A : 100V –20% C : CSA par t

CM : Mica 2B : 125V P : +100% W : UL-CSA type

CF : Metallized 2C : 160V –0% F : Lead wire forming

CH : Metallized 2D : 200V C : ±0.25pF

] Capacity (electrolyte only)

2 2 2 ⇒ 2200µF

s

s

• Units: µF.

2 R 2 ⇒ 2.2µF

s

s

• Units: µF.

] Capacity (except electrolyte)

2 2 2 ⇒ 2200pF=0.0022µF

s

s

(More than 2) Indicates number of zeros after effective number.

• Units: pF.

2 2 1 ⇒ 220pF

s

s

(0 or 1) Indicates number of zeros after effective number.

• Units: pF.

• When the dielectric strength is indicated in AC, "AC" is included after the dieelectric

strength value.

2E : 250V D : ±0.5pF

2H : 500V = : Others

2J : 630V

Indicates number of zeros after effective number.

2-digit effective number.

1-digit effective number.

2-digit effective number, decimal point indicated by R.

2-digit effective number.

2-digit effective number.

requency

CE 04W 1H 2R2 M BP

CE : 0J : 6.3 V F : ±1% HS :

CA : 1A : 10 V G : ±2% BP :

CS : 1C : 16 V J : ±5% HR :

CQ : 1E : 25 V K : ±10% DL :

CK : 1V : 35 V M : ±20% HF :

CC : 1H : 50 V Z : +80% U : UL

CP : 2A : 100 V −20% C : CSA

CM : 2B : 125 V P : +100% W : UL-CSA

CF : 2C : 160 V − 0% F :

CH : 2D : 200 V C : ±0.25pF

2E : 250 V D : ±0.5pF

2H : 500 V = :

2J : 630 V

∗

22 2

22 2

2200µF

Ö

2

µ

F

2200pF=0.0022µF

Ö

(0 2 )

2

p

F

0

0

2R 2

22 1

Ö

1

2 R

µ

F

Ö

(0 0 1 )

2

p

F

AC

2.2µF

220pF

0

25

Page 26

AVR-1306

PARTS LIST OF P.W.B. UNIT

*本表に記載されている部品は、補修用部品のため製品に使用している部品とは一部、形状、寸法などが異なる場合があります。

* The parts listed below are for maintenance only, might differ from the parts used in the unit in appearances or dimensions.

*"nsp" 印の部品は常時在庫していませんので供給に長時間を要することがあります。場合によっては、供給をお断りする場合があります。

* Part indicated with the mark “nsp” are not always in stock and possibly to take a long period of time for supplying, or in some case supplying of part may be refused.

MAIN P.W.B. UNIT ASS'Y

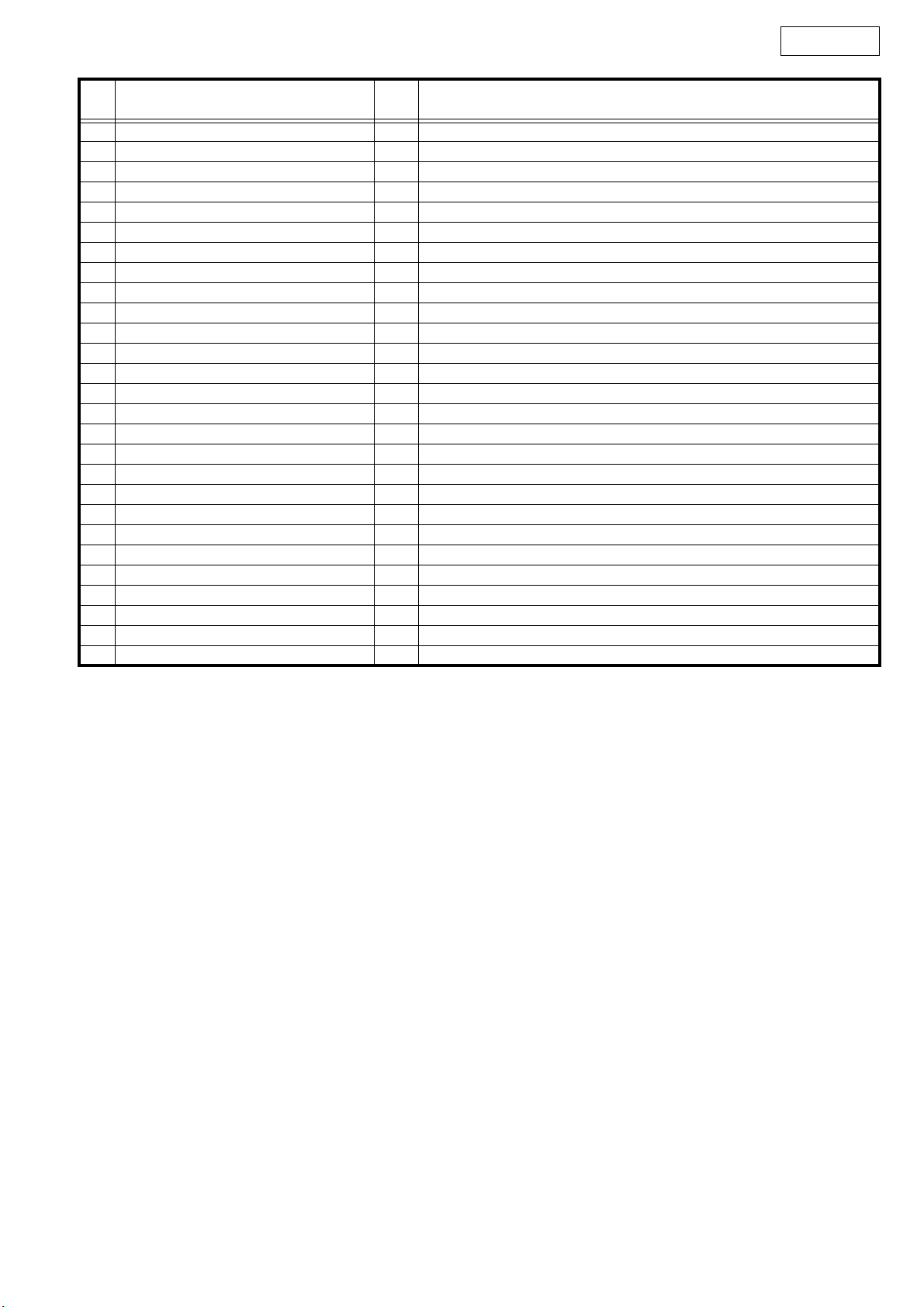

Ref. No. nsp Part No. Part Name Remarks Q'ty New

SEMICONDUCTORS GROUP

IC101 00D 963 0219 408 IC CJ7815

IC102 00D 963 0219 505 IC CJ7915F

IC103 00D 963 0057 806 IC KIA78R05PI

IC104 00D 963 0219 204 IC CJ7805

! IC105 00D 960 0195 808 IC ICP-N15

IC601 00D 963 0148 401 IC LA7956

Q104C 00D 960 0196 506 TR KSC1845F

Q104FL 00D 960 0196 506 TR KSC1845F

Q104FR 00D 960 0196 506 TR KSC1845F

Q104SL 00D 960 0196 506 TR KSC1845F

Q104SR 00D 960 0196 506 TR KSC1845F

Q111 00D 963 0121 208 TR KRC107M

Q112 00D 963 0121 208 TR KRC107M

Q113 00D 963 0121 208 TR KRC107M

Q114 00D 963 0121 208 TR KRC107M

Q115 00D 963 0121 208 TR KRC107M

Q116 00D 960 0196 409 TR 2SC1740SR

Q117 00D 963 0121 208 TR KRC107M

Q151 00D 960 0196 409 TR 2SC1740SR

Q171 00D 960 0196 700 TR KTC3200BL

Q171A 00D 960 0196 302 TR KTA1268BL

Q171B 00D 960 0196 302 TR KTA1268BL

Q171C 00D 960 0196 302 TR KTA1268BL

Q172 00D 960 0196 700 TR KTC3200BL

Q173 00D 960 0196 700 TR KTC3200BL

Q174 00D 960 0196 700 TR KTC3200BL

Q175 00D 960 0196 700 TR KTC3200BL

Q176 00D 960 0196 700 TR KTC3200BL

Q177 00D 960 0196 700 TR KTC3200BL

Q178 00D 960 0196 302 TR KTA1268BL

Q179 00D 960 0133 103 TR KSA916Y

Q180 00D 960 0196 302 TR KTA1268BL

Q181 00D 960 0196 302 TR KTA1268BL

Q601 00D 963 0255 802 TR KTC3199Y

Q602 00D 963 0255 802 TR KTC3199Y

Q603 00D 963 0121 208 TR KRC107M

Q604 00D 963 0121 208 TR KRC107M

Q605 00D 960 0097 508 TR KRC111M

Q606 00D 960 0097 508 TR KRC111M

D101 00D 963 0020 309 D, 1SS133

D102 00D 963 0020 309 D, 1SS133

D103 00D 963 0020 309 D, 1SS133

D104 00D 963 0020 309 D, 1SS133

D105 00D 963 0020 309 D, 1SS133

D121 00D 963 0020 309 D, 1SS133

D122 00D 963 0020 309 D, 1SS133

D123 00D 963 0020 309 D, 1SS133

D124 00D 963 0020 309 D, 1SS133

D125 00D 963 0020 309 D, 1SS133

D126 00D 963 0020 309 D, 1SS133

D131A 00D 960 0197 107 D, KBPC604 6A

D131B 00D 960 0197 107 D, KBPC604 6A

D132 00D 963 0020 309 D, 1SS133

D135 00D 963 0020 309 D, 1SS133

D137 00D 963 0020 309 D, 1SS133

26

Page 27

AVR-1306

Ref. No. nsp Part No. Part Name Remarks Q'ty New

D138 00D 963 0058 407 D, 1N4007

D141 00D 963 0058 407 D, 1N4007

D142 00D 963 0058 407 D, 1N4007

D143 00D 963 0058 407 D, 1N4007

D144 00D 963 0058 407 D, 1N4007

D145 00D 963 0058 407 D, 1N4007

D146 00D 963 0058 407 D, 1N4007

D148 00D 963 0020 309 D, 1SS133

D149 00D 963 0058 407 D, 1N4007

D150 00D 963 0058 407 D, 1N4007

D151 00D 963 0020 309 D, 1SS133

D152 00D 963 0058 407 D, 1N4007

D153 00D 963 0058 407 D, 1N4007

D158 00D 963 0020 309 D, 1SS133

D159 00D 963 0020 309 D, 1SS133

D160 00D 963 0020 309 D, 1SS133

D601 00D 963 0020 309 D, 1SS133

D602 00D 963 0020 309 D, 1SS133

ZD133 00D 963 0046 202 D,ZENER MTZJ18B

ZD134 00D 963 0046 202 D,ZENER MTZJ18B

ZD136 00D 963 0058 504 D,ZENER MTZJ11B

ZD154 00D 960 0095 704 D,ZENER MTZJ6.2B

ZD157 00D 963 0219 903 D,ZENER MTZJ16B

RESISTORS GROUP

R104C 00D 963 9006 285 R,FIXED 1WJ-5.6K

R104FL 00D 963 9006 285 R,FIXED 1WJ-5.6K

R104FR 00D 963 9006 285 R,FIXED 1WJ-5.6K

R104SL 00D 963 9006 285 R,FIXED 1WJ-5.6K

R104SR 00D 963 9006 285 R,FIXED 1WJ-5.6K

R105C 00D 963 9006 285 R,FIXED 1WJ-5.6K

R105FL 00D 963 9006 285 R,FIXED 1WJ-5.6K

R105FR 00D 963 9006 285 R,FIXED 1WJ-5.6K

R105SL 00D 963 9006 285 R,FIXED 1WJ-5.6K

R105SR 00D 963 9006 285 R,FIXED 1WJ-5.6K

R106C 00D 963 0215 907 R,METAL FILM 4.7-J,1W

R106FL 00D 963 0215 907 R,METAL FILM 4.7-J,1W

R106FR 00D 963 0215 907 R,METAL FILM 4.7-J,1W

R106SL 00D 963 0215 907 R,METAL FILM 4.7-J,1W

R106SR 00D 963 0215 907 R,METAL FILM 4.7-J,1W

R107C 00D 963 0215 907 R,METAL FILM 4.7-J,1W

R107FL 00D 963 0215 907 R,METAL FILM 4.7-J,1W

R107FR 00D 963 0215 907 R,METAL FILM 4.7-J,1W

R107SL 00D 963 0215 907 R,METAL FILM 4.7-J,1W

R107SR 00D 963 0215 907 R,METAL FILM 4.7-J,1W

R108C 00D 963 9006 269 R,FIXED 1WJ-0.22

R108FL 00D 963 9006 269 R,FIXED 1WJ-0.22

R108FR 00D 963 9006 269 R,FIXED 1WJ-0.22

R108SL 00D 963 9006 269 R,FIXED 1WJ-0.22

R108SR 00D 963 9006 269 R,FIXED 1WJ-0.22

R109C 00D 963 9006 269 R,FIXED 1WJ-0.22

R109FL 00D 963 9006 269 R,FIXED 1WJ-0.22

R109FR 00D 963 9006 269 R,FIXED 1WJ-0.22

R109SL 00D 963 9006 269 R,FIXED 1WJ-0.22

R109SR 00D 963 9006 269 R,FIXED 1WJ-0.22

R110C 00D 963 9006 269 R,FIXED 1WJ-0.22

R110FL 00D 963 9006 269 R,FIXED 1WJ-0.22

R110FR 00D 963 9006 269 R,FIXED 1WJ-0.22

R110SL 00D 963 9006 269 R,FIXED 1WJ-0.22

R110SR 00D 963 9006 269 R,FIXED 1WJ-0.22

R111C 00D 963 9006 269 R,FIXED 1WJ-0.22

R111FL 00D 963 9006 269 R,FIXED 1WJ-0.22

R111FR 00D 963 9006 269 R,FIXED 1WJ-0.22

27

Page 28

AVR-1306

Ref. No. nsp Part No. Part Name Remarks Q'ty New

R111SL 00D 963 9006 269 R,FIXED 1WJ-0.22

R111SR 00D 963 9006 269 R,FIXED 1WJ-0.22

R118C 00D 963 9006 256 R,FIXED 1WJ-10

R118FL 00D 963 9006 256 R,FIXED 1WJ-10

R118FR 00D 963 9006 256 R,FIXED 1WJ-10

R118SL 00D 963 9006 256 R,FIXED 1WJ-10

R118SR 00D 963 9006 256 R,FIXED 1WJ-10

R119C 00D 963 9006 256 R,FIXED 1WJ-10

R119FL 00D 963 9006 256 R,FIXED 1WJ-10

R119FR 00D 963 9006 256 R,FIXED 1WJ-10

R119SL 00D 963 9006 256 R,FIXED 1WJ-10

R119SR 00D 963 9006 256 R,FIXED 1WJ-10

R135 00D 963 0144 502 R,CEMENT 0.1-J 5W

R136 00D 963 0144 502 R,CEMENT 0.1-J 5W

R141 00D 963 0216 003 R,METAL FILM 0.22-J,1W

R142 00D 963 0216 003 R,METAL FILM 0.22-J,1W

R148 00D 963 0216 003 R,METAL FILM 0.22-J,1W

R149 00D 963 0216 003 R,METAL FILM 0.22-J,1W

R151 00D 963 0232 809 R,METAL FILM 10-J,1/4W

R179 00D 963 0232 906 R,METAL FILM 47K-F,1/4W

R181 00D 963 0215 907 R,METAL FILM 4.7-J,1W

R184 00D 963 9006 256 R,FIXED 1WJ-10

R185 00D 963 9005 655 R,METAL FILM 22-J,1/4W

VR101 00D 960 0091 601 VR,SEMI CERMET 1KB

VR102 00D 960 0091 601 VR,SEMI CERMET 1KB

VR103 00D 960 0091 601 VR,SEMI CERMET 1KB

VR104 00D 960 0091 601 VR,SEMI CERMET 1KB

VR105 00D 960 0091 601 VR,SEMI CERMET 1KB

CAPACITORS GROUP

C101C 00D 963 0234 506 C,ELECT 47UF-M/50V

C101FL 00D 963 0234 506 C,ELECT 47UF-M/50V

C101FR 00D 963 0234 506 C,ELECT 47UF-M/50V

C101SL 00D 963 0234 506 C,ELECT 47UF-M/50V

C101SR 00D 963 0234 506 C,ELECT 47UF-M/50V

C102C 00D 963 0234 205 C,ELECT 10UF-M/50V

C102FL 00D 963 0234 205 C,ELECT 10UF-M/50V

C102FR 00D 963 0234 205 C,ELECT 10UF-M/50V

C102SL 00D 963 0234 205 C,ELECT 10UF-M/50V

C102SR 00D 963 0234 205 C,ELECT 10UF-M/50V

C103C 00D 963 9003 084 C,CERAMIC 100PF-K/500V

C103FL 00D 963 9003 084 C,CERAMIC 100PF-K/500V

C103FR 00D 963 9003 084 C,CERAMIC 100PF-K/500V

C103SL 00D 963 9003 084 C,CERAMIC 100PF-K/500V

C103SR 00D 963 9003 084 C,CERAMIC 100PF-K/500V

C104C 00D 963 9003 084 C,CERAMIC 100PF-K/500V

C104FL 00D 963 9003 084 C,CERAMIC 100PF-K/500V

C104FR 00D 963 9003 084 C,CERAMIC 100PF-K/500V

C104SL 00D 963 9003 084 C,CERAMIC 100PF-K/500V

C104SR 00D 963 9003 084 C,CERAMIC 100PF-K/500V

C105C 00D 960 9003 108 C,CERAMIC 0.022UF-Z/25V

C105FL 00D 960 9003 108 C,CERAMIC 0.022UF-Z/25V

C105FR 00D 960 9003 108 C,CERAMIC 0.022UF-Z/25V

C105SL 00D 960 9003 108 C,CERAMIC 0.022UF-Z/25V

C105SR 00D 960 9003 108 C,CERAMIC 0.022UF-Z/25V

C107C 00D 963 9003 097 C,FILM 0.1UF-K/250V

C107FL 00D 963 9003 097 C,FILM 0.1UF-K/250V

C107FR 00D 963 9003 097 C,FILM 0.1UF-K/250V

C107SL 00D 963 9003 097 C,FILM 0.1UF-K/250V

C107SR 00D 963 9003 097 C,FILM 0.1UF-K/250V

C131 00D 963 9003 097 C,FILM 0.1UF-K/250V

C132 00D 963 9003 097 C,FILM 0.1UF-K/250V

C133 00D 963 9003 097 C,FILM 0.1UF-K/250V

28

Page 29

Ref. No. nsp Part No. Part Name Remarks Q'ty New

C134 00D 963 9003 097 C,FILM 0.1UF-K/250V

C135 00D 963 9003 097 C,FILM 0.1UF-K/250V

C136 00D 254 6242 702 CE68W1J103M(DL)

C137 00D 254 6242 702 CE68W1J103M(DL)

C138 00D 963 9005 749 C,ELECT 1UF-M/50V

C141 00D 963 0021 900 C,FILM 0.047UF-J/100V

C142 00D 963 0021 900 C,FILM 0.047UF-J/100V

C143 00D 963 0021 900 C,FILM 0.047UF-J/100V

C144 00D 963 0217 109 C,ELECT 3300UF-M/35V

C145 00D 963 9003 123 C,ELECT 1000UF-M/35V

C146 00D 963 9005 749 C,ELECT 1UF-M/50V

C148 00D 963 9005 749 C,ELECT 1UF-M/50V

C150 00D 963 0021 900 C,FILM 0.047UF-J/100V

C151 00D 963 0021 900 C,FILM 0.047UF-J/100V

C152 00D 963 0021 900 C,FILM 0.047UF-J/100V

C153 00D 963 0021 104 C,ELECT 6800UF-M/16V

C154 00D 963 0234 205 C,ELECT 10UF-M/50V

C155 00D 963 0020 202 C,CERAMIC 0.1UF-Z/50V

C157 00D 963 9005 749 C,ELECT 1UF-M/50V

C158 00D 963 0217 002 C,ELECT 3300UF-M/16V

C159 00D 963 9005 749 C,ELECT 1UF-M/50V

C161 00D 963 0234 205 C,ELECT 10UF-M/50V

C171 00D 960 9009 911 C,ELECT 100UF-M/10V

C171A 00D 963 0020 202 C,CERAMIC 0.1UF-Z/50V

C171B 00D 963 0020 202 C,CERAMIC 0.1UF-Z/50V

C171C 00D 963 0020 202 C,CERAMIC 0.1UF-Z/50V

C172 00D 963 9005 833 C,ELECT 220UF-M/6.3V

C173 00D 963 9005 833 C,ELECT 220UF-M/6.3V

C174 00D 963 0234 205 C,ELECT 10UF-M/50V

C175 00D 963 9006 544 C,ELECT 22UF-M/25V

C176 00D 963 9005 749 C,ELECT 1UF-M/50V

C177 00D 963 9005 749 C,ELECT 1UF-M/50V

C178 00D 963 9003 149 C,ELECT 330UF-M/63V

! C181 00D 963 9006 191 C,CERAMIC AC13F472MDOA

C182 00D 963 0234 302 C,ELECT 10UF-M/100V

C191 00D 963 0233 400 C,CERAMIC 2200PF-K/16V

C192 00D 963 0233 400 C,CERAMIC 2200PF-K/16V

C193 00D 963 0233 400 C,CERAMIC 2200PF-K/16V

C194 00D 963 0233 400 C,CERAMIC 2200PF-K/16V

C195 00D 963 0233 400 C,CERAMIC 2200PF-K/16V

C196 00D 963 0233 400 C,CERAMIC 2200PF-K/16V

C197 00D 963 0233 400 C,CERAMIC 2200PF-K/16V

C198C 00D 963 0024 703 C,FILM 0.01UF-J/100V

C198FL 00D 963 0024 703 C,FILM 0.01UF-J/100V

C198FR 00D 963 0024 703 C,FILM 0.01UF-J/100V

C198SL 00D 963 0024 703 C,FILM 0.01UF-J/100V

C198SR 00D 963 0024 703 C,FILM 0.01UF-J/100V

C199FL 00D 963 0024 703 C,FILM 0.01UF-J/100V

C199FR 00D 963 0024 703 C,FILM 0.01UF-J/100V

C601 - C,CERAMIC 100PF-K/50V

C602 00D 963 9005 862 C,ELECT 47UF-M/16V

C603 00D 963 9005 862 C,ELECT 47UF-M/16V

C604 00D 963 9005 862 C,ELECT 47UF-M/16V

C605 00D 963 9005 901 C,ELECT 470UF-M/10V

C606 00D 963 9005 901 C,ELECT 470UF-M/10V

C607 00D 963 9005 794 C,ELECT 100UF-M/16V

C611 00D 963 0233 303 C,CERAMIC 0.01UF-M/16V

C612 00D 963 0225 609 C,CERAMIC 0.047UF-Z/50V

C613 00D 963 0225 609 C,CERAMIC 0.047UF-Z/50V

AVR-1306

29

Page 30

Ref. No. nsp Part No. Part Name Remarks Q'ty New

OTHER PARTS GROUP

CN601 nsp 00D 963 0256 801 CN.WAFER 10P *

CP101 nsp 00D 960 0118 908 CN.WAFER 2P

CP102 nsp 00D 960 0123 304 CN.WAFER 2P

CP103 nsp 00D 963 0066 208 CN.WAFER 3P

CP104 nsp 00D 960 0128 804 CN.WAFER 6P

CP105 nsp 00D 963 0149 109 CN.WAFER 2P (BLACK)

CP106 nsp 00D 960 0123 207 CN.WAFER 3P

CP501 nsp 00D 963 0206 505 CN.WAFER 9P

CP502 nsp 00D 963 0206 408 CN.WAFER 7P

CP503 nsp 00D 963 0206 301 CN.WAFER 5P

CP504 nsp 00D 963 0206 301 CN.WAFER 5P

CP505 nsp 00D 963 0256 908 CN.WAFER 10P *

CP555 nsp 00D 963 0111 108 CN.WAFER 14P

CP556 nsp 00D 963 0087 805 CN.WAFER 11P

CP901 nsp 00D 963 0235 806 CN.WAFER 3P

CP931 nsp 00D 963 0149 206 CN.WAFER 2P (BLUE)

! F102 00D 963 0104 801 FUSE T3.15A/250V

GND101 - TERMINAL, EARTH

GND102 - TERMINAL, EARTH

GND103 - TERMINAL, EARTH

AVR-1306

L101C 00D 963 0049 005 COIL,INDUCTOR 0.5UH

L101FL 00D 963 0049 005 COIL,INDUCTOR 0.5UH

L101FR 00D 963 0049 005 COIL,INDUCTOR 0.5UH

L101SL 00D 963 0049 005 COIL,INDUCTOR 0.5UH

L101SR 00D 963 0049 005 COIL,INDUCTOR 0.5UH

RLY101 00D 960 0181 702 RELAY, G5PA-28 24V 5A

RLY102 00D 960 0181 702 RELAY, G5PA-28 24V 5A

RLY103 00D 960 0181 702 RELAY, G5PA-28 24V 5A

RLY104 00D 960 0181 702 RELAY, G5PA-28 24V 5A

RLY105 00D 963 0218 506 RELAY, BC3-24

RLY106 00D 963 0218 205 RELAY, G5PA-1 DC9V 250V/5A

! SUB101 00D 963 0215 606 STAND BY TRANS 230V/50HZ

TP101 nsp 00D 960 0161 405 CN.WAFER 3P

TP102 nsp 00D 960 0161 405 CN.WAFER 3P

TP103 nsp 00D 960 0161 405 CN.WAFER 3P

TP104 nsp 00D 960 0161 405 CN.WAFER 3P

TP105 nsp 00D 960 0161 405 CN.WAFER 3P

00D 963 0146 005 TER,RCA 1PIN

00D 963 0257 004 TER,RCA 2PIN *

00D 963 0257 101 TER,RCA 3PIN *

00D 963 0158 608 2P TER, SP

00D 963 0257 208 4P TER, SP *

00D 963 0119 906 8P TER, SP

-HEAT SINK

-HEAT SINK

- COVER, CAPACITOR

nsp 00D 963 0018 007 SCREW, 3*8 B-TYPE ZNY/BH

nsp 00D 960 0005 804 HOLDER,FUSE CLIP for F102A

nsp 00D 960 0005 804 HOLDER,FUSE CLIP for F102B

30

Page 31

FRONT P.W.B. UNIT ASS'Y

Ref. No. nsp Part No. Part Name Remarks Q'ty New

SEMICONDUCTORS GROUP

IC201 00D 262 3542 105 M30622MEP-282FP

IC202 00D 963 0057 602 IC TDA7330BD

IC271 00D 963 0252 902 IC CJ7812

IC301 00D 960 0180 004 IC LC75721E

IC302 00D 963 0074 504 IC BU2090F

Q201 00D 963 0121 004 TR KRC104M

Q202 00D 963 0121 509 TR KTC3875S

Q203 00D 963 0044 301 TR KTC2875B

Q204 00D 963 0044 301 TR KTC2875B

Q205 00D 963 0120 704 TR KRA102S

Q206 00D 963 0044 301 TR KTC2875B

Q207 00D 963 0044 301 TR KTC2875B

Q251 00D 960 0097 207 TR KRA102M

Q252 00D 960 0196 603 TR KTC2874B

Q253 00D 960 0196 603 TR KTC2874B

Q261 00D 963 0102 803 TR 2SA933S

Q262 00D 960 0111 808 TR KRC107S

Q301 00D 963 0120 704 TR KRA102S

Q310 00D 963 0120 704 TR KRA102S

Q311 00D 963 0120 801 TR KRC102S

Q312 00D 963 0120 704 TR KRA102S

Q313 00D 963 0120 801 TR KRC102S

Q314 00D 963 0120 704 TR KRA102S

Q315 00D 963 0120 801 TR KRC102S

Q321 00D 963 0102 803 TR 2SA933S

Q322 00D 960 0111 808 TR KRC107S

Q901 00D 963 0120 704 TR KRA102S

Q902 00D 963 0120 704 TR KRA102S

AVR-1306

D201 00D 963 0020 309 D, 1SS133

D202 00D 963 0058 407 D, 1N4007

D203 00D 963 0020 309 D, 1SS133

D204 00D 963 0020 309 D, 1SS133

D205 00D 963 0020 309 D, 1SS133

D206 00D 963 0020 309 D, 1SS133

D302 00D 963 0020 309 D, 1SS133

D303 00D 963 0020 309 D, 1SS133

D304 00D 963 0020 309 D, 1SS133

D305 00D 963 0219 709 D, 1N4148W

D307 00D 963 0020 309 D, 1SS133

D308 00D 963 0219 709 D, 1N4148W

D309 00D 963 0219 709 D, 1N4148W

ZD201 00D 963 0047 502 D,ZENER MTZJ3.3B

ZD301 00D 960 0095 801 D,ZENER MTZJ6.8B

ZD331 00D 960 0095 500 D,ZENER MTZJ5.1B

ZD332 00D 960 0095 500 D,ZENER MTZJ5.1B

ZD335 00D 960 0095 500 D,ZENER MTZJ5.1B

ZD336 00D 960 0095 500 D,ZENER MTZJ5.1B

LED301 00D 960 0197 204 LED PI5-RD/HL50RDRF4T

LED302 00D 960 0197 204 LED PI5-RD/HL50RDRF4T

LED303 00D 960 0197 204 LED PI5-RD/HL50RDRF4T

LED304 00D 960 0197 204 LED PI5-RD/HL50RDRF4T

LED306 00D 960 0197 204 LED PI5-RD/HL50RDRF4T

LED308 00D 960 0197 204 LED PI5-RD/HL50RDRF4T

LED309 00D 960 0197 204 LED PI5-RD/HL50RDRF4T

FL301 00D 963 0257 305 DISPLAY,FLT HNA-16SM13T *

31

Page 32

Ref. No. nsp Part No. Part Name Remarks Q'ty New

RESISTORS GROUP

R211 00D 960 9003 807 R,METAL FILM 100-J,1/4W

R271 00D 963 0215 907 R,METAL FILM 4.7-J,1W

CAPACITORS GROUP

C201 nsp 00D 963 9004 698 C,CERAMIC CHIP 0.01UF-K/50V

C202 nsp 00D 963 9004 711 C,CERAMIC CHIP 0.1UF-Z/50V

C203 nsp 00D 963 9004 698 C,CERAMIC CHIP 0.01UF-K/50V

C204 00D 960 9010 764 C,ELECT 4.7UF-M/50V

C205 nsp 00D 963 9004 711 C,CERAMIC CHIP 0.1UF-Z/50V

C206 00D 963 9005 862 C,ELECT 47UF-M/16V

C207 00D 963 0233 303 C,CERAMIC 0.01UF-M/16V

C208 nsp 00D 963 0223 708 C,CERAMIC CHIP 270PF-J/50V

C209 00D 963 0234 205 C,ELECT 10UF-M/50V

C210 nsp 00D 963 9004 698 C,CERAMIC CHIP 0.01UF-K/50V

C211 nsp 00D 963 9004 614 C,CERAMIC CHIP 27PF-J/50V

C212 nsp 00D 963 9004 614 C,CERAMIC CHIP 27PF-J/50V

C221 00D 960 9009 911 C,ELECT 100UF-M/10V

C261 nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C262 nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C267 nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C268 nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C269 nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C270 nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C271 00D 963 0234 205 C,ELECT 10UF-M/50V

C272 00D 963 0234 205 C,ELECT 10UF-M/50V

C275 nsp 00D 963 9004 711 C,CERAMIC CHIP 0.1UF-Z/50V

C278 nsp 00D 963 9004 711 C,CERAMIC CHIP 0.1UF-Z/50V

C291 00D 963 9004 517 C,CERAMIC 0.022UF-Z/50V

C292 00D 963 9004 517 C,CERAMIC 0.022UF-Z/50V

C293 00D 963 0233 303 C,CERAMIC 0.01UF-M/16V

C294 nsp 00D 963 9004 698 C,CERAMIC CHIP 0.01UF-K/50V

C295 00D 963 0233 303 C,CERAMIC 0.01UF-M/16V

C301 00D 963 0234 205 C,ELECT 10UF-M/50V

C302 nsp 00D 963 0234 001 C,CERAMIC CHIP 0.047UF-Z/50V

C303 00D 963 9005 862 C,ELECT 47UF-M/16V

C304 00D 960 9003 108 C,CERAMIC 0.022UF-Z/25V

C305 00D 963 9005 862 C,ELECT 47UF-M/16V

C306 00D 963 0216 401 C,FILM 0.1UF-J/100V

C307 00D 963 9005 749 C,ELECT 1UF-M/50V

C308 00D 963 0021 900 C,FILM 0.047UF-J/100V

C309 00D 963 0021 900 C,FILM 0.047UF-J/100V

C310 00D 963 9005 749 C,ELECT 1UF-M/50V

C311 nsp 00D 963 0233 701 C,CERAMIC CHIP 30PF-J/50V

C312 00D 963 9005 859 C,ELECT 47UF-M/16V

C313 00D 963 0216 702 C,FILM 0.047UF-J/63V

C321 nsp 00D 963 0224 105 C,CERAMIC CHIP 1000PF-K/50V

C322 nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C324 nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C325 nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C326X nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C331 00D 963 0233 303 C,CERAMIC 0.01UF-M/16V

C332 00D 963 0233 303 C,CERAMIC 0.01UF-M/16V

C335 00D 963 0233 303 C,CERAMIC 0.01UF-M/16V

C336 00D 963 0233 303 C,CERAMIC 0.01UF-M/16V

C343X nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C381 00D 963 9005 862 C,ELECT 47UF-M/16V

C382 nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C383 nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C384 00D 963 9005 749 C,ELECT 1UF-M/50V

C385 00D 963 9005 749 C,ELECT 1UF-M/50V

C386 nsp 00D 963 0234 001 C,CERAMIC CHIP 0.047UF-Z/50V

C387 nsp 00D 963 9004 711 C,CERAMIC CHIP 0.1UF-Z/50V

C388 nsp 00D 963 9004 711 C,CERAMIC CHIP 0.1UF-Z/50V

AVR-1306

32

Page 33

Ref. No. nsp Part No. Part Name Remarks Q'ty New

BC201 00D 254 4666 005 CE04W0H105ZC(FG)

OTHER PARTS GROUP

BD201 00D 963 0154 602 BEAD,COIL

BD202 00D 963 0154 602 BEAD,COIL

BD203 00D 963 0154 602 BEAD,COIL

CN201 nsp 00D 963 0253 202 CN,WIRE 210MM/6P

CN302 nsp 00D 963 0159 209 CN,WIRE 100MM/7P

CN902 nsp 00D 963 0246 002 CN,WIRE 80MM/3P

CN931 nsp 00D 963 0148 809 CN,WIRE 350MM/2P

CP201 nsp 00D 963 0097 604 CN.WAFER 6P

CP301A nsp 00D 963 0161 103 CN.FPC 23P

CP301B nsp 00D 963 0161 006 CN.FPC 23P

CP303 nsp 00D 963 0236 009 CN.WAFER 3P

CP401 nsp 00D 963 0097 507 CN.WAFER 15P

CP402 nsp 00D 960 0239 609 CN.WAFER 13P

CP552 nsp 00D 963 0097 507 CN.WAFER 15P

CP553 nsp 00D 963 0087 805 CN.WAFER 11P

CP601 nsp 00D 963 0256 908 CN.WAFER 10P *

CP701 nsp 00D 963 0087 504 CN.WAFER 19P

CP702 nsp 00D 963 0087 504 CN.WAFER 19P

CP703 nsp 00D 963 0087 407 CN.WAFER 16P

CP801 nsp 00D 963 0087 601 CN.WAFER 18P

CP802 nsp 00D 963 0087 504 CN.WAFER 19P

CP803 nsp 00D 963 0235 709 CN.WAFER 12P

AVR-1306

G304 nsp 00D 963 0257 509 RING,TER WIRE 80MM/1P *

GND201 - TERMINAL, EARTH

L301 00D 960 0128 008 COIL,INDUCTOR 100UH

L302 00D 960 0010 307 COIL,INDUCTOR 10UH

RMC301 00D 963 0217 808 MODULE,REMOCON NJL34H380A

SW301C 00D 963 0200 103 SW,TACT SKHV10920A

SW302A 00D 963 0095 305 SW,TACT SKHV10910D01

SW302B 00D 963 0095 305 SW,TACT SKHV10910D01

SW302C 00D 963 0200 103 SW,TACT SKHV10920A

SW303A 00D 963 0095 305 SW,TACT SKHV10910D01

SW303B 00D 963 0095 305 SW,TACT SKHV10910D01

SW303C 00D 963 0200 103 SW,TACT SKHV10920A

SW304A 00D 963 0095 305 SW,TACT SKHV10910D01

SW304B 00D 963 0095 305 SW,TACT SKHV10910D01

SW304C 00D 963 0200 103 SW,TACT SKHV10920A

SW305A 00D 963 0200 103 SW,TACT SKHV10920A

SW305B 00D 963 0095 305 SW,TACT SKHV10910D01

SW305C 00D 963 0200 103 SW,TACT SKHV10920A

SW306A 00D 963 0095 305 SW,TACT SKHV10910D01

SW306B 00D 963 0095 305 SW,TACT SKHV10910D01

SW306C 00D 963 0200 103 SW,TACT SKHV10920A

SW307B 00D 963 0095 305 SW,TACT SKHV10910D01

SW307C 00D 963 0200 103 SW,TACT SKHV10920A

SW308B 00D 963 0095 305 SW,TACT SKHV10910D01

SW308C 00D 963 0200 103 SW,TACT SKHV10920A

SW309B 00D 963 0095 305 SW,TACT SKHV10910D01

SW309C 00D 963 0200 103 SW,TACT SKHV10920A

! SW931 00D 963 0145 802 SW,PUSH SDDL-005-S(C-UL)

TP301 00D 963 0060 709 CN.WAFER 8P

TP601 00D 960 0123 605 CN.WAFER 13P

33

Page 34

AVR-1306

Ref. No. nsp Part No. Part Name Remarks Q'ty New

VEC301 00D 963 0095 208 SW,ENCODER EC16B24SA

VEC302 00D 963 0095 208 SW,ENCODER EC16B24SA

X201 00D 963 0217 701 RESONATOR,CERAMIC ZTT12.00MT

X202 00D 963 0217 604 CRYSTAL 4.332MHZ

00D 963 0146 403 TER,RCA 3PIN

nsp 00D 960 0184 408 HOLDER, FLT

-HEAT SINK

nsp 00D 963 0018 007 SCREW, 3*8 B-TYPE ZNY/BH

34

Page 35

CNT P.W.B. UNIT ASS'Y

Ref. No. nsp Part No. Part Name Remarks Q'ty New

SEMICONDUCTORS GROUP

IC401 00D 960 0296 105 IC CJ7812F

IC551 00D 963 0218 807 IC BU4094BCF

IC552 00D 963 0218 807 IC BU4094BCF

Q501C 00D 960 0196 603 TR KTC2874B

Q501FL 00D 960 0196 603 TR KTC2874B

Q501FR 00D 960 0196 603 TR KTC2874B

Q501SL 00D 960 0196 603 TR KTC2874B

Q501SR 00D 960 0196 603 TR KTC2874B

Q502C 00D 960 0196 205 TR KSA992F

Q502FL 00D 960 0196 205 TR KSA992F

Q502FR 00D 960 0196 205 TR KSA992F

Q502SL 00D 960 0196 205 TR KSA992F

Q502SR 00D 960 0196 205 TR KSA992F

Q503C 00D 960 0196 205 TR KSA992F

Q503FL 00D 960 0196 205 TR KSA992F

Q503FR 00D 960 0196 205 TR KSA992F

Q503SL 00D 960 0196 205 TR KSA992F

Q503SR 00D 960 0196 205 TR KSA992F

Q504C 00D 960 0196 506 TR KSC1845F

Q504FL 00D 960 0196 506 TR KSC1845F

Q504FR 00D 960 0196 506 TR KSC1845F

Q504SL 00D 960 0196 506 TR KSC1845F

Q504SR 00D 960 0196 506 TR KSC1845F

Q551 00D 960 0196 700 TR KTC3200BL

Q552 00D 960 0196 302 TR KTA1268BL

Q553 00D 963 0120 704 TR KRA102S

Q554 00D 963 0120 704 TR KRA102S

Q555 00D 963 0120 704 TR KRA102S

Q570A 00D 960 0005 105 TR KTA1266Y

Q570B 00D 963 0121 606 TR KRC107S

Q571X 00D 963 0121 606 TR KRC107S

Q572X 00D 960 0005 105 TR KTA1266Y

AVR-1306

D551 00D 963 0020 309 D, 1SS133

D552 00D 963 0020 309 D, 1SS133

D553 00D 963 0020 309 D, 1SS133

D554 00D 963 0020 309 D, 1SS133

D555 00D 963 0020 309 D, 1SS133

D556 00D 963 0020 309 D, 1SS133

D557 00D 963 0020 309 D, 1SS133

D558 00D 963 0020 309 D, 1SS133

D559 00D 963 0020 309 D, 1SS133

D560 00D 963 0020 309 D, 1SS133

D561 00D 963 0020 309 D, 1SS133

D562 00D 963 0058 407 D, 1N4007

D563 00D 963 0058 407 D, 1N4007

D565 00D 963 0020 309 D, 1SS133

D572 00D 963 0058 407 D, 1N4007

ZD341 00D 960 0095 500 D,ZENER MTZJ5.1B

ZD342 00D 960 0095 500 D,ZENER MTZJ5.1B

ZD564 00D 960 0095 500 D,ZENER MTZJ5.1B

LED901 00D 963 0148 605 LED, SML1216W (RED/GREEN)

RESISTORS GROUP

R509C 00D 960 9005 902 R,METAL FILM 1.2K-J,1/4W

R509FL 00D 960 9005 902 R,METAL FILM 1.2K-J,1/4W

R509FR 00D 960 9005 902 R,METAL FILM 1.2K-J,1/4W

R509SL 00D 960 9005 902 R,METAL FILM 1.2K-J,1/4W

35

Page 36

Ref. No. nsp Part No. Part Name Remarks Q'ty New

R509SR 00D 960 9005 902 R,METAL FILM 1.2K-J,1/4W

R511C 00D 960 9004 301 R,METAL FILM 47-J,1/4W

R511FL 00D 960 9004 301 R,METAL FILM 47-J,1/4W

R511FR 00D 960 9004 301 R,METAL FILM 47-J,1/4W

R511SL 00D 960 9004 301 R,METAL FILM 47-J,1/4W

R511SR 00D 960 9004 301 R,METAL FILM 47-J,1/4W

R559 00D 960 9005 642 R,METAL FILM 1.2K-J,1W

R565 00D 960 9005 642 R,METAL FILM 1.2K-J,1W

R570 00D 960 9005 642 R,METAL FILM 1.2K-J,1W

R901 00D 960 9009 270 R,METAL 470-J,2W

R902 00D 960 9009 270 R,METAL 470-J,2W

CAPACITORS GROUP

C341 00D 963 0233 303 C,CERAMIC 0.01UF-M/16V

C342 00D 963 0233 303 C,CERAMIC 0.01UF-M/16V

C401 00D 963 9005 804 C,ELECT 100UF-M/25V

C402 00D 963 9005 778 C,ELECT 10UF-M/50V

C403 00D 963 0233 303 C,CERAMIC 0.01UF-M/16V

C404 00D 963 0233 303 C,CERAMIC 0.01UF-M/16V

C481C nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C481FL nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C481FR nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C481SL nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C481SR nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C481SW nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C501C 00D 963 9006 544 C,ELECT 22UF-M/25V

C501FL 00D 963 9006 544 C,ELECT 22UF-M/25V

C501FR 00D 963 9006 544 C,ELECT 22UF-M/25V

C501M 00D 963 0234 205 C,ELECT 10UF-M/50V

C501SL 00D 963 9006 544 C,ELECT 22UF-M/25V

C501SR 00D 963 9006 544 C,ELECT 22UF-M/25V

C502C 00D 963 0234 205 C,ELECT 10UF-M/50V

C502FL 00D 963 0234 205 C,ELECT 10UF-M/50V

C502FR 00D 963 0234 205 C,ELECT 10UF-M/50V

C502SL 00D 963 0234 205 C,ELECT 10UF-M/50V

C502SR 00D 963 0234 205 C,ELECT 10UF-M/50V

C503C 00D 963 0216 207 C,CERAMIC 220PF 500V

C503FL 00D 963 0216 207 C,CERAMIC 220PF 500V

C503FR 00D 963 0216 207 C,CERAMIC 220PF 500V

C503SL 00D 963 0216 207 C,CERAMIC 220PF 500V

C503SR 00D 963 0216 207 C,CERAMIC 220PF 500V

C504C - C,CERAMIC 220PF-K/50V

C504FL - C,CERAMIC 220PF-K/50V

C504FR - C,CERAMIC 220PF-K/50V

C504SL - C,CERAMIC 220PF-K/50V

C504SR - C,CERAMIC 220PF-K/50V

C505C 00D 963 0216 100 C,CERAMIC 33PF-J/500V

C505FL 00D 963 0216 100 C,CERAMIC 33PF-J/500V

C505FR 00D 963 0216 100 C,CERAMIC 33PF-J/500V

C505SL 00D 963 0216 100 C,CERAMIC 33PF-J/500V

C505SR 00D 963 0216 100 C,CERAMIC 33PF-J/500V

C506C 00D 960 9009 911 C,ELECT 100UF-M/10V

C506FL 00D 960 9009 911 C,ELECT 100UF-M/10V

C506FR 00D 960 9009 911 C,ELECT 100UF-M/10V

C506SL 00D 960 9009 911 C,ELECT 100UF-M/10V

C506SR 00D 960 9009 911 C,ELECT 100UF-M/10V

C507C 00D 963 9003 194 C,FILM 0.0022UF-J/100V

C507FL 00D 963 9003 194 C,FILM 0.0022UF-J/100V

C507FR 00D 963 9003 194 C,FILM 0.0022UF-J/100V

C507SL 00D 963 9003 194 C,FILM 0.0022UF-J/100V

C507SR 00D 963 9003 194 C,FILM 0.0022UF-J/100V

C551 00D 963 0257 606 C,ELECT 1000UF-M/16V *

C551M 00D 963 0234 205 C,ELECT 10UF-M/50V

C551S 00D 963 0225 609 C,CERAMIC 0.047UF-Z/50V

AVR-1306

36

Page 37

Ref. No. nsp Part No. Part Name Remarks Q'ty New

C555 00D 963 0233 303 C,CERAMIC 0.01UF-M/16V

C556 00D 963 0233 303 C,CERAMIC 0.01UF-M/16V

C557 00D 963 0234 205 C,ELECT 10UF-M/50V

C563X 00D 963 0234 205 C,ELECT 10UF-M/50V

C564X nsp 00D 960 9010 094 C,CERAMIC CHIP 0.01UF-Z/50V

C565X 00D 963 0234 205 C,ELECT 10UF-M/50V

C566X nsp 00D 960 9010 094 C,CERAMIC CHIP 0.01UF-Z/50V

C567X nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C568X nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C569X nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C570X nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C901 00D 963 0233 206 C,CERAMIC 0.001UF-K/50V

C902 00D 963 0233 206 C,CERAMIC 0.001UF-K/50V

C903 00D 963 0233 109 C,CERAMIC 0.01UF-Z/50V

C904 00D 960 9003 108 C,CERAMIC 0.022UF-Z/25V

C905 00D 963 0020 202 C,CERAMIC 0.1UF-Z/50V

OTHER PARTS GROUP

BD401 00D 963 0154 602 BEAD,COIL

BD402 00D 963 0154 602 BEAD,COIL

AVR-1306

CN105 nsp 00D 963 0148 702 CN,WIRE 120MM/2P

CN402 nsp 00D 960 0239 900 CN.WAFER 13P

CN501 nsp 00D 963 0085 506 CN.WAFER 9P

CN502 nsp 00D 963 0086 505 CN.WAFER 7P

CN503 nsp 00D 963 0205 700 CN.WAFER 5P

CN504 nsp 00D 963 0205 700 CN.WAFER 5P

CN505 nsp 00D 963 0257 703 CN.WAFER 10P *

CN552 nsp 00D 963 0097 303 CN.WAFER 15P

CN553 nsp 00D 963 0086 709 CN.WAFER 11P

CN554A nsp 00D 963 0253 406 CN.WAFER 14P

CN554B nsp 00D 963 0235 903 CN.WAFER 4P

CN555 nsp 00D 963 0110 701 CN.WAFER 14P

CN556 nsp 00D 963 0086 709 CN.WAFER 11P

CN901 nsp 00D 963 0184 601 CN,WIRE 260MM/3P

CP302 nsp 00D 963 0257 800 CN.WAFER 7P *

CP401 nsp 00D 963 0097 303 CN.WAFER 15P

CP401A nsp 00D 963 0149 303 CN.FPC 15P

CP551 nsp 00D 963 0253 406 CN.WAFER 14P

CP554A nsp 00D 963 0184 805 CN,WIRE 80MM/14P

CP554B nsp 00D 963 0184 708 CN,WIRE 80MM/4P

CP902 nsp 00D 963 0235 806 CN.WAFER 3P

! F101 00D 963 0104 704 FUSE T2.5A/250V

G901 nsp 00D 963 0257 907 CN,1P WIRE LUGPIN 160MM *

! JK201 00D 960 0143 203 AC OUTLET

JK901 00D 963 0095 402 JACK PHONE, D6.5

SW901 00D 963 0200 103 SW,TACT SKHV10920A

VEC303 00D 963 0095 208 SW,ENCODER EC16B24SA

00D 960 0268 803 TER,RCA 6PIN

nsp 00D 960 0184 000 BRACKET, SCREW

nsp 00D 960 0005 804 HOLDER,FUSE CLIP for F101A

nsp 00D 960 0005 804 HOLDER,FUSE CLIP for F101B

37

Page 38

INPUT P.W.B. UNIT ASS'Y

Ref. No. nsp Part No. Part Name Remarks Q'ty New

SEMICONDUCTORS GROUP

IC701 00D 963 0096 401 IC BD3811K1

IC761 00D 963 0202 305 IC NJM2068M

IC762 00D 963 0202 305 IC NJM2068M

IC763 00D 963 0202 305 IC NJM2068M

IC781 00D 963 0202 305 IC NJM2068M

IC782 00D 963 0202 305 IC NJM2068M

IC783 00D 963 0202 305 IC NJM2068M

Q771 00D 963 0121 004 TR KRC104M

Q772 00D 960 0097 207 TR KRA102M

Q773 00D 960 0196 807 FET 2SK117Y

Q774 00D 960 0196 807 FET 2SK117Y

D771 00D 963 0219 709 D, 1N4148W

D772 00D 963 0219 709 D, 1N4148W

ZD701 00D 960 0222 603 D,ZENER MTZJ7.5A

ZD702 00D 960 0222 603 D,ZENER MTZJ7.5A

AVR-1306

RESISTORS GROUP

R731 00D 963 9005 668 R,METAL FILM 220-J,1W

R732 00D 963 9005 668 R,METAL FILM 220-J,1W

R771 00D 963 9005 639 R,METAL FILM 100-J,1W

R772 00D 963 9005 639 R,METAL FILM 100-J,1W

R791 00D 963 9005 639 R,METAL FILM 100-J,1W

R792 00D 963 9005 639 R,METAL FILM 100-J,1W

CAPACITORS GROUP

C701CH nsp 00D 963 0223 009 R,CHIP 0-J,1/16W

C701L nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C701R nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C702CH nsp 00D 963 0223 009 R,CHIP 0-J,1/16W

C702L nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C702R nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C703CH nsp 00D 963 0223 009 R,CHIP 0-J,1/16W

C703L nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C703R nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C704L nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C704R nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C705L nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C705R nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C706L nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C706R nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C707L nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C707R nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C708L nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C708R nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C721 00D 963 9005 875 C,ELECT 47UF-M/25V

C722 00D 963 0223 504 C,CERAMIC 0.047UF-Z/50V

C723 00D 963 9005 875 C,ELECT 47UF-M/25V

C724 00D 963 0223 504 C,CERAMIC 0.047UF-Z/50V

C725 00D 963 9005 736 C,FILM 0.0047UF-J/100V

C726 00D 963 9005 736 C,FILM 0.0047UF-J/100V

C727 00D 963 0216 401 C,FILM 0.1UF-J/100V

C728 00D 963 0216 401 C,FILM 0.1UF-J/100V

C729 00D 963 0216 401 C,FILM 0.1UF-J/100V

C730 00D 963 0216 401 C,FILM 0.1UF-J/100V

C731 00D 963 0234 205 C,ELECT 10UF-M/50V

C732 00D 963 0234 205 C,ELECT 10UF-M/50V

38

Page 39

AVR-1306

Ref. No. nsp Part No. Part Name Remarks Q'ty New

C733 00D 963 0234 205 C,ELECT 10UF-M/50V

C734 00D 963 0234 205 C,ELECT 10UF-M/50V

C735 00D 963 0234 205 C,ELECT 10UF-M/50V

C736 00D 963 0234 205 C,ELECT 10UF-M/50V

C741 nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C742 nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C743 nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C761FL nsp 00D 963 0234 001 C,CERAMIC CHIP 0.047UF-Z/50V

C761FR nsp 00D 963 0234 001 C,CERAMIC CHIP 0.047UF-Z/50V

C761SW nsp 00D 963 0234 001 C,CERAMIC CHIP 0.047UF-Z/50V

C762FL nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C762FR nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C762SW nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C763FL nsp 00D 963 0234 001 C,CERAMIC CHIP 0.047UF-Z/50V

C763FR nsp 00D 963 0234 001 C,CERAMIC CHIP 0.047UF-Z/50V

C763SW nsp 00D 963 0234 001 C,CERAMIC CHIP 0.047UF-Z/50V

C764FL nsp 00D 963 0223 805 C,CERAMIC CHIP 33PF-J/50V

C764FR nsp 00D 963 0223 805 C,CERAMIC CHIP 33PF-J/50V

C764SW nsp 00D 963 0233 808 C,CERAMIC CHIP 47PF-J/50V

C765FL 00D 963 0234 205 C,ELECT 10UF-M/50V

C765FR 00D 963 0234 205 C,ELECT 10UF-M/50V

C765SW 00D 963 0234 205 C,ELECT 10UF-M/50V

C771 00D 963 9005 875 C,ELECT 47UF-M/25V

C772 00D 963 9005 875 C,ELECT 47UF-M/25V

C773 00D 963 9005 749 C,ELECT 1UF-M/50V

C781C nsp 00D 963 0234 001 C,CERAMIC CHIP 0.047UF-Z/50V

C781FL nsp 00D 963 0234 001 C,CERAMIC CHIP 0.047UF-Z/50V

C781FR nsp 00D 963 0234 001 C,CERAMIC CHIP 0.047UF-Z/50V

C781SL nsp 00D 963 0234 001 C,CERAMIC CHIP 0.047UF-Z/50V

C781SR nsp 00D 963 0234 001 C,CERAMIC CHIP 0.047UF-Z/50V

C781SW nsp 00D 963 0234 001 C,CERAMIC CHIP 0.047UF-Z/50V

C782C 00D 960 9010 010 C,ELECT 4.7UF-M/50V

C782FL 00D 963 0234 205 C,ELECT 10UF-M/50V

C782FR 00D 963 0234 205 C,ELECT 10UF-M/50V

C782SL 00D 963 0234 205 C,ELECT 10UF-M/50V

C782SR 00D 963 0234 205 C,ELECT 10UF-M/50V

C782SW 00D 960 9010 010 C,ELECT 4.7UF-M/50V

C783C nsp 00D 963 0223 902 C,CERAMIC CHIP 39PF-J/50V

C783FL nsp - C,CERAMIC CHIP 56PF-J/50V

C783FR nsp - C,CERAMIC CHIP 56PF-J/50V

C783SL nsp 00D 963 0223 902 C,CERAMIC CHIP 39PF-J/50V

C783SR nsp 00D 963 0223 902 C,CERAMIC CHIP 39PF-J/50V

C783SW nsp 00D 963 0223 601 C,CERAMIC CHIP 100PF-J/50V

C786SW 00D 960 9010 010 C,ELECT 4.7UF-M/50V

C791 00D 963 9005 875 C,ELECT 47UF-M/25V

C792 00D 963 9005 875 C,ELECT 47UF-M/25V

OTHER PARTS GROUP

CN551 nsp 00D 963 0184 407 CN,WIRE 160MM/14P

CN701 nsp 00D 963 0086 204 CN.WAFER 19P

CN702 nsp 00D 963 0086 204 CN.WAFER 19P

CN703 nsp 00D 963 0086 107 CN.WAFER 16P

J705 nsp 00D 963 0223 009 R,CHIP 0-J,1/16W

J706 nsp 00D 963 0223 009 R,CHIP 0-J,1/16W

J707 nsp 00D 963 0258 003 R,CHIP 0-J,1/8W *

J708 nsp 00D 963 0258 003 R,CHIP 0-J,1/8W *

00D 963 0146 209 TER,RCA 4PIN

00D 960 0268 803 TER,RCA 6PIN

nsp 00D 963 0094 005 CUSHION (24*18*2.7t)

nsp 00D 963 0094 102 PLATE

39

Page 40

DSP P.W.B. UNIT ASS'Y

Ref. No. nsp Part No. Part Name Remarks Q'ty New

SEMICONDUCTORS GROUP

IC802 00D 963 0237 503 JSR1165-C /OPTICAL

IC803 00D 963 0237 503 JSR1165-C /OPTICAL

IC804 00D 262 3370 005 ADSP-21266SKSTZ-1B

IC805 00D 262 3544 006 LH28F800BJE-BTL90

IC807 00D 262 3066 102 LC89057W-VF4-E(AC) +REF

IC808 00D 262 3535 002 AD1837AASZ

IC809 00D 960 0266 805 IC MM74LCX244

IC810 00D 960 0266 805 IC MM74LCX244

IC811 00D 960 0266 805 IC MM74LCX244

IC812 00D 960 0266 902 IC MM74HCT244

IC814 00D 963 0218 904 IC MM74HCT00MTCX

IC815 00D 963 0218 904 IC MM74HCT00MTCX

IC815A 00D 963 0043 807 IC BA4510F

IC816 00D 262 2870 904 74LVX157MTC +C

IC816A 00D 963 0043 807 IC BA4510F

IC817 00D 262 3372 003 IC63LV1024-10T

IC817A 00D 963 0202 305 IC NJM2068M

IC818 00D 262 2642 909 SN74LV573APWR +REF

IC818A 00D 963 0202 305 IC NJM2068M

IC819 00D 262 2642 909 SN74LV573APWR +REF

IC819A 00D 963 0202 305 IC NJM2068M

IC820 00D 262 3339 907 SN74LVC139APWR +REF

IC821 00D 262 2870 904 IC 74LCX74MTC

IC822 00D 960 0296 008 IC CJ7805F

IC823 00D 963 0111 603 IC RC1117-3.3

IC824 00D 963 0147 509 IC RC1117-1.2

IC825 00D 262 2870 904 IC 74LCX74MTC

IC827 00D 963 0219 107 IC MM74HC151MTCX

IC828 00D 963 0219 000 IC 74VHCU04

IC829 00D 963 0244 907 IC SN74LV14APWR

AVR-1306

Q804C 00D 960 0196 603 TR KTC2874B

Q804FL 00D 960 0196 603 TR KTC2874B

Q804FR 00D 960 0196 603 TR KTC2874B

Q804SL 00D 960 0196 603 TR KTC2874B

Q804SR 00D 960 0196 603 TR KTC2874B

Q804SW 00D 960 0196 603 TR KTC2874B