Page 1

5

4

3

2

1

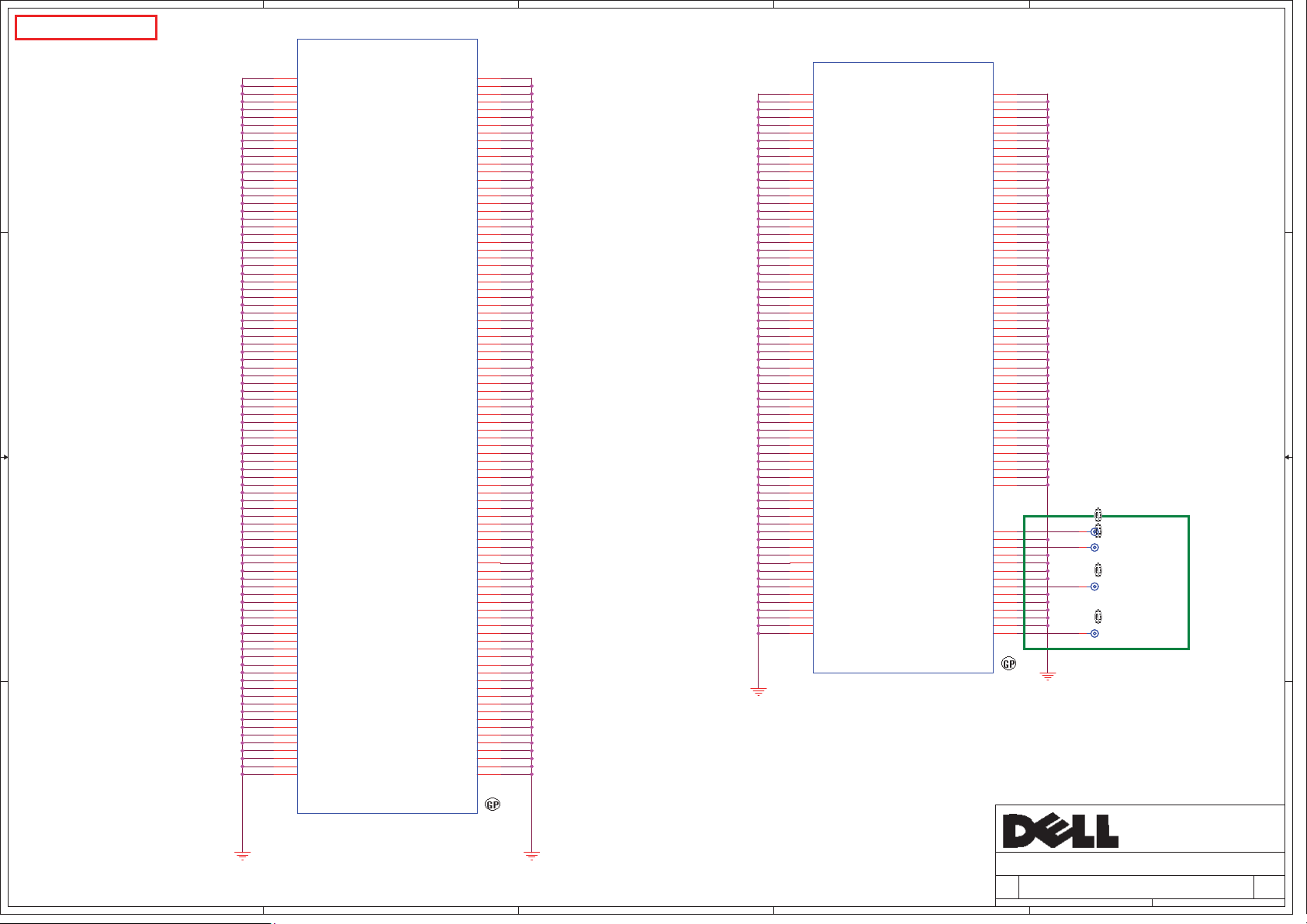

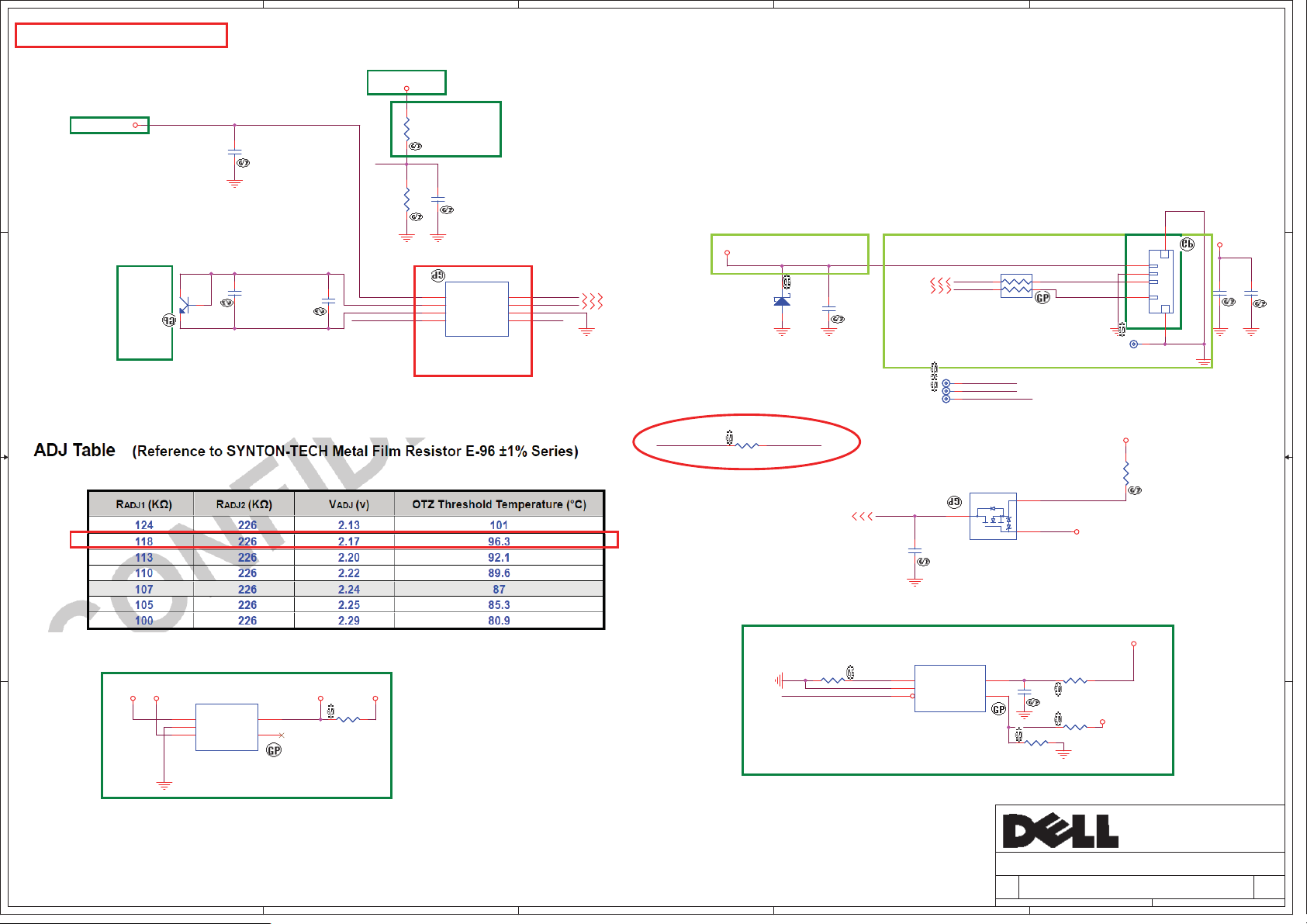

DB13 DIS Schematics Document

D D

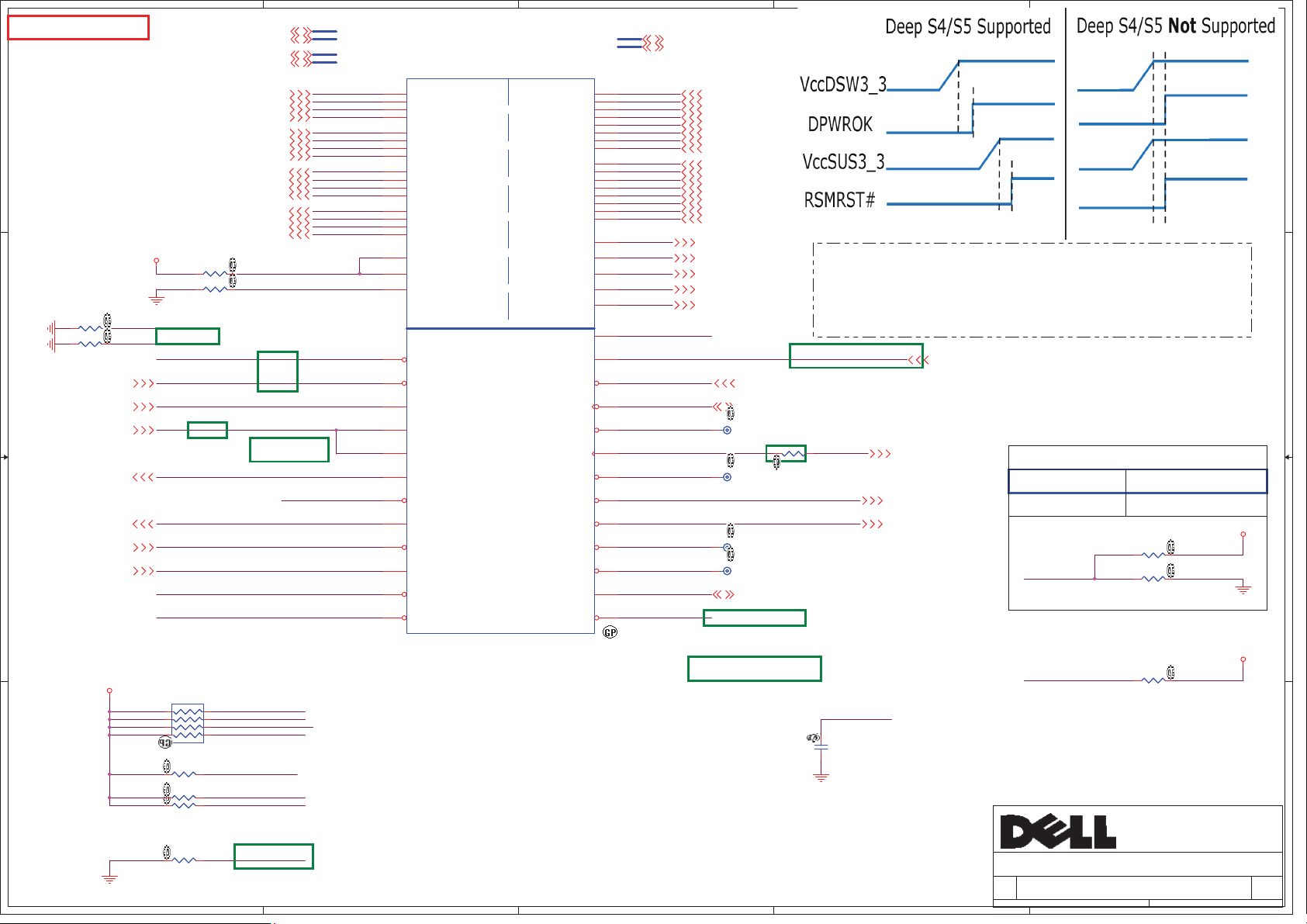

Sandy Bridge

Intel PCH

C C

2010-11-25

REV : X00

B B

DY :None Installed

PSL: KBC795 PSL circuit for 10mW solution installed.

10mW: External circuit for 10mW solution installed.

GSONSOR_ST: Stuff for ST G-Sensor

GSENSOR_ADI: Stuff for ADI G-Sensor

A A

5

4

http://hobi-elektronika.net

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

Cover

Cover

Cover

DB13 DIS

DB13 DIS

DB13 DIS

1 105Friday, November 26, 2010

1 105Friday, November 26, 2010

1 105Friday, November 26, 2010

of

of

1

of

X00

X00

X00

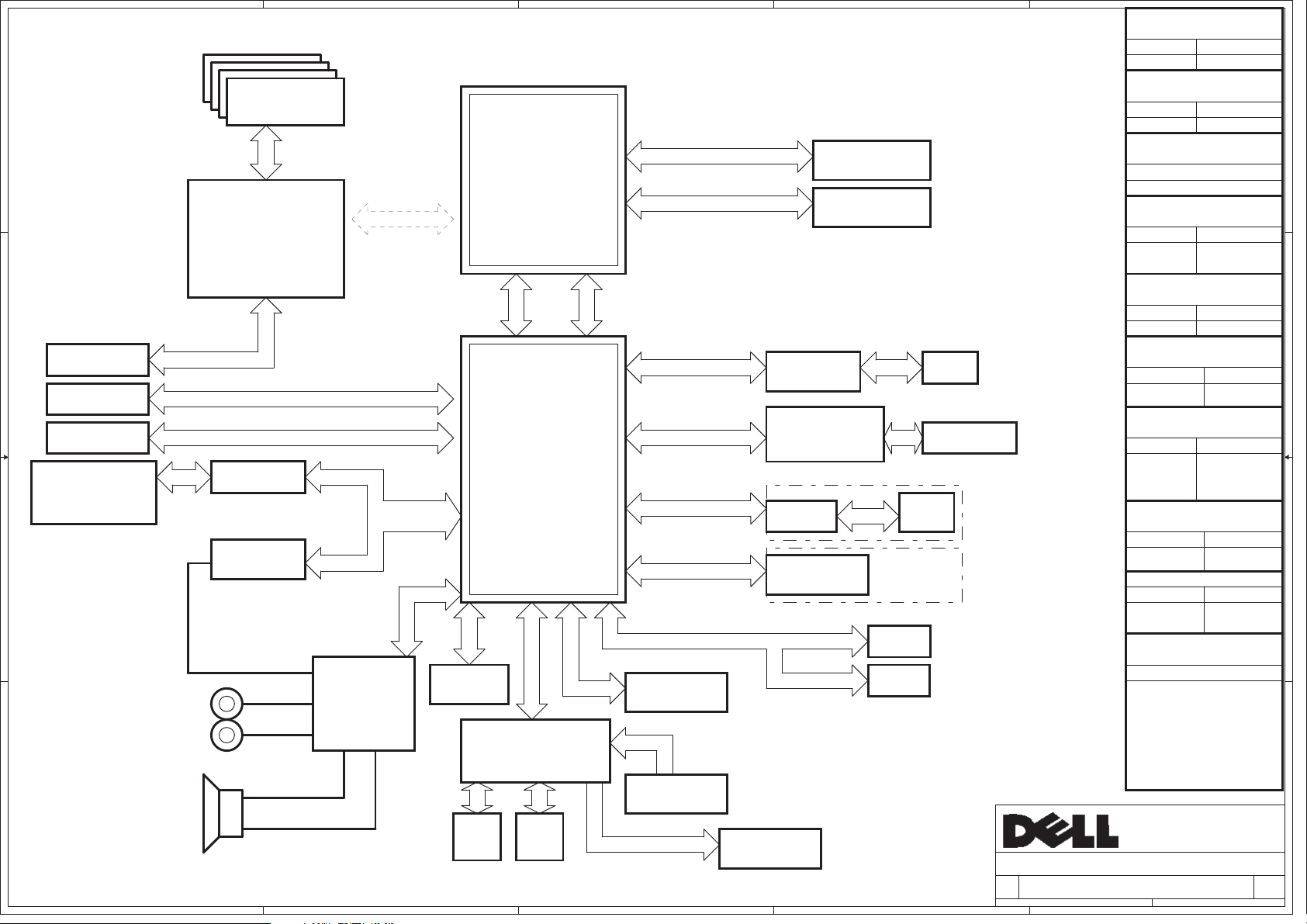

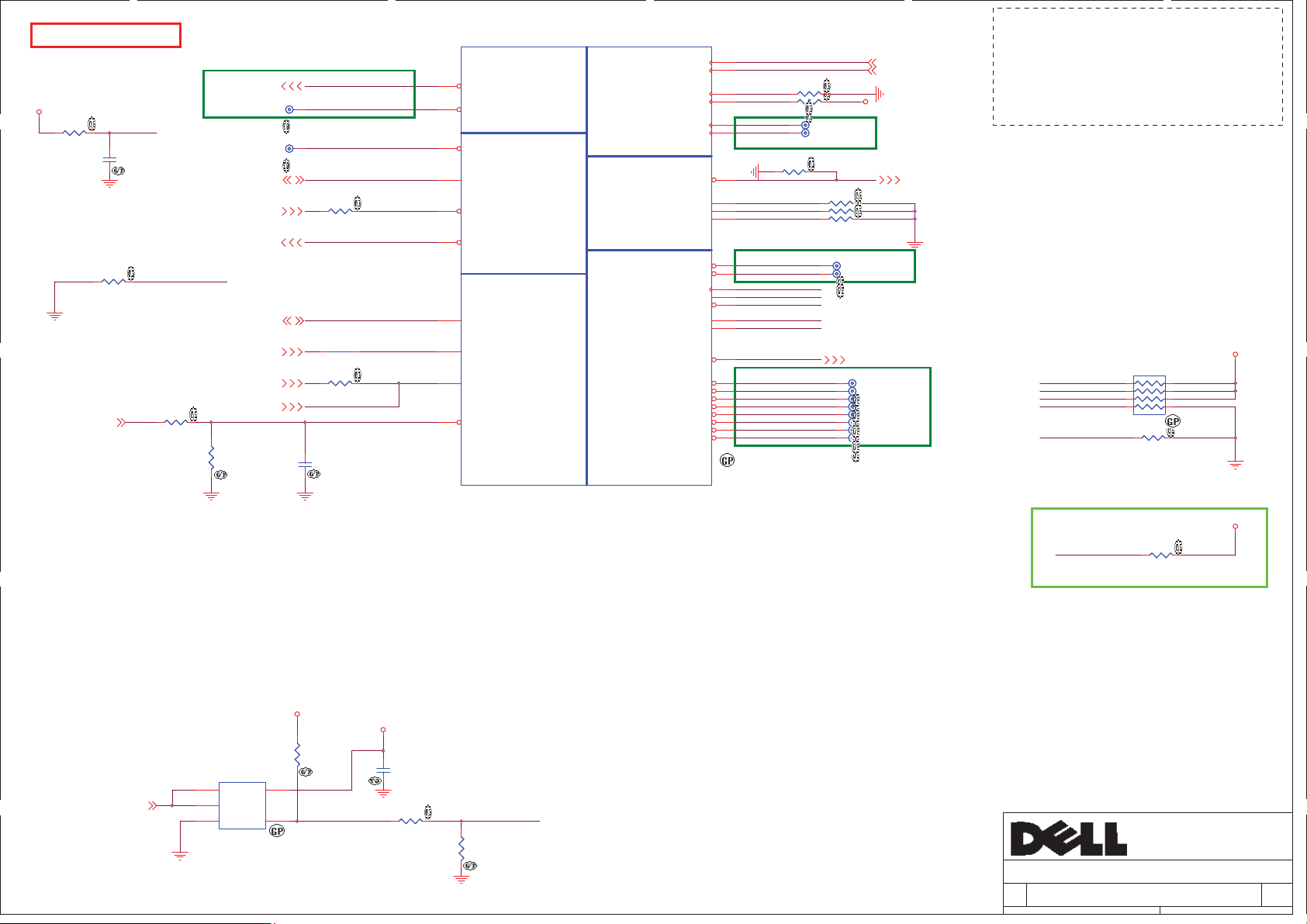

Page 2

5

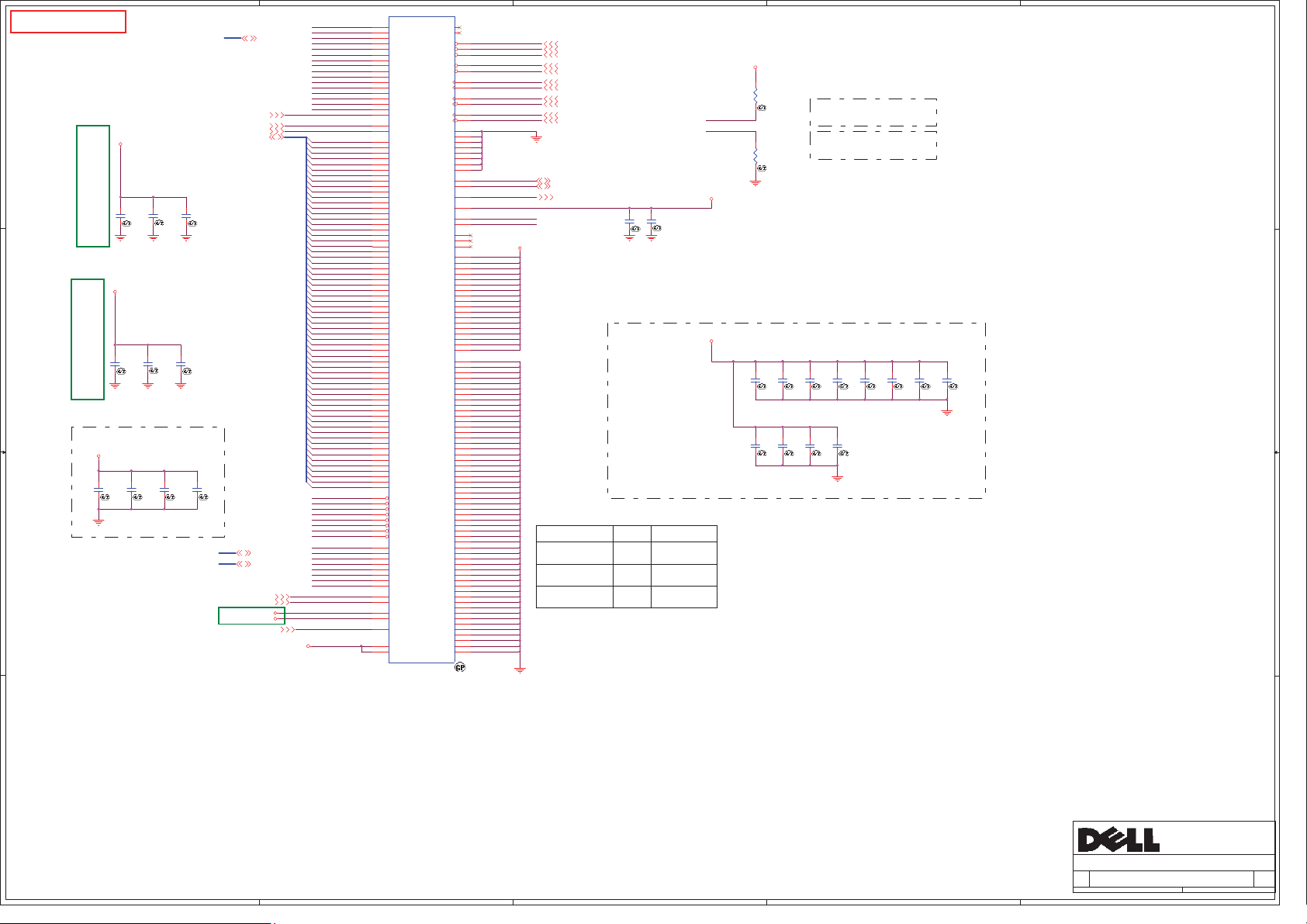

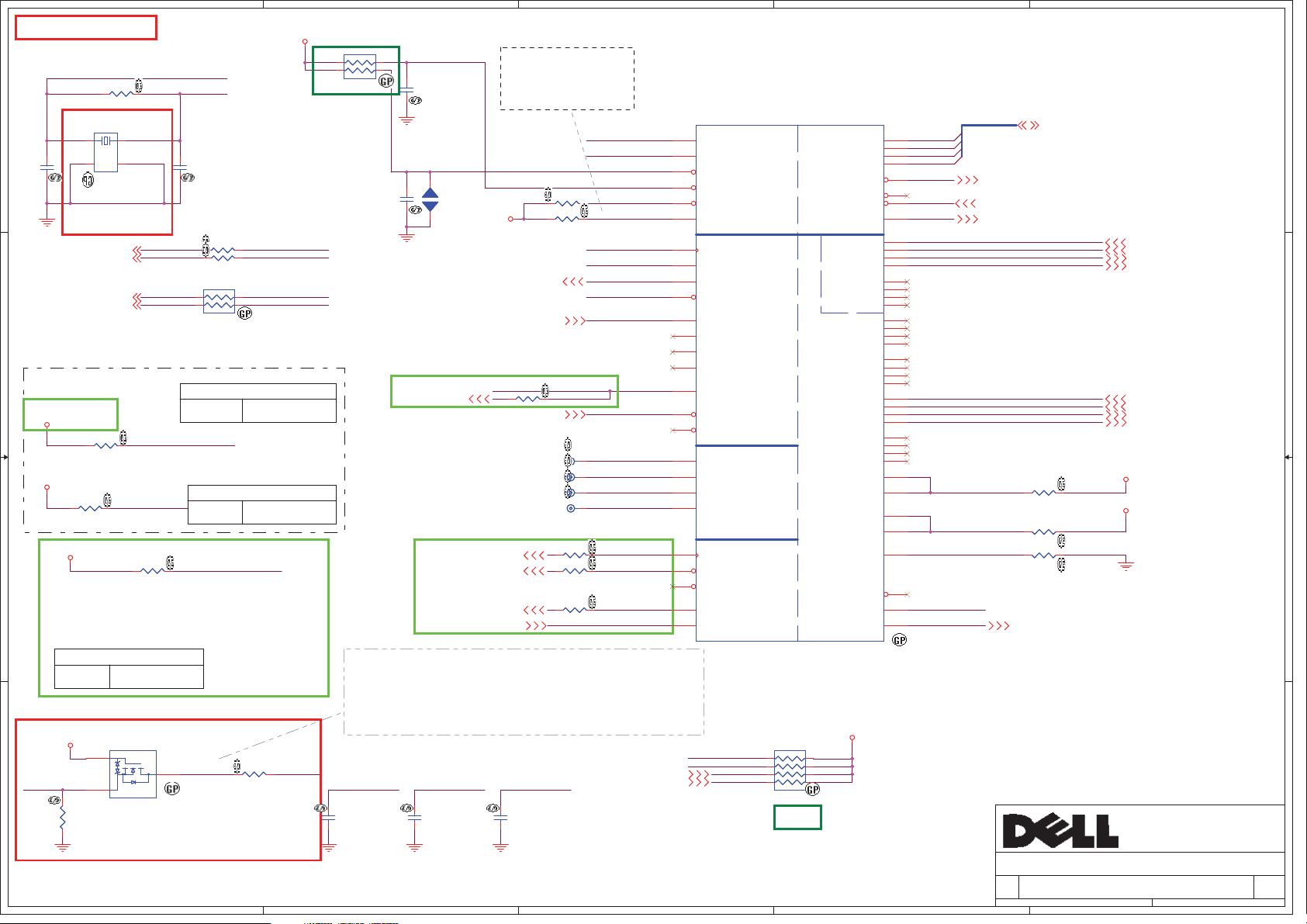

##OnMainBoard

4

VRAM

512MB/1GB Colay

D D

88,89

4

gDDR3

800MHz

NVIDIA

N12P-GV

83.84,85,86,87

C C

HDMI

Display Port

LCD

SD/SDIO/SDHC

/SDXC/MS/MS Pro

MSXC/MMC/xD

51

52

49

74

LVDS(Dual Channel)

Card Reader

RTS5209

PCIE x 1

32

(9 in 1)

CAMERA

B B

w/ Digital MIC

49

USB 2.0 x 1

CODEC

HP

58

MIC IN

58

A A

2CH SPEAKER

(2W/4ohm)

5

58

IDT

92HD87B1

4

3

DB13 DIS Block Diagram

Intel CPU

DDRIII 1066/1333 Channel A

Sandy Bridge

PCIe x 16

(Discrete only)

PCIE x 1

USB2.0 x 1

HDA

29

4

BGA Type

4,5,6,7,8,9,10,11,12,13

FDIx4x2

(UMA only)

PCH

Cougar Point

14 USB 2.0/1.1 ports

ETHERNET (10/100/1000Mb)

High Definition Audio

SATA ports (6)

PCIE ports (8)

17,18,19,20,21,22,23,24,25,26

SPI

Flash ROM

4MB

27

Touch

PAD

60

NUVOTON

NPCE795PA

69 69

DMIx4

Intel

LPC I/F

ACPI 1.1

SMBus

LPC Bus

KBC

ADC

PWM

Int.

KB

http://hobi-elektronika.net

DDRIII 1066/1333 Channel B

PCIE x 1

PCIE x 1

PCIE x 1,USB2.0 x 1

PCIE x 1,USB2.0 x 1

SATA x 2

Free Fall Sensor

Thermal Sensor

Main:ENEP2800

PWM x 1

3

79

28

25

Project Code: 91.4NY01.001

PCB P/N :48.4NY02.0SA

Revision : 10320-SA

10/100/1000 LOM

Realtek

RTL8111E-VB

USB3.0 Controller

TI TUSB7320RKM

(NEC uPD720200F1)

(On Daughter Board)

Mini-Card

WWAN

Mini-Card

802.11a/b/g +

BT version 3.0

PWM Fan

28

DDRIII

1066/1333

DDRIII

1066/1333

31

66

65

2

Slot 1

14

Slot 2

15

RJ45

CONN

35

(On Daughter Board)

HDD

ODD

USB3.0 x 2

SIM

56

56

2

1

CPU DC/DC

VT1316+VT1317

INPUTS

DCBATOUT

SYSTEM DC/DC

VT1316+VT1317

INPUTS

DCBATOUT

SYSTEM DC/DC

TPS51461

INPUTS

DCBATOUT

SYSTEM DC/DC

INPUTS

VT358

DCBATOUT

SYSTEM DC/DC

VT357

INPUTS

DCBATOUT

TI CHARGER

59

BQ24745

INPUTS

+DC_IN_S5

SYSTEM DC/DC

62

TPS51427

INPUTS

DCBATOUT 5V_S5

26

SYSTEM DC/DC

TPS51311

INPUTS

3D3V_S5

Switches

INPUTS OUTPUTS

1D5V_S3

5V_S5

PCB LAYER

DIS

L1:Top

L2:GND

L3:Signal

L4:Signal

L5:VCC

L6:Signal

L7:GND

L8:Bottom

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Friday, November 26, 2010

Friday, November 26, 2010

Friday, November 26, 2010

Taipei Hsien 221, Taiwan, R.O.C.

Block Diagram

Block Diagram

Block Diagram

DB13 DIS

DB13 DIS

DB13 DIS

1

OUTPUTS

VCC_CORE

OUTPUTS

VCC_GFXCORE

OUTPUTS

0D85V_S0

OUTPUTS

1D5V_S3

0D75V_S0

DDR_VREF_S3

OUTPUTS

1D05V_VTT

OUTPUTS

DCBATOUT+PBATT

OUTPUTS

5V_AUX_S5

3D3V_AUX_S5

3D3V_S5

15V_S5

OUTPUTS

1D8V_S0

1D5V_S0

5V_S0

3D3V_S03D3V_S5

of

of

of

2 105

2 105

2 105

42

44

48

46

45

40

41

47

36

X00

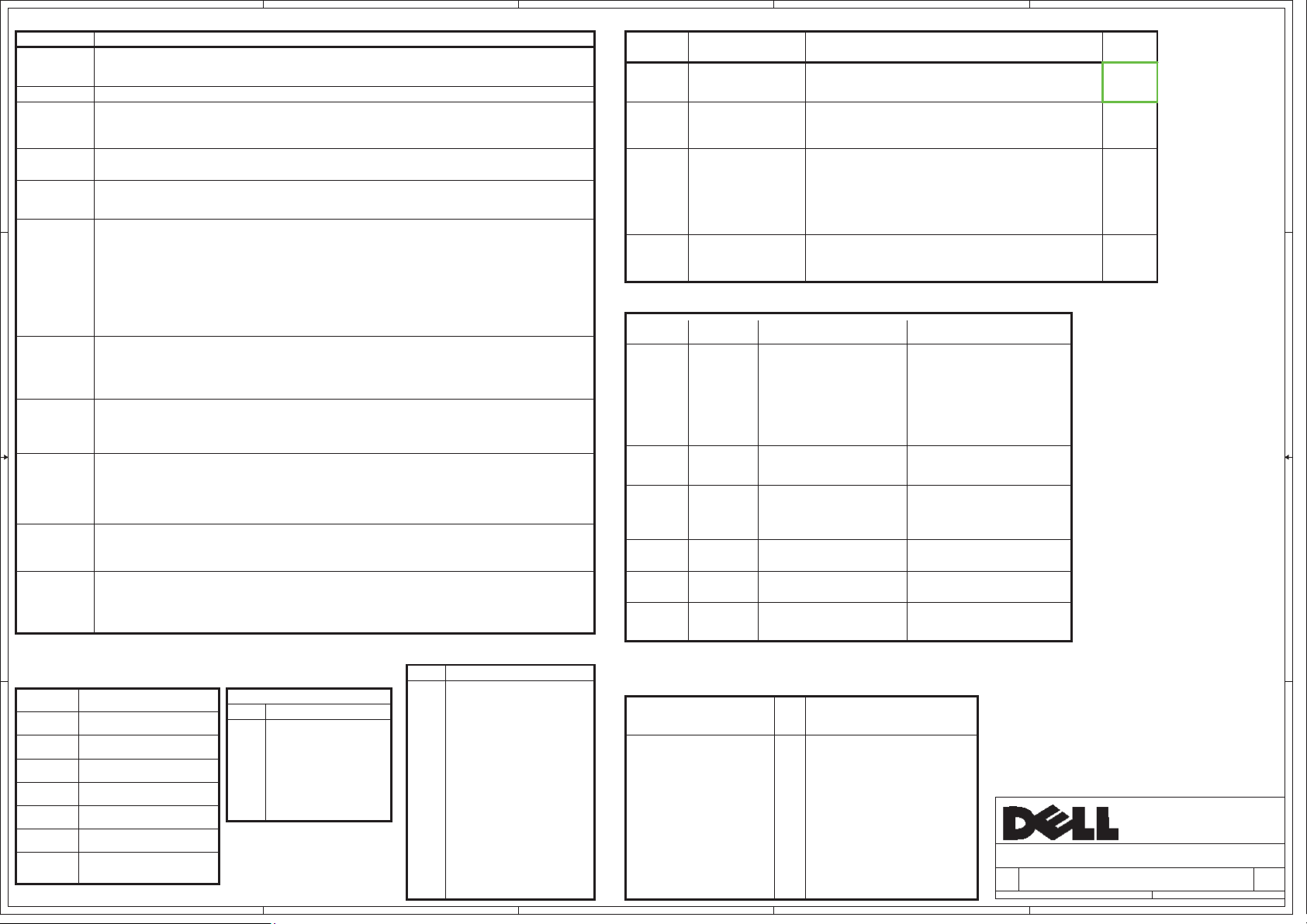

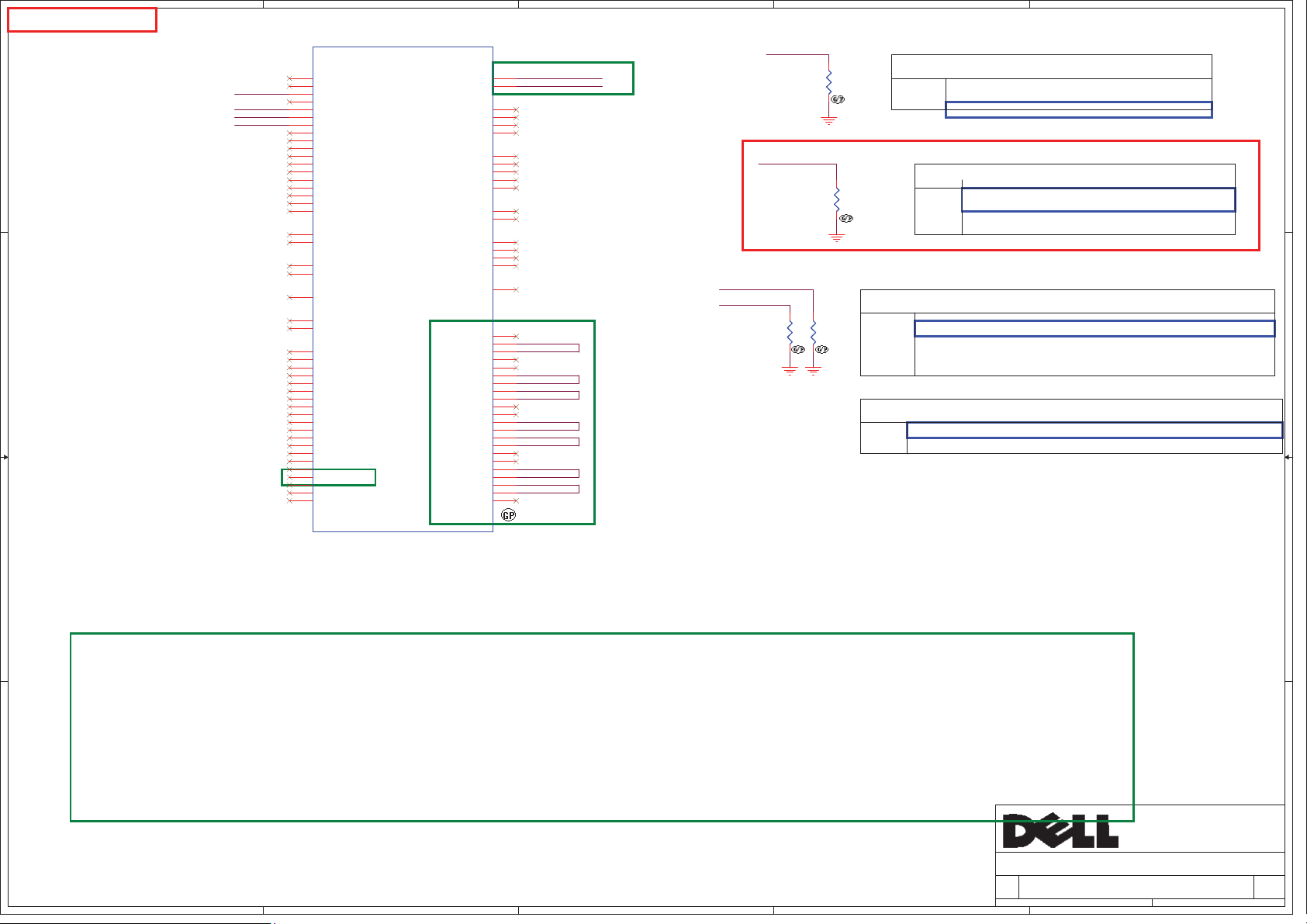

Page 3

5

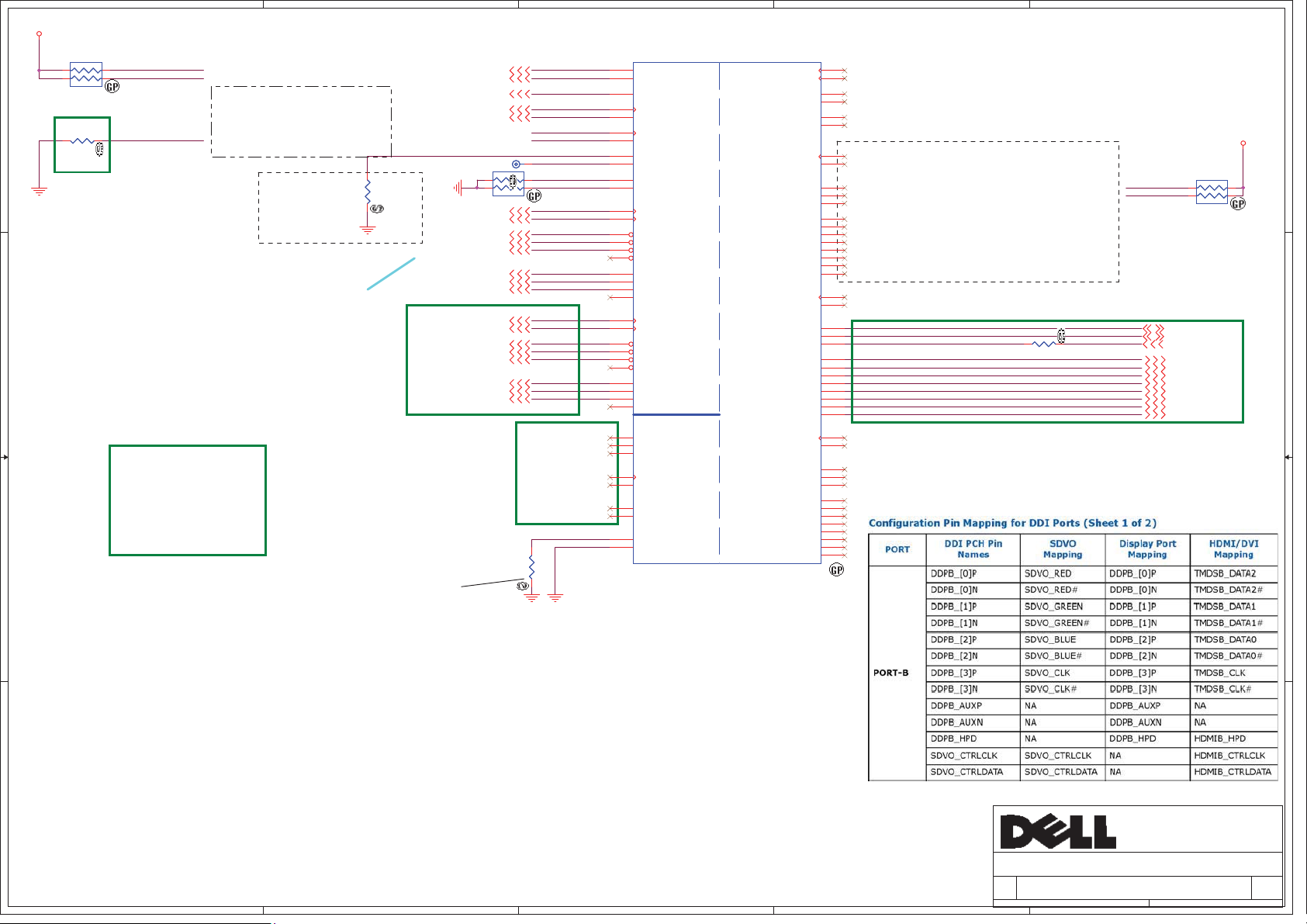

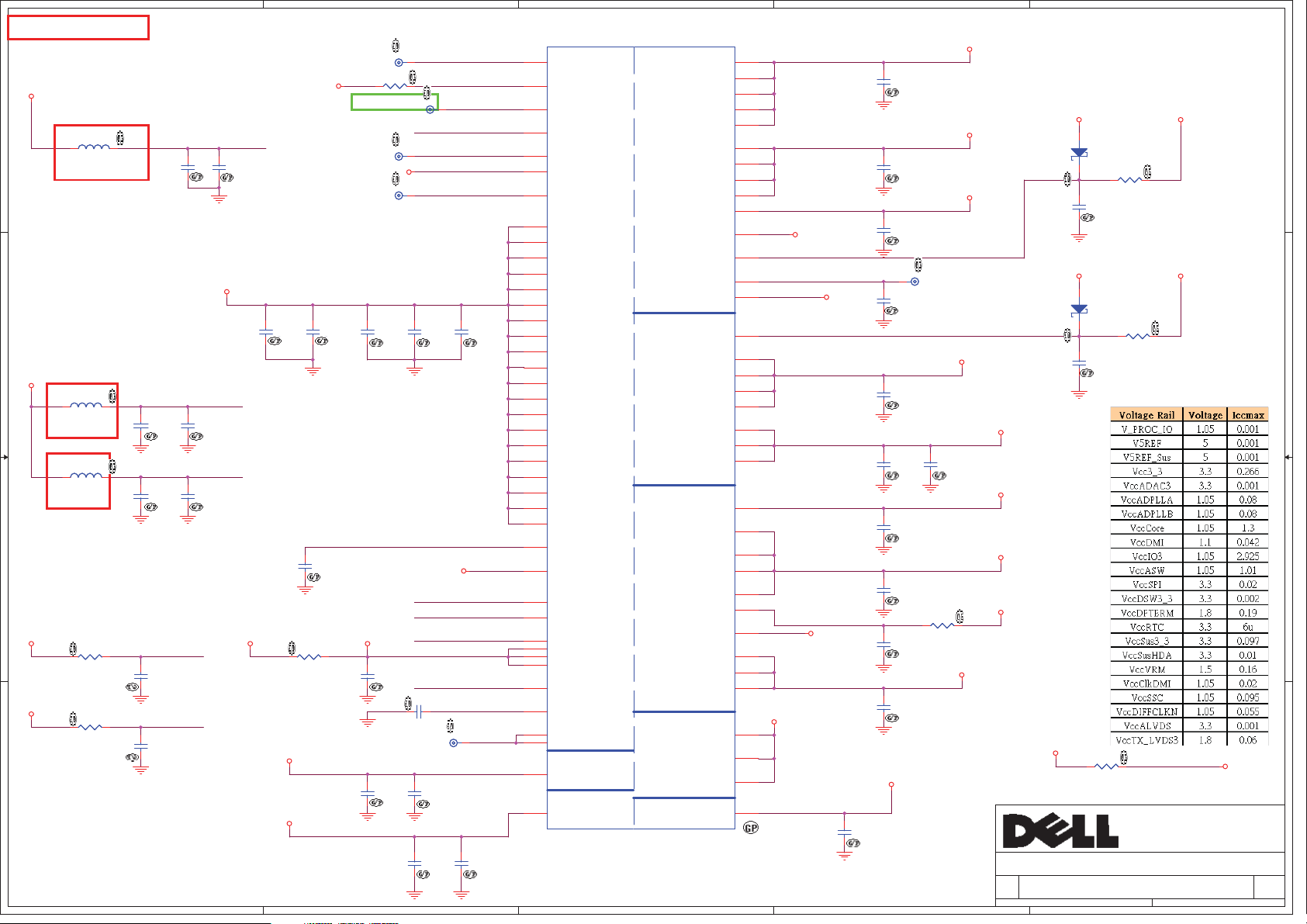

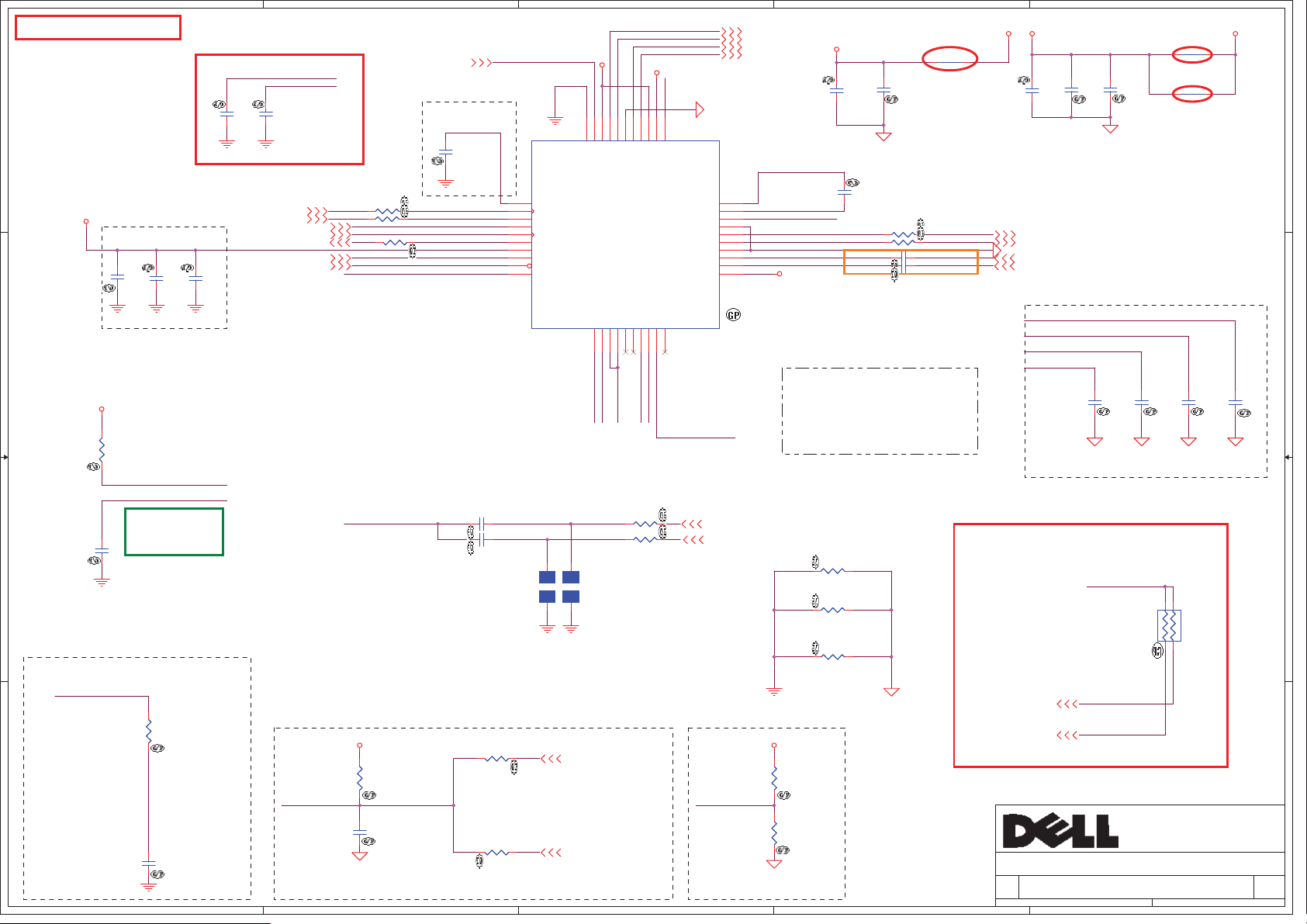

PCH Strapping

Huron River Schematic Checklist Rev.1_0

Name Schematics Notes

SPKR

INIT3_3V# Weak internal pull-up. This signal should not be pulled low. Leave as "No Connect".

GNT3#/GPIO55

D D

GNT2#/GPIO53

GNT1#/GPIO51

INTVRMEN

DF_TVS

SATA1GP

/GPIO19

C C

HDA_SDO

HDA_SYNC

GPIO15

DSWVRMEN

B B

GPIO28

Reboot option at power-up

Internal weak Pull-down.

Default Mode:

Enable when Pull-up.

No Reboot Mode with TCO Disabled:

GNT[3:0]# functionality is not available on Mobile.

Mobile: Used as GPIO only

Pull-up resistors are not required on these signals.

If pull-ups are used, they should be tied to the Vcc3_3 power rail.

Integrated 1.05 V VRM Enable / Disable

Integrated 1.05 V VRMs is enabled when high. This signal should always be pulled high

DMI and FDI Tx/Rx Termination Voltage

Weak internal pull-down. It needs to be connected to PROC_SELECT with a 1K±5% pull-up

resistor to PCH VCCPNAND rail and a 4.7K±5% series resistor.

Boot BIOS Strap bit 0

This Signal has a weak internal pull-up.

Note: This field determines the destination of accesses to the BIOS memory range.

This strap is used in conjunction with Boot BIOS

Destination Selection 1 strap.

Bit11 Bit 10 Boot BIOS Destination

0 1 Reserved

1 0 PCI

1 1 SPI

0 0 LPC

Signal has a weak internal pull-down.

Default: the security measures defined in the Flash Descriptor will be in effect.

Pull-up: the Flash Descriptor Security will be overridden.

This strap should only be asserted high via external pull-up in manufacturing

or debug environments ONLY.

On-Die PLL Voltage Regulator Voltage Select

This signal has a weak internal pull-down.

On Die PLL VR is supplied by 1.5 V when sampled high, 1.8 V when sampled low.

Needs to be pulled High for Huron River platform.

TLS Confidentiality

Low - Intel ME Crypto Transport Layer Security (TLS) cipher suite with no confidentiality

High - Intel ME Crypto Transport Layer Security (TLS) cipher suite with confidentiality

This signal has a weak internal pull-down.

NOTE: A strong pull-up may be needed for GPIO functionality

Deep S4/S5 Well On-Die Voltage Regulator Enable

This signal enables the internal Deep Sleep 1.05 V regulators.

This signal must be always pulled-up to VccRTC.

On-Die PLL Voltage Regulator

This signal has a weak internal pull-up.

The On-Die PLL voltage regulator is enabled when sampled high.

When sampled low the On-Die PLL Voltage Regulator is disabled.

If not used, 8.2-kȍ to 10-kȍ pull-up to +V3.3A power-rail.

4

3

Processor Strapping

Pin Name Strap Description Configuration (Default value for each bit is

CFG[2]

CFG[4]

CFG[6:5]

CFG[7]

POWER PLANE

5V_S0

3D3V_S0

1D8V_S0

1D5V_S0

1D05V_VTT

0D85V_S0

0D75V_S0

VCC_CORE

VCC_GFXCORE

5V_USBX_S3

1D5V_S3

DDR_VREF_S3

BT+

DCBATOUT

5V_S5

5V_AUX_S5

3D3V_S5

3D3V_AUX_S5

3D3V_AUX_KBC

3D3V_AUX_S5

PCI-Express Static

Lane Reversal

Display Port

Presence strap

PCI-Express

Port Bifurcation

Straps

PEG DEFER TRAINING

VOLTAGE DESCRIPTION

5V

3.3V

1.8V

1.5V

1.05V

0.95 - 0.85V

0.75V

0.35V to 1.5V

0.4 to 1.25V

5V

1.5V

0.75V

6V-14.1V

6V-14.1V

5V

5V

3.3V

3.3V

3.3V3D3V_LAN_S5

3.3V

3.3V

1 unless specified otherwise)

1:

Normal Operation.

Lane Numbers Reversed 15 -> 0, 14 -> 1, ...

0:

Disabled - No Physical Display Port attached to

1:

Embedded Display Port.

Enabled - An external Display Port device is

0:

connectd to the Embedded Display Port

11 : x16 - Device 1 functions 1 and 2 disabled

10 : x8, x8 - Device 1 function 1 enabled ;

function 2 disabled

01 : Reserved - (Device 1 function 1 disabled ;

function 2 enabled)

00 : x8, x4, x4 - Device 1 functions 1 and 2

enabled

1:

PEG Train immediately following xxRESETB de assertion

PEG Wait for BIOS for training

0:

Voltage Rails

ACTIVE IN

S0

S3

All S states

WOL_EN

DSW, Sx ON for supporting Deep Sleep states

G3, Sx

2

Huron River Schematic Checklist Rev.1_0

CPU Core Rail

Graphics Core Rail

AC Brick Mode only

Legacy WOL

Powered by Li Coin Cell in G3

and +V3ALW in Sx

Default

Value

0

1

11

1

1

USB Table

PCIE Routing

LANE1

LANE2

LANE3

LANE4

A A

LANE5

LANE6

LANE7

X

LAN (I/O Board)

Mini Card2(WWAN)

Mini Card1(WLAN)

USB3.0

Card Reader

X

SATA Table

SATA

Pair

0

1

2

3

4

5

Device

HDD1

N/A

N/A

N/A

ODD

N/A

LANE8 X

Pair

0

1

2

3

4

5

6

7

8

9

10

11

12

13

5

4

Device

X

X

X

X

Mini Card2 (WWAN)

X

X

X

X

X

X

Mini Card1 (WLAN)

CAMERA

X

http://hobi-elektronika.net

SMBus ADDRESSES

2

I C / SMBus Addresses

Device

EC SMBus 1

Battery

Capacity Board

EC SMBus 2

PCH

MXM

LCD

Thermal Sensor

PCH SMBus

CK505 Clock Generator

SO-DIMMA (SPD)

SO-DIMMB (SPD)

Digital Pot

3

HURON RIVER ORB

Address Hex Bus Ref Des

KBC_SDA1/KBC_SCL1

KBC_SDA1/KBC_SCL1

KBC_SDA2/KBC_SCL2

KBC_SDA2/KBC_SCL2

KBC_SDA2/KBC_SCL2

KBC_SDA2/KBC_SCL2

PCH_SMBDATA/PCH_SMBCLK

PCH_SMBDATA/PCH_SMBCLK

PCH_SMBDATA/PCH_SMBCLK

PCH_SMBDATA/PCH_SMBCLK

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

Table of Content

Table of Content

Table of Content

DB13 DIS

DB13 DIS

DB13 DIS

3 105Friday, November 26, 2010

3 105Friday, November 26, 2010

3 105Friday, November 26, 2010

1

of

of

of

X00

X00

X00

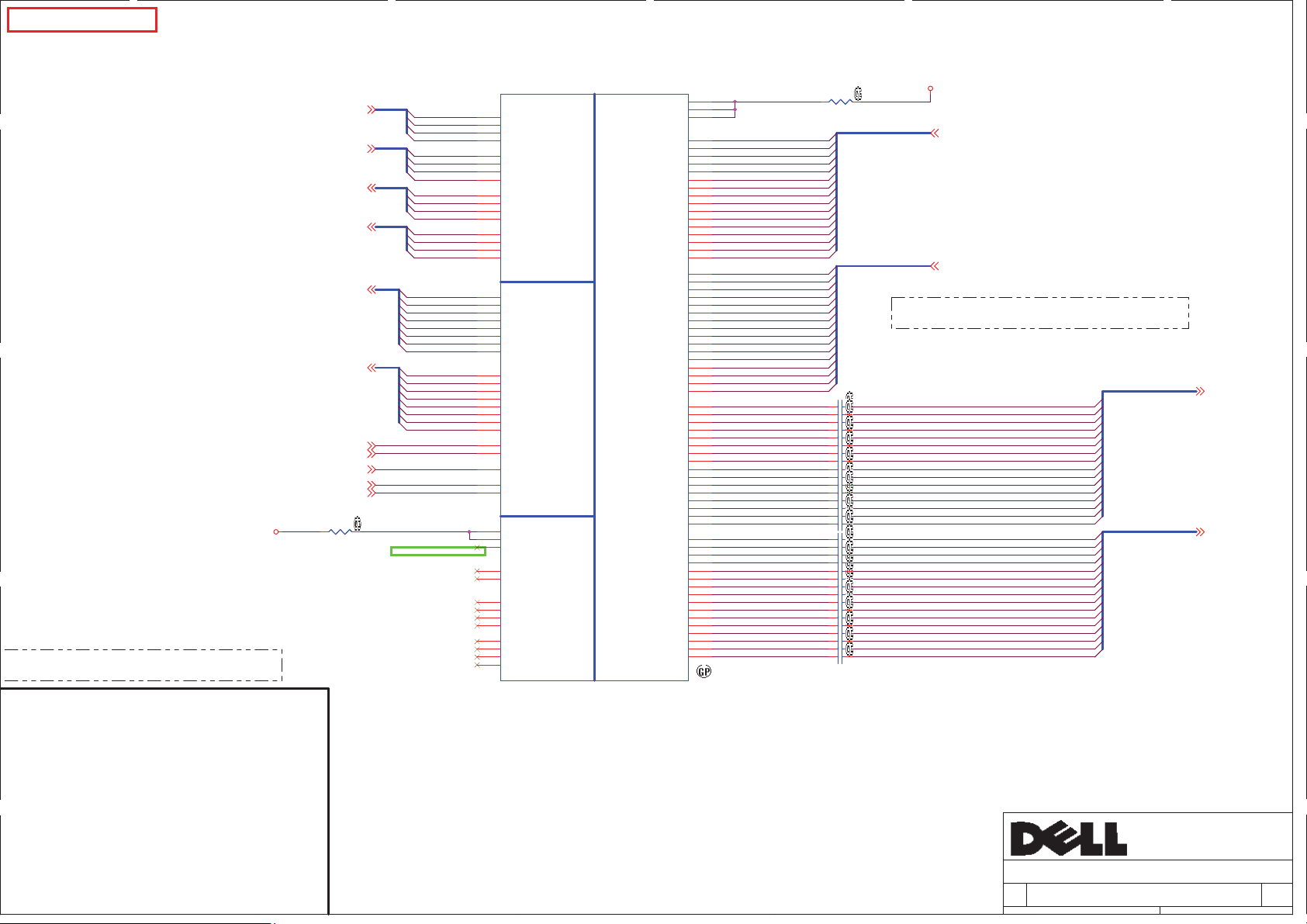

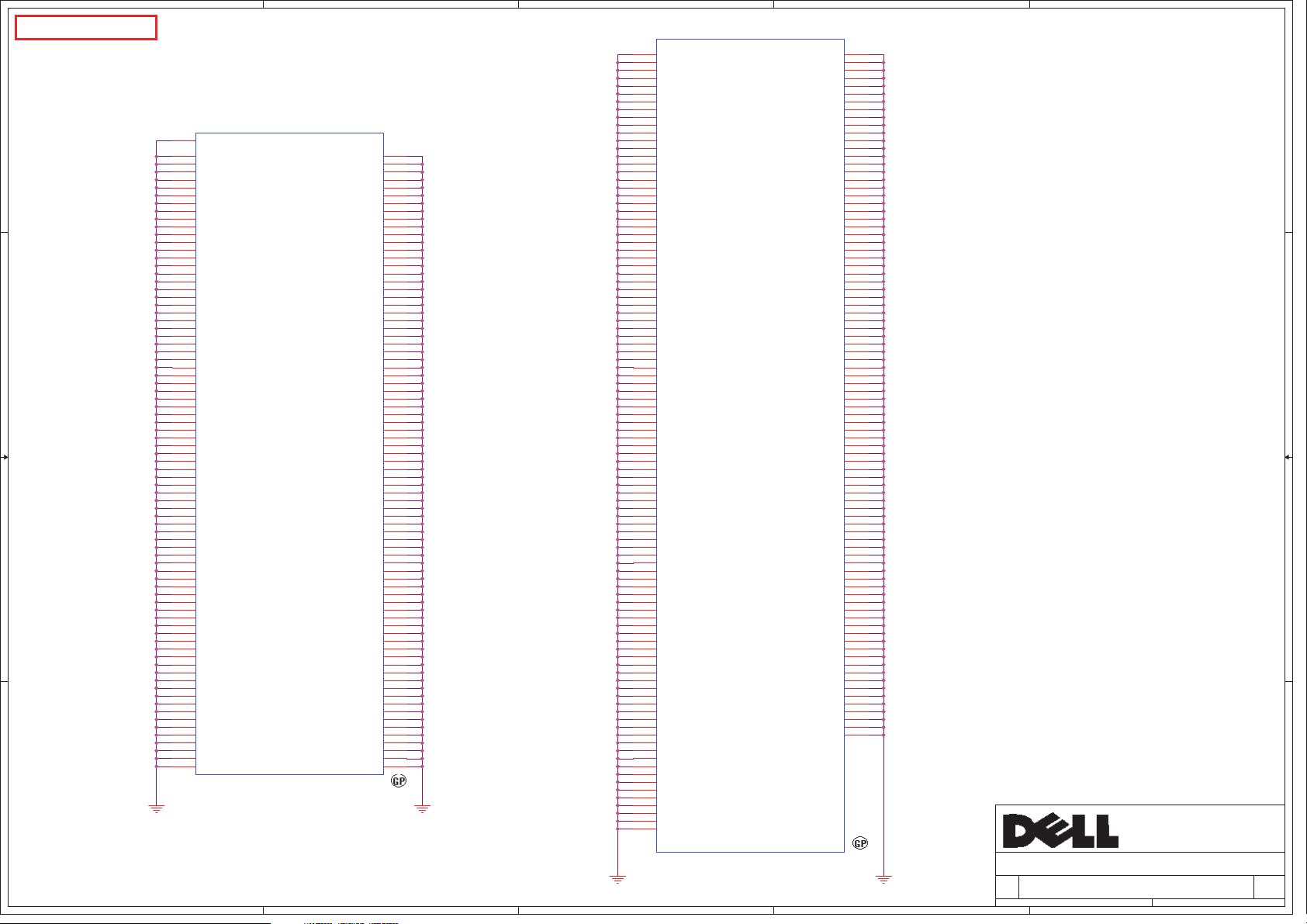

Page 4

5

4

3

2

1

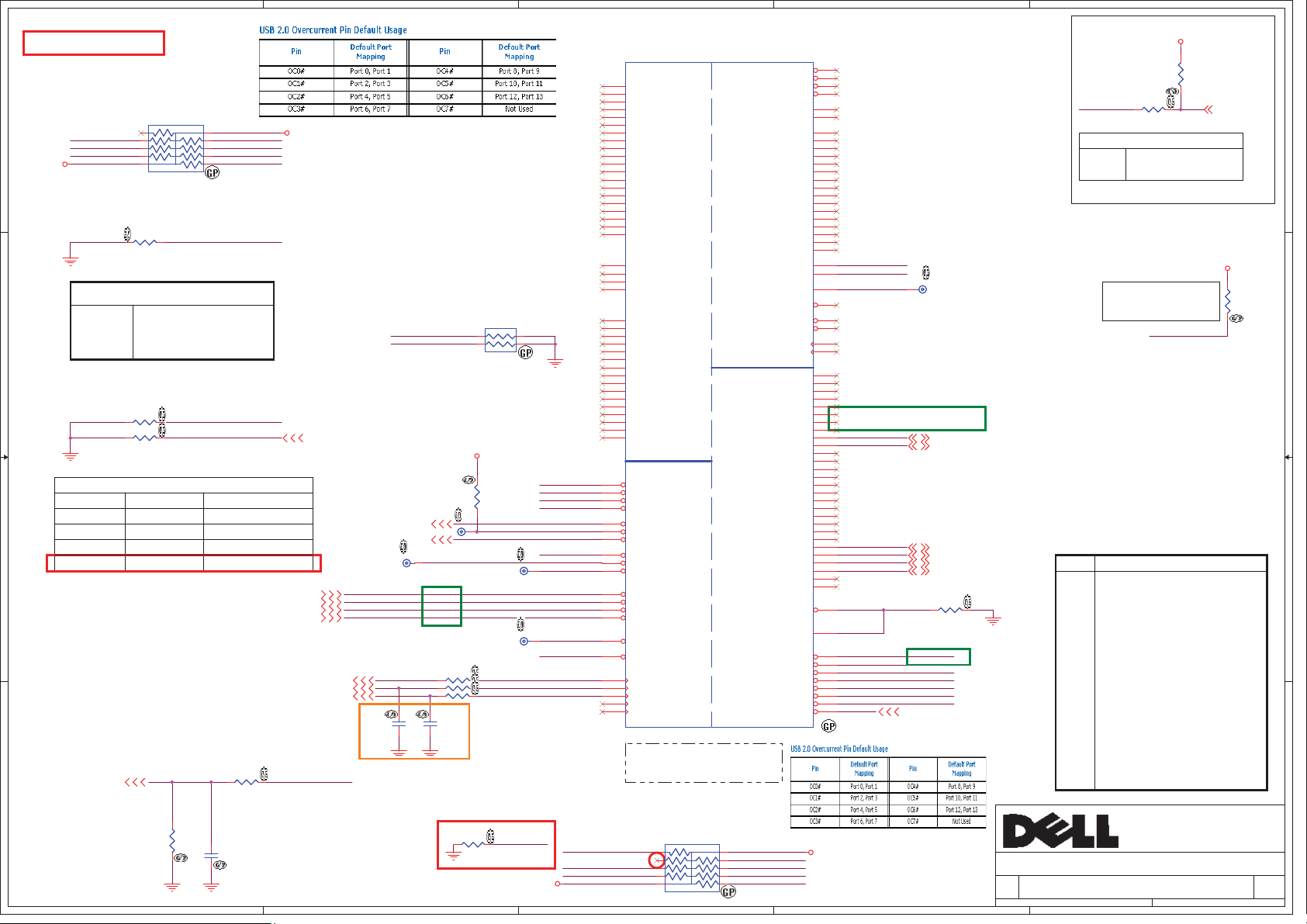

SSID = CPU

Signal Routing Guideline:

PEG_ICOMPO keep W/S=12/15 mils and routing length less than 500 mils.

PEG_ICOMPI & PEG_RCOMPO keep W/S=4/15 mils and routing length less than 500 mils.

1 OF 9

CPU1A

CPU1A

D D

C C

Note:

Intel DMI supports both Lane

Reversal and polarity inversion

but only at PCH side. This is

enabled via a soft strap.

Note:

Intel FDI supports both Lane

Reversal and polarity inversion

but only at PCH side. This is

enabled via a soft strap.

Note:

Lane reversal does not apply to

FDI sideband signals.

1D05V_VTT

DMI_TXN[3:0](19)

DMI_TXP[3:0](19)

DMI_RXN[3:0](19)

DMI_RXP[3:0](19)

FDI_TXN[7:0](19)

FDI_TXP[7:0](19)

FDI_FSYNC0(19)

FDI_FSYNC1(19)

FDI_INT(19)

FDI_LSYNC0(19)

FDI_LSYNC1(19)

R402 24D9R2F-L-GPR402 24D9R2F-L-GP

1 2

X00 1111 Del R403

B B

NOTE.

Processor strap CFG[4] should be pulled low to enable Embedded DisplayPort.

Signal Routing Guideline:

EDP_ICOMPO keep W/S=12/15 mils and routing

length less than 500 mils.

EDP_COMPIO keep W/S=4/15 mils and routing

length less than 500 mils.

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

DP_COMP

M2

DMI_RX#0

P6

DMI_RX#1

P1

DMI_RX#2

P10

DMI_RX#3

N3

DMI_RX0

P7

DMI_RX1

P3

DMI_RX2

P11

DMI_RX3

K1

DMI_TX#0

M8

DMI_TX#1

N4

DMI_TX#2

R2

DMI_TX#3

K3

DMI_TX0

M7

DMI_TX1

P4

DMI_TX2

T3

DMI_TX3

U7

FDI0_TX#0

W11

FDI0_TX#1

W1

FDI0_TX#2

AA6

FDI0_TX#3

W6

FDI1_TX#0

V4

FDI1_TX#1

Y2

FDI1_TX#2

AC9

FDI1_TX#3

U6

FDI0_TX0

W10

FDI0_TX1

W3

FDI0_TX2

AA7

FDI0_TX3

W7

FDI1_TX0

T4

FDI1_TX1

AA3

FDI1_TX2

AC8

FDI1_TX3

AA11

FDI0_FSYNC

AC12

FDI1_FSYNC

U11

FDI_INT

AA10

FDI0_LSYNC

AG8

FDI1_LSYNC

AF3

EDP_COMPIO

AD2

EDP_ICOMPO

AG11

EDP_HPD

AG4

EDP_AUX#

AF4

EDP_AUX

AC3

EDP_TX#0

AC4

EDP_TX#1

AE11

EDP_TX#2

AE7

EDP_TX#3

AC1

EDP_TX0

AA4

EDP_TX1

AE10

EDP_TX2

AE6

EDP_TX3

SANDYBRIDGE-1-GP-U-NF

SANDYBRIDGE-1-GP-U-NF

DMI

DMI

Intel(R) FDI

Intel(R) FDI

DP

DP

1 OF 9

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#0

PEG_RX#1

PEG_RX#2

PEG_RX#3

PEG_RX#4

PEG_RX#5

PEG_RX#6

PEG_RX#7

PEG_RX#8

PEG_RX#9

PEG_RX#10

PEG_RX#11

PEG_RX#12

PEG_RX#13

PEG_RX#14

PEG_RX#15

SANDYBRIDGE

SANDYBRIDGE

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

PEG_TX#0

PEG_TX#1

PEG_TX#2

PEG_TX#3

PEG_TX#4

PEG_TX#5

PEG_TX#6

PEG_TX#7

PEG_TX#8

PEG_TX#9

PEG_TX#10

PEG_TX#11

PEG_TX#12

PEG_TX#13

PEG_TX#14

PEG_TX#15

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

G3

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

PEG_IRCOMP_R

PEG_RXN15

PEG_RXN14

PEG_RXN13

PEG_RXN12

PEG_RXN11

PEG_RXN10

PEG_RXN9

PEG_RXN8

PEG_RXN7

PEG_RXN6

PEG_RXN5

PEG_RXN4

PEG_RXN3

PEG_RXN2

PEG_RXN1

PEG_RXN0

PEG_RXP15

PEG_RXP14

PEG_RXP13

PEG_RXP12

PEG_RXP11

PEG_RXP10

PEG_RXP9

PEG_RXP8

PEG_RXP7

PEG_RXP6

PEG_RXP5

PEG_RXP4

PEG_RXP3

PEG_RXP2

PEG_RXP1

PEG_RXP0

PEG_C_TXN15

PEG_C_TXN14

PEG_C_TXN13

PEG_C_TXN12

PEG_C_TXN11

PEG_C_TXN10

PEG_C_TXN9

PEG_C_TXN8

PEG_C_TXN7

PEG_C_TXN6

PEG_C_TXN5

PEG_C_TXN4

PEG_C_TXN3

PEG_C_TXN2

PEG_C_TXN1

PEG_C_TXN0

PEG_C_TXP15

PEG_C_TXP14

PEG_C_TXP13

PEG_C_TXP12

PEG_C_TXP11

PEG_C_TXP10

PEG_C_TXP9

PEG_C_TXP8

PEG_C_TXP7

PEG_C_TXP6

PEG_C_TXP5

PEG_C_TXP4

PEG_C_TXP3

PEG_C_TXP2

PEG_C_TXP1

PEG_C_TXP0

R401 24D9R2F-L-GPR401 24D9R2F-L-GP

1 2

PEG_RXN[0..15]

PEG_RXP[0..15]

C401 SCD22U10V2KX-1GPC401 SCD22U10V2KX-1GP

1 2

C402 SCD22U10V2KX-1GPC402 SCD22U10V2KX-1GP

1 2

C403 SCD22U10V2KX-1GPC403 SCD22U10V2KX-1GP

1 2

C404 SCD22U10V2KX-1GPC404 SCD22U10V2KX-1GP

1 2

C405 SCD22U10V2KX-1GPC405 SCD22U10V2KX-1GP

1 2

C406 SCD22U10V2KX-1GPC406 SCD22U10V2KX-1GP

1 2

C407 SCD22U10V2KX-1GPC407 SCD22U10V2KX-1GP

1 2

C408 SCD22U10V2KX-1GPC408 SCD22U10V2KX-1GP

1 2

C409 SCD22U10V2KX-1GPC409 SCD22U10V2KX-1GP

1 2

C410 SCD22U10V2KX-1GPC410 SCD22U10V2KX-1GP

1 2

C411 SCD22U10V2KX-1GPC411 SCD22U10V2KX-1GP

1 2

C412 SCD22U10V2KX-1GPC412 SCD22U10V2KX-1GP

1 2

C413 SCD22U10V2KX-1GPC413 SCD22U10V2KX-1GP

1 2

C414 SCD22U10V2KX-1GPC414 SCD22U10V2KX-1GP

1 2

C415 SCD22U10V2KX-1GPC415 SCD22U10V2KX-1GP

1 2

C416 SCD22U10V2KX-1GPC416 SCD22U10V2KX-1GP

1 2

C417 SCD22U10V2KX-1GPC417 SCD22U10V2KX-1GP

1 2

C418 SCD22U10V2KX-1GPC418 SCD22U10V2KX-1GP

1 2

C419 SCD22U10V2KX-1GPC419 SCD22U10V2KX-1GP

1 2

C420 SCD22U10V2KX-1GPC420 SCD22U10V2KX-1GP

1 2

C421 SCD22U10V2KX-1GPC421 SCD22U10V2KX-1GP

1 2

C422 SCD22U10V2KX-1GPC422 SCD22U10V2KX-1GP

1 2

C423 SCD22U10V2KX-1GPC423 SCD22U10V2KX-1GP

1 2

C424 SCD22U10V2KX-1GPC424 SCD22U10V2KX-1GP

1 2

C425 SCD22U10V2KX-1GPC425 SCD22U10V2KX-1GP

1 2

C426 SCD22U10V2KX-1GPC426 SCD22U10V2KX-1GP

1 2

C427 SCD22U10V2KX-1GPC427 SCD22U10V2KX-1GP

1 2

C428 SCD22U10V2KX-1GPC428 SCD22U10V2KX-1GP

1 2

C429 SCD22U10V2KX-1GPC429 SCD22U10V2KX-1GP

1 2

C430 SCD22U10V2KX-1GPC430 SCD22U10V2KX-1GP

1 2

C431 SCD22U10V2KX-1GPC431 SCD22U10V2KX-1GP

1 2

C432 SCD22U10V2KX-1GPC432 SCD22U10V2KX-1GP

1 2

1D05V_VTT

PEG_RXN[0..15] (83)

PEG_RXP[0..15] (83)

NOTE.

If PEG is not implemented, the RX&TX pairs can be left as No Connect

PEG_TXN[0..15]

PEG_TXN15

PEG_TXN14

PEG_TXN13

PEG_TXN12

PEG_TXN11

PEG_TXN10

PEG_TXN9

PEG_TXN8

PEG_TXN7

PEG_TXN6

PEG_TXN5

PEG_TXN4

PEG_TXN3

PEG_TXN2

PEG_TXN1

PEG_TXN0

PEG_TXP15

PEG_TXP14

PEG_TXP13

PEG_TXP12

PEG_TXP11

PEG_TXP10

PEG_TXP9

PEG_TXP8

PEG_TXP7

PEG_TXP6

PEG_TXP5

PEG_TXP4

PEG_TXP3

PEG_TXP2

PEG_TXP1

PEG_TXP0

PEG_TXP[0..15]

PEG_TXN[0..15] (83)

PEG_TXP[0..15] (83)

Stuff to disable internal graphics

function for power saving.

<Core Design>

<Core Design>

A A

http://hobi-elektronika.net

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU 1/7(PEG/DMI/FDI/eDP)

CPU 1/7(PEG/DMI/FDI/eDP)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

CPU 1/7(PEG/DMI/FDI/eDP)

Taipei Hsien 221, Taiwan, R.O.C.

DB13 DIS

DB13 DIS

DB13 DIS

of

4 105Friday, November 26, 2010

of

4 105Friday, November 26, 2010

of

4 105Friday, November 26, 2010

X00

X00

X00

Page 5

5

SSID = CPU

1D05V_VTT

R501

D D

C C

7,31,32,35,65,66,71,83)

R501

1 2

62R2J-GP

62R2J-GP

H_PROCHOT#

CRB : 47pf

CEKLT:43pf

R503

R503

1 2

PLT_RST#

12

C502

C502

SC47P50V2JN-3GP

SC47P50V2JN-3GP

Connect EC to PROCHOT# through inverting OD buffer.

10KR2J-3-GP

10KR2J-3-GP

1 2

1K5R2F-2-GP

1K5R2F-2-GP

EDS R1.5:

BGA have different name with rPGA

X00 1008

H_SNB_IVB#(18)

TP501TPAD14-GP TP501TPAD14-GP

TP502TPAD14-GP TP502TPAD14-GP

H_PECI(22,27)

H_PROCHOT#(27,40,42)

H_THERMTRIP#(22,36)

H_CPUPWRGD_R

H_PM_SYNC(19)

H_CPUPWRGD(22,36)

PM_DRAM_PWRGD(19,37)

VDDPWRGOOD(37)

R510

R510

12

R509

R509

750R2F-GP

750R2F-GP

1

1

R513

R513

1 2

56R2J-4-GP

56R2J-4-GP

20100923 X01 Modify:

Change R504 to 0R0402

short pad from 0ohm.

R504

R504

1 2

0R0402-PAD

0R0402-PAD

R505

R505

1 2

DY

DY

12

C501

C501

DY

DY

SC220P50V2KX-3GP

SC220P50V2KX-3GP

SKTOCC#_R

H_CATERR#

H_PROCHOT#_R

H_CPUPWRGD_R

VDDPWRGOOD

0R2J-2-GP

0R2J-2-GP

BUF_CPU_RST#

4

CPU1B

CPU1B

MISC

MISC

F49

PROC_SELECT#

C57

PROC_DETECT#

C49

CATERR#

A48

PECI

C45

PROCHOT#

D45

THERMTRIP#

C48

PM_SYNC

B46

UNCOREPWRGOOD

BE45

SM_DRAMPWROK

D44

RESET#

SANDYBRIDGE-1-GP-U-NF

SANDYBRIDGE-1-GP-U-NF

THERMAL

THERMAL

SANDYBRIDGE

SANDYBRIDGE

PWR MANAGEMENT

PWR MANAGEMENT

3

2 OF 9

2 OF 9

BCLK

BCLK#

DPLL_REF_CLK

DPLL_REF_CLK#

MISC

MISC

BCLK_ITP

BCLK_ITP#

SM_DRAMRST#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

PRDY#

PREQ#

TCK

TMS

TRST#

TDO

DBR#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

TDI

CLOCKS

CLOCKS

DDR3

DDR3

JTAG & BPM

JTAG & BPM

J3

H2

AG3

AG1

N59

N58

AT30

BF44

BE43

BG43

N53

N55

L56

L55

J58

M60

L59

K58

G58

E55

E59

G55

G59

H60

J59

J61

CLK_DP_P_R

CLK_DP_N_R

TEST_ITP

TEST_ITP#

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

XDP_PRDY#

XDP_PREQ#

XDP_TCLK

XDP_TMS

XDP_TRST#

XDP_TDI

XDP_TDO

XDP_DBRESET#

XDP_BPM0

XDP_BPM1

XDP_BPM2

XDP_BPM3

XDP_BPM4

XDP_BPM5

XDP_BPM6

XDP_BPM7

R512

R512

1 2

1KR2J-1-GP

1KR2J-1-GP

R514

R514

1 2

1KR2J-1-GP

1KR2J-1-GP

1

TP513 TPAD14-GPTP513 TPAD14-GP

1

TP514 TPAD14-GPTP514 TPAD14-GP

R502

R502

1 2

4K99R2F-L-GP

4K99R2F-L-GP

R506 140R2F-GPR506 140R2F-GP

1 2

R507 25D5R2F-GPR507 25D5R2F-GP

1 2

R508 200R2F-L-GPR508 200R2F-L-GP

1 2

1

TP511 TPAD14-GPTP511 TPAD14-GP

1

TP512 TPAD14-GPTP512 TPAD14-GP

XDP_DBRESET# (19)

1

1

1

1

1

1

1

1

2

CLK_EXP_P (20)

CLK_EXP_N (20)

1D05V_VTT

X00 1011

SM_DRAMRST# (37)

TP503 TPAD14-GPTP503 TPAD14-GP

TP504 TPAD14-GPTP504 TPAD14-GP

TP505 TPAD14-GPTP505 TPAD14-GP

TP506 TPAD14-GPTP506 TPAD14-GP

TP507 TPAD14-GPTP507 TPAD14-GP

TP508 TPAD14-GPTP508 TPAD14-GP

TP509 TPAD14-GPTP509 TPAD14-GP

TP510 TPAD14-GPTP510 TPAD14-GP

Disabling Guidelines:

If motherboard only supports external graphics:

Connect DPLL_REF_SSCLK on Processor to GND through

1K +/- 5% resistor.

Connect DPLL_REF_SSCLK# on Processor to VCCP

through 1K +/- 5% resistorpower (~15 mW) may be

wasted.

Signal Routing Guideline:

SM_RCOMP keep routing length less than 500 mils.

1

X00 1011

X00 1011

XDP_TDI

XDP_TMS

XDP_TDO

XDP_TCLK

XDP_TRST#

RN501

RN501

1

8

2

7

3

6

4 5

SRN51J-1-GP

SRN51J-1-GP

R511 51R2J-2-GPR511 51R2J-2-GP

1 2

1D05V_VTT

3D3V_S0

XDP_DBRESET#

B B

DY

DY

VCC

1D05V_VTT

DY

DY

5

4

12

R518

R518

75R2J-1-GP

75R2J-1-GP

3D3V_S0

12

C503

C503

DY

DY

SCD1U10V2KX-5GP

SCD1U10V2KX-5GP

1 2

DY

DY

R517 43R2J-GP

R517 43R2J-GP

DY

DY

12

0R2J-2-GP

0R2J-2-GP

BUF_CPU_RST#BUFO_CPU_RST#

R515

R515

0617 Modify:Joseph Removed U501 Buffer reset to CPU circuit.

2010/07/19 Add buffer for PLT_RST# based on Intel review.

2010/07/20 DY buffer circuit and add R510, R509 and C501

2010/07/20 Change U501 to 73.01G09.AAH

Buffered reset to CPU

U501

U501

1

IN B

A A

PLT_RST#(18,27,31,32,35,65,66,71,83)

2

IN A

GND3OUT Y

74VHC1G09DFT2G-GP

74VHC1G09DFT2G-GP

73.01G09.AAH

73.01G09.AAH

http://hobi-elektronika.net

For XDP connector no enough space 6/28

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

CPU 2/7(THERMAL/CLOCK/PM )

CPU 2/7(THERMAL/CLOCK/PM )

CPU 2/7(THERMAL/CLOCK/PM )

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

1 2

20100722 Modify:

Change R516 10K from 1K

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

DB13 DIS

DB13 DIS

DB13 DIS

R516

R516

10KR2J-3-GP

10KR2J-3-GP

5 105Friday, November 26, 2010

5 105Friday, November 26, 2010

5 105Friday, November 26, 2010

X00

X00

of

of

of

X00

Page 6

5

SSID = CPU

4

3

2

1

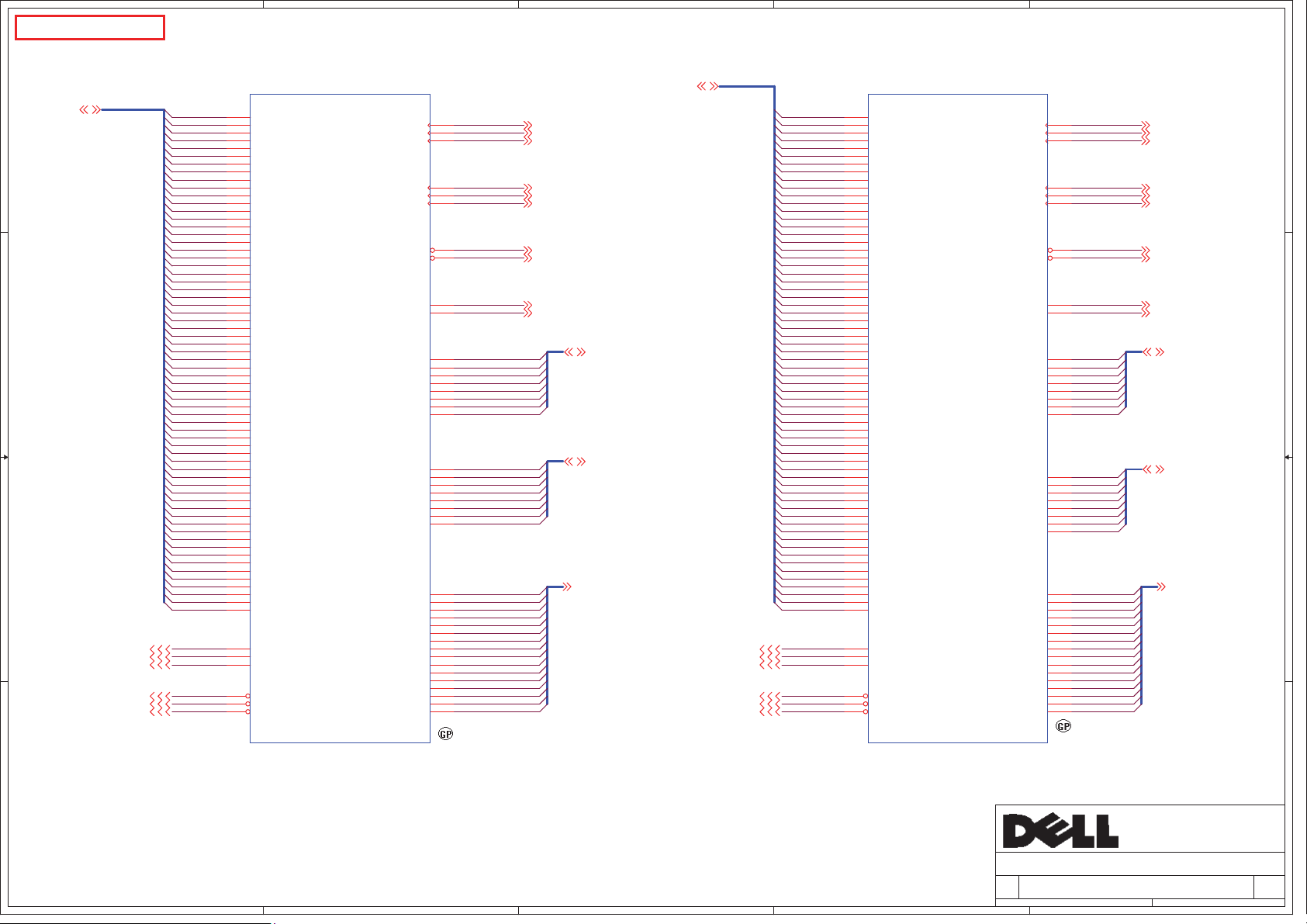

3 OF 9

CPU1C

M_A_DQ[63:0](14)

D D

C C

B B

M_A_DQ[63:0]

M_A_BS0(14)

M_A_BS1(14)

M_A_BS2(14)

M_A_CAS#(14)

M_A_RAS#(14)

M_A_WE#(14)

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AG6

AP11

AJ10

AR11

AP6

AU6

AV9

AR6

AP8

AT13

AU13

BC7

BB7

BA13

BB11

BA7

BA9

BB9

AY13

AV14

AR14

AY17

AR19

BA14

AU14

BB14

BB17

BA45

AR43

AW48

BC48

BC45

AR45

AT48

AY48

BA49

AV49

BB51

AY53

BB49

AU49

BA53

BB55

BA55

AV56

AP50

AP53

AV54

AT54

AP56

AP52

AN57

AN53

AG56

AG53

AN55

AN52

AG55

AK56

BD37

BF36

BA28

BE39

BD39

AT41

CPU1C

SA_DQ0

AJ6

SA_DQ1

SA_DQ2

AL6

SA_DQ3

SA_DQ4

AJ8

SA_DQ5

AL8

SA_DQ6

AL7

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SA_BS0

SA_BS1

SA_BS2

SA_CAS#

SA_RAS#

SA_WE#

SANDYBRIDGE

SANDYBRIDGE

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

3 OF 9

SA_CLK0

SA_CLK#0

SA_CKE0

SA_CLK1

SA_CLK#1

SA_CKE1

SA_CS#0

SA_CS#1

SA_ODT0

SA_ODT1

SA_DQS#0

SA_DQS#1

SA_DQS#2

SA_DQS#3

SA_DQS#4

SA_DQS#5

SA_DQS#6

SA_DQS#7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

AU36

AV36

AY26

AT40

AU40

BB26

BB40

BC41

AY40

BA41

AL11

AR8

AV11

AT17

AV45

AY51

AT55

AK55

AJ11

AR10

AY11

AU17

AW45

AV51

AT56

AK54

BG35

BB34

BE35

BD35

AT34

AU34

BB32

AT32

AY32

AV32

BE37

BA30

BC30

AW41

AY28

AU26

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DIM0_CLK_DDR0 (14)

M_A_DIM0_CLK_DDR#0 (14)

M_A_DIM0_CKE0 (14)

M_A_DIM0_CLK_DDR1 (14)

M_A_DIM0_CLK_DDR#1 (14)

M_A_DIM0_CKE1 (14)

M_A_DIM0_CS#0 (14)

M_A_DIM0_CS#1 (14)

M_A_DIM0_ODT0 (14)

M_A_DIM0_ODT1 (14)

M_A_DQS#[7:0] (14)

M_A_DQS[7:0] (14)

M_A_A[15:0] (14)

M_B_DQ[63:0](15)

M_B_DQ[63:0]

M_B_BS0(15)

M_B_BS1(15)

M_B_BS2(15)

M_B_CAS#(15)

M_B_RAS#(15)

M_B_WE#(15)

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AN3

AR4

AK4

AK3

AN4

AR1

AU4

AT2

AV4

BA4

AU3

AR3

AY2

BA3

BE9

BD9

BD13

BF12

BF8

BD10

BD14

BE13

BF16

BE17

BE18

BE21

BE14

BG14

BG18

BF19

BD50

BF48

BD53

BF52

BD49

BE49

BD54

BE53

BF56

BE57

BC59

AY60

BE54

BG54

BA58

AW59

AW58

AU58

AN61

AN59

AU59

AU61

AN58

AR58

AK58

AL58

AG58

AG59

AM60

AL59

AF61

AH60

BG39

BD42

AT22

AV43

BF40

BD45

4 OF 9

CPU1D

CPU1D

AL4

SB_DQ0

AL1

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

SB_BS0

SB_BS1

SB_BS2

SB_CAS#

SB_RAS#

SB_WE#

SANDYBRIDGE

SANDYBRIDGE

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

4 OF 9

SB_CLK0

SB_CLK#0

SB_CKE0

SB_CLK1

SB_CLK#1

SB_CKE1

SB_CS#0

SB_CS#1

SB_ODT0

SB_ODT1

SB_DQS#0

SB_DQS#1

SB_DQS#2

SB_DQS#3

SB_DQS#4

SB_DQS#5

SB_DQS#6

SB_DQS#7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

BA34

AY34

AR22

BA36

BB36

BF27

BE41

BE47

AT43

BG47

AL3

AV3

BG11

BD17

BG51

BA59

AT60

AK59

AM2

AV1

BE11

BD18

BE51

BA61

AR59

AK61

BF32

BE33

BD33

AU30

BD30

AV30

BG30

BD29

BE30

BE28

BD43

AT28

AV28

BD46

AT26

AU22

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DIM0_CLK_DDR0 (15)

M_B_DIM0_CLK_DDR#0 (15)

M_B_DIM0_CKE0 (15)

M_B_DIM0_CLK_DDR1 (15)

M_B_DIM0_CLK_DDR#1 (15)

M_B_DIM0_CKE1 (15)

M_B_DIM0_CS#0 (15)

M_B_DIM0_CS#1 (15)

M_B_DIM0_ODT0 (15)

M_B_DIM0_ODT1 (15)

M_B_DQS#[7:0] (15)

M_B_DQS[7:0] (15)

M_B_A[15:0] (15)

SANDYBRIDGE-1-GP-U-NF

SANDYBRIDGE-1-GP-U-NF

A A

5

4

http://hobi-elektronika.net

3

SANDYBRIDGE-1-GP-U-NF

SANDYBRIDGE-1-GP-U-NF

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

CPU 3/7(DDR)

CPU 3/7(DDR)

CPU 3/7(DDR)

DB13 DIS

DB13 DIS

DB13 DIS

1

of

6 105Friday, November 26, 2010

of

6 105Friday, November 26, 2010

of

6 105Friday, November 26, 2010

X00

X00

X00

Page 7

5

4

3

2

1

SSID = CPU

BGA pin out modify

5 OF 9

CPU1E

X00 1011

CFG2

CFG4

CFG5

D D

C C

CFG6

Remove to Page 8, BGA pin out

X00 1011

CPU1E

B50

CFG0

C51

CFG1

B54

CFG2

D53

CFG3

A51

CFG4

C53

CFG5

C55

CFG6

H49

CFG7

A55

CFG8

H51

CFG9

K49

CFG10

K53

CFG11

F53

CFG12

G53

CFG13

L51

CFG14

F51

CFG15

D52

CFG16

L53

CFG17

H43

VCC_VAL_SENSE

K43

VSS_VAL_SENSE

H45

VAXG_VAL_SENSE

K45

VSSAXG_VAL_SENSE

F48

VCC_DIE_SENSE

H48

RSVD#H48

K48

RSVD#K48

BA19

RSVD#BA19

AV19

RSVD#AV19

AT21

RSVD#AT21

BB21

RSVD#BB21

BB19

RSVD#BB19

AY21

RSVD#AY21

BA22

RSVD#BA22

AY22

RSVD#AY22

AU19

RSVD#AU19

AU21

RSVD#AU21

BD21

RSVD#BD21

BD22

RSVD#BD22

BD25

RSVD#BD25

BD26

RSVD#BD26

BG22

RSVD#BG22

BE22

RSVD#BE22

BG26

RSVD#BG26

BE26

RSVD#BE26

BF23

RSVD#BF23

BE24

RSVD#BE24

SANDYBRIDGE

SANDYBRIDGE

RESERVED

RESERVED

5 OF 9

RSVD#BE7

RSVD#BG7

RSVD#N42

RSVD#L42

RSVD#L45

RSVD#L47

RSVD#M13

RSVD#M14

RSVD#U14

RSVD#W14

RSVD#P13

RSVD#AT49

RSVD#K24

RSVD#AH2

RSVD#AG13

RSVD#AM14

RSVD#AM15

RSVD#N50

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

X00 1116 remove M3

M_VREF_DQ_DIMM0_C

BE7

M_VREF_DQ_DIMM1_C

BG7

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

N50

A4

DC_TEST_C4D3

C4

D3

D1

A58

DC_TEST_A59C59

A59

C59

DC_TEST_A61C61

A61

C61

D61

BD61

DC_TEST_BE61BE59

BE61

BE59

DC_TEST_BG61BG59

BG61

BG59

BG58

BG4

DC_TEST_BG3BE3

BG3

BE3

DC_TEST_BE1BG1

BG1

BE1

BD1

CFG5

CFG6

CFG4

CFG2

DY

DY

12

R701

R701

DY

DY

1KR2J-1-GP

1KR2J-1-GP

12

12

DY

DY

12

R702

R702

1KR2J-1-GP

1KR2J-1-GP

R703

R703

3K3R2F-2-GP

3K3R2F-2-GP

PEG Static Lane Reversal

CFG2

PCIE Port Bifurcation Straps

R704

R704

1KR2J-1-GP

1KR2J-1-GP

CFG[6:5]

11: x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2 disabled

01: Reserved - (Device 1 function 1 disabled ; function 2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

PEG DEFER TRAINING

CFG7

1: PEG Train immediately following xxRESETB de assertion

0: PEG Wait for BIOS for training

1: Normal Operation; Lane #

definition matches socket pin map definition

0:Lane Reversed

Display Port Presence Strap

CFG4

1: Disabled; No Physical Display Port

attached to Embedded Display Port

0: Enabled; An external Display Port device is

connected to the Embedded Display Port

SANDYBRIDGE-1-GP-U-NF

SANDYBRIDGE-1-GP-U-NF

B B

Intel CRB

X00 1011

X00 2010-11-16 Remove M3 - Processor Generated SO-DIMM VREF_DQ

A A

5

4

http://hobi-elektronika.net

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU 4/7(RESERVED)

CPU 4/7(RESERVED)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

CPU 4/7(RESERVED)

DB13 DIS

DB13 DIS

DB13 DIS

Taipei Hsien 221, Taiwan, R.O.C.

of

7 105Friday, November 26, 2010

of

7 105Friday, November 26, 2010

of

7 105Friday, November 26, 2010

1

X00

X00

X00

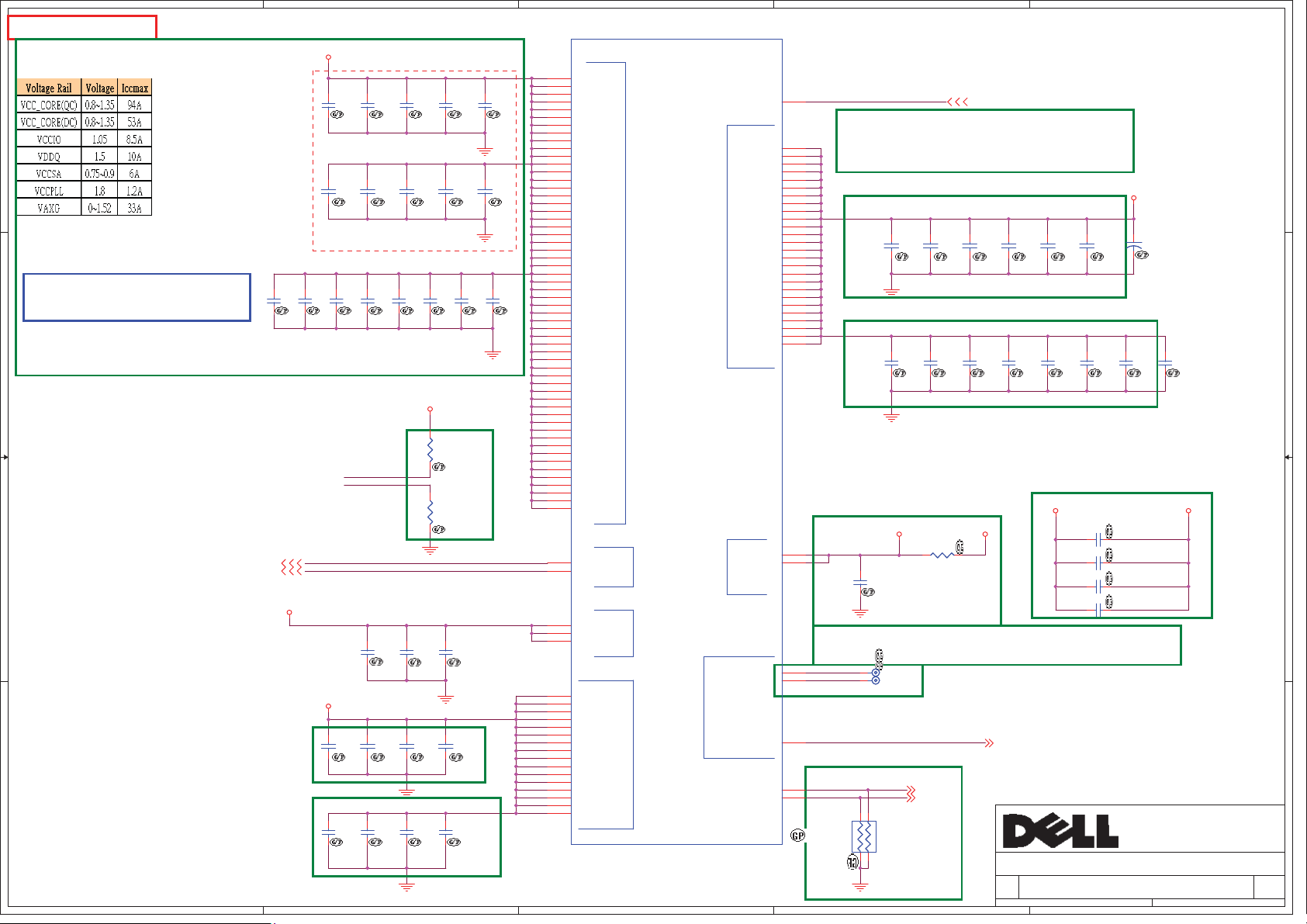

Page 8

5

4

3

2

1

SSID = CPU

D D

X00 1008

VCCIO Output Decoupling Recommendation:

Modify VCCCORE Cap

X00 1011

VCC_CORE

PROCESSOR CORE POWER: 53A

12

12

C801

C801

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C818

C818

C C

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C822

C822

C821

C821

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

12

12

C858

C858

C856

C856

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

12

12

C802

C802

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

Layout Note: 10u Cap place during CPU & IMVP

C819

C819

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

12

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

C804

C804

C803

C803

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C847

C847

C849

C849

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C823

C823

C824

C824

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

Layout Note: 2.2u Cap place under CPU

12

12

C851

C851

C861

C861

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

POP rule: 1. MLCC number * 0.8

2. 22u-->10u

12

12

12

C811

C811

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C817

C817

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C826

C826

C825

C825

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

12

C853

C853

C855

C855

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

C814

C814

C813

C813

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C837

C837

C836

C836

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C828

C828

C827

C827

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

12

12

C859

C859

C862

C862

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

VCC_CORE

12

12

12

C815

C815

C816

C816

C812

C812

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C831

C831

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

C852

C852

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

12

12

C820

C846

C846

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

C820

C848

C848

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

12

12

12

C832

C832

C833

C833

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

12

12

C857

C857

C854

C854

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

C850

C850

C835

C835

C834

C834

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

12

12

C863

C863

C864

C864

C860

C860

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

SC2D2U6D3V2CX-LL-GP

VCC Output Decoupling CAP Recommendation:

1. 1.9m ohm loadline design:(for SV)

4 x 470 uF

B B

A A

25 x 22 uF

35 x 2.2uF

2. 2.9m ohm loadline design: (for ULV/LV)

3 x 330uF

12 x 22uF

16 x 2.2uF

Revised VCC decoupling Cap list

X00 1011

5

4

CPU1F

CPU1F

A26

VCC

A29

VCC

A31

VCC

A34

VCC

A35

VCC

A38

VCC

A39

VCC

A42

VCC

C26

VCC

C27

VCC

C32

VCC

C34

VCC

C37

VCC

C39

VCC

C42

VCC

D27

VCC

D32

VCC

D34

VCC

D37

VCC

D39

VCC

D42

VCC

E26

VCC

E28

VCC

E32

VCC

E34

VCC

E37

VCC

E38

VCC

F25

VCC

F26

VCC

F28

VCC

F32

VCC

F34

VCC

F37

VCC

F38

VCC

F42

VCC

G42

VCC

H25

VCC

H26

VCC

H28

VCC

H29

VCC

H32

VCC

H34

VCC

H35

VCC

H37

VCC

H38

VCC

H40

VCC

J25

VCC

J26

VCC

J28

VCC

J29

VCC

J32

VCC

J34

VCC

J35

VCC

J37

VCC

J38

VCC

J40

VCC

J42

VCC

K26

VCC

K27

VCC

K29

VCC

K32

VCC

K34

VCC

K35

VCC

K37

VCC

K39

VCC

K42

VCC

L25

VCC

L28

VCC

L33

VCC

L36

VCC

L40

VCC

N26

VCC

N30

VCC

N34

VCC

N38

VCC

SANDYBRIDGE-1-GP-U-NF

SANDYBRIDGE-1-GP-U-NF

SANDYBRIDGE

SANDYBRIDGE

CORE SUPPLY

CORE SUPPLY

POWER

POWER

6 OF 9

6 OF 9

AF46

VCCIO

AG48

VCCIO

AG50

VCCIO

AG51

VCCIO

AJ17

VCCIO

AJ21

VCCIO

AJ25

VCCIO

AJ43

VCCIO

AJ47

VCCIO

AK50

VCCIO

AK51

VCCIO

AL14

VCCIO

AL15

VCCIO

AL16

VCCIO

AL20

VCCIO

AL22

VCCIO

AL26

VCCIO

AL45

VCCIO

AL48

VCCIO

AM16

VCCIO

AM17

VCCIO

AM21

VCCIO

AM43

VCCIO

AM47

VCCIO

AN20

VCCIO

AN42

VCCIO

AN45

VCCIO

AN48

VCCIO

AA14

VCCIO

AA15

VCCIO

AB17

VCCIO

AB20

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO_SEL

VCCPQE

VCCPQE

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

AC13

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

W17

BC22

AM25

AN22

A44

B43

C44

F43

G43

AN16

AN17

H_VCCP_SEL

X00 1008

H_CPU_SVIDALRT#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

PEG AND DDR

PEG AND DDR

SVID QUIET RAILS

SVID QUIET RAILS

VSS_SENSE_VCCIO

SENSE LINES

SENSE LINES

http://hobi-elektronika.net

2 x 330 uF (3 x 330 uF for 2012 capable designs)

5 x 22 uF & 5 x 0805 no-stuff at Bottom

7 x 22 uF & 2 x 0805 no-stuff at Top

12

C871

C871

12

C872

C872

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

+V1.05S_VCCP_DDR_R

12

12

C865

C865

C866

C866

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

PROCESSOR VCCIO: 8.5A

12

12

12

C869

C869

C867

C867

C868

C868

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C870

C870

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

Layout Note: 10u Cap place during CPU & VR

No-stuff sites outside the socket may be removed.

No-stuff sites inside the socket cavity need to remain.

+V1.05S_VCCP_DDR_R

12

12

VCCPQE

12

12

C877

C877

C888

C888

C892

C892

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

Layout Note: 1u Cap place under CPU

12

12

12

C875

C875

C876

C876

C874

C874

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

PROCESSOR 1.05V Quiet rail for DDR block (BGA only)

+V1.05S_VCCPQE should be short to +V1.05S_VCCP_DDR_R on board

R807 0R2J-2-GP

R807 0R2J-2-GP

1 2

DY

DY

+V1.05S_VCCP_DDR_R

R808

R808

1 2

0R2J-2-GP

0R2J-2-GP

C927

C927

SC1U10V2KX-1GP

SC1U10V2KX-1GP

R803 43R2J-GPR803 43R2J-GP

1 2

VCCIO_SENSE (45)

VSSIO_SENSE (45)

12

12

12

12

C885

C885

C890

C890

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

12

C880

C880

C878

C878

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

C891

C891

C873

C873

C879

C879

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

12

12

C883

C883

C882

C882

C881

C881

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

X00 1011

+V1.05S_VCCP_DDR_R 1D05V_VTT

VR_SVID_ALERT# (42)

H_CPU_SVIDCLK (42)

H_CPU_SVIDDAT (42)

VCC_CORE

12

12

R801

R801

100R2F-L1-GP-U

100R2F-L1-GP-U

R802

R802

100R2F-L1-GP-U

100R2F-L1-GP-U

For CRB VIDSOUT need to pull high 130 ohm closr to CPU and IMVP7

For CRB VIDALERT# need to pull high 75 ohm close to CPU

Place near processor

3

X00 1008

X00 1011

12

12

C887

C887

C889

C889

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

12

C886

C886

C884

C884

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

1 2

R809 D01RL0816F-L-GPR809 D01RL0816F- L-GP

1 2

R810 D01RL0816F-L-GPR810 D01RL0816F- L-GP

VCCSENSE (42)

VSSSENSE (42)

These resistors need to close to power IC.

1D05V_VTT

X00 1125

2

VR_SVID_ALERT#

H_CPU_SVIDDAT

R805 75R2J-1-GPR805 75R2J-1-GP

1 2

R804 130R2F-1-GPR804 130R2F-1-GP

1 2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiw an, R.O.C.

Taipei Hsien 221, Taiw an, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiw an, R.O.C.

CPU 5/7(VCC_CORE)

CPU 5/7(VCC_CORE)

CPU 5/7(VCC_CORE)

DB13 DIS

DB13 DIS

DB13 DIS

1

8 105Friday, Novemb er 26, 2010

8 105Friday, Novemb er 26, 2010

8 105Friday, Novemb er 26, 2010

of

of

of

X00

X00

X00

Page 9

5

SSID = CPU

D D

X00 1011

VCC_GFXCORE

12

C901

C901

12

C906

C906

X00 1011

VAXG Output Decoupling CAP Recommendation:

1. 3.9m ohm loadline design:(for GT2)

2 x 470 uF 6 x 22 uF (0805)

6 x 10 uF (0603) 11 x 1 uF (0402)

2. 4.6m ohm loadline design:(for GT1)

2 x 330 uF 5 x 22 uF (0805)

6 x 10 uF (0603) 6 x 1 uF (0402)

C C

12

C921

C921

12

12

C920

C920

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

X00 1011

Disabling Guidelines for External Graphics Designs:

Can connect to GND if motherboard only supports external

graphics and if GFX VR is not stuffed.

Can be left floating (Gfx VR keeps VAXG rail from floating)

if the VR is stuffed

VCC_AXG_SENSE(42)

B B

VCCPLL Output Decoupling Recommendation:

1 x 330 uF

2 x 1 uF

1 x 10 uF

A A

VCCSA Output Decoupling

Recommendation:

1 x 330 uF

5 x 10 uF (0603) 5 x 1uF (0402)

5

VSS_AXG_SENSE(42)

X00 1011

1D8V_S0

0D85V_S0

12

C938

C938

Layout Note: Place under CPU

12

C940

C940

4

PROCESSOR VAXG: 33A (for GT2)

12

C902

C902

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C908

C908

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C929

C929

C928

C928

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

VCC_AXG_SENSE

VSS_AXG_SENSE

12

12

C931

C931

VCC_GFXCORE

C903

C903

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C934

C934

C935

C935

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C930

C930

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

R906

R906

10R2F-N1-GP

10R2F-N1-GP

12

R907

R907

10R2F-N1-GP

10R2F-N1-GP

C904

C904

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C933

C933

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

12

12

PROCESSOR VCCPLL: 1.2A

12

12

C923

C923

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C922

C922

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C924

C924

SC1U10V2KX-1GP

SC1U10V2KX-1GP

PROCESSOR VCCSA: 6A

12

C937

C937

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C942

C942

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

SC1U10V2KX-1GP

4

12

C939

C939

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C943

C943

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

C941

C941

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C944

C944

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C905

C905

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C936

C936

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C932

C932

SC1U10V2KX-1GP

SC1U10V2KX-1GP

3

CPU1G

CPU1G

AA46

VAXG

AB47

VAXG

AB50

VAXG

AB51

VAXG

AB52

VAXG

AB53

VAXG

AB55

VAXG

AB56

VAXG

AB58

VAXG

AB59

VAXG

AC61

VAXG

AD47

VAXG

AD48

VAXG

AD50

VAXG

AD51

VAXG

AD52

VAXG

AD53

VAXG

AD55

VAXG

AD56

VAXG

AD58

VAXG

AD59

VAXG

AE46

VAXG

N45

VAXG

P47

VAXG

P48

VAXG

P50

VAXG

P51

VAXG

P52

VAXG

P53

VAXG

P55

VAXG

P56

VAXG

P61

VAXG

T48

VAXG

T58

VAXG

T59

VAXG

T61

VAXG

U46

VAXG

V47

VAXG

V48

VAXG

V50

VAXG

V51

VAXG

V52

VAXG

V53

VAXG

V55

VAXG

V56

VAXG

V58

VAXG

V59

VAXG

W50

VAXG

W51

VAXG

W52

VAXG

W53

VAXG

W55

VAXG

W56

VAXG

W61

VAXG

Y48

VAXG

Y61

VAXG

F45

VAXG_SENSE

G45

VSSAXG_SENSE

BB3

VCCPLL

BC1

VCCPLL

BC4

VCCPLL

L17

VCCSA

L21

VCCSA

N16

VCCSA

N20

VCCSA

N22

VCCSA

P17

VCCSA

P20

VCCSA

R16

VCCSA

R18

VCCSA

R21

VCCSA

U15

VCCSA

V16

VCCSA

V17

VCCSA

V18

VCCSA

V21

VCCSA

W20

VCCSA

SANDYBRIDGE-1-GP-U-NF

SANDYBRIDGE-1-GP-U-NF

http://hobi-elektronika.net

SANDYBRIDGE

SANDYBRIDGE

GRAPHICS

GRAPHICS

SENSE

LINES

SENSE

LINES

1.8V RAIL

1.8V RAIL

SA RAIL

SA RAIL

3

POWER

POWER

SENSE LINES

SENSE LINES

SM_VREF

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

QUIET RAILS

QUIET RAILS

VDDQ_SENSE

VSS_SENSE_VDDQ

VCCSA_SENSE

VCCSA_VID

VCCSA_VID

EDS R1.5:

rPGA988 PinC22

BGA1023 PinD48

2

Refer to the latest Huron River Mainstream PDG

(Doc# 436735) for more details on S3 power

7 OF 9

7 OF 9

reduction implementation.

+V_SM_VREF_CNT should have 20 mil trace width

20 mil spacing

X00 1008

+V_SM_VREF_CNT

12

12

C958

C958

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

Layout Note: Place during CPU & VR

Layout Note: Place under CPU

12

12

C952

C952

SC1U10V2KX-1GP

SC1U10V2KX-1GP

TacomaFalls_Schm_Rev0p5

R901

R901

1 2

0R2J-2-GP

12

C926

C926

SC1U10V2KX-1GP

SC1U10V2KX-1GP

0R2J-2-GP

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCCDQ

VCCDQ

AY43

AJ28

AJ33

AJ36

AJ40

AL30

AL34

AL38

AL42

AM33

AM36

AM40

AN30

AN34

AN38

AR26

AR28

AR30

AR32

AR34

AR36

AR40

AV41

AW26

BA40

BB28

BG33

AM28

AN26

PROCESSOR DDR 1.5V QUIET RAIL (BGA only)

+V1.5S_VCCD_Q should be short to +V1.5S_VCCDDQ on board

TP_VDDQ_SENSE

BC43

TP_VDDQ_VSS

BA43

U10

D48

D49

1

1

VCCUSA_SENSE

H_FC_C22

VCCSA_SEL

TP901 TPAD14-GPTP901 TPAD14-GP

TP902 TPAD14-GPTP902 TPAD14-GP

1

23

RN901

RN901

SRN1KJ-7-GP

SRN1KJ-7-GP

4

H_FC_C22 (48)

VCCSA_SEL (48)

2

+V_SM_VREF_CNT (37)

12

C954

C954

C953

C953

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

C945

C945

SC1U10V2KX-1GP

SC1U10V2KX-1GP

1D5V_S01D5V_VCCDQ

X00 1007

1

Routing Guideline:

Power from DDR_VREF_S3 and +V_SM_VREF_CNT

should have 10 mils trace width.

X00 1124

PROCESSOR VDDQ: 10A

12

12

C955

C955

C956

C956

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

12

C946

C946

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C948

C948

SC1U10V2KX-1GP

SC1U10V2KX-1GP

C947

C947

S3 power reduction 1.5V power plan; stitching Cap

VCCUSA_SENSE (48)

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

CPU 6/7(VCC_GFX_CORE)

CPU 6/7(VCC_GFX_CORE)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

CPU 6/7(VCC_GFX_CORE)

1D5V_S0

12

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

12

SC1U10V2KX-1GP

SC1U10V2KX-1GP

VDDQ Output Decoupling Recommendation:

1 x 330 uF

6 x 10 uF

C907 SCD1U10V2KX-5GP

C907 SCD1U10V2KX-5GP

1 2

C918 SCD1U10V2KX-5GP

C918 SCD1U10V2KX-5GP

1 2

C919 SCD1U10V2KX-5GP

C919 SCD1U10V2KX-5GP

1 2

C925 SCD1U10V2KX-5GP

C925 SCD1U10V2KX-5GP

1 2

DB13 DIS

DB13 DIS

DB13 DIS

12

C957

C957

TC901

TC901

ST330U2VDM-4-GP

ST330U2VDM-4-GP

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

Layout Note:

Place near SM_VREF pin

12

12

C950

C950

SC1U10V2KX-1GP

SC1U10V2KX-1GP

DY

DY

DY

DY

DY

DY

DY

DY

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

C951

C951

C949

C949

SC1U10V2KX-1GP

SC1U10V2KX-1GP

1D5V_S31D5V_S0

1

SC1U10V2KX-1GP

SC1U10V2KX-1GP

9 105Friday, November 26, 2010

9 105Friday, November 26, 2010

9 105Friday, November 26, 2010

X00 1011

of

of

of

X00

X00

X00

Page 10

5

4

3

2

1

SSID = CPU

D D

C C

B B

A A

5

CPU1H

CPU1H

A13

VSS

A17

VSS

A21

VSS

A25

VSS

A28

VSS

A33

VSS

A37

VSS

A40

VSS

A45

VSS

A49

VSS

A53

VSS

A9

VSS

AA1

VSS

AA13

VSS

AA50

VSS

AA51

VSS

AA52

VSS

AA53

VSS

AA55

VSS

AA56

VSS

AA8

VSS

AB16

VSS

AB18

VSS

AB21

VSS

AB48

VSS

AB61

VSS

AC10

VSS

AC14

VSS

AC46

VSS

AC6

VSS

AD17

VSS

AD20

VSS

AD4

VSS

AD61

VSS

AE13

VSS

AE8

VSS

AF1

VSS

AF17

VSS

AF21

VSS

AF47

VSS

AF48

VSS

AF50

VSS

AF51

VSS

AF52

VSS

AF53

VSS

AF55

VSS

AF56

VSS

AF58

VSS

AF59

VSS

AG10

VSS

AG14

VSS

AG18

VSS

AG47

VSS

AG52

VSS

AG61

VSS

AG7

VSS

AH4

VSS

AH58

VSS

AJ13

VSS

AJ16

VSS

AJ20

VSS

AJ22

VSS

AJ26

VSS

AJ30

VSS

AJ34

VSS

AJ38

VSS

AJ42

VSS

AJ45

VSS

AJ48

VSS

AJ7

VSS

AK1

VSS

AK52

VSS

AL10

VSS

AL13

VSS

AL17

VSS

AL21

VSS

AL25

VSS

AL28

VSS

AL33

VSS

AL36

VSS

AL40

VSS

AL43

VSS

AL47

VSS

AL61

VSS

AM13

VSS

AM20

VSS

AM22

VSS

AM26

VSS

AM30

VSS

AM34

VSS

SANDYBRIDGE-1-GP-U-NF

SANDYBRIDGE-1-GP-U-NF

SANDYBRIDGE

SANDYBRIDGE

VSS

VSS

4

8 OF 9

8 OF 9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM38

AM4

AM42

AM45

AM48

AM58

AN1

AN21

AN25

AN28

AN33

AN36

AN40

AN43

AN47

AN50

AN54

AP10

AP51

AP55

AP7

AR13

AR17

AR21

AR41

AR48

AR61

AR7

AT14

AT19

AT36

AT4

AT45

AT52

AT58

AU1

AU11

AU28

AU32

AU51

AU7

AV17

AV21

AV22

AV34

AV40

AV48

AV55

AW13

AW43

AW61

AW7

AY14

AY19

AY30

AY36

AY4

AY41

AY45

AY49

AY55

AY58

AY9

BA1

BA11

BA17

BA21

BA26

BA32

BA48

BA51

BB53

BC13

BC5

BC57

BD12

BD16

BD19

BD23

BD27

BD32

BD36

BD40

BD44

BD48

BD52

BD56

BD8

BE5

BG13

http://hobi-elektronika.net

3

CPU1I

CPU1I

BG17

VSS

BG21

VSS

BG24

VSS

BG28

VSS

BG37

VSS

BG41

VSS

BG45

VSS

BG49

VSS

BG53

VSS

BG9

VSS

C29

VSS

C35

VSS

C40

VSS

D10

VSS

D14

VSS

D18

VSS

D22

VSS

D26

VSS

D29

VSS

D35

VSS

D4

VSS

D40

VSS

D43

VSS

D46

VSS

D50

VSS

D54

VSS

D58

VSS

D6

VSS

E25

VSS

E29

VSS

E3

VSS

E35

VSS

E40

VSS

F13

VSS

F15

VSS

F19

VSS

F29

VSS

F35

VSS

F40

VSS

F55

VSS

G48

VSS

G51

VSS

G6

VSS

G61

VSS

H10

VSS

H14

VSS

H17

VSS

H21

VSS

H4

VSS

H53

VSS

H58

VSS

J1

VSS

J49

VSS

J55

VSS

K11

VSS

K21

VSS

K51

VSS

K8

VSS

L16

VSS

L20

VSS

L22

VSS

L26

VSS

L30

VSS

L34

VSS

L38

VSS

L43

VSS

L48

VSS

L61

VSS

M11

VSS

M15

VSS

SANDYBRIDGE-1-GP-U-NF

SANDYBRIDGE-1-GP-U-NF

SANDYBRIDGE

SANDYBRIDGE

VSS

VSS

NCTF_VSS_NCTF#A5

NCTF_VSS_NCTF#A57

NCTF_VSS_NCTF#BC61

VSS_NCTF

VSS_NCTF

VSS_NCTF

VSS_NCTF

NCTF_VSS_NCTF#BG5

NCTF_VSS_NCTF#BG57

NCTF_VSS_NCTF#C3

NCTF

NCTF

NCTF TEST PIN:

A5,A57,BC61,BG5,BG57,C3,E1,E61

NCTF TEST PIN:

A5,A57,BC61,BG5,BG57,C3,E1,E61

2

VSS_NCTF

VSS_NCTF

NCTF_VSS_NCTF#E1

NCTF_VSS_NCTF#E61

9 OF 9

9 OF 9

M4

VSS

M58

VSS

M6

VSS

N1

VSS

N17

VSS

N21

VSS

N25

VSS

N28

VSS

N33

VSS

N36

VSS

N40

VSS

N43

VSS

N47

VSS

N48

VSS

N51

VSS

N52

VSS

N56

VSS

N61

VSS

P14

VSS

P16

VSS

P18

VSS

P21

VSS

P58

VSS

P59

VSS

P9

VSS

R17

VSS

R20

VSS

R4

VSS

R46

VSS

T1

VSS

T47

VSS

T50

VSS

T51

VSS

T52

VSS

T53

VSS

T55

VSS

T56

VSS

U13

VSS

U8

VSS

V20

VSS

V61

VSS

W13

VSS

W15

VSS

W18

VSS

W21

VSS

W46

VSS

W8

VSS

Y4

VSS

Y47

VSS

Y58

VSS

Y59

VSS

TP_NCTP_A5

A5

A57

BC61

BD3

BD59

BE4

BE58

BG5

BG57

C3

C58

D59

E1

E61

TP_NCTP_BC61

TP_NCTP_BG5

TP_NCTP_E61

1

TP1001 TPAD14-GPTP1001 TPAD14-GP

1

TP1002 TPAD14-GPTP1002 TPAD14-GP

1

TP1003 TPAD14-GPTP1003 TPAD14-GP

1

TP1004 TPAD14-GPTP1004 TPAD14-GP

Add NCTF test pin

X00 1011

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Taipei Hsien 221, Taiwan, R.O.C.

CPU 7/7(VSS)

CPU 7/7(VSS)

CPU 7/7(VSS)

DB13 DIS

DB13 DIS

DB13 DIS

1