Page 1

A

www.kythuatvitinh.com

Digitally signed by

fdsf

DN: cn=fdsf, o=fsdfsd,

ou=ffsdf,

email=fdfsd@fsdff,

c=US

Date: 2010.03.29

18:09:00 +07'00'

B

C

D

E

DC/DC IMVP4

Switching Power

ISL6218

INPUTS

4 4

DCBATOUT VCC_CORE

OUTPUT

32

SPR.01.2004

SYSTEM DC/DC

MAX1715

INPUTS OUTPUTS

DCBATOUT

34

1D35V_S0

2D5V_S3

DC/DC&CHARGER

MAX1645

3 3

INPUTS OUTPUTS

AD+

35

BT+

DC/DC

MAX1999

OUTPUTSINPUTS

DCBATOUT

2 2

G913C/APL1085

APL5331kAC/G1211X

OUTPUTSINPUTS

3D3V_S0 1D8V_VCCA_S0

3D3V_S5 1D5V_S5

3D3V_S0

2D5V_S3 1D25V_S0

1D35V_S0 VCC_IO_S0

1D5V_S0

33

3D3V_S5

5V_S5

38

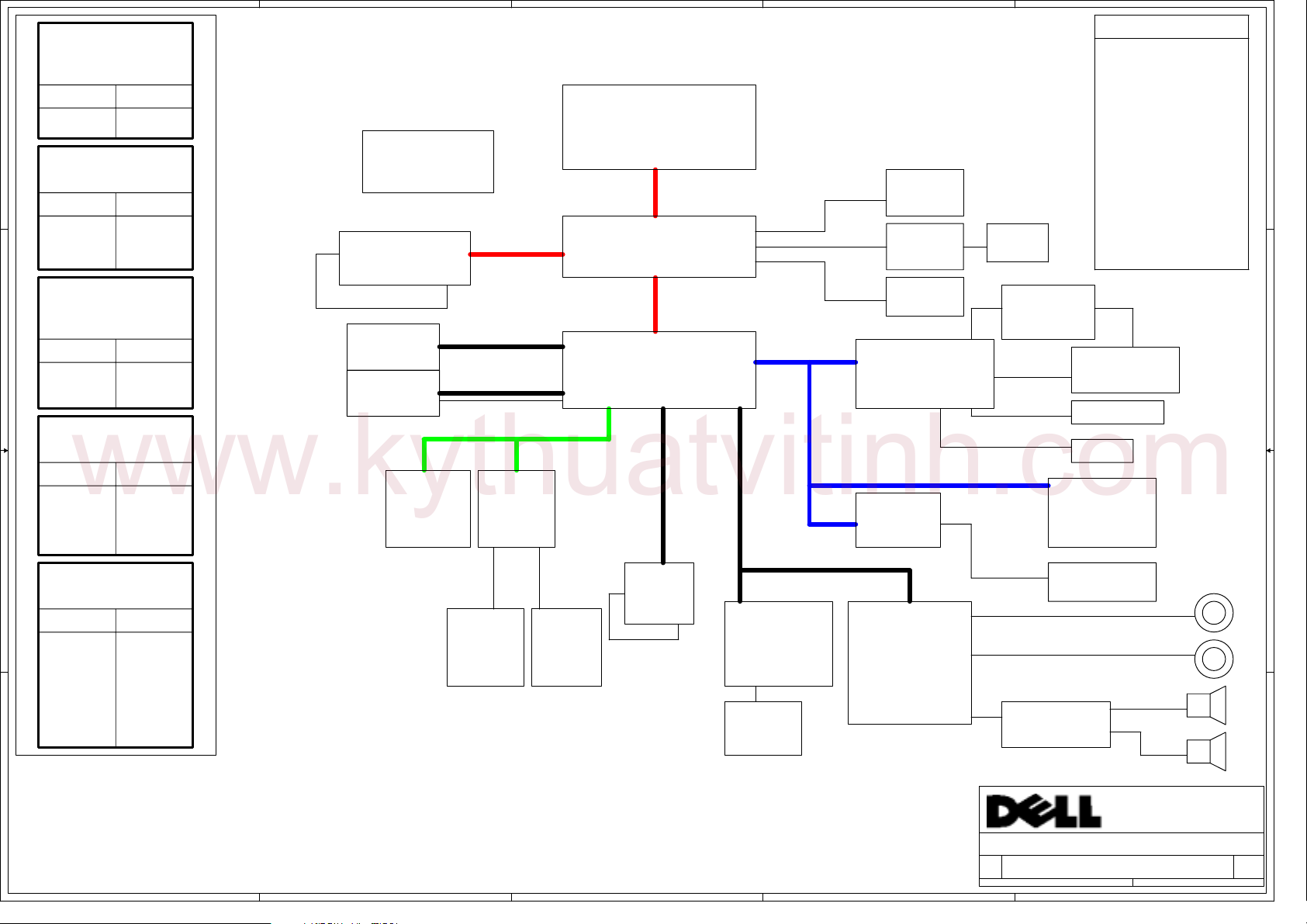

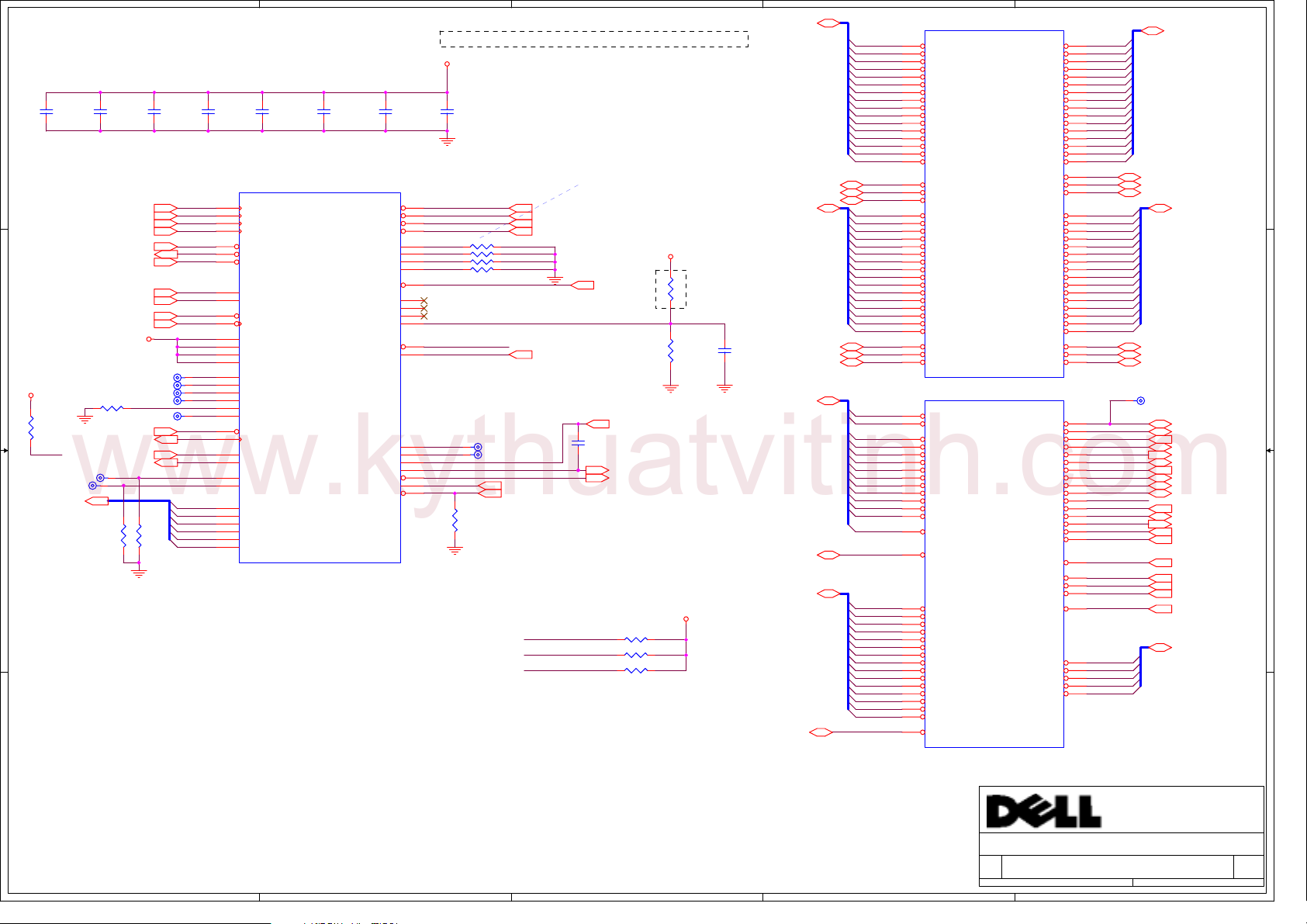

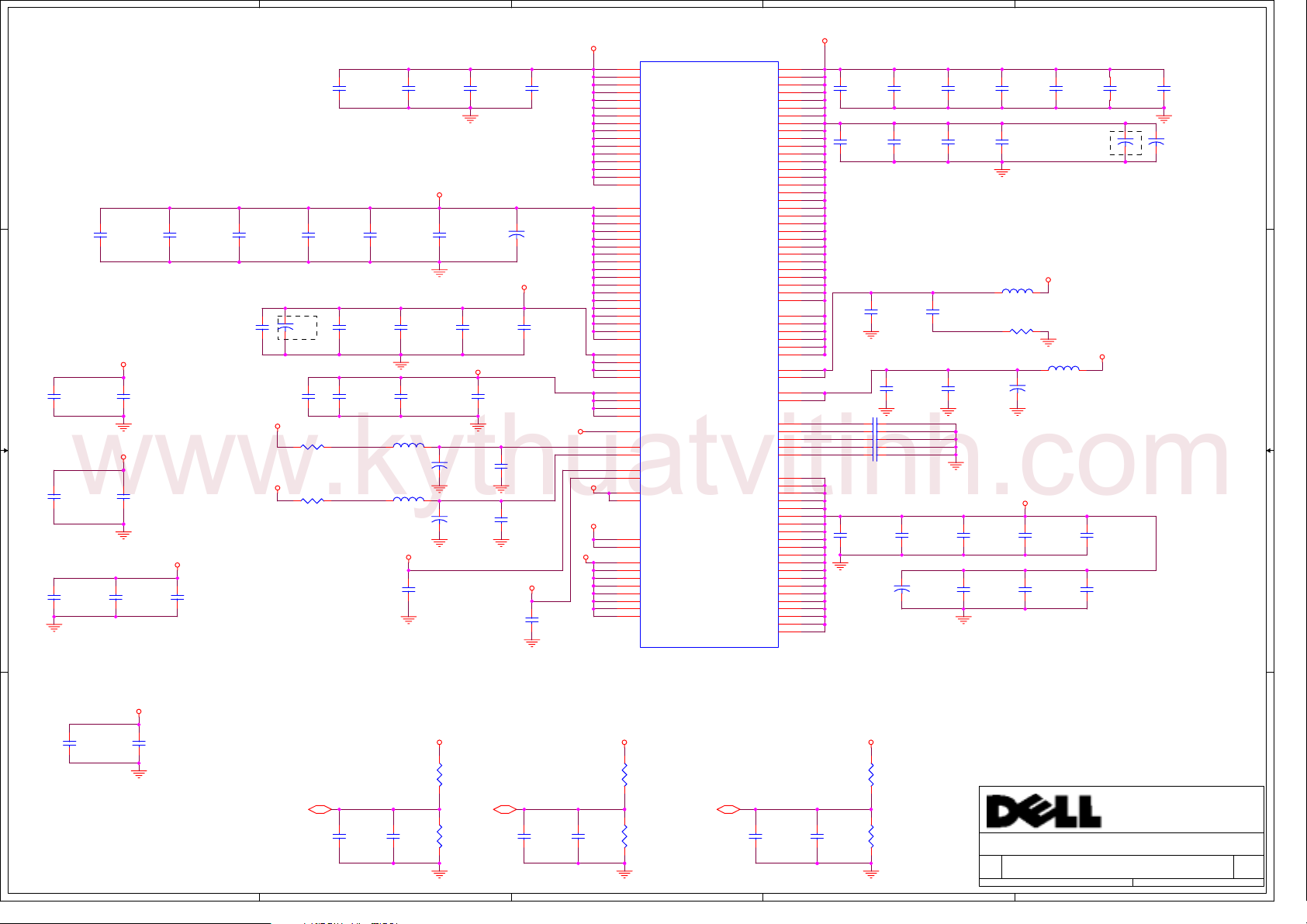

MOLOKAI Block Diagram

CLOCK

Generator

ICS950810

DDR

DRAM

Socket

* 2

HDD

OPTICAL

49LF004-334C

10,11,12

26

USB2.0

LPC BUS

BIOS

ROM

3

DDR 266/333

Ultra

DMA-100

IDE BUS

KBC

M38859

27 28

TOUCH

PAD

CPU

Banias/Dothan

Montara-GM+

ICH4-M

USB 2.0

2 Ports

INT

KB

5,6

HOST BUS

100MHz

7,8,9

Hub I/F

PCI BUS

16,17,18

USB2.0

AC-LINK

29

MODEM

DAUGHTER

CARD

RJ-11

Project Code:91.43E01.001

CRT

DVO

LVDS

CH7011

(CHRONTEL)

LCD

SD/MS CARD

READER + 1394

PCI7420

LAN

BCM4401

23

AC 97

Codec

29

STAC9750

03249-SC

13

15

14

24

TV_OUT

POWER SW

TPS2220A

21

MINIPCI

802.11B

802.11G

Amplifier

TPA0312

PCB LAYER

L1:COMPONENT

L2:GND

L3:SIGNAL1

L4:SIGNAL2

L5:VCC

L6:GND

L7:SIGNAL3

L8:COMPONENT

20

CARDBUS

SLOT B

CardReader

1394

19

RJ-45

25

(TBD)

22

Line-out

MIC

1 1

A

B

C

Wistron Confidential

D

Title

Size Document Number Rev

A3

Date: Sheet

BLOCK DIAGRAM

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

MOLOKAI

139Monday, April 05, 2004

E

SC

of

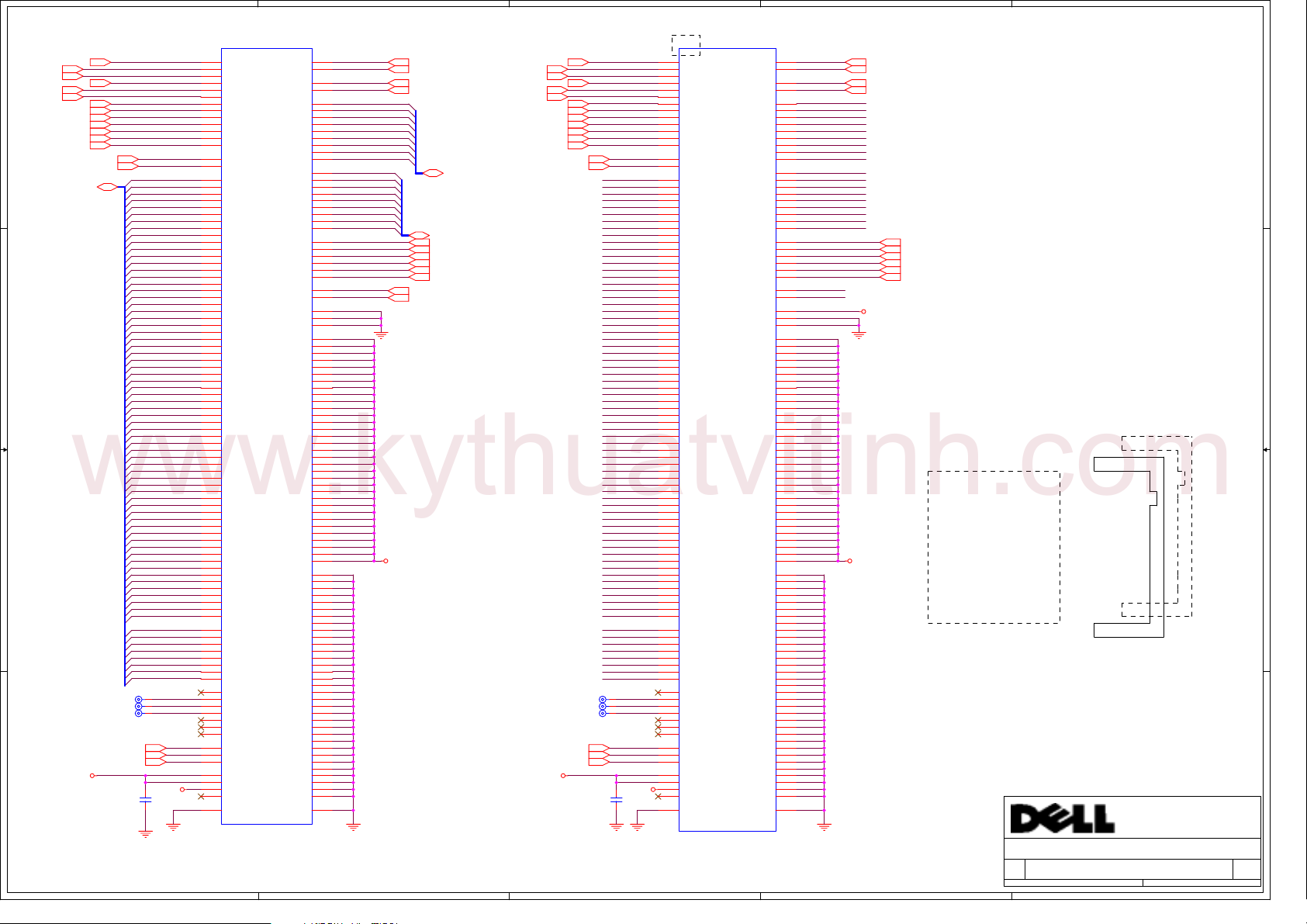

Page 2

A

www.kythuatvitinh.com

B

C

D

E

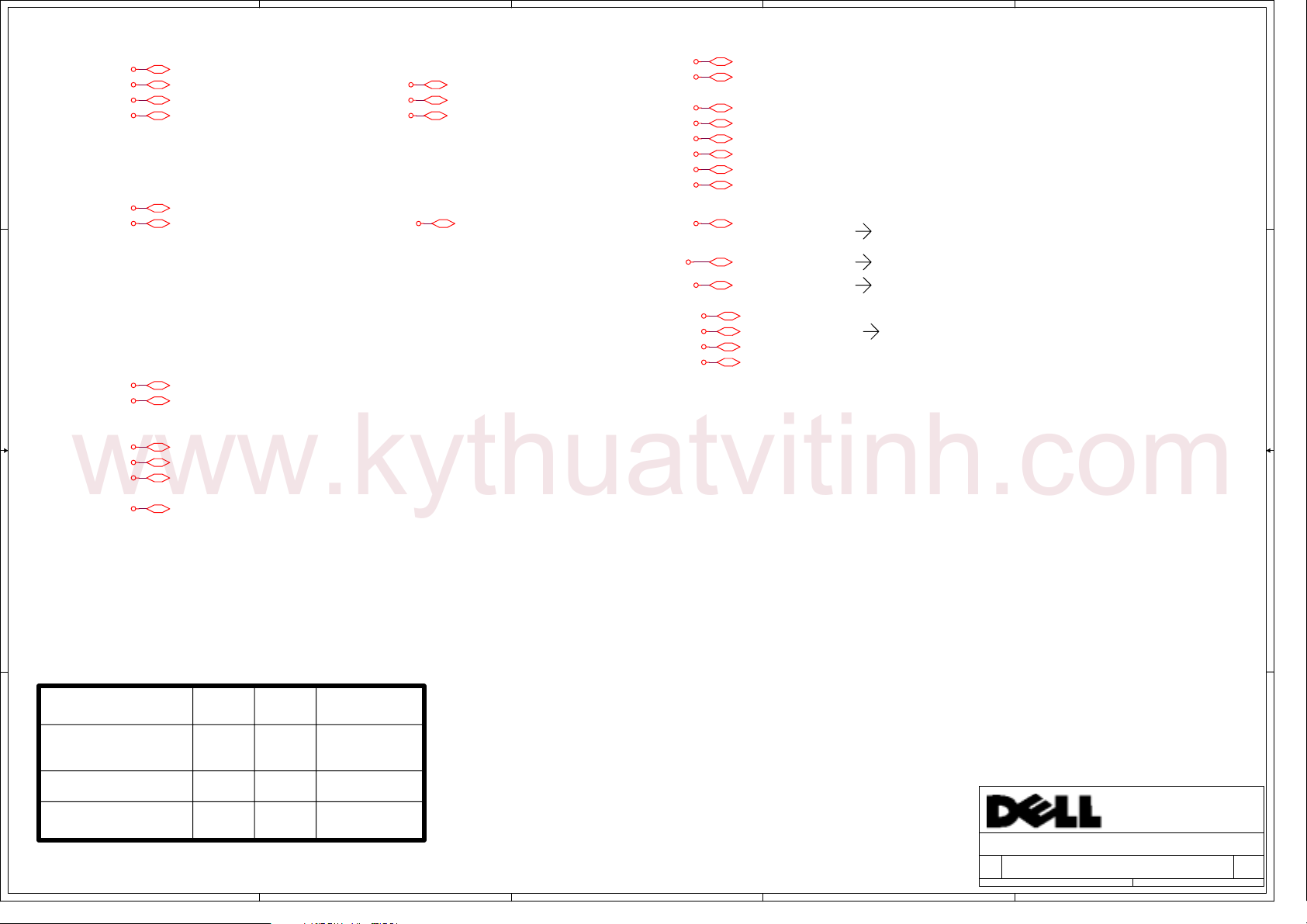

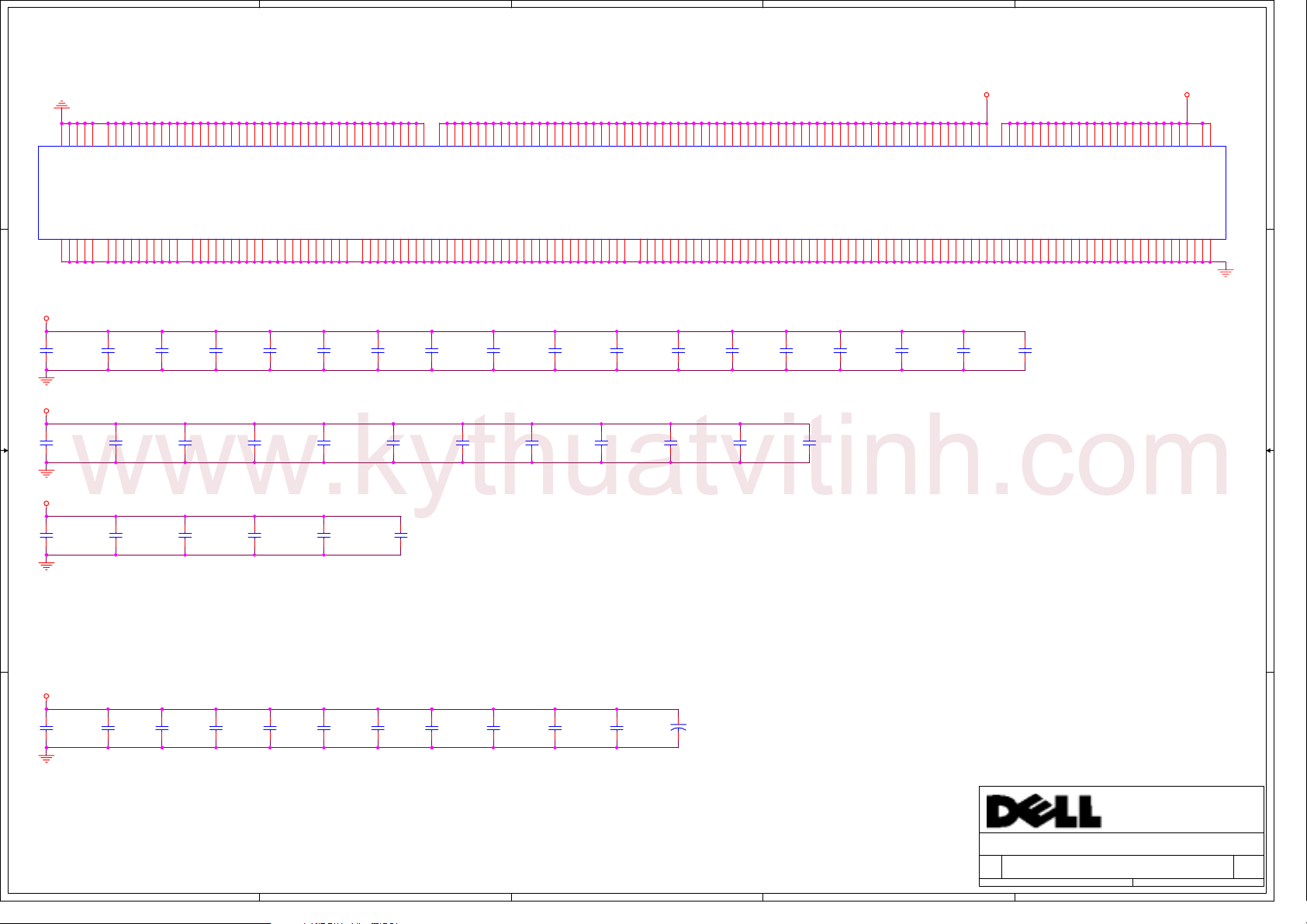

S5 S0S3

5V_S5

3D3V_S5

1D5V_S5

4 4

VCC_RTC_S5

AD+

DCBATOUT

5V_S5 18,33,34,36

3D3V_S5 4,16,17,18,28,30,31,33,36,38,39

1D5V_S5 18,38

VCC_RTC_S5 17

AD+ 35,37,39

DCBATOUT 14,32,33,34,35,36,38,39

3D3V_S3

2D5V_S3

1D25V_DDRVREF_S3

3D3V_LAN_S5AC

3D3V_S3 14,25,28,30,34,36,39

2D5V_S3 7,9,10,11,34,38,39

1D25V_DDRVREF_S3 7,10,34

LAN-ACAC-IN / BAT.-IN

3D3V_LAN_S5AC 23,29,36,37

1D8V_VCCA_S0

5V_S0

3D3V_S0

1D5V_S0

1D25V_S0

1D35V_S0

VCC_CORE_S0

VCC_IO_S0

5VA_AUD_S3

5V_S0 13,14,17,18,19,20,24,26,28,30,32,34,36,38,39

3D3V_S0 3,7,8,9,10,13,14,15,16,17,18,19,20,21,22,24,25,26,27,29,30,31,32,36,38,39

1D5V_S0 7,8,9,15,16,18,27,38,39

1D25V_S0 11,12,38

1D35V_S0 7,9,34,38,39

VCC_CORE_S0 6,32,39

VCC_IO_S0 4,5,6,7,9,17,18,32,38,39

1D8V_VCCA_S0 5,38

5VA_AUD_S3 24

AUDIO

3D3V_LCD_S0

CRT_VCC_S0

TV3D3V1_S0

3 3

OTHERS

5V_AUX

3D3V_AUX

3D3V_RTC

ICH_VBIAS

MAX1999_REF

MAX1999_VCC

2 2

5V_AUX 30,31,33,35,37,38,39

3D3V_AUX 14,17,33

3D3V_RTC 17,28

ICH_VBIAS 17

MAX1999_REF 33,38

MAX1999_VCC 33

TV3D3VA_S0

TV3D3V2_S0

TV1D5V_S0

3D3V_LCD_S0 14

CRT_VCC_S0 13

TV3D3V1_S0 15

TV3D3VA_S0 15

TV3D3V2_S0 15

TV1D5V_S0 15

LCD

CRT

TV-OUT

PCI TABLE

DEVICE IDSEL IRQ REQ# / GNT#

SD/MS CARD READER+1394

AD20

PCI7420

1 1

MINI PCI 802.11B/G AD17 REQ#0 / GNT#0PIRQE#

LAN BCM4401

A

AD21 PIRQD# REQ#4 / GNT#4

PIRQB#

PIRQC#

PIRQF#

PIRQG#

REQ#1 / GNT#1

B

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Size Document Number Rev

A3

C

D

Date: Sheet

Table of Content

Taipei Hsien 221, Taiwan, R.O.C.

MOLOKAI

239Saturday, April 17, 2004

E

SC

of

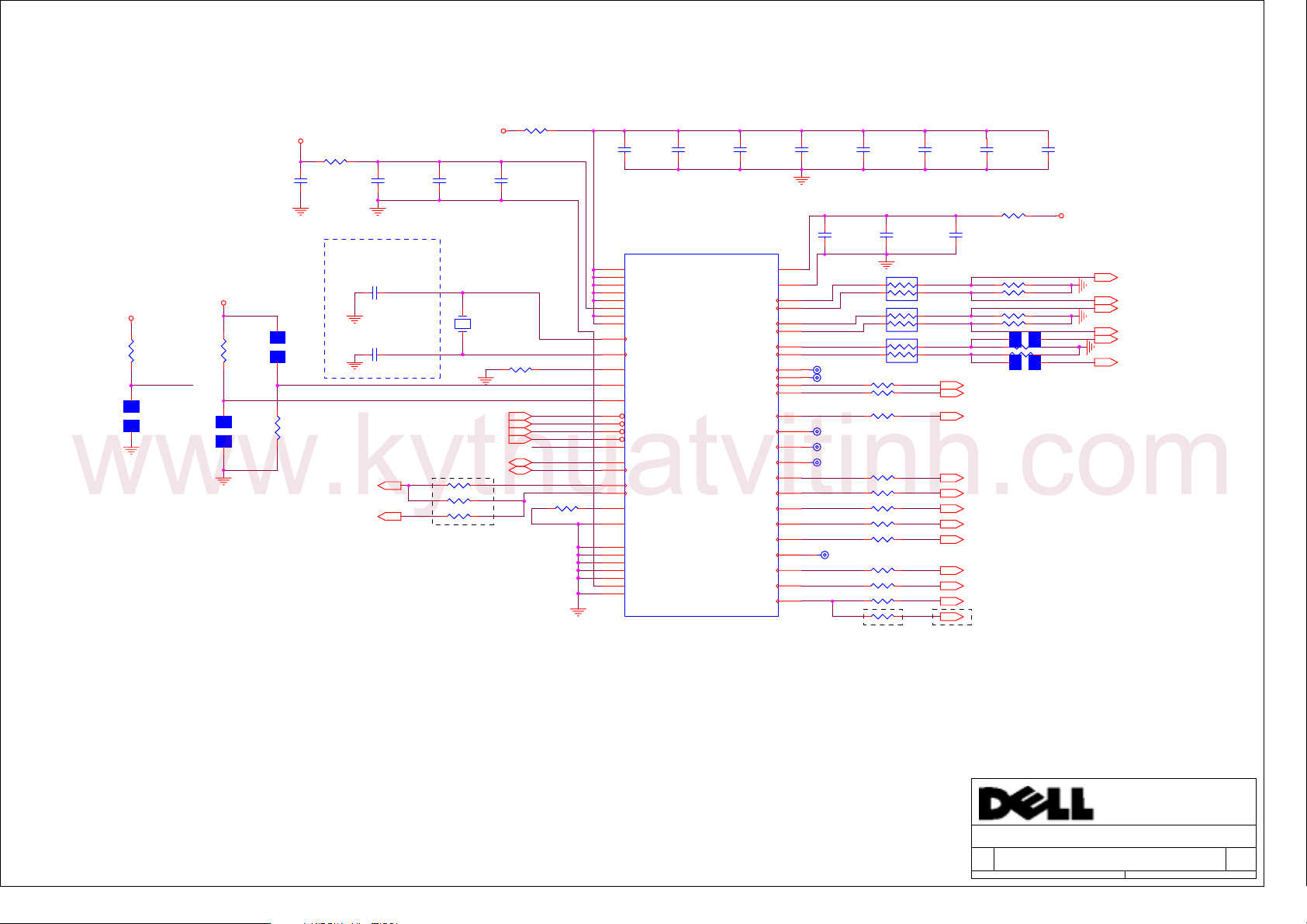

Page 3

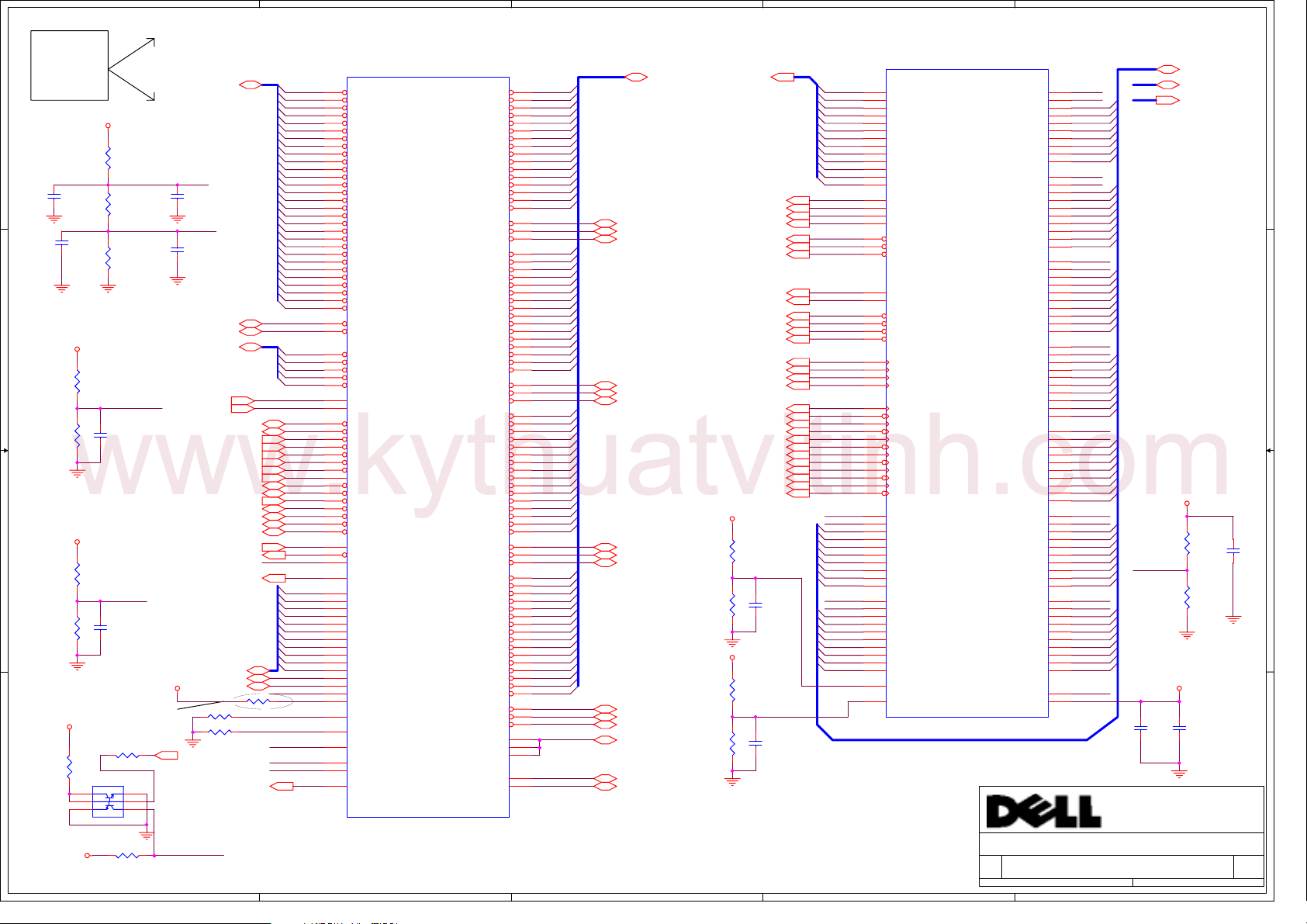

Host Freq. Setting

www.kythuatvitinh.com

FS1/0 = 00 166MHz

FS1/0 = 01 100MHz

FS1/0 = 10 200MHz

FS1/0 = 11 133MHz

FS2 = 0 unbuffer mode (disable 66MHz-IN)

FS2 = 1 buffer mode

Mult0 = 0 Rr=221,Iref=5mA =>Vswing=1.0V@50ohm

Mult0 = 1 Rr=475,Iref=2.32mA =>Vswing=0.7V@50ohm

CPU & MEMORY Freq. Selection

3D3V_S0

12

12

R483

10KR2

CK-408_MULT0

R484

DUMMY-R2

3D3V_S0

12

12

R184

DUMMY-R2

R185

1KR2

3D3V_S0

12

R181

DUMMY-R2

12

R182

1KR2

R192

1 2

12

0R5J-1

BC145

SCD1U16V

No stuff:

caps are internal

to CK-TITAN.

CLK66_DREF_GMCH8

CLK48_DOT21

Filtering CKT for

48MHz power plane

12

BC128

SC10U10V5ZY

BC140

12

DUMMY-SC10P50V2JN-1

BC127

12

DUMMY-SC10P50V2JN-1

CLKGEN_48MPWR

R191 33R2

1 2

R603 DUMMY-33R2

1 2

R190 33R2

1 2

3D3V_S0

BC229

SCD01U16V2KX

X2

X-14D31818M-7

1 2

PM_SLP_S1#17

PM_STPPCI#17

PM_STPCPU#17,32

CLK_PWD#32

SMBD_ICH10,17

SMBC_ICH10,17

02/09/2004

R208

1 2

0R5J-1

12

BC230

SCD1U10V2MX-1

R187 1KR2

1 2

SEL2

CK-408_MULT0

SMBD_ICH

SMBC_ICH

R186

1 2

475R3F

CLKGEN_+3VRUN

12

BC139

DUMMY-SC10U10V5ZY

U40

1

VDDREF

8

VDDPCI

14

VDDPCI

19

VDD3V66

32

VDD3V66

37

VDD48

46

VDDCPU

50

VDDCPU

2

X1

3

X2

40

FS2

55

FS1

54

25

34

53

28

43

29

30

33

35

42

41

4

9

15

20

31

36

47

CK-408

FS0

PD#

PCI_STOP#

CPU_STOP#

VTT_PWRGD#

MULTSEL0

SDATA

SCLK

3V66_0

3V66_1/VCH_CLK

IREF

GND

GND

GND

GND

GND

GND

GND

GND

ICS950810CG

12

BC237

SCD1U10V2MX-1

12

BC238

SCD1U10V2MX-1

VDDA

GND

CPUCLKT2

CPUCLKC2

CPUCLKT1

CPUCLKC1

CPUCLKT0

CPUCLKC0

3V66_5

3V66_4

3V66_3

3V66_2

PCICLK_F2

PCICLK_F1

PCICLK_F0

PCICLK6

PCICLK5

PCICLK4

PCICLK3

PCICLK2

PCICLK1

PCICLK0

48MHZ_USB

48MHZ_DOT

REF

12

26

27

45

44

49

48

52

51

24

23

22

21

7

6

5

18

17

16

13

12

11

10

39

38

56

BC228

SCD1U10V2MX-1

12

12

BC142

SCD1U10V2MX-1

RN26 SRN33-2-U2

RN25 SRN33-2-U2

RN24 DUMMY-SRN33-2-U2

TP90

TP89

TPAD28

R217 33R2

1 2

TPAD28

R216 33R2

1 2

R209 33R2

1 2

TP86

TPAD28

TP84

TPAD28

TP88

TPAD28

R215 33R2

1 2

R214 33R2

1 2

R213 33R2

1 2

R212 33R2

1 2

R211 33R2

1 2

TP182 TPAD28

R188 33R2

1 2

R189 33R2

1 2

R183 33R2

1 2

R655 DY-33R2

1 2

SC:Because codec

change to use

crystal so dummy

CLK source

BC239

SCD1U10V2MX-1

CLKGEN_APWR

BC143

SCD01U16V2KX

1

2 3

1

2 3

1

2 3

12

BC141

SCD1U10V2MX-1

12

4

4

4

CLK_ITP_R

CLK_ITP#_R

01/15/2004

PLACE NEAR EACH PIN

12

BC231

SCD1U10V2MX-1

1 2

BC144

DUMMY-SC10U10V5ZY

R160 49D9R3F

1 2

R161 49D9R3F

1 2

R158 49D9R3F

1 2

R159 49D9R3F

1 2

R155 DUMMY-R2

1 2

R154 DUMMY-49D9R3F

1 2

R157 DUMMY-49D9R3F

1 2

R156 DUMMY-R2

1 2

CLK66_GMCH 8

CLK66_ICH 16

CLKPCIF_ICH 17

PCLK_CBUS 21

PCLK_KBC 28

PCLK_FWH 27

PCLK_MINI 19

PCLK_LAN 23

CLK48_ICH 16

CLK48_DREF_GMCH 8

CLK14_ICH 17

CLK14_AUDIO 24

12

R218

0R5J-1

BC227

SCD1U10V2MX-1

3D3V_S0

CLK_CPU 5

CLK_CPU# 5

CLK_MCH 7

CLK_MCH# 7

CLK_ITP_CPU 4,5

CLK_ITP_CPU# 4,5

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Size Document Number Rev

A3

Date: Sheet

Clock GEN.

Taipei Hsien 221, Taiwan, R.O.C.

MOLOKAI

339Thursday, April 15, 2004

SC

of

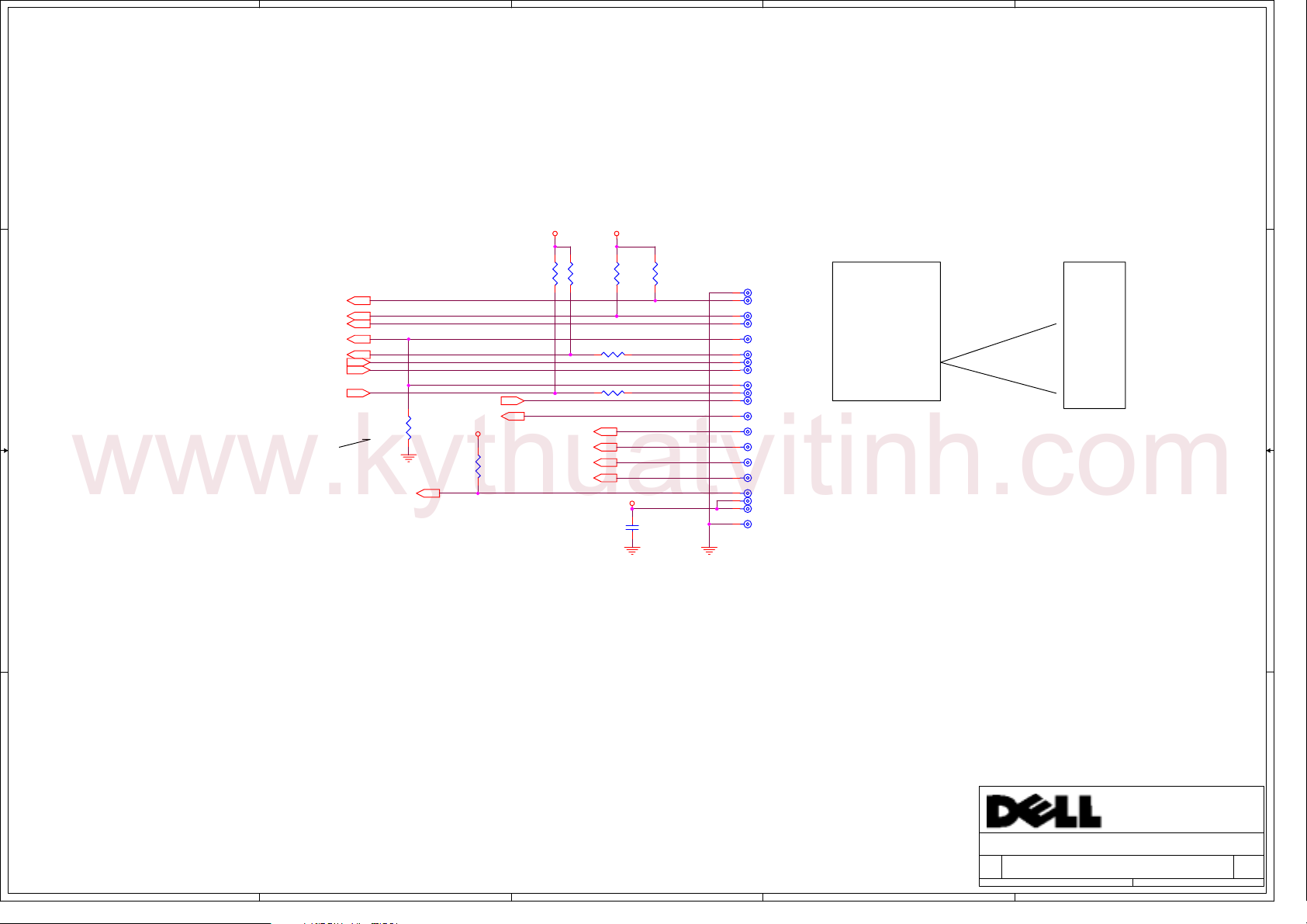

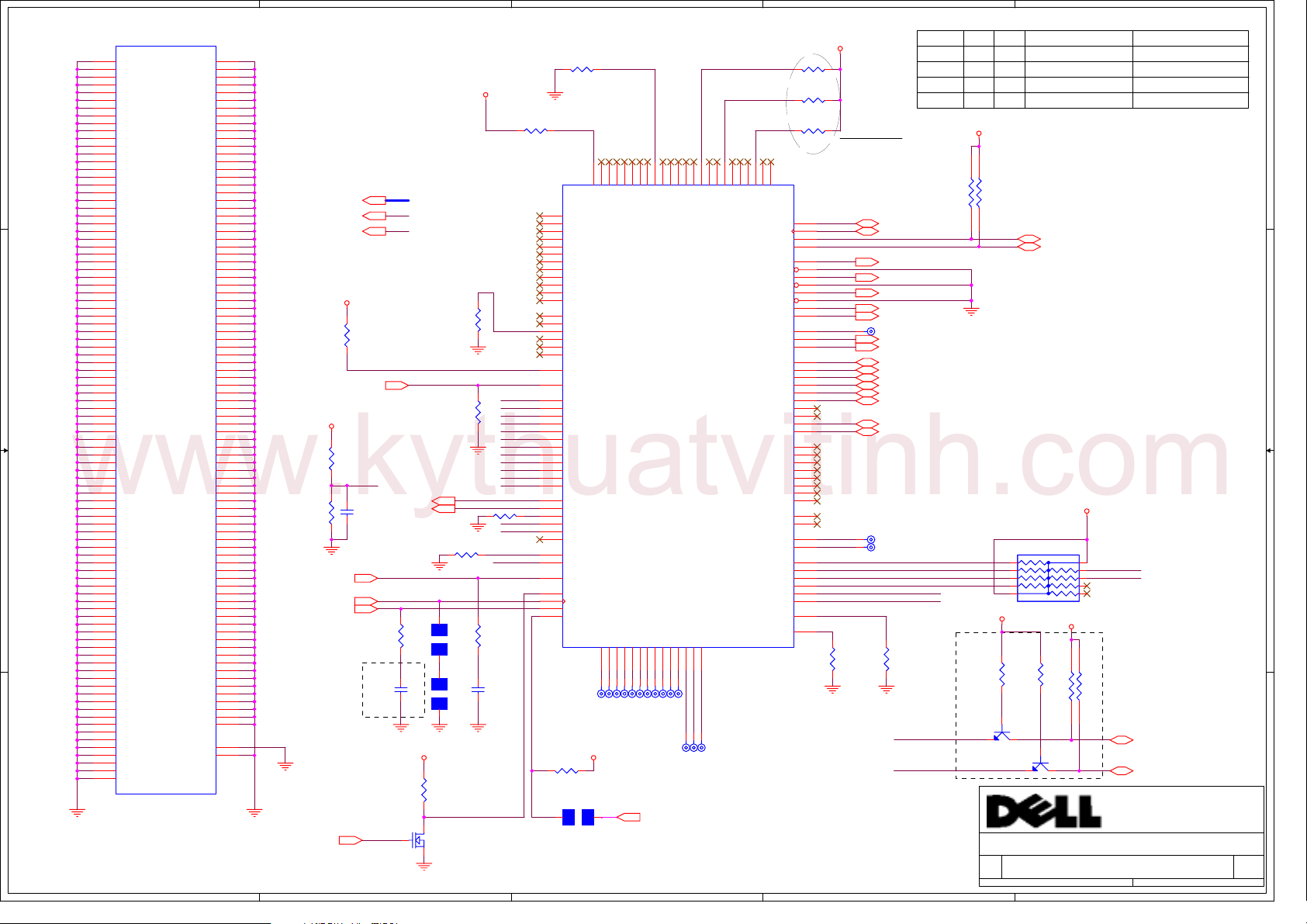

Page 4

A

www.kythuatvitinh.com

4 4

B

C

D

E

ITP Debug Pad

12

R440

54D9R3F

1 2

DUMMY-22D6R3F

1 2

VCC_IO_S0

12

R456

39D2R3F

R441

R453

DUMMY-22D6R3F

VCC_IO_S0

12

C365

DUMMY-SCD1U10V2MX-1

12

R442

150R2

TDI_FLEX

TMS_FLEX

TRST_FLEX

TCK_FLEX

TDO_FLEX

CLK_ITP_CPU#

CLK_ITP_CPU

H_TCK

RESET_FLEX#

CPU ITP Conn.

TP60TPAD28

TP63TPAD28

TP71TPAD28

TP62TPAD28

TP61TPAD28

TP64TPAD28

TP9TPAD28

TP8TPAD28

TP67TPAD28

TP66TPAD28

TP17TPAD28

TP74TPAD28

TP16TPAD28

TP70TPAD28

TP73TPAD28

TP13TPAD28

TP68TPAD28

TP69TPAD28

TP65TPAD28

TP72TPAD28

TCK(PIN A13)

TCK(PIN 5)

FBO(PIN 11)

VCC_IO_S0

12

R454

54D9R3F

H_TDI5

H_TMS5

H_TRST#5

3 3

Should place near conn.

2 2

H_TCK5

H_TDO5

CLK_ITP_CPU#3,5

CLK_ITP_CPU3,5

GTL_CPURST#5,7

R439

27D4R3F

ITP_DBRESET#5

12

GTL_CPURST#

H_BPM5_PREQ#5

H_BPM4_PRDY#5

3D3V_S5

12

R455

150R2

H_BPM3_ITP#5

H_BPM2_ITP#5

H_BPM1_ITP#5

H_BPM0_ITP#5

1 1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Size Document Number Rev

A3

A

B

C

D

Date: Sheet

ITP

Taipei Hsien 221, Taiwan, R.O.C.

MOLOKAI

439Thursday, April 15, 2004

E

SC

of

Page 5

A

www.kythuatvitinh.com

For CPU VCCA[0:3] PLL

place one 0.01u & 10u for

each VCCA pin

12

4 4

DY-SC10U6D3V5MX

3 3

VCC_IO_S0

12

R116

150R2

H_TDI

H_VID[5:0]32

2 2

1 1

BC87

CLK_ITP_CPU3,4

CLK_ITP_CPU#3,4

1D8V_VCCA_S0

1 2

DUMMY-1KR2

TP12

TP11

TPAD28

TPAD28

DUMMY-54D9R3F

12

BC75

SC10U6D3V5MX

CLK_CPU3

CLK_CPU#3

CC_A20M#17

CC_FERR#17

CC_IGNNE#17

CC_INTR17

CC_NMI17

CC_SMI#17

CC_STPCLK#17

R113

CC_CPUSLP#17

H_TCK4

H_TDI4

H_TDO4

12

R131

A

12

BC108

DY-SC10U6D3V5MX

CC_FERR#

TP20

TP10

TPAD28

TP7

TPAD28

TP14

TPAD28

TEST3

TPAD28

TP19

TPAD28

H_TCK

H_TDI

H_TDO

H_VID5

H_VID4

12

H_VID3

H_VID2

H_VID1

R132

H_VID0

DUMMY-54D9R3F

12

BC104

DY-SC10U6D3V5MX

U68D

B15

BCLK0

B14

BCLK1

A16

ITP_CLK0

A15

ITP_CLK1

C2

A20M#

D3

FERR#

A3

IGNNE#

D1

LINT0

D4

LINT1

B4

SMI#

C6

STPCLK#

AC26

VCCA3

N1

VCCA2

B1

VCCA1

F26

VCCA0

B2

RSVD

AF7

RSVD

C14

RSVD

C3

RSVD

C16

RSVD

E1

RSVD

A6

SLP#

A13

TCK

C12

TDI

A12

TDO

AE7

VCCSENSE

AF6

VSSSENSE

H4

VID5

G4

VID4

G3

VID3

F3

VID2

F2

VID1

E2

VID0

BGA479-SKT-2-U

BC106

SCD01U16V2KX

120mA

BC105

SCD01U16V2KX

BPM3#

BPM2#

BPM1#

BPM0#

COMP3

COMP2

COMP1

COMP0

DPSLP#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

PROCHOT#

PWRGOOD

TEST1

TEST2

THERMDA

THERMDC

THERMTRIP#

TMS

TRST#

B

BC86

SCD01U16V2KX

C9

A9

B8

C8

AB1

AB2

P26

P25

B7

AC1

G1

E26

AD26

B17

E4

C5

F23

B18

A18

C17

C11

B13

B

C

CPU VCCA POWER:

At Dothan CPU application, POWER is 1.5V or 1.8V.

1D8V_VCCA_S0

BC90

SCD01U16V2KX

Layout note:

COMP0 and COMP2 need to

H_BPM3_ITP#

H_BPM2_ITP#

H_BPM1_ITP#

H_BPM0_ITP#

27D4-3

27D4-1

27D4-4

27D4-2

CC_PROCHOT#

CC_CPUPWRGD

TEST1

TEST2

H_TMS

12

1 2

1 2

1 2

1 2

TP6

TP15

TPAD28

TPAD28

R115

680R2

H_BPM3_ITP# 4

H_BPM2_ITP# 4

H_BPM1_ITP# 4

H_BPM0_ITP# 4

CC_CPUPWRGD 7,17

H_TMS 4

H_TRST# 4

GTL_IERR#

CC_CPUPWRGD

CC_PROCHOT#

be Zo=27.4ohm traces.

COMP1 and COMP3 should be

routed asx Zo=54.9ohm,

traces shorter than 0.5".

R13554D9R3F

R13627D4R3F

R11054D9R3F

R10927D4R3F

CC_DPSLP# 7,17

C165

SC1000P50V

R450 56R2J

R133 330R2

R114 56R2J

VCC_IO_S0

H_GTLREF_0

2/3 RATIO

THERMDP1 30

THERMDN 30

PM_THERMTRIP# 17

VCC_IO_S0

1 2

1 2

1 2

C

SC: Change

to 1KR2F for

12

GTLREF pass

R108

1KR2F

Voltage divider placed

within 0.5" of CPU pin

via a Zo=55ohm trace.

12

R107

2KR3F

12

D

GTL_D#[15..0]7

GTL_D#15

GTL_D#14

GTL_D#13

GTL_D#12

GTL_D#11

GTL_D#10

GTL_D#9

GTL_D#8

GTL_D#7

GTL_D#6

GTL_D#5

GTL_D#4

GTL_D#3

GTL_D#2

GTL_D#1

GTL_D#0

GTL_DINV#07

GTL_DSTBN#07

GTL_DSTBP#07

GTL_D#[31..16]7 GTL_D#[63..48] 7

C134

DUMMY-SCD1U16V

GTL_DINV#17

GTL_DSTBN#17

GTL_DSTBP#17

GTL_A#[16..3]7

GTL_ADSTB#07

GTL_A#[31..17]7

GTL_ADSTB#17

GTL_D#31

GTL_D#30

GTL_D#29

GTL_D#28

GTL_D#27

GTL_D#26

GTL_D#25

GTL_D#24

GTL_D#23

GTL_D#22

GTL_D#21

GTL_D#20

GTL_D#19

GTL_D#18

GTL_D#17

GTL_D#16

GTL_A#16

GTL_A#15

GTL_A#14

GTL_A#13

GTL_A#12

GTL_A#11

GTL_A#10

GTL_A#9

GTL_A#8

GTL_A#7

GTL_A#6

GTL_A#5

GTL_A#4

GTL_A#3

GTL_A#31

GTL_A#30

GTL_A#29

GTL_A#28

GTL_A#27

GTL_A#26

GTL_A#25

GTL_A#24

GTL_A#23

GTL_A#22

GTL_A#21

GTL_A#20

GTL_A#19

GTL_A#18

GTL_A#17

D

U68C

C25

D15#

E23

D14#

B23

D13#

C26

D12#

E24

D11#

D24

D10#

B24

D9#

C20

D8#

B20

D7#

A21

D6#

B26

D5#

A24

D4#

B21

D3#

A22

D2#

A25

D1#

A19

D0#

D25

DINV0#

C23

DSTBN0#

C22

DSTBP0#

K25

D31#

N25

D30#

H26

D29#

M25

D28#

N24

D27#

L26

D26#

J25

D25#

M23

D24#

J23

D23#

G24

D22#

F25

D21#

H24

D20#

M26

D19#

L23

D18#

G25

D17#

H23

D16#

J26

DINV1#

K24

DSTBN1#

L24

DSTBP1#

U68B

AA2

A16#

Y3

A15#

AA3

A14#

U1

A13#

Y1

A12#

Y4

A11#

W2

A10#

T4

A9#

W1

A8#

V2

A7#

R3

A6#

V3

A5#

U4

A4#

P4

A3#

U3

ADSTB0#

AF1

A31#

AE1

A30#

AF3

A29#

AD6

A28#

AE2

A27#

AD5

A26#

AC6

A25#

AB4

A24#

AD2

A23#

AE4

A22#

AD3

A21#

AC3

A20#

AC7

A19#

AC4

A18#

AF4

A17#

AE5

ADSTB1#

BGA479-SKT-2-U

GTL_D#47

Y25

D47#

GTL_D#46

AA26

D46#

Y23

GTL_D#45

D45#

V26

GTL_D#44

D44#

U25

GTL_D#43

D43#

GTL_D#42

V24

D42#

GTL_D#41

U26

D41#

AA23

GTL_D#40

D40#

R23

GTL_D#39

D39#

GTL_D#38

R26

D38#

R24

GTL_D#37

D37#

GTL_D#36

V23

D36#

GTL_D#35

U23

D35#

GTL_D#34

T25

D34#

GTL_D#33

AA24

D33#

GTL_D#32

Y26

D32#

T24

DINV2#

W25

DSTBN2#

W24

DSTBP2#

AF26

D63#

AF22

D62#

AF25

D61#

AD21

D60#

AE21

D59#

AF20

D58#

AD24

D57#

AF23

D56#

AE22

D55#

AD23

D54#

AC25

D53#

AC22

D52#

AC20

D51#

AB24

D50#

AC23

D49#

AB25

D48#

AD20

DINV3#

AE24

DSTBN3#

AE25

DSTBP3#

BGA479-SKT-2-U

N2

ADS#

L1

BNR#

J3

BPRI#

N4

BR0#

A7

DBR#

M2

DBSY#

L4

DEFER#

H2

DRDY#

K3

HIT#

K4

HITM#

A4

IERR#

B5

INIT#

J2

LOCK#

A10

PRDY#

B10

PREQ#

B11

RESET#

M3

TRDY#

L2

RS2#

K1

RS1#

H1

RS0#

C19

DPWR#

GTL_REQ#4

T1

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

Title

Size Document Number Rev

A3

Date: Sheet

GTL_REQ#3

P1

GTL_REQ#2

T2

GTL_REQ#1

P3

R2

GTL_REQ#0

Banias CPU (1 of 2)

MOLOKAI

E

GTL_D#[47..32] 7

GTL_DINV#2 7

GTL_DSTBN#2 7

GTL_DSTBP#2 7

GTL_D#63

GTL_D#62

GTL_D#61

GTL_D#60

GTL_D#59

GTL_D#58

GTL_D#57

GTL_D#56

GTL_D#55

GTL_D#54

GTL_D#53

GTL_D#52

GTL_D#51

GTL_D#50

GTL_D#49

GTL_D#48

GTL_DINV#3 7

GTL_DSTBN#3 7

GTL_DSTBP#3 7

TP18

TPAD28

GTL_IERR#

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

539Thursday, April 15, 2004

E

GTL_ADS# 7

GTL_BNR# 7

GTL_BPRI# 7

GTL_BR0# 7

ITP_DBRESET# 4

GTL_DBSY# 7

GTL_DEFER# 7

GTL_DRDY# 7

GTL_HIT# 7

GTL_HITM# 7

CC_INIT# 17,27

GTL_LOCK# 7

H_BPM4_PRDY# 4

H_BPM5_PREQ# 4

GTL_CPURST# 4,7

GTL_TRDY# 7

GTL_RS#2 7

GTL_RS#1 7

GTL_RS#0 7

GTL_DPWR# 7

GTL_REQ#[0..4] 7

of

SC

Page 6

A

www.kythuatvitinh.com

U68A

4 4

A11

A14

A17

A20

A23

A26

B12

B16

B19

B22

B25

C10

C13

C15

C18

C21

VSS

VSS

VSS

VSSD2VSSD5VSSD7VSSD9VSS

C24

BGA479-SKT-2-U

VSS

VSS

VSS

VSS

VSS

VSSB3VSSB6VSSB9VSS

VSS

VSS

VSS

VSS

VSSC1VSSC4VSSC7VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSE3VSSE6VSSE8VSS

VSS

E10

D11

D13

D15

D17

D19

D21

D23

E12

D26

E14

VSS

VSS

VSS

VSS

E16

E18

VSS

VSS

E20

AD25

AE3

VSSA2VSSA5VSSA8VSS

VSS

VSS

VSS

VSS

VSSF1VSSF4VSSF5VSSF7VSSF9VSS

E22

E25

AE6

VSS

AE8

VSS

AE10

VSS

AE12

VSS

AE14

VSS

F11

AE16

VSS

VSS

F13

AE18

VSS

VSS

F15

AE20

VSS

VSS

F17

AE23

VSS

VSS

F19

AE26

VSS

VSS

F21

AF2

VSS

AF5

F24

VSS

VSS

AF9

VSS

B

AF11

AF13

VSS

VSS

VSSG6VSSG2VSS

G22

AF15

VSS

VSS

G23

AF17

VSS

VSS

G26

AF19

VSS

AF21

VSS

VSSH5VSSH3VSS

AF24

VSS

H21

VCCD6VCCD8VCC

VSS

VSSJ1VSSJ4VSSJ6VSS

H25

C

D18

D20

D22

E17

E19

E21

F18

F20

F22

G21

H22

J21

K22

V22

W21

Y22

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AB6

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC9

AC11

AC13

AC15

AC17

VCC

VCC

VCCE5VCCE7VCCE9VCC

VCC

VCC

VCCF6VCCF8VCC

VCC

VCC

VCCG5VCC

VCCH6VCC

VCCJ5VCC

VCC

VCCU5VCCV6VCC

VCCW5VCC

VCCY6VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSSK2VSSK5VSS

VSS

VSS

VSSL3VSSL6VSS

VSS

VSSM1VSSM4VSSM5VSS

VSS

VSSN3VSSN6VSS

VSS

VSS

VSSP2VSSP5VSS

VSS

VSSR1VSSR4VSSR6VSS

VSS

VSST3VSST5VSS

VSS

VSS

VSSU2VSSU6VSS

VSS

VSSV1VSSV4VSSV5VSS

VSS

VSSW3VSSW6VSS

VSS

J22

J24

K21

K23

K26

L22

L25

M21

M24

P21

N22

P24

N23

N26

T21

T23

T26

R22

R25

V21

V25

U22

U24

W22

W23

W26

AC19

VCC

VCC

VSS

VSSY2VSSY5VSS

AD8

VCC

AD10

VCC

Y21

AD12

VCC

VSS

Y24

AD14

VCC

VSS

AA1

D

AD16

VCC

VSS

AA4

AD18

VCC

VSS

AA6

AE9

AA8

VCC

VSS

AE11

VCC

VSS

AA10

AE13

VCC

VSS

AA12

VCC_CORE_S0 VCC_IO_S0

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16

VCCP

VCCP

VCCP

VCCP

VCCPK6VCCPL5VCCP

L21

VCCPM6VCCP

AE15

VCC

AE17

VCC

AE19

VCC

AF8

VCC

AF10

VCC

AF12

VCC

AF14

VCC

AF16

VCC

AF18

VCC

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

21A

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB3

AB5

AB7

AA14

AA16

AA18

AA20

AA22

AA25

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

M22

VSS

AC18

N21

VCCPN5VCCP

VSS

AC21

AC24

E

VSS

AD1

P22

VCCPP6VCCP

VSS

VSS

AD4

AD7

R21

VCCPR5VCCP

VSS

VSS

AD9

AD11

T22

U21

VCCPT6VCCP

2.5A

VSS

VSS

AD13

AD15

VCCP

VSS

AD17

P23

VSS

AD19

W4

VCCQ0

VCCQ1

VSS

VSS

AD22

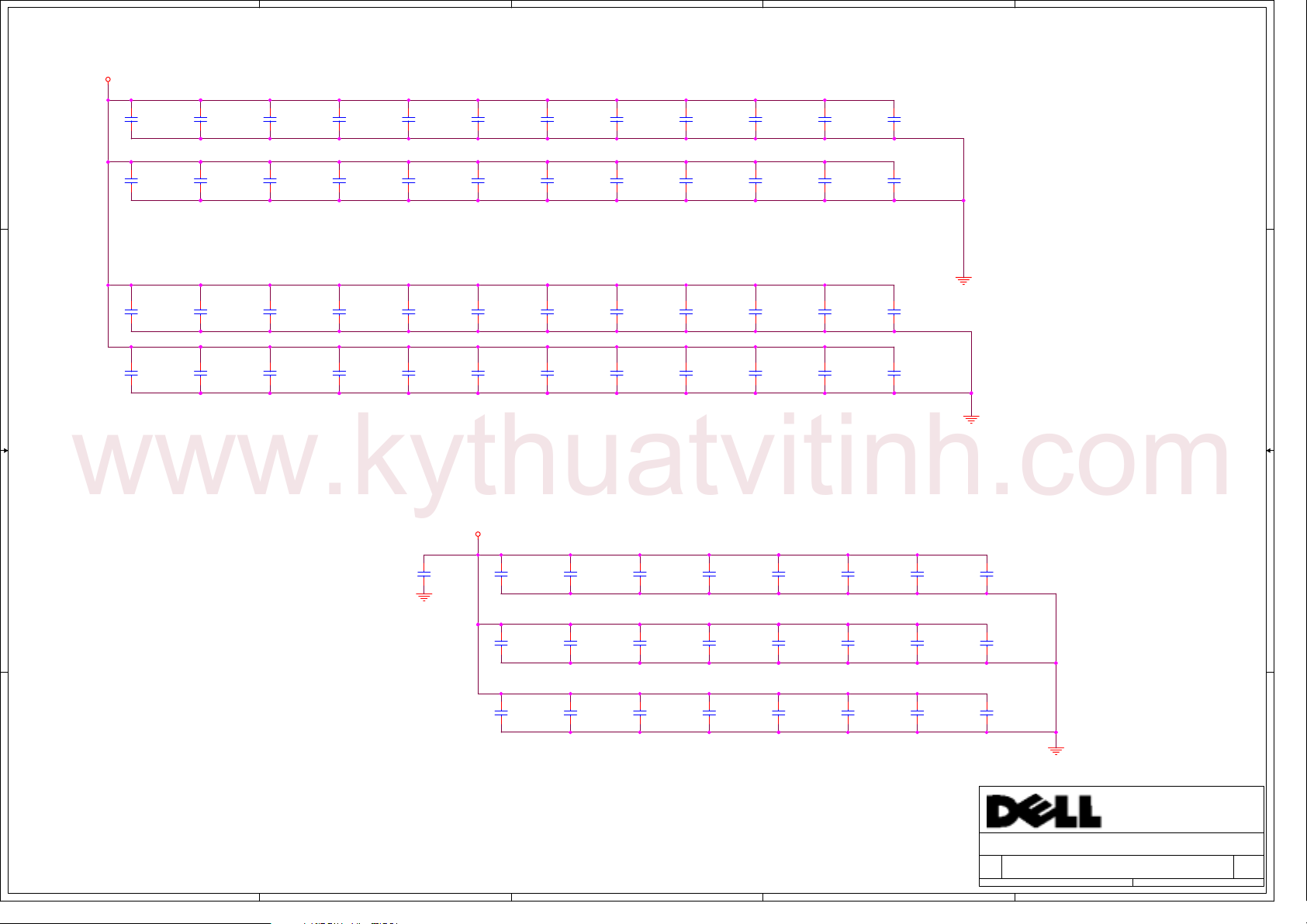

VCC_CORE_S0

3 3

C182

SCD1U10V2MX-1

10uF_6.3V *18 ,0805,X5R

C148

SCD1U10V2MX-1

C149

SCD1U10V2MX-1

C151

SCD1U10V2MX-1

C150

SCD1U10V2MX-1

0.1uF_10V *18 ,0402,X7R

C173

SCD1U10V2MX-1

C172

SCD1U10V2MX-1

C175

SCD1U10V2MX-1

C174

SCD1U10V2MX-1

C177

SCD1U10V2MX-1

C136

SCD1U10V2MX-1

C137

SCD1U10V2MX-1

C135

SCD1U10V2MX-1

C162

SCD1U10V2MX-1

C142

SCD1U10V2MX-1

C143

SCD1U10V2MX-1

C186

SCD1U10V2MX-1

C185

SCD1U10V2MX-1

Place near CPU

VCC_CORE_S0

12

C138

SC10U6D3V5MX

VCC_CORE_S0

12

C181

SC10U6D3V5MX

2 2

VCC_IO_S0

12

C179

SC10U6D3V5MX

12

C153

SC10U6D3V5MX

12

C159

SC10U6D3V5MX

BC99

SCD1U10V2MX-1

12

C155

SC10U6D3V5MX

12

C146

SC10U6D3V5MX

BC98

SCD1U10V2MX-1

12

C152

SC10U6D3V5MX

12

C145

SC10U6D3V5MX

BC188

SCD1U10V2MX-1

BC102

SCD1U10V2MX-1

12

C156

SC10U6D3V5MX

12

C147

SC10U6D3V5MX

0.1uF_10V *10 ,0402,X7R10uF_10V *1 ,0805,X5R

BC103

SCD1U10V2MX-1

12

C154

SC10U6D3V5MX

12

C133

SC10U6D3V5MX

BC89

SCD1U10V2MX-1

12

C178

SC10U6D3V5MX

BC76

SCD1U10V2MX-1

12

C176

SC10U6D3V5MX

POSCAP 100uF_4V*1

BC88

SCD1U10V2MX-1

BC200

SCD1U10V2MX-1

12

C158

SC10U6D3V5MX

C161

SCD1U10V2MX-1

12

C160

SC10U6D3V5MX

DUMMY-ST100U4VBM

12

TC8

12

C141

SC10U6D3V5MX

12

C180

SC10U6D3V5MX

Place near CPU

1 1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Size Document Number Rev

A3

A

B

C

D

Date: Sheet

Banias CPU (2 of 2)

Taipei Hsien 221, Taiwan, R.O.C.

MOLOKAI

639Thursday, April 15, 2004

E

SC

of

Page 7

A

www.kythuatvitinh.com

B

C

D

E

R330

226R3F

R331

147R3F

R332

113R3F

HYSWING

R91

470R2

1

2

34

300R3

A

CPU

ITP

Close to pin

PSWING

1D35V_S0

change

for

MGM+

12

GMCH_PWROK

GTL_A#[31:3]5

C304

SCD01U16V2KX

HLVREF

C306

SCD01U16V2KX

GTL_ADSTB#05

GTL_ADSTB#15

GTL_REQ#[4:0]5

CLK_MCH3

CLK_MCH#3

GTL_ADS#5

GTL_DRDY#5

GTL_DEFER#5

GTL_TRDY#5

GTL_RS#05

GTL_RS#15

GTL_RS#25

PCIRST#_315,17,18,19,20,21,23,27,28

GTL_BR0#5

GTL_BNR#5

GTL_BPRI#5

GTL_DBSY#5

GTL_HITM#5

GTL_HIT#5

GTL_LOCK#5

CC_DPSLP#5,17

GTL_CPURST#4,5

GTL_DPWR#5

HL_[10:0]16

HL_STB16

HL_STB#16

1 2

R421 27D4R3F

1 2

R94 27D4R3F

1 2

CC_CPUPWRGD 5,17

HXRCOMP,HYRCOMP as

18mil wide trace

AC18

AD14

AD13

AD17

AD11

AC13

AD8

AD7

AC6

AC5

AC19

AD5

AB5

AD16

AC12

AF11

AD10

AD25

AC24

AC21

AD22

AD20

AD23

AD26

AC22

AC25

AC7

AB7

AC9

AC10

AB2

AA2

AC26

AB25

AC3

AD4

AC2

AD2

AB23

AB24

AA3

AB4

AH27

AH28

AH26

AE26

AG28

AF28

AG26

AF26

AE27

AD27

AD15

AH15

AG14

AE14

AE17

AG16

AH14

AE15

AF16

AF17

AJ22

AJ19

U61A

SMA[0]

SMA[1]

SMA[2]

SMA[3]

SMA[4]

SMA[5]

SMA[6]

SMA[7]

SMA[8]

SMA[9]

SMA[10]

SMA[11]

SMA[12]

SMAB[1]

SMAB[2]

SMAB[4]

SMAB[5]

SWE#

SCAS#

SRAS#

SBA[0]

SBA[1]

SCS[0]#

SCS[1]#

SCS[2]#

SCS[3]#

SCKE[0]

SCKE[1]

SCKE[2]

SCKE[3]

SCK[0]

SCK[0]#

SCK[1]

SCK[1]#

SCK[2]

SCK[2]#

SCK[3]

SCK[3]#

SCK[4]

SCK[4]#

SCK[5]

SCK[5]#

SDQS[7]

SDM[7]

SDQ[56]

SDQ[57]

SDQ[58]

SDQ[59]

SDQ[60]

SDQ[61]

SDQ[62]

SDQ[63]

SDQS[8]

SDM[8]

SDQ[64]

SDQ[65]

SDQ[66]

SDQ[67]

SDQ[68]

SDQ[69]

SDQ[70]

SDQ[71]

SMVSWINGL

SMVSWINGH

MONTARA-GM

D

DDR

MEMORY

Title

Size Document Number Rev

A3

Date: Sheet

SDQS[0]

SDQS[1]

SDQ[10]

SDQ[11]

SDQ[12]

SDQ[13]

SDQ[14]

SDQ[15]

SDQS[2]

SDQ[16]

SDQ[17]

SDQ[18]

SDQ[19]

SDQ[20]

SDQ[21]

SDQ[22]

SDQ[23]

SDQS[3]

SDQ[24]

SDQ[25]

SDQ[26]

SDQ[27]

SDQ[28]

SDQ[29]

SDQ[30]

SDQ[31]

SDQS[4]

SDQ[32]

SDQ[33]

SDQ[34]

SDQ[35]

SDQ[36]

SDQ[37]

SDQ[38]

SDQ[39]

SDQS[5]

SDQ[40]

SDQ[41]

SDQ[42]

SDQ[43]

SDQ[44]

SDQ[45]

SDQ[46]

SDQ[47]

SDQS[6]

SDQ[48]

SDQ[49]

SDQ[50]

SDQ[51]

SDQ[52]

SDQ[53]

SDQ[54]

SDQ[55]

SMRCOMP

SMVREF_0

U61C

P23

HA[3]#

T25

GTL_A#4

GTL_A#5

GTL_A#6

GTL_A#7

GTL_A#8

GTL_A#9

GTL_A#10

GTL_A#11

GTL_A#12

GTL_A#13

GTL_A#14

GTL_A#15

GTL_A#16

GTL_A#17

GTL_A#18

GTL_A#19

GTL_A#20

GTL_A#21

GTL_A#22

GTL_A#23

GTL_A#24

GTL_A#25

GTL_A#26

GTL_A#27

GTL_A#28

GTL_A#29

GTL_A#30

GTL_A#31

GTL_REQ#0

GTL_REQ#1

GTL_REQ#2

GTL_REQ#3

GTL_REQ#4

GMCH_PWROK

HL_0

HL_1

HL_2

HL_3

HL_4

HL_5

HL_6

HL_7

HL_8

HL_9

HL_10

HLVREF SMRCOMP

R329

HLZCOMP

37D4R3F

HYRCOMP

HXRCOMP

PSWING

HYSWING

HXSWING

R27

U23

U24

R24

U28

V28

U27

V27

U25

V26

V25

V23

W25

AA27

W24

W23

W27

AA28

W28

AB27

AB28

AA26

R28

P25

R23

R25

AE29

AD29

N24

M28

M25

N23

P26

M27

AD28

M23

N25

P28

M26

N28

N27

P27

AA22

H28

B20

K28

B18

T28

T27

Y24

Y25

Y27

Y26

T26

T23

L28

Y23

F15

J11

U7

U4

U3

V3

W2

W6

V6

W7

T3

V5

V4

W3

V2

W1

T2

U2

F7

HA[4]#

HA[5]#

HA[6]#

HA[7]#

HA[8]#

HA[9]#

HA[10]#

HA[11]#

HA[12]#

HA[13]#

HA[14]#

HA[15]#

HA[16]#

HA[17]#

HA[18]#

HA[19]#

HA[20]#

HA[21]#

HA[22]#

HA[23]#

HA[24]#

HA[25]#

HA[26]#

HA[27]#

HA[28]#

HA[29]#

HA[30]#

HA[31]#

HADSTB[0]#

HADSTB[1]#

HREQ[0]#

HREQ[1]#

HREQ[2]#

HREQ[3]#

HREQ[4]#

BCLK

BCLK#

ADS#

DRDY#

DEFER#

HTRDY#

RS[0]#

RS[1]#

RS[2]#

RSTIN#

BREQ0#

BNR#

BPRI#

DBSY#

HITM#

HIT#

HLOCK#

DPSLP#

CPURST#

PWROK

DPWR#

HL[0]

HL[1]

HL[2]

HL[3]

HL[4]

HL[5]

HL[6]

HL[7]

HL[8]

HL[9]

HL[10]

HLSTB

HLSTB#

HLVREF

HLZCOMP

HYRCOMP

HXRCOMP

PSWING

HYSWING

HXSWING

AGPBUSY#

HOST

HUB LINK

B

HDSTBP[0]#

HDSTBN[0]#

HDSTBP[1]#

HDSTBN[1]#

HDSTBP[2]#

HDSTBN[2]#

HDSTBP[3]#

HDSTBN[3]#

MONTARA-GM

HD[0]#

HD[1]#

HD[2]#

HD[3]#

HD[4]#

HD[5]#

HD[6]#

HD[7]#

HD[8]#

HD[9]#

HD[10]#

HD[11]#

HD[12]#

HD[13]#

HD[14]#

HD[15]#

DINV[0]#

HD[16]#

HD[17]#

HD[18]#

HD[19]#

HD[20]#

HD[21]#

HD[22]#

HD[23]#

HD[24]#

HD[25]#

HD[26]#

HD[27]#

HD[28]#

HD[29]#

HD[30]#

HD[31]#

DINV[1]#

HD[32]#

HD[33]#

HD[34]#

HD[35]#

HD[36]#

HD[37]#

HD[38]#

HD[39]#

HD[40]#

HD[41]#

HD[42]#

HD[43]#

HD[44]#

HD[45]#

HD[46]#

HD[47]#

DINV[2]#

HD[48]#

HD[49]#

HD[50]#

HD[51]#

HD[52]#

HD[53]#

HD[54]#

HD[55]#

HD[56]#

HD[57]#

HD[58]#

HD[59]#

HD[60]#

HD[61]#

HD[62]#

HD[63]#

DINV[3]#

HDVREF[0]

HDVREF[1]

HDVREF[2]

HAVREF

HCCVREF

K22

H27

K25

L24

J27

G28

L27

L23

L25

J24

H25

K23

G27

K26

J23

H26

K27

J28

J25

F25

F26

B27

H23

E27

G25

F28

D27

G24

C28

B26

G22

C26

E26

G23

B28

D26

C27

E25

B21

G21

C24

C23

D22

C25

E24

D24

G20

E23

B22

B23

F23

F21

C20

C21

E21

E22

B25

G18

E19

E20

G17

D20

F19

C19

C17

F17

B19

G16

E16

C16

E17

D16

C18

E18

D18

G19

K21

J21

J17

Y22

Y28

GTL_D#0GTL_A#3

GTL_D#1

GTL_D#2

GTL_D#3

GTL_D#4

GTL_D#5

GTL_D#6

GTL_D#7

GTL_D#8

GTL_D#9

GTL_D#10

GTL_D#11

GTL_D#12

GTL_D#13

GTL_D#14

GTL_D#15

GTL_D#16

GTL_D#17

GTL_D#18

GTL_D#19

GTL_D#20

GTL_D#21

GTL_D#22

GTL_D#23

GTL_D#24

GTL_D#25

GTL_D#26

GTL_D#27

GTL_D#28

GTL_D#29

GTL_D#30

GTL_D#31

GTL_D#32

GTL_D#33

GTL_D#34

GTL_D#35

GTL_D#36

GTL_D#37

GTL_D#38

GTL_D#39

GTL_D#40

GTL_D#41

GTL_D#42

GTL_D#43

GTL_D#44

GTL_D#45

GTL_D#46

GTL_D#47

GTL_D#48

GTL_D#49

GTL_D#50

GTL_D#51

GTL_D#52

GTL_D#53

GTL_D#54

GTL_D#55

GTL_D#56

GTL_D#57

GTL_D#58

GTL_D#59

GTL_D#60

GTL_D#61

GTL_D#62

GTL_D#63

HDVREF

HAVREF

HCCVREF

GTL_D#[63..0] 5

GTL_DSTBP#0 5

GTL_DSTBN#0 5

GTL_DINV#0 5

GTL_DSTBP#1 5

GTL_DSTBN#1 5

GTL_DINV#1 5

GTL_DSTBP#2 5

GTL_DSTBN#2 5

GTL_DINV#2 5

GTL_DSTBP#3 5

GTL_DSTBN#3 5

GTL_DINV#3 5

HDVREF 9

HAVREF 9

HCCVREF 9AGPBUSY#17

C

R380

604R3F

R378

150R3F

R379

150R3F

R381

604R3F

M_A[12..0]10,12

2D5V_S3

12

12

2D5V_S3

12

12

M_AB110,12

M_AB210,12

M_AB410,12

M_AB510,12

M_WE#10,12

M_CAS#10,12

M_RAS#10,12

M_BS0#10,12

M_BS1#10,12

M_CS0_R#10,12

M_CS1_R#10,12

M_CS2_R#10,12

M_CS3_R#10,12

M_CKE0_R#10,12

M_CKE1_R#10,12

M_CKE2_R#10,12

M_CKE3_R#10,12

CLK_DDR010

CLK_DDR0#10

CLK_DDR110

CLK_DDR1#10

CLK_DDR210

CLK_DDR2#10

CLK_DDR310

CLK_DDR3#10

CLK_DDR410

CLK_DDR4#10

CLK_DDR510

CLK_DDR5#10

SMVSWINGL

12

12

C337

SCD1U10V2MX-1

SMVSWINGH

C335

SCD1U10V2MX-1

M_A0

M_A1

M_A2

M_A3

M_A4

M_A5

M_A6

M_A7

M_A8

M_A9

M_A10

M_A11

M_A12

M_DQS7

M_DM7

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

M_DQS8

M_DM8

M_DATA64

M_DATA65

M_DATA66

M_DATA67

M_DATA68

M_DATA69

M_DATA70

M_DATA71

AG2

AE5

SDM[0]

AF2

SDQ[0]

AE3

SDQ[1]

AF4

SDQ[2]

AH2

SDQ[3]

AD3

SDQ[4]

AE2

SDQ[5]

AG4

SDQ[6]

AH3

SDQ[7]

AH5

AE6

SDM[1]

AD6

SDQ[8]

AG5

SDQ[9]

AG7

AE8

AF5

AH4

AF7

AH6

AH8

AE9

SDM[2]

AF8

AG8

AH9

AG10

AH7

AD9

AF10

AE11

AE12

AH12

SDM[3]

AH10

AH11

AG13

AF14

AG11

AD12

AF13

AH13

AH17

AD19

SDM[4]

AH16

AG17

AF19

AE20

AD18

AE18

AH18

AG19

AE21

AD21

SDM[5]

AH20

AG20

AF22

AH22

AF20

AH19

AH21

AG22

AH24

AD24

SDM[6]

AE23

AH23

AE24

AH25

AG23

AF23

AF25

AG25

AB1

AJ24

Montara (1 of 3)

M_DQS0

M_DM0

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DQS1

M_DM1

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DQS2

M_DM2

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DQS3

M_DM3

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DQS4

M_DM4

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DQS5

M_DM5

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DQS6

M_DM6

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

SMRCOMP

C347

SCD1U10V2MX-1

12

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

MOLOKAI

E

M_DATA[71..0] 12

M_DQS[8..0] 12

M_DM[8..0] 12

2D5V_S3

12

R334

60D4R3F

12

R333

60D4R3F

1D25V_DDRVREF_S3

C345

SCD01U16V2KX

12

739Thursday, April 15, 2004

of

SCD1U10V2MX-1

12

C308

SC

GMCH

CPURST#

(GTL_CPURST#)

12

12

VCC_IO_S0

R422

R423

VCC_IO_S0

R92

R93

3D3V_S0

3D3V_S0

C303

1 2

C305

12

12

12

12

6

5

1D5V_S0

12

12

12

12

C352

SCD1U10V2MX-1

HXSWING

12

C103

SCD1U10V2MX-1

Q20

UMX1N-U

1 2

R72

4 4

SCD1U10V2MX-1

SCD1U10V2MX-1

3 3

301R3F

150R3F

2 2

301R3F

150R3F

R70

470R2

1 1

Page 8

A

www.kythuatvitinh.com

U61E

AA29

VSS

W29

VSS

U29

VSS

N29

VSS

L29

VSS

J29

VSS

G29

VSS

E29

VSS

4 4

3 3

2 2

1 1

C29

AE28

AC28

E28

D28

AJ27

AG27

AC27

F27

A27

AJ26

AB26

W26

U26

R26

N26

G26

AE25

AA25

D25

A25

AG24

AA24

V24

T24

P24

M24

K24

H24

F24

B24

AJ23

AC23

AA23

D23

A23

AE22

W22

U22

R22

N22

F22

C22

AG21

AB21

AA21

Y21

V21

T21

P21

M21

H21

D21

A21

AJ20

AC20

AA20

F20

AE19

AB19

H19

D19

A19

AJ18

AG18

AA18

F18

AC17

AB17

U17

R17

N17

H17

D17

A17

AE16

AA16

T16

P16

L26

J26

L22

J22

J20

J18

J16

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

MONTARA-GM

A

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSADAC

VSSALVDS

AE13

AB13

U13

R13

N13

H13

F13

D13

A13

AJ12

AG12

AA12

J12

AJ11

AC11

AB11

H11

F11

D11

AJ10

AE10

AA10

J10

C10

AG9

AB9

W9

U9

T9

R9

N9

L9

E9

AC8

Y8

V8

T8

P8

K8

H8

AJ7

AE7

AA7

R7

M7

J7

G7

E7

C7

AG6

Y6

L6

Y5

U5

B5

AE4

AC4

AA4

W4

T4

N4

K4

G4

D4

AJ3

AG3

R2

AJ1

AE1

AA1

U1

L1

G1

C1

F16

AG15

AB15

U15

R15

N15

H15

D15

AC14

AA14

T14

P14

J14

B8

B11

DEFAULT NOT USE TV ENCODER

IF USE TV ENCODER ADD R63 ,REMOVE

R76 AND R66

TV_D[0..11]15

TV_HSYNC15

TV_VSYNC15

1D5V_S0

R326

100KR2

1D5V_S0

R324

1KR2F

1 2

R325

1KR2F

1 2

CLK66_GMCH3

CLK48_DREF_GMCH3

CLK66_DREF_GMCH3

SB: for SIV pass

PM_SUS_CLK17,30

1 2

TV_STALL15

GVREF

12

C301

SCD1U10V2MX-1

R95

10R2

SC2D2P50V2CN

B

1D5V_S0

R76

1 2

DUMMY-1KR2

R3

R5

R6

R4

P6

P5

N5

P2

N2

N3

M1

TV_D0

TV_D1

TV_D2

TV_D3

TV_D4

TV_D5

TV_D6

TV_D7

TV_D8

TV_D9

TV_D10

TV_D11

TV_HSYNC

TV_VSYNC

DVORCOMP

GVREF

M5

P3

P4

M2

T6

T5

L2

G2

M3

K5

K1

K3

K2

H2

H1

H3

H4

H6

G3

H5

K6

L5

L3

D1

F1

Y3

D5

B7

B17

D6

MONTARA-GM

12

R328

100KR2

12

R66

DUMMY-100KR2

TV_CLK15

TV_CLK#15

12

12

C102

1D5V_S0 3D3V_S0

12

1KR2

1

G

2 3

B

1 2

12

R62

12

C58

R59

D

Q19

2N7002

S

TV_CLK

TV_CLK#

100KR2

40D2R3F

R323

DUMMY-R2

DUMMY-C2

CLK48_DPMS

1 2

R64

12

R67

10R2

SC10P50V2JN-1

C63

12

R63

1KR2

DVODETECT

U61B

DVOBD[0]

DVOBD[1]

DVOBD[2]

DVOBD[3]

DVOBD[4]

DVOBD[5]

DVOBD[6]

DVOBD[7]

DVOBD[8]

DVOBD[9]

DVOBD[10]

DVOBD[11]

DVOBCLK

DVOBCLK#

DVOBFLDSTL

DVOBHSYNC

DVOBVSYNC

DVOBBLANK#

DVOBCINTR#

DVOBCCLKINT

DVOCD[0]

DVOCD[1]

DVOCD[2]

DVOCD[3]

J6

DVOCD[4]

J5

DVOCD[5]

DVOCD[6]

DVOCD[7]

DVOCD[8]

DVOCD[9]

DVOCD[10]

DVOCD[11]

J3

DVOCCLK

J2

DVOCCLK#

DVOCFLDSTL

DVOCHSYNC

DVOCVSYNC

DVOCBLANK#

DVORCOMP

GVREF

GCLKIN

DPMS

DREFCLK

DREFSSCLK

EXTTS_0

R71

10KR2F-U

R73

1 2

DUMMY-R2

C

12

ADDID7

F12

RSVDL7RSVDE5RSVDF5RSVDE3RSVDE2RSVDG5RSVDF4RSVDG6RSVDF6RSVD

DVOB CRT

VIDEO

DVOC

NC

NC

NC

NC

NC

NC

NC

AJ4NCAJ2

B29NCA29

A28

AA9

AJ29

AJ28

AH29

TP2

TP58

TP57

TP56

TP55

TP59

TP54

TP46

TP47

TPAD28

TPAD28

TPAD28

TPAD28

TPAD28

TPAD28

TPAD28

12

PM_THRM# 17,30

C

D12

B12

AA5

RSVD

RSVD

RSVD

RSVDL4RSVDC4RSVDF3RSVDD3RSVDC3RSVDB3RSVDF2RSVDD2RSVDC2RSVDB2RSVD

LVDS

NCA2NC

NCB1NC

AH1

AC16NCAC15

TP44

TP48

M_RCVI#

M_RCVO#

TPAD28

TPAD28

TPAD28

TPAD28

DDR Feedback(inside the package)

Route transitioned to buttom

TP4

TP3

TP45

side with vias near ball

TPAD28

TPAD28

TPAD28

GST[0]

GST[1]

GST[2]

D7

DDCA_DATA

DDCA_CLK

DDCPDATA

DDCPCLK

RED

RED#

GREEN

GREEN#

BLUE

BLUE#

HSYNC

VSYNC

PANELBKLTCTL

PANELBKLTEN

PANELVDDEN

IYAP[0]

IYAM[0]

IYAP[1]

IYAM[1]

IYAP[2]

IYAM[2]

IYAP[3]

IYAM[3]

ICLKAP

ICLKAM

IYBP[0]

IYBM[0]

IYBP[1]

IYBM[1]

IYBP[2]

IYBM[2]

IYBP[3]

IYBM[3]

ICLKBM

ICLKBP

LCLKCTLA

LCLKCTLB

MDDCCLK

MDDCDATA

MDVICLK

MDVIDATA

MI2CCLK

MI2CDATA

REFSET

LIBG

R61

1 2

DUMMY-1KR2

R60

1 2

DUMMY-1KR2

R40

1 2

DUMMY-1KR2

G9

B6

C5

B4

A7

A8

C8

D8

C9

D9

H10

J9

G8

F8

A5

F14

G14

E14

E15

C14

C15

B13

C13

E13

D14

G12

H12

E11

E12

C11

C12

G10

G11

E10

F10

H9

LCLKCTLA

LCLKCTLB

C6

P7

T7

N7

M6

K7

N6

E8

A10

1D5V_S0

BL_PWM

REFSET

12

R75

1K5R3F

D

DAT_DDC1 13

CLK_DDC1 13

DAC_RED 13

DAC_GREEN 13

DAC_BLUE 13

DAC_HSYNC 13

DAC_VSYNC 13

TP1

TPAD28

NB_BL_ON 14

LCDVDD_ON 14

TXOUT0+ 14

TXOUT0- 14

TXOUT1+ 14

TXOUT1- 14

TXOUT2+ 14

TXOUT2- 14

TXCLK+ 14

TXCLK- 14

TP183

TPAD28

TPAD28

TP184

12

D

FOR MGM+

change

for

MGM+

MI2CCLK

MI2CDATA

R65

127R3F

MI2CCLK

MI2CDATA

GST[2:0]

000

001

010

111

MDDCCLK

MDDCDATA

MDVI_CLK

MDVI_DAT

E

internal pull down

DDRFSB Gfx Core Clock Low Gfx Core Clock High

400 266 133 200

400

400

3D3V_S0

3

2

RN5

SRN2D7KJ

1 4

200

333400

100200

100

DAT_DDC_EDID 14

CLK_DDC_EDID 14

200

133

250166

short trace

1D5V_S0

RP1

1

2

3

4

5 6

SRP2K2

1D5V_S0

12

R677

R678

2K7R2J

2K7R2J

1

CHT2222A

Q62

3

2

CHT2222A

Q63

2

Title

Size Document Number Rev

A3

Date: Sheet

10

MI2CCLK

9

MI2CDATA

8

7

3D3V_S0

12

3

RN74

SRN8K2J

2

1 4

1

3

Montara (2 of 3)

MOLOKAI

SB:03/03/2004

TV_I2C_CLK 15

TV_I2C_DATA 15

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

839Thursday, April 15, 2004

E

of

SC

Page 9

A

www.kythuatvitinh.com

B

C

D

E

AG29

AF29

AC29

AF27

AJ25

AF24

AB22

AJ21

AF21

AB20

AF18

AB18

AJ17

AB16

AF15

AB14

AJ13

AA13

AF12

AB12

AA11

AB10

AJ9

AF9

Y9

AB8

AA8

Y7

AF6

AB6

AA6

AJ5

Y4

AF3

AB3

AG1

AC1

AJ8

AJ6

AF1

AD1

V29

M29

H29

A24

A22

AB29

Y29

K29

F29

A26

V22

T22

P22

M22

H22

U21

R21

N21

L21

H20

A20

J19

H18

A18

H16

G15

2D5V_S3

12

SCD1U10V2MX-1

12

SCD1U10V2MX-1

C354 SCD1U10V2MX-1

C353 SCD1U10V2MX-1

C350 SCD1U10V2MX-1

C129 SCD1U10V2MX-1

C104 SCD1U10V2MX-1

12

C336

C316

2D5V_VCC_QSM_S3

12

C328

SCD1U10V2MX-1

1D2V_VCC_ASM_S0

12

1 2

1 2

1 2

1 2

1 2

C131

SC10U6D3V5MX

DUMMY-ST100U4VBM

12

C357

SCD1U10V2MX-1

12

C330

SCD1U10V2MX-1

C310

SCD1U10V2MX-1

12

12

12

SCD1U10V2MX-1

12

SCD1U10V2MX-1

12

C312

SC10U6D3V5MX

VSS_QSM_GND

12

C108

SC10U6D3V5MX

TC6

C358

C329

1 2

IND-D68UH-6

C307

SC10U6D3V5MX

12

C110

SCD1U10V2MX-1

12

C139

SCD1U10V2MX-1

12

C311

SCD1U10V2MX-1

12

C338

SCD1U10V2MX-1

2D5V_S3

L16

R335

1 2

1R5

1 2

DUMMY-ST100U4VBM

12

TC11

VCC_IO_S0

12

C105

SCD1U10V2MX-1

12

C163

SCD1U10V2MX-1

12

C309

SCD1U10V2MX-1

1D35V_S0

L15

IND-1UH-6

12

C77

SCD1U10V2MX-1

TC12

ST220U4VDM-6

SC: populate

220uF for 2.5V

undershoot

issue.

12

C184

SCD1U10V2MX-1

12

C140

SCD1U10V2MX-1

12

12

C76

SCD1U10V2MX-1

ST100U4VBM

12

TC14

1D5V_S0

12

C85

SC10U6D3V5MX

12

SCD1U10V2MX-1

L17

1 2

IND-D1UH

L4

1 2

IND-D1UH

1D35V_S0

12

C82

SC10U6D3V5MX

1D35V_S0

12

C112

DUMMY-SC22U10V-1

C59

12

12

12

C64

SCD1U10V2MX-1

Cap for

VCCAGPLL

12

C74

SCD1U10V2MX-1

C80

SC10U6D3V5MX

12

C86

SCD1U10V2MX-1

1D5V_S0

12

C81

SCD1U10V2MX-1

TC13

ST100U4VBM

1D2V_ADPLLB-1_S0

TC15

ST100U4VBM

12

C60

SCD1U10V2MX-1

12

TC3

ST100U4VBM

2D5V_S3

12

C87

SCD1U10V2MX-1

1D5V_S0

12

C315

SCD1U10V2MX-1

12

C101

SCD1U10V2MX-1

1D35V_S0

12

C107

SCD1U10V2MX-1

Cap for

VCCAHPLL

1D2V_ADPLLA-1_S0

1D5V_S0

3D3V_S0

1D35V_S0

12

C72

SC10U6D3V5MX

4 4

12

C61

SCD01U16V2KX

12

C56

SC10U6D3V5MX

1D35V_S0

C65

SCD1U10V2MX-1

12

C84

SCD1U10V2MX-1

12

C114

SCD1U10V2MX-1

12

C113

SCD1U10V2MX-1

3 3

Caps for VCCALVDS

12

Caps for VCCGPIO

12

2 2

Caps for VCCHL

12

C78

SCD1U10V2MX-1

C57

SCD1U10V2MX-1

C83

SC10U6D3V5MX

1D5V_S0

3D3V_S0

12

12

C313

SC10U6D3V5MX

SC10U6D3V5MX

C130

SCD1U10V2MX-1

SC: Populate

C331 for 2.5V

undershoot

issue

12

12

C79

1D35V_S0

1 2

1D35V_S0

1 2

12

C109

SCD1U10V2MX-1

DUMMY-SC22U10V-1

ST100U4VBM

C331

12

R356

1R5

ESR<50mohm,ESL<2.5mH

TC8,C78 on the same s ide

R74

1R5

ESR<50mohm,ESL<2.5mH

TC9,C81 on the same s ide

C297

DUMMY-SC47U10V-1

12

C302

1D2V_ADPLLA_S0

1D2V_ADPLLB_S0

W21

AA19

AA17

U16

R16

N16

AA15

U14

R14

N14

H14

D10

G13

D29

T17

P17

T15

P15

T13

P13

A12

B10

B15

B14

A11

B16

P9

M9

K9

R8

N8

M8

L8

J8

H7

E6

M4

J4

E4

N1

J1

E1

J15

F9

J13

A6

Y2

B9

A9

A3

A4

V9

W8

U8

V7

U6

W5

Y1

V1

U61D

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

90mA

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCC

VCC

VCC

VCC

VCC

POWER

VCC

VCC

VCC

VCC

2.24A

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCTXLVDS

VCCTXLVDS

50mA

VCCTXLVDS

VCCTXLVDS

VCCDLVDS

VCCDLVDS

40mA

VCCDLVDS

VCCDLVDS

70mA

VCCALVDS

VCCADPLLA

VCCADPLLB

VCCAGPLL

VCCAHPLL

VCCADAC

70mA

VCCADAC

VCCGPIO

20mA

VCCGPIO

VCCHL

VCCHL

VCCHL

VCCHL

90mA

VCCHL

VCCHL

VCCHL

VCCHL

25mA

90mA

690mA

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCQSM

VCCQSM

VCCASM

VCCASM

VTTHF

VTTHF

VTTHF

VTTHF

VTTHF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

MONTARA-GM

C73

SCD1U10V2MX-1

1D5V_S0

A

C75

SCD01U16V2KX

12

C355

SCD1U10V2MX-1

Caps for VCCADAC

12

1 1

This two cap chould connect to

VSSADAC first then to GND

Reference Voltage: 2/3 Vcc_IO_S0

12

R425

49D9R3F

12

12

BC199

SC1U10V3KX

B

R424

100R3F

12

BC65

SC1U10V3KX

12

C111

SCD1U10V2MX-1

12

12

R99

49D9R3F

R98

100R3F

C

VCC_IO_S0VCC_IO_S0VCC_IO_S0

12

R96

49D9R3F

HDVREF7HAVREF7HCCVREF7

HDVREFHAVREFHCCVREF

12

C106

SCD1U10V2MX-1

12

BC64

SC1U10V3KX

12

R97

100R3F

D

Title

Size Document Number Rev

A3

Date: Sheet

Montara (3 of 3)

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

MOLOKAI

939Thursday, April 15, 2004

E

SC

of

Page 10

A

www.kythuatvitinh.com

DIMM1 DIMM2

DM1

112

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10 / AP

100

A11

99

A12

117

BA0

116

BA1

5

DQ0

7

DQ1

13

DQ2

17

DQ3

6

DQ4

8

DQ5

14

DQ6

18

DQ7

19

DQ8

23

DQ9

29

DQ10

31

DQ11

20

DQ12

24

DQ13

30

DQ14

32

DQ15

41

DQ16

43

DQ17

49

DQ18

53

DQ19

42

DQ20

44

DQ21

50

DQ22

54

DQ23

55

DQ24

59

DQ25

65

DQ26

67

DQ27

56

DQ28

60

DQ29

66

DQ30

68

DQ31

127

DQ32

129

DQ33

135

DQ34

139

DQ35

128

DQ36

130

DQ37

136

DQ38

140

DQ39

141

DQ40

145

DQ41

151

DQ42

153

DQ43

142

DQ44

146

DQ45

152

DQ46

154

DQ47

163

DQ48

165

DQ49

171

DQ50

175

DQ51

164

DQ52

166

DQ53

172

DQ54

176

DQ55

177

DQ56

181

DQ57

187

DQ58

189

DQ59

178

DQ60

182

DQ61

188

DQ62

190

DQ63

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

85

NC

86

NC/(RESET#)

97

NC/A13

98

NC/BA2

123

NC

124

NC

200

NC

118

/RAS

120

/CAS

119

/WE

1

VREF

2

VREF

197

VDDSPD

199

VDDID

202

GND

SKTSODIMM200-1U1

62.10017.311

121

/CS0

122

/CS1

96

CKE0

95

CKE1

11

DQS0

25

DQS1

47

DQS2

61

DQS3

133

DQS4

147

DQS5

169

DQS6

183

DQS7

77

DQS8

12

DM0

26

DM1

48

DM2

62

DM3

134

DM4

148

DM5

170

DM6

184

DM7

78

DM8

35

CK0

37

/CK0

160

CK1

158

/CK1

89

CK2

91

/CK2

195

SCL

193

SDA

194

SA0

196

SA1

198

SA2

9

VDD

10

VDD

21

VDD

22

VDD

33

VDD

34

VDD

36

VDD

45

VDD

46

VDD

57

VDD

58

VDD

69

VDD

70

VDD

81

VDD

82

VDD

92

VDD

93

VDD

94

VDD

113

VDD

114

VDD

131

VDD

132

VDD

143

VDD

144

VDD

155

VDD

156

VDD

157

VDD

167

VDD

168

VDD

179

VDD

180

VDD

191

VDD

REVERSE TYPE

192

VDD

3

VSS

4

VSS

15

VSS

16

VSS

27

VSS

28

VSS

38

VSS

39

VSS

40

VSS

51

VSS

52

VSS

63

VSS

64

VSS

75

VSS

76

VSS

87

VSS

88

VSS

90

VSS

103

VSS

104

VSS

125

VSS

126

VSS

137

VSS

138

VSS

149

VSS

150

VSS

159

VSS

161

VSS

162

VSS

173

VSS

174

VSS

185

VSS

186

VSS

201

GND

M_A_SR012

M_A17,12 M_CS1_R# 7,12

M_A27,12

M_A_SR312

M_A47,12

M_A57,12

M_A_SR612

M_A_SR712

4 4

3 3

2 2

1 1

M_A_SR812

M_A_SR912

M_A_SR1012

M_A_SR1112

M_A_SR1212

M_DATA_R_[71..0]12

1D25V_DDRVREF_S3

M_BS0_SR#12

M_BS1_SR#12

M_A1

M_A2

M_A4

M_A5

M_RAS_SR#12

M_CAS_SR#12

M_WE_SR#12

M_A_SR6

M_A_SR7

M_A_SR8

M_A_SR9

M_A_SR10

M_A_SR11

M_A_SR12

TP49TPAD28

TP5TPAD28

TP51TPAD28

A

M_A_SR0

M_A_SR3

M_DATA_R_0

M_DATA_R_1

M_DATA_R_2

M_DATA_R_3

M_DATA_R_4

M_DATA_R_5

M_DATA_R_6

M_DATA_R_7

M_DATA_R_8

M_DATA_R_9

M_DATA_R_10

M_DATA_R_11

M_DATA_R_12

M_DATA_R_13

M_DATA_R_14

M_DATA_R_15

M_DATA_R_16

M_DATA_R_17

M_DATA_R_18

M_DATA_R_19

M_DATA_R_20

M_DATA_R_21

M_DATA_R_22

M_DATA_R_23

M_DATA_R_24

M_DATA_R_25

M_DATA_R_26

M_DATA_R_27

M_DATA_R_28

M_DATA_R_29

M_DATA_R_30

M_DATA_R_31

M_DATA_R_32

M_DATA_R_33

M_DATA_R_34

M_DATA_R_35

M_DATA_R_36

M_DATA_R_37

M_DATA_R_38

M_DATA_R_39

M_DATA_R_40

M_DATA_R_41

M_DATA_R_42

M_DATA_R_43

M_DATA_R_44

M_DATA_R_45

M_DATA_R_46

M_DATA_R_47

M_DATA_R_48

M_DATA_R_49

M_DATA_R_50

M_DATA_R_51

M_DATA_R_52

M_DATA_R_53

M_DATA_R_54

M_DATA_R_55

M_DATA_R_56

M_DATA_R_57

M_DATA_R_58

M_DATA_R_59

M_DATA_R_60

M_DATA_R_61

M_DATA_R_62

M_DATA_R_63

M_DATA_R_64

M_DATA_R_65

M_DATA_R_66

M_DATA_R_67

M_DATA_R_68

M_DATA_R_69

M_DATA_R_70

M_DATA_R_71

DM0_RESET#

DM0_A13

DM0_BA2

12

BC17

SCD1U10V2MX-1

M_DQS_R0

M_DQS_R1

M_DQS_R2

M_DQS_R3

M_DQS_R4

M_DQS_R5

M_DQS_R6

M_DQS_R7

M_DQS_R8

M_DM_R_0

M_DM_R_1

M_DM_R_2

M_DM_R_3

M_DM_R_4

M_DM_R_5

M_DM_R_6

M_DM_R_7

M_DM_R_8

B

2D5V_S3

B

M_CS0_R# 7,12

M_CKE0_R# 7,12

M_CKE1_R# 7,12

M_DQS_R[0..8] 12

M_DM_R_[8..0] 12

CLK_DDR0 7

CLK_DDR0# 7

CLK_DDR1 7

CLK_DDR1# 7

CLK_DDR2 7

CLK_DDR2# 7

SMBC_ICH 3,17

SMBD_ICH 3,17

M_AB17,12

M_AB27,12

M_AB47,12

M_AB57,12

1D25V_DDRVREF_S3

C

Use old symbol change PN only

DM2

112

TP50TPAD28

TP53TPAD28

TP52TPAD28

M_A0

M_A3

M_A6

M_A7

M_A8

M_A9

M_A10

M_A11

M_A12

M_DATA_R_0

M_DATA_R_1

M_DATA_R_2

M_DATA_R_3

M_DATA_R_4

M_DATA_R_5

M_DATA_R_6

M_DATA_R_7

M_DATA_R_8

M_DATA_R_9

M_DATA_R_10

M_DATA_R_11

M_DATA_R_12

M_DATA_R_13

M_DATA_R_14

M_DATA_R_15

M_DATA_R_16

M_DATA_R_17

M_DATA_R_18

M_DATA_R_19

M_DATA_R_20

M_DATA_R_21

M_DATA_R_22

M_DATA_R_23

M_DATA_R_24

M_DATA_R_25

M_DATA_R_26

M_DATA_R_27

M_DATA_R_28

M_DATA_R_29

M_DATA_R_30

M_DATA_R_31

M_DATA_R_32

M_DATA_R_33

M_DATA_R_34

M_DATA_R_35

M_DATA_R_36

M_DATA_R_37

M_DATA_R_38

M_DATA_R_39

M_DATA_R_40

M_DATA_R_41

M_DATA_R_42

M_DATA_R_43

M_DATA_R_44

M_DATA_R_45

M_DATA_R_46

M_DATA_R_47

M_DATA_R_48

M_DATA_R_49

M_DATA_R_50

M_DATA_R_51

M_DATA_R_52

M_DATA_R_53

M_DATA_R_54

M_DATA_R_55

M_DATA_R_56

M_DATA_R_57

M_DATA_R_58

M_DATA_R_59

M_DATA_R_60

M_DATA_R_61

M_DATA_R_62

M_DATA_R_63

M_DATA_R_64

M_DATA_R_65

M_DATA_R_66

M_DATA_R_67

M_DATA_R_68

M_DATA_R_69

M_DATA_R_70

M_DATA_R_71

DM1_RESET#

DM1_A13

DM1_BA2

3D3V_S03D3V_S0

12

BC34

SCD1U10V2MX-1

C

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10 / AP

100

A11

99

A12

117

BA0

116

BA1

5

DQ0

7

DQ1

13

DQ2

17

DQ3

6

DQ4

8

DQ5

14

DQ6

18

DQ7

19

DQ8

23

DQ9

29

DQ10

31

DQ11

20

DQ12

24

DQ13

30

DQ14

32

DQ15

41

DQ16

43

DQ17

49

DQ18

53

DQ19

42

DQ20

44

DQ21

50

DQ22

54

DQ23

55

DQ24

59

DQ25

65

DQ26

67

DQ27

56

DQ28

60

DQ29

66

DQ30

68

DQ31

127

DQ32

129

DQ33

135

DQ34

139

DQ35

128

DQ36

130

DQ37

136

DQ38

140

DQ39

141

DQ40

145

DQ41

151

DQ42

153

DQ43

142

DQ44

146

DQ45

152

DQ46

154

DQ47

163

DQ48

165

DQ49

171

DQ50

175

DQ51

164

DQ52

166

DQ53

172

DQ54

176

DQ55

177

DQ56

181

DQ57

187

DQ58

189

DQ59

178

DQ60

182

DQ61

188

DQ62

190

DQ63

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

85

NC

86

NC/(RESET#)

97

NC/A13

98

NC/BA2

123

NC

124

NC

200

NC

118

/RAS

120

/CAS

119

/WE

1

VREF

2

VREF

197

VDDSPD

199

VDDID

201

GND

SKT-SODIMM200-7U

62.10024.481

BOT sideTop Side

M_A07,12

M_A37,12

M_A67,12

M_A77,12

M_A87,12

M_A97,12

M_A107,12

M_A117,12

M_A127,12

M_BS0#7,12

M_BS1#7,12

M_RAS#7,12

M_CAS#7,12

M_WE#7,12

121

/CS0

122

/CS1

96

CKE0

95

CKE1

11

25

47

61

133

147

169

183

77

12

26

48

62

134

148

170

184

78

35

37

160

158

89

91

195

193

194

196

198

9

10

21

22

33

34

36

45

46

57

58

69

70

81

82

92

93

94

113

114

131

132

143

144

155

156

157

167

168

179

180

191

192

3

4

15

16

27

28

38

39

40

51

52

63

64

75

76

87

88

90

103

104

125

126

137

138

149

150

159

161

162

173

174

185

186

202

SMBC_ICH

SMBD_ICH

M_DQS_R0

M_DQS_R1

M_DQS_R2

M_DQS_R3

M_DQS_R4

M_DQS_R5

M_DQS_R6

M_DQS_R7

M_DQS_R8

M_DM_R_0

M_DM_R_1

M_DM_R_2

M_DM_R_3

M_DM_R_4

M_DM_R_5

M_DM_R_6

M_DM_R_7

M_DM_R_8

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

CK0

/CK0

CK1

/CK1

CK2

/CK2

SCL

SDA

SA0

SA1

SA2

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

NORMAL TYPE

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

M_CS2_R# 7,12

M_CS3_R# 7,12

M_CKE2_R# 7,12

M_CKE3_R# 7,12

3D3V_S0

2D5V_S3

D

CLK_DDR3 7

CLK_DDR3# 7

CLK_DDR4 7

CLK_DDR4# 7

CLK_DDR5 7

CLK_DDR5# 7

D

Montara-GM+

(BOT side)

Title

Size Document Number Rev

Custom

Date: Sheet

E

(Normal Type)

DIMM 2(BOT side)

(REVERSE TYPE)

DIMM 1(Top side)

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

DDR Socket

MOLOKAI

E

of

10 39Thursday, April 15, 2004

SC

Page 11

A

www.kythuatvitinh.com

B

C

D

E

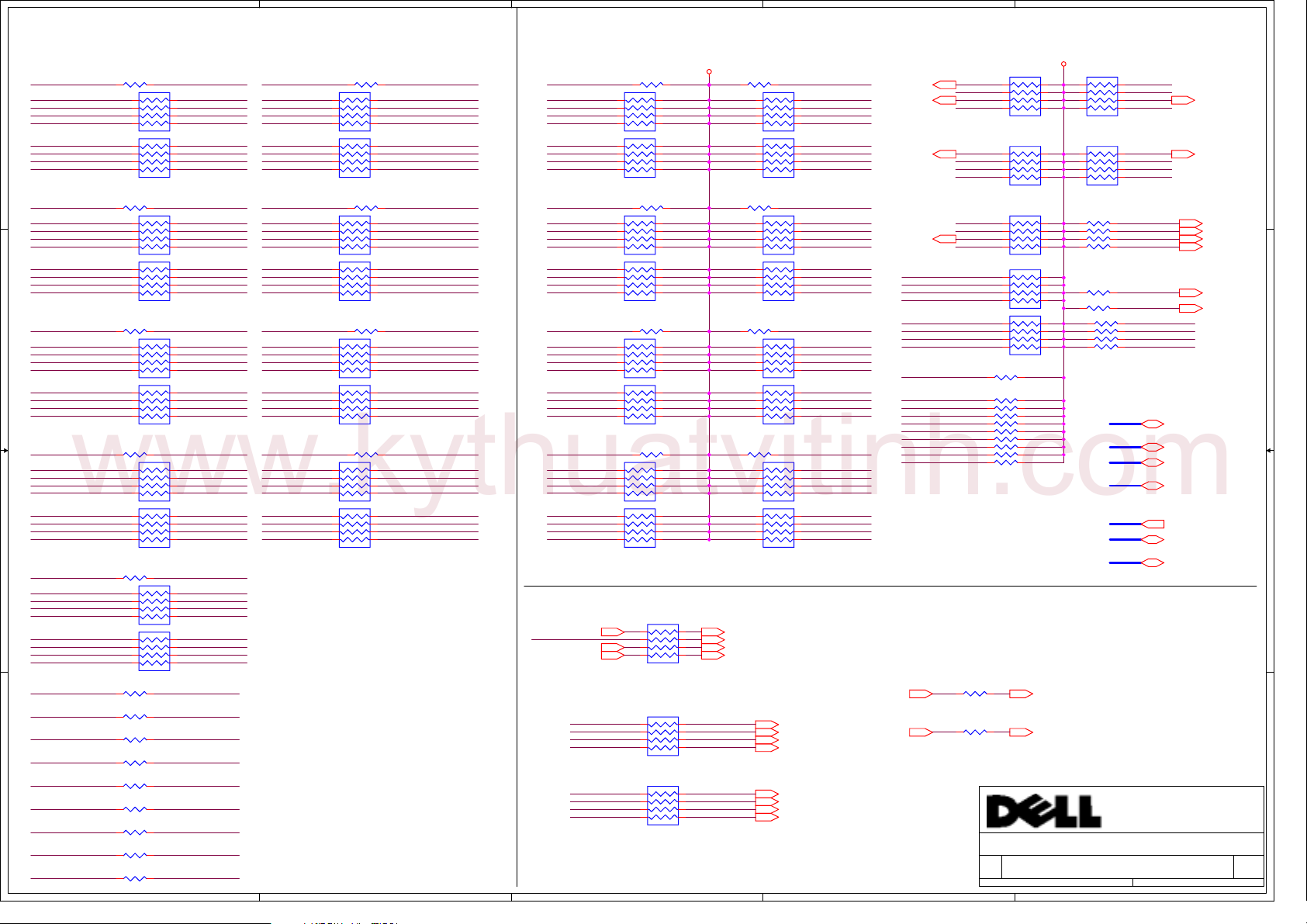

1D25V_S0

4 4

BC47

SCD01U16V2KX

BC58

SCD01U16V2KX

0.01u_25V*24,0402-X7R

BC49

SCD01U16V2KX

BC62

SCD01U16V2KX

BC40

SCD01U16V2KX

BC61

SCD01U16V2KX

BC36

SCD01U16V2KX

BC51

SCD01U16V2KX

BC35

SCD01U16V2KX

BC52

SCD01U16V2KX

BC37

SCD01U16V2KX

BC46

SCD01U16V2KX

BC39

SCD01U16V2KX

BC48

SCD01U16V2KX

BC42

SCD01U16V2KX

BC50

SCD01U16V2KX

BC41

SCD01U16V2KX

BC72

SCD01U16V2KX

BC38

SCD01U16V2KX

BC73

SCD01U16V2KX

BC60

SCD01U16V2KX

BC69

SCD01U16V2KX

BC59

SCD01U16V2KX

BC67

SCD01U16V2KX

0.1u_10V*24,0402-X5R

12

BC55

SCD1U10V2MX-1

3 3

12

BC92

SCD1U10V2MX-1

12

BC57

SCD1U10V2MX-1

12

BC96

SCD1U10V2MX-1

12

BC84

SCD1U10V2MX-1

12

BC95

SCD1U10V2MX-1

12

BC82

SCD1U10V2MX-1

12

BC94

SCD1U10V2MX-1

12

BC83

SCD1U10V2MX-1

12

BC91

SCD1U10V2MX-1

2D5V_S3

12

BC85

SCD1U10V2MX-1

12

BC93

SCD1U10V2MX-1

FOR DDR SKTS POWER PIN

10u_6.3V*1,0805-X5R

0.1u_10V*24,0402-X5R

12

BC78

SCD1U10V2MX-1

12

BC97

SCD1U10V2MX-1

12

BC81

SCD1U10V2MX-1

12

BC77

SCD1U10V2MX-1

12

BC71

SCD1U10V2MX-1

12

BC80

SCD1U10V2MX-1

12

BC74

SCD1U10V2MX-1

12

BC79

SCD1U10V2MX-1

12

BC68

SCD1U10V2MX-1

12