DELL 3700 Schematics

伟力电脑医院

技术支持:252670528

5

D D

4

3

2

1

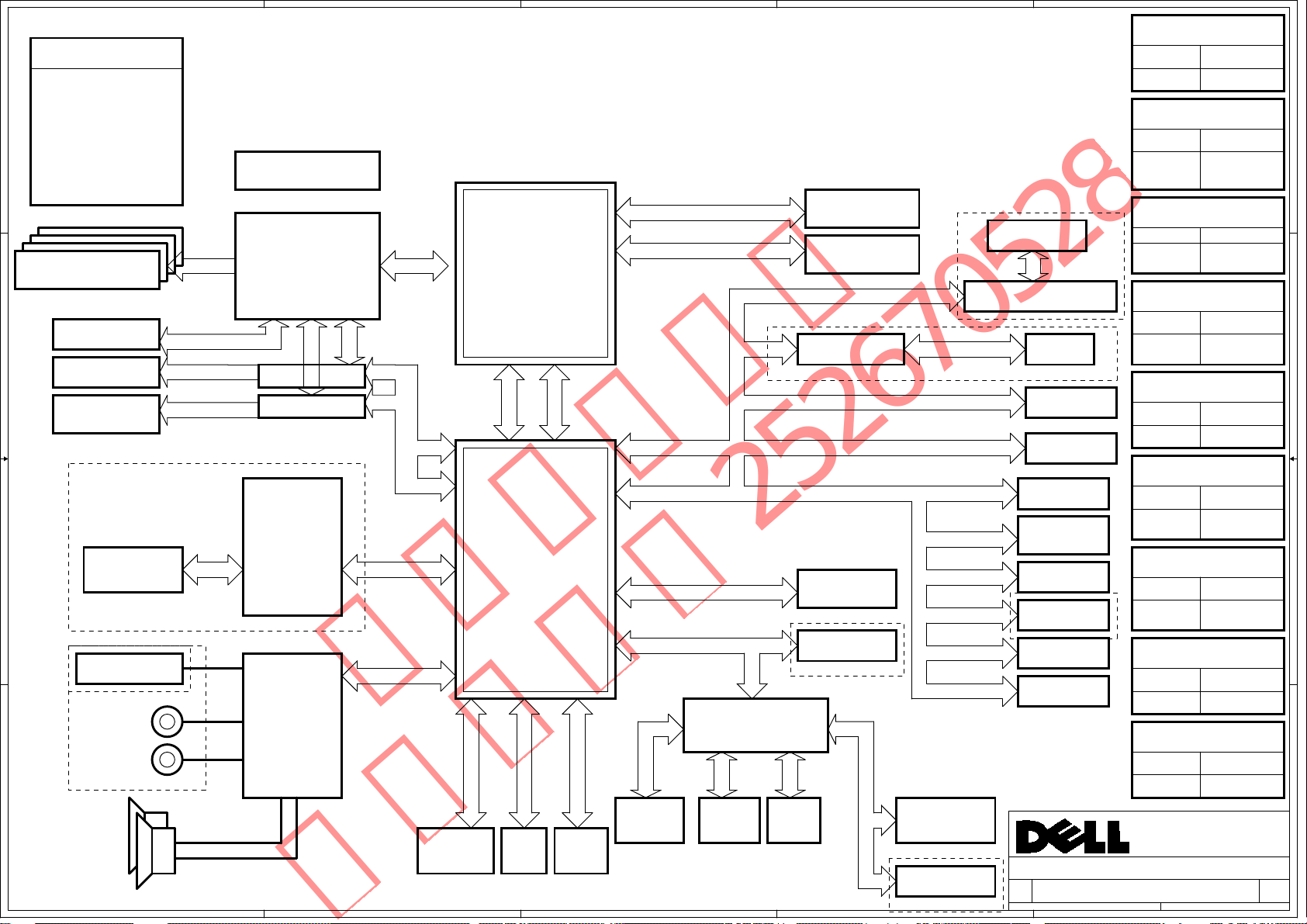

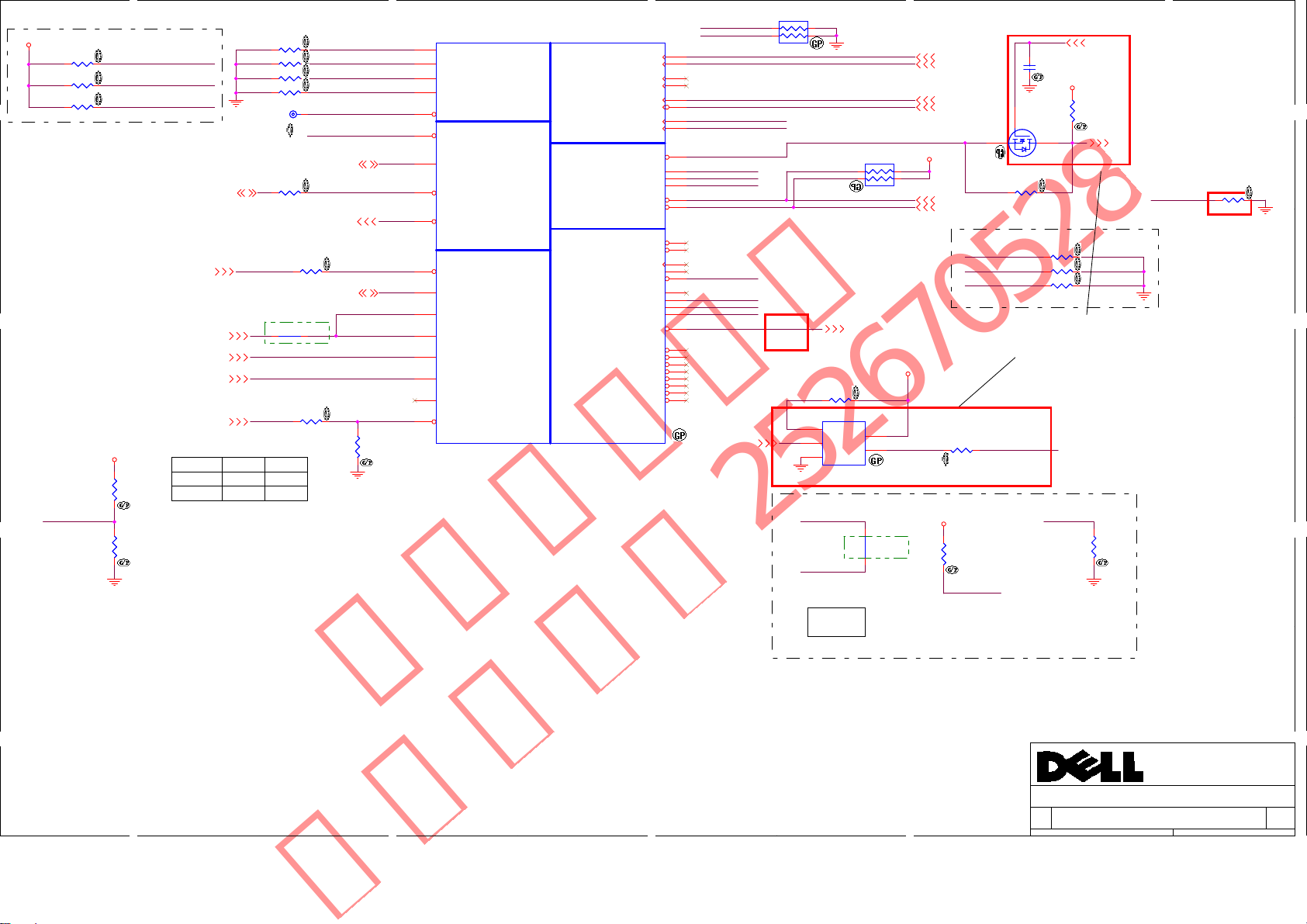

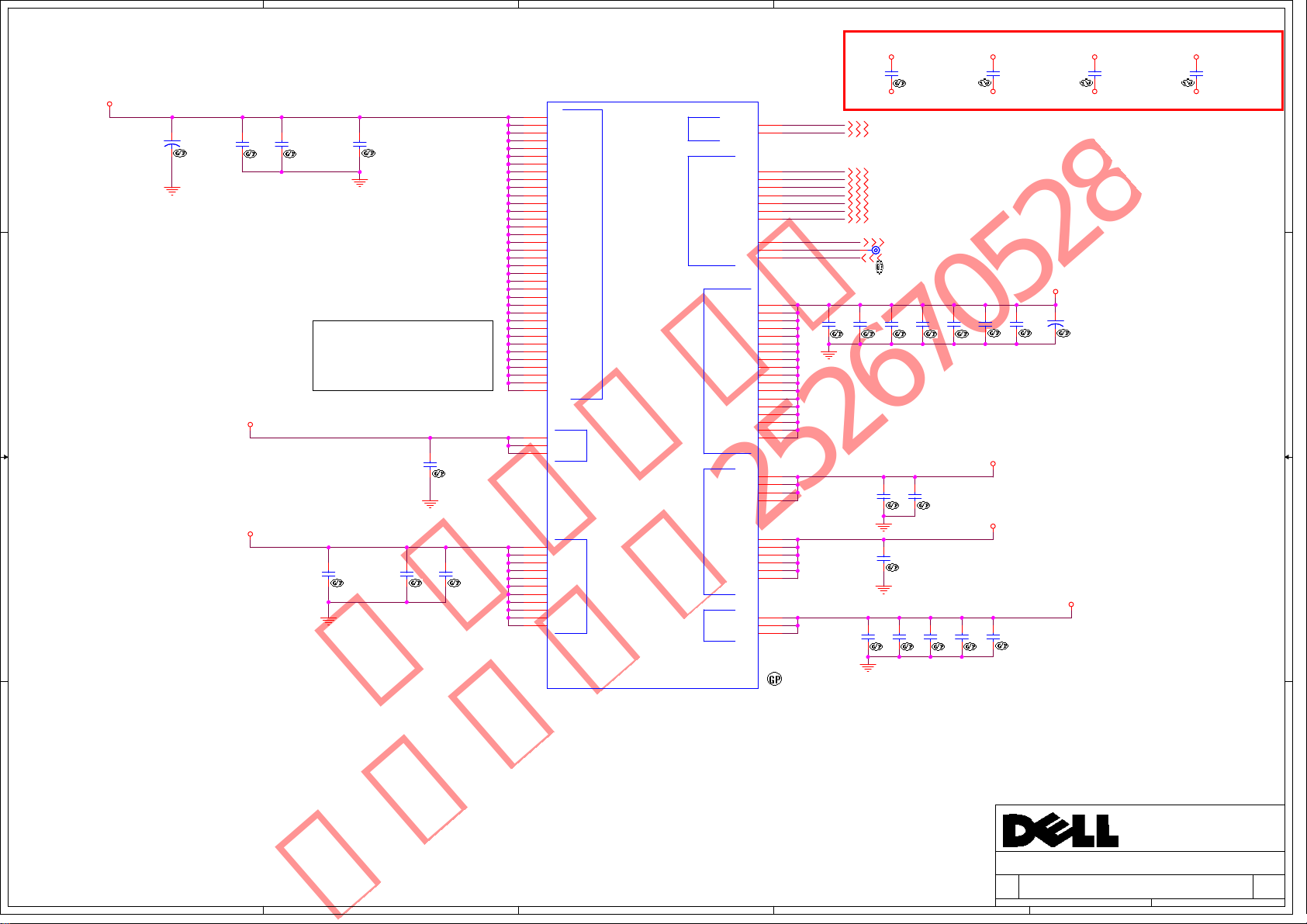

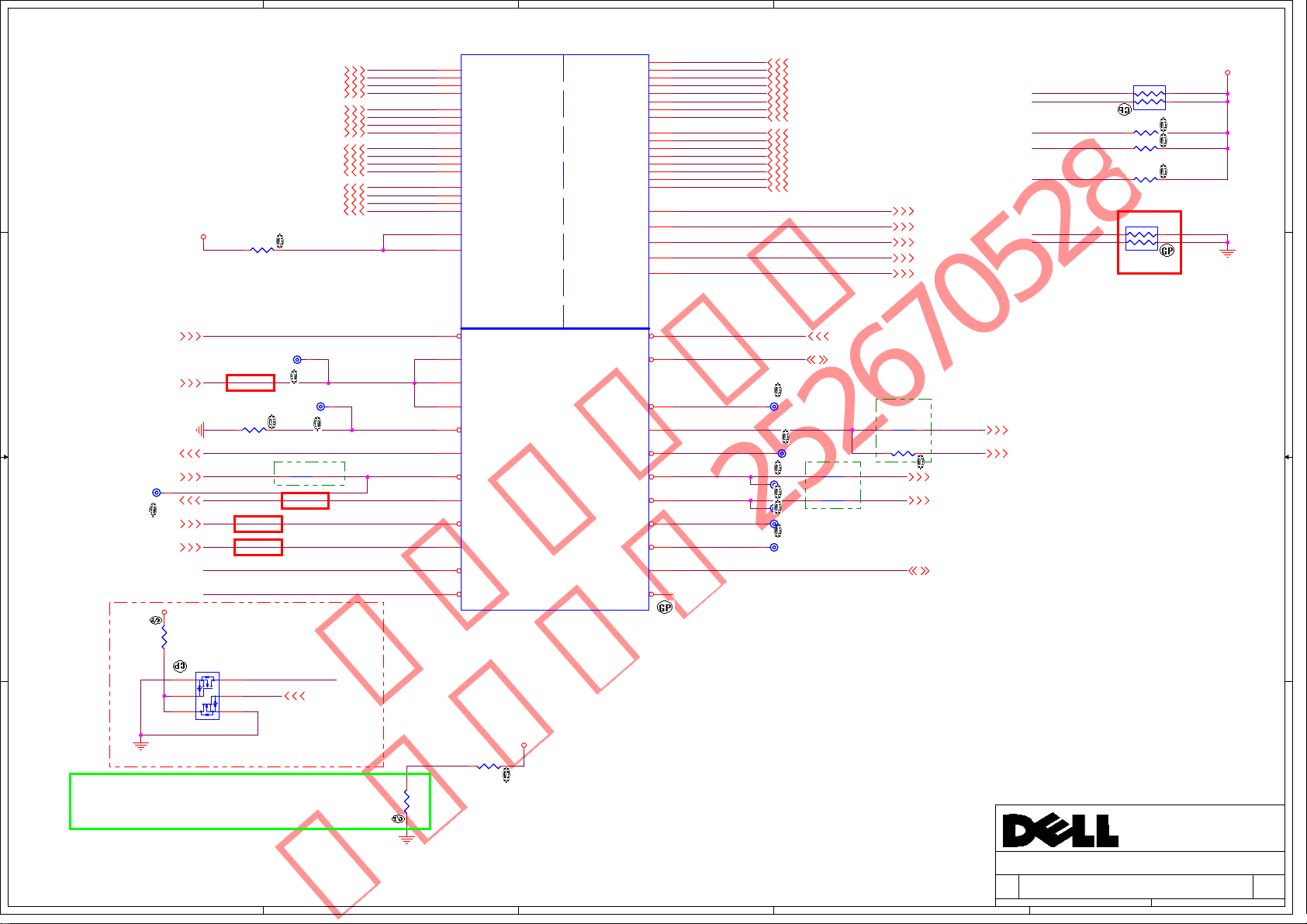

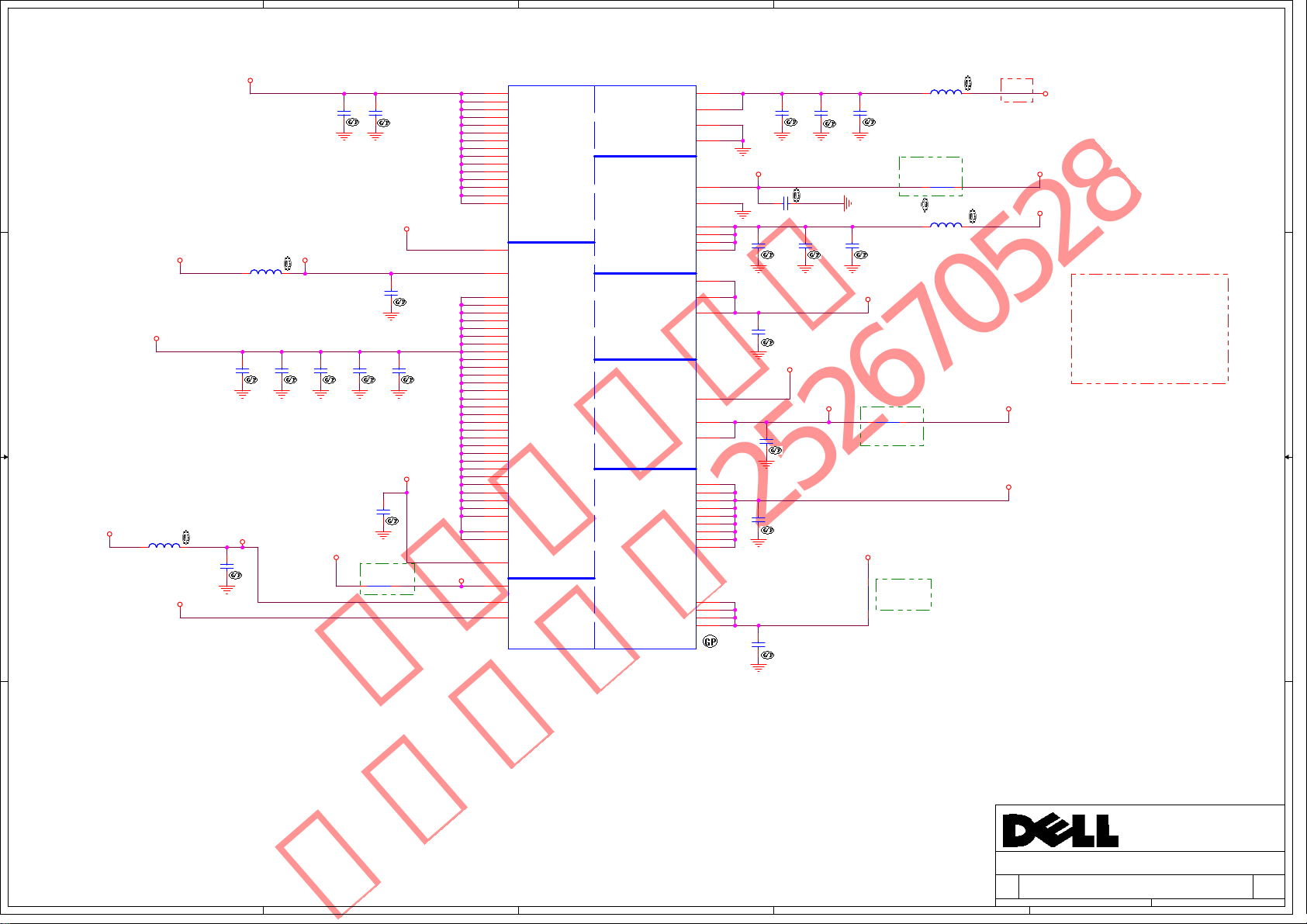

Winery CALPELLA N11M-GE Schematics

Mobile Arrandale

Intel Ibex Peak-M

C C

2010-01-18

REV : X-build

B B

A A

5

DY : Nopop Component

UMA : Pop when schematic is UMA

DIS : Pop when schematic is DIS

4

3

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Vostro Calpella

Vostro Calpella

Vostro Calpella

Taipei Hsien 221, Taiwan, R.O.C.

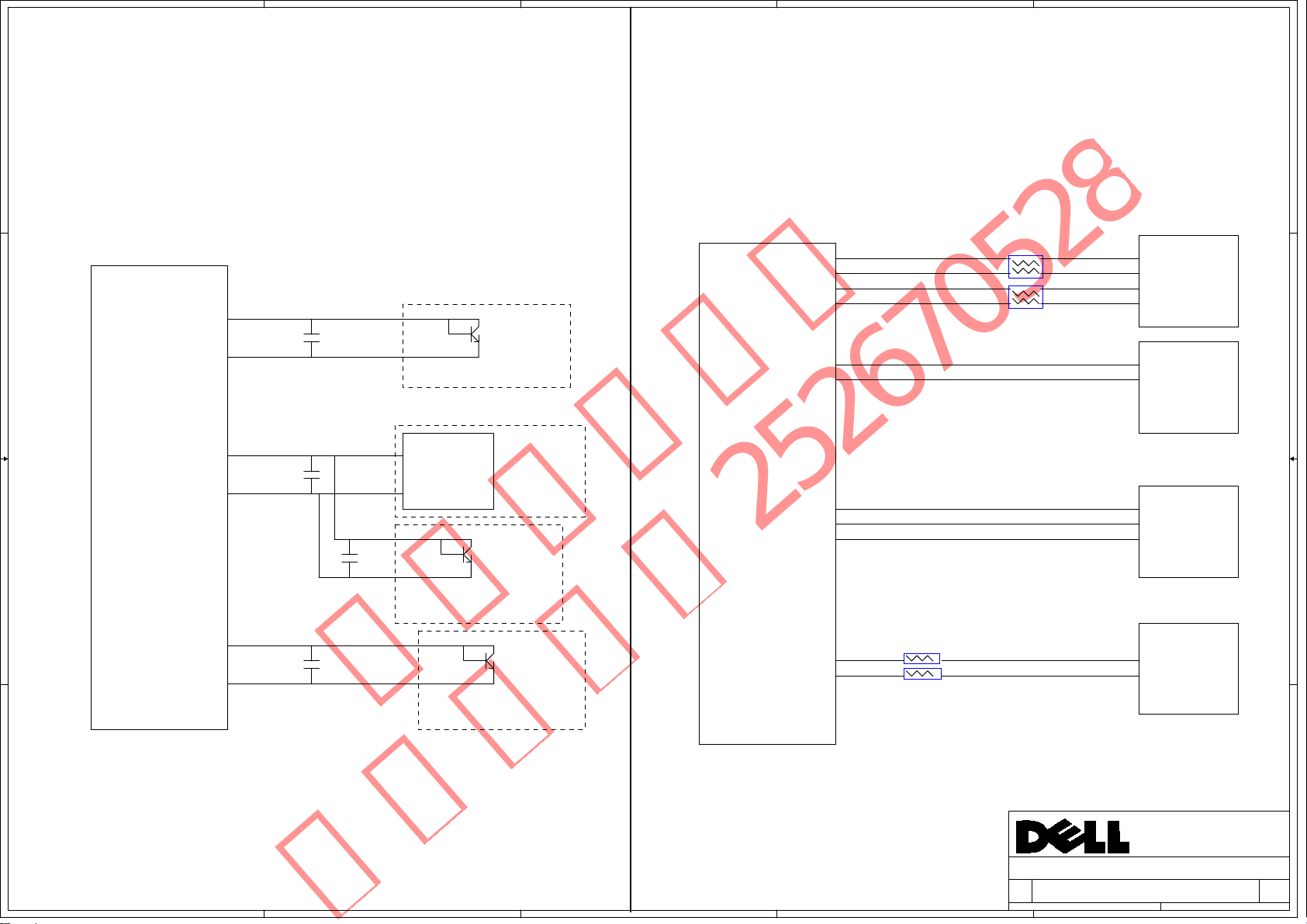

Cover Page

Cover Page

Cover Page

1 91Monday, January 18, 2010

1 91Monday, January 18, 2010

1 91Monday, January 18, 2010

1

X01

X01

X01

伟力电脑医院

技术支持:252670528

5

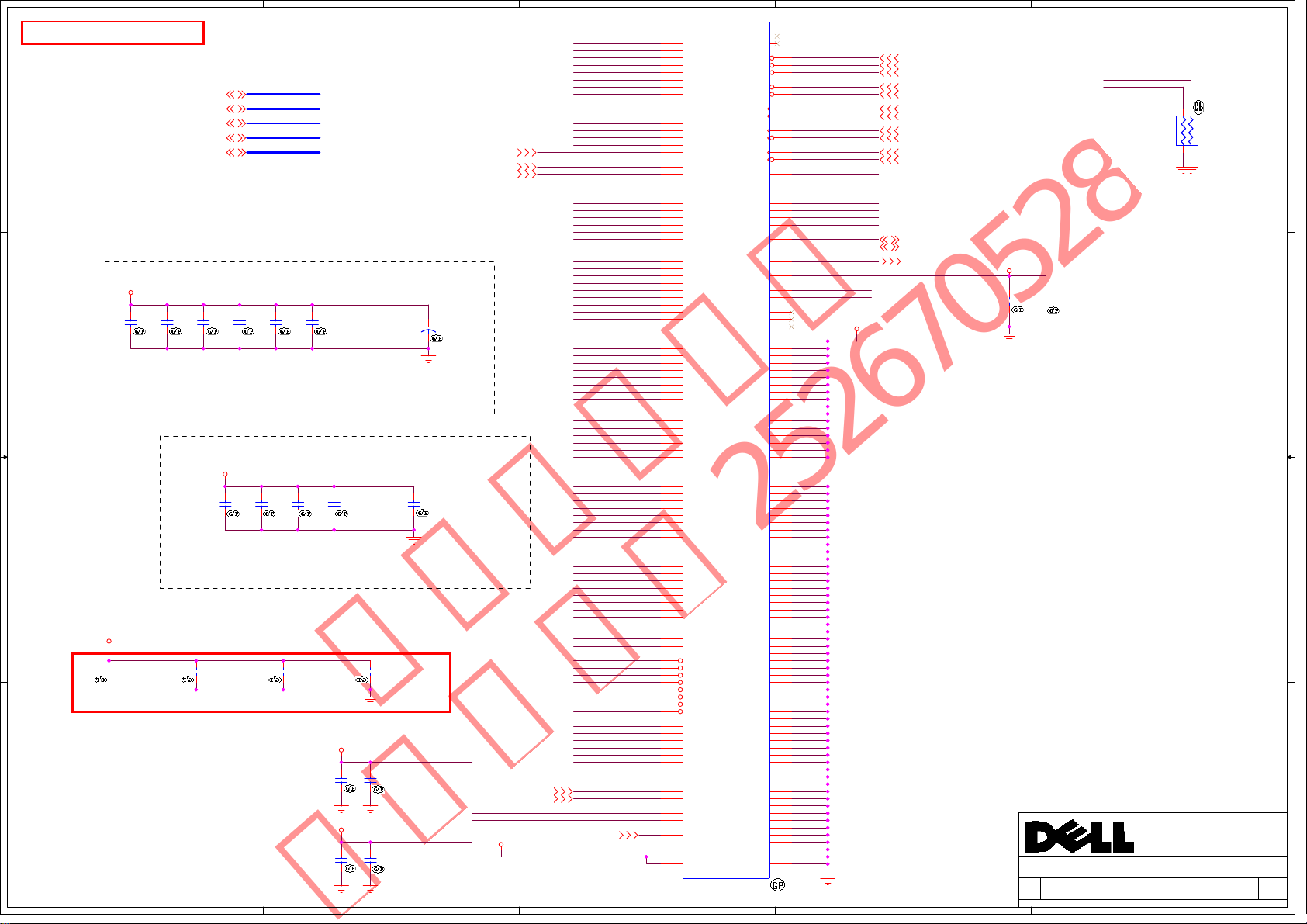

Winery CALPELLA Block Diagram

PCB LAYER

L1: Top

L2: VCC

D D

L3: Signal

L4: Signal

L5: GND

L6: Bottom

Clock Generator

SLG8SP585

4

7

3

Project code : 91.4ES01.001

Part Number : 48.4ES11.0SB

PCB P/N : 09297

Revision : SA

2

1

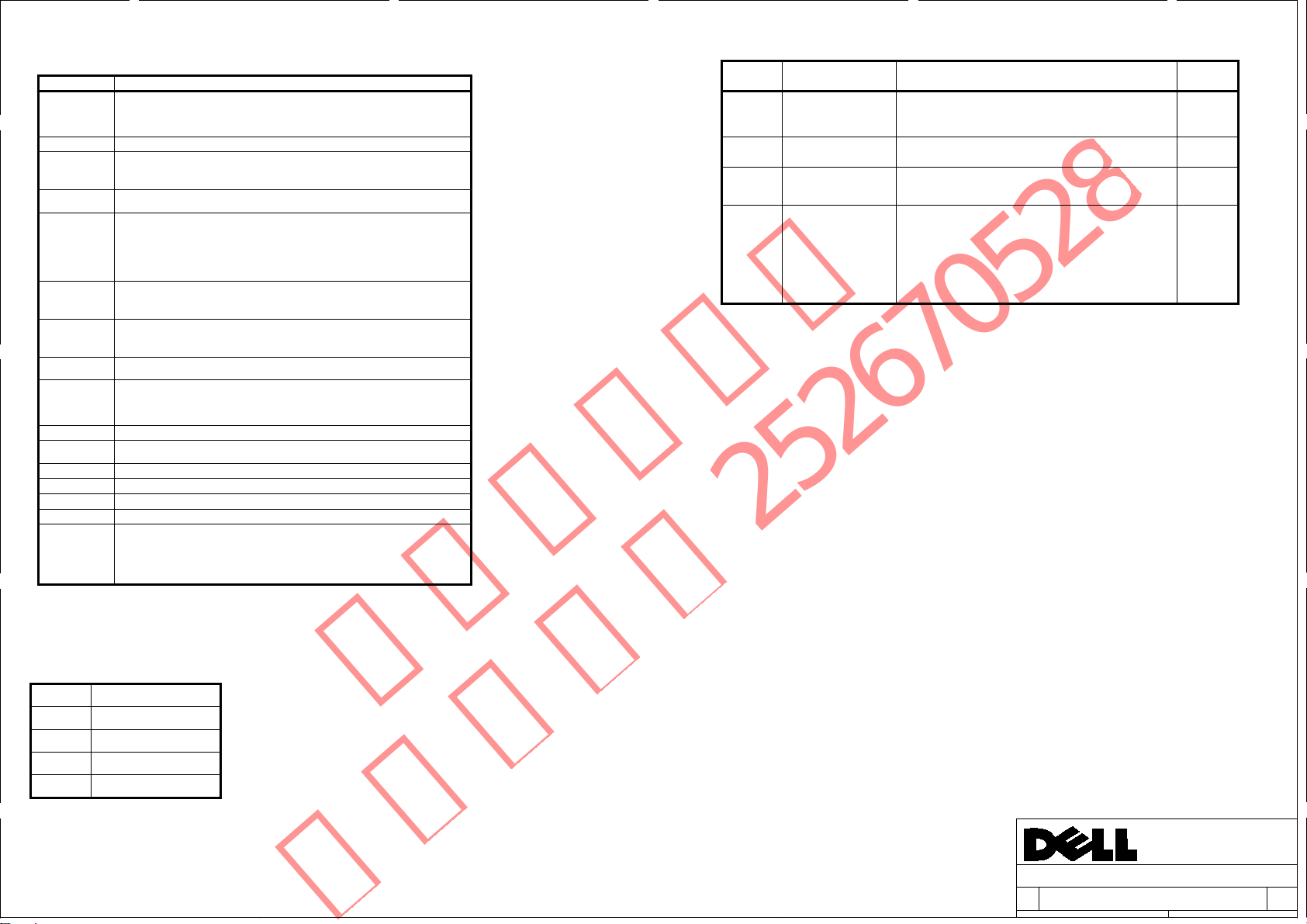

CPU DC/DC

ISL62883

INPUTS

+PWR_SRC

OUTPUTS

+VCC_CORE

SYSTEM DC/DC

TPS51125

INPUTS

+PWR_SRC

OUTPUTS

+15V_ALW

+3.3V_RTC_LDO

+5V_ALW

+3.3V_ALW

47,48

46

100MHz/

RGB CRT

75

74

74

2.5Gbps

PCIe x 16

Bandwidth

:8GB

RGB CRT

LVDS

2.5 GT/s 2.7 GT/s

RGB CRT

VRAM(gDDR3)

64Mbx16x4 (512MB)

4

84,85

HDMI

C C

CRT

LCD

VRAM

57

HDMI

RGB CRT

55

LVDS

54

Nvidia

N11M-GE(40nm)

80,81,82,83

HDMI

LVDS

Switchable

Switchable

Intel CPU

Arrandale

8,9,10,11,12,13,14

DMIx4 FDI(UMA)

DDRIII 1066 Channel A

800/1066MHz

DDR III 1066 Channel B

800/1066MHz

PCIE x 1

PCIE

DDRIII

1066

DDRIII

1066

PCIE x 1 & USB 2.0 x 1

10/100/1000LOM

RTL8111DL

(On daughter board)

100MHz

CardReader

LVDS

B B

(8 in 1)SD/MMC

MS/MS Pro/xD

(On daughter board)

Realtek

RTS5138

USB 2.0

480Mbps

Intel

PCH

14 USB 2.0/1.1 ports

ETHERNET (10/100/1000Mb)

High Definition Audio

SATA ports (6)

PCIE ports (8)

LPC I/F

ACPI 1.1

PCI/PCI BRIDGE

Digital Mic Array

Azalia

CODEC

AZALIA

24MHz

20,21,22,23,24,25,26,27,28

MIC IN

OP AMP

HP OUT

(On daughter board)

A A

2CH SPEAKER

60

5

IDT

92HD81

3Gbps

Flash ROM

4MB

SPI

62

ODD

HDD

SATA

59

30

USB,ESATA

Multi-Port x1

4

SATA,USB

63

2.5Gbps

USB 2.0

480Mbps

SPI

Flash ROM

256kB

3

SM Bus

Free fall sensor

400KHz

LPC Bus

33MHz

TPM

(only for 15")

(On daughter board)

KBC

NUVOTON

NPCE781BA0DX

Touch

PAD

62 68 39,58

68

37

Int.

KB

SM Bus

Slot 0

18

Slot 1

19

35

USB 2.0 x 1

USB 2.0 x 1

40

76

Thermal

& Fan

EMC2102

Capacity Board

(On daughter board)

2

PCIE x 1

PCIE x 1

USB 2.0 x 1

USB 2.0 x 2

USB 2.0 x 1

USB 2.0 x 1

USB 2.0 x 1

USB 2.0 x 1

SYSTEM DC/DC

Power SW

TPS2231R

New Card

(On daughter board)

RJ45

CONN

61

TPS51116

OUTPUTSINPUTS

+PWR_SRC

+1.5V_SUS

+0.75V_DDR_VTT

+V_DDR_MCH_REF

SYSTEM DC/DC

ADP3211

OUTPUTSINPUTS

+PWR_SRC +CPU_GFXCORE

SYSTEM DC/DC

INPUTS

+PWR_SRC

TPS51218

OUTPUTS

+VCC_GFX_CORE

Mini-Card

802.11a/b/g/n

Mini-Card

WWAN/ WiMAX

65

64

CHARGER

Touch Panel

(only for 15")

Left Side:

USB x 2

Right Side:

USB x 1

CAMERA

Bluetooth

Biometric

76

76

63

73

73

78

BQ24745

INPUTS

+DC_IN

+PBATT

OUTPUTS

+PWR_SRC

SYSTEM DC/DC

TPS51218

OUTPUTSINPUTS

+PWR_SRC

VTT_CORE

LDO

APL5930

INPUTS

OUTPUTS

+1.8V_RUN+3.3V_ALW

LDO

RT9025

2 91Monday, January 18, 2010

2 91Monday, January 18, 2010

2 91Monday, January 18, 2010

OUTPUTS

+1.8V_RUN_GPU+3.3V_ALW

INPUTS

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Vostro Calpella

Vostro Calpella

Vostro Calpella

Taipei Hsien 221, Taiwan, R.O.C.

Block Diagram

Block Diagram

Block Diagram

1

50

53

86

49

51

87

X01

X01

X01

伟力电脑医院

技术支持:252670528

5

D D

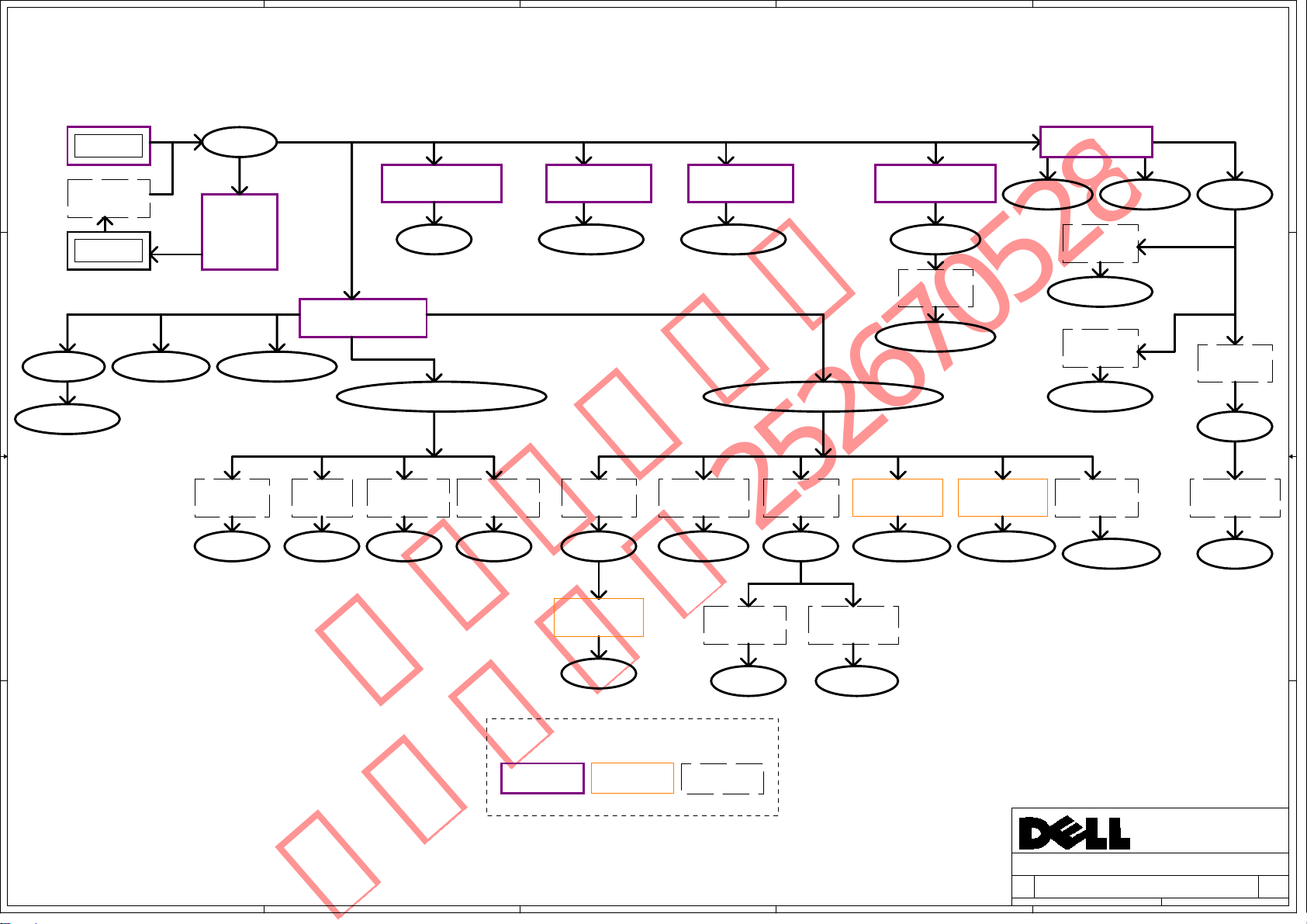

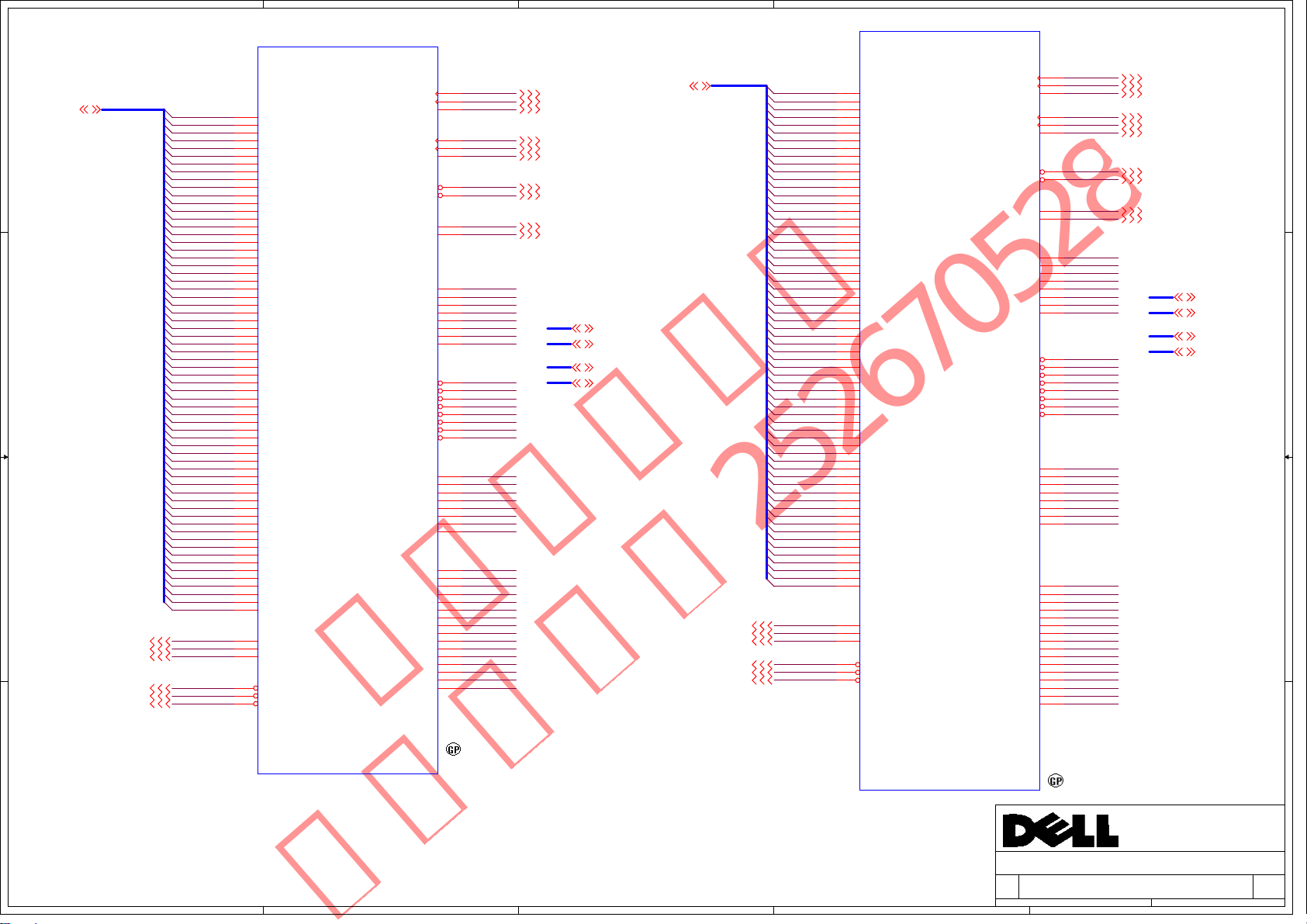

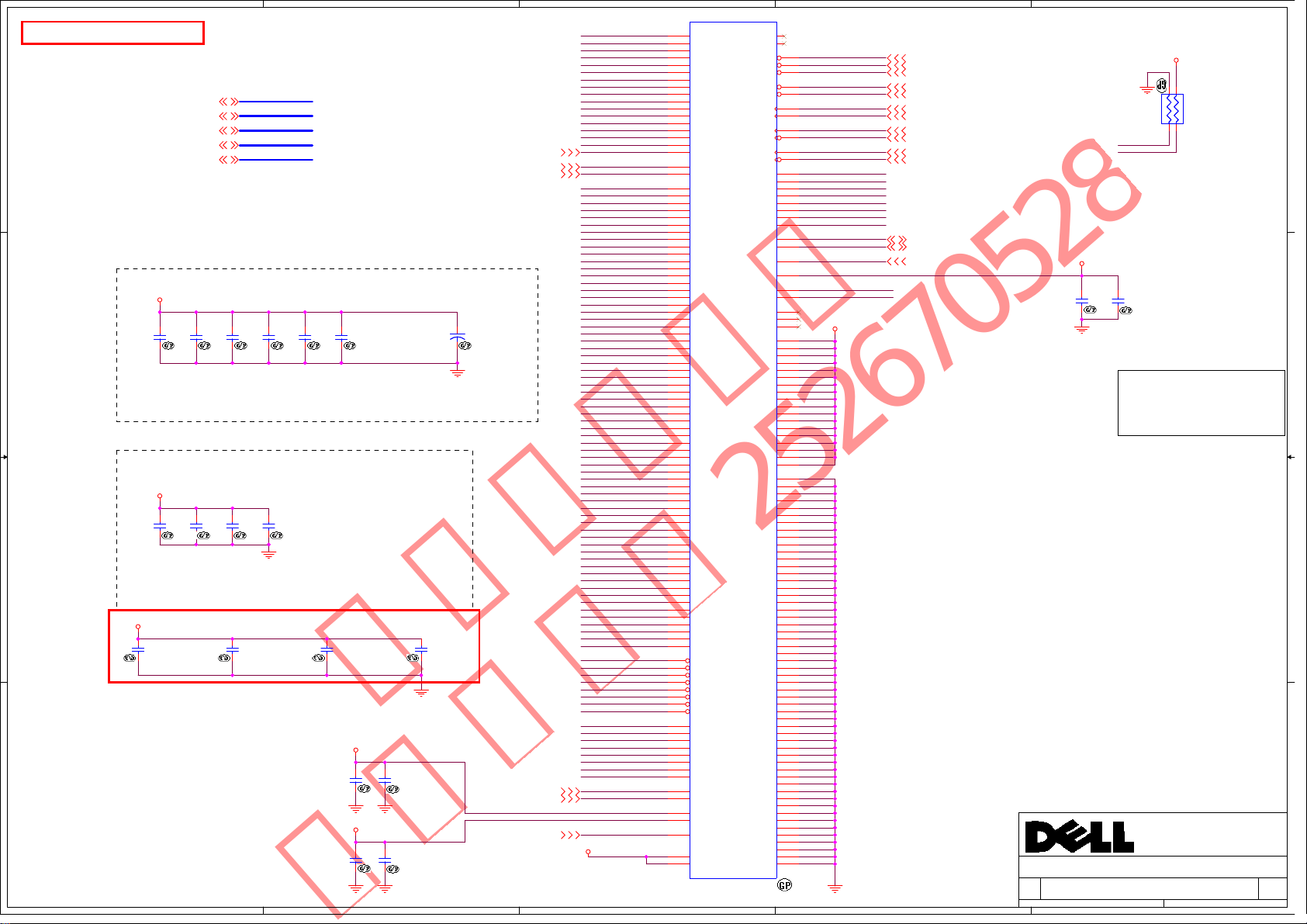

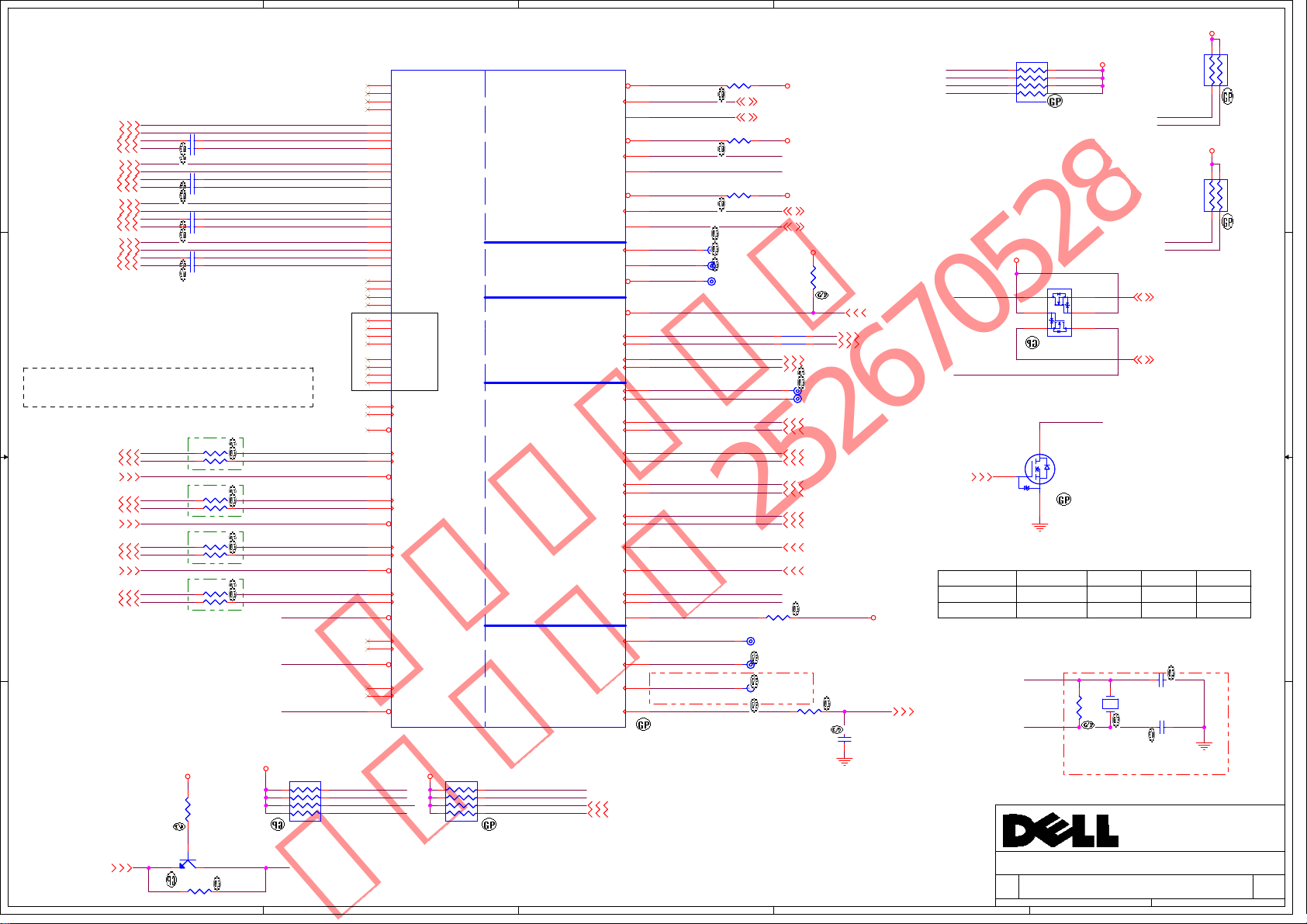

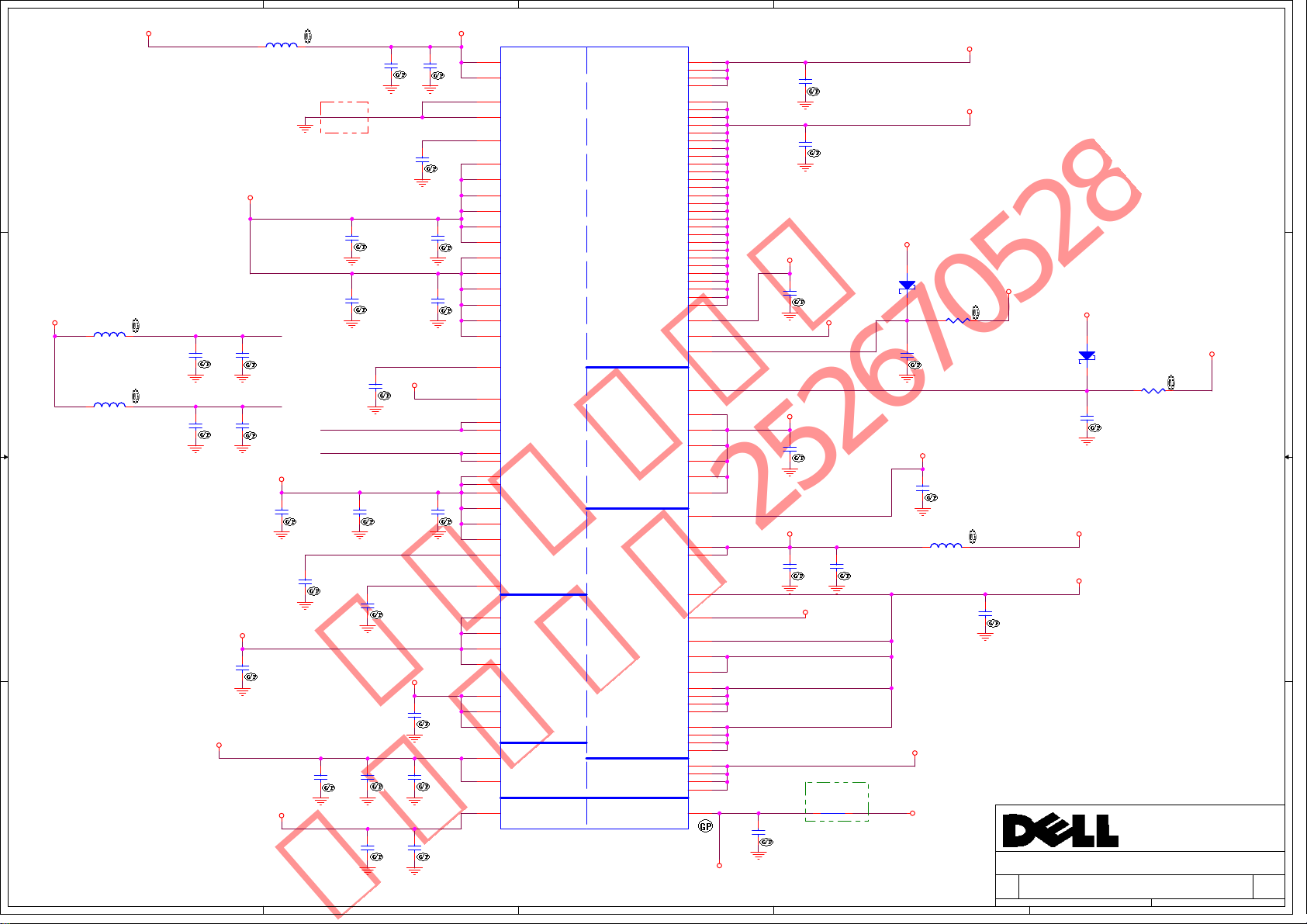

Adapter

AO4407A

45

+PWR_SRC

Charger

BQ24745

Battery

+PBATT

45

TPS51125

C C

+5V_ALW

+5V_ALW2

+3.3V_RTC_LDO

+15V_ALW

4

ISL62883

+VCC_CORE

46

+5V_ALW

3

47、48 86

ADP3211

+CPU_GFXCORE

53

TPS51218

+VCC_GFX_CORE

For NVIDIA GPUFor Intel GPU

+3.3V_ALW

2

TPS51218DSCR

+1.05V_VTT

Arrandale : 1.05V

FDS8880

+1.05V_GFX_PCIE

87

1

TPS51116PWPRG4

49

FDS8880

+1.5V_RUN_GPU

P2703

+1.5V_CPU

50

+0.75V_DDR_VTT+V_DDR_MCH_REF

87

52

+1.5V_SUS

AO4468

+1.5V_RUN

42

TPS2062AD

Daughter BD 6342

+5V_USB0

B B

For USB Port1 For USB Port2,3 For ESATA

AO4468

+5V_RUN

TPS2062AD

+5V_USB1

TPS2062AD

+5V_USB2

63

AO3403

+3.3V_LAN

RTL8111DL

DVDD12

35

TPS2231R

Daughter BD

G5285T11U

+LCDVDD

AO4468

+3.3V_RUN+3.3V_CARDAUX

54

42

TPS2231R

Daughter BD

+3.3V_CARD

APL5930

+1.8V_RUN

51

RT9025

+1.8V_RUN_GPU

87

FDS8880

+3.3V_RUN_GPU

TPS2231R

87

Daughter BD

+1.5V_CARD

Power Shape

Regulator LDO Switch

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Power Block Diagram

Power Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Power Block Diagram

Vostro Calpella

Vostro Calpella

Vostro Calpella

Taipei Hsien 221, Taiwan, R.O.C.

3 91Monday, January 18, 2010

3 91Monday, January 18, 2010

3 91Monday, January 18, 2010

1

X01

X01

X01

伟力电脑医院

技术支持:252670528

5

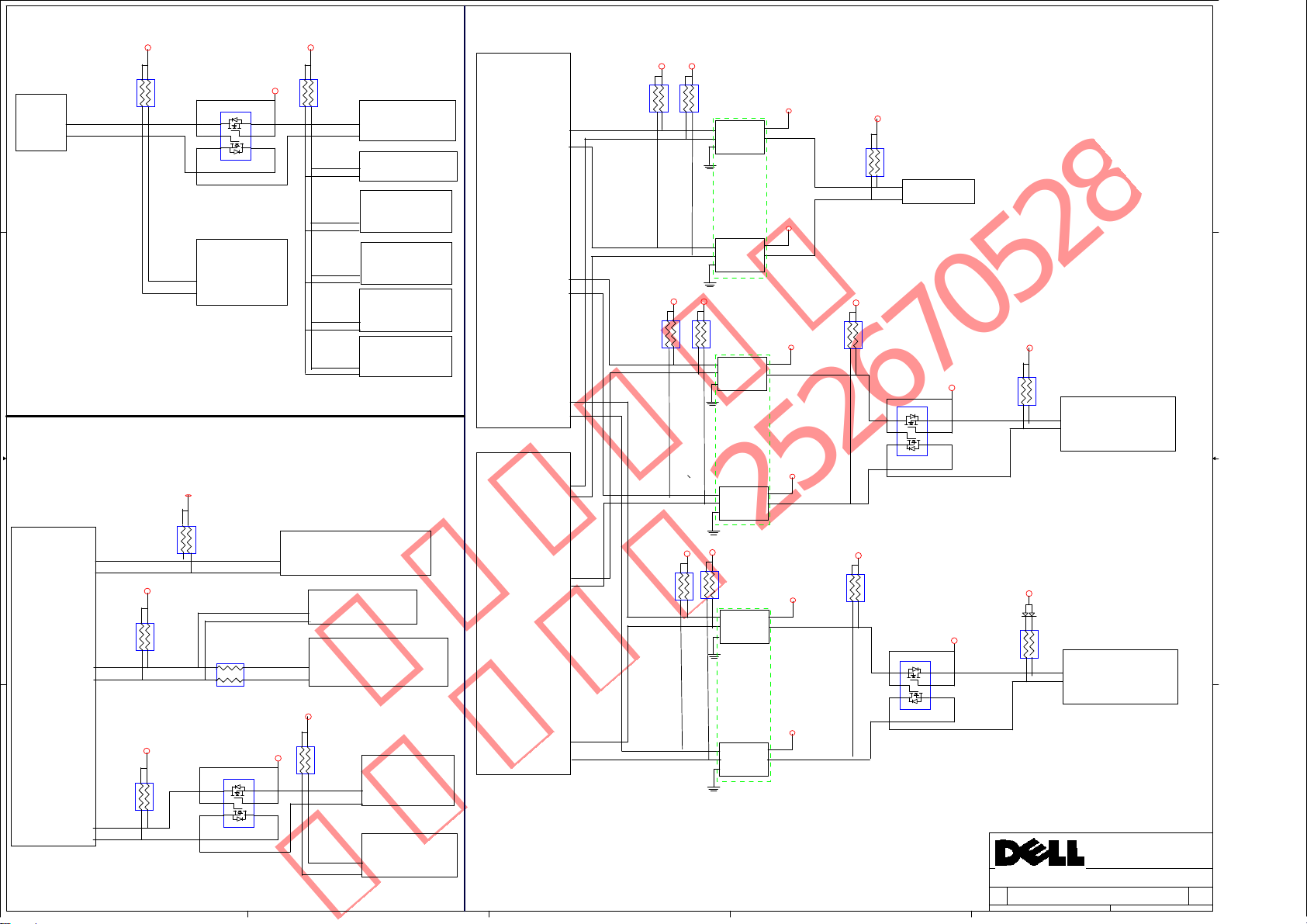

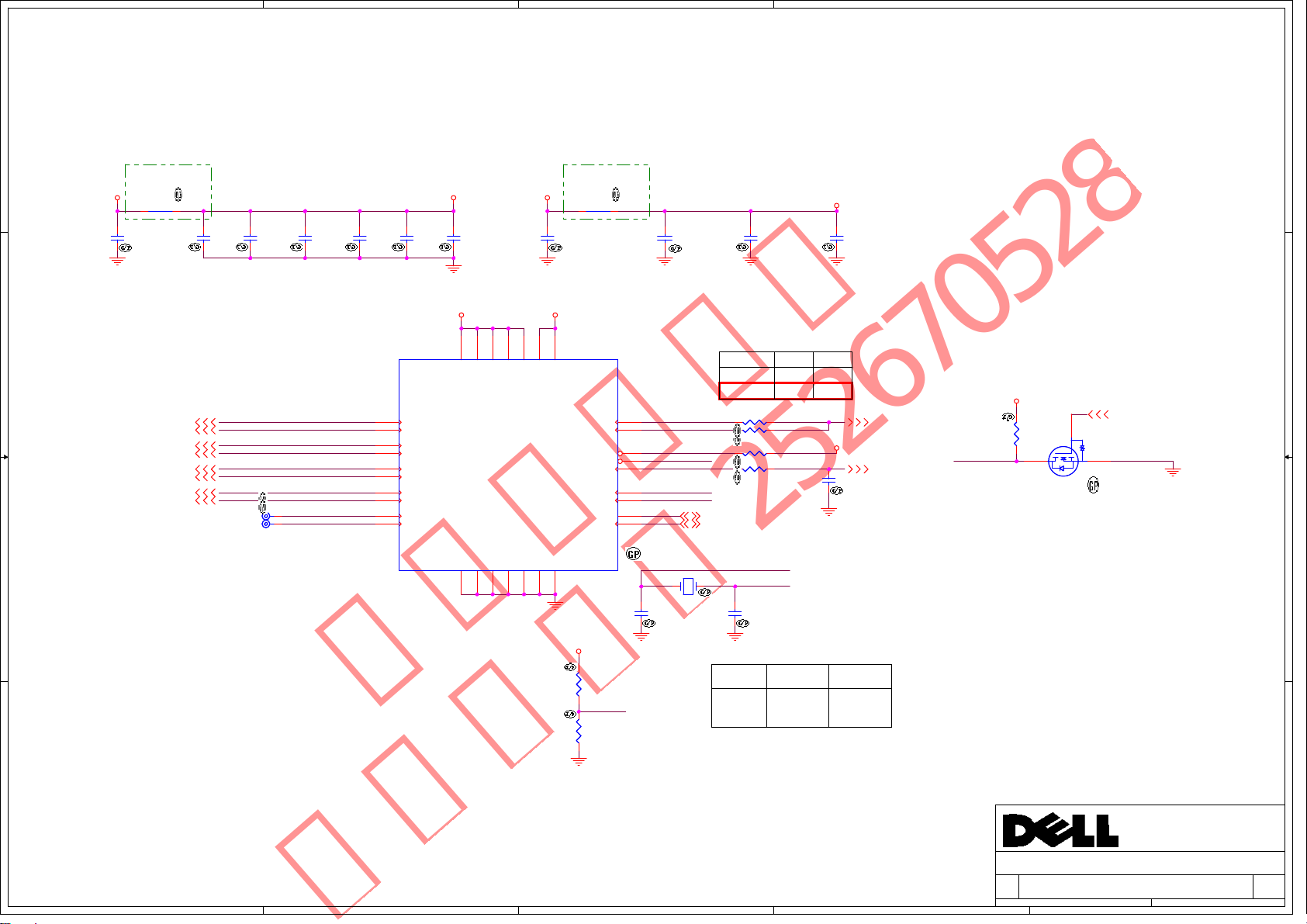

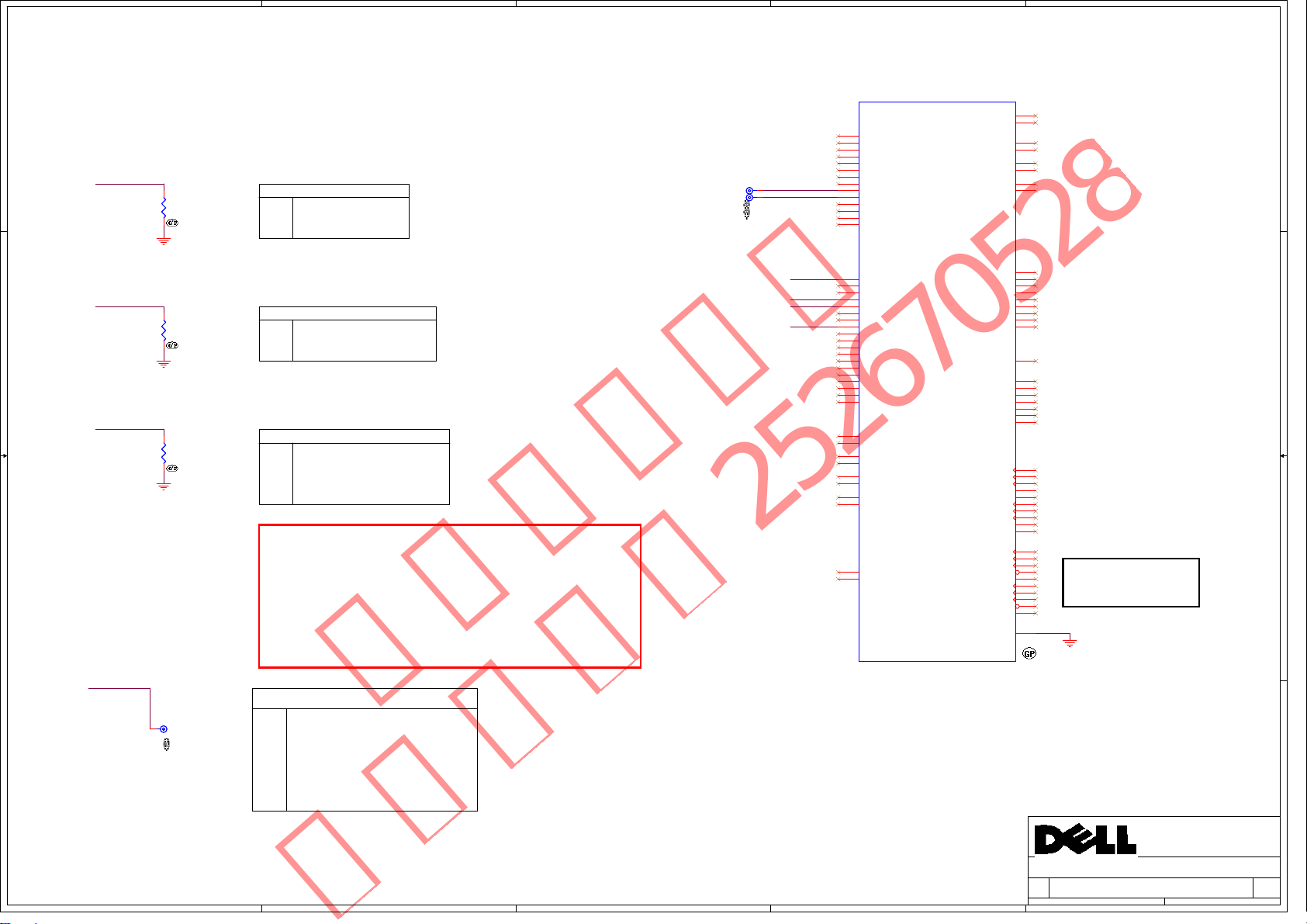

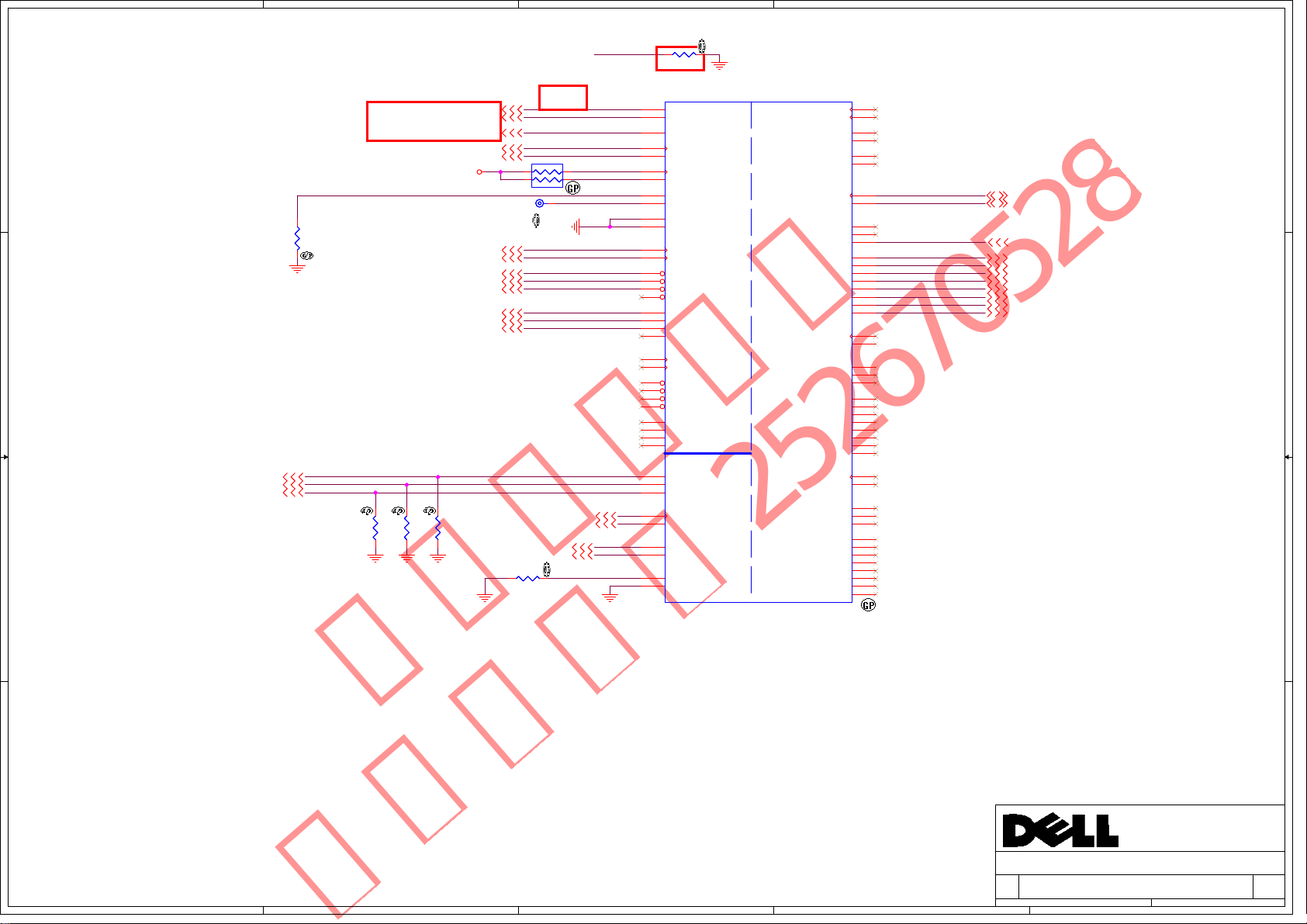

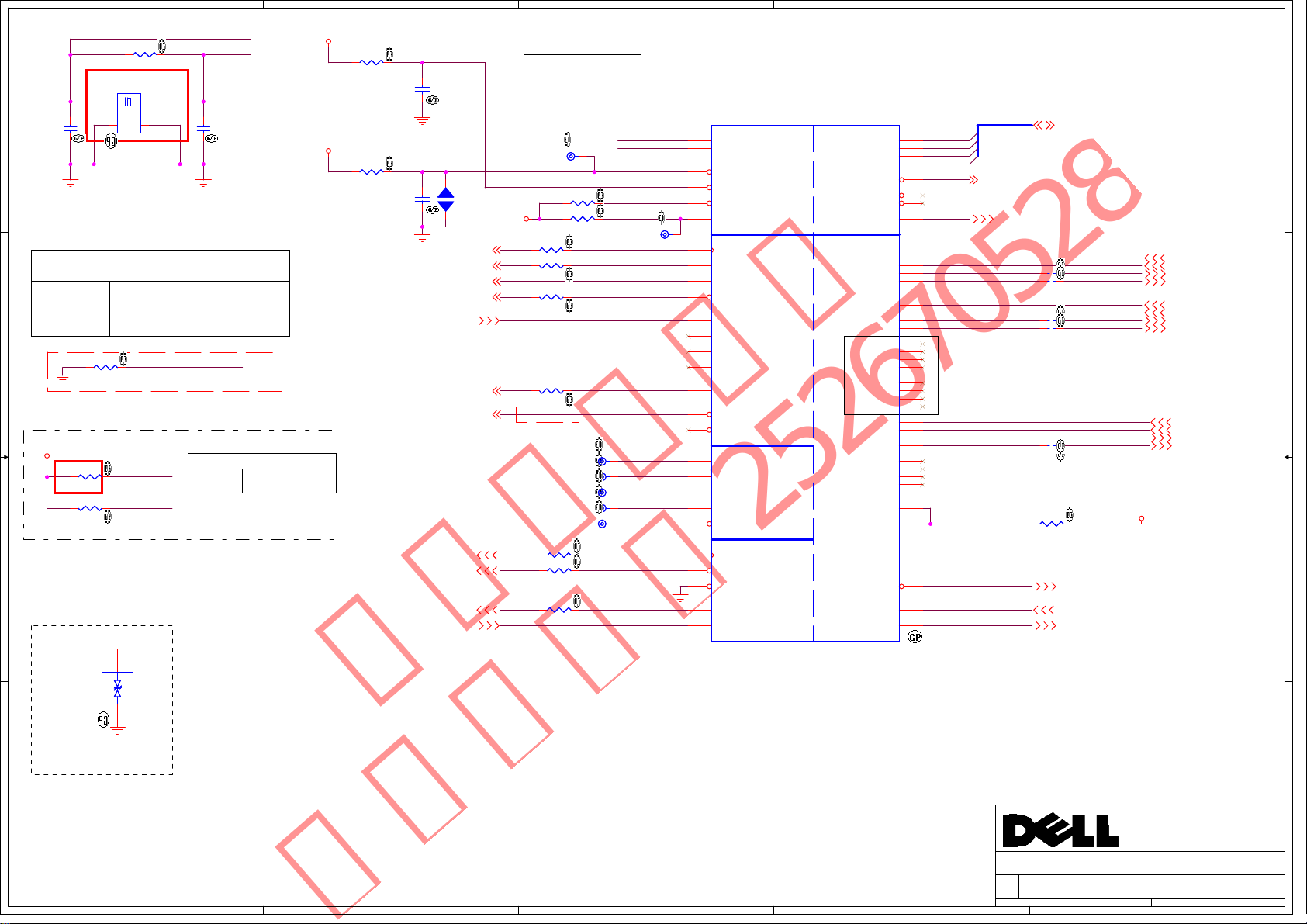

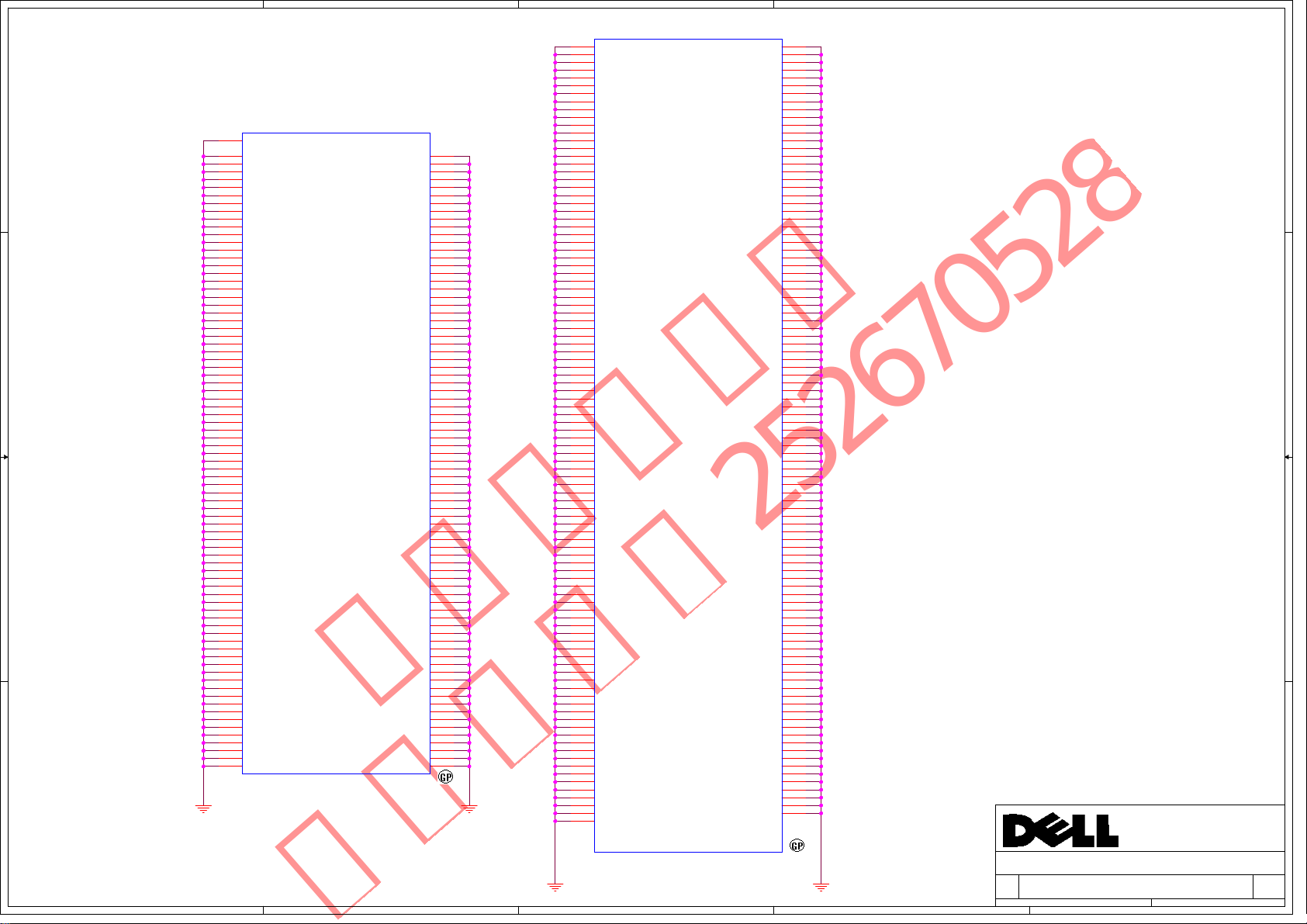

PCH SMBus Block Diagram

+3.3V_ALW

‧

SRN2K2J-1-GP

PCH

D D

SMBCLK

SMBDATA

SMB_CLK

SMB_DATA

22

‧

‧

2N7002SPT

+3.3V_RUN

‧

+3.3V_RUN

‧

‧

‧

‧

‧

‧

‧

SRN2K2J-1-GP

PCH_SMBCLK

PCH_SMBDATA

PCH_SMBCLK

PCH_SMBDATA

PCH_SMBCLK

PCH_SMBDATA

Express

Card

SMB_CLK

SMB_CLK

SMB_DATA

SMB_DATA

C C

PCH_SMBCLK

‧

PCH_SMBDATA

‧

76

PCH_SMBCLK

‧

PCH_SMBDATA

‧

PCH_SMBCLK

‧

PCH_SMBDATA

‧

KBC SMBus Block Diagram

+5V_RUN

‧

SRN10KJ-5-GP

TPDATA

PSDAT1

TPCLK

B B

PSCLK1

+3.3V_RTC_LDO

‧

‧

‧

SRN4K7J-8-GP

BAT_SCL

SCL1

SDA1

BAT_SDA

‧

‧

‧

‧

SRN100J-3-GP

KBC

KBC_SCL1

KBC_SDA1

+3.3V_RTC_LDO

‧

SRN4K7J-8-GP

‧

‧

5

2N7002DW-1-GP

NPCE781

A A

GPIO73/SCL2

GPIO74/SDA2

TouchPad Conn.

TPDATA

TPDATA

TPCLK

TPCLK

SMBus address:12

PBAT_SMBCLK1

PBAT_SMBDAT1

+3.3V_RUN

Battery Conn.

CLK_SMB

DAT_SMB

SMBus address:16

‧

SRN4K7J-8-GP

+3.3V_RUN

‧

THERM_SCL

‧

THERM_SDA

‧

THERM_SCL

THERM_SDA

4

DIMM 1

SCL

SDA

SMBus Address:A0

DIMM 2

SCL

SDA

SMBus Address:A2

Clock

Generator

SMBCLK

SMBDATA

SMBus address:D2

Minicard

WLAN

SMB_CLK

SMB_DATA

Minicard

WWAN

SMB_CLK

SMB_DATA

Free fall

sensor

SCL/SPC

SDA/SDI/SDO

BQ24745

SCL

SDA

Thermal

SMCLK

SMDATA

SMBus address:7A

Capacity

Board

SCL

(On daughter board)

SDA

SMBus address:0A

4

3

2

1

Switchable Graphic SMBus Block Diagram

+3.3V_RUN

PCH

SRN2K2J-1-GP

_DDC_CLK

18

19

07

64

65

40

L_DDC_CLK

L_DDC_DATA

CRT_DDC_CLK

CRT_DDC_DATA

SDVO_CTRLCLK

SDVO_CTRLDATA

L

LDDC_CLK

L_DDC_DATA

LDDC_DATA

SRN2K2J-1-GP

GMCH_DDCCLK

CRT_CLK_DDC

N11M-GE

I2CC_SCL

I2CC_SDA

68

45

44

39

I2CA_SCL

I2CA_SDA

IFPC_AUX_I2CW_SCL

IFPC_AUX_I2CW_SDA#

SRN2K2J-1-GP

HDMI_SDATA_DDC

3

‧

‧

‧

+3.3V_RUN

GMCH_DDCDATA

CRT_DAT_DDC

+3.3V_RUN

SDVO_CLK

HDMI_SCLK_DDC

SDVO_DAT

‧

‧

‧

+3.3V_RUN

‧

‧

‧

+3.3V_RUN

‧

‧

‧

‧

SRN2K2J-1-GP

B1

B0

GND

NC7SB3157P6X-1GP

B1

B0

GND

NC7SB3157P6X-1GP

‧

B1

B0

GND

NC7SB3157P6X-1GP

B1

B0

‧

GND

NC7SB3157P6X-1GP

+3.3V_RUN

‧

SRN2K2J-1-GP

B1

B0

‧

GND

NC7SB3157P6X-1GP

B1

B0

‧‧

GND

NC7SB3157P6X-1GP

VCC

A

S

VCC

A

S

VCC

A

S

VCC

A

S

VCC

A

S

VCC

A

S

+3.3V_RUN

+3.3V_RUN

SRN2K2J-1-GP

+3.3V_RUN

DDC_CLK_CON2

+3.3V_RUN

DDC_DATA_CON2

SRN2K2J-1-GP

+3.3V_RUN

HDMI_SCLK_CON_L

+3.3V_RUN

HDMI_SDATA_CON_L

LDDC_CLK_CON

LDDC_DATA_CON

+3.3V_RUN

DY

‧

+3.3V_RUN

‧

‧

‧

‧

DY

‧

2

+3.3V_RUN

‧

‧

‧

SRN2K2J-1-GP

LCD Conn.

2N7002DW-1-GP

2N7002DW-1-GP

54

+3.3V_RUN_GPU

‧

DDC_CLK_CON

DDC_DATA_CON

+3.3V_RUN

‧

HDMI_SCLK_CON

HDMI_SDATA_CON

+5V_CRT_RUN

‧

SRN2K2J-1-GP

‧

‧

+5V_RUN

‧

‧

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

CRT CONN

SRN2K2J-1-GP

HDMI

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

SMBUS Block Diagram

SMBUS Block Diagram

SMBUS Block Diagram

Vostro Calpella

Vostro Calpella

Vostro Calpella

4 91Monday, January 18, 2010

4 91Monday, January 18, 2010

4 91Monday, January 18, 2010

1

55

55

X01

X01

X01

伟力电脑医院

技术支持:252670528

A

B

C

D

E

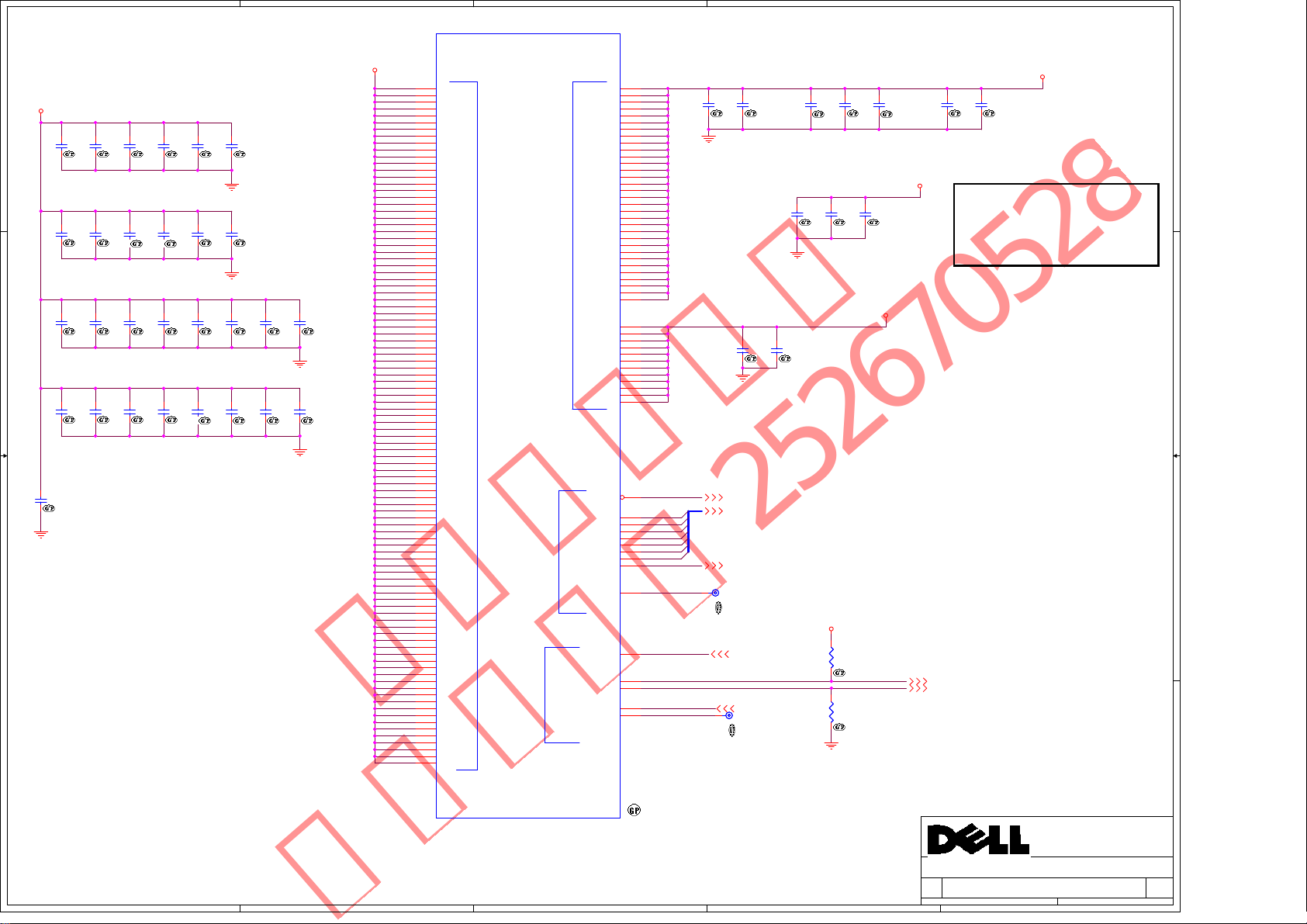

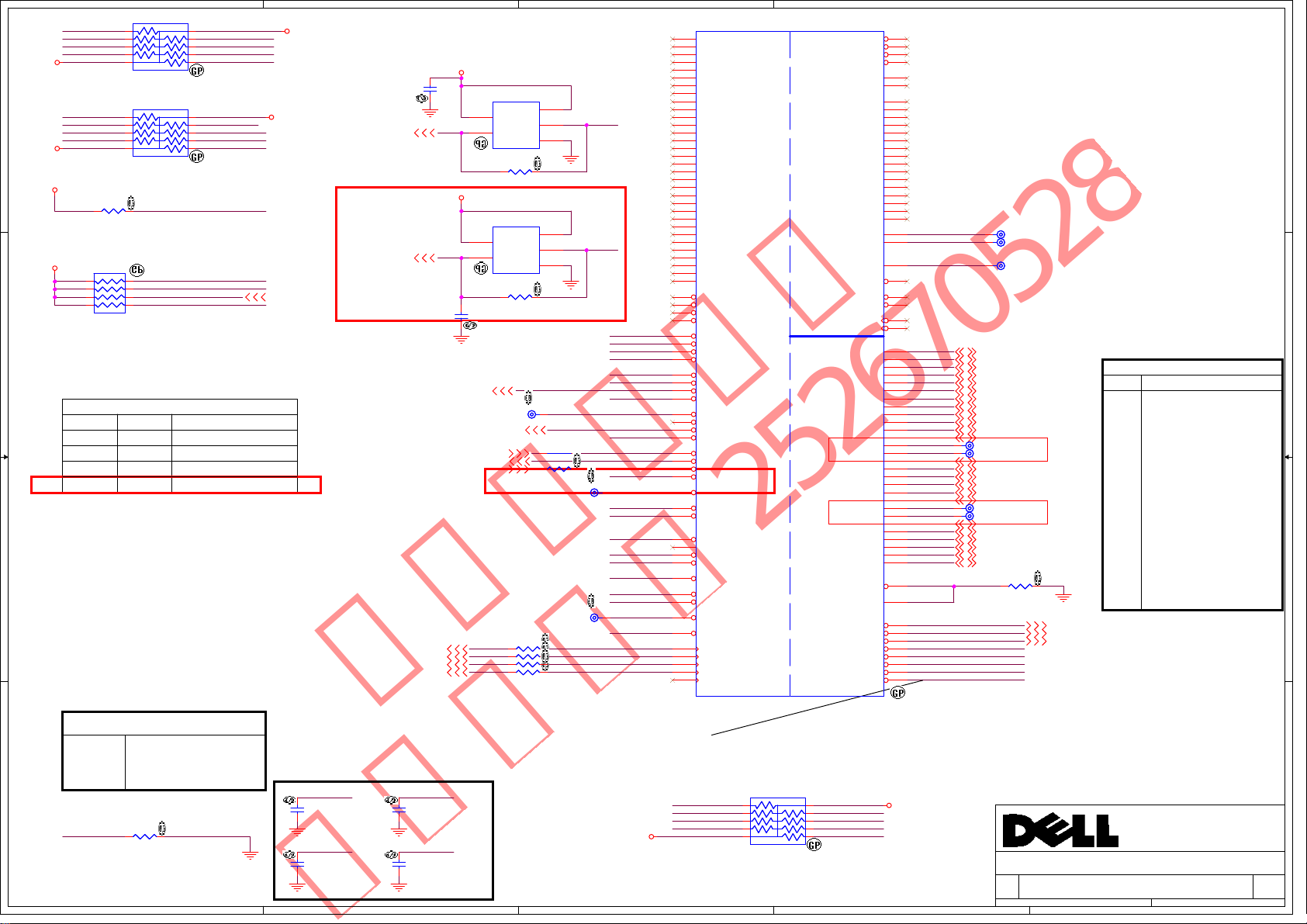

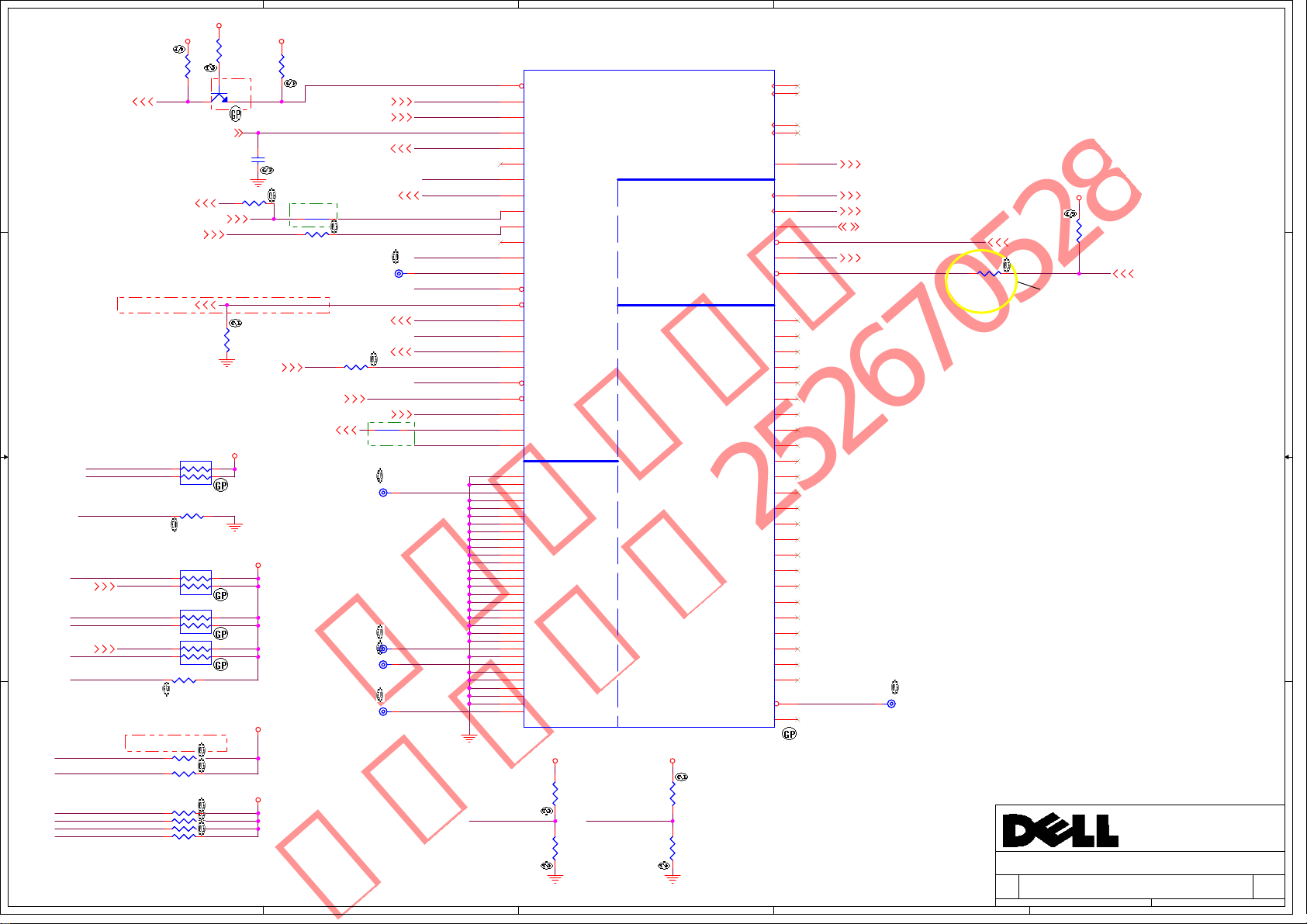

Thermal Block Diagram

1 1

DP1

EMC2102_DN1

2 2

DN1

EMC2102_DP1

Thermal

SC470P50V3JN-2GP

WWAN

EMC2102

DP2

VGA_THERMDA

SC470P50V3JN-2GP

DN2

VGA_THERMDC

3 3

SC470P50V3JN-2GP

DPLUS

DMINUS

MMBT3904-3-GP

GPU

54

MMBT3904-3-GP

Audio Block Diagram

SPKR_PORT_D_L+

SPKR_PORT_D_LSPKR_PORT_D_RSPKR_PORT_D_R+

HP1_PORT_B_L

HP1_PORT_B_R

Codec

92HD81

HP0_PORT_A_L

HP0_PORT_A_R

VREFOUT_A_OR_F

AUD_SPK_L1

AUD_SPK_L2

AUD_SPK_R2

AUD_SPK_R1

AUD_HP1_JACK_L

AUD_HP1_JACK_R

AUD_EXT_MIC_L

AUD_EXT_MIC_R

AUD_VREFOUT_B

0R3-0-U-GP

0R3-0-U-V-GP

AUD_SPK_L1_R

AUD_SPK_L2_R

AUD_SPK_R2_R

AUD_SPK_R1_R

SPEAKER

44

HP

OUT

50

MIC

IN

50

HW T8 sensor

CPU_THERMDA

DP3

DN3

CPU_THERMDC

SC470P50V3JN-2GP

MMBT3904-3-GP

DMIC_CLK/GPIO1

DMIC0/GPIO2

AUD_DMIC_CLK

AUD_DMIC_IN0

HW T8 sensor

28

4 4

A

B

( CPU )

22

C

33R2J-2-GP

33R2J-2-GP AUD_DMIC_IN0_R

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

AUD_DMIC_CLK_G_R

Thermal/Audio Block Diagram

Thermal/Audio Block Diagram

Thermal/Audio Block Diagram

Custom

Custom

Custom

Vostro Calpella

Vostro Calpella

Vostro Calpella

Digital

MIC

Array

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

E

47

5 91Monday, January 18, 2010

5 91Monday, January 18, 2010

5 91Monday, January 18, 2010

X01

X01

X01

伟力电脑医院

技术支持:252670528

A

B

C

D

E

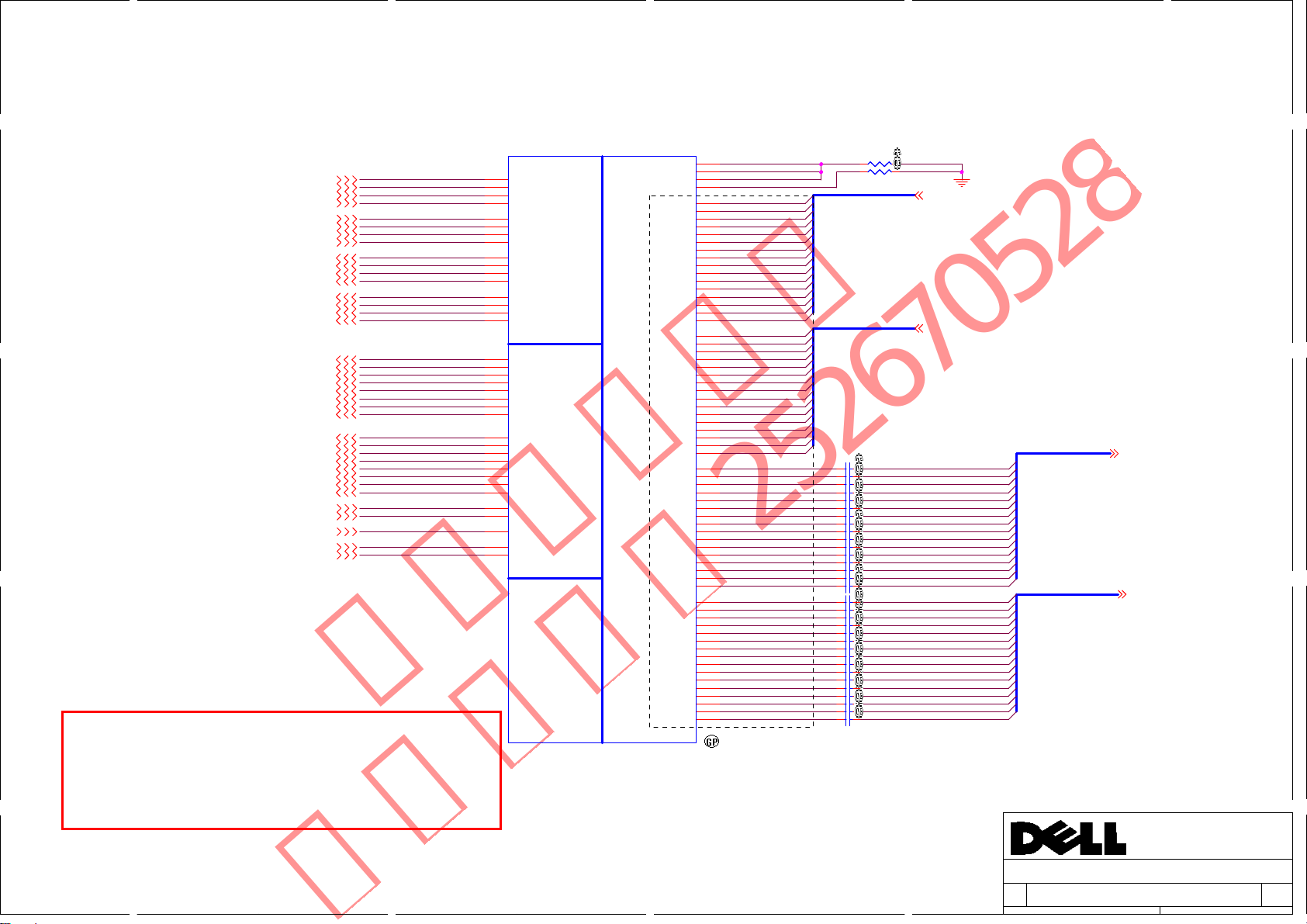

Processor Strapping

PCH Strapping

Name Schematics Notes

Calpella Schematic Checklist Rev.0_7

SPKR

4 4

INIT3_3V# Weak internal pull-down. Do not pull high.

GNT3#/

GPIO55

INTVRMEN

GNT0#,

GNT1#/GPIO51

GNT2#/

GPIO53

GPIO33

3 3

SPI_MOSI

NV_ALE

NC_CLE Weak internal pull-up. Do not pull low.

HAD_DOCK_EN#

/GPIO[33]

HDA_SDO Weak internal pull-down. Do not pull high.

HDA_SYNC

GPIO15

GPIO8

GPIO27

Reboot option at power-up

Internal weak Pull-down.

Default Mode:

Connect to Vcc3_3 with 8.2-kΩ

No Reboot Mode with TCO Disabled:

- 10-kΩ weak pull-up resistor.

Internal pull-up.

Default Mode:

Note: Connect to ground with 4.7-k?

Low (0) = Top Block Swap Mode

weak pull-down resistor. CRB uses a 1 k do not stuff resistor.

High (1) = Integrated VRM is enabled

Low (0) = Integrated VRM is disabled

Left both GNT0# and GNT1# floating. No pull up

Default (SPI):

required.

Connect GNT1# to ground with 1-kΩ pull-down

Boot from PCI:

resistor. Leave GNT0# Floating.

Connect both GNT0# and GNT1# to ground with 1-kΩ

Boot from LPC:

pull-down resistor.

Default - Internal pull-up.

= Configures DMI for ESI compatible operation (for servers

Low (0)

only. Not for mobile/desktops).

Do not pull low.

Default:

Connect to ground with 1-kΩ

Disable ME in Manufacturing Mode:

pull-down resistor.

Connect to Vcc3_3 with 8.2-kΩ weak pull-up resistor.

Enable iTPM:

Left floating, no pull-down required.

Disable iTPM:

Connect to Vcc3_3 with 8.2-kΩ weak pull-up

Enable Danbury:

resistor.

Connect to ground with 4.7-kΩ weak pull-down

Disable Danbury:

resistor.

Flash Descriptor Security will be overridden.

Low (0):

Flash Descriptor Security will be in effect.

High (1) :

Weak internal pull-down. Do not pull high.

Weak internal pull-down. Do not pull high.

Weak internal pull-up. Do not pull low.

Default = Do not connect (floating)

High(1) = Enables the internal VccVRM to have a clean supply for

analog rails. No need to use on-board filter circuit.

Low (0) = Disables the VccVRM. Need to use on-board filter

circuits for analog rails.

2 2

Pin Name Strap Description Configuration (Default value for each bit is

CFG[4] Disabled - No Physical Display Port attached to

CFG[3]

CFG[0]

CFG[7]

DisplayPort

Presence

PCI-Express Static

Lane Reversal

PCI-Express

Configuration

Select

Reserved Temporarily used

for early

Clarksfield

samples.

1 unless specified otherwise)

1:Embedded

Embedded DisplayPort.

Enabled - An external Display Port device is

0:

connected to the Embedded Display Port.

Normal Operation.

1:

Lane Numbers Reversed 15 -> 0, 14 -> 1, ...

0:

Single PCI-Express Graphics

1:

Bifurcation enabled

0:

-

Clarksfield (only for early samples pre-ES1)

Connect to GND with 3.01K Ohm/5% resistor

Only temporary for early CFD samples

Note:

(rPGA/BGA) [For details please refer to the WW33

MoW and sighting report].

For a common motherboard design (for AUB and CFD),

the pull-down resistor should be used. Does not

impact AUB functionality.

Calpella Schematic Checklist Rev.0_7

Default

Value

1

1

1

0

PCIE Routing

LANE1

LANE2

LANE3 LAN

1 1

Card reader

MiniCard WLAN

MiniCard WWANLANE4

New CardLANE5

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Vostro Calpella

Vostro Calpella

Vostro Calpella

Taipei Hsien 221, Taiwan, R.O.C.

Table of Content

Table of Content

Table of Content

6 91Monday, January 18, 2010

6 91Monday, January 18, 2010

6 91Monday, January 18, 2010

X01

X01

X01

伟力电脑医院

技术支持:252670528

5

D D

DW

12/08 Item 5

R708

R708

0R0603-PAD-1-GP

0R0603-PAD-1-GP

+3.3V_RUN +3.3V_RUN_SL585

1 2

12

DY

DY

C701

C701

SC1U10V2KX-1GP

SC1U10V2KX-1GP

12

DY

DY

C702

C702

SC10U10V5ZY-1GP

SC10U10V5ZY-1GP

12

C704

C704

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

C703

C703

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

4

12

C705

C705

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C707

C707

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C708

C708

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

+3.3V_RUN_SL585 +1.05V_RUN_SL585_IO

+1.05V_VTT

12

DY

DY

DW

12/08 Item 5

R709

R709

0R0603-PAD-1-GP

0R0603-PAD-1-GP

1 2

C709

C709

SC1U10V2KX-1GP

SC1U10V2KX-1GP

3

12

DY

DY

C710

C710

SC10U6D3V3MX-GP

SC10U6D3V3MX-GP

+1.05V_RUN_SL585_IO

12

C711

C711

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

12

C712

C712

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

2

1

C C

DREFCLK#[23]

DREFCLK[23]

CLKIN_DMI#[23]

CLKIN_DMI[23]

CLK_PCIE_SATA#[23]

CLK_PCIE_SATA[23]

CLK_CPU_BCLK#[23]

CLK_CPU_BCLK[23]

B B

TP701TPAD14-GP TP701TPAD14-GP

TP702TPAD14-GP TP702TPAD14-GP

DREFCLK#

DREFCLK

CLKIN_DMI#

CLKIN_DMI

CLK_PCIE_SATA#

CLK_PCIE_SATA

CLK_CPU_BCLK#

CLK_CPU_BCLK

TP_CPU_1#

1

TP_CPU_1

1

U701

U701

4

DOT_96#

3

DOT_96

14

SRC_2#

13

SRC_2

11

SRC_1/SATA#

10

SRC_1/SATA

22

CPU_0#

23

CPU_0

19

CPU_1#

20

CPU_1

SLG8SP585VTR-GP

SLG8SP585VTR-GP

29

17

24

VDD_SRC

VDD_CPU

VSS_REF

GND

21

26

33

1st Silego 71.08585.003

2nd ICS 71.93197.003

A A

5

4

VDD_REF

VSS_CPU

1

VDD_DOT

VSS_SRC

12

15

5

VDD_27

VDD_SRC_IO

VSS_DOT

VSS_278VSS_SATA

2

+1.05V_VTT

R704

R704

4K7R2J-2-GP

4K7R2J-2-GP

R707

R707

10KR2J-3-GP

10KR2J-3-GP

18

VDD_CPU_IO

27MHZ

27MHZ_SS

CPU_STOP#

CKPWRGD/PD#

REF_0/CPU_SEL

XTAL_IN

XTAL_OUT

9

DY

DY

1 2

1 2

SDA

SCL

FSC

6

7

16

25

30

28

27

31

32

12

CLK_27M

CLK_27M_SS

CPU_STOP#

CK_PWRGD

FSC

CLK_XTAL_IN

CLK_XTAL_OUT

X701

X701

1 2

X-14D31818M-37GP

X-14D31818M-37GP

C714

C714

SC12P50V2JN-3GP

SC12P50V2JN-3GP

3

VGA 27M

SS

DY Mount

NON-SS Mount DY

R706 33R2J-2-GP

R706 33R2J-2-GP

R710 33R2J-2-GP

R710 33R2J-2-GP

R701 2K2R2J-2-GPR701 2K2R2J-2-GP

R703 33R2J-2-GPR703 33R2J-2-GP

PCH_SMBDATA [18,19,23,40,64,65]

PCH_SMBCLK [18,19,23,40,64,65]

12

DY

DY

12

DY

DY

12

12

CLK_XTAL_IN

CLK_XTAL_OUT

12

C715

C715

SC15P50V2JN-2-GP

SC15P50V2JN-2-GP

FSC 0 1

SPEED

133MHz

(Default)

R710R706

+3.3V_RUN

12

EC701

EC701

DY

DY

SC4D7P50V2CN-1GP

SC4D7P50V2CN-1GP

100MHz

CLK_VGA_27M [81]

CLK_PCH_14M [23]

2

+3.3V_RUN_SL585

R705

R705

10KR2J-3-GP

10KR2J-3-GP

CK_PWRGD

1 2

Q701

Q701

2N7002A-7-GP

2N7002A-7-GP

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Clock Generator SLG8SP585

Clock Generator SLG8SP585

Clock Generator SLG8SP585

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

Date: Sheet of

Date: Sheet of

Date: Sheet of

G

VR_CLKEN# [47]

SD

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Vostro Calpella

Vostro Calpella

Vostro Calpella

1

X01

X01

7 91Monday, January 18, 2010

7 91Monday, January 18, 2010

7 91Monday, January 18, 2010

X01

伟力电脑医院

技术支持:252670528

5

A

4

3

2

1

D D

1 OF 9

CPU1A

CPU1A

DMI_PTX_CRXN0[22]

DMI_PTX_CRXN1[22]

DMI_PTX_CRXN2[22]

DMI_PTX_CRXN3[22]

DMI_PTX_CRXP0[22]

DMI_PTX_CRXP1[22]

DMI_PTX_CRXP2[22]

DMI_PTX_CRXP3[22]

DMI_CTX_PRXN0[22]

DMI_CTX_PRXN1[22]

DMI_CTX_PRXN2[22]

DMI_CTX_PRXN3[22]

DMI_CTX_PRXP0[22]

DMI_CTX_PRXP1[22]

DMI_CTX_PRXP2[22]

DMI_CTX_PRXP3[22]

C C

FDI_TXN0[22]

FDI_TXN1[22]

FDI_TXN2[22]

FDI_TXN3[22]

FDI_TXN4[22]

FDI_TXN5[22]

FDI_TXN6[22]

FDI_TXN7[22]

FDI_TXP0[22]

FDI_TXP1[22]

FDI_TXP2[22]

FDI_TXP3[22]

FDI_TXP4[22]

FDI_TXP5[22]

FDI_TXP6[22]

FDI_TXP7[22]

FDI_FSYNC0[22]

FDI_FSYNC1[22]

FDI_INT[22]

FDI_LSYNC0[22]

FDI_LSYNC1[22]

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

A24

C23

B22

A21

B24

D23

B23

A22

D24

G24

F23

H23

D25

F24

E23

G23

E22

D21

D19

D18

G21

E19

F21

G18

D22

C21

D20

C18

G22

E20

F20

G19

F17

E17

C17

F18

D17

DMI_RX#0

DMI_RX#1

DMI_RX#2

DMI_RX#3

DMI_RX0

DMI_RX1

DMI_RX2

DMI_RX3

DMI_TX#0

DMI_TX#1

DMI_TX#2

DMI_TX#3

DMI_TX0

DMI_TX1

DMI_TX2

DMI_TX3

FDI_TX#0

FDI_TX#1

FDI_TX#2

FDI_TX#3

FDI_TX#4

FDI_TX#5

FDI_TX#6

FDI_TX#7

FDI_TX0

FDI_TX1

FDI_TX2

FDI_TX3

FDI_TX4

FDI_TX5

FDI_TX6

FDI_TX7

FDI_FSYNC0

FDI_FSYNC1

FDI_INT

FDI_LSYNC0

FDI_LSYNC1

CLARKSFIELD

CLARKSFIELD

B B

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

Calpella Platform Design Guide

Revision 1.6

2.4 Arrandale Graphics Disable Guideline

It applies to Arrandale and Clarksfield discrete graphic designs.

FDI_TX[7:0] and FDI_TX#[7:0] can be left floating on the Arrandale. The GFX_IMON,

FDI_FSYNC[0], FDI_FSYNC[1], FDI_LSYNC[0], FDI_LSYNC[1], and FDI_INT signals on

the Arrandale side should be tied to GND (through 1-kΩ ±5% resistors).

Page 89

CLARKUNF

CLARKUNF

1 OF 9

PEG_RX#0

PEG_RX#1

PEG_RX#2

PEG_RX#3

PEG_RX#4

PEG_RX#5

PEG_RX#6

PEG_RX#7

PEG_RX#8

PEG_RX#9

PEG_RX0

PEG_RX1

PEG_RX2

PEG_RX3

PEG_RX4

PEG_RX5

PEG_RX6

PEG_RX7

PEG_RX8

PEG_RX9

PEG_RX10

PEG_RX11

PEG_RX12

PEG_RX13

PEG_RX14

PEG_RX15

PEG_TX#0

PEG_TX#1

PEG_TX#2

PEG_TX#3

PEG_TX#4

PEG_TX#5

PEG_TX#6

PEG_TX#7

PEG_TX#8

PEG_TX#9

PEG_TX0

PEG_TX1

PEG_TX2

PEG_TX3

PEG_TX4

PEG_TX5

PEG_TX6

PEG_TX7

PEG_TX8

PEG_TX9

PEG_TX10

PEG_TX11

PEG_TX12

PEG_TX13

PEG_TX14

PEG_TX15

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

DMI

DMI

PEG_RX#10

PEG_RX#11

PEG_RX#12

PEG_RX#13

PEG_RX#14

PEG_RX#15

Intel(R) FDI

Intel(R) FDI

PEG_TX#10

PEG_TX#11

PEG_TX#12

PEG_TX#13

PEG_TX#14

PEG_TX#15

PEG_IRCOMP_R

EXP_RBIAS

PCIE_MRX_GTX_N15

PCIE_MRX_GTX_N14

PCIE_MRX_GTX_N13

PCIE_MRX_GTX_N12

PCIE_MRX_GTX_N11

PCIE_MRX_GTX_N10

PCIE_MRX_GTX_N9

PCIE_MRX_GTX_N8

PCIE_MRX_GTX_N7

PCIE_MRX_GTX_N6

PCIE_MRX_GTX_N5

PCIE_MRX_GTX_N4

PCIE_MRX_GTX_N3

PCIE_MRX_GTX_N2

PCIE_MRX_GTX_N1

PCIE_MRX_GTX_N0

PCIE_MRX_GTX_P15

PCIE_MRX_GTX_P14

PCIE_MRX_GTX_P13

PCIE_MRX_GTX_P12

PCIE_MRX_GTX_P11

PCIE_MRX_GTX_P10

PCIE_MRX_GTX_P9

PCIE_MRX_GTX_P8

PCIE_MRX_GTX_P7

PCIE_MRX_GTX_P6

PCIE_MRX_GTX_P5

PCIE_MRX_GTX_P4

PCIE_MRX_GTX_P3

PCIE_MRX_GTX_P2

PCIE_MRX_GTX_P1

PCIE_MRX_GTX_P0

PCIE_MTX_GRX_C_N15

PCIE_MTX_GRX_C_N14

PCIE_MTX_GRX_C_N13

PCIE_MTX_GRX_C_N12

PCIE_MTX_GRX_C_N11

PCIE_MTX_GRX_C_N10

PCIE_MTX_GRX_C_N9

PCIE_MTX_GRX_C_N8

PCIE_MTX_GRX_C_N7

PCIE_MTX_GRX_C_N6

PCIE_MTX_GRX_C_N5

PCIE_MTX_GRX_C_N4

PCIE_MTX_GRX_C_N3

PCIE_MTX_GRX_C_N2

PCIE_MTX_GRX_C_N1

PCIE_MTX_GRX_C_N0

PCIE_MTX_GRX_C_P15

PCIE_MTX_GRX_C_P14

PCIE_MTX_GRX_C_P13

PCIE_MTX_GRX_C_P12

PCIE_MTX_GRX_C_P11

PCIE_MTX_GRX_C_P10

PCIE_MTX_GRX_C_P9

PCIE_MTX_GRX_C_P8

PCIE_MTX_GRX_C_P7

PCIE_MTX_GRX_C_P6

PCIE_MTX_GRX_C_P5

PCIE_MTX_GRX_C_P4

PCIE_MTX_GRX_C_P3

PCIE_MTX_GRX_C_P2

PCIE_MTX_GRX_C_P1

PCIE_MTX_GRX_C_P0

R801 49D9R2F-GPR801 49D9R2F-GP

1 2

R802 750R2F-GPR802 750R2F-GP

1 2

PCIE_MRX_GTX_N[0..15]

PCIE_MRX_GTX_P[0..15]

C829 SCD1U10V2KX-5GP

C829 SCD1U10V2KX-5GP

1 2

DIS

DIS

C827 SCD1U10V2KX-5GP

C827 SCD1U10V2KX-5GP

1 2

DIS

DIS

C832 SCD1U10V2KX-5GP

C832 SCD1U10V2KX-5GP

1 2

DIS

DIS

C812 SCD1U10V2KX-5GP

C812 SCD1U10V2KX-5GP

1 2

DIS

DIS

C803 SCD1U10V2KX-5GP

C803 SCD1U10V2KX-5GP

1 2

DIS

DIS

C811 SCD1U10V2KX-5GP

C811 SCD1U10V2KX-5GP

1 2

DIS

DIS

C828 SCD1U10V2KX-5GP

C828 SCD1U10V2KX-5GP

1 2

DIS

DIS

C810 SCD1U10V2KX-5GP

C810 SCD1U10V2KX-5GP

1 2

DIS

DIS

C823 SCD1U10V2KX-5GP

C823 SCD1U10V2KX-5GP

1 2

DIS

DIS

C804 SCD1U10V2KX-5GP

C804 SCD1U10V2KX-5GP

1 2

DIS

DIS

C831 SCD1U10V2KX-5GP

C831 SCD1U10V2KX-5GP

1 2

DIS

DIS

C825 SCD1U10V2KX-5GP

C825 SCD1U10V2KX-5GP

1 2

DIS

DIS

C821 SCD1U10V2KX-5GP

C821 SCD1U10V2KX-5GP

1 2

DIS

DIS

C813 SCD1U10V2KX-5GP

C813 SCD1U10V2KX-5GP

1 2

DIS

DIS

C806 SCD1U10V2KX-5GP

C806 SCD1U10V2KX-5GP

1 2

DIS

DIS

C816 SCD1U10V2KX-5GP

C816 SCD1U10V2KX-5GP

1 2

DIS

DIS

C826 SCD1U10V2KX-5GP

C826 SCD1U10V2KX-5GP

1 2

DIS

DIS

C822 SCD1U10V2KX-5GP

C822 SCD1U10V2KX-5GP

1 2

DIS

DIS

C818 SCD1U10V2KX-5GP

C818 SCD1U10V2KX-5GP

1 2

DIS

DIS

C815 SCD1U10V2KX-5GP

C815 SCD1U10V2KX-5GP

1 2

DIS

DIS

C808 SCD1U10V2KX-5GP

C808 SCD1U10V2KX-5GP

1 2

DIS

DIS

C802 SCD1U10V2KX-5GP

C802 SCD1U10V2KX-5GP

1 2

DIS

DIS

C820 SCD1U10V2KX-5GP

C820 SCD1U10V2KX-5GP

1 2

DIS

DIS

C805 SCD1U10V2KX-5GP

C805 SCD1U10V2KX-5GP

1 2

DIS

DIS

C817 SCD1U10V2KX-5GP

C817 SCD1U10V2KX-5GP

1 2

DIS

DIS

C801 SCD1U10V2KX-5GP

C801 SCD1U10V2KX-5GP

1 2

DIS

DIS

C814 SCD1U10V2KX-5GP

C814 SCD1U10V2KX-5GP

1 2

DIS

DIS

C824 SCD1U10V2KX-5GP

C824 SCD1U10V2KX-5GP

1 2

DIS

DIS

C830 SCD1U10V2KX-5GP

C830 SCD1U10V2KX-5GP

1 2

DIS

DIS

C809 SCD1U10V2KX-5GP

C809 SCD1U10V2KX-5GP

1 2

DIS

DIS

C807 SCD1U10V2KX-5GP

C807 SCD1U10V2KX-5GP

1 2

DIS

DIS

C819 SCD1U10V2KX-5GP

C819 SCD1U10V2KX-5GP

1 2

DIS

DIS

PCIE_MRX_GTX_N[0..15] [80]

PCIE_MRX_GTX_P[0..15] [80]

PCIE_MTX_GRX_N15

PCIE_MTX_GRX_N14

PCIE_MTX_GRX_N13

PCIE_MTX_GRX_N12

PCIE_MTX_GRX_N11

PCIE_MTX_GRX_N10

PCIE_MTX_GRX_N9

PCIE_MTX_GRX_N8

PCIE_MTX_GRX_N7

PCIE_MTX_GRX_N6

PCIE_MTX_GRX_N5

PCIE_MTX_GRX_N4

PCIE_MTX_GRX_N3

PCIE_MTX_GRX_N2

PCIE_MTX_GRX_N1

PCIE_MTX_GRX_N0

PCIE_MTX_GRX_P15

PCIE_MTX_GRX_P14

PCIE_MTX_GRX_P13

PCIE_MTX_GRX_P12

PCIE_MTX_GRX_P11

PCIE_MTX_GRX_P10

PCIE_MTX_GRX_P9

PCIE_MTX_GRX_P8

PCIE_MTX_GRX_P7

PCIE_MTX_GRX_P6

PCIE_MTX_GRX_P5

PCIE_MTX_GRX_P4

PCIE_MTX_GRX_P3

PCIE_MTX_GRX_P2

PCIE_MTX_GRX_P1

PCIE_MTX_GRX_P0

Reversal

1.PCI-Express Static Lane Reversal

(15 -> 0, 14 -> 1, ...)

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

PCIE_MTX_GRX_N[0..15]

PCIE_MTX_GRX_P[0..15]

CPU (PCIE/DMI/FDI)

CPU (PCIE/DMI/FDI)

CPU (PCIE/DMI/FDI)

PCIE_MTX_GRX_N[0..15] [80]

PCIE_MTX_GRX_P[0..15] [80]

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Vostro Calpella

Vostro Calpella

Vostro Calpella

8 91Monday, January 18, 2010

8 91Monday, January 18, 2010

8 91Monday, January 18, 2010

X01

X01

X01

A

伟力电脑医院

技术支持:252670528

5

A

+1.05V_VTT

D D

C C

B B

Processor Pullups

R902 49D9R2F-GPR902 49D9R2F-GP

1 2

R933 68R2-GPR933 68R2-GP

1 2

R904 68R2-GP

R904 68R2-GP

1 2

DY

DY

+1.5V_RUN

12

R919

R919

1K1R2F-GP

1K1R2F-GP

DY

DY

PM_DRAM_PWRGD

12

R920

R920

750R2F-GP

750R2F-GP

H_CATERR#

H_PROCHOT_R#

H_CPURST#

H_PROCHOT#[47]

PLT_RST#[21,37,64,65,70,76,77,80]

H_PWRGOOD[25,42]

PM_DRAM_PWRGD[22]

H_VTTPWRGD[49]

S3 circuit

Normal 1.27k 3k

Processor Compensation Signals

1 2

R901 20R2F-GPR901 20R2F-GP

1 2

R903 20R2F-GPR903 20R2F-GP

1 2

R905 49D9R2F-GPR905 49D9R2F-GP

1 2

R906 49D9R2F-GPR906 49D9R2F-GP

TP901TPAD14-GP TP901TPAD14-GP

R936

R936

0R2J-2-GP

0R2J-2-GP

1 2

DY

DY

R931

R931

1KR2J-1-GP

1KR2J-1-GP

DW

12/08 Item 5

PLT_RST#[21,37,64,65,70,76,77,80]

R908

R908

0R0402-PAD

0R0402-PAD

1 2

R920R919

1.1k

No Stuff

0.75k

1

H_THRMTRIP#[25,37,42]

1 2

DY

DY

R913

R913

1K6R2F-GP

1K6R2F-GP

1 2

SKTOCC#_R

H_CATERR#

H_PECI[25]

H_PROCHOT_R#

H_PM_SYNC[22]

4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

H_CPURST#

VCCPWRGOOD

PM_DRAM_PWRGD

PLT_RST#_R

12

R915

R915

750R2F-GP

750R2F-GP

AT23

AT24

G16

AT26

AH24

AK14

AT15

AN26

AK15

AP26

AL15

AN14

AN27

AK13

AM15

AM26

AL14

CPU1B

CPU1B

COMP3

COMP2

COMP1

COMP0

SKTOCC#

CATERR#

PECI

PROCHOT#

THERMTRIP#

RESET_OBS#

PM_SYNC

VCCPWRGOOD_1

VCCPWRGOOD_0

SM_DRAMPWROK

VTTPWRGOOD

TAPPWRGOOD

RSTIN#

CLARKUNF

CLARKUNF

MISC THERMAL

MISC THERMAL

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

CLOCKS

CLOCKS

SM_DRAMRST#

SM_RCOMP0

SM_RCOMP1

MISC

MISC

SM_RCOMP2

PM_EXT_TS#0

PM_EXT_TS#1

CLARKSFIELD

CLARKSFIELD

DDR3

DDR3

PWR MANAGEMENT

PWR MANAGEMENT

JTAG & BPM

JTAG & BPM

3

2 OF 9

2 OF 9

BCLK

BCLK#

PRDY#

PREQ#

TCK

TMS

TRST#

TDO

TDI_M

TDO_M

DBR#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

RN907

DPLL_REF_SSCLK#_R

DPLL_REF_SSCLK_R

A16

B16

AR30

AT30

E16

D16

DPLL_REF_SSCLK_R

A18

DPLL_REF_SSCLK#_R

A17

SM_DRAMRST#

F6

SM_RCOMP_0

AL1

SM_RCOMP_1

AM1

SM_RCOMP_2

AN1

AN15

AP15

AT28

AP27

AN28

AP28

XDP_TRST#

AT27

AT29

TDI

AR27

AR29

AP29

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

XDP_TDO_R

XDP_TDI_M

XDP_TDO_M

XDP_DBRESET#

VTT_PWRGD[25,37,49,50]

RN907

1

4

2 3

SRN1KJ-7-GP

SRN1KJ-7-GP

DW

10/26 Item 31

R2114 10KR2J-3-GPR2114 10KR2J-3-GP

1 2

U927_B

1

2

3

XDP_TDO_M

XDP_TDI_M

Scan Chain

(Default)

4

XDP_DBRESET# [22,25]

U927

U927

B

VCC

A

Y

GND

74LVC1G08GW-1-GP

74LVC1G08GW-1-GP

2

BCLK_CPU_P [25]

BCLK_CPU_N [25]

CLK_EXP_P [23]

CLK_EXP_N [23]

RN905

RN905

SRN10KJ-5-GP

SRN10KJ-5-GP

12

+1.05V_VTT

1

23

PM_EXTTS#0 [18]

PM_EXTTS#1 [19]

DDR3 Compensation Signals

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

Calpella Platform S3 Power Reduction Platform

S3 Power Reduction CRB Implementation

Design Details

+3.3V_ALW

R977

+1.05V_VTT

12

R977

1K6R2F-GP

1K6R2F-GP

R928

R928

51R2J-2-GP

51R2J-2-GP

XDP_TDO_R

12

5

VTT_PWRGD_R3 PM_DRAM_PWRGD

4

R924

R924

0R0402-PAD

0R0402-PAD

DW

12/08 Item 5

12

G

Vgs(th)<=1.5V

Q901

Q901

BSS138-7-F-GP

BSS138-7-F-GP

1 2

DY

DY

R935

R935

0R2J-2-GP

0R2J-2-GP

R907 100R2F-L1-GP-UR907 100R2F-L1-GP-U

R910 24D9R2F-L-GPR910 24D9R2F-L-GP

R911 130R2F-1-GPR911 130R2F-1-GP

DDR_RST_GATE [25]

C915

C915

SCD047U16V2ZY-1GP

SCD047U16V2ZY-1GP

+1.5V_SUS

12

R934

R934

1KR2J-1-GP

1KR2J-1-GP

DS

0611

1 2

1 2

1 2

XDP_TRST#

DDR3_DRAMRST# [18,19]

12

R923

R923

51R2J-2-GP

51R2J-2-GP

1

SM_DRAMRST#

Revision 0.1

1 2

R988

R988

100KR2J-1-GP

100KR2J-1-GP

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU (THERMAL/CLOCK/PM )

CPU (THERMAL/CLOCK/PM )

5

4

3

2

CPU (THERMAL/CLOCK/PM )

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

Date: Sheet of

Date: Sheet of

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

Vostro Calpella

Vostro Calpella

Vostro Calpella

9 91Monday, January 18, 2010

9 91Monday, January 18, 2010

9 91Monday, January 18, 2010

1

X01

X01

X01

A

伟力电脑医院

技术支持:252670528

5

CPU1C

CPU1C

4

3 OF 9

3 OF 9

3

CPU1D

CPU1D

2

4 OF 9

4 OF 9

1

W8

AA6

SA_CK0

AA7

M_A_DQ[63..0][18]

D D

C C

B B

M_A_DQ[63..0]

M_A_BS0[18]

M_A_BS1[18]

M_A_BS2[18]

M_A_CAS#[18]

M_A_RAS#[18]

M_A_WE#[18]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

A10

C10

B10

D10

E10

F10

H10

G10

AH5

AF5

AK6

AK7

AF6

AG5

AJ7

AJ6

AJ10

AJ9

AL10

AK12

AK8

AL7

AK11

AL8

AN8

AM10

AR11

AL11

AM9

AN9

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AL13

AR14

AP14

AC3

AB2

AE1

AB3

AE9

SA_DQ0

SA_DQ1

C7

SA_DQ2

A7

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

A8

SA_DQ7

D8

SA_DQ8

SA_DQ9

E6

SA_DQ10

F7

SA_DQ11

E9

SA_DQ12

B7

SA_DQ13

E7

SA_DQ14

C6

SA_DQ15

SA_DQ16

G8

SA_DQ17

K7

SA_DQ18

J8

SA_DQ19

G7

SA_DQ20

SA_DQ21

J7

SA_DQ22

J10

SA_DQ23

L7

SA_DQ24

M6

SA_DQ25

M8

SA_DQ26

L9

SA_DQ27

L6

SA_DQ28

K8

SA_DQ29

N8

SA_DQ30

P9

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SA_BS0

SA_BS1

U7

SA_BS2

SA_CAS#

SA_RAS#

SA_WE#

SA_CK#0

P7

SA_CKE0

Y6

SA_CK1

Y5

SA_CK#1

P6

SA_CKE1

AE2

SA_CS#0

AE8

SA_CS#1

CLARKSFIELD

CLARKSFIELD

AD8

SA_ODT0

AF9

SA_ODT1

M_A_DM0

B9

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS#0

SA_DQS#1

SA_DQS#2

SA_DQS#3

SA_DQS#4

SA_DQS#5

SA_DQS#6

SA_DQS#7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_CLK_DDR0 [18]

M_CLK_DDR#0 [18]

M_CKE0 [18]

M_CLK_DDR1 [18]

M_CLK_DDR#1 [18]

M_CKE1 [18]

M_CS0# [18]

M_CS1# [18]

M_ODT0 [18]

M_ODT1 [18]

M_B_DQ[63..0][19]

M_A_DM[7..0] [18]

M_A_DQS#[7..0] [18]

M_A_DQS[7..0] [18]

M_A_A[15..0] [18]

M_B_DQ[63..0]

M_B_BS0[19]

M_B_BS1[19]

M_B_BS2[19]

M_B_CAS#[19]

M_B_RAS#[19]

M_B_WE#[19]

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AF3

AG1

AK1

AG4

AG3

AH4

AK3

AK4

AM6

AN2

AK5

AK2

AM4

AM3

AP3

AN5

AT4

AN6

AN4

AN3

AT5

AT6

AN7

AP6

AP8

AT9

AT7

AP9

AR10

AT10

AC5

AC6

AJ3

AJ4

AB1

B5

SB_DQ0

A5

SB_DQ1

C3

SB_DQ2

B3

SB_DQ3

E4

SB_DQ4

A6

SB_DQ5

A4

SB_DQ6

C4

SB_DQ7

D1

SB_DQ8

D2

SB_DQ9

F2

SB_DQ10

F1

SB_DQ11

C2

SB_DQ12

F5

SB_DQ13

F3

SB_DQ14

G4

SB_DQ15

H6

SB_DQ16

G2

SB_DQ17

J6

SB_DQ18

J3

SB_DQ19

G1

SB_DQ20

G5

SB_DQ21

J2

SB_DQ22

J1

SB_DQ23

J5

SB_DQ24

K2

SB_DQ25

L3

SB_DQ26

M1

SB_DQ27

K5

SB_DQ28

K4

SB_DQ29

M4

SB_DQ30

N5

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

SB_BS0

W5

SB_BS1

R7

SB_BS2

SB_CAS#

Y7

SB_RAS#

SB_WE#

CLARKSFIELD

CLARKSFIELD

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

SB_CK0

SB_CK#0

SB_CKE0

SB_CK1

SB_CK#1

SB_CKE1

SB_CS#0

SB_CS#1

SB_ODT0

SB_ODT1

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS#0

SB_DQS#1

SB_DQS#2

SB_DQS#3

SB_DQS#4

SB_DQS#5

SB_DQS#6

SB_DQS#7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

W9

M3

V7

V6

M2

AB8

AD6

AC7

AD1

D4

E1

H3

K1

AH1

AL2

AR4

AT8

D5

F4

J4

L4

AH2

AL4

AR5

AR8

C5

E3

H4

M5

AG2

AL5

AP5

AR7

U5

V2

T5

V3

R1

T8

R2

R6

R4

R5

AB5

P3

R3

AF7

P5

N1

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_CLK_DDR2 [19]

M_CLK_DDR#2 [19]

M_CKE2 [19]

M_CLK_DDR3 [19]

M_CLK_DDR#3 [19]

M_CKE3 [19]

M_CS2# [19]

M_CS3# [19]

M_ODT2 [19]

M_ODT3 [19]

M_B_DM[7..0] [19]

M_B_DQS#[7..0] [19]

M_B_DQS[7..0] [19]

M_B_A[15..0] [19]

CLARKUNF

CLARKUNF

CLARKUNF

A A

5

4

3

CLARKUNF

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU (DDR)

CPU (DDR)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

CPU (DDR)

Vostro Calpella

Vostro Calpella

Vostro Calpella

1

X01

X01

10 91Monday, January 18, 2010

10 91Monday, January 18, 2010

10 91Monday, January 18, 2010

X01

伟力电脑医院

技术支持:252670528

5

D D

CFG0

CFG3

C C

CFG4

B B

DIS

DY

DY

改改改改

DY

DY

12

12

12

R1101

R1101

3KR2F-GP

3KR2F-GP

5%

R1102

R1102

3KR2F-GP

3KR2F-GP

R1103

R1103

3KR2F-GP

3KR2F-GP

PCI-Express Configuration Select

1:Single PEG

CFG0

0:Bifurcation enabled

CFG3 - PCI-Express Static Lane Reversal

1 :Normal Operation

CFG3

0 :Lane Numbers Reversed

15 -> 0, 14 -> 1, ...

CFG4 - Display Port Presence

1:Disabled; No Physical Display Port

CFG4

attached to Embedded Display Port

0:Enabled; An external Display Port

device is connected to the Embedded

Display Port

Calpella Platform Design Guide

Revision 1.6

4.8.3.1 LVDS Switching

Switchable GFX, just like integrated GFX only, to enable LVDS it is required that the

OEM set the LDVS (L_DDC_DATA) strap to present (pulled up) and the eDP strap

(CFG[4]) to disabled (not pulled down).

4.8.3.2 eDP Switching

eDP for Switchable GFX can only be driven out of Port D of PCH. To configure Port D for

embedded DP it is required to set the DDPD_CTRLDATA strap high to 3.3V Core rail

through 2.2 kΩ ±5% resistor, LVDS (L_DDC_DATA) strap as no connect and the eDP

strap CFG[4] as no connect.

CFG7

TP1118

TP1118

TPAD14-GP

TPAD14-GP

1

A A

5

CFG7(Reserved) - Temporarily used for early

Clarksfield samples.

CFG7 Clarksfield (only for early samples pre-ES1) -

Connect to GND with 3.01K Ohm/5% resistor.

Note: Only temporary for early CFD sample

(rPGA/BGA) [For details please refer to the

WW33 MoW and sighting report].

For a common M/B design (for AUB and CFD),

the pull-down resistor shouble be used. Does

not impact AUB functionality.

4

Page 482,486

4

3

AP25

AL25

AL24

AL22

AJ33

AG9

M27

CFG0

CFG3

CFG4

CFG7

AM30

AM28

AP31

AL32

AL30

AM31

AN29

AM32

AK32

AK31

AK28

AJ28

AN30

AN32

AJ32

AJ29

AJ30

AK30

L28

J17

H17

G25

G17

E31

E30

H16

B19

A19

A20

B20

U9

T9

AC9

AB9

J29

J28

TP1116TP1116

TP1117TP1117

3

SA_DIMM_VREF#

1

SB_DIMM_VREF#

1

CPU1E

CPU1E

RSVD#AP25

RSVD#AL25

RSVD#AL24

RSVD#AL22

RSVD#AJ33

RSVD#AG9

RSVD#M27

RSVD#L28

SA_DIMM_VREF

SB_DIMM_VREF

RSVD#G25

RSVD#G17

RSVD#E31

RSVD#E30

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

RSVD_TP_86

RSVD#B19

RSVD#A19

RSVD#A20

RSVD#B20

RSVD#U9

RSVD#T9

RSVD#AC9

RSVD#AB9

RSVD#J29

RSVD#J28

CLARKUNF

CLARKUNF

2

CLARKSFIELD

CLARKSFIELD

RESERVED

RESERVED

2

5 OF 9

5 OF 9

RSVD#AJ13

RSVD#AJ12

RSVD#AH25

RSVD#AK26

RSVD#AL26

RSVD_NCTF_37

RSVD#AJ26

RSVD#AJ27

RSVD#AL28

RSVD#AL29

RSVD#AP30

RSVD#AP32

RSVD#AL27

RSVD#AT31

RSVD#AT32

RSVD#AP33

RSVD#AR33

RSVD#AR32

RSVD_TP#E15

RSVD_TP#F15

RSVD#D15

RSVD#C15

RSVD#AJ15

RSVD#AH15

SA_CK2

SA_CK#2

SA_CKE2

SA_CS#2

SA_ODT2

SA_CK3

SA_CK#3

SA_CKE3

SA_CS#3

SA_ODT3

SB_CK2

SB_CK#2

SB_CKE2

SB_CS#2

SB_ODT2

SB_CK3

SB_CK#3

SB_CKE3

SB_CS#3

SB_ODT3

1

AJ13

AJ12

AH25

AK26

AL26

AR2

AJ26

AJ27

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

AR32

E15

F15

A2

KEY

D15

C15

AJ15

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

VSS

VSS (AP34) can be left NC is

CRB implementation; EDS/DG

recommendation to GND.

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (RESERVED)

CPU (RESERVED)

CPU (RESERVED)

Taipei Hsien 221, Taiwan, R.O.C.

Vostro Calpella

Vostro Calpella

Vostro Calpella

11 91Monday, January 18, 2010

11 91Monday, January 18, 2010

11 91Monday, January 18, 2010

1

X01

X01

X01

伟力电脑医院

技术支持:252670528

5

4

CPU1F

CPU1F

3

6 OF 9

6 OF 9

2

1

+VCC_CORE

PROCESSOR CORE POWER

+VCC_CORE

D D

C C

B B

DY

DY

C1206

C1206

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C1212

C1212

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

DY

DY

C1225

C1225

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C1235

C1235

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

DY

DY

C1243

C1243

12

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

C1208

C1208

C1207

C1207

12

12

12

12

12

C1213

C1213

C1226

C1226

C1236

C1236

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

DY

DY

C1214

C1214

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C1227

C1227

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C1237

C1237

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C1220

C1220

C1210

C1209

C1209

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C1215

C1215

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C1228

C1228

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C1238

C1238

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

DY

DY

C1210

12

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

DY

DY

C1224

C1224

C1223

C1223

12

12

12

12

C1229

C1229

C1239

C1239

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C1231

C1231

C1230

C1230

12

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C1240

C1240

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

C1241

C1241

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

48A

C1232

C1232

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C1242

C1242

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

AG35

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y35

VCC

Y34

VCC

Y33

VCC

Y32

VCC

Y31

VCC

Y30

VCC

Y29

VCC

Y28

VCC

Y27

VCC

Y26

VCC

V35

VCC

V34

VCC

V33

VCC

V32

VCC

V31

VCC

V30

VCC

V29

VCC

V28

VCC

V27

VCC

V26

VCC

U35

VCC

U34

VCC

U33

VCC

U32

VCC

U31

VCC

U30

VCC

U29

VCC

U28

VCC

U27

VCC

U26

VCC

R35

VCC

R34

VCC

R33

VCC

R32

VCC

R31

VCC

R30

VCC

R29

VCC

R28

VCC

R27

VCC

R26

VCC

P35

VCC

P34

VCC

P33

VCC

P32

VCC

P31

VCC

P30

VCC

P29

VCC

P28

VCC

P27

VCC

P26

VCC

CLARKSFIELD

CLARKSFIELD

1.1V RAIL POWER

1.1V RAIL POWER

CPU CORE SUPPLY

CPU CORE SUPPLY

PROC_DPRSLPVR

CPU VIDS

CPU VIDS

POWER

POWER

VTT_SELECT

VSS_SENSE_VTT

SENSE LINES

SENSE LINES

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

VTT0

PSI#

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

VID

VID

VID

VID

VID

VID

VID

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

CPU_VID0

AK35

CPU_VID1

AK33

CPU_VID2

AK34

CPU_VID3

AL35

CPU_VID4

AL33

CPU_VID5

AM33

CPU_VID6

AM35

AM34

TP_H_VTTVID1

G15

AN35

VCC_SENSE

AJ34

VSS_SENSE

AJ35

B15

TP_VSS_SENSE_VTT

A15

C1216

C1216

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

1

12

C1201

C1201

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

DY

DY

PSI# [47]

CPU_VID[6..0] [47]

PM_DPRSLPVR [47]

TP1203

TP1203

IMVP_IMON [47]

VTT_SENSE [49]

1

TP1202

TP1202

TPAD14-GP

TPAD14-GP

C1233

C1233

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

TPAD14-GP

TPAD14-GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C1221

C1221

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

+1.05V_VTT

R1201

R1201

100R2F-L1-GP-U

100R2F-L1-GP-U

R1204

R1204

100R2F-L1-GP-U

100R2F-L1-GP-U

12

DY

DY

C1222

C1222

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

+1.05V_VTT

12

C1204

C1204

C1205

C1205

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

DY

DY

DY

DY

The decoupling capacitors, filter

recommendations and sense resistors on the

CPU/PCH Rails are specific to the CRB

Implementation. Customers need to follow the

recommendations in the Calpella Platform

Design Guide.

VCC_SENSE [47]

VSS_SENSE [47]

12

C1218

C1218

C1217

C1217

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

DY

DY

C1211

C1211

12

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

C1234

C1234

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

+VCC_CORE

12

12

C1203

C1203

12

+1.05V_VTT

12

A A

CLARKUNF

CLARKUNF

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

CPU (VCC_CORE)

CPU (VCC_CORE)

CPU (VCC_CORE)

Vostro Calpella

Vostro Calpella

Vostro Calpella

1

X01

X01

12 91Monday, January 18, 2010

12 91Monday, January 18, 2010

12 91Monday, January 18, 2010

X01

伟力电脑医院

技术支持:252670528

5

4

3

2

1

+1.5V_RUN

12

C1376

C1376

SC56P25V2JN-GP

+CPU_GFXCORE

D D

C C

22A

TC1303

TC1303

SE330U2VDM-L-GP

SE330U2VDM-L-GP

12

DY

DY

C1327

C1327

C1328

C1326

C1326

12

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

12

C1328

12

SC10U6D3V5MX-3GP

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC10U6D3V5MX-3GP

Please note that the VTT Rail

Values are

Arrandale VTT=1.05V;

Clarksfield VTT=1.1V

+1.05V_VTT

12

C1309

C1309

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

+1.05V_VTT

B B

18A

12

C1312

C1312

12

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C1314

C1314

C1315

C1315

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

AT21

AT19

AT18

AT16

AR21

AR19

AR18

AR16

AP21

AP19

AP18

AP16

AN21

AN19

AN18

AN16

AM21

AM19

AM18

AM16

AL21

AL19

AL18

AL16

AK21

AK19

AK18

AK16

AJ21

AJ19

AJ18

AJ16

AH21

AH19

AH18

AH16

J24

J23

H25

K26

J27

J26

J25

H27

G28

G27

G26

F26

E26

E25

CPU1G

CPU1G

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VAXG

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

SENSE

SENSE

GRAPHICS

GRAPHICS

CLARKSFIELD

CLARKSFIELD

FDI PEG & DMI

FDI PEG & DMI

POWER

POWER

LINES

LINES

GRAPHICS VIDs

GRAPHICS VIDs

7 OF 9

7 OF 9

GFX_VID

GFX_VID

GFX_VID

GFX_VID

GFX_VID

GFX_VID

GFX_VID

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VTT0

VTT0

VTT0

VTT0

VTT1

VTT1

VTT1

VTT1

VTT1

VTT1

VCCPLL

VCCPLL

VCCPLL

AR22

AT22

AM22

AP22

AN22

AP23

AM23

AP24

AN24

AR25

TP_GFX_DPRSLPVR

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

VAXG_SENSE

VSSAXG_SENSE

GFX_VR_EN

GFX_DPRSLPVR

GFX_IMON

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

1.1V1.8V

1.1V1.8V

12

C1301

C1301

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

1

12

C1310

C1310

C1316

C1316

DY

DY

SC56P25V2JN-GP

+1.5V_SUS

VCC_AXG_SENSE [53]

VSS_AXG_SENSE [53]

GFX_VID0 [53]

GFX_VID1 [53]

GFX_VID2 [53]

GFX_VID3 [53]

GFX_VID4 [53]

GFX_VID5 [53]

GFX_VID6 [53]

GFX_VR_EN [53]

TP1303TPAD14-GPTP1303TPAD14-GP

GFX_IMON [53]

12

12

C1303

C1303

C1302

C1302

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

12

12

C1311

C1311

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

DY

DY

12

DY

DY

12

12

C1318

C1318

C1319

C1319

SC1U25V5KX-1GP

SC1U25V5KX-1GP

SC1U25V5KX-1GP

SC1U25V5KX-1GP

DY

DY

C1304

C1304

12

C1320

C1320

+1.5V_RUN

12

DY

DY

+1.5V_SUS

C1377

C1377

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

+1.5V_RUN

12

DY

DY

+1.5V_SUS

C1378

C1378

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

+1.5V_RUN

12

DY

DY

+1.5V_SUS

C1379

C1379

SCD1U10V2KX-4GP

SCD1U10V2KX-4GP

425302_425302_Calpella_S3PowerReduction_WhitePape

Revision 0.7

3A

12

12

C1305

C1305

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

SC1U6D3V2KX-GP

+1.05V_VTT

+1.05V_VTT

1.35A

12

C1321

C1321

SC4D7U6D3V5KX-3GP

SC4D7U6D3V5KX-3GP

SC2D2U10V3KX-1GP

SC2D2U10V3KX-1GP

+1.5V_RUN

12

C1306

C1306

C1307

C1307

SC22U6D3V5MX-2GP

SC22U6D3V5MX-2GP

SC10U6D3V5KX-1GP

SC10U6D3V5KX-1GP

12

C1322

C1322

SC10U6D3V5MX-3GP

SC10U6D3V5MX-3GP

12

TC1301

TC1301

SE330U2VDM-L-GP

SE330U2VDM-L-GP

+1.8V_RUN

CLARKUNF

CLARKUNF

A A

5

4

3

2

<Core Design>

<Core Design>

<Core Design>

Wistron Corporation

Wistron Corporation

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Taipei Hsien 221, Taiwan, R.O.C.

Title

Title

Title

CPU (VCC_GFXCORE)

CPU (VCC_GFXCORE)

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

Date: Sheet of

Date: Sheet of

Date: Sheet of

CPU (VCC_GFXCORE)

Vostro Calpella

Vostro Calpella

Vostro Calpella

13 91Monday, January 18, 2010

13 91Monday, January 18, 2010

13 91Monday, January 18, 2010

1

X01

X01

X01

伟力电脑医院

技术支持:252670528

5

CPU1H

CPU1H

AT20

VSS

AT17

VSS

AR31

VSS

AR28

VSS

AR26

VSS

AR24

VSS

D D

C C

B B

AR23

AR20

AR17

AR15

AR12

AR9

AR6

AR3

AP20

AP17

AP13

AP10

AP7

AP4

AP2

AN34

AN31

AN23

AN20

AN17

AM29

AM27

AM25

AM20

AM17

AM14

AM11

AM8

AM5

AM2

AL34

AL31

AL23

AL20

AL17

AL12

AL9

AL6

AL3

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AJ8

AJ5

AJ2

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AH9

AH6

AH3

AG10

AF8

AF4

AF2

AE35

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS