5

Vinafix.com

4

3

2

1

PCB Number: 14003-A00

PAGE

01

02

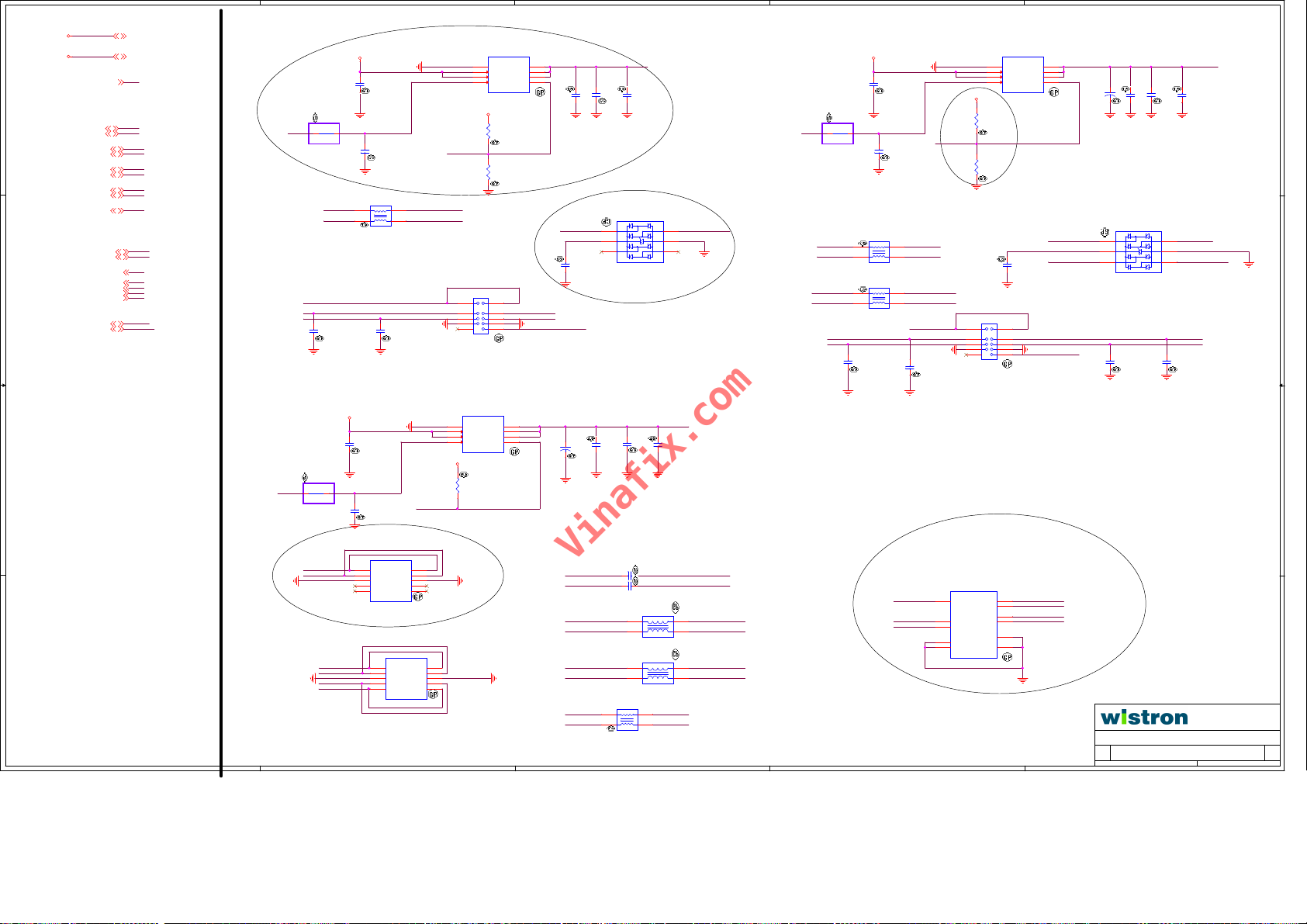

03 Power Delivery

D D

04

05

06

07

08

09

10

11

12

13

14 CPU_VCC_CORE(NEW)

15

16

17

18

19

C C

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

B B

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

A A

52

53

54

55

56

57

58

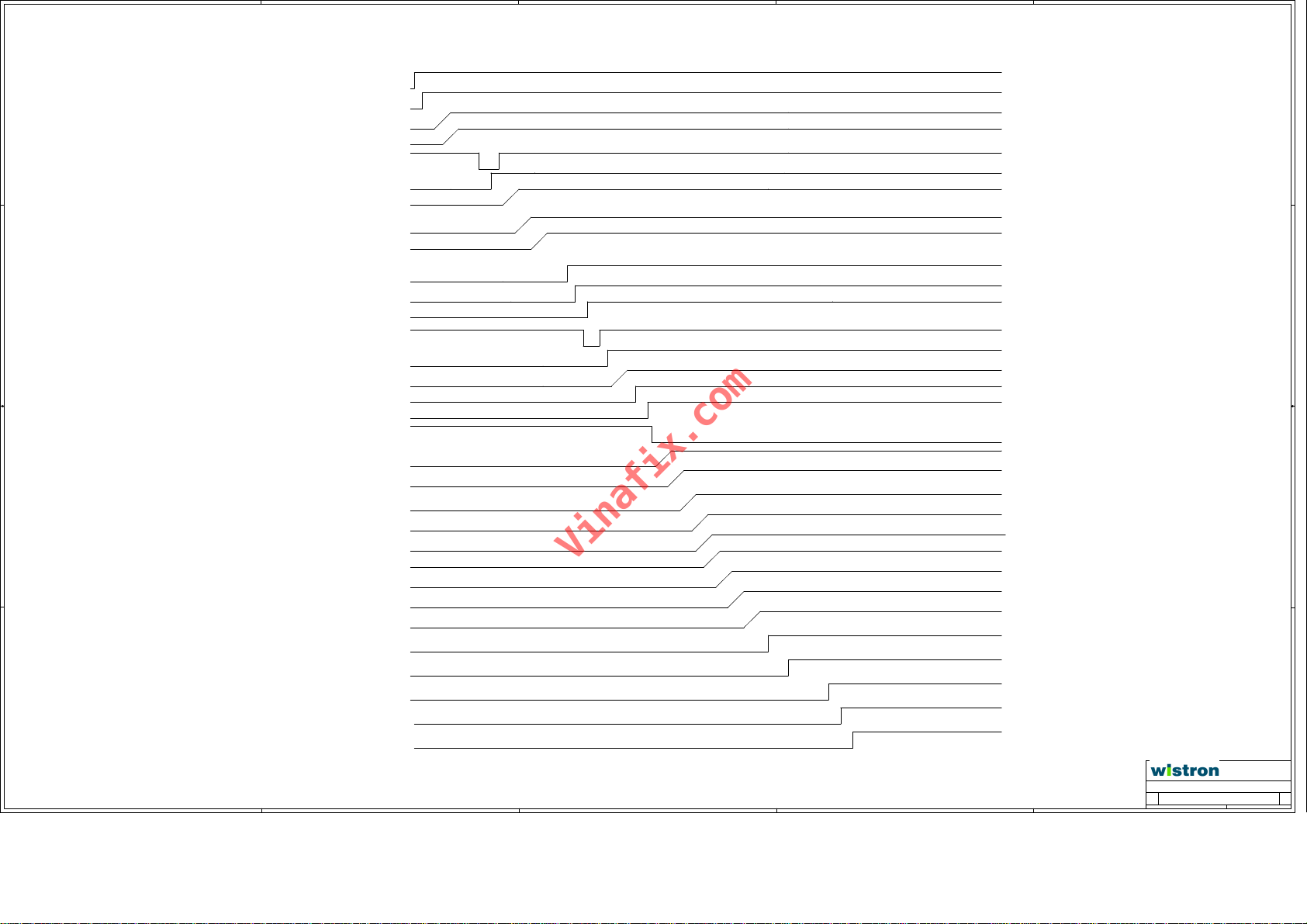

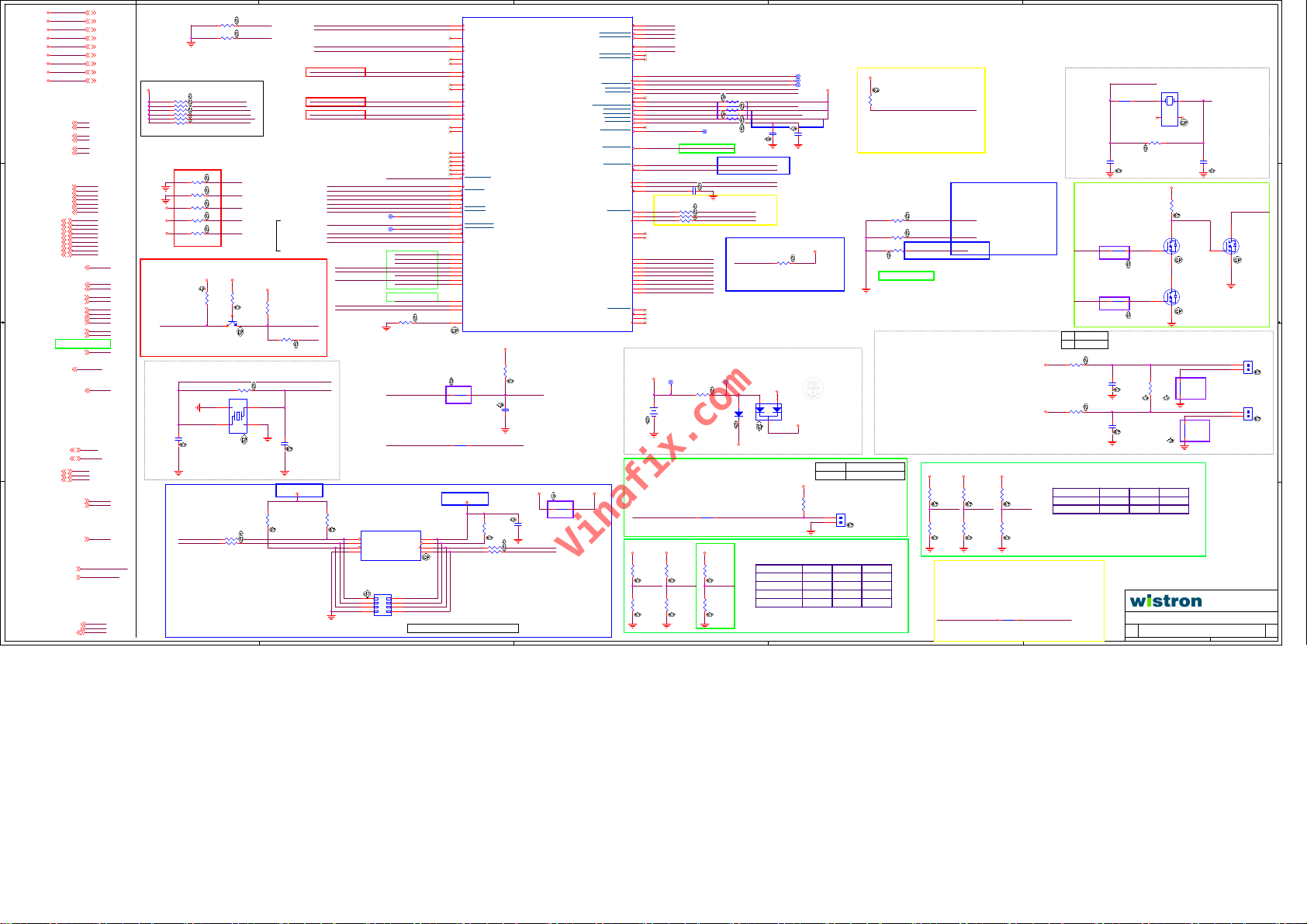

TITLE

Cover Page

Block Diagram

Power Good & Reset Diagram

Clock Diagram

Power Sequence

GPIO TABLE

CPU_DDRIIIA(NEW)

CPU_DDRIIIB(NEW)

CPU_SATA/SD/PCIE/AZ(NEW)

CPU_DISPLAY(NEW)

CPU_CLK/GPIO/RTC/MISC(NEW)

CPU_USB/LPC/SMBus(NEW)

CPU_POWER(NEW)

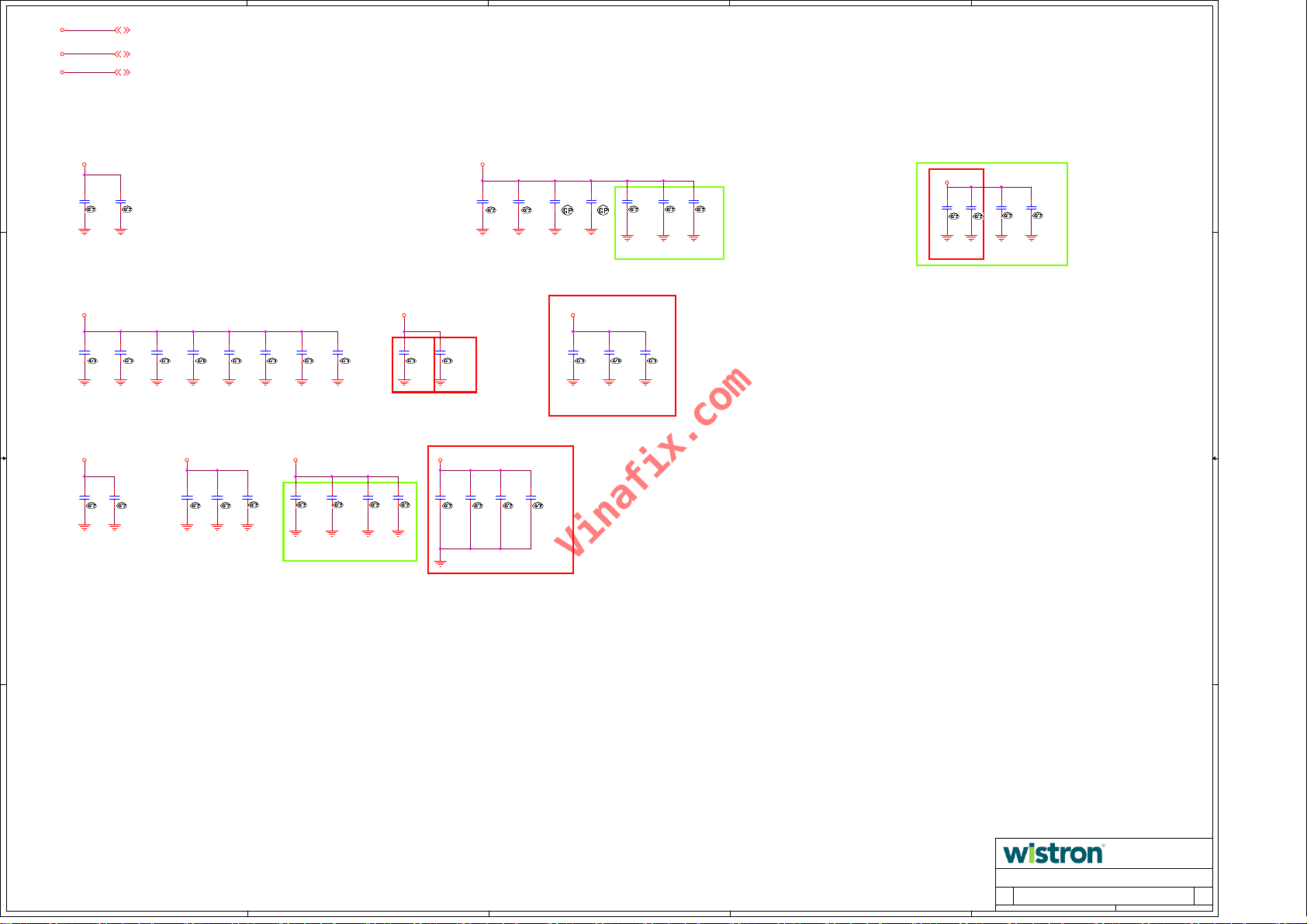

CPU_POWER CAP1(NEW)

CPU_POWER CAP2(NEW)

CPU_ (VSS)(NEW)

CPU_(STRAP)(NEW)

LEVEL SHIFT(NEW)

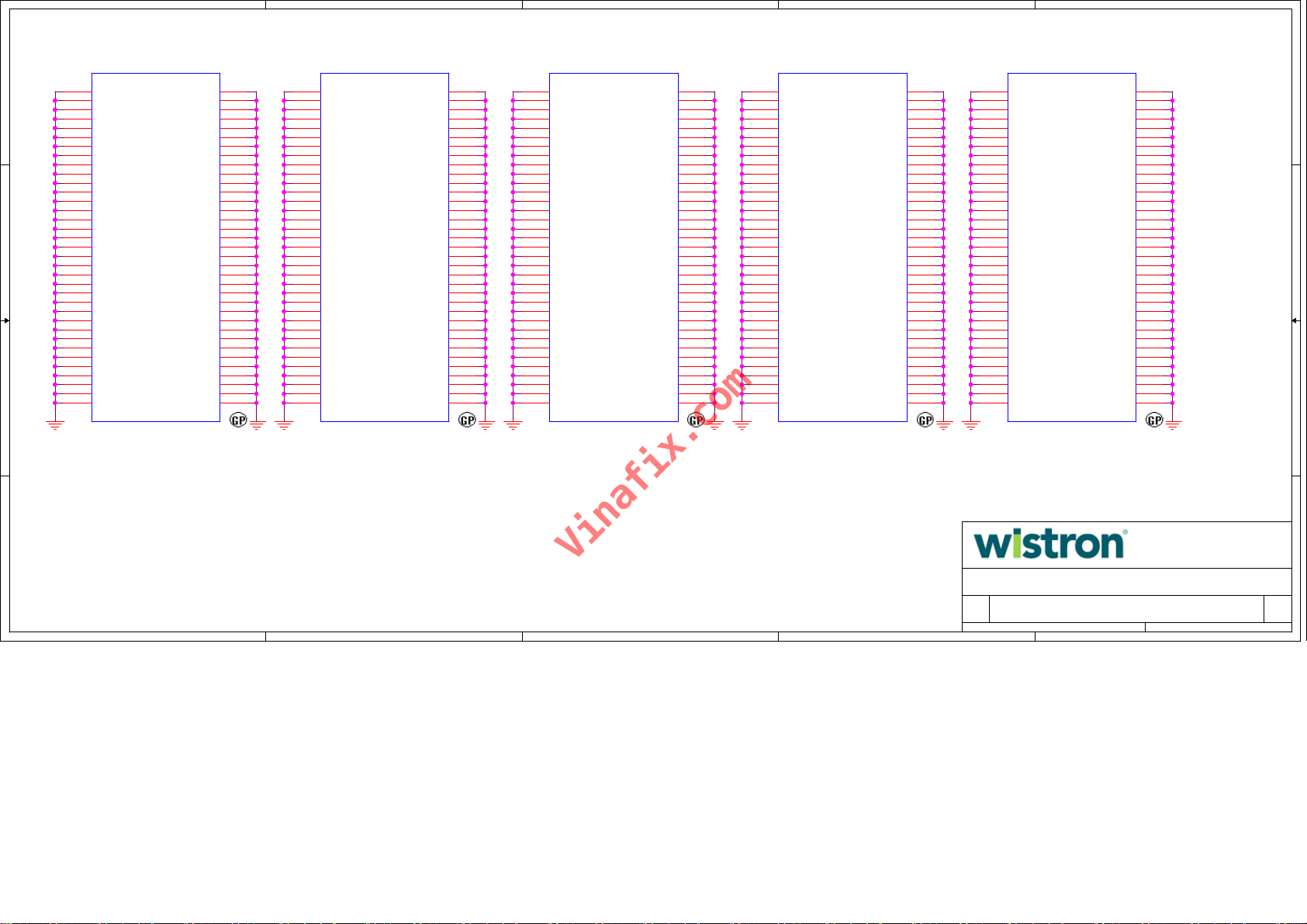

DIMM_A(New)

TBD

DEBUG/XDP(NEW)

VGA(New)

TBD

TBD

USB HUB(NEW)

USB/USB30(New)

TBD

LAN_RTL8151GD

AUDIO ALC3600

TBD

TBD

WIRELESS

SATA/LED/BTN

FAN CIRCUITS/HOLE

TBD

SIO_ITE8732(NEW)

DC IN

PWR_3P3V / 5P0V

PWR_12V

1D35V_0D675_TPS51363(NEW)

1P5_S0&1P05_S0&1P8V_S0(NEW)

LDO_CPU 1V_S0&CPU 1V_S5

CPU CORE&VNN(NEW)

Run PWR/USB PWR(NEW)

DSW_POWER_CTL

PWROK(NEW)

GPU(1/5):PCI Express(NEW)

GPU(2/5): IFB(IO)(NEW)

GPU(3/5):MEMORY FBA(NEW)

GPU(4/5):GPIO/STRAP(NEW)

GPU(5/5):PWR/GND(NEW)

GPU_DDR3 128MX16(NEW)

GPU_POWER Sequence

GPU_CTF/PPLAY/LDO/MVDD

DC to DC_1D8V_RT8237(NEW)

GPU_VDDC_NCP81172

5

4

Quantity

BOM Configuration

(R):Unmount

(G):GPU

(U):UMA

(D):Debug used

(C):HDMI Level Shift

(H):HDMI Driver IC

PCB BOARD SIZE

6 Layers

185mm X 244mm

SA BUILD

INTEL Bay Trail Platform

LAN : Gb LAN RTL8151GD

AUDIO: ALC3600

SIO_EC:ITE8732

PCB1

PCB

(348.01D02.00SA)

PCB

(348.01D03.00SA)

PCB3

PCB

(348.01D04.00SA)

3

LBL1

LABEL

(45.3E702.001)

LANID :

F80F4105EB9A

LBL2

LABEL

(40.3EQ13.011)PCB2

LANID :

F80F4105EB9A

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Cover Page

Cover Page

Cover Page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_BayTrail_DT

Custom

Rosa_BayTrail_DT

Custom

Rosa_BayTrail_DT

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

1 58Tuesday, April 15, 2014

1 58Tuesday, April 15, 2014

1 58Tuesday, April 15, 2014

1

A00

A00

A00

5

Vinafix.com

4

3

2

1

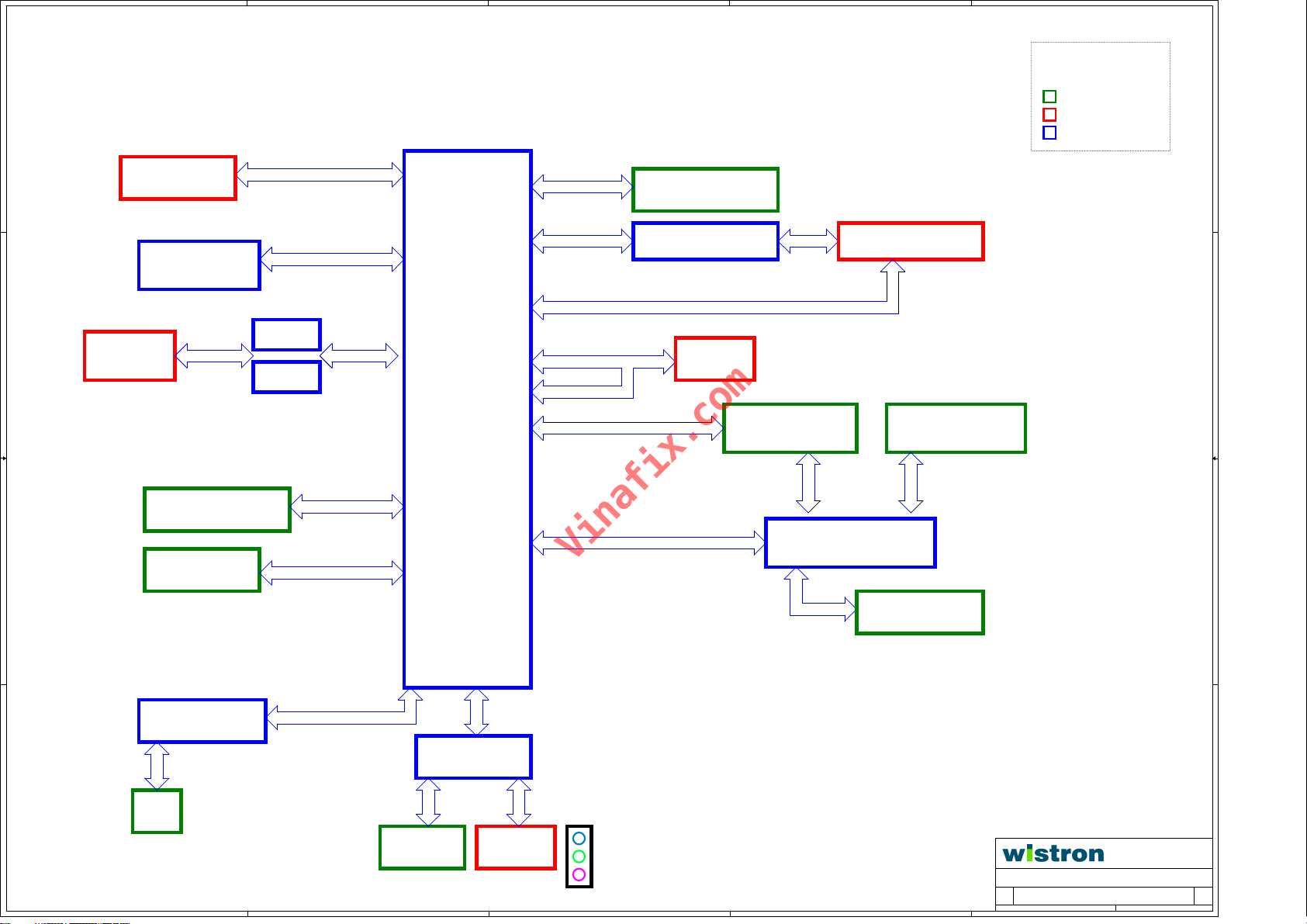

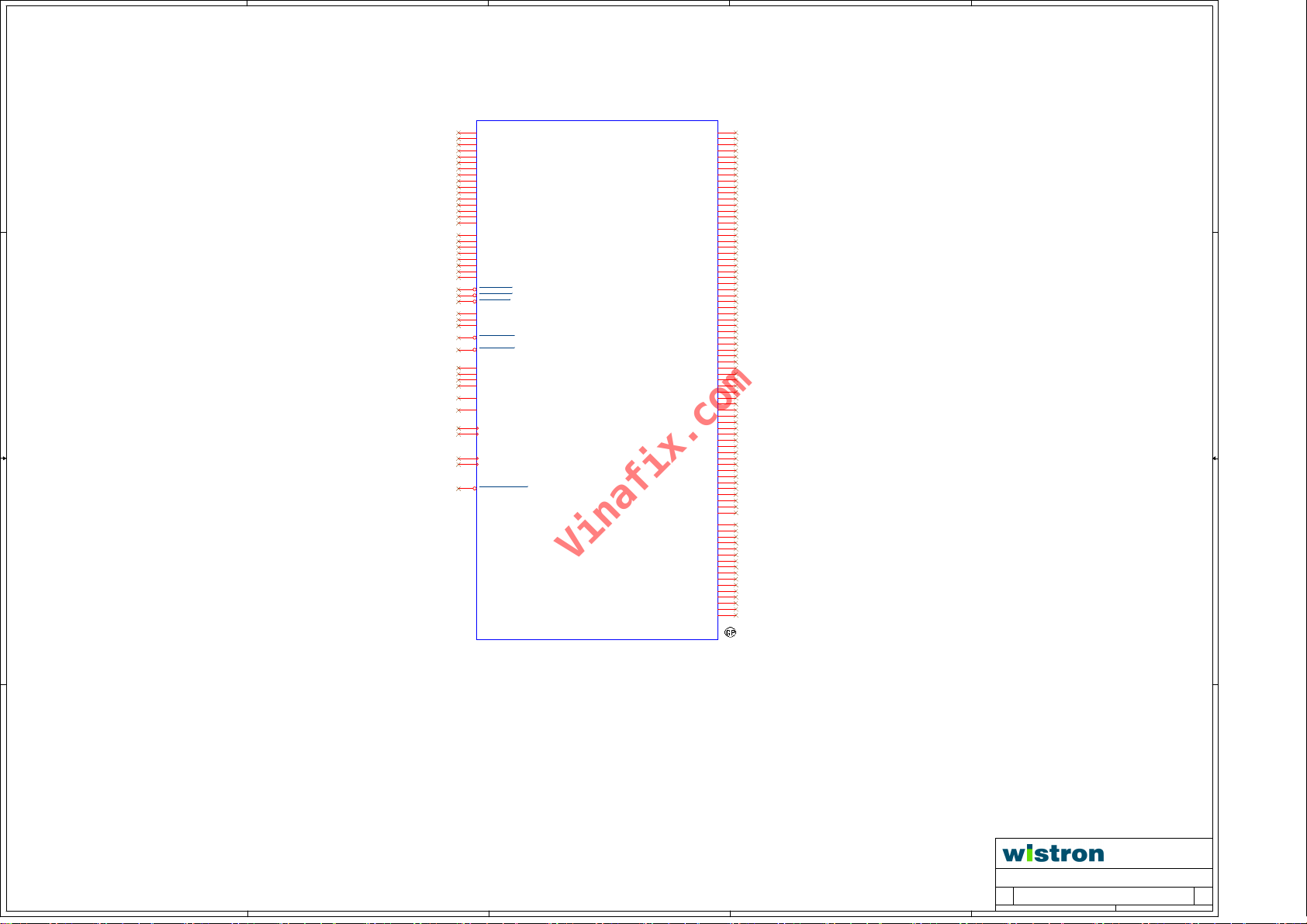

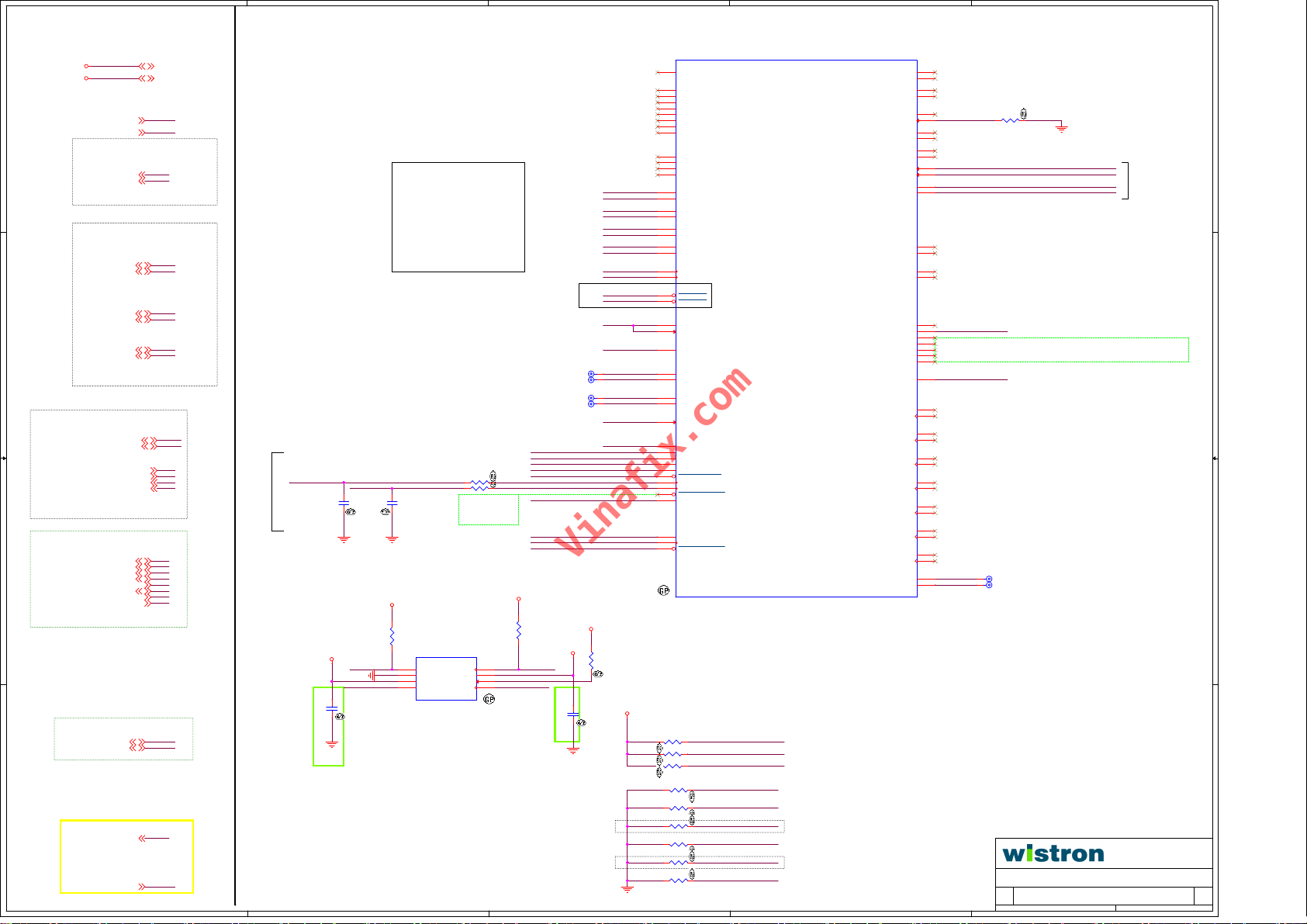

Project Name: Saffron

Project Code: 3PD01D010001

PCB Version: A00

PCB Number : 14003-1

D D

PCB BOARD SIZE

180mm x 244mm

6 Layer

Internal Slot/Header

Front/Rear IO

Chipset

VGA PORT

GPU (N15V-GM)

RGB

PCIEx2

Intel CPU

Bay Trail-D

1.35V

DDR3L

PCIEx1

CHA

DDR3L-SODIMM

LAN RTL8151GD

RJ45+USB CONN

(Rear)

BGA1170

TDP: 10W

Package

C C

HDMI

HDMI

Level Shift

HDMI

25*27*1.4

USB2.0 x2

Port1,2

USB3.0

USB3.0

(Rear)

PS8407

USB2.0

BOM Option

HDD & ODD PORT

B B

8MB SPI ROM

SATA2.0

SPI

ETHERNET (10/100/1000Mb)

USB 3.0/2.0 ports (4)

High Definition Audio

SATA ports (2)

PCIe ports (4)

LPC I/F

Port0

PCIEx1

Port3

USB2.0

WLAN(Mini Card)

BT

U2x1

USB HUB GL852G

U2x2

SD Card USB2.0x1

Pin Header

U2x1

USB2.0x2

(Front)

Pin Header

SIO ITE8732

LPC

Azalia

ALC3600

A A

FAN

<Variant Name>

<Variant Name>

<Variant Name>

Pin Header Line out

Title

Title

Title

Block Diagram

Block Diagram

(Front) (Rear)

5

4

3

2

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_BayTrail_DT

C

Rosa_BayTrail_DT

C

Rosa_BayTrail_DT

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

2 58Tuesday, April 15, 2014

2 58Tuesday, April 15, 2014

2 58Tuesday, April 15, 2014

A00

A00

A00

5

Vinafix.com

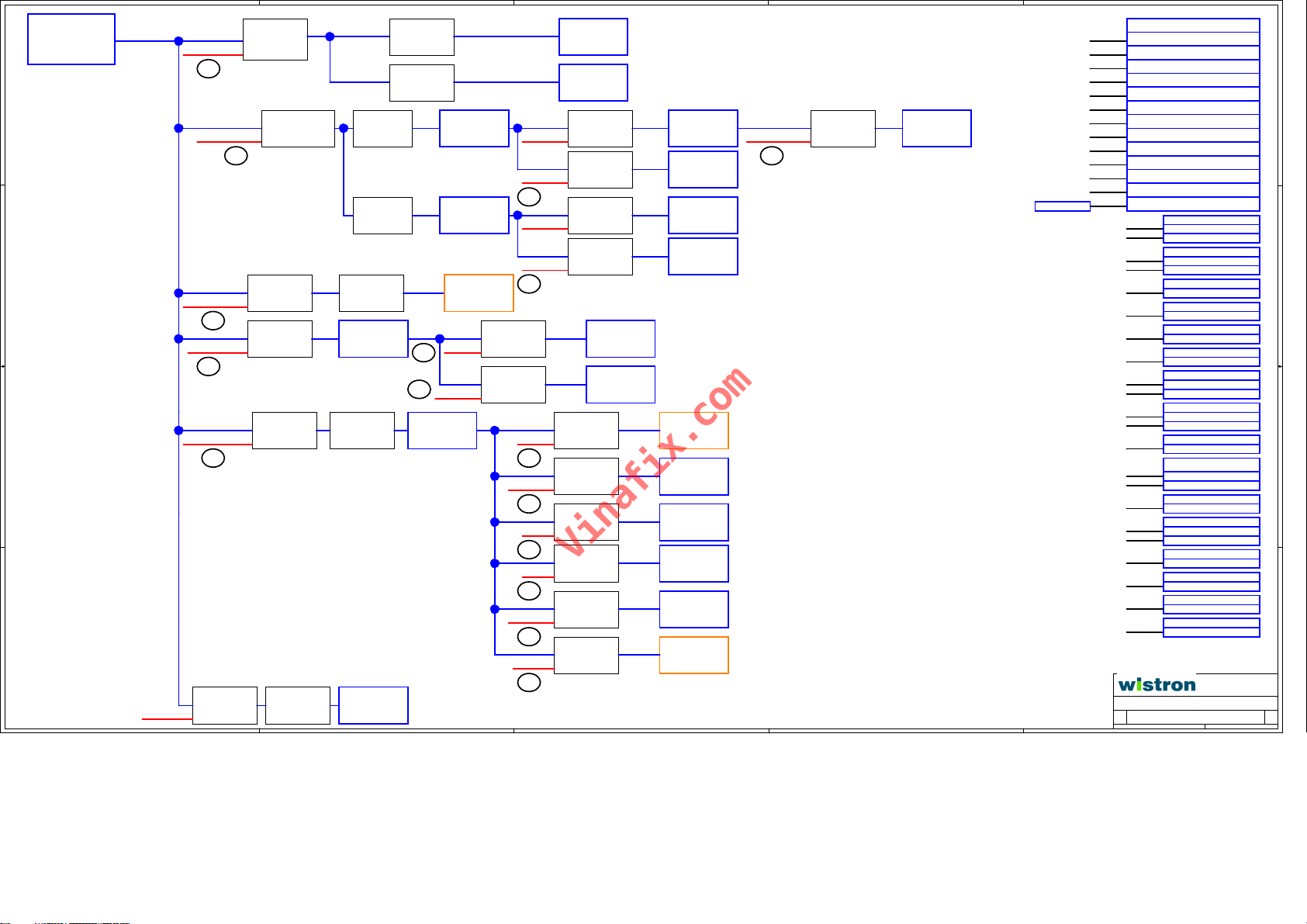

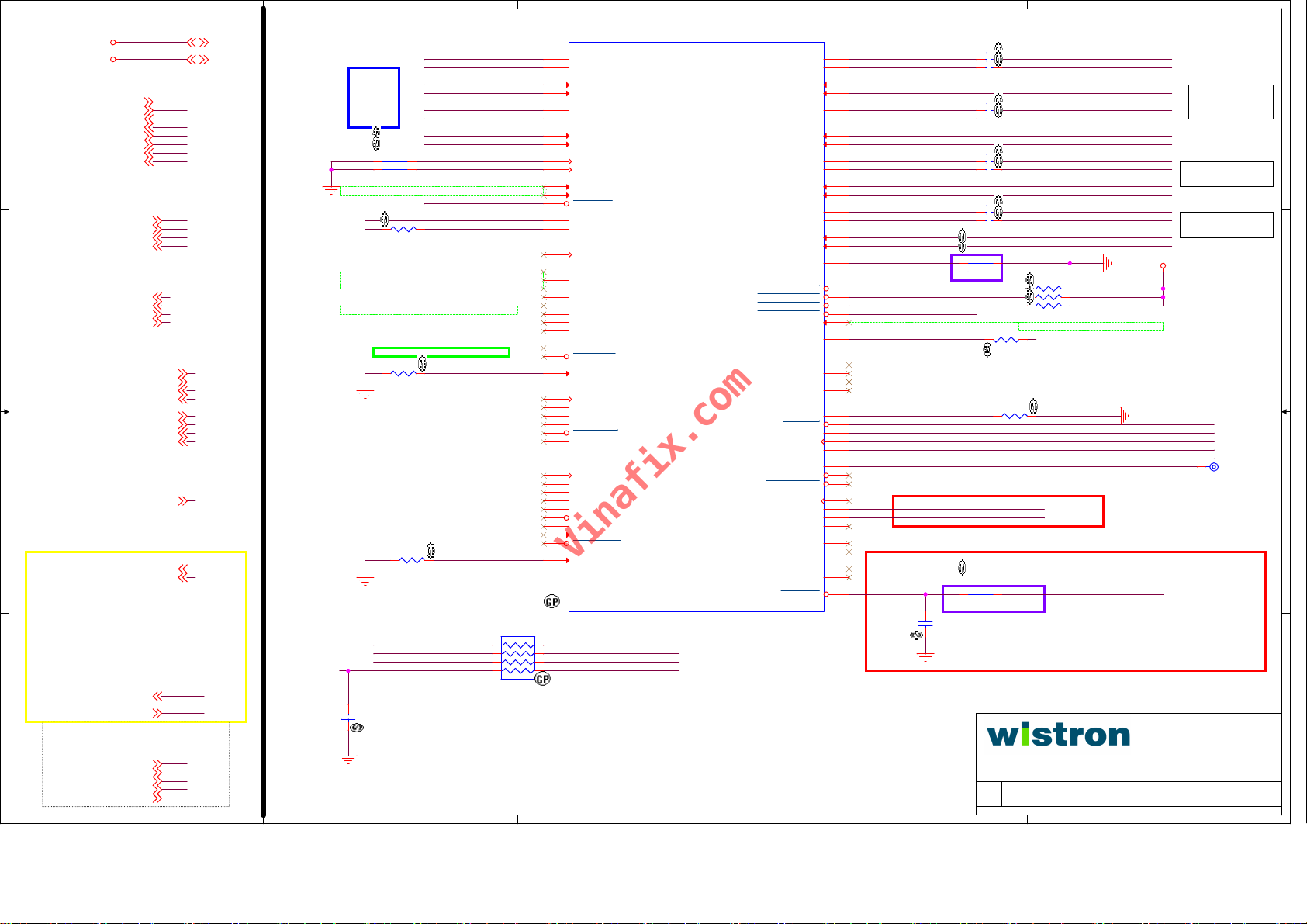

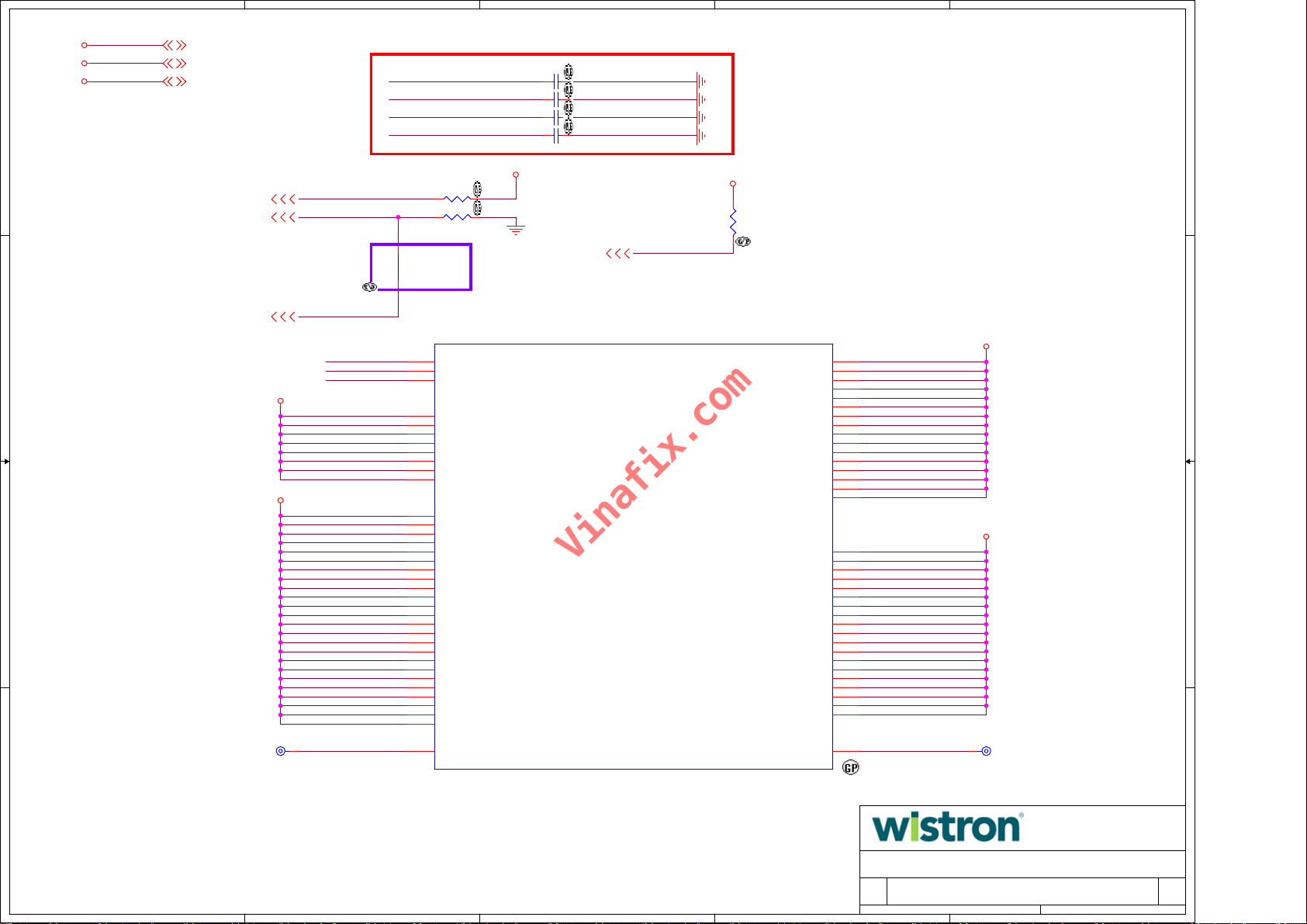

AC/DC ADAPTER

POWER: ADP-90WB

INPUT: 100~240V(1.5A)

OUTPUT: 19.5V(4.62A)

ADP_19V

SLP_S3_N

5

D D

PWR_3_5V_DCBATOUT

C C

VCC3

ISL95833

PWM

EN

Page 45

RT8243B

PWM

EN

Page 40 Page 44

1 2

NCP81172

PWM

EN

12

TPS51363

SLP_S4_N

4

CPU 1V_S5_RUNPWROK

B B

A A

NCP1589A

SIO_PSON_N

5

SWITCH

EN

CONVERTOR

EN

Page 42

RT8237C

PWM

EN

3

Page 57

SIR172DP*1

SIRA12DP*1

SI4214DDY*1

FDS8884*1

FDS6690*1

FDS8884*1

FDS6690*1

SIRA14DP*2

SIRA10DP*2

DDR_VDDQ

Imax = 6A

VCC12

Imax = 0.3A

4

SIR172ADP*1

SIRA12DP*1

SIR172ADP*1

SIRA12DP*1

12

8

1D8V_S5

Imax = 9A

4

V_3P3_A

Imax = 2.5A

V_5P0_A

Imax = 6.5A

+V_VGA_CORE

0.6V - 1.2V

TDC 26A

VCC

1D05V_RUNPWROK

LDO

APL5337

Switch

AO4468L

DGPU_PWROK

1.5V_S0_PWRGD

VNN_GFX_PWRGD

+1.5V_GPU_PG

SIO_EUP_EN#

1D8V_S0

11

SIO_EUP_EN#

1D8V_S0

11

13

10

1D35V_S0

9

1D0V_S0

7

6

14

Page 42

Page 42

VCORE_VCC

1.00V

TDC 12A

VGFX_VNN

1.00V

TDC 14A

Switch

AO4468L

Switch

AO6402A

Switch

AO6402A

Switch

AO4468L

Imax = 0.445A

LDO

APL5912

Switch

AO4468L

LDO

APL5930

LDO

APL5930

LDO

APL5912

LDO

APL5912

VDD_VTT

Imax = 1A

1D35V_S0

Page 56

Page 43

Page 43

Page 43

Page 44

Page 56

3

Page 46

Page 46

3

SB3V

Imax = 1.5A

VCC3

Imax = 0.71A

SB5V

VCC

Imax = 6.23A

+V_1P5_VGA

Imax = 2.8A

1D8V_S0

Imax = 0.018A

1D5V_S0

Imax = 0.39A

1D05V_S0

Imax = 1.1A

1D0V_S0

Imax = 3A

+V_1P05_VGA

Imax = 1.1A

SB3V

LDO

APL5930

EN

2

1D0V_S5

Imax = 0.35A

2

V_3P0_BAT_VREG

1

VCORE

VGFX

VDDQ

1D0V_S5

1D8V_S5

V_3P3_A

1D0V_S0

1D05V_S0

1P35V_S0

1D8V_S0

VCC3

VDD_VTT

19V_AMP_PVCC

V_3P3_PCIVAUX

<Variant Name>

<Variant Name>

<Variant Name>

T

T

Title

itle

itle

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Bay Trail SoC

VCC

0.40 - 1.14V ; 12A TDC

VNN

0.50 - 1.05V ; 14A TDC

VDDQ 1.35V ; 1.25A

V1P0A 1.00V ; 0.35A

V1P8A 1.80V ; 0.065A

V3P3A 3.30V ; 0.055A

V1P0S

V1P05S 1.05V ; 1.1A

V1P35S 1.35V ; 0.445A

V1P8S

V3P3S

VDDQ_VTT 0.675V ; 1A

VRTC

DDR_VDDQ

VDD_VTT

VCC

V_3P3_A

1D8V_SPI

VCC12

VCC5_USB

VCC5_USB

V_3P3_LAN

V_1P05_LAN

3V_VA

V_5_CODEC

DVCC33_2136

SWR_V12

VCC3

V_1P5_PCIE

VCC3_CAM

HUB_VCC

V_5HDD

V_5HDD

Power Delivery

Power Delivery

Power Delivery

Rosa_BayTrail_DT

Rosa_BayTrail_DT

Rosa_BayTrail_DT

1

1.00V ; 3A

1.80V ; 0.018A

3.30V ; 0.03A

3V ; 100uA (Avg. 6uA)

SO-DIMM

V_MEM_S

V_MEM_VTT

SIO- IT8732

3.3V; 20mA

3.3V; 9.37mA

BIOS ROM

1.8V; 67mA

CPU FAN

12V; 300mA

USB2.0 VBUS

5V; 500mA

USB3.0 VBUS

5V; 900mA

LAN- RTL8151GD

3.3V; 70mA

(Internal Switch)

1.05V;300mA

HD CODEC ALC3661-CG

3.3V; 50mA

5V; 50mA

AMP TPA3131

19V; 270mA

DPtoLVDS_ RTD2136R

3.3V; 180mA

1.2V; 210mA (Internal Switch)

Card Reader RTS5170-GR

3.3V; 120mA

PCI-E Mini Card

3.3V; 1.1A

1.5V; 0.38A

WEBCAM

3.3V; 240mA

USB HUB - GL850-G

5V; 52.4mA

HDD

5V; 1.1A

Slim ODD

5V; 1.5A

TDP = 10W

1.35V ; 3.75A

0.675V ; 1A

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

3 58Tuesday, April 15, 2014

3 58Tuesday, April 15, 2014

3 58Tuesday, April 15, 2014

X3

A00

A00

A00

5

Vinafix.com

4

3

2

1

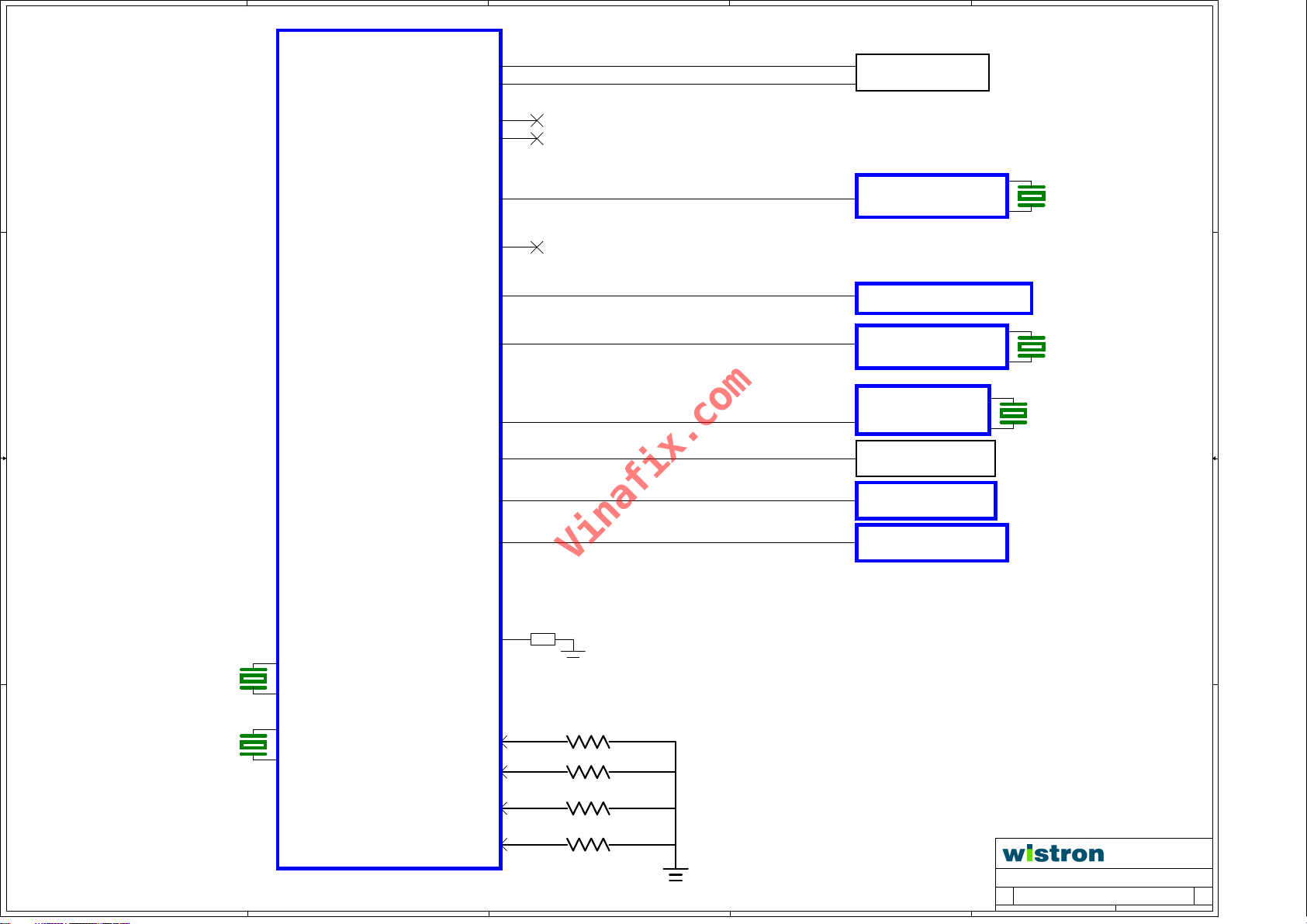

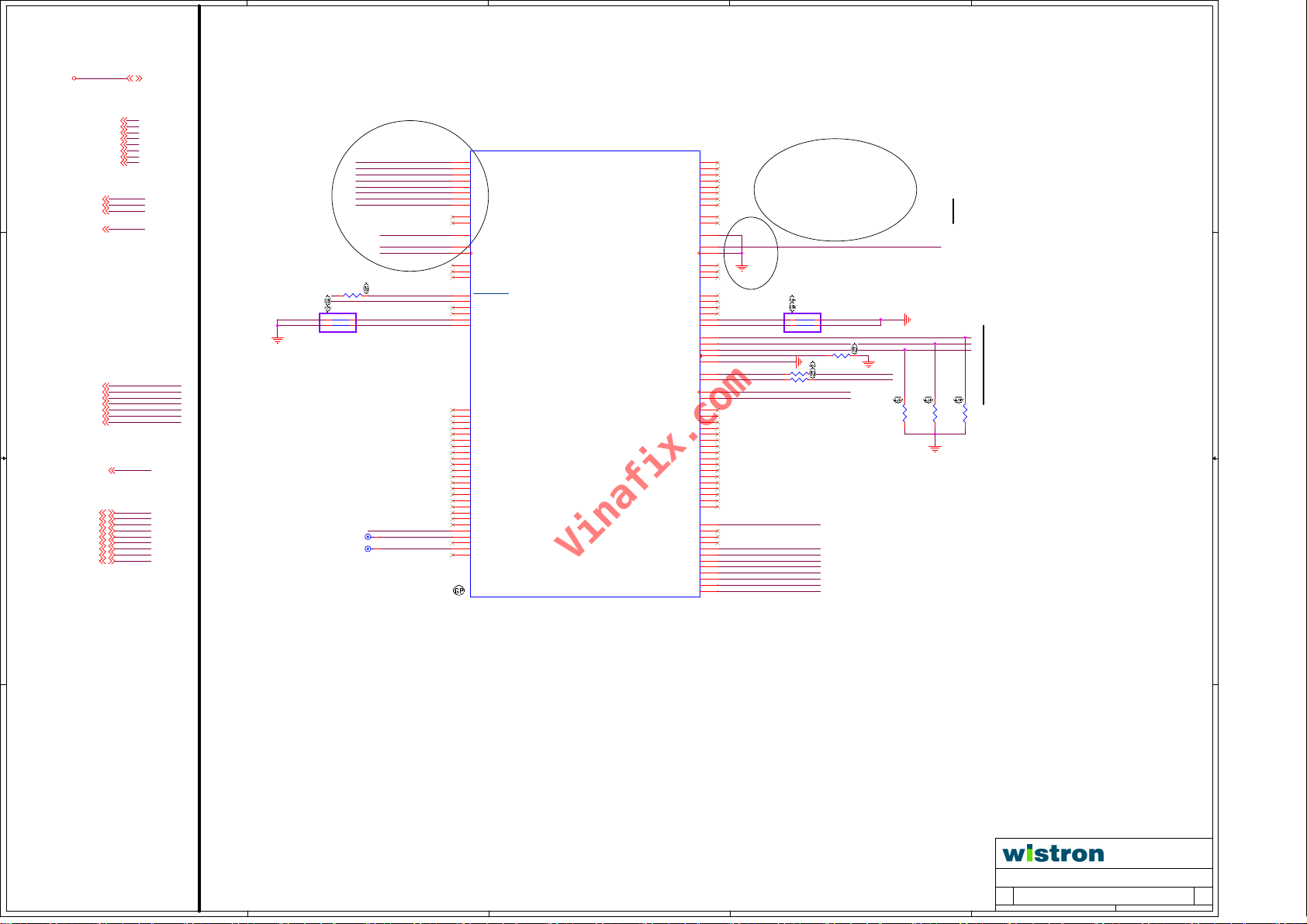

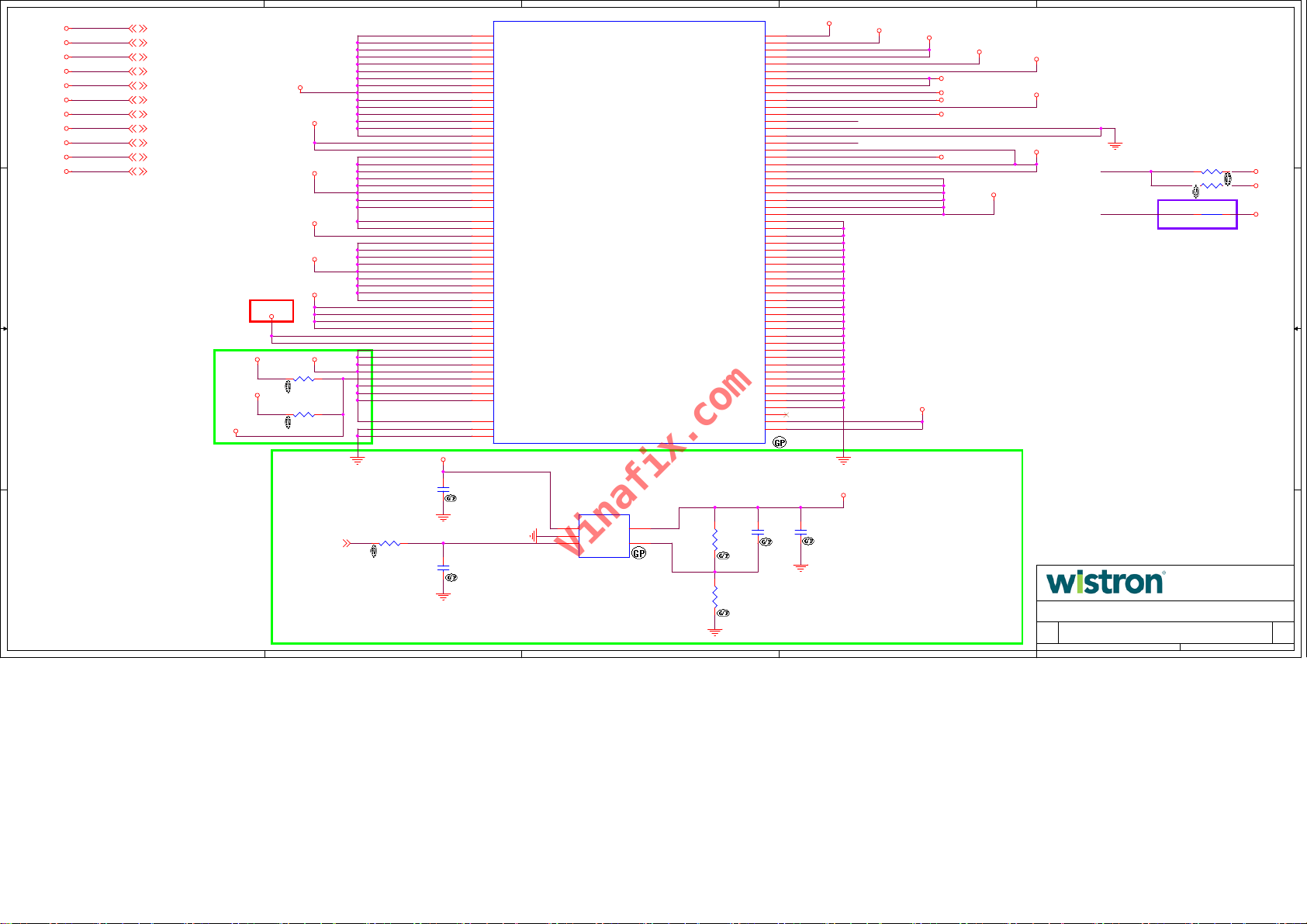

Bay-Trail Soc

D D

Battery

1

RTC_VCC

RTC_RST#

PMC_RSMRST#

PMC_PWRBTN#

Codec

RESET#

11

DDR3_DRAM_PWROK

19

SYS_PWRGD

C C

2

DCBATOUT

B B

11b

VNN_GFX_PWRGD

12

1D0V_S0

21b

AZ_RST_N_M

V_5P0_A

V_3P3_A

1D0V_S0

1D05V_S0

HDA_RST#

DRAM_VDD_S4_PWROK

PMC_CORE_PWROK

4

SIO_EUP_EN#

13

1D05V_RUNPWROK

14

1D35V_S0

PMC_SLP_S4#

PMC_SLP_S3#

PMC_PLTRST#

SB3V

8

SLP_S4_N

9

SLP_S3_N

20

PLTRST_N

SB3V

1D0V_S5

1D35V_S0

1D5V_S0

5a

5b

1D0V_S5SB5V

1D8V_S5

15

1.5V_S0_PWRGD

16 VCC3

1D8V_S0

8a

SLP_S4_N

10

SIO_PSON_N

1D8V_S0

VCC

6

RSMRST_N

7

SW_ON_N_SIO

10 21a

SIO_PSON_N

DDR_VDDQ

12V_S0

SIO - ITE8732

RSMRST#

PWRON#

SUSC#

SUSB#

LRESET#

PSON#

9a

SLP_S3_N

17a

VCC

VNN_GFX

VCORE

PANSWH#

5VSB_CTRL#

SYS_3VSB

ATXPG

PCIRST1#

PCIRST3#

PWROK1

DDR_0D675V

VCORE_PWRGD

SLP_S3_N

PWRGD_3V

4

SIO_EUP_EN#

21a

PCIRST1#

PCIRST3#

18

PWRGD_3V

11a

9b

18

AND

SYS_PWRGD

3

PWRBTN_N

5

SB3V

17

VCC3

19

Power Button

GPU

Giga LAN

WirelessCard

17b

A A

+V_3P3_VGA DGPU_PWROK

VGA_CORE

19a

+V_1P5_VGA

+V_1P05_VGA

<Variant Name>

<Variant Name>

5

<Variant Name>

T

T

Title

itle

itle

Power Good & Reset Diagram

Power Good & Reset Diagram

Power Good & Reset Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_BayT rail_DT

D

Rosa_BayT rail_DT

D

Rosa_BayT rail_DT

D

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin T ai Wu Rd

21F, 88, Hsin T ai Wu Rd

21F, 88, Hsin T ai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

4 58Tuesday, April 15, 2014

4 58Tuesday, April 15, 2014

4 58Tuesday, April 15, 2014

A00

A00

A00

5

Vinafix.com

4

3

2

1

Bay-Trail Soc

D D

C C

DRAM0_CKP_0(M50)

DRAM0_CKN_0(M48)

DRAM0_CKP_2(P50)

DRAM0_CKN_2(P48)

DRAM1_CKP_0(AV50)

DRAM1_CKN_0(AV48)

DRAM1_CKP_2(AT50)

DRAM1_CKN_2(AT48)

PCIE_CLKN_0(AF6)

PCIE_CLKP_1(AF7)

PCIE_CLKN_1(AF9)

PCIE_CLKP_2(AK6)

PCIE_CLKN_2(AK4)

PCIE_CLKP_3(AM6)

PCIE_CLKN_3(AM4)

ILB_LPC_CLK_0(BG15)

ILB_LPC_CLK_0(BH14)

PCU_SPI_CLK(C22)

CK_M_DDR0_A_DP/CK_M_DDR0_A_DN

CK_M_DDR1_A_DP/CK_M_DDR1_A_DN

100MHzPCIE_CLKP_0(AF4)

100MHz

100MHz

25MHz

25MHz

24MHz/48MHz/100MHz

DIMM1

GPU (N15S-GM)

Mini PCIE WLAN+BT

LAN RTL8151GD

SIO IT8732F

PCICLK(47)

LPC Debug Port

SPI ROM

CLKIN(37)

27MHz

25MHz

48MHz

Rs

24MHz

AUDIO ALC3661

HDA_CLK(BJ21)

B B

ICLK_ICOMP(AD14)

ICLK_RCOMP(AD13)

ICLK_OSCIN

25MHz

32.768KHz

A A

5

ICLK_OSCOUT

ILB_RTC_X1

ILB_RTC_X2

ICLK_DDI_TERMP(AM3)

ICLK_DDI_TERMN(AM2)

ICLK_SATA_TERMP(BB10)

ICLK_SATA_TERMN(BC10)

ICLK_USB_TERMP(D10)

ICLK_USB_TERMN(F10)

ICLK_PCIE_TERMP(BB7)

ICLK_PCIE_TERMN(BB5)

4

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Clock Diagram

Clock Diagram

Clock Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_BayTrail_DT

C

Rosa_BayTrail_DT

C

Rosa_BayTrail_DT

C

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

5 58Tuesday, April 15, 2014

5 58Tuesday, April 15, 2014

5 58Tuesday, April 15, 2014

A00

A00

A00

5

Vinafix.com

4

3

2

1

Source Destination Signal

RTC Battery CPU/SIO

D D

RTC Battery CPU/SIO

Adaptor

VRs CPU/SIO

Button SIO

SIO VRs SIO_EUP_EN#

RTC_VCC

RTC_TEST#

RTC_RST#

DCBATOUT

MB

V_3P3_A

PWRBTN_N

SB3V/SB5VVRs MB

VRs MB

VRs MB

1D0V_S5

1D8V_S5

RSMRST_NSIO CPU

C C

CPU MB

PMC_SUSCLKCPU SIO

PMC_SUSPWRDNACK

SIO CPU PMC_PWBTN_N

CPU SIO / VRs

VRs MB

SLP_S4#

DDR_VDDQ

DDR3_DRAM_PWROKCPUMB

SLP_S3#

SIO / VRsCPU

SIO VRs

SIO_PSON#

VCC12VRs MB

VNN/VCOREVRs CPU

B B

VRs

VRs

1D0V_S0

MB

1D05V_S0

MBVRs

1D35V_S0

MB

VRs 1D5V_S0MB

VRs

VRs

1D8V_S0

MB

VCC3/VCC5

MBVRs

V_SM_VTTSO-DIMM

PWRGD_3VSIO MB

SIO PMC_CORE_PWROKCPU

A A

SIO CPU

CPU MB

CPU MB

5

DRAM_CORE_PWROK

PMC_SUS_STAT#

PMC_PLTRST#

4

<Variant Name>

<Variant Name>

<Variant Name>

T

T

Title

itle

itle

Power Sequence

Power Sequence

Power Sequence

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_BayTrail_DT

D

Rosa_BayTrail_DT

D

Rosa_BayTrail_DT

D

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin T ai Wu Rd

21F, 88, Hsin T ai Wu Rd

21F, 88, Hsin T ai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

6 58Tuesday, April 15, 2014

6 58Tuesday, April 15, 2014

6 58Tuesday, April 15, 2014

A00

A00

A00

5

Vinafix.com

D D

C C

4

3

2

1

B B

<Variant Name>

<Variant Name>

A A

5

4

3

2

<Variant Name>

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Title

Title

Title

TBD

TBD

TBD

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_BayTrail_DT

B

Rosa_BayTrail_DT

B

Rosa_BayTrail_DT

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

Hsichih, Taipei

7 58Tuesday, April 15, 2014

7 58Tuesday, April 15, 2014

7 58Tuesday, April 15, 2014

1

A00

A00

A00

5

Vinafix.com

DDR_VDDQ

MEM_A0MEM_A1

M_DATA_A[0..63]21

D D

C C

B B

A A

M_DATA_A63

M_DATA_A62

M_DATA_A61

M_DATA_A60

M_DATA_A59

M_DATA_A58

M_DATA_A57

M_DATA_A56

M_DATA_A55

M_DATA_A54

M_DATA_A53

M_DATA_A52

M_DATA_A51

M_DATA_A50

M_DATA_A49

M_DATA_A48

M_DATA_A47

M_DATA_A46

M_DATA_A45

M_DATA_A44

M_DATA_A43

M_DATA_A42

M_DATA_A41

M_DATA_A40

M_DATA_A39

M_DATA_A38

M_DATA_A37

M_DATA_A36

M_DATA_A35

M_DATA_A34

M_DATA_A33

M_DATA_A32

M_DATA_A31

M_DATA_A30

M_DATA_A29

M_DATA_A28

M_DATA_A27

M_DATA_A26

M_DATA_A25

M_DATA_A24

M_DATA_A23

M_DATA_A22

M_DATA_A21

M_DATA_A20

M_DATA_A19

M_DATA_A18

M_DATA_A17

M_DATA_A16

M_DATA_A15

M_DATA_A14

M_DATA_A13

M_DATA_A12

M_DATA_A11

M_DATA_A10

M_DATA_A9

M_DATA_A8

M_DATA_A7

M_DATA_A6

M_DATA_A5

M_DATA_A4

M_DATA_A3

M_DATA_A2

M_DATA_A1

M_DATA_A0

M_MAA_A[0..15]21

M_MA_DM[7..0]21

M_DQS_A_DP[0..7]21

M_DQS_A_DN[0..7]21

M_SBS_A221

M_SBS_A121

M_SBS_A021

CK_M_DDR0_A_DP21

CK_M_DDR0_A_DN21

CK_M_DDR1_A_DP21

CK_M_DDR1_A_DN21

M_SCS_A_N021

M_SCS_A_N121

M_ODT_A021

M_ODT_A121

M_SCKE_A021

M_SCKE_A121

M_CAS_A_N21

M_WE_A_N21

M_RAS_A_N21

DDR3_DRAMRST_N21

DDR3_DRAM_PWROK48

DDR3_VCCA_PWRGD48

4

DDR_VDDQ 14,16,21,42,48

CK_M_DDR0_A_DP

CK_M_DDR0_A_DN

CK_M_DDR1_A_DP

CK_M_DDR1_A_DN

M_SCS_A_N0

M_SCS_A_N1

M_ODT_A0

M_ODT_A1

M_SCKE_A0

M_SCKE_A1

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A10

M_MAA_A11

M_MAA_A12

M_MAA_A13

M_MAA_A14

M_MAA_A15

M_MA_DM0

M_MA_DM1

M_MA_DM2

M_MA_DM3

M_MA_DM4

M_MA_DM5

M_MA_DM6

M_MA_DM7

M_DQS_A_DP7

M_DQS_A_DP6

M_DQS_A_DP5

M_DQS_A_DP4

M_DQS_A_DP3

M_DQS_A_DP2

M_DQS_A_DP1

M_DQS_A_DP0

M_DQS_A_DN7

M_DQS_A_DN6

M_DQS_A_DN5

M_DQS_A_DN4

M_DQS_A_DN3

M_DQS_A_DN2

M_DQS_A_DN1

M_DQS_A_DN0

M_SBS_A2

M_SBS_A1

M_SBS_A0

1 2

R526

1 2

R529

1 2

R527

1 2

R535

1 2

R534

DDR3_VREF

ICLK_DRAM_TERMN

100KR2F-L1-GP

ICLK_DRAM_TERMN_AF42

100KR2F-L1-GP

DRAM_RCOMP_0

23D2R2F-GP

DRAM_RCOMP_1

29D4R2F-GP

DRAM_RCOMP_2

162R2F-GP

3

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A10

M_MAA_A11

M_MAA_A12

M_MAA_A13

M_MAA_A14

M_MAA_A15

M_MA_DM0

M_MA_DM1

M_MA_DM2

M_MA_DM3

M_MA_DM4

M_MA_DM5

M_MA_DM6

M_MA_DM7

M_RAS_A_N

M_CAS_A_N

M_WE_A_N

M_SBS_A0

M_SBS_A1

M_SBS_A2

M_SCS_A_N0

M_SCS_A_N1

M_SCKE_A0

M_SCKE_A1

M_ODT_A0

M_ODT_A1

CK_M_DDR0_A_DP

CK_M_DDR0_A_DN

CK_M_DDR1_A_DP

CK_M_DDR1_A_DN

DDR3_DRAMRST_N

DDR3_VREF

ICLK_DRAM_TERMN

ICLK_DRAM_TERMN_AF42

DDR3_DRAM_PWROK

DDR3_VCCA_PWRGD

DRAM_RCOMP_0

DRAM_RCOMP_1

DRAM_RCOMP_2

CPU1A

K45

DRAM0_MA_0

H47

DRAM0_MA_1

L41

DRAM0_MA_2

H44

DRAM0_MA_3

H50

DRAM0_MA_4

G53

DRAM0_MA_5

H49

DRAM0_MA_6

D50

DRAM0_MA_7

G52

DRAM0_MA_8

E52

DRAM0_MA_9

K48

DRAM0_MA_10

E51

DRAM0_MA_11

F47

DRAM0_MA_12

J51

DRAM0_MA_13

B49

DRAM0_MA_14

B50

DRAM0_MA_15

G36

DRAM0_DM_0

B36

DRAM0_DM_1

F38

DRAM0_DM_2

B42

DRAM0_DM_3

P51

DRAM0_DM_4

V42

DRAM0_DM_5

Y50

DRAM0_DM_6

Y52

DRAM0_DM_7

M4 5

DRAM0_RAS

M4 4

DRAM0_CAS

H51

DRAM0_WE

K47

DRAM0_BS_0

K44

DRAM0_BS_1

D52

DRAM0_BS_2

P44

DRAM0_CS_0

P45

DRAM0_CS_2

C47

DRAM0_CKE_0

D48

RESERVED_D48

F44

DRAM0_CKE_2

E46

RESERVED_E46

T41

DRAM0_ODT_0

P42

DRAM0_ODT_2

M5 0

DRAM0_CKP_0

M4 8

DRAM0_CKN_0

P50

DRAM0_CKP_2

P48

DRAM0_CKN_2

P41

DRAM0_DRAMRST

AF44

DRAM_VREF

AH42

ICLK_DRAM_TERMN

AF42

ICLK_DRAM_TERMN_AF42

AD42

DRAM_VDD_S4_PWROK

AB42

DRAM_CORE_PWROK

AD44

DRAM_RCOMP_0

AF45

DRAM_RCOMP_1

AD45

DRAM_RCOMP_2

AF40

RESERVED_AF40

AF41

RESERVED_AF41

AD40

RESERVED_AD40

AD41

RESERVED_AD41

BAY-TRAIL-GP

(71.00BAY.C0U)

BAY TRAIL-M/D SOC

2

1 OF 13

DRAM0_DQ_0

DRAM0_DQ_1

DRAM0_DQ_2

DRAM0_DQ_3

DRAM0_DQ_4

DRAM0_DQ_5

DRAM0_DQ_6

DRAM0_DQ_7

DRAM0_DQ_8

DRAM0_DQ9_C32

DRAM0_DQ_10

DRAM0_DQ_11

DRAM0_DQ_12

DRAM0_DQ_13

DRAM0_DQ_14

DRAM0_DQ_15

DRAM0_DQ_16

DRAM0_DQ_17

DRAM0_DQ_18

DRAM0_DQ_19

DRAM0_DQ_20

DRAM0_DQ_21

DRAM0_DQ_22

DRAM0_DQ_23

DRAM0_DQ_24

DRAM0_DQ_25

DRAM0_DQ_26

DRAM0_DQ_27

DRAM0_DQ_28

DRAM0_DQ_29

DRAM0_DQ_30

DRAM0_DQ_31

DRAM0_DQ_32

DRAM0_DQ_33

DRAM0_DQ_34

DRAM0_DQ_35

DRAM0_DQ_36

DRAM0_DQ_37

DRAM0_DQ_38

DRAM0_DQ_39

DRAM0_DQ_40

DRAM0_DQ_41

DRAM0_DQ_42

DRAM0_DQ_43

DRAM0_DQ_44

DRAM0_DQ_45

DRAM0_DQ_46

DRAM0_DQ_47

DRAM0_DQ_48

DRAM0_DQ_49

DRAM0_DQ_50

DRAM0_DQ_51

DRAM0_DQ_52

DRAM0_DQ_53

DRAM0_DQ_54

DRAM0_DQ_55

DRAM0_DQ_56

DRAM0_DQ_57

DRAM0_DQ_58

DRAM0_DQ_59

DRAM0_DQ_60

DRAM0_DQ_61

DRAM0_DQ_62

DRAM0_DQ_63

DRAM0_DQSP_0

DRAM0_DQSN_0

DRAM0_DQSP_1

DRAM0_DQSN_1

DRAM0_DQSP_2

DRAM0_DQSN_2

DRAM0_DQSP_3

DRAM0_DQSN_3

DRAM0_DQSP_4

DRAM0_DQSN_4

DRAM0_DQSP_5

DRAM0_DQSN_5

DRAM0_DQSP_6

DRAM0_DQSN_6

DRAM0_DQSP_7

DRAM0_DQSN_7

DDR_VDDQ

12

DDR3_VREF_R

12

M_DATA_A0

M3 6

M_DATA_A1

J36

M_DATA_A2

P40

M_DATA_A3

M4 0

M_DATA_A4

P36

M_DATA_A5

N36

M_DATA_A6

K40

M_DATA_A7

K42

M_DATA_A8

B32

M_DATA_A9

C32

M_DATA_A10

C36

M_DATA_A11

A37

M_DATA_A12

C33

M_DATA_A13

A33

M_DATA_A14

C37

M_DATA_A15

B38

M_DATA_A16

F36

M_DATA_A17

G38

M_DATA_A18

F42

M_DATA_A19

J42

M_DATA_A20

G40

M_DATA_A21

C38

M_DATA_A22

G44

M_DATA_A23

D42

M_DATA_A24

A41

M_DATA_A25

C41

M_DATA_A26

A45

M_DATA_A27

B46

M_DATA_A28

C40

M_DATA_A29

B40

M_DATA_A30

B48

M_DATA_A31

B47

M_DATA_A32

K52

M_DATA_A33

K51

M_DATA_A34

T52

M_DATA_A35

T51

M_DATA_A36

L51

M_DATA_A37

L53

M_DATA_A38

R51

M_DATA_A39

R53

M_DATA_A40

T47

M_DATA_A41

T45

M_DATA_A42

Y40

M_DATA_A43

V41

M_DATA_A44

T48

M_DATA_A45

T50

M_DATA_A46

Y42

M_DATA_A47

AB40

M_DATA_A48

V45

M_DATA_A49

V47

M_DATA_A50

AD48

M_DATA_A51

AD50

M_DATA_A52

V48

M_DATA_A53

V50

M_DATA_A54

AB44

M_DATA_A55

Y45

M_DATA_A56

V52

M_DATA_A57

W51

M_DATA_A58

AC53

M_DATA_A59

AC51

M_DATA_A60

W53

M_DATA_A61

Y51

M_DATA_A62

AD52

M_DATA_A63

AD51

M_DQS_A_DP0

J38

M_DQS_A_DN0

K38

M_DQS_A_DP1

C35

M_DQS_A_DN1

B34

M_DQS_A_DP2

D40

M_DQS_A_DN2

F40

M_DQS_A_DP3

B44

M_DQS_A_DN3

C43

M_DQS_A_DP4

N53

M_DQS_A_DN4

M5 2

M_DQS_A_DP5

T42

M_DQS_A_DN5

T44

M_DQS_A_DP6

Y47

M_DQS_A_DN6

Y48

M_DQS_A_DP7

AB52

M_DQS_A_DN7

AA51

R545

4K7R2F-GP

R542

4K7R2F-GP

1A 0115 Allen modify

R539 0R0402-PAD-2-GP

12

12

C372

SCD1U16V2KX-3GP

1

DDR3_VREF

12

C385

SCD1U16V2KX-3GP

(R)

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_BayTrail_DT

C

Rosa_BayTrail_DT

C

Rosa_BayTrail_DT

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

8 58Tuesday, April 15, 2014

8 58Tuesday, April 15, 2014

8 58Tuesday, April 15, 2014

A00

A00

A00

5

Vinafix.com

4

3

2

1

D D

C C

B B

AY45

BB47

AW41

BB44

BB50

BC53

BB49

BF50

BC52

BE52

AY48

BE51

BD47

BA51

BH49

BH50

BD38

BH36

BC36

BH42

AT5 1

AM42

AK50

AK52

AV45

AV44

BB51

AY47

AY44

BF52

AT4 4

AT4 5

BG47

BE46

BD44

BF48

AP41

AT4 2

AV50

AV48

AT5 0

AT4 8

AT4 1

CPU1B

DRAM1_MA_0

DRAM1_MA_1

DRAM1_MA_2

DRAM1_MA_3

DRAM1_MA_4

DRAM1_MA_5

DRAM1_MA_6

DRAM1_MA_7

DRAM1_MA_8

DRAM1_MA_9

DRAM1_MA_10

DRAM1_MA_11

DRAM1_MA_12

DRAM1_MA_13

DRAM1_MA_14

DRAM1_MA_15

DRAM1_DM_0

DRAM1_DM_1

DRAM1_DM_2

DRAM1_DM_3

DRAM1_DM_4

DRAM1_DM_5

DRAM1_DM_6

DRAM1_DM_7

DRAM1_RAS

DRAM1_CAS

DRAM1_WE

DRAM1_BS_0

DRAM1_BS_1

DRAM1_BS_2

DRAM1_CS_0

DRAM1_CS_2

DRAM1_CKE_0

RESERVED_BE46

DRAM1_CKE_2

RESERVED_BF48

DRAM1_ODT_0

DRAM1_ODT_2

DRAM1_CKP_0

DRAM1_CKN_0

DRAM1_CKP_2

DRAM1_CKN_2

DRAM1_DRAMRST

BAY TRAIL-M/D SOC

2 OF 13

DRAM1_DQ_0

DRAM1_DQ_1

DRAM1_DQ_2

DRAM1_DQ_3

DRAM1_DQ_4

DRAM1_DQ_5

DRAM1_DQ_6

DRAM1_DQ_7

DRAM1_DQ_8

DRAM1_DQ_9

DRAM1_DQ_10

DRAM1_DQ_11

DRAM1_DQ_12

DRAM1_DQ_13

DRAM1_DQ_14

DRAM1_DQ_15

DRAM1_DQ_16

DRAM1_DQ_17

DRAM1_DQ_18

DRAM1_DQ_19

DRAM1_DQ_20

DRAM1_DQ_21

DRAM1_DQ_22

DRAM1_DQ_23

DRAM1_DQ_24

DRAM1_DQ_25

DRAM1_DQ_26

DRAM1_DQ_27

DRAM1_DQ_28

DRAM1_DQ_29

DRAM1_DQ_30

DRAM1_DQ_31

DRAM1_DQ_32

DRAM1_DQ_33

DRAM1_DQ_34

DRAM1_DQ_35

DRAM1_DQ_36

DRAM1_DQ_37

DRAM1_DQ_38

DRAM1_DQ_39

DRAM1_DQ_40

DRAM1_DQ_41

DRAM1_DQ_42

DRAM1_DQ_43

DRAM1_DQ_44

DRAM1_DQ_45

DRAM1_DQ_46

DRAM1_DQ_47

DRAM1_DQ_48

DRAM1_DQ_49

DRAM1_DQ_50

DRAM1_DQ_51

DRAM1_DQ_52

DRAM1_DQ_53

DRAM1_DQ_54

DRAM1_DQ_55

DRAM1_DQ_56

DRAM1_DQ_57

DRAM1_DQ_58

DRAM1_DQ_59

DRAM1_DQ_60

DRAM1_DQ_61

DRAM1_DQ_62

DRAM1_DQ_63

DRAM1_DQSP_0

DRAM1_DQSN_0

DRAM1_DQSP_1

DRAM1_DQSN_1

DRAM1_DQSP_2

DRAM1_DQSN_2

DRAM1_DQSP_3

DRAM1_DQSN_3

DRAM1_DQSP_4

DRAM1_DQSN_4

DRAM1_DQSP_5

DRAM1_DQSN_5

DRAM1_DQSP_6

DRAM1_DQSN_6

DRAM1_DQSP_7

DRAM1_DQSN_7

BG38

BC40

BA42

BD42

BC38

BD36

BF42

BC44

BH32

BG32

BG36

BJ37

BG33

BJ33

BG37

BH38

AU36

AT3 6

AV40

AT4 0

BA36

AV36

AY42

AY40

BJ41

BG41

BJ45

BH46

BG40

BH40

BH48

BH47

AY52

AY51

AP52

AP51

AW51

AW53

AR51

AR53

AP47

AP45

AK40

AM41

AP48

AP50

AK42

AH40

AM45

AM47

AF48

AF50

AM48

AM50

AH44

AK45

AM52

AL51

AG53

AG51

AL53

AK51

AF52

AF51

BF40

BD40

BG35

BH34

BA38

AY38

BH44

BG43

AU53

AV52

AP42

AP44

AK47

AK48

AH52

AJ51

BAY-TRAIL-GP

(71.00BAY.C0U)

A A

5

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_BayTrail_DT

C

Rosa_BayTrail_DT

C

Rosa_BayTrail_DT

C

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

9 58Tuesday, April 15, 2014

9 58Tuesday, April 15, 2014

9 58Tuesday, April 15, 2014

A00

A00

A00

5

Vinafix.com

4

3

2

1

1D8V_S0

VCC3

1D8V_S0 12,13,15,17,19,23,25,30,35,38,43,46

VCC3 12,13,15,17,20,21,23,24,25,30,31,34,35,36,38,39,46,56

X2 GPU

PEG_RXP049

D D

PEG_RXN049

PEG_TXP049

PEG_TXN049

PEG_RXP149

PEG_RXN149

PEG_TXP149

PEG_TXN149

Wireless

HSI_C_DP234

HSI_C_DN234

HSO_C_DP234

HSO_C_DN234

Giga LAN

HSI_LAN_DP330

HSI_LAN_DN330

C C

HDD

ODD

B B

HSO_C_LAN_DP330

HSO_C_LAN_DN330

SATA 2.0

SATAHDR_TX_DP035

SATAHDR_TX_DN035

SATAHDR_RX_DN035

SATAHDR_RX_DP035

SATAHDR_TX_DP135

SATAHDR_TX_DN135

SATAHDR_RX_DN135

SATAHDR_RX_DP135

LANCLK_REQ_N30

SB 1129 Allen modify

0808 Allen modify

SATAHDR_TX_DP0

SATAHDR_TX_DN0

HDD

ODD

0R0402-PAD-2-GP

R518

R517

remove OSD_UP/DN (Patrick)

R519 402R2F-GP

remove Panel select pin (Patrick)

remove PWRCN_DET_N_C (Patrick)

1 2

49D9R2F-GP

12

12

0R0402-PAD-2-GP

12

R520

SATAHDR_RX_DP0

SATAHDR_RX_DN0

SATAHDR_TX_DP1

SATAHDR_TX_DN1

SATAHDR_RX_DP1

SATAHDR_RX_DN1

ICLK_SATA_TERMP

ICLK_SATA_TERMN

APU_SATA_LED_N

SATA_RCOMP_DP

SATA_RCOMP_DN

MMC1_RCOMP

SD

1 2

R533

LPE_I2S2_DATAOUT19

LPE_I2S2_FRM19

APU_SATA_LED_N35

A A

APU_PROCHOT#39,45,52

HDA BUS

AUD_LINK_SDO31

AUD_LINK_SYNC31

AUD_LINK_BCLK31

AUD_LINK_RST_N31

AUD_LINK_SDIN31

5

49D9R2F-GP

AUD_LINK_SYNC AZ_SYNC_M

AUD_LINK_SDO AZ_SDOUT_M

AUD_LINK_BCLK AZ_BCLK_M

AUD_LINK_RST_N

12

(R)

C86

SCD01U25V2KX-3GP

Follow Nadia ESD

02/23

4

SD3_RCOMP

RN1

1

2

3

4 5

SRN33J-4-GP

CPU1D

BF6

SATA_TXP_0

BG7

SATA_TXN_0

AU16

SATA_RXP_0

AV16

SATA_RXN_0

BD10

SATA_TXP_1

BF10

SATA_TXN_1

AY16

SATA_RXP_1

BA16

SATA_RXN_1

BB10

ICLK_SATA_TERMP

BC10

ICLK_SATA_TERMN

BA12

SATA_GP0

AY14

SATA_GP1

AY12

SATA_LED

AU18

SATA_RCOMP_P_AU18

AT18

SATA_RCOMP_N_AT18

AT22

MMC1_CLK

AV20

MMC1_D0

AU22

MMC1_D1

AV22

MMC1_D2

AT20

MMC1_D3

AY24

MMC1_D4

AU26

MMC1_D5

AT26

MMC1_D6

AU20

MMC1_D7

AV26

MMC1_CMD

BA24

MMC1_RST

AY18

MMC1_RCOMP

BA18

SD2_CLK

AY20

SD2_D0

BD20

SD2_D1

BA20

SD2_D2

BD18

SD2_D3_CD

BC18

SD2_CMD

AY26

SD3_CLK

AT28

SD3_D0

BD26

SD3_D1

AU28

SD3_D2

BA26

SD3_D3

BC24

SD3_CD#

AV28

SD3_CMD

BF22

SD3_1P8EN

BD22

SD3_PWREN

BF26

SD3_RCOMP

BAY-TRAIL-GP

(71.00BAY.C0U)

8

7

6

AZ_RST_N_M

3

BAY TRAIL-M/D SOC

PCIE_RCOMP_P_AP14

PCIE_RCOMP_N_AP13

LPE_I2S2_DATAOUT

4 OF 13

PCIE_TXP_0

PCIE_TXN_0

PCIE_RXP_0

PCIE_RXN_0

PCIE_TXP_1

PCIE_TXN_1

PCIE_RXP_1

PCIE_RXN_1

PCIE_TXP_2

PCIE_TXN_2

PCIE_RXP_2

PCIE_RXN_2

PCIE_TXP_3

PCIE_TXN_3

PCIE_RXP_3

PCIE_RXN_3

VSS_BB7

VSS_BB5

PCIE_CLKREQ_0

PCIE_CLKREQ_1

PCIE_CLKREQ_2

PCIE_CLKREQ_3

SD3_WP_BD5

RESERVED_BB4

RESERVED_BB3

RESERVED_AV10

RESERVED_AV9

HDA_LPE_RCOMP

HDA_RST

HDA_SYNC

HDA_CLK

HDA_SDO

HDA_SDI0

HDA_SDI1

HDA_DOCKRST

HDA_DOCKEN

LPE_I2S2_CLK

LPE_I2S2_FRM

LPE_I2S2_DATAIN

RESERVED_P34

RESERVED_N34

RESERVED_AK9

RESERVED_AK7

PROCHOT

P_GFX_TXP0

AY7

P_GFX_TXN0

AY6

AT14

AT13

P_GFX_TXP1

AV6

P_GFX_TXN1 PEG_TXN1

AV4

AT10

AT9

C_GPP_TXP2 HSO_C_DP2

AT7

C_GPP_TXN2

AT6

AP12

AP10

HSO_LAN_DP3

AP6

HSO_LAN_DN3

AP4

AP9

AP7

1A 0115 Allen modify

VSS_BB7_TP

BB7

VSS_BB5_TP

BB5

BG3

BD7

BG5

BE3

BD5

AP14

AP13

BB4

BB3

AV10

AV9

BF20

BG22

BH20

BJ21

BG20

BG19

BG21

BH18

BG18

BF28

BA30

BC30

BD28

P34

N34

AK9

AK7

C24

PCIE_CLKREQ_0

PCIE_CLKREQ_1

PCIE_CLKREQ_2

LANCLK_REQ_N

PCIE_RCOMP_P_AP14_AP14

PCIE_RCOMP_N_AP13_AP13

HDA_LPE_RCOMP

12

2

1 2

C325 SCD1U16V2KX-3GP(G)

1 2

C322 SCD1U16V2KX-3GP(G)

1 2

C324 SCD1U16V2KX-3GP(G)

1 2

C328 SCD1U16V2KX-3GP(G)

1 2

C54 SCD1U16V2KX-3GP

1 2

C56 SCD1U16V2KX-3GP

1 2

C315 SCD1U16V2KX-3GP

1 2

C316 SCD1U16V2KX-3GP

PR219 0R0402-PAD-2-GP

PR218 0R0402-PAD-2-GP

1A 0115 Allen modify

R490 0R0402-PAD-2-GP

C313

SC47P50V2JN-3GP

(R)

12

12

R510 10KR2J-3-GP

R512 10KR2J-3-GP

R515 10KR2J-3-GP

remove OSD MENU (Patrick)

12

R513 402R2F-GP

1 2

R522 49D9R2F-GP

LPE_I2S2_FRM

LPE_I2S2_DATAOUT

12

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

09_FT3_PCIE

09_FT3_PCIE

09_FT3_PCIE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_BayTrail_DT

B

Rosa_BayTrail_DT

B

Rosa_BayTrail_DT

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

PEG_TXP0

PEG_TXN0

PEG_RXP0

PEG_RXN0

PEG_TXP1

PEG_RXP1

PEG_RXN1

12

12

12

APU_PROCHOT#APU_PROCHOT#_R

HSO_C_DN2

HSI_C_DP2

HSI_C_DN2

HSO_C_LAN_DP3

HSO_C_LAN_DN3

HSI_LAN_DP3

HSI_LAN_DN3

AZ_RST_N_M

AZ_SYNC_M

AZ_BCLK_M

AZ_SDOUT_M

AUD_LINK_SDIN

HDA_SDI1_TP

Wireless

Giga LAN

1D8V_S0

0808 Allen modify

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

10 58Tuesday, April 15, 2014

10 58Tuesday, April 15, 2014

10 58Tuesday, April 15, 2014

1

X2 GPU

1

TP10

A00

A00

A00

5

Vinafix.com

4

3

2

1

1D8V_S0

1D8V_S0 10,12,13,15,17,19,23,25,30,35,38,43,46

HDMI

D D

C C

B B

DDSP_C_TX_DP_025

DDSP_C_TX_DN_025

DDSP_C_TX_DP_125

DDSP_C_TX_DN_125

DDSP_C_TX_DP_225

DDSP_C_TX_DN_225

DDSP_C_TX_DP_325

DDSP_C_TX_DN_325

DDSP_C_HPD25

DDPC_CTRL_CLK25

DDPC_CTRL_DATA19,25

DDI1_DDCDATA19

Debug VGA

XDP

VGA_RED

VGA_GREEN

VGA_BLUE

VGA_HSYNC_3V

VGA_VSYNC_3V

VGA_FCH_DDCSCL

VGA_FCH_DDCSDA

VGA_RED24

VGA_GREEN24

VGA_BLUE24

VGA_HSYNC_3V24

VGA_VSYNC_3V24

VGA_FCH_DDCSCL24

VGA_FCH_DDCSDA24

GPIO_S0_NC1319

DBG1523

DBG1423

DBG1323

DBG1223

DBG1123

DBG1023

DBG923

DBG823

OBSFN_C023

Add HDMI function (Patrick)

DDSP_C_TX_DP_0

DDSP_C_TX_DN_0

DDSP_C_TX_DP_1

DDSP_C_TX_DN_1

DDSP_C_TX_DP_2

DDSP_C_TX_DN_2

DDSP_C_TX_DP_3

DDSP_C_TX_DN_3

DDSP_C_HPD

DDPC_CTRL_DATA

DDPC_CTRL_CLK

402R2F-GP

R503

DDI0_RCOMP_N

1 2

1A 0115 Allen modify

PR216 0R0402-PAD-2-GP

PR217 0R0402-PAD-2-GP

DDI0_RCOMP_P

12

12

GPIO_S0_NC13

GPIO_S0_NC14_TP

1

TP7

GPIO_S0_NC12_TP

1

TP8

VSS_AM3_TP

VSS_AM2_TP

AM14

AM13

AK13

AK12

AB14

AV3

AV2

AT2

AT3

AR3

AR1

AP3

AP2

AL3

AL1

D27

C26

C28

B28

C27

B26

AM3

AM2

T2

T3

AB3

AB2

Y3

Y2

W3

W1

V2

V3

R3

R1

AD6

AD4

AB9

AB7

Y4

Y6

V4

V6

A29

C29

B30

C30

CPU1C

DDI0_TXP_0

DDI0_TXN_0

DDI0_TXP_1

DDI0_TXN_1

DDI0_TXP_2

DDI0_TXN_2

DDI0_TXP_3

DDI0_TXN_3

DDI0_AUXP

DDI0_AUXN

DDI0_HPD

DDI0_DDCDATA

DDI0_DDCCLK

DDI0_VDDEN

DDI0_BKLTEN

DDI0_BKLTCTL

DDI0_RCOMP

DDI0_RCOMP_P

RESERVED_AM14

RESERVED_AM13

VSS_AM3

VSS_AM2

RESERVED_T2

RESERVED_T3

RESERVED_AB3

RESERVED_AB2

RESERVED_Y3

RESERVED_Y2

RESERVED_W3

RESERVED_W1

RESERVED_V2

RESERVED_V3

RESERVED_R3

RESERVED_R1

RESERVED_AD6

RESERVED_AD4

RESERVED_AB9

RESERVED_AB7

RESERVED_Y4

RESERVED_Y6

RESERVED_V4

RESERVED_V6

GPIO_S0_NC13

GPIO_S0_NC14_C29

RESERVED_AB14

GPIO_S0_NC12

RESERVED_C30

BAY-TRAIL-GP

(71.00BAY.C0U)

BAY TRAIL-M/D SOC

3 OF 13

DDI1_TXP_0

DDI1_TXN_0

DDI1_TXP_1

DDI1_TXN_1

DDI1_TXP_2

DDI1_TXN_2

DDI1_TXP_3

DDI1_TXN_3

DDI1_AUXP

DDI1_AUXN

DDI1_HPD

DDI1_DDCDATA

DDI1_DDCCLK

DDI1_VDDEN

DDI1_BKLTEN

DDI1_BKLTCTL

RESERVED_AH14

RESERVED_AH13

RESERVED_AF14

RESERVED_AF13

VSS_AH3

VSS_AH2

VGA_RED

VGA_BLUE

VGA_GREEN

VGA_IREF

VGA_IRTN

VGA_HSYNC

VGA_VSYNC

VGA_DDCCLK

VGA_DDCDATA

RESERVED_T7

RESERVED_T9

RESERVED_AB13

RESERVED_AB12

RESERVED_Y12

RESERVED_Y13

RESERVED_V10

RESERVED_V9

RESERVED_T12

RESERVED_T10

RESERVED_V14

RESERVED_V13

RESERVED_T14

RESERVED_T13

RESERVED_T6

RESERVED_T4

RESERVED_P14

RESERVED_K34

GPIO_S0_NC26

GPIO_S0_NC25

GPIO_S0_NC24

GPIO_S0_NC23

GPIO_S0_NC22

GPIO_S0_NC21

GPIO_S0_NC20

GPIO_S0_NC18

GPIO_S0_NC17

GPIO_S0_NC16

GPIO_S0_NC15

AG3

AG1

AF3

AF2

AD3

AD2

AC3

AC1

AK3

AK2

K30

P30

G30

N30

J30

M3 0

AH14

AH13

AF14

AF13

AH3

AH2

BA3

AY2

BA1

AW1

AY3

BD2

BF2

BC1

BC2

T7

T9

AB13

AB12

Y12

Y13

V10

V9

T12

T10

V14

V13

T14

T13

T6

T4

P14

K34

D32

N32

J34

K28

F28

F32

D34

J28

D28

M3 2

F34

remove DP to LVDS (Patrick)

None use link to GND

VSS_AH3_TP

VSS_AH2_TP

VGA_RED

VGA_BLUE

VGA_GREEN

VGA_IREF

VGA_HSYNC

VGA_VSYNC

VGA_FCH_DDCSCL

VGA_FCH_DDCSDA

R109 15R2F-2-GP

R110 15R2F-2-GP

1A 0115 Allen modify

12

PR215 0R0402-PAD-2-GP

12

PR214 0R0402-PAD-2-GP

1 2

R104

357R2F-GP

1 2

1 2

DBG11

DBG15

DBG14

DBG13

DBG12

DBG10

DBG9

DBG8

OBSFN_C0

VGA_HSYNC_3V

VGA_VSYNC_3V

DDI1_DDCDATA

R107

150R2F-1-GP

1 2

1 2

150R2F-1-GP

R105

R108

150R2F-1-GP

1 2

TO VGA

A A

5

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

CPU LGA 1155_1

CPU LGA 1155_1

CPU LGA 1155_1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_BayTrail_DT

C

Rosa_BayTrail_DT

C

Rosa_BayTrail_DT

C

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

1

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

11 58Tuesday, April 15, 2014

11 58Tuesday, April 15, 2014

11 58Tuesday, April 15, 2014

A00

A00

A00

1D8V_S0

Vinafix.com

1D8V_S5

1D0V_S0

SB5V

V_3P0_BAT_VREG

V_3P3_A

VBAT2

VCC3

SB3V

D D

CLOCK

CK_GLAN_DP30

CK_GLAN_DN30

CK_PE_100M_16PORT_DP49

CK_PE_100M_16PORT_DN49

CK_PCIEX1_WLAN_DP34

CK_PCIEX1_WLAN_DN34

XDP

XDP_H_TCK23

XDP_H_TRST_N23

XDP_H_TMS23

XDP_H_TDI23

TAP_PREQ#23

XDP_H_TDO23

TAP_PRDY#23

OBSFN_C123

DBG023

DBG123

DBG223

DBG323

DBG423

C C

DBG523

DBG623

DBG723

SLP_S3_N20,38,45

PM_SLP_S3#_CPU20

PM_SLP_S4#_CPU20

PWRGD_3V38

THERMA L_SHUT#38

SIO_PWNBTN_N38

RSMRST_N23,38,57

PLT_RST#_CPU20

COREPWROK23,39

PSTBTN_N23

PWRBTN_N23,35,38

PCIE_WAKE#_CPU20

FP_AUD_DETECT31

SYS_PWRGD48,52

B B

A A

THERMAL

PIN Header DET

FB_USBF1_DET28

FB_USBF2_DET28

CHASSIS_ID_035

CHASSIS_ID_135

MTST_ID35

LPC_PME_N38

IO_SMI_N38

PCH_RTCTEST_PULLUP23

MINICARD

W1_DETECT_USB_H34

W1_DETECT_PE34

VR_SVID_ALERT#45

VR_SVID_CLK45

VR_SVID_DATA45

5

1D8V_S0 10, 13,15,17,19,23,25,30,35,38, 43,46

1D8V_S5 15, 17,20,23,28,30,34,38,43,44, 56,57

1D0V_S0 15, 17,43,44,45

SB5V 27,31, 35,38,39,41,42,43,44,45,47, 57

V_3P0_BAT_VREG 15

V_3P3_A 20,23, 35,38,40,46,47,57

VBAT2 38

VCC3 13,15,17,20,21,23,24,25, 30,31,34,35,36,38,39,46,56

SB3V 15,17, 20,30,34,35,38,43,44,45,47, 48,57

1D8V_S5

1 2

R1255 10KR2J-3-GP

1 2

R1256 10KR2J-3-GP

1 2

R1244 10KR2J-3-GP

1 2

R1245 2K2R2J-2-GP

1 2

R1254 2K2R2J-2-GP

1 2

R1246 2K2R2J-2-GP

NEW GPIO Pull high (Patrick)

1D8V_S5

1D8V_S5

1D8V_S5

10KR2J-3-GP

APU_PWNBTN_N_R

SB 1128 Allen modify

12

SPI_CS0_N

WP# function is not supported when

W1_DETECT_USB_H

W1_DETECT_PE

SPI ROM is used on descriptor mode.

5

ICLK_ICOMP

1 2

R500

4K02R2F-GP

ICLK_RCOMP

1 2

R501

47D5R2F-1-GP

FB_USBF1_DET

FB_USBF2_DET

CHASSIS_ID_0

CHASSIS_ID_1

FP_AUD_DETECT

MTST_ID

XDP_H_TCK

1 2

R466

51R2J-2-GP

XDP_H_TRST_N

1 2

R456

51R2J-2-GP

XDP_H_TMS

1 2

R458

51R2J-2-GP

XDP_H_TDI

1 2

R457

51R2J-2-GP

XDP_H_TDO

1 2

R473

SPI ROM

51R2J-2-GP

Level shift

0828 Allen Add

1D8V_S51D8V_S5

V_3P3_A

12

R56

Joey_SA_0515

C55

SC12P50V2JN-3GP

SPI ROM

R55

2K2R2J-2-GP

R57

SIO_PWNBTN_B

Q18

1 2

X2

10KR2J-3-GP

(R)

1 2

23

12

R169

10KR2J-3-GP

1 2

CBE

MMBT3904-4-GP

NOTE:The 1Mohm Damping Resistor

Use 0603 and Can't change to 0402!

R96 1MR3F-GP

4 1

XTAL-25MHZ-181-GP

SMT

+- 20ppm CL:12P

1 2

R171 22R2F-1-GP

1 2

R170 22R2F-1-GP

GPU

WLAN

GLAN

SIO_PWNBTN_N

R664

1 2

0R2J-2-GP

(R)

XTAL_25M_PCH_IN

XTAL_25M_PCH_OUT

12

C53

SC12P50V2JN-3GP

1D8V_SPI

SPI_CS0_N_ROM_1

SPI_MISO_ROM_1SPI_DATAIN

SPI_WP#

XTAL_25M_PCH_IN

XTAL_25M_PCH_OUT

ICLK_ICOMP

ICLK_RCOMP

CK_PE_100M_16PORT_DN

CK_PE_100M_16PORT_DP

CK_PCIEX1_WLAN_DN

CK_PCIEX1_WLAN_DP

CK_GLAN_DN

CK_GLAN_DP

XDP_H_TCK

XDP_H_TRST_N

XDP_H_TMS

XDP_H_TDI

XDP_H_TDO

TAP_PRDY#

TAP_PREQ#

SPI_CS0_N

SPI_DATAIN

SPI_DATAOUT

SPI_CLK

IO_SMI_N

PW_CLEAR

LPC_PME_N

W1_DETECT_PE_C

W1_DETECT_USB

PWRBTN_N

1025 Allen modify

Power plane from 1D8V_S0 change to 1D8V_S5

12

R172

10KR2J-3-GP

4

PCH_RTCRST_PULLUP

AT34_TP

1

TP39

1

TP1407

TP32

Remove WEBCAM,LVDS DET

FB_USBF1_DET

FB_USBF2_DET

CHASSIS_ID_0

CHASSIS_ID_1

MTST_ID

Add new GPIO (Patrick)

FP_AUD_DETECT

GPIO_RCOMP18

1 2

R504

49D9R2F-GP

1A 0115 Allen modify

SYS_PWRGD

W1_DETECT_PE_C W1_DETECT_PE

R178

0R0402-PAD-2-GP

SOP8 for 8Mb

U8

1

CS#

2

DO/IO1

3

WP#/IO2

4

GND

W25Q64FWSSIG-GP

SRCON1

1

3 6

425

SKT-G6179-GP-U

62.10076.011

62.10089.001

8

VCC

7

HOLD#/RESET#/IO3

6

CLK

5

DI/IO0

8

7

(D62.10089.121)

SPI socket mount in SA stage

4

AH12

AH10

AD9

AD14

AD13

AD10

AD12

AF6

AF4

AF9

AF7

AK4

AK6

AM4

AM6

AM10

AM9

BH7

BH5

BH4

BH8

BH6

BJ9

C12

D14

G12

F14

F12

G16

D18

F16

AT34

C23

C21

B22

A21

C22

B18

B16

C18

A17

C17

C16

B14

C15

C13

A13

C19

N26

0R0402-PAD

SST_HOLDJ_1

SPI_CLK_1

SPI_MOSI_1

CPU1E

ICLK_OSCIN

ICLK_OSCOUT

RESERVED_AD9

ICLK_ICOMP

ICLK_RCOMP

RESERVED_AD10

RESERVED_AD12

PCIE_CLKN_0

PCIE_CLKP_0

PCIE_CLKN_1

PCIE_CLKP_1

PCIE_CLKN_2

PCIE_CLKP_2

PCIE_CLKN_3

PCIE_CLKP_3

RESERVED_AM10

RESERVED_AM9

PMC_PLT_CLK_0

PMC_PLT_CLK_1

PMC_PLT_CLK_2

PMC_PLT_CLK_3

PMC_PLT_CLK_4

PMC_PLT_CLK_5

ILB_RTC_RST

TAP_TCK

TAP_TRST

TAP_TMS

TAP_TDI

TAP_TDO

TAP_PRDY

TAP_PREQ

RESERVED

PCU_SPI_CS_0

PCU_SPI_CS_1

PCU_SPI_MISO

PCU_SPI_MOSI

PCU_SPI_CLK

GPIO_S5_0

GPIO_S5_1

GPIO_S5_2

GPIO_S5_3

GPIO_S5_4

GPIO_S5_5

GPIO_S5_6

GPIO_S5_7

GPIO_S5_8

GPIO_S5_9

GPIO_S5_10

GPIO_RCOMP

BAY-TRAIL-GP

(71.00BAY.C0U)

12

12

R443

1D8V_SPI

VCC3

12

1 2

12

R186

10KR2J-3-GP

1 2

R188 22R2F-1-GP

1 2

R187 22R2F-1-GP

R184

10KR2J-3-GP

COREPWROK

C111

SCD1U16V2KX-3GP

(R)

C116

SCD1U16V2KX-3GP

1 2

BAY TRAIL-M/D SOC

R713

0R0402-PAD-2-GP

SPI_CLK

SPI_DATAOUT

12

1A 0115 Allen modify

SIO_UART1_RXD

SIO_UART1_TXD

SIO_UART1_RTS

SIO_UART1_CTS

SIO_UART2_RXD

SIO_UART2_TXD

SIO_UART2_RTS

SIO_UART2_CTS

PMC_SUSPWRDNACK

PMC_SUSCLK0_G24

PMC_SLP_S0IX

PMC_SLP_S4

PMC_SLP_S3

GPIO_S514_J20

PMC_ACPRESENT

PMC_WAKE_PCIE_0

PMC_BATLOW

PMC_PWRBTN

PMC_RSTBTN

PMC_PLTRST

GPIO_S517_J24

PMC_SUS_STAT

ILB_RTC_TEST

PMC_RSMRST

PMC_CORE_PWROK

ILB_RTC_X1

ILB_RTC_X2

ILB_RTC_EXTPAD

SVID_ALERT

SVID_DATA

SVID_CLK

SIO_PWM_0

SIO_PWM_1

GPIO_S5_22

GPIO_S5_23

GPIO_S5_24

GPIO_S5_25

GPIO_S5_26

GPIO_S5_27

GPIO_S5_28

GPIO_S5_29

GPIO_S5_30

SIO_SPI_CS

SIO_SPI_MISO

SIO_SPI_MOSI

SIO_SPI_CLK

1D8V_S51D8V_SPI

5 OF 13

AU34

AV34

BA34

AY34

BF34

BD34

BD32

BF32

D26

G24

F18

F22

D22

J20

D20

F26

K26

J26

BG9

F20

J24

G18

C11

B10

B7

C9

A9

B8

B24

A25

C25

AU32

AT32

K24

N24

M20

J18

M18

K18

K20

M22

M24

AV32

BA28

AY28

AY30

VCCRTC

PW_CLEAR

12

12

3

SKEW1

SKEW2

SKEW3

BOARD1

BOARD2

BOARD3

SUS_PWR_ACK_CPU

SUSCLK_SIO_C

SLP_SLP_S0

PM_SLP_S4#_CPU

PM_SLP_S3#_CPU

AC_PRESENT_CPU

WAKE_N_APU PCIE_WAKE#_CPU

PMC_BATLOW#

PSTBTN_N

PLT_RST#_CPU

PMC_SUS_STAT

BVCCRTC_EXTPAD

1 2

SVID_DATA_L

1 2

SVID_CLK_L

1 2

R491 10KR2J-3-GP

R69 0R0402-PAD-2-GP

R492 20KR2J-L2-GP

R70 0R0402-PAD-2-GP

R1208 10KR2J-3-GP(R)

1A 0112 Allen modify

1

TP35

PCH_RTCTEST_PULLUP

1 2

C49

SCD1U10V2KX-5GP

R98 20R2F-GP

R494 16D9R2F-1-GP

R497 0R2J-2-GP

1A 0115 Allen modify

1 2

1 2

1 2

2

SCD01U25V2KX-3GP

RSMRST_N

COREPWROK

0812 Vcore IC check

VR_SVID_ALERT#SVID_ALERT#_L

VR_SVID_DATA

VR_SVID_CLK RSMRST_N

9/2: Add PH resistor (MARK)

OBSFN_C1

DBG0

DBG1

DBG2

DBG3

DBG4

DBG5

DBG6

DBG7

VBAT1

R561

10KR2J-3-GP

(R)

R557

10KR2J-3-GP

3

TP14

TPAD28

1

+

12

BT1

BAT-AAA-BAT-029-K01-GP

12

R554

10KR2J-3-GP

12

R552

10KR2J-3-GP

TP13

TPAD28

R199

1

1 2

1KR2J-1-GP

D6

RB551V30-GP

VBAT2

12

R88

0R0402-PAD

1D8V_S01D8V_S0 1D8V_S0

12

R556

10KR2J-3-GP

(R)

(R)

BOARD3BOARD1 BOA RD2

12

R553

10KR2J-3-GP

12

1

12

(R)

C42

SB 1126 Allen modify

PCH_RTCX1

PCH_RTCX2

Power VID control

VR_SVID_ALERT#

1 2

69D8R2F-GP

Battery Socket

ST: 22.70017.051

FLAT: 22.70017.061

Battery (CR2032):

23.22063.001

V_3P3_A

VBAT1_R

2

3

K A

PW_CLEAR_H

Board ID Settings

MB Version Board1

SA 0

SB 0

-1A 1

-1 001

SB 1201 Allen modify

APU_PWNBTN_N_RAPU_PWNBTN_N

R487

1

D5

BAS40C-2-GP

V_3P0_BAT_VREG

1

1

1

1 2

TP36

TP34

TP33

C44

SC150P50V2KX-1-GP

1D0V_S0

1D8V_S5

R89

10KR2J-3-GP

1 2

1D8V_S5

1D8V_S5

W/T CAP

W/O CAP

BAT1

BATTERY CR2032

(23.22063.001)

R499

10KR2J-3-GP

SUS_PWR_ACK_CPU

1 2

1 2

R94

1 2

R181

NORMAL(DEFAULT)

CLR PASSWORD

PASSWORD CLEAR

PSWD1

2

1

JOWLE-CON2-5-GP

(21.63045.102)

Board2

Board3

0

0

1

0

0

1

2

0828 Allen Add

100KR2J-1-GP

COREPWROK

100KR2J-1-GP(R)

THERMA L_SHUT#

12

R287

10KR2J-3-GP(R)

Need to check the GPIO

portion

SB 1128 Allen modify

CLEAN CMOS

12

12

R563

R567

10KR2J-3-GP

10KR2J-3-GP

(R)

12

12

R560

R562

10KR2J-3-GP

10KR2J-3-GP

W1_DETECT_USB W1_DETECT_USB_H

2

1

PCH_RTCX2

X1

RTCX_L PCH_RTCX1

1

12

R77

0R0402-PAD

12

C45

SC15P50V3JN-DLGP

1A 0115 Allen modify

SLP_S3_N

PWRGD_3V

1 GND

2 RTC_RST

1 2

R87 20KR2F-L-GP

V_3P0_BAT_VREG

Debug Only

1 2

R91 20KR2F-L-GP

V_3P0_BAT_VREG

1D8V_S01D8V_S0 1D8V_S0

12

R558

10KR2J-3-GP

(G)

SKEW3SKEW1 SKEW 2

12

R555

10KR2J-3-GP

(R)

(U)

12

R78

0R0402-PAD

Skew ID Settings

MB Version Board1

GPU 0

UMA 0

Level shift

0828 Allen Add

(84.2N702.J31)

SLP_S3_N_G

1 2

R724

0R0402-PAD-2-GP

1A 0115 Allen modify

1 2

R723

0R0402-PAD-2-GP

12

12

(84.2N702.J31)

PWRGD_3V_G

C50

SC1U10V2KX-1GP

C52

SC1U10V2KX-1GP

Board2

<Variant Name>

<Variant Name>

<Variant Name>

Title

T

itle

T

itle

Size D ocument Number R ev

Size D ocument Number R ev

Size D ocument Number R ev

Custo m

Custo m

Custo m

Date : Sheet of

Date : Sheet of

Date : Sheet of

4

2 3

XTAL-32D768KHZ-65-GP

R81

12

10MR3F-GP

Q78

2N7002H-GP

Q77

2N7002H-GP

12

R92

0R2J-2-GP

(R)

1

0

FT3_ACPI/SD/AZ/GPIO/RTC/MISC

FT3_ACPI/SD/AZ/GPIO/RTC/MISC

FT3_ACPI/SD/AZ/GPIO/RTC/MISC

Rosa_BayTrail_DT

Rosa_BayTrail_DT

Rosa_BayTrail_DT

1

12

C43

SC15P50V3JN-DLGP

SB3V

12

R717

10KR2J-3-GP

SYS_PWRGD_G

G

S D

PWRGD_3V_D

G

S D

SB 1121 Allen modify

PCH_RTCRST_PULLUP

PCH_RTCRST_DOWN

12

1A 0115 Allen modify

R86

0R0402-PAD-2-GP

PCH_RTCTEST_PULLUP

PCH_SRTTEST_DOWN

12

R729

0R0402-PAD-2-GP

Board3

1

1

G

JOWLE-CON2-5-GP

JOWLE-CON2-5-GP

1A 0115 Allen modify

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

SYS_PWRGD

Q79

2N7002H-GP

(84.2N702.J31)

S D

CMCLR1

2

(R)

1

CMCLR2

2

1

A00

A00

A00

12 5 8Tuesday, April 15, 2014

12 5 8Tuesday, April 15, 2014

12 5 8Tuesday, April 15, 2014

5

Vinafix.com

4

3

2

1

2

6 OF 13

RESERVED_M10

RESERVED_M9

RESERVED_P7

RESERVED_P6

RESERVED_M7

USB3_REXT0

RESERVED_P10

RESERVED_P12

RESERVED_M4

RESERVED_M6

USB3_RXP0

USB3_RXN0

USB3_TXP0

USB3_TXN0

RESERVED_H8

RESERVED_H7

RESERVED_H5

RESERVED_H4

GPIO_S0_SC_55

GPIO_S0_SC_56

GPIO_S0_SC_57

GPIO_S0_SC_58

GPIO_S0_SC_59

GPIO_S0_SC_60

GPIO_S0_SC_61

ILB_8254_SPKR

SIO_I2C0_DATA

SIO_I2C0_CLK

SIO_I2C1_DATA

SIO_I2C1_CLK

SIO_I2C2_DATA

SIO_I2C2_CLK

SIO_I2C3_DATA

SIO_I2C3_CLK

SIO_I2C4_DATA

SIO_I2C4_CLK

SIO_I2C5_DATA

SIO_I2C5_CLK

SIO_I2C6_DATA

SIO_I2C6_CLK

GPIO_S0_SC_92

GPIO_S0_SC_93

M1 0

M9

P7

P6

M7

M1 2

P10

P12

M4

M6

D4

E3

K6

K7

H8

H7

H5

H4

BD12

BC12

BD14

BC14

BF14

BD16

BC16

BH12

BH22

BG23

BG24

BH24

BG25

BJ25

BG26

BH26

BF27

BG27

BH28

BG28

BJ29

BG29

BH30

BG30

USB3_P1_REXT

GPIO_S0_SC_56

APU_SPKR

TP_BH30

TP_BG30

R493

1 2

1K24R2F-GP

USB30_RXP0

USB30_RXN0

USB30_TXP0

USB30_TXN0

remove GPIO56,57,60 (BIST,INV_DET)

Patrick

1

TP11 TPAD28

1

TP12 TPAD28

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

CPU LGA 1155_3

CPU LGA 1155_3

CPU LGA 1155_3

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Rosa_BayTrail_DT

C

Rosa_BayTrail_DT

C

Rosa_BayTrail_DT

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

USB3.0 Port

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

13 58Tuesday, April 15, 2014

13 58Tuesday, April 15, 2014

13 58Tuesday, April 15, 2014

A00

A00

A00

1D8V_S0

VCC3

OC

D D

USBOC0130

USBOC0228

1D8V_S0 10,12,15,17,19,23,25,30,35,38,43,46

VCC3 12,15,17,20,21,23,24,25,30,31,34,35,36,38,39,46,56

GLAN

CK_GLAN_DP12,30

CK_GLAN_DN12,30

USB3.0 SIDE I/O

Rear USB

Rear USB

USB HUB

F_USB3P27

F_USB3N27

Rear USB

F_USB1P30

F_USB1N30

C C

F_USB2P30

F_USB2N30

USB HUB

USBOC01 --- Rear IO USB2.0

USBOC02 --- USB3.0

USB3.0

F_USB0P28

F_USB0N28

USB30_RXP028

USB30_RXN028

USB30_TXP028

USB30_TXN028

LPC

CK_25M_SIO

12

C80

SC100P50V2JN-3GP (R)

12

Follow VIC

C84

SC100P50V2JN-3GP(R)

1 2

R116 22R2J-2-GP

1 2

R118 22R2J-2-GP

Remove

TCM_CLK_RUN

(Patrick)

LPC

LAD0_FWH023,38

LAD1_FWH123,38

B B

A A

LAD2_FWH223,38

LAD3_FWH323,38

LFRAMEJ_FW423,38

INT_SERIRQ_CPU38

LPC_CLK123

CK_25M_SIO38

1D8V_S0

SMBUS

SMB0_CLK21,23,38,52

SMB0_DATA21,23,38,52

2 1

VCC3

12

R120

2K2R2J-2-GP

(R)

SMB0_DATA SMB0_CLK

SMB0_DATA_C SMB0_CLK_C

C570

SCD1U10V2KX-5DLGP

U3

1

SDA_B

2

GND

3

VCCA

SDA_A4SCL_A

TCA9406DCUR-GP

SCL_B

VCCB

OE

2K2R2J-2-GP

8

7

6

5

R121

SMBUS_OE

SB 1124 C570, C569 Allen modify

GPIO

APU_SPKR31

GPIO_S0_SC_5619

5

4

VCC3

12

(R)

Avoid routing next to

clock/high speed signals.

Connected to package ground.

LAD0_FWH0

LAD1_FWH1

LAD2_FWH2

LAD3_FWH3

LFRAMEJ_FW4

LPC_CLK0_R

LPC_CLK1_RLPC_CLK1

INT_SERIRQ_CPU

SMB0_DATA_C

SMB0_CLK_C

SMB0_ALERT#

VCC3

TP4

TP3

TP31

TP6

1D8V_S0

12

C569

SCD1U10V2KX-5DLGP

2 1

F_USB0P

F_USB0N

F_USB1P

F_USB1N

F_USB2P

F_USB2N

F_USB3P

F_USB3N

ICLK_USB_TERMN_0

ICLK_USB_TERMN_1

USBOC01

USBOC02

USB_RCOMP

USB_PLL_MON

USB_HSIC_0_DATA

1

USB_HSIC_0_STROBE

1

USB_HSIC_1_DATA

1

USB_HSIC_1_STROBE

1

USB_HSIC_RCOMP

RCOMP_LPC_HVT

R124

8K2R2F-1-GP

1D8V_S0

3

CPU1F

G2

GPIO_S5_31

M3

GPIO_S5_32

L1

GPIO_S5_33

K2

GPIO_S5_34

K3

GPIO_S5_35

M2

GPIO_S5_36

N3

GPIO_S5_37

P2

GPIO_S5_38

L3

GPIO_S5_39

J3

GPIO_S5_40

P3

GPIO_S5_41

H3

GPIO_S5_42

B12

GPIO_S5_43

M1 6

USB_DP0

K16

USB_DN0

J14

USB_DP1

G14

USB_DN1

K12

USB_DP2

J12

USB_DN2

K10

USB_DP3

H10

USB_DN3

D10

ICLK_USB_TERMN_D10

F10

ICLK_USB_TERMN

C20

USB_OC_0

B20

USB_OC_1

D6

USB_RCOMPO

C7

USB_RCOMPI

M1 3

USB_PLL_MON

B4

USB_HSIC0_DATA

B5

USB_HSIC0_STROBE

E2

USB_HSIC1_DATA

D2

USB_HSIC1_STROBE

A7

USB_HSIC_RCOMP

BF18

LPC_RCOMP

BH16

ILB_LPC_AD_0

BJ17

ILB_LPC_AD_1

BJ13

ILB_LPC_AD_2

BG14

ILB_LPC_AD_3

BG17

ILB_LPC_FRAME

BG15

ILB_LPC_CLK_0

BH14

ILB_LPC_CLK_1

BG16

ILB_LPC_CLKRUN

BG13

ILB_LPC_SERIRQ

BG12

PCU_SMB_DATA

BH10

PCU_SMB_CLK

BG11

PCU_SMB_ALERT

BAY-TRAIL-GP

(71.00BAY.C0U)

R486

1 2

R488

1 2

R489

1 2

R496

(R)

1 2

R85

1 2

R524

1 2

12

12

(R)

12

(R)

ICLK_USB_TERMN_0

1KR2F-3-GP

ICLK_USB_TERMN_1

1KR2F-3-GP

USB_RCOMP

45D3R2F-L-GP

USB_PLL_MON

0R2J-2-GP

USB_HSIC_RCOMP

45D3R2F-L-GP

RCOMP_LPC_HVT

49D9R2F-GP

R113 2K2R2J-2-GP

R111 2K2R2J-2-GP

R112 2K2R2J-2-GP

SMB0_ALERT#

SMB0_CLK_C

SMB0_DATA_C

BAY TRAIL-M/D SOC

5

Vinafix.com

4

3

2

1

DDR_VDDQ

VCORE

VNN_GFX

D D

C C

B B

A A

5

DDR_VDDQ 8,16,21,42,48

VCORE 16,38,45

VNN_GFX 16,45

VCC_SENSE45

VSS_SENSE45

1A 0115 Allen modify

VSS_AXG_SENSE45

DDR_VDDQ

VCORE

TP38

1

TPAD28

VCC_SENSE

VSS_SENSE

VSS_AXG_SENSE

TP_CORE_V1P05_S4

reserve the 0402 0.1u caps on reset for EMI.

VCC_SENSE

VCC_AXG_SENSE

VSS_SENSE

4

VCC_SENSE

VSS_SENSE

VSS_AXG_SENSE

VCC_AXG_SENSE

1 2

R440 100R2F-L1-GP-U

1 2

R434 100R2F-L1-GP-U

12

R448

0R0402-PAD-2-GP

CPU1G

P28

CORE_VCC_SENSE_P28

BB8

UNCORE_VNN_SENSE

N28

CORE_VSS_SENSE_N28

AD38

DRAM_VDD_S4_AD38

AF38

DRAM_VDD_S4_AF38

A48

DRAM_VDD_S4

AK38

DRAM_VDD_S4_AK38

AM38

DRAM_VDD_S4_AM38

AV41

DRAM_VDD_S4_AV41

AV42

DRAM_VDD_S4_AV42

BB46

DRAM_VDD_S4_BB46

AA27

CORE_VCC_S0IX_AA27

AA29

CORE_VCC_S0IX_AA29

AA30

CORE_VCC_S0IX_AA30

AC27

CORE_VCC_S0IX_AC27

AC29

CORE_VCC_S0IX_AC29

AC30

CORE_VCC_S0IX_AC30

AD27

CORE_VCC_S0IX_AD27

AD29

CORE_VCC_S0IX_AD29

AD30

CORE_VCC_S0IX_AD30

AF27

CORE_VCC_S0IX_AF27

AF29

CORE_VCC_S0IX_AF29

AG27

CORE_VCC_S0IX_AG27

AG29

CORE_VCC_S0IX_AG29

AG30

CORE_VCC_S0IX_AG30

P26

CORE_VCC_S0IX_P26

P27

CORE_VCC_S0IX_P27

U27

CORE_VCC_S0IX_U27

U29

CORE_VCC_S0IX_U29

V27

CORE_VCC_S0IX_V27

V29

CORE_VCC_S0IX_V29

V30

CORE_VCC_S0IX_V30

Y27

CORE_VCC_S0IX_Y27

Y29

CORE_VCC_S0IX_Y29

Y30

CORE_VCC_S0IX_Y30

AF30

TP_CORE_V1P05_S4

BAY-TRAIL-GP

(71.00BAY.C0U)

VCORE

C330

(R)

C284

(R)

C283

(R)

C312

(R)

1

1

1

1

VCC_AXG_SENSE45

2

SCD1U10V2KX-5GP

2

SCD1U10V2KX-5GP

2

SCD1U10V2KX-5GP

2

SCD1U10V2KX-5GP

BAY TRAIL-M/D SOC

3

VCC_AXG_SENSE

VNN_GFX

12

R485

100R2F-L1-GP-U

DRAM_VDD_S4_BD49

DRAM_VDD_S4_BD52

DRAM_VDD_S4_BD53

DRAM_VDD_S4_BF44

DRAM_VDD_S4_BG51

DRAM_VDD_S4_BJ48

DRAM_VDD_S4_C51

DRAM_VDD_S4_D44

DRAM_VDD_S4_F49

DRAM_VDD_S4_F52

DRAM_VDD_S4_F53

DRAM_VDD_S4_H46

DRAM_VDD_S4_M41

DRAM_VDD_S4_M42

DRAM_VDD_S4_V38

DRAM_VDD_S4_Y38

UNCORE_VNN_S3_AA24

UNCORE_VNN_S3_AC22

UNCORE_VNN_S3_AC24

UNCORE_VNN_S3_AD22

UNCORE_VNN_S3_AD24

UNCORE_VNN_S3_AF22

UNCORE_VNN_S3_AF24

UNCORE_VNN_S3_AG22

UNCORE_VNN_S3_AG24

UNCORE_VNN_S3_AJ22

UNCORE_VNN_S3_AJ24

UNCORE_VNN_S3_AK22

UNCORE_VNN_S3_AK24

UNCORE_VNN_S3_AK25

UNCORE_VNN_S3_AK27

UNCORE_VNN_S3_AK29

UNCORE_VNN_S3_AK30

UNCORE_VNN_S3_AK32

UNCORE_VNN_S3_AM22

TP2_CORE_VCC_S0IX

7 OF 13

DDR_VDDQ

BD49

BD52

BD53

BF44

BG51

BJ48

C51

D44

F49

F52

F53

H46

M41

M42

V38

Y38

VNN_GFX

AA24

AC22

AC24

AD22

AD24

AF22

AF24

AG22

AG24

AJ22

AJ24

AK22

AK24

AK25

AK27

AK29

AK30

AK32

AM22

TP2_CORE_VCC_S0IX

AA22

Title

Title

Title

CPU (VCC_CORE)

CPU (VCC_CORE)

CPU (VCC_CORE)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Rosa_BayTrail_DT

Rosa_BayTrail_DT

Rosa_BayTrail_DT

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

TP37

1

TPAD28

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

12F, 88, Hsin Tai Wu Rd

12F, 88, Hsin Tai Wu Rd

12F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

14 58Tuesday, April 15, 2014

14 58Tuesday, April 15, 2014

14 58Tuesday, April 15, 2014

1

A00

A00

A00

5

Vinafix.com

1D0V_S0

1D05V_S0

1D5V_S0

1D8V_S0

1D8V_S5

D D

1D35V_S0

V_3P0_BAT_VREG

V_3P3_A

VCC3

1D0V_S5

SB3V

C C

B B

A A

1D0V_S0 12,17,43,44,45

1D05V_S0 17,43

1D5V_S0 17,31,34,43

1D8V_S0 10,12,13,17,19,23,25,30,35,38,43,46

1D8V_S5 12,17,20,23,28,30,34,38,43,44,56,57

1D35V_S0 17,42,43

V_3P0_BAT_VREG 12

V_3P3_A 12,20,23,35,38,40,46,47,57

VCC3 12,13,17,20,21,23,24,25,30,31,34,35,36,38,39,46,56

1D0V_S5 17,44

SB3V 12,17,20,30,34,35,38,43,44,45,47,48,57

1D0V_S0

CRB1.05V

1D05V_S0

SB 1126 Allen modify

SB 1126 Allen modify

5

1D35V_S0

1D35V_CRT_S0

VGA_1P35V

R734

0R2J-2-GP

R735

0R2J-2-GP

Bogis 20131104

Add power solution for 1D35V_CRT_S0

1D05V_S0 POK

1D05V_RUNPWROK20,42,43

1D0V_S5

1D0V_S0

1D05V_S0

1D0V_S0

1D0V_S5

1D35V_S0

12

12

(R)

4

VGA_1P35V

R730 0R2J-2-GP

12

(R)

4

V32

BJ6

AD35

AF35

AF36

AA36

AJ36

AK35

AK36

Y35

Y36

AK19

AK21

AJ18

AM16

U22

V22

AN29

AN30

AF16

AF18

Y18

G1

AM21

AN21

AN18

AN19

AA33

AF21

AG21

V24

Y22

Y24

M14

U18

U19

AN25

Y19

C3

C5

B6

AC32

Y32

U36

AA25

AG32

V36

BD1

AF19

AG19

AJ19

AG18

AN16

U16

SB3V

(R)

12

PC2124

SC10U10V5KX-2GP

Hi:1.4V

Lo:0.4V

PWR_1D35V_CRT_EN

(R)

12

PC2123

SCD1U10V2KX-5GP

CPU1H

SVID_V1P0_S3_V32

VGA_V1P0_S3_BJ6

DRAM_V1P0_S0IX_AD35

DRAM_V1P0_S0IX_AF35

DRAM_V1P0_S0IX_AF36

DRAM_V1P0_S0IX_AA36

DRAM_V1P0_S0IX_AJ36

DRAM_V1P0_S0IX_AK35

DRAM_V1P0_S0IX_AK36

DRAM_V1P0_S0IX_Y35

DRAM_V1P0_S0IX_Y36

DDI_V1P0_S0IX_AK19

DDI_V1P0_S0IX_AK21

DDI_V1P0_S0IX_AJ18

DDI_V1P0_S0IX_AM16

UNCORE_V1P0_G3_U22

UNCORE_V1P0_G3_V22

VIS_V1P0_S0IX_AN29

VIS_V1P0_S0IX_AN30

UNCORE_V1P0_S3_AF16

UNCORE_V1P0_S3_AF18

UNCORE_V1P0_S3_Y18

UNCORE_V1P0_S3_G1

PCIE_V1P0_S3_AM21

PCIE_V1P0_S3_AN21

PCIE_GBE_SATA_V1P0_S3_AN18

SATA_V1P0_S3_AN19

CORE_V1P05_S3_AA33

UNCORE_V1P0_S0IX_AF21

UNCORE_V1P0_S0IX_AG21

VIS_V1P0_S0IX_V24

VIS_V1P0_S0IX_Y22

VIS_V1P0_S0IX_Y24

USB_V1P0_S3_M14

USB_V1P0_S3_U18

USB_V1P0_S3_U19

GPIO_V1P0_S3_AN25

USB3_V1P0_G3_Y19

USB3_V1P0_G3_C3

UNCORE_V1P0_G3_C5

UNCORE_V1P0_G3_B6

CORE_V1P0_S3_AC32

CORE_V1P0_S3_Y32

UNCORE_V1P35_S0IX_F4_U36

UNCORE_V1P35_S0IX_F5_AA25

UNCORE_V1P35_S0IX_F2_AG32

UNCORE_V1P35_S0IX_F3_V36

VGA_V1P35_S3_F1_BD1

UNCORE_V1P35_S0IX_F6

UNCORE_V1P35_S0IX_F1_AG19

ICLK_V1P35_S3_F1_AJ19

ICLK_V1P35_S3_F2

VSSA_AN16

USB_VSSA_U16

BAY-TRAIL-GP

(71.00BAY.C0U)

PU2101

AME8818DEEVADJZ-GP

1

2

(R)

BAY TRAIL-M/D SOC

IN

OUT

GND

EN3ADJ

3

DRAM_V1P35_S0IX_F1_AD36

HDA_LPE_V1P5V1P8_S3_AM32

UNCORE_V1P8_S3_AM30

UNCORE_V1P8_S3_AN32

LPC_V1P8V3P3_S3_AM27

SD3_V1P8V3P3_S3_AN27

USB_HSIC_V1P2_G3_V18

UNCORE_V1P8_G3_AA18

5

4

PWR_1D35V_CRT_ADJ

3

8 OF 13

UNCORE_V1P8_G3_U24

USB_V3P3_G3_N18

USB_V3P3_G3_P18

UNCORE_V1P8_S3_U38

VGA_V3P3_S3_AN24

PCU_V1P8_G3_V25

PCU_V3P3_G3_N22

VSS_AD16

VSS_AD18

RTC_VCC_P22

USB_V1P8_G3_N20

PMU_V1P8_G3_U25

CORE_V1P05_S3_AF33

CORE_V1P05_S3_AG33

CORE_V1P05_S3_AG35

CORE_V1P05_S3_U33

CORE_V1P05_S3_U35

CORE_V1P05_S3_V33

VSS_A3

VSS_A49

VSS_A5

VSS_A51

VSS_A52

VSS_A6

VSS_B2

VSS_B52

VSS_B53

VSS_BE1

VSS_BE53

VSS_BG1

VSS_BG53

VSS_BH1

VSS_BH2

VSS_BH52

VSS_BH53

VSS_BJ2

VSS_BJ3

VSS_BJ5

VSS_BJ49

VSS_BJ51

VSS_BJ52

VSS_C1

VSS_C53

VSS_E1

VSS_E53

RESERVED_F1

PCIE_V1P0_S3_AK18

PCIE_V1P0_S3_AM18

Vo(cal.)=1.36V

12

(R)

PR2124

7K68R2F-GP

R1

12

(R)

PR2125

20KR2F-L-GP

R2

AD36

AM32

AM30

AN32

AM27

U24

N18

P18

U38

AN24

V25

N22

SD3_V1P8V3P3_S3_AN27

AN27

AD16

AD18

USB_HSIC_V1P2_G3_V18

V18

AA18

P22

N20

U25

AF33

AG33

AG35

U33

U35

V33

A3

A49

A5

A51

A52

A6

B2

B52

B53

BE1

BE53

BG1

BG53

BH1

BH2

BH52

BH53

BJ2

BJ3

BJ5

BJ49

BJ51

BJ52

C1

C53

E1

E53

F1

AK18

AM18

(R)

12

PC2125

SC100P50V2JN-3GP

1D35V_S0

1D35V_CRT_S0