Page 1

1-A Quad-HBD (Quad-Half-Bridge Driver) TLE 4208

Overview

Features

• Driver for up to 3 motors

• Delivers up to 0.8 A continuous

• Optimized for DC motor management applications

• Very low current consumption

in stand-by (Inhibit) mode

• Low saturation voltage

• Output protected against short circuit

• Error flag diagnosis

• Overvoltage lockout and diagnosis

• Undervoltage lockout

• CMOS/TTL compatible inputs with hysteresis

• No crossover current

• Internal clamp diodes

• Overtemperature protection with hysteresis and diagnosis

• Enhanced power P-DSO-Package

; typ.1.2 V total @ 25 °C; 0.4 A

P-DSO-28-6

Type Ordering Code Package

TLE 4208 G Q67007-A9335 P-DSO-28-6

Description

The TLE 4208 is a fully protected Quad-Half-Bridge-Driver designed specially for

automotive and industrial motion control applications.

The part is built using the Siemens bipolar high voltage power technology DOPL.

In a cascade configuration up to three actuators (DC motors) can be connected between

the four half-bridges. These four half-bridges are configured as 2 dual-half-bridges,

which are supplied and controlled separately. Operation modes forward (cw), reverse

(ccw), brake and high impedance are invoked from a standard interface.

The standard enhanced power P-DSO-28 package meets the application requirements

and saves PCB-board space and costs.

Furthermore the built-in features like diagnosis, over- and undervoltage-lockout, shortcircuit protection, over-temperature protection and the very low quiescent current in

stand-by mode will open a wide range of automotive and industrial applications.

Semiconductor Group 1 1998-06-03

Page 2

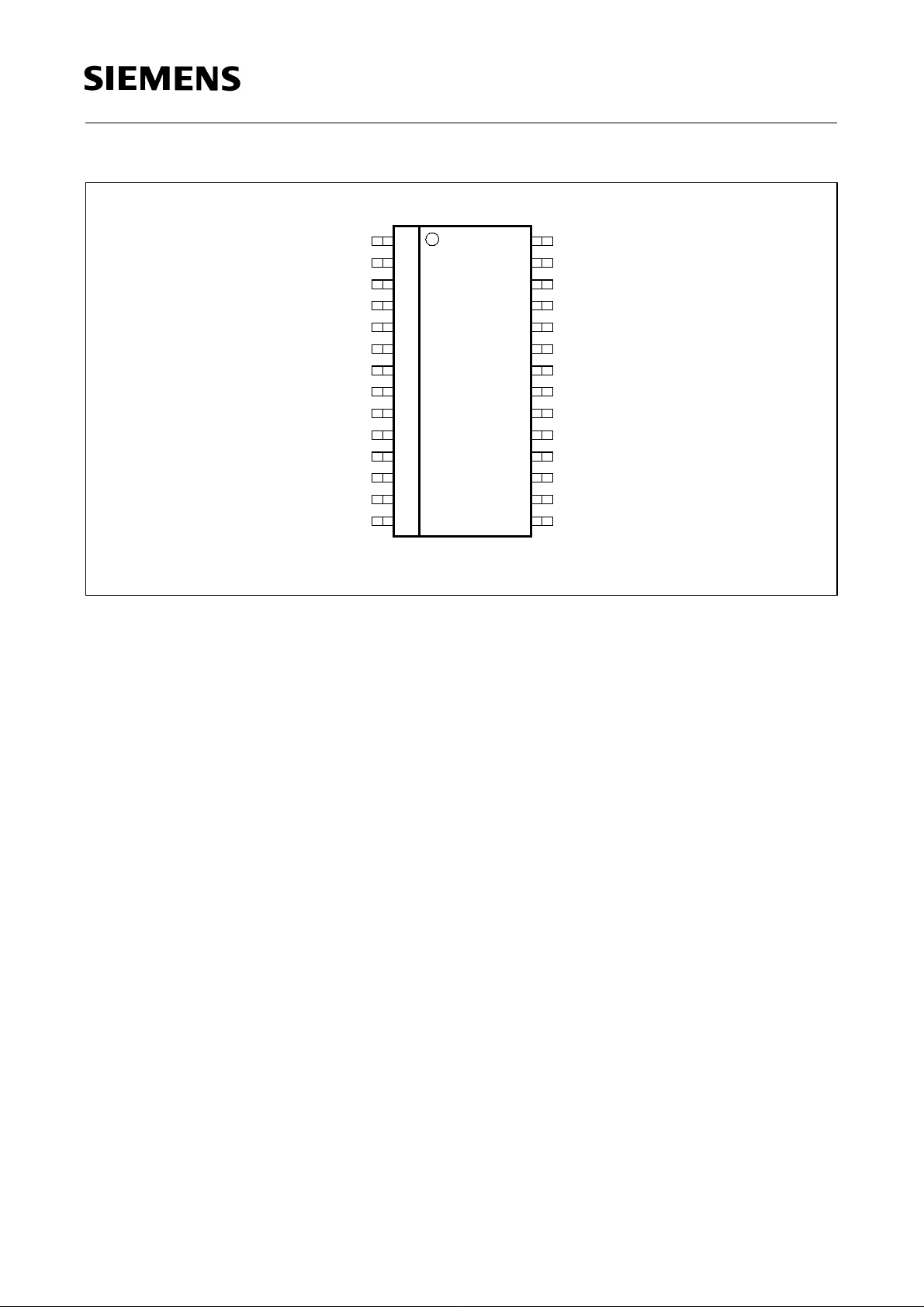

TLE 4208

GND

EF

IN1

N.C.

OUT1

GND

GND

GND

GND

OUT3

N.C.

IN3

INH

GND

128

2

12

3

4

5

6

7

TLE 4208 G

8

9

10

11

12

13

34

14

Figure 1 Pin Configuration (top view)

27

26

25

24

23

22

21

20

19

18

17

16

15

N.C.

INH

12

IN2

V

S12

OUT2

GND

GND

GND

GND

OUT4

V

S34

IN4

EF

34

N.C.

AEP02349

Semiconductor Group 2 1998-06-03

Page 3

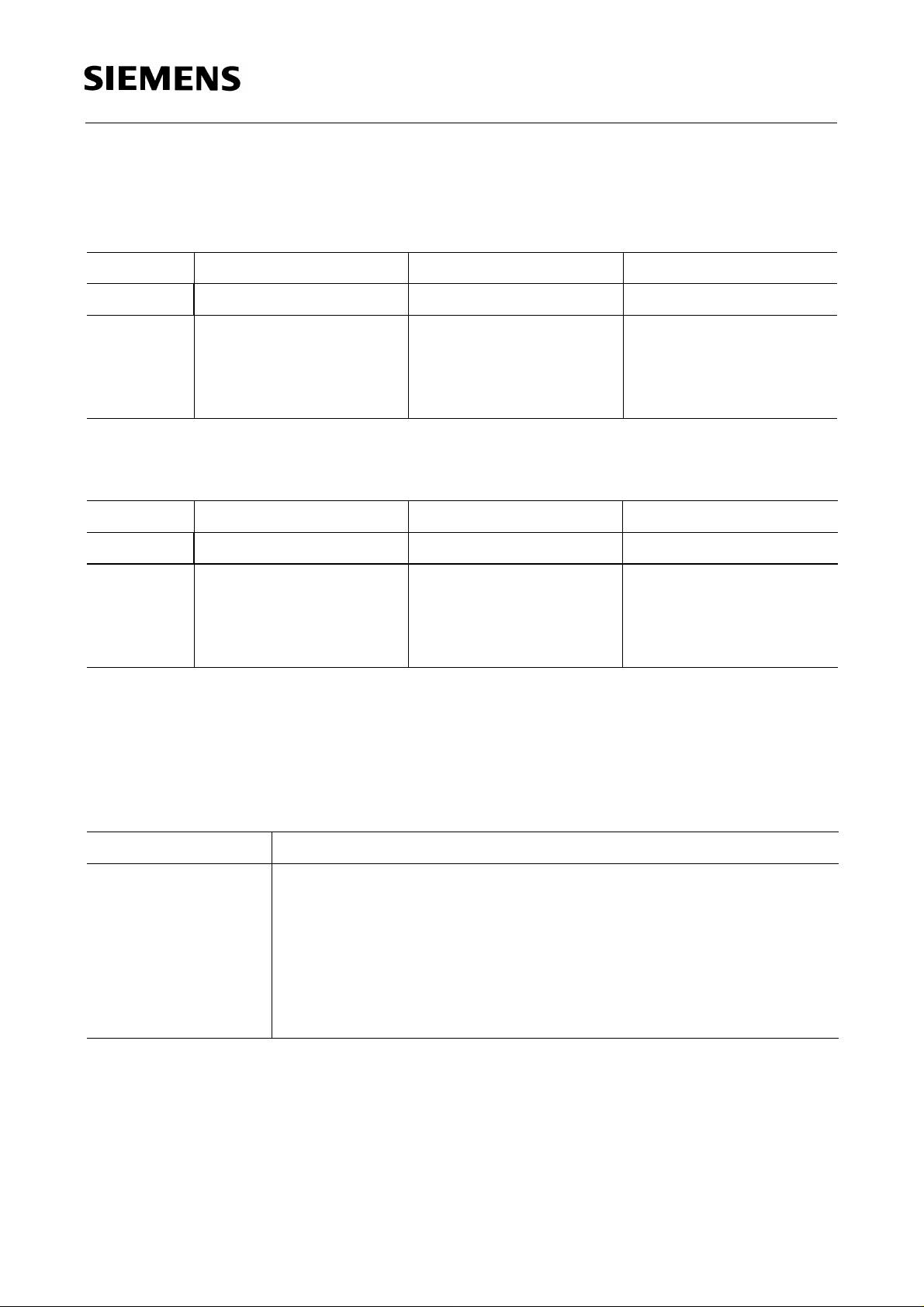

Pin Definitions and Functions

Pin No. Symbol Function

TLE 4208

1, 6, 7, 8, 9,

14, 20, 21,

GND Ground;

negative reference potential for blocking capacitor

22, 23

2EF

12

Error Flag output of half-bridges 1and 2;

open collector; low = error

3 IN1 Input channel of half-bridge 1;

controls OUT1

4, 11, 15, 28 N.C. Not connected

5 OUT1 Power output of half-bridge 1;

full short circuit protected; with integrated clamp diodes

10 OUT3 Power output of half-bridge 3;

full short-circuit protected; with integrated clamp diodes

12 IN3 Input channel of half-bridge 3;

controls OUT3

13 INH

34

Inhibit input of half-bridges 3 and 4;

low = half-bridges 3 and 4 in stand-by

16 EF

34

Error Flag output of half-bridges 3 and 4;

open collector; low = error

17 IN4 Input channel of half-bridge 4;

controls OUT4

18

V

S34

Power supply voltage of half-bridges 3 and 4;

positive reference potential for blocking capacitor

19 OUT4 Power output of half-bridge 4;

full short circuit protected; with integrated clamp diodes

24 OUT2 Power-output of half-bridge 2;

full short circuit protected; with integrated clamp diodes

25

V

S12

Power supply voltage of half-bridges 1 and 2;

positive reference potential for blocking capacitor

26 IN2 Input channel of half-bridge 2;

controls OUT2

27 INH

12

Inhibit input of half-bridges 1and 2;

low = half-bridges 1 and 2 in stand-by

Semiconductor Group 3 1998-06-03

Page 4

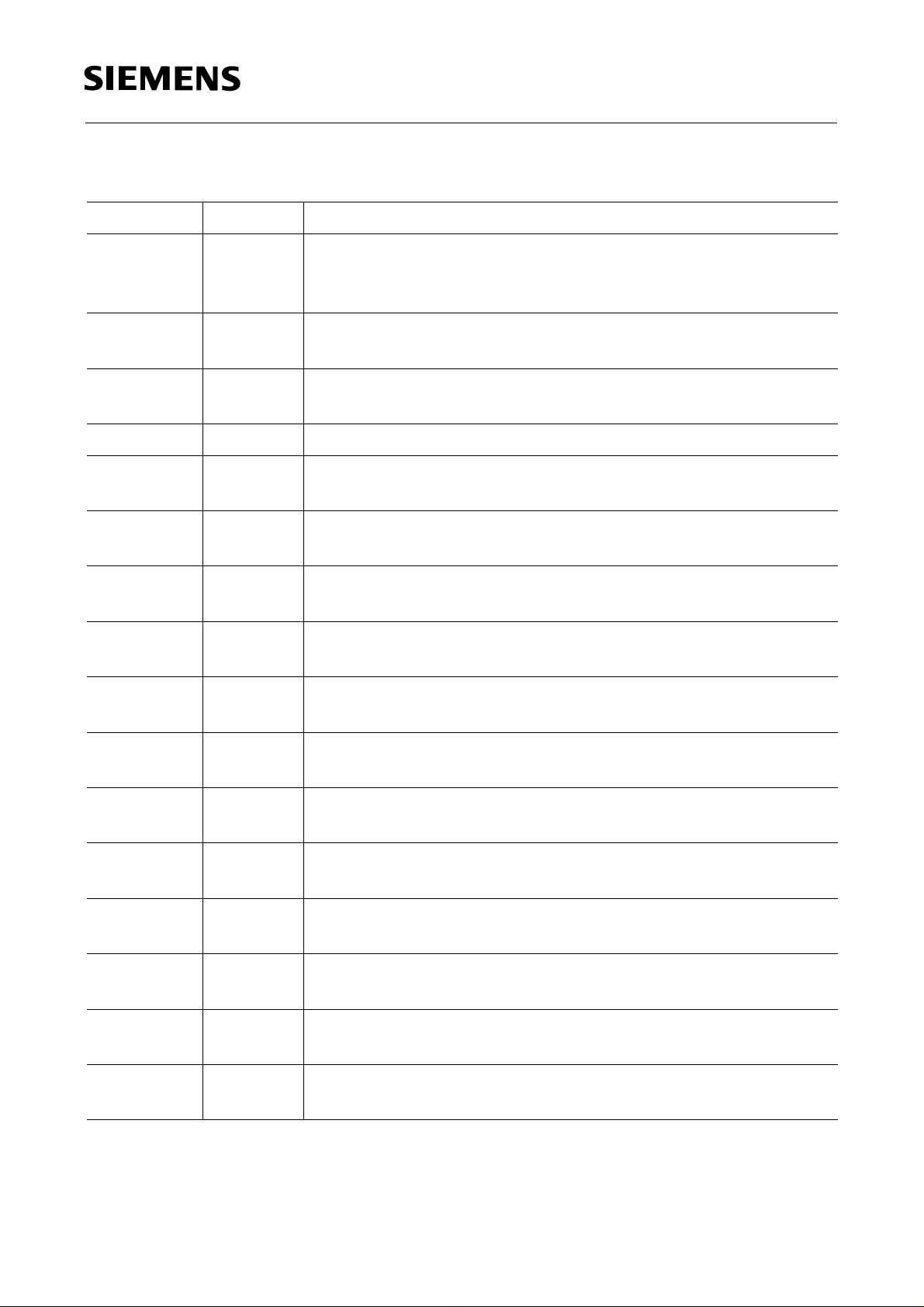

TLE 4208

INH

EF

INH

EF

12

12

IN1

IN2

34

34

IN3

IN4

27

2

3

26

13

16

12

17

INH

0

1

1

1

INH

0

1

1

1

1

Inhibit 1,2

Fault-Detection 1,2

IN1 IN2

12

0

0

1

1

Inhibit 3,4

Fault-Detection 3,4

34

IN3

IN4

X

0

0

1

1

0

1

0

11

X

0

1

0

1

TLE 4208 G

OUT1 OUT2

ZXZX

L

L

H

H

OUT3

Z

L

L

H

L

H

OUT4

Z

L

LH

H

H

L

H

DRV1

DRV2

DRV3

DRV4

25

5

24

1,6,7,8,

9,14,

20,21,

22,23

10

19

18

V

S12

OUT1

OUT2

GND

OUT3

OUT4

V

S34

AEB02350

Figure 2 Block Diagram

Semiconductor Group 4 1998-06-03

Page 5

Input Logic

Functional Truth Table of Halfbridge 1 and 2

TLE 4208

INH

12

IN1 IN2 OUT1 OUT2 Mode

0 X X Z Z Stand-By

1

1

1

1

0

0

1

1

0

1

0

1

L

L

H

H

L

H

L

H

Brake LL

CW

CCW

Brake HH

Note: Half-Bridge 1 and 2 connected to a full-bridge

Functional Truth Table of Half-Bridge 3 and 4

INH

34

IN3 IN4 OUT3 OUT4 Mode

0 X X Z Z Stand-By

1

1

1

1

0

0

1

1

0

1

0

1

L

L

H

H

L

H

L

H

Brake LL

CW

CCW

Brake HH

IN: 0 = Logic LOW OUT: Z = Output in tristate condition

1 = Logic HIGH L = Output in sink condition

X = don’t care H = Output in source condition

Note: Half-Bridge 3 and 4 connected to a full-bridge

Diagnosis

EF

1

0

0

1

1

0

0

12

EF

1

1

1

0

0

0

0

34

Error

no error

over temperature of half-bridge 1 and 2 or

over voltage of half-bridge 1 and 2

over temperature of half-bridge 3 and 4 or

over voltage of half-bridge 3 and 4

over temperature of all half-bridges or

over voltage of all half-bridges

Semiconductor Group 5 1998-06-03

Page 6

Electrical Characteristics

Absolute Maximum Ratings

Parameter Symbol Limit Values Unit Remarks

min. max.

Voltages

V

Supply voltage

V

S12

S34

,

– 0.3 45 V –

TLE 4208

Supply voltage

Logic input voltages

(IN1; IN2; INH

IN3; IN4; INH

34

12

;

)

Logic output voltage

; EF34)

(EF

12

Currents

Output current (cont.)

Output current (peak)

Output current (diode)

Output current (EF)

Temperatures

Junction temperature

V

S12

V

S34

V

I

V

EF12

V

EF34

I

OUT1-4

I

OUT1-4

I

OUT1-4

I

EF12-34

T

j

,

– 1 – V t < 0.5 s;

– 5 20 V 0V < V

,

– 0.3 20 V 0 V < V

I

S12

, I

S34

S12

S12

> – 2 A

, V

S34

, V

S34

< 45 V

< 45 V

– – A internally limited

– – A internally limited

–1 1 A –

–2 5 mA –

– 40 150 °C–

Storage temperature

T

stg

– 50 150 °C–

Thermal Resistances

Junction pin

Junction ambient

R

R

thj-pin

thjA

– 25 K/W measured to pin 7

– 65 K/W –

Note: Maximum ratings are absolute ratings; exceeding any one of these values may

cause irreversible damage to the integrated circuit.

Semiconductor Group 6 1998-06-03

Page 7

Operating Range

Parameter Symbol Limit Values Unit Remarks

min. max.

TLE 4208

Supply voltage

Supply voltage increasing V

Supply voltage decreasing

Logic input voltages

(IN1; IN2; INH

IN3; IN4; INH

34

12

;

)

Junction temperature

V

V

V

V

V

V

T

S12

S34

S12

S34

S12

S34

I

j

,

,

,

V

UV OFF

18 V After V

– 0.3 V

– 0.3 V

UV ON

UV OFF

rising

above

S12,VS34

V

UV ON

V Outputs in tristate

V Outputs in tristate

– 2 18 V –

– 40 150 °C–

Note: In the operating range the functions given in the circuit description are fulfilled.

Semiconductor Group 7 1998-06-03

Page 8

TLE 4208

Electrical Characteristics

V

8 V <

S12

= V

unless otherwise specified

Parameter Symbol Limit Values Unit Test Condition

Current Consumption

INH

= INH34 = LOW

12

< 18 V; INH12 = INH34 = HIGH; I

S34

min. typ. max.

OUT1-4

= 0 A; – 40 °C < Tj < 150 °C;

Quiescent current

Quiescent current I

INH

= HIGH and INH34 = LOW or INH12 = LOW and INH34 = HIGH

12

Supply current

Supply current

Supply current

I

I

I

I

S

S

S12

S12

S12

, I

, I

, I

Over- and Under Voltage Lockout

UV Switch ON voltage

UV Switch OFF voltage

V

UV ON

V

UV OFF

– – 100 µA IS = I

–2040µA IS = I

–1020mA–

S34

– – 30 mA I

S34

– – 50 mA I

S34

– 6.5 7.5 V V

56–VV

+ I

S12

+ I

S12

V

= V

S12

T

= 25 °C

j

OUT1/3

I

OUT2/4

OUT1/3

I

OUT2/4

S12

S34

= 0.4 A

= – 0.4 A

= 0.8 A

= – 0.8 A

, V

S34

increasing

S12,VS34

decreasing

S34

;

S34

= 13.2 V;

UV ON/OFF hysteresis

OV Switch OFF voltage V

V

UV HY

OV OFF

– 0.5 – V V

–2024VV

– V

UV ON

S12,VS34

UV OFF

increasing

OV Switch ON voltage

V

OV ON

18 19.5 – V V

S12,VS34

decreasing

OV ON/OFF hysteresis

Semiconductor Group 8 1998-06-03

V

OV HY

– 0.5 – V V

OV OFF

– V

OV ON

Page 9

TLE 4208

Electrical Characteristics (cont’d)

V

8 V <

S12

= V

unless otherwise specified

Parameter Symbol Limit Values Unit Test Condition

Outputs OUT1; OUT2; OUT 3; OUT 4

Saturation Voltages

< 18 V; INH12 = INH34 = HIGH; I

S34

min. typ. max.

= 0 A; – 40 °C < Tj < 150 °C;

OUT1-4

Source (upper)

I

OUT12

, I

OUT34

= – 0.2 A

Source (upper)

I

OUT12

, I

OUT34

= – 0.4 A

Sink (upper)

I

OUT12

, I

OUT34

= – 0.8 A

Sink (lower)

I

OUT12

, I

OUT34

= 0.2 A

Sink (lower)

I

OUT12

, I

OUT34

= 0.4 A

Sink (lower)

I

OUT12

, I

OUT34

= 0.8 A

Total Drop

I

OUT12

, I

OUT34

= 0.2 A

Total Drop

I

OUT12

, I

OUT34

= 0.4 A

Total Drop

I

OUT12

, I

OUT34

= 0.8 A

V

V

V

V

V

V

V

V

V

SAT U

SAT U

SAT U

SAT L

SAT L

SAT L

SAT

SAT

SAT

– 0.85 1.15 V Tj = 25 °C

– 0.90 1.20 V Tj = 25 °C

– 1.10 1.50 V Tj = 25 °C

– 0.15 0.23 V Tj = 25 °C

– 0.25 0.40 V Tj = 25 °C

– 0.45 0.75 V Tj = 25 °C

V

V

V

SAT

SAT

SAT

= V

= V

= V

SAT U

SAT U

SAT U

– 1 1.4 V

– 1.2 1.7 V

– 1.6 2.5 V

+ V

+ V

+ V

SAT L

SAT L

SAT L

Clamp Diodes

Forward voltage; upper

Upper leakage current

Forward voltage; lower V

Notes see page 11.

Semiconductor Group 9 1998-06-03

V

I

FU

LKU

FL

– 1 1.5 V IF = 0.4 A

––5mAIF = 0.4 A

– 0.9 1.4 V IF = 0.4 A

1)

Page 10

Electrical Characteristics (cont’d)

TLE 4208

8 V <

V

S12

= V

< 18 V; INH12 = INH34 = HIGH; I

S34

OUT1-4

= 0 A; – 40 °C < Tj < 150 °C;

unless otherwise specified

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Input Interface

Logic Inputs IN1; IN2; IN3; IN4

H-input voltage

L-input voltage

Hysteresis of input voltage

H-input current

L-input current

Logic Inputs INH12; INH

V

V

V

I

I

34

H-input voltage V

IH

IL

IHY

IH

IL

IH

– 2.0 3.0 V –

1.0 1.5 – V –

– 0.5 – V –

–2 – 10 µA VI = 5 V

– 100 – 20 – 5 µA VI = 0 V

– 2.7 3.5 V –

L-input voltage

Hysteresis of input voltage

H-input current

L-input current

Error-Flags EF12; EF

34

V

V

I

I

L-output voltage level V

Leakage current

I

IL

IHY

IH

IL

EFL

EFLK

1.0 2.0 – V –

– 0.7 – V –

– 100 250 µA V

–10 – 10 µA V

INH

INH

= 5 V

= 0 V

– 0.2 0.4 V IEF = 2 mA

– –10µA 0 V < VEF < 7 V

Semiconductor Group 10 1998-06-03

Page 11

TLE 4208

Electrical Characteristics (cont’d)

V

8 V <

S12

= V

unless otherwise specified

Parameter Symbol Limit Values Unit Test Condition

Thermal Shutdown

< 18 V; INH12 = INH34 = HIGH; I

S34

min. typ. max.

= 0 A; – 40 °C < Tj < 150 °C;

OUT1-4

Thermal shutdown junction

T

jSD

150 175 200 °C–

temperature

Thermal switch-on junction

T

jSO

120 – 170 °C–

temperature

Temperature hysteresis ∆

1)

Guaranteed by design.

T –30–K–

Note: The listed characteristics are ensured over the operating range of the integrated

circuit. Typical characteristics specify mean values expected over the production

spread. If not otherwise specified, typical characteristics apply at

T

= 25°C and

A

the given supply voltage.

Semiconductor Group 11 1998-06-03

Page 12

Watchdog In

Watchdog Out

Reset Out

Q

8

1

14

9

TLE 4278 G

3,4,5,10,11,12 76

Input

13

Watchdog

Adjust

2

TLE 4208

= 12 V

V

S

D1

1N4001

R

GNDD

QA

R

Ω

10 k

10 k

V

RWDIWDO

CC

INH12

QB

Ω

C

Q

22 F

µ

4

C

D

100 nF

Inhibit 1,2

Reset

Adjust

TLE 4208 G

R

WA

100 k

Ω

C

Ι

100 nF

V

28

C

S

22 F

µ

S12

DRV1

EF12

25

24

IN1

5

IN2

µ

C

INH34

18

Fault-Detection 1,2

INH12

IN1 IN2

0

0L0

1

0

1

1

1

0

1

1H11

Inhibit 3,4

OUT1 OUT2

ZXZX

L

H

L

L

H

H

DRV2

DRV3

27

1

6,7,8,9,

20,21,

22,23

OUT1

M1

OUT2

GND

EF34

IN3

IN4

11

10

19

Fault-Detection 3,4

INH34

IN3

IN4

0

1

1

1

1

X

X

0

0

0

1

0

1

1

1

OUT4

OUT3

Z

Z

L

L

LH

H

L

H

H

DRV4

13

15

14

OUT3

M2

OUT4

V

S34

AES02351

Figure 3 Application Circuit 1 (Device is used as Dual-Full-Bridge-Driver)

Semiconductor Group 12 1998-06-03

Page 13

Diagrams

TLE 4208

Quiescent current

over Temperature

50

µ

A

Ι

S

40

30

20

10

0

-50 0

V

S

V

S

V

S

I

S

= 18 V

= 13.2 V

= 8 V

AED02352

100

T

j

Saturation Voltage of Source V

SAT U

over Temperature

1500

V

SAT U

1250

V

S

= 14 V

Ι

OUT

= 800 mA

mV

1000

750

Ι

Ι

OUT

OUT

= 400 mA

= 200 mA

500

250

0

15050

C

-50

0 50 100 150

AED02308

˚C

T

j

Saturation Voltage of Sink

over Temperature

1000

V

SAT L

750

500

250

mV

0

-50

= 14 V

V

S

= 800 mA

Ι

OUT

= 400 mA

Ι

OUT

= 200 mA

Ι

OUT

0 50 100 150

V

SAT L

AED02309

˚C

T

Total Drop at outputs

V

SAT

over Temperature

2000

V

SAT

= 14 V

V

S

mV

= 800 mA

Ι

OUT

1500

= 400 mA

Ι

OUT

= 200 mA

Ι

1000

OUT

500

0

-50

j

0 50 100 150

AED02310

˚C

T

j

Semiconductor Group 13 1998-06-03

Page 14

Package Outlines

P-DSO-28-6

(Plastic Dual Small Outline Package)

1.27

+0.15

0.35

2)

0.2 28x

1528

-0.1

0.2

-0.2

2.45

0.1

2.65 max

0.35 x 45˚

7.6

-0.2

0.4

10.3

1)

+0.8

±0.3

+0.09

0.23

TLE 4208

8˚ max

114

18.1

-0.4

1)

Index Marking

1) Does not include plastic or metal protrusions of 0.15 max rer side

2) Does not include dambar protrusion of 0.05 max per side

GPS05123

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

SMD = Surface Mounted Device

Dimensions in mm

Semiconductor Group 14 1998-06-03

Loading...

Loading...