Page 1

1-A DC Motor Driver for Servo Driver Applications

Overview

Features

• Optimized for headlight beam control applic atio ns

• Current-peak-blanking (no electrolytic capacitor at

• Delivers up to 0.8 A continuous

• Low saturation voltage

; typ.1.2 V total @ 25 °C; 0.4 A

• Output protected against short circuit

• Overtemperature protection with hysteresis

• Over- and undervoltage lockout

• No crossover current

• Internal clamp diodes

• Enhanced power packages

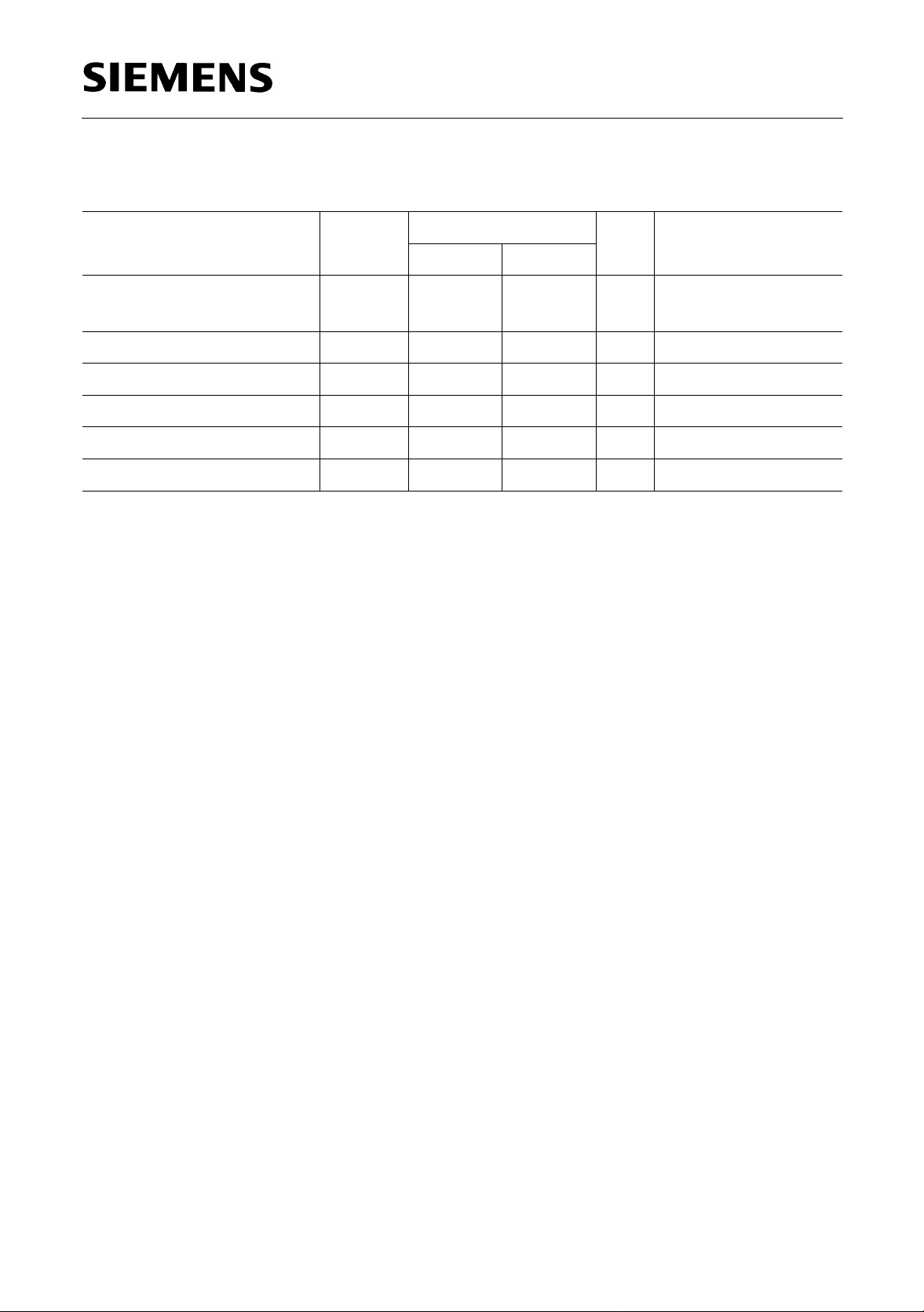

Type Ordering Code Package

V

)

S

TLE 4206

P-DIP-16-5

TLE 4206 Q67000-A9303 P-DIP-16-5

TLE 4206 G Q67006-A9299 P-DSO-14-4

P-DSO-14-4

Description

The TLE 4206 is a fully p rotected H-Bridge Driv er designed speci fically for automot ive

headlight beam control and industrial servo control applications.

The part is built using the Siemens bipolar high voltage power technology DOPL.

The standard enhanced power P-DSO-14 package meets the app licatio n requireme nts

and saves PCB-board space and costs. A P-DIP-16 package is also available.

The servo-loop-parameter pos.- and neg. Hysteresis, pos.- and neg. deadband and

angle-amplification are programmable with external resitors.

An internal window-comp arator controls the input line. In the case of a fault condition,

like short circuit to GND, short circuit to supply-voltage, and broken wire, the

TLE 4206 stops the motor immediately (brake condition).

V

The “programable current-peak-blank ing” d isa bles the s ervo - loop durin g the

voltage

S

drop caused by the stall current spi ke. So there is no need of an electrolytic blocking

V

capacitor at the

-terminal.

S

Furthermore the built in features like over- and undervoltage-lockout, short-circuitprotection and over-tempera ture-protection will open a wide range of automotiv e- and

industrial applications.

Semiconductor Group 1 1998-02-01

Page 2

TLE 4206

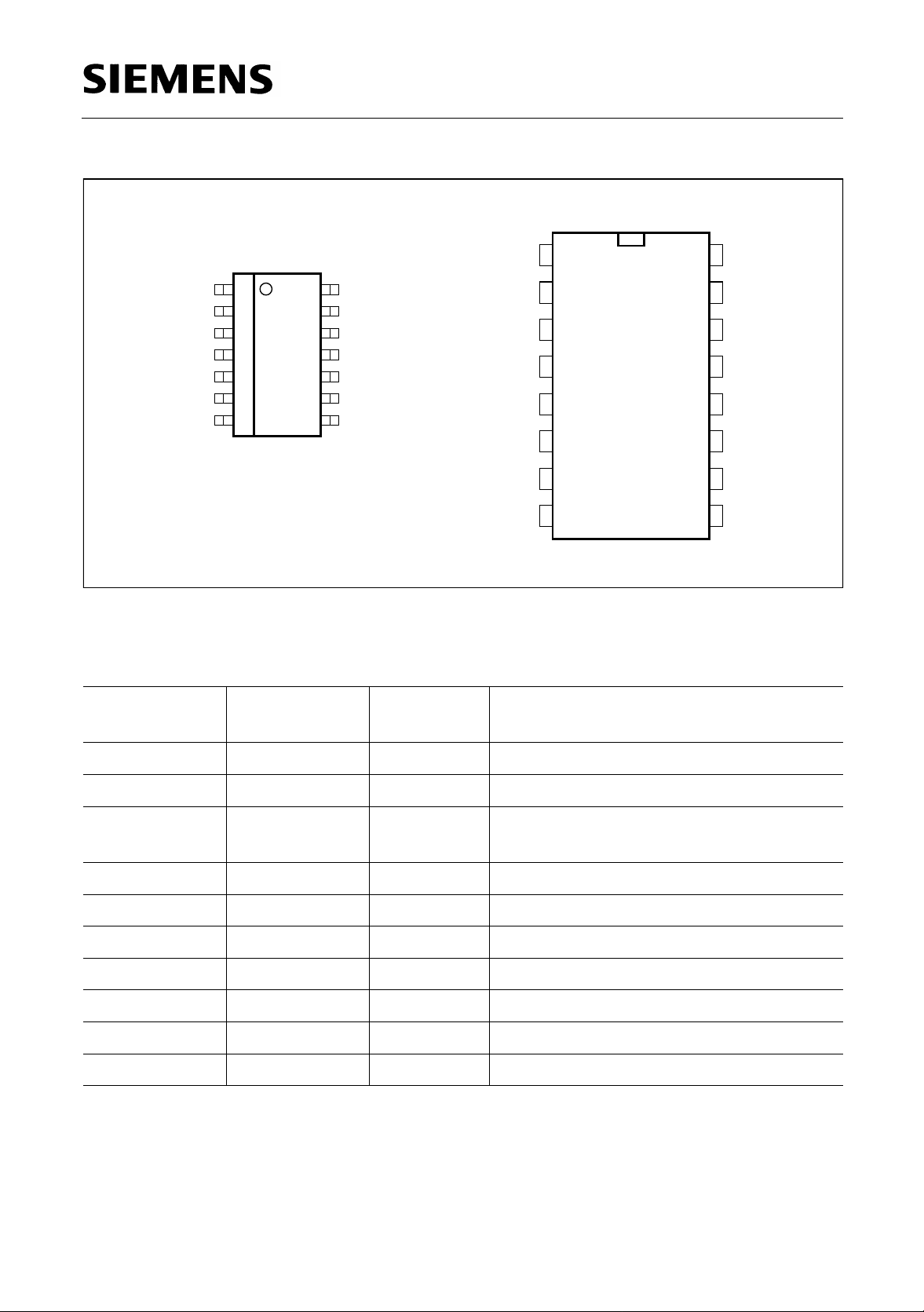

P-DSO-14-4 P-DIP-16-5

FB

HYST

GND

GND

GND

OUT1

CPB

1

2

3

4

5

6

7

14

13

12

11

10

9

8

AEP02261

REF

RANGE

GND

GND

GND

OUT2

V

S

Figure 1 Pin Configuration (top view)

Pin Definitions and Functions

Pin No.

P-DSO-14-4

Pin No.

P-DIP-16-5

Symbol Function

FB

1

HYST

N.C.

GND

GND GND

GND GND

OUT1

CPB

2

3

4

5

6

7

8

AEP02262

16

15

14

13

12

11

10

9

REF

RANGE

N.C.

GND

OUT2

V

S

1 1 FB Feedback Input

2 2 HYST Hysteresis I/O

3, 4, 5,

10, 11, 12

4, 5, 6,

11, 12, 13

GND Ground

6 7 OUT1 Power Output 1

78CPB Current Peak Blanking Input

89

V

S

Power Supply Voltage

9 10 OUT2 Power Output 2

13 15 RANGE Range Input

14 16 REF Reference Input

3, 14 N.C. Not connected

Semiconductor Group 2 1998-02-01

Page 3

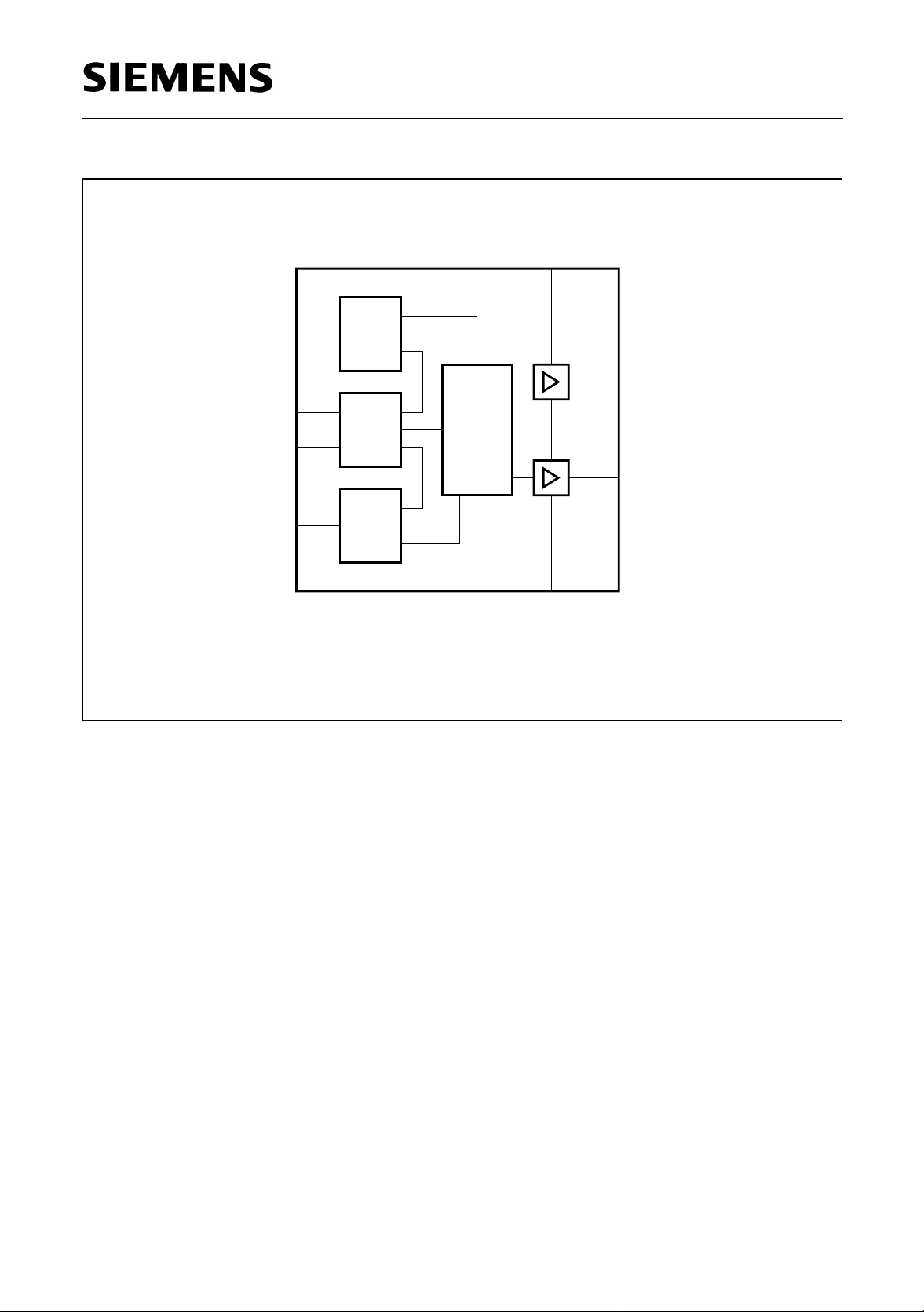

TLE 4206

V

S

TLE 4206G

8

RANGE

REF

FB

HYST

13

14

1

2

Range-

AMP

Servo-

AMP

Hyst-

AMP

Protection

and Logic

HalfBridge

HalfBridge

6

OUT1

9

OUT2

3,4,5,

7

CPB

10,11,12

GND

AEB02258

Figure 2 Block Diagram (Pin numbers are valid for TLE 4206 G in P-DSO-14-4)

Semiconductor Group 3 1998-02-01

Page 4

Absolute Maximum Ratings

Parameter Symbol Limit Values Unit Remarks

min. max.

Voltages

TLE 4206

Supply voltage

Supply voltage

Logic input voltages

(FB, REF, RANGE, HYST,

CPB)

Currents

Output current (OUT1, OUT2)

Output current (Diode)

Input current

(FB, REF, RANGE, HYST)

Temperatures

Junction temperature

Storage temperature

V

V

V

I

OUT

I

OUT

I

IN

T

T

S

S

I

j

stg

– 0.3 45 V –

– 1 – V t < 0.5 s; IS > – 2 A

– 0.3 20 V –

– – A internally limited

–1 1 A –

– 2

– 6

2

6

mA

mA

t < 2 ms; t/T < 0.1

– 40 150 °C–

– 50 150 °C–

Thermal Resistances

Junction pin

R

thj-pin

– 25 K/W measured to pin 5

(P-DSO-14-4)

Junction ambient

R

thjA

–65K/W–

(P-DSO-14-4)

Junction pin

R

thj-pin

– 15 K/W measured to pin 5

(P-DSO-16-5)

Junction ambient

R

thjA

–60K/W–

(P-DSO-16-5)

Note: Maximum ratings are abso lute ratings; exceeding any one of thes e values may

cause irreversible damage to the integrated circuit.

Semiconductor Group 4 1998-02-01

Page 5

Operating Range

Parameter Symbol Limit Values Unit Remarks

min. max.

TLE 4206

Supply voltage

Supply voltage increasing

Supply voltage decreasing

Output current

Input current (FB, REF)

Junction temperature

V

S

V

S

V

S

I

OUT1-2

I

IN

T

j

818VAfter V

above

– 0.3 V

– 0.3 V

UV ON

UV OFF

V Outputs in tristate

V Outputs in tristate

– 0.8 0.8 A –

– 50 500 µA–

– 40 150 °C–

rising

S

V

UV ON

Semiconductor Group 5 1998-02-01

Page 6

TLE 4206

Electrical Characteristics

V

8 V <

< 18 V; I

S

OUT1-2

(unless otherwise specified)

Parameter Symbol Limit Values Unit Test Condition

Current Consumption

= 0 A; – 40 °C < Tj < 150 °C

min. typ. max.

Supply current

Supply current

Supply current

I

S

I

S

I

S

Over- and Under Voltage Lockout

UV Switch ON voltage

UV Switch OFF voltage

UV ON/OFF Hysteresis

OV Switch OFF voltage V

OV Switch ON voltage

OV ON/OFF Hysteresis

V

UV ON

V

UV OFF

V

UVHY

OV OFF

V

OV ON

V

OVHY

–1220mA–

–2030mAI

–3050mAI

OUT1

I

OUT2

OUT1

I

OUT2

= 0.4 A

= – 0.4 A

= 0.8 A

= – 0.8 A

–7.48VVS increasing

66.9–VVS decreasing

–0.5–VV

UV ON

– V

UV OFF

–20.523VVS increasing

17.5 20 – V VS decreasing

–0.5–VV

OV OFF

– V

OV ON

Semiconductor Group 6 1998-02-01

Page 7

TLE 4206

Electrical Characteristics (cont’d)

8 V <

(unless otherwise specified)

Parameter Symbol Limit Values Unit Test Condition

Outputs OUT1-2

Saturation Voltages

V

< 18 V; I

S

OUT1-2

= 0 A; – 40 °C < Tj < 150 °C

min. typ. max.

Source (upper )

I

= – 0.2 A

OUT

Source (upper )

I

= – 0.4 A

OUT

Sink (upper)

I

= – 0.8 A

OUT

Sink (lower)

I

= 0.2 A

OUT

Sink (lower)

I

= 0.4 A

OUT

Sink (lower)

I

= 0.8 A

OUT

Total drop

Total drop I

Total drop I

I

= 0.2 A V

OUT

= 0.4 A V

OUT

= 0.8 A V

OUT

V

SAT U

V

SAT U

V

SAT U

V

SAT L

V

SAT L

V

SAT L

SAT

SAT

SAT

– 0.85 1.15 V Tj = 25 °C

– 0.90 1.20 V Tj = 25 °C

– 1.10 1.50 V Tj = 25 °C

– 0.15 0.23 V Tj = 25 °C

– 0.25 0.40 V Tj = 25 °C

– 0.45 0.75 V Tj = 25 °C

V

V

V

SAT

SAT

SAT

= V

= V

= V

SAT U

SAT U

SAT U

–1.01.4V

–1.21.7V

–1.62.5V

+ V

+ V

+ V

SAT L

SAT L

SAT L

Clamp Diodes

Forward voltage; upper

Upper leakage current

Forward voltage; lower

Semiconductor Group 7 1998-02-01

V

I

V

FU

LKU

FL

–11.5VIF = 0.4 A

––5mAIF = 0.4 A

–0.91.4VIF = 0.4 A

Page 8

TLE 4206

Electrical Characteristics (cont’d)

V

8 V <

< 18 V; I

S

OUT1-2

(unless otherwise specified)

Parameter Symbol Limit Values Unit Test Condition

Input-Interface

Input REF

= 0 A; – 40 °C < Tj < 150 °C

min. typ. max.

Quiescent voltage

Input resistance

Input FB

Quiescent voltage

Input resistance

Input/Output HYST

Current Amplification

A

HYST

=

I

/ (I

HYST

REF

Current Offset

V

REFq

R

REF

V

FBq

R

FB

A

HYST

–

I

)

FB

–200–mVI

–6–kΩ 0 V < V

REF

= 0 µA

REF

–200–mVIFB = 0 µA

–6–kΩ 0 V < V

FB

0.8 0.95 1.1 − –20 µA < I

< – 10 µA;

10 µA <

I

HYST

< 0.5 V

< 0.5 V

HYST

< 20 µA;

I

=250µA

REF

I

HYSTIO

–2 0.5 3 µA

V

IREF

V

= VS / 2

HYST

= IFB =250µA

= VS / 2

HYST

V

V

V

V

V

/ V

HYH

/ V

DBH

/ V

DBL

/ V

HYL

/ VS345%(V

HYW

/ VS0.4 0.8 1.2 % (V

DBW

Threshold voltage High

Deadband voltage High

Deadband voltage Low

Threshold voltage Low

Hysteresis Window

Deadband Window V

Semiconductor Group 8 1998-02-01

–52–%–

S

–50.4–%–

S

–49.6–%–

S

–48–%–

S

HYH

DBH

– V

– V

HYL

DBL

)/ V

)/ V

S

S

Page 9

TLE 4206

Electrical Characteristics (cont’d)

8 V <

(unless otherwise specified)

Parameter Symbol Limit Values Unit Test Condition

Input RANGE

V

< 18 V; I

S

OUT1-2

= 0 A; – 40 °C < Tj < 150 °C

min. typ. max.

Input current

Switch-OFF voltage High V

Switch-OFF voltage Low V

I

RANGE

OFFH

OFFL

Input CPB (Current Peak Blanking)

Charge current

Low voltage

High voltage threshold V

Clamp voltage V

Blanking time t

I

CPBCH

V

CPBL

CPBH

CPBC

CPB

Thermal Shutdown

Thermal shutdown junction

T

jSD

temperature

– 1 – 1 µA0V <V

– 100 0 100 mV refer to V

RANGE

S

300 400 500 mV refer to GND

–6.5–µA V

–20100mVV

55.76.5VV

–6.2–VV

–40–msC

HYL

V

CPB

HYL

< V

HYL

HYL

CPB

> V

= 0 V

< V

HYH

> V

> V

= 47 nF

HYST

HYST

HYST

HYST

150 175 200 °C–

< V

;

S

Thermal switch-on junction

T

jSO

120 – 170 °C–

temperature

Temperature hysteresis ∆

Semiconductor Group 9 1998-02-01

T –30–K–

Page 10

TLE 4206

V

+

B

V

+

B

R

REF

1 kΩ

V

REFIN

GND

R

FB

R

R

Ω50 k

R

REF

50 k

Ω

50 kΩ

R

HYH

100 kΩ

RANGE

REF 14

FB 1

HYST 2

R

HYL

Ω

100 k

13

Range-

AMP

Servo-

AMP

Hyst-

AMP

1N4001

TLE 4206G

Protection

and Logic

7

CPB

C

CPB

47 nF

Dr

C

S

470 nF

Dz

36 V

V

S

8

HalfBridge

6

HalfBridge

9

3,4,5,

10,11,12

GND

OUT1

OUT2

M

P

FB

1 kΩ

AES02259

Figure 3 Application Circuit (Pin numbers are valid for TLE 4206G in P-DSO-14-4)

Semiconductor Group 10 1998-02-01

Page 11

V

V

Motor

=

OUT1

-

V

OUT2

-2.0% -0.4%

TLE 4206

Motor

Status

Turn

CW

V(V

-)/

V

FBREF

S

2.0%0.4%

Brake

Turn

CCW

DBW

DBL DBH

HYW

HYL HYH

Expressions:

= Hysteresis

HY

DeadbandDB=

HighH=

LowL=

WindowW=

Figure 4 Hysteresis, Phaselag and Deadband-Definitions

AED02260

Semiconductor Group 11 1998-02-01

Page 12

V

OFFH

V

HYH

V

DBH

V

DBL

V

HYL

V

OFFL

V

CPBC

V

CPBH

V

V

V

t

)

S(

t

FB(

REF(t)

TLE 4206

)

t

Start-Command

Stop-Command

CPB(V)

t

V

CPBL

V

OUT2

t

CPB

H

L

V

OUT1

Brake CCW

H

L

Testconditions:

V

= ; no revers polarity voltage diode

S

RR

HYH

RR

REF=FB

Figure 5 Timing and Phaselag

t

CPB

Brake

CW Brake CW

V

B

=

= Ω;

HYL

100 k

= Ω50 k

t

CPB

Brake

CCW

Blanking-Time

t

CPB

Motor Status

AED02314

t

t

t

Semiconductor Group 12 1998-02-01

Page 13

Package Outlines

P-DSO-14-4

(Plastic Dual Small Outline Package)

-0.1

0.2

-0.2

1.45

4

-0.2

1.75 max

TLE 4206

0.35 x 45˚

1)

+0.06

0.19

0.35

1.27

+0.15

2)

0.1

0.2 14x

±0.2

6

0.4

+0.8

8˚ max.

14 8

17

8.75

-0.2

1)

Index Marking

1) Does not include plastic or metal protrusion of 0.15 max. per side

2) Does not include dambar protrusion of 0.05 max. per side

GPS05093

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

SMD = Surface Mounted Device

Dimensions in mm

Semiconductor Group 13 1998-02-01

Page 14

P-DIP-16-5

(Plastic Dual In-line Package)

1.7 max

0.25

16x

0.46

2.54

±0.1

0.38 min

3.25 min

4.37 max

7.87

8.9

±0.38

±1

0.25

6.35

+0.1

±0.25

TLE 4206

1)

16

1

19.05

±0.25

9

8

1)

Index Marking

1) Does not include plastic or metal protrusion of 0.25max per side

GPD05585

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

Dimensions in mm

Semiconductor Group 14 1998-02-01

Loading...

Loading...