Page 1

1.0 GENERAL DESCRIPTION

STMicroelectronics’ STLC1502 is a high performance VoIP processor specially targeted for the time

effective design of I P-Phones and analog gateway

applications bundled with a comprehensive embedded software solution.

When used in the Enterprise LAN IP Phone space,

this device enables t he augmentation and replacement of traditional telephone systems with network

based communications systems running over local

and wide area IP networks. To design an IP phone,

the only other parts required will be an analog interface, some optional Flash memory for upgradable

software and Fast Ethernet physical layer devices.

The ST complete IP Phone reference design includes standards compliant Application Programming Interfaces (APIs), protocol management

software and software development tools.

STLC1502

VOICE OVER IP PROCESSOR

PQFP208

ORDERING NUM BER: STLC 1502

• 16-bit, fixed point 120 MIPs DSP (D950)

• Two 10/100 Base-T Ethernet MACs

• VLAN support

• Ethernet Bridge

•JTAG

• Smart power management

2.0 REFERENCE SOFTWARE FEATURES

Some of the features of the SW provided are:

The STLC1502 also has all the proper interfaces to

be a cost effective soluti on f or Small Gateway applications. ST also offer a complete SW reference design for Small Gateway applications.

Hence, the STLC1502 enables a superior and cost

effective platform development for IP-phones as well

as voice gateway applications, prov i di ng developers

with a low risk, rapid time to market solutio n .

The STLC1502

a ARM7/TDMI MCU and a dual port 10/100 Base-T

switched Ethernet media access control interface

The main characteristics of the STLC1502 IP processor are as follows:

• HCMOS7 technology

• Power supply: Core 2.5 V and I/O: 3.3 V

• Industry standard 32-bit RISC microprocessor

(ARM7/TDMI core)

integrates low power D950 DSP with

.

ARM7/TDMI

• Industry standard Real time OS: VxWorks

• Network Protocol Stack

• TCP/IP, UDP, TFTP, DHCP, HTTP server

• Ethernet/PC communication drivers

• High Level Chip Control

• Stack management

• SNMP (optional)

• Application Specific MIBS

• Signalling Protocol

• MGCP, H.323 (including H.450), SIP

D950 Voice Codec Unit (VCU) features:

• G.711 Packetized PCM

• G.729AB, 8kbps CS-ACELP

• G.726, 16-40 kbps ADPCM

• G.723.1a, 6.3/5.3 kbps MP-MLQ

• Encoding and decoding of PCM sample

frames

• Packing/unpacking of compressed information in Codewords

• Fax Modem : T.38 Fax Relay, V.21, V.17,

V.27ter and V.29 f ax datapump

January 2002

This is preliminary information on a new product now in development. Details are subject to change without notice.

Revision: A04

1/81

Page 2

STLC1502

• Data Modem: V.34 datapump

• Rate selection

• High performance voice activity detector (VA D)

• Comfort noise generator (CNG)

• G.165 32 ms Line & acoustic echo canceller

• Low latency system implementation

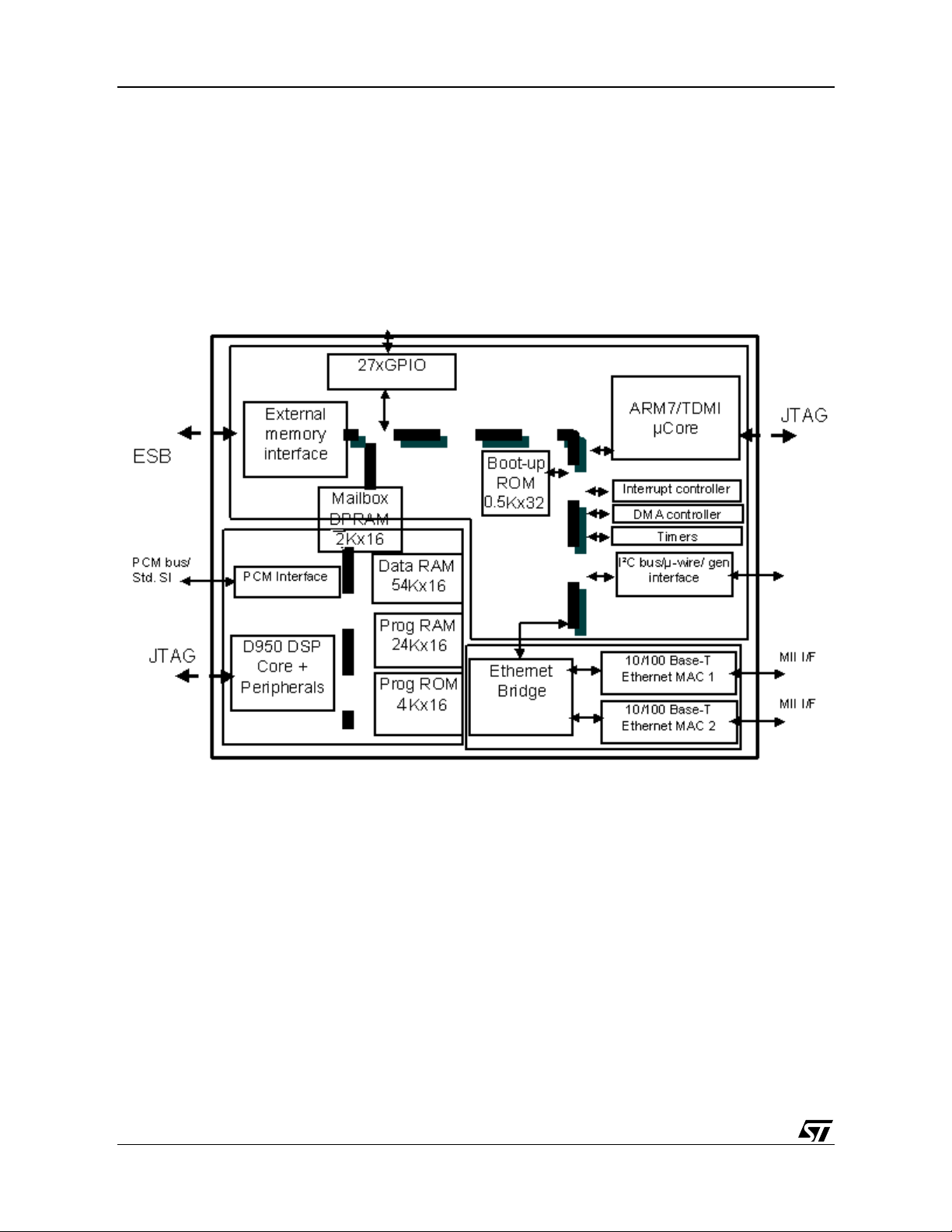

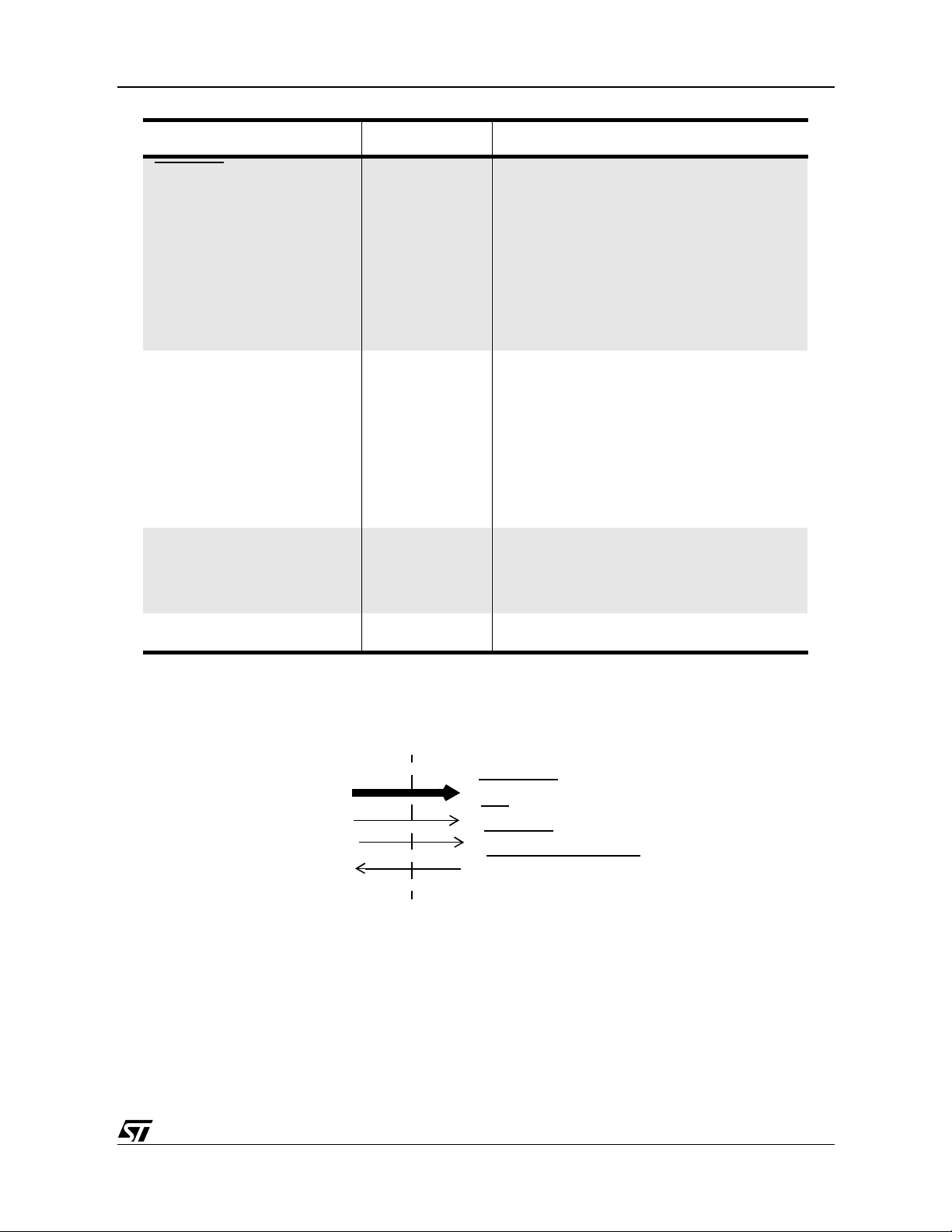

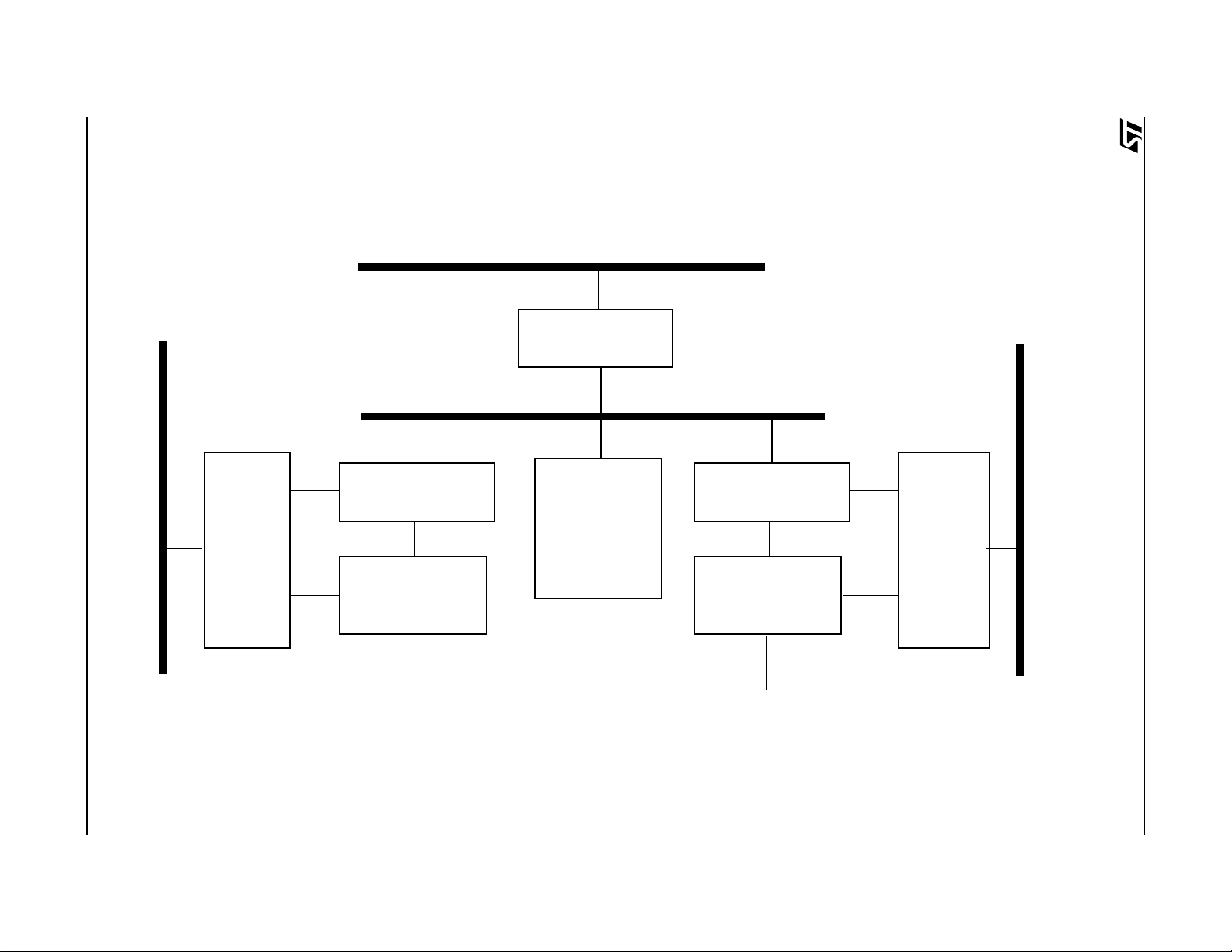

Figure 1: Block diagram

3.0 SYSTEM OVERVIEW

Three main blocks can be identified in the device architecture: ARM domain, the D950 domain and the

Clocks tree domain.

3.1 ARM7 domain

The ARM domain is a multibus microprocessor system based on the ARM7TDMI processor.

• The system bus is based on the Advanced Microcontroller Bus Architecture (AMBA) that includes

two distinct buses:

• The Advanced High performance Bus (AHB) for high performances system modules

• The Advanced Peripheral Bus (APB) for low power peripherals.

• A high speed 32 bit data bus is provided to connect external memories.

• A controller for external static memory (ESM) and a controller for external dynamic memory (EDM)

are provided.

• St atic memories, like FLASH EPROM, SRAM and dynamic memories like EDO, SDRAM, can be

2/81

Page 3

STLC1502

connected on the same external 32 bits high speed bus

• Two MII interfaces can hook directly to two 10/100 Ethernet PHYs

• Internal control hardware manages the switching and MAC processing of frames on the two Ethernet

ports

• Standard serial communication ports are available for easy device connection

• The SPI port is mainly dedicated to the CODEC control. It is compatible with the STM codecs

STLC5046, STLC5048, STW5093. It is a standard SPI port and other peripherals can be connected

to it beside the codec

• I2C port can be use to connect a LCD driver in case of IP-phone application, and a serial EEPROM

for boot coded and configuration data storage

• GPIO block includes as an alternative function a scanning key encoder for direct interface with a 6x6

keypad matrix

• Debouncing function is performed, so no overhead for the ARM controller is introduced

• UART port allows connection to a host terminal. Code downloaded through UART can be performed

during boot

• A Host Processor Interface (HPI) allows direct connection of an external control processor. The interface is directly compatible with the Motorola MPC850 external bus

3.2 D950 domain

The D950 domain is a DSP machine based on the D950 core.

• The D950 core is based on Harvard architecture with separate buses for instruction (I-bus) and data

(X-bus, Y-bus)

• The internal ROM runs basic system management code and standard vocoders

G711,G723.1A,G729AB that are included in the H.323 specification

• Additional vocoders and algorithms are downloaded from the ARM side through the DPRAM

• External CODEC is connected with a standard four wires PCM bus interface

• JT A G and emulation port are available for system software/hardware testing

• DPRAM is used as a communication channel betwee n the ARM and D950

• Control messages and voice packets are exchanged through the DPRAM

• Fax over IP support

3.3 Clock Domain

Three main clock domains are present:

• D950 and peripherals (100 MHz max)

• ARM7 and peripherals (60 MHz max)

• PCM (8.192 MHz max)

The clock base is provided by a fixed external 25MHz crystal/oscillator. A 25MHz clock output can be used

as a master clock for external Ethernet PHY devices, in 10BaseT operation.

NOTE: For 100BaseT operation, this clock may not be sufficiently stable with tight jitter requirements.

Thus the PHY’s may need their own 25 MHz crystal.

Internal PLL’s provide independent clocks to the D950 and ARM7 domain.

The ARM frequency is set by external pin, that selects between 50 MHz and 60 MHz.

The D950 frequency can be set by the ARM via Status register programming.

Four possible values are provided:

100 MHz

180 MHz

190 MHz

3/81

Page 4

STLC1502

200 MHz

To change the D950 master clock frequency the following procedure must be followed:

1) Disable the D950 clock, by resetting the DCLK bit in the control register of the MISC Control register.

2) Wait 10 ARM cycles

3) Select a new D950 master clock, by writing the MISC Status register.

4) Wait 4 ms

5) Disable the D950 clock, by setting the DCLK bit in the MISC Control register.

An Internal divider provides an internal PCM clock, 2083 KHz, that is not exactly the standard 2048 KHz.

- An external PCM clock frequency can be applied using a dedicated crystal or oscillator, to provide exactly

8KHz synch and sampling clock on the PCM bus. (External pins configuration Testsel[3:0] at [0011]).

The PCM clock rate can be selected via software to achieve the following values:

1536 (24 Ch.) 2048 (32 Ch.) 4096 (64 Ch.) 8192 KHz (128 Ch.).

- The PCM clock and Frame synch signals can be selected as inputs or outputs, by programming the con-

trol register in the miscellaneous block.

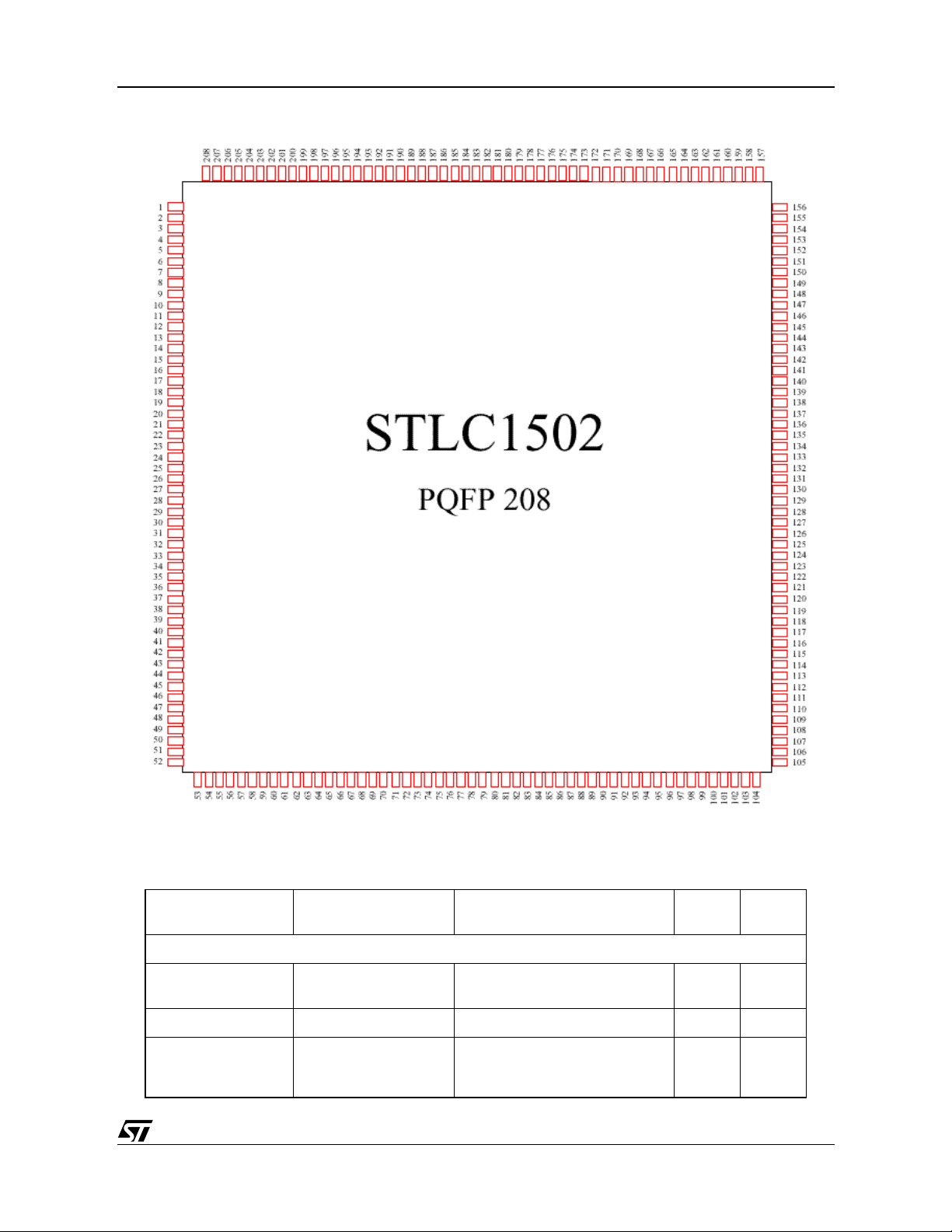

4.0 Pin Descriptions

The STLC1502 will be delivered in:

• PQFP 208 Pins

4/81

Page 5

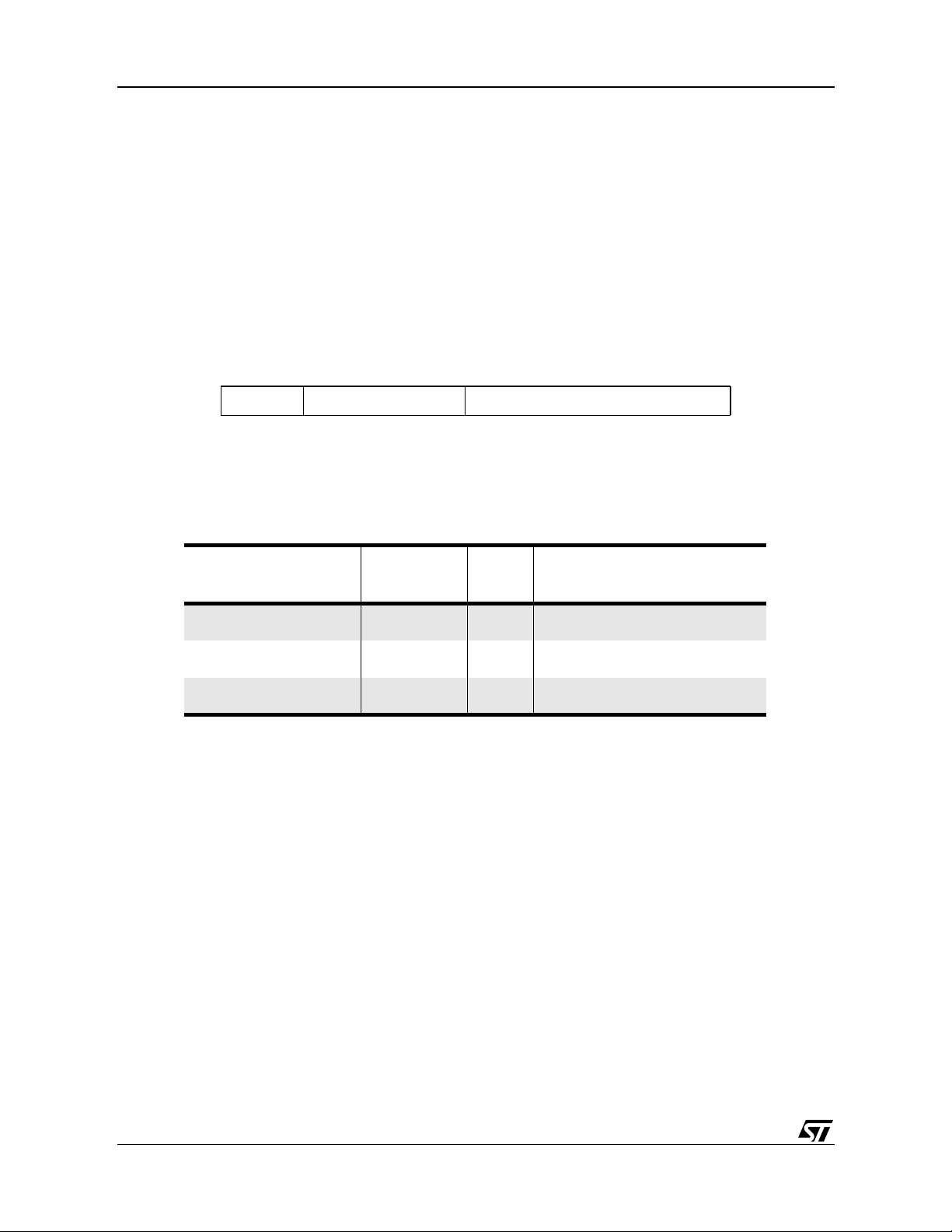

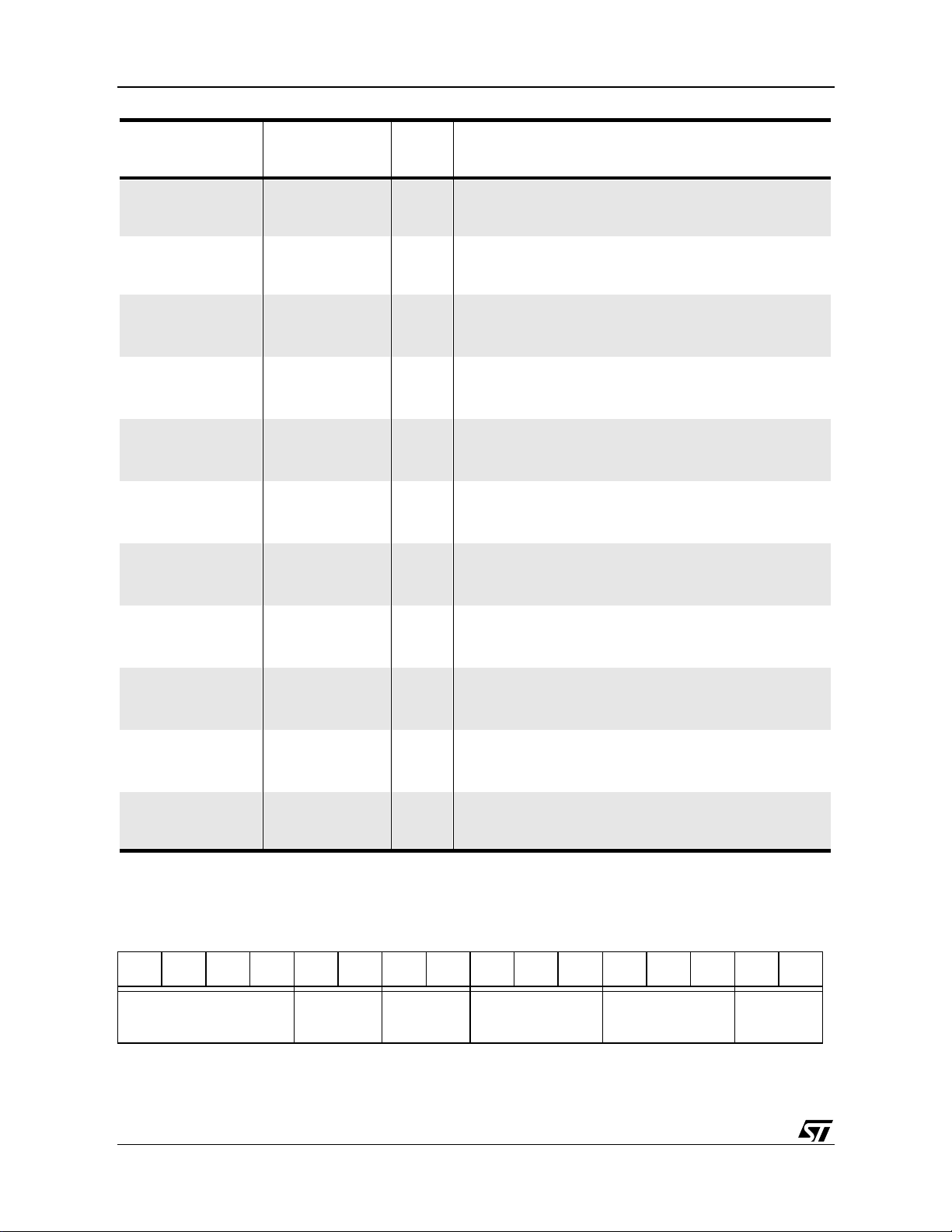

Figure 2: 208-Pin PQFP

STLC1502

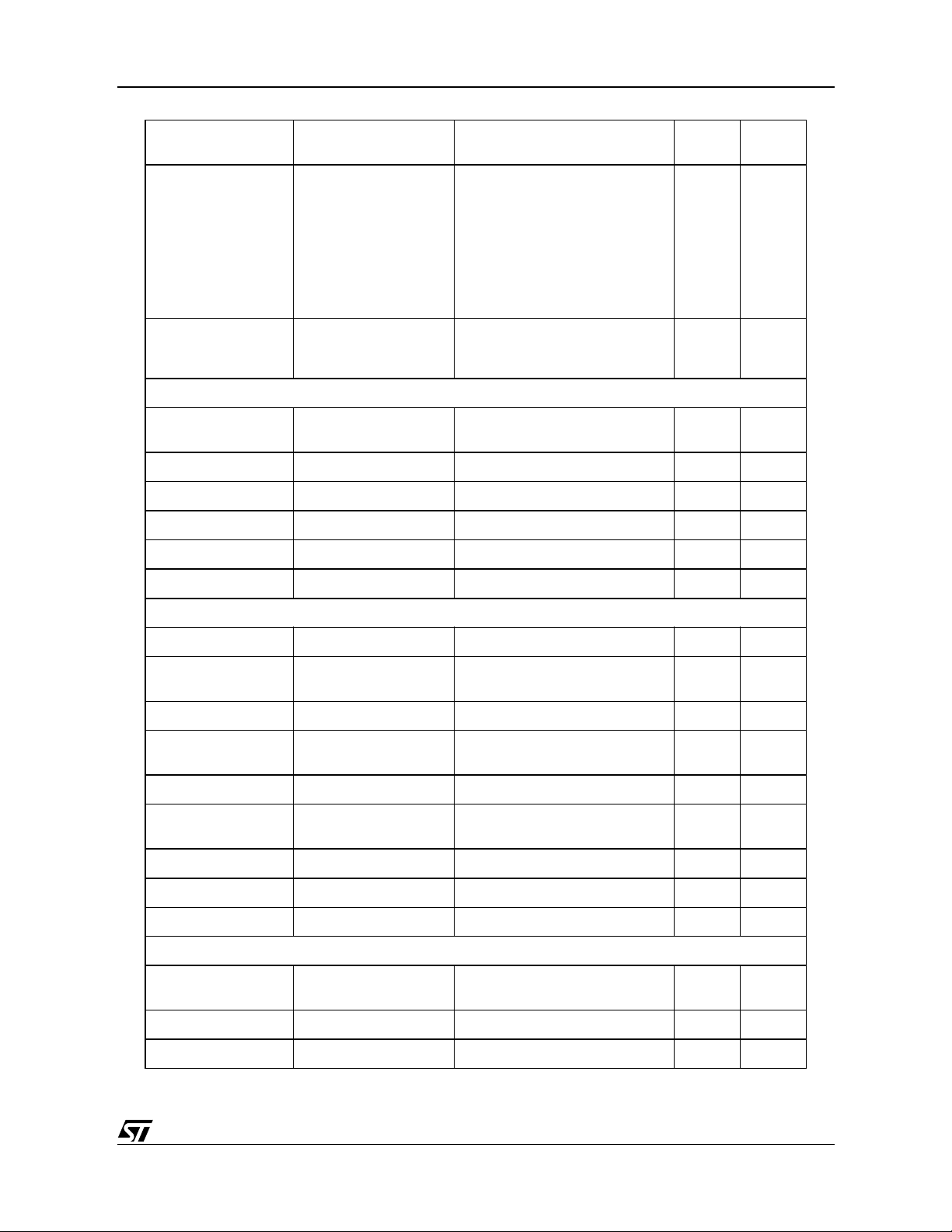

4.1 Pin Description Table

Pin Pin Name Pin Description/Note

Clocks, Reset

41 xtalin 25 MHz crystal input Master clock

42 xtalout 25 MHz crystal feedback O

43 pxtalin 8.192 MHz crystal input PCM I/F

or DSP clock in PLL bypass mode

Clock or PCM input clock in PLL

bypass mode

Pin

Drive

Pin

Type

I

I

5/81

Page 6

STLC1502

Pin Pin Name Pin Description/Note

44 pxtalout 8.192 MHz crystal feedback O

45 edmiclk SDRAM feedback clock (input) 8mA I/O

46 testarmclk ARM clock in bypass mode I

52 selarmfreq Selects ARM PII Vco frequency I

53 rstn Asynchronous Master Reset Input I

188 clkout 25MHz master clock out 4mA O

Miscellaneous

47 bootsel_treqa Boot selection: Select internal [1]

118 hp isel Select between HPI[1] or

Memory I/F (shared signals)

125, 126, 127, 129,

130, 131, 133, 134,

135, 136, 137, 138,

140, 141

add[0..13] Memory address bus.

or external [0] booting ROM. If

proper test configuration has been

selected, then signal assumes Tic

request A functionality

GPIO_KBD IF [0]

For Dynamic RAM, they are the

whole address, whereas for static,

they are the LSBits addresses. At

power up or hardware reset all

address values are 0

Pin

Drive

4mA O

Type

Pin

I

I

62, 63, 64, 65, 66, 69,

70, 71, 72, 73, 74, 75,

77, 78, 79, 81, 82, 84,

85, 86, 88, 89, 91, 92,

93, 95, 96, 98, 99,

100, 102, 103

2, 3, 4, 5 wenbsn[0..3] Write byte enable for external

6 oen Output enable for static/dynamic

ESM (specific controls)

142, 144, 145, 146,

148, 149, 150, 152

data[0..31] Memory data bus, to exchange

data between memory controller

and external memories

static RAM or byte strobe for

dynamic external RAM

external RAM. At power up or

hardware reset, the signal will be

asserted if the external booting

(bootsel = ‘1’) has been selected

add[14..21] Memory address bus’ MSBits.

They complete the ESM

addressability. A total of 4Mbyte

external (FLASH/SRAM) address

space is addressed by the

STLC1502 device. At the first fetch

of instruction after power_up or

hardware reset, all address values

are ‘0’

8mA I/O

8mA O

8mA O

4mA O

6/81

Page 7

STLC1502

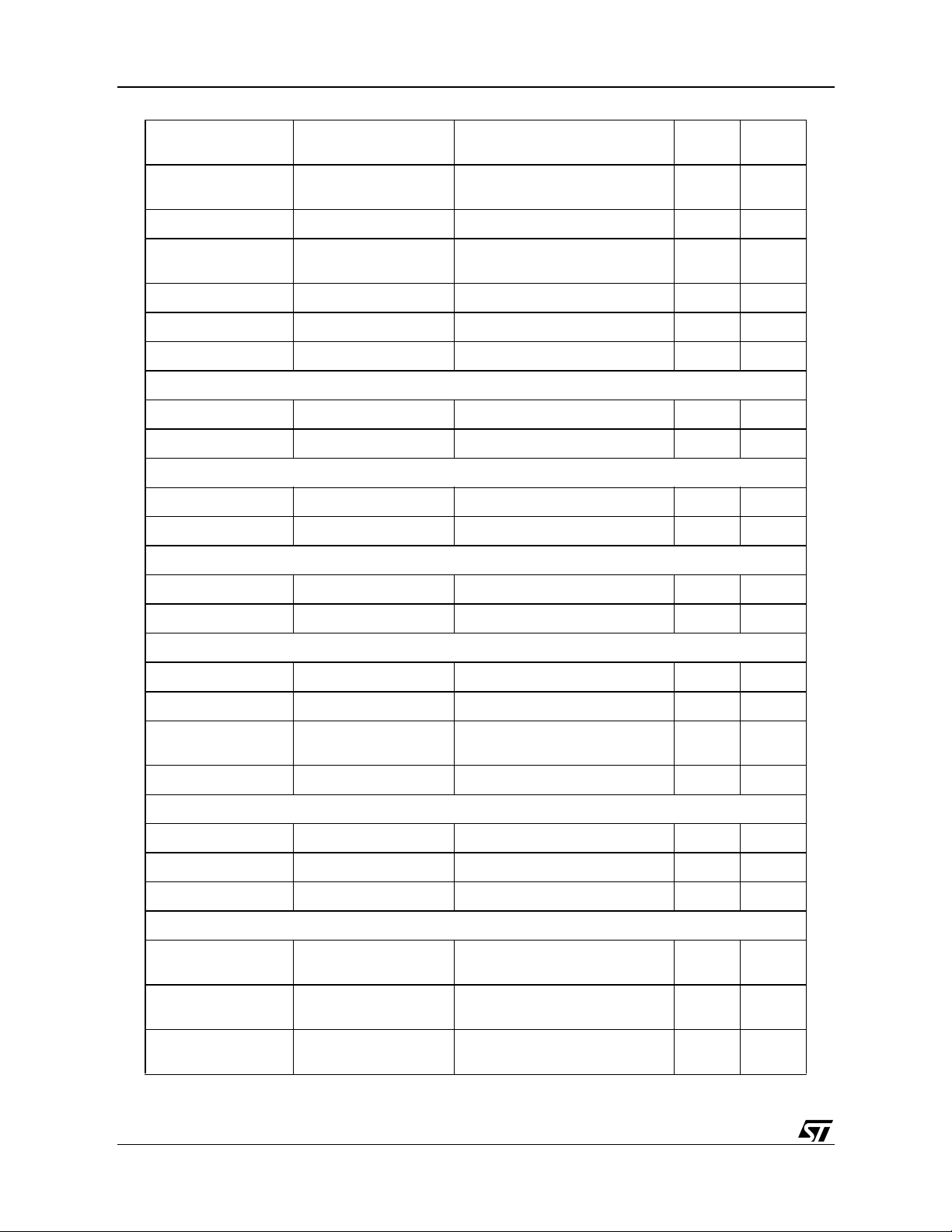

Pin Pin Name Pin Description/Note

153, 154, 155 esmcs[0..2]n Chip select [0..2] for external

memory (FLASH/SR AM). At

power up or hardware reset, if

external boot ROM has been

selected, (bootsel =’1’) the signal

is asserted during the fetch

instruction, else the selection

depends on internal address

mapping

61 ecs0width External FLASH/SRAM Data bus

size: if settled to ‘L’, select a 8 bit

parallelism data.

EDM ( specific controls)

156, 158, 159, 160 edmcsn[0..3] Chip select for SDRAM or RAS for

EDO DRAM

161 edmclken SDRAM clock enable 8mA O

162 edmoclk SDRAM output clock 8mA O

165 edmras SDRAM ras command 8mA O

166 edmcas SDRAM cas command 8mA O

167 edmwe SDRAM we command 8mA O

Pin

Drive

4mA O

8mA O

Type

Pin

I

MII Interface Port # 1

168 mii1_txen Transmit enable 4mA O

169 mii1_txclk Transmit clock reference for txd,

txen, txer

170, 171, 174, 175 mii1_txd[0..3] Transmit data bus 4mA O

176 mii1_rxclk Receive clock reference for rxd,

rxdv, rxer

177 mii1_rxdv Receive data valid I

178 mii1_rxer Receive error signal, indicates an

error condition on receiving data

181, 182, 183, 184 mii1_rxd[0..3] Receive data bus I

185 mii1_col Collision signal I

186 mii1_crs Carrier sense indication I

MII Interface Port # 2

193 mii2_txclk Transmit clock reference for txd,

txen, txer

194 mii2_txen Transmit enable 4mA O

195, 196, 197, 198 mii2_txd[0..3] Transmit data bus 4mA O

I

I

I

I

7/81

Page 8

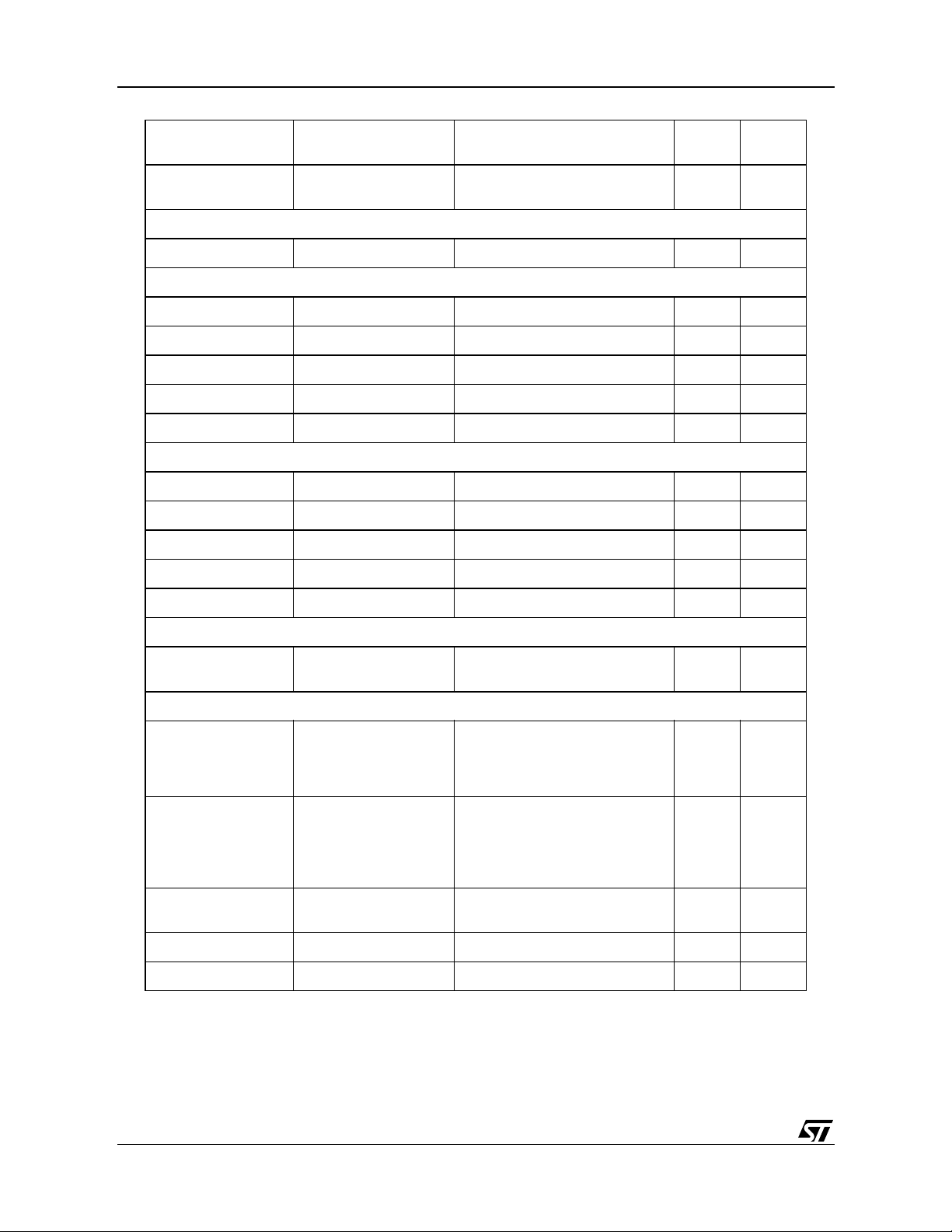

STLC1502

Pin Pin Name Pin Description/Note

200 mii2_rxclk Receive clock reference for rxd,

rxdv, rxer

201 mii2_rxdv Receive data valid I

202 mii2_rxer Receive error signal, indicates an

error condition on receiving data

203, 204, 205, 206 mii2_rxd[0..3] Receive data bus I

207 mii2_col Collision signal I

208 mii2_crs Carrier sense indication I

PHY I/F Management

189 mdc MII management clock 4mA O

190 mdio MII management data i/o 4mA I/O

UART I/F

112 sin Serial data input I

113 sout Serial data output 2mA O

I2C I/F

Pin

Drive

Pin

Type

I

I

116 scl I2C clock 2mA I/O

117 sda I2C data 2mA I/O

PCM I/F

104 pdx PCM Downstream data I

105 pdr PCM Upstream data 2mA O

106 pfs PCM Input/Output Frame

107 pdc PCM Input/Output Data clock 4mA I/O

SPI I/F

109 sck SPI interf ace Clock 2mA O

110 smi SPI master data input I

111 smo SPI master data output 2mA O

KBD/GPIO/HPI I/F

9 gpio0_r1_hpidata0 GPIO[0] or keypad matrix row 1 or

10 gpio1_r2_hpidata1 GPIO[1] or keypad matrix row 2 or

synchronization

2mA I/O

4mA I/O

Hpidata[0]

4mA I/O

Hpidata[1]

8/81

1 1 gpio2_r3_hpidata2 GPIO[2] or keypad matrix row 3 or

Hpidata[2]

4mA I/O

Page 9

STLC1502

Pin Pin Name Pin Description/Note

14 gpio3_r4_hpidata3 GPIO[3] or keypad matrix row 4 or

Hpidata[3]

15 gpio4_r5_hpidata4 GPIO[4] or keypad matrix row 5 or

Hpidata[4]

16 gpio5_r6_hpidata5 GPIO[5] or keypad matrix row 6 or

Hpidata[5]

17 gpio6_c1_hpidata6 GPIO[6] or keypad matrix col 1 or

Hpidata[6]

18 gpio7_c2_hpidata7 GPIO[7] or keypad matrix col 2 or

Hpidata[7]

19 gpio8_c3_hpiadr0 GPIO[8] or keypad matrix col 3 or

Hpiadr[0]

20 gpio9_c4_hpiadr1 GPIO[9] or keypad matrix col 4 or

Hpiadr[1]

23 gpio10_c5_hpiadr2 GPIO[10] or keypad matrix col 5 or

Hpiadr[2]

24 gpio11_c6_hpiclk GPIO[11] or keypad matrix col 6 or

Hpiclk input

Pin

Drive

4mA I/O

4mA I/O

4mA I/O

2mA I/O

2mA I/O

2mA I/O

2mA I/O

2mA I/O

2mA I/O

Pin

Type

25 gpio12_dreq GPIO[12] or Dma input request

(software selection)

26 gpio13_dack GPIO[13] or Dma output

acknowledge (software selection)

27 gpio14_hpics_d950idle GPIO[14] or Hpi Chip Select

(active low) or D950 emulator

output idle state

28 gpio15_hpias_d950snap GPIO[15] or Hpi Address Strobe

(active low) or D950 snap output

sate

29 gpio16_hpirw_treqb GPIO[16] or Hpi Read (active

high) Write (active low) strobe or

Tic request B input. The Tic mode

is forced selecting the proper test

configuration through testsel[3..0]

pin

30 gpio17_hpiint_tack GPIO[17] or Hpi Interrupt out or

Tic acknowledge output. The Tic

mode is forced selecting the

proper test configuration through

testsel[3..0] pin

33 gpio18_irq1 GPIO[18] and External interrupt

input 1

2mA I/O

2mA I/O

2mA I/O

2mA I/O

2mA I/O

2mA I/O

2mA I/O

9/81

Page 10

STLC1502

Pin Pin Name Pin Description/Note

34 gpio19_irq2 GPIO[19] and External interrupt

input 2

Test Signal

55, 56, 57, 58 testsel[0..3] Test mode selection I

Stradivarius STLC1502 and/or ARM’s JTAG

119 tdi Data input I

120 tdo Data output 2mA O

121 tms Test mode select I

122 tck Clock I

123 trstn Jtag Input Reset I

D950’s JTAG

35 d950tdi Data input I

36 d950tdo Data output 2mA O

37 d950tms TMS command I

38 d950tck Clock I

Pin

Drive

2mA I/O

Pin

Type

39 d950trstn Reset Input I

D950’s EMU signals

54 d950erqn Halt request to enter emulation

Power and Ground pins

1, 12, 21, 31, 67, 76,

83, 90, 97, 124, 132,

139, 147, 164, 180,

192, 199

7, 13, 22, 32, 40, 51,

60, 68, 80, 87, 94,

101, 108, 115, 128,

143, 151, 157, 163,

173, 179, 191

8, 48, 59, 114, 172,

187

49 PLL_VSS PLL digital ground P

50 PLL_VDD PLL analog power supply 2.5V P

vdd3 I/O Power P

gnd Core ground P

vdd Core Power P

5.0 ARM Memory Configuration

I

mode

• The AMBA bus system allows to handle memory blocks and peripherals on distinct buses, in order to

optimize the AHB architecture for maximum speed .

10/81

Page 11

STLC1502

• The memory blocks are attached to the AHB bus so ARM code can run at maximum speed.

• An internal ROM is used to store boot code that polls serial peripherals (I2C EEPROM, UART) and

HPI for code download in external RAM. After download, the control is given to code in external

RAM.

• An internal RAM is used to store ARM7 interrupt vectors and some data (network frames)

• Four external memory types can be connected.

• Flash

• SRAM

• DRAM (SDRAM or EDO)

• Serial EEPROM

• Flash, SRAM, DRAM share the same 32 bits data bus and 32 bits address bus. Little/Big endian

mode is software programmable for the DRAM memory controller. Serial EEPROM can be connected to the I2C bus.

• The chip provides the option of booting from Flash or from serial EEPROM, by selection from an

external BOOT_SEL pin. So different memory configuration s are possible depending on the application:

1. Flash, DRAM: The boot code including BOO TP and TFT P is stored in Flash. Application can be

stored in flash also, or can be downloaded into DRAM from Ethernet Network or UART.

2. EEPROM, DRAM: The boot is perf ormed from inte r n a l ROM. The ROM code loads th e code stored

in EPROM that includ es BOO TP and TFTP. Applic at ion code w ill be downl oaded int o D RA M from

Ethernet or UART .

3. Flash, DRAM, EEPROM: It is like case 1, but has more flexibility. The EEPROM can be used to store

Network parameter data (MAC address) and other specific board data, so the code to store in flash is

the same for all the platforms, and you do not need to split the flash in a permanent storage area and

in an upgradable storage area. The EEPROM can also be used to allow the programming of the flash

the first time with a code downloaded from Ethernet Network.

4. DRAM: The boot is performed from internal ROM. The application code is downloaded from the host

processor through the HPI interface. To access external memory bus an internal decoder is implemented, that can select different external memory devices. 32 bits data bus is provided with the possibility to select external accesses at 16 and 8 bits for each memory bank. For example the flash can

be at 16 bits and the DRAM at 32 bits. There are 3 chip select available for static memory (4Mbytes

each), 4 chip selects for dynamic memory (8Mbytes each).

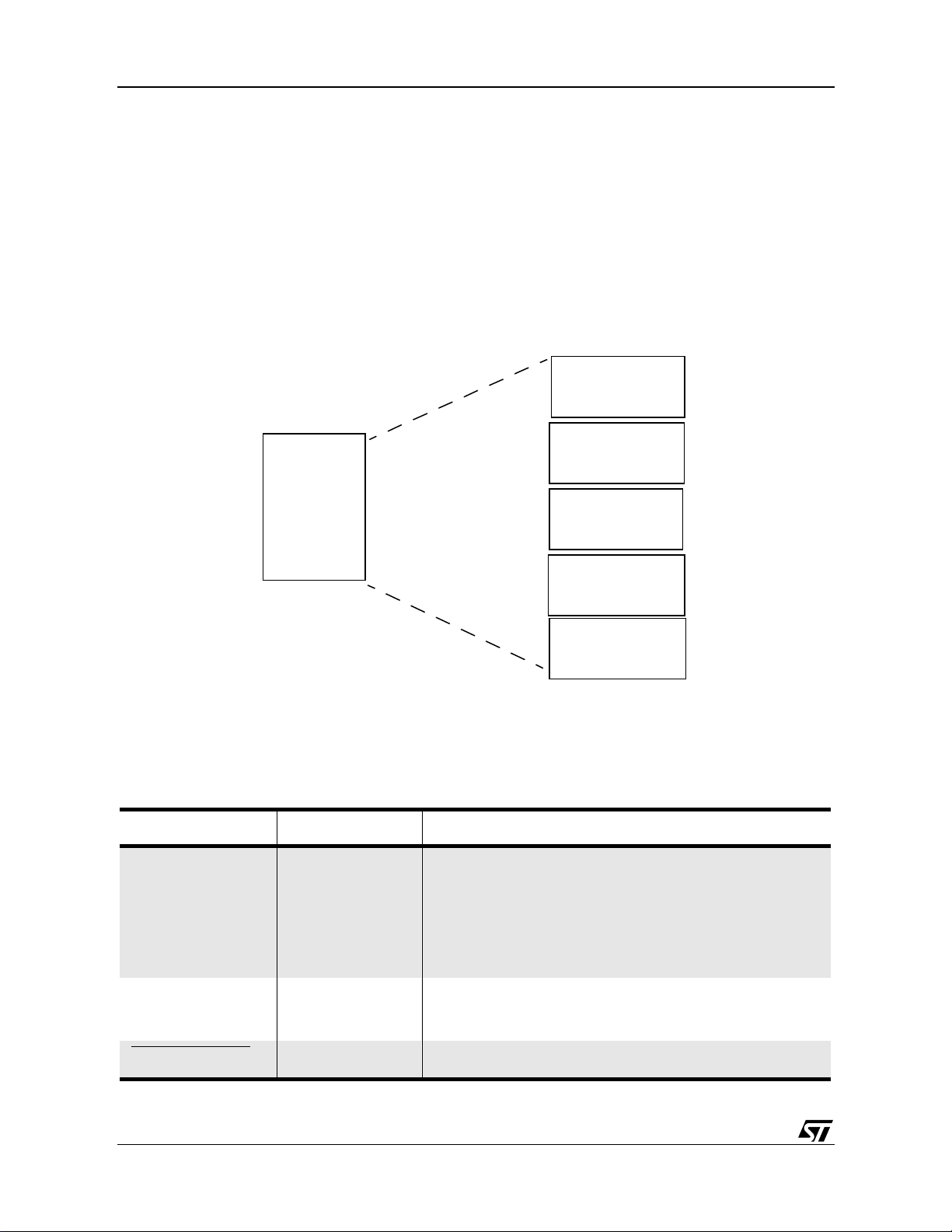

5.1 ARM Memory Map

The ARM microprocessor sees 5 main memory areas.

Actually the memory map depends on the phase the microprocessor is working on:

• Boot from internal ROM phase (REMAP=0 and BOOT_SEL=0);

• Boot from external Flash phase (REMAP=0 and BOOT_S E L=1);

• Operating phase (REMAP=1).

The first two phases are alternative (only one of them happens at the power on reset, while the third happens

after the boot.

6.0 AHB Bus

AHB Bus is a 32 bits data and 32 bits address bus.

6.1 Internal RAM

An internal Static RAM 2048x 32 is mapped starting at address 0x0 in operational mode and is used for ARM

interrupt vector tables.

11/81

Page 12

STLC1502

6.2 ESM interface

• The ESM (External Static Memory) interface is used to access static RAMs or Flash devices. It provides 3 chip select signals and gives external access to 21 address bits, so that the memory space

accessible through each chip select is 4 Mbytes.

• The data bus on ESM external interface is 32bits wide, with the additional ability to perform 16 and 8

bits accesses. Little endian byte ordering is used. The data bus and address bus pins are shared with

the DRAM driver, using EBI interface.

• Programmable per chip-select wait-states from 0 to 15 internal clock cycles are available.

• At reset, every CS space has 15 wait states. The actual value is contained in the downloaded code.

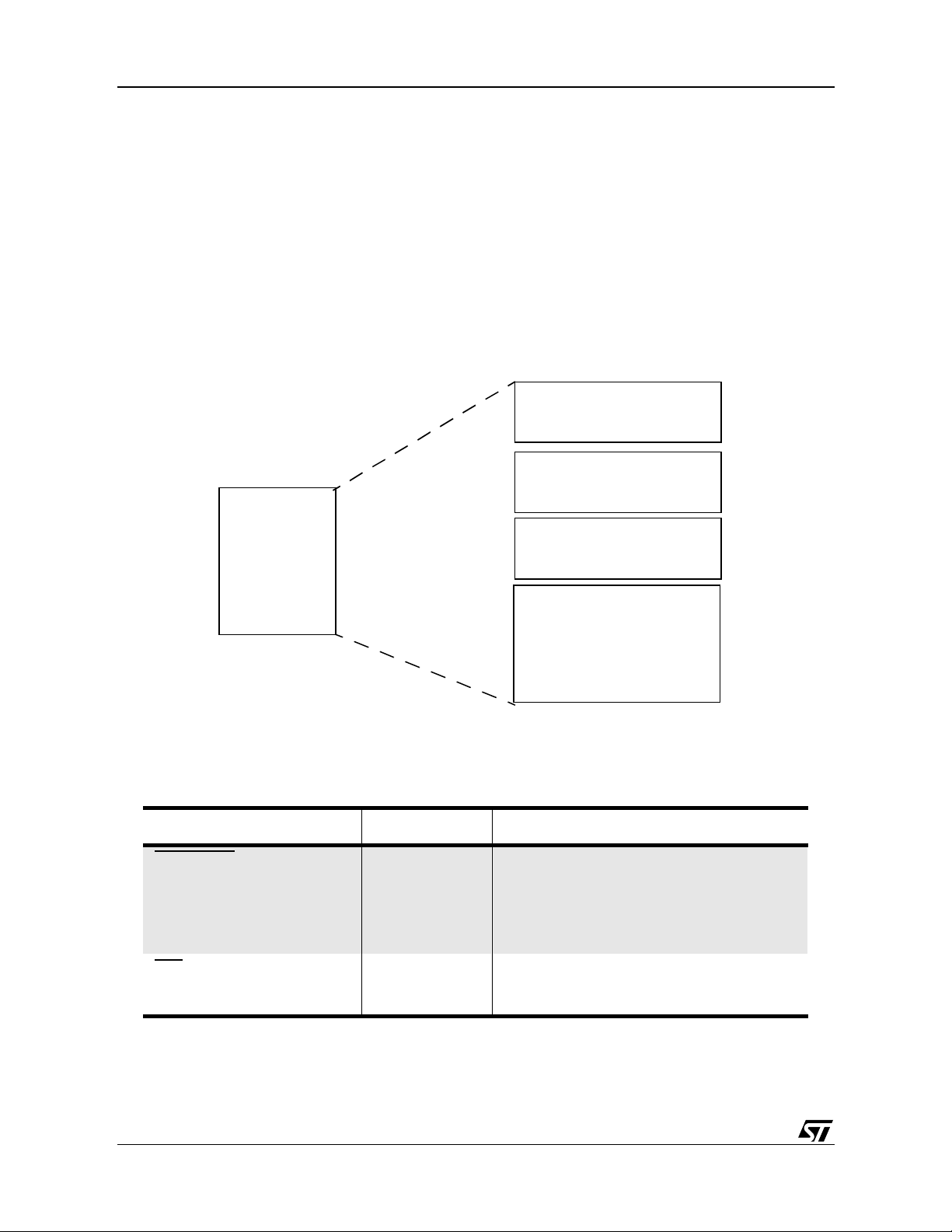

• The external memory spaces are mapped by the ESM interface as reported in Figure 4.

• There are 3 addressable memory spaces 0x00400000 byte long each.

04000000

ESM_CS0

043FFFFF

04400000

ESM_CS1

04000000

ESM

External

Memories

ESM_CS2

047FFFFF

04800000

04BFFFFF

04C00000

07FFFFFF

Reserved

07FFFFFF

Figure 4: ESM memory map

Following is the list of the available external signals that implement SRAM or F LASH read and write cycles. Data

and address buses are not shown as they are shared with the DRAM EBI interface.

NAME Signal type Description

ESM_CS(2:0) OUT Chip Select. Asserted when the

ESM decodes the proper address

space in order to select the right

external device

OE

OUT

Output Enable. Asserted during a

read cycle (shared with EDM)

12/81

Page 13

NAME Signal type Description

STLC1502

WE[3:0]

OUT

Bytes Write enable. They are

used to select one/two bytes

when a x16/x32 Flash/SRAM is

present (shared with EDM).

0: lower byte

1: 2nd byte

2: 3rd byte

3: higher byte

ESM_CS0WIDTH

IN

This input informs whether a x8

(ESM_CS0WIDTH=0) or x16

(ESM_CS0WIDTH=1) device is

present on the CS0. This information is needed the boot from external memory is selected.

A[21:0] OUT 22 Address lines for up to

4Mbytes address space (shared

with EDM A[13:0])

D[31:0]

A scheme of the ESM control interface is reported in Figure 5.

device side

INOUT Data bus(shared with EDM bus)

external side

ESM_CS(2:0)

OE

WE[3:0]

ESM_CS0WIDTH

Figure 5: ESM control interface

Every CS space can be programmed through internal register (one for each CS) in order to:

• select the number of wait states to perform external access depending on the speed of the external

device mapped on that memory area

• select if the data bus is x8 or x16 (available only for CS1 to CS2). When the x8 memories are used,

their data bus has to be placed on the ESM_D(7:0) signals

The wait states number f or the ext ernal memories (dependi ng on memory access t ime) is obt ained from the

software code during the download phase. During the initialization phase, it is the responsibility of the software

to determine if a SRAM or a FLASH is present or not on a given CS space and the width of CS1-2 memories (if

13/81

Page 14

STLC1502

present).

It is possible to connect every CSx to a Dual Port SRAM and use that as a communication mailbox betwee n the

device and an external microprocessor. For example, the microprocessor can write a message in the memory

using one port and can send an interrupt to the dev i ce so t hat t he executi on routi ne rel ated wit h that i nterrupt

can read from the other port of the memory connected to the same CSx of the ESM.

Viceversa, the ESM can write a message in the memory and then can send an interrupt to the external microprocessor t hat will r ead the message from the other port of the memory.

The SRAM and the FLASH dev ices that are used as references are standard.

6.2.1 ESM address decoding scheme

The ESM block includes also a decoder in order to generate the proper CS to the external device. In particular

this decoder will wor k on the b it 22,2 3,24 and 25 of the internal ARM address bus.

ESM decoder ESM_A(21:0)

ESM decoding scheme

6.2.2 ESM Register Map [

The base address of the ESM register is 0x0C600000.

0x0C600000

]

Address Register

R/W Notes

Name

ESMBase + 0x00 CS0 R/W CS0 bank control

ESMBase + 0x04 CS1 R/W CS1 bank control

ESMBase + 0x08 CS2 R/W CS2 bank control

6.3 EDM interface

The EDM interface is used to access external DRAMs. This block supports both EDO and SDRAM interfaces

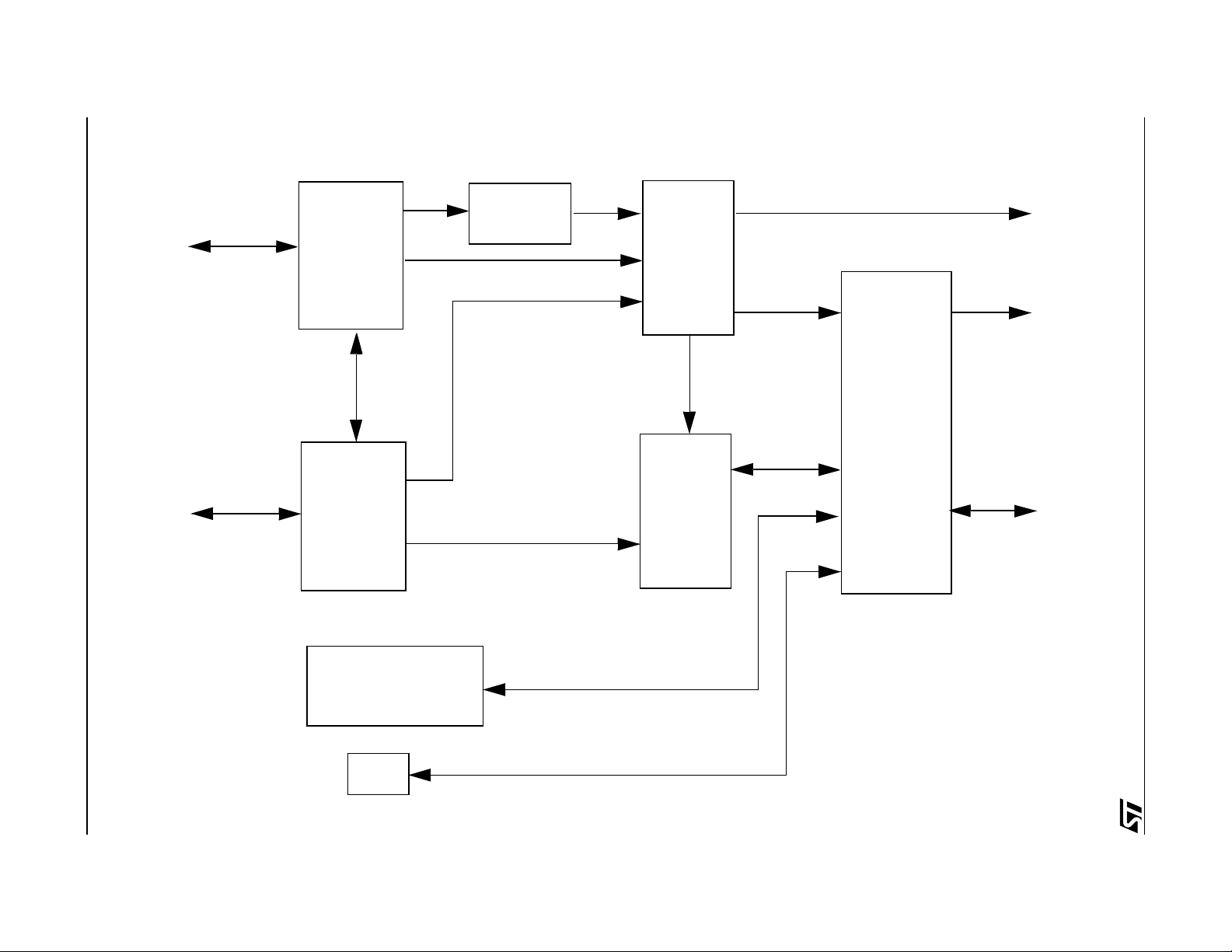

with enough flexibility to be used with several DRAM chips available in the market. This block has a separate

bus for control (the registers are placed on the APB bus) and for data (data and address are placed on the ASB

bus) and also includes an external bus interface that allows to share address and data bus pins with the static

ESM interface.

Figure 6 shows a block diagram of the EDM block.

14/81

Page 15

15/81

STLC1502

APB

bus

AHB

bus

Registers

AHB

interface

Refresh

Memory

driver

Data

Mux

Control

Address

External

bus

interface

Data

ESM

External Static

Memory Co ntroller

TIC

Page 16

STLC1502

Figure 6: EDM block diagram

It is possible to connect up to 4 external chips with x8, x16, and x32 data bus. Each memory bank space is

8Mbytes big so that a standard 64Mbi t DRAM device can be connected. It is not possible to use a single

32Mbytes memory device.

It is the responsibility of the ARM c ode to properly configure the EDM block to initialize the DRAM at startup.

The external memory is mapped by the EDM interface as shown in Fig. 7.

10000000

EDM_CS0

107FFFFF

10000000

13FFFFFF

EDM

External

DRAM

EDM_CS1

EDM_CS2

EDM_CS3

10800000

10FFFFFF

11000000

117FFFFF

11800000

11FFFFFF

12000000

Reserved

13FFFFFF

Figure 7: EDM memory map

In the following table there is the list of the available external signals of the EDM interface.

NAME Signal type Description

EDM_CS(3:0) OUT Chip Select. Asserted when the EDM

decodes the proper address space in order

to select the right external device. To be connected to RAS signal in case of use of EDO

memorie s

EDM_CLK OUT

EDM_CLKEN

16/81

OUT

SDRAM Memory clock (same as ARM

clock). Not used with EDO.

SDRAM clock enable. Not used with EDO.

Page 17

NAME Signal type Description

STLC1502

EDM_RAS

EDM_CAS

OEN

OUT

OUT

OUT

SDRAM RAS signal. Not used with EDO.

SDRAM CAS signal. Not used with EDO

SRAM Output Enable. Not used with

SDRAM

EDM_WE

OUT

DRAM Write Enable

EDM_BS(3:0) OUT SDRAM byte strobe. CA S w hen EDO memo-

ries are used

EDM_A(21::0) OUT DRAM address lines, only 14 lines are

driven.. Lines.21:14 are driven by static

memory cont ro l le r

EDM_D(31:0) INOUT DRAM data lines, shared with static memory

controller lines.

The EDM block includes a decoder in order to generate proper CS to the external device. In particular this decoder will work on bits 25 and 26 of internal ARM address bus.

EDM

Decoder

EDM decoding scheme

• Every CS space can be programmed through internal register in order to configure the EDM to work

with the proper external device

• The DRAM Controller has nine registers, the configuration register, four bank registers and four

SDRAM configuration registers. The registers are accesses via the APB bus. The register data path

is 16 bits wide.

6.3.1 EDM Register Ma p [0x0C5800 00]

• The base address of the EDM register is 0x0C580000

Address Register

Name

EDMBase +

0x00

EDMBase +

0x04

MB1Config

MB2Config

R/W Notes

R/W

R/W

Memory Bank 1 Configuration Register

Memory Bank 2 Configuration Register

EDM_A(13:0)

17/81

Page 18

STLC1502

Address Register

Name

EDMBase +

0x08

EDMBase +

0x0C

EDMBase +

0x10

EDMBase +

0x14

EDMBase +

0x18

EDMBase +

0x1C

EDMBase +

0x20

MB3Config

MB4Config

SDRAM1C

onfigLo

SDRAM1C

onfigHi

SDRAM2C

onfigLo

SDRAM2C

onfigHi

SDRAM3C

onfigLo

R/W Notes

R/W

R/W

WO

Memory Bank 3 Configuration Register

Memory Bank 4 Configuration Register

Memory Bank 1 Low SDRAM Configuration Register

WO

Memory Bank 1 High SDRAM Configuration Register

WO

Memory Bank 2 Low SDRAM Configuration Register

WO

Memory Bank 2 High SDRAM Configuration Register

WO

Memory Bank 3 Low SDRAM Configuration Register

EDMBase +

0x24

EDMBase +

0x28

EDMBase +

0x2C

EDMBase +

0x30

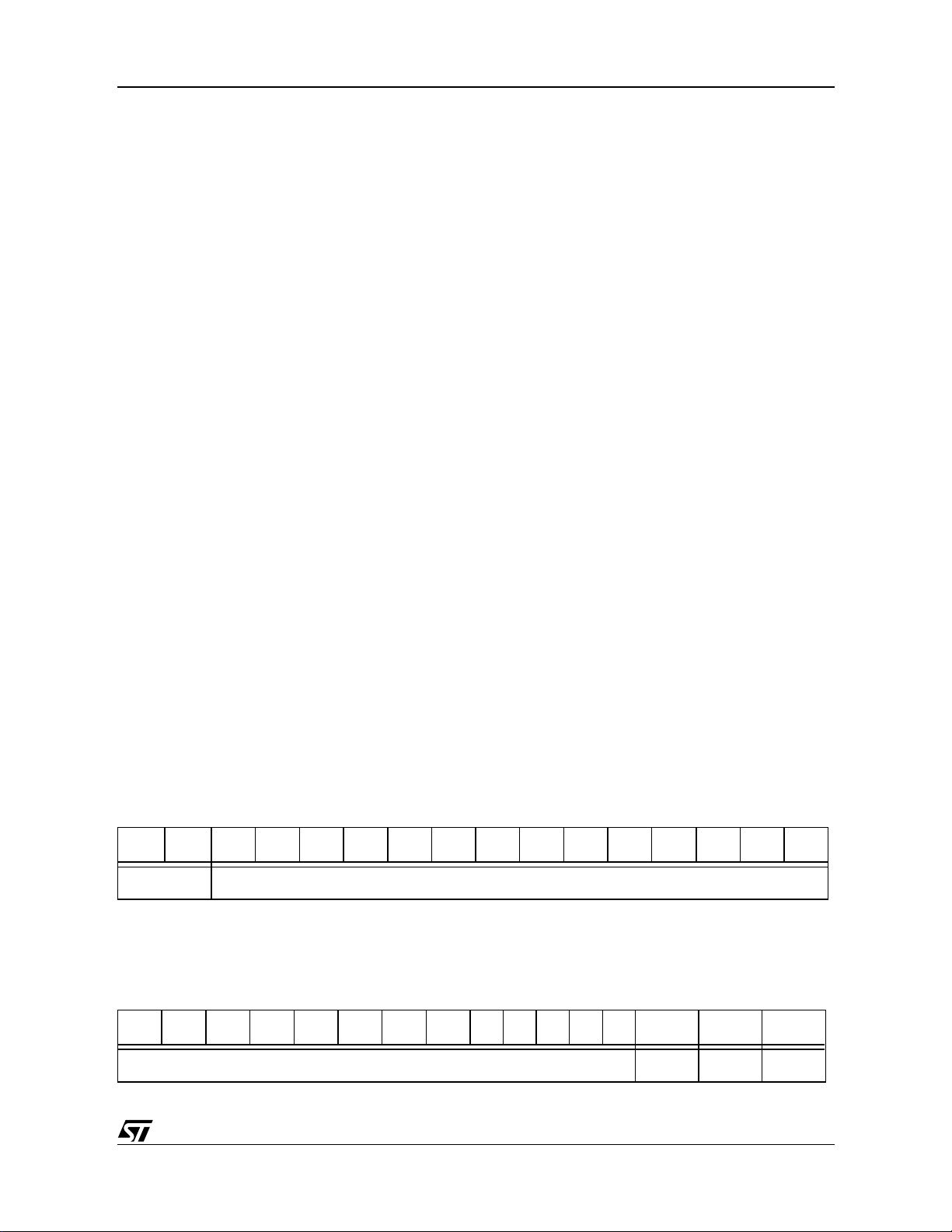

6.3.1.1 Memory Bank Configuration registers

Memory bank configuration registers are used to setup memory bank specific parameters:

1514131211109876543210

Reserved DEVWID DATA-

SDRAM3C

onfigHi

SDRAM4C

onfigLo

SDRAM4C

onfigHi

MemConfig

WO

WO

WO

R/W

LAT

Memory Bank 3 High SDRAM Configuration Register

Memory Bank 4Low SDRAM Configuration Register

Memory Bank 4 High SDRAM Configuration Register

Memory Configuration Register

SETUP TIME IDLET IME SDRAM-

COL

DEVWID: Device Width

18/81

Page 19

STLC1502

• Defines the data width of the external memory device:

• 00 - Byte (8 bit)

• 01 - Half Word (16 bit)

• 10 - Word (32 bit)

DATALAT: Data Latency

• Defines the number of memory clock cycles between the start of a memory read access and the first

valid data.

• The DATALAT value is valid between 0 and 3.

SETUPTIME: Setup Time

• Defines the number of memory clock cycles t he m emory driver spends in the DECODE state before

accessing the external memory.

• The SETUPTIME value is valid between 0 and 7.

IDLETIME: Idle Time

• Defines the minimum time the memory driver must spend in the IDLE state following memory

accesses.

• The value defines the number of Memory Clock cycles.

• The IDLETIME value is valid between 0 and 7.

SDRAMCOL : SD RAM Column Width Definition

• Specifies the width of the SDRAM column address:

• 00 - 8 bits

• 01 - 9 bits

• 10 - 10 bits

• 1 1 - reserved

6.3.1.2 SDRAM Configuration registers

These registers are write only. A write access to the high registers will start the SDRAM configuration cycle,

during which the value written to the register will be asserted on the memory bus for a one clock period.

Low SDRAM Configuration Registers

1514131211109876543210

Reserved MIAB

MIAB: Memory Interface Address Bus

High SDRAM Configuration Registers

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved MIVE MIAA MISA

19/81

Page 20

STLC1502

MIAB: Memory Interface Address Bus

MIWE: Memory Interface Write Enable

MIAA: M e mory Interface Access A ctive (nCAS)

MISA: M e mory Interface Setup Active (nRAS)

After the power-up the CPU must configure each SDRAM device, i.e. perform precharge-refresh-mode register

set procedure.

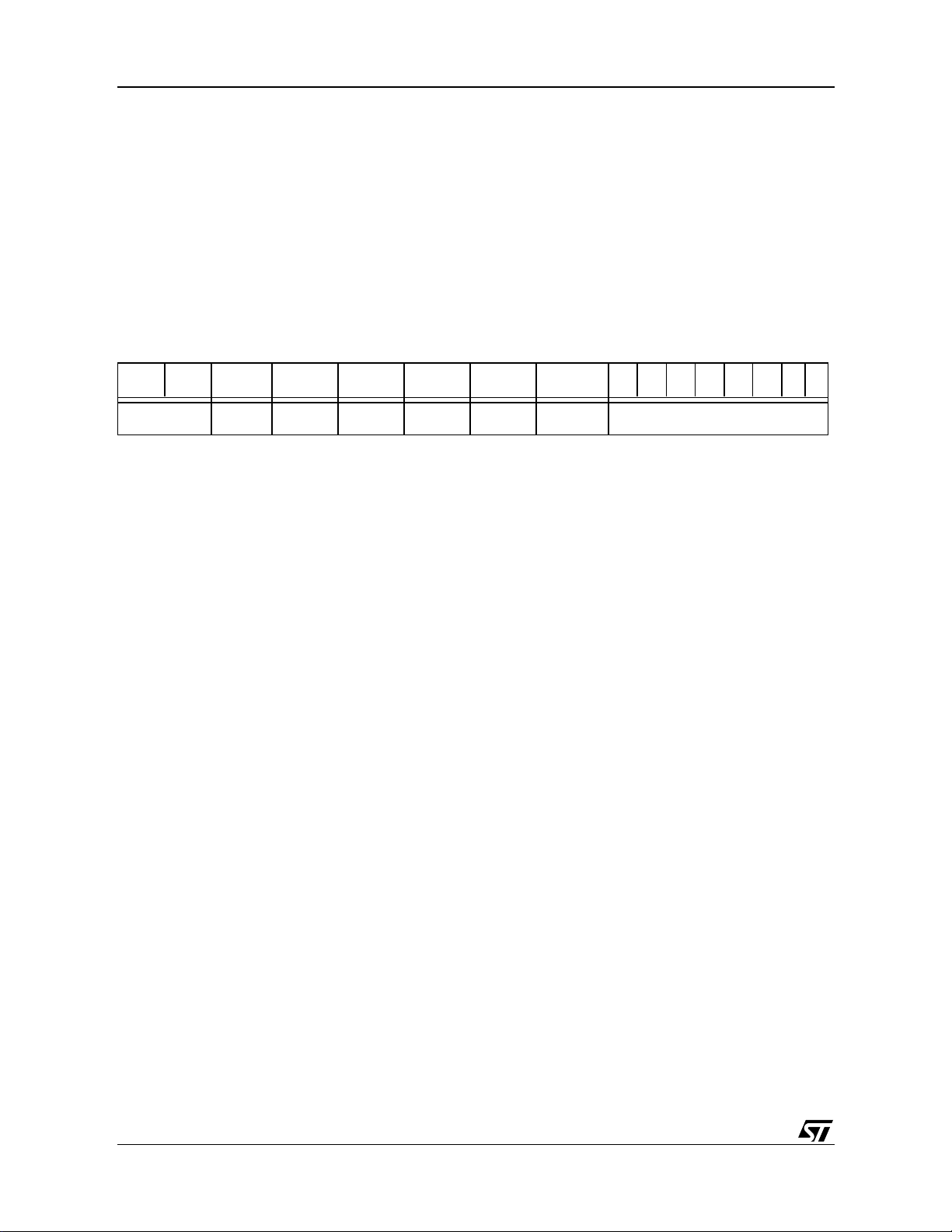

6.3.1.3 Memory Configuration register

Memory configuration registers are used to setup parameters that are same for all banks:

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved PWS TYPE B3EN B2EN B1EN B0E N R EFR

PWS: Power save mode

• If PWS bit is set to’1’, the next refresh cycle will set the memory devices in the self-refresh mode.

• The memories will exit the self-refresh mode, when the PWS mode is set to’0’.

TYPE: M e mory type:

• The TYPE bit is used to select a type of the external memory.

•1 - SDRAM

•0 - EDO

B3EN: Bank 3 enable

B2EN: Bank 2 enable

B1EN: Bank 1 enable

B0EN: Bank 0 enable

• The bank enable bits are used to enable each bank separately.

• If an AHB transfer is accessing a disabled bank, the DRAM Controller will return the error response

to the AHB master.

REFR: Refresh period

• The REFR value is used to determine the refresh period. The period can be set in the 1 us steps.

• REFR Refresh Period

• 00000000 Refresh is disabled

• 00000001 Refresh period is 1us

• 00000010 Refresh period is 2us

•.

• 11111111 Refresh period is 255us

6.4 DMA Controller

• The DMA controller is intended to be used with the Ethernet switch block to transfer Ethernet frames

between the Ethernet switch buffers and memory.

• The DMAC needs initialization before starting operation. During operation it does not need interven-

20/81

Page 21

STLC1502

tion from the ARM controller.

• In receive, when the complete frame is stored in memory, the DMAC asserts the interrupt for the

ARM that can read the frame.

• In transmit the DMAC provides an interrupt when the complete frame is transferred.

6.5 Ethernet Switch

The Ethernet switch block interfaces two MAC cores to implement a 3-port Ethernet Fast switch and MAC layer

for the Embedded VoIP network software.

Main features of the block are:

• Internal FIFOs for easy DMA transfers.

• Full duplex support using separate Tx, Rx FIFOs.

• Fast switching using hardware connections between the two MAC cores. ARM microcontroller is not

involved in the switching function.

• Support for priority mechanism for voice packets, using store-and-forward procedure for incoming

data packets.

• VLAN support

• 10/100 Mb/s data transfer rates

• The MAC cores provide 2 MII interfaces to connect two external PHYs.

The device works normally as a bidirectional switch between the two ports. When the following conditions happen the device triggers additional operations:

• Received frame destination MAC address matches device MAC address. The frame is transferred to

memory using DMA, and is not switched to the other port.

• A frame has to be transmitted by the device. In this case the block waits for the end of the current

frame being switched if any. If the frame is a voice frame, as soon as the line is free the block starts

transfer of the frame. Eventual incoming frames in the same direction are stored and forwarded after

the voice frame has been sent.

The block diagram of the Ethernet switch is shown below:

21/81

Page 22

AHB bus

APB bus

Config

Control

registers

Internal bus

DMA_MAC

MAC

MII1

Bridge/arbiter

Ethernet

switching

memory

DMA_MAC

MAC

MII2

APB bus

Config

Control

registers

STLC1502

22/81

Page 23

STLC1502

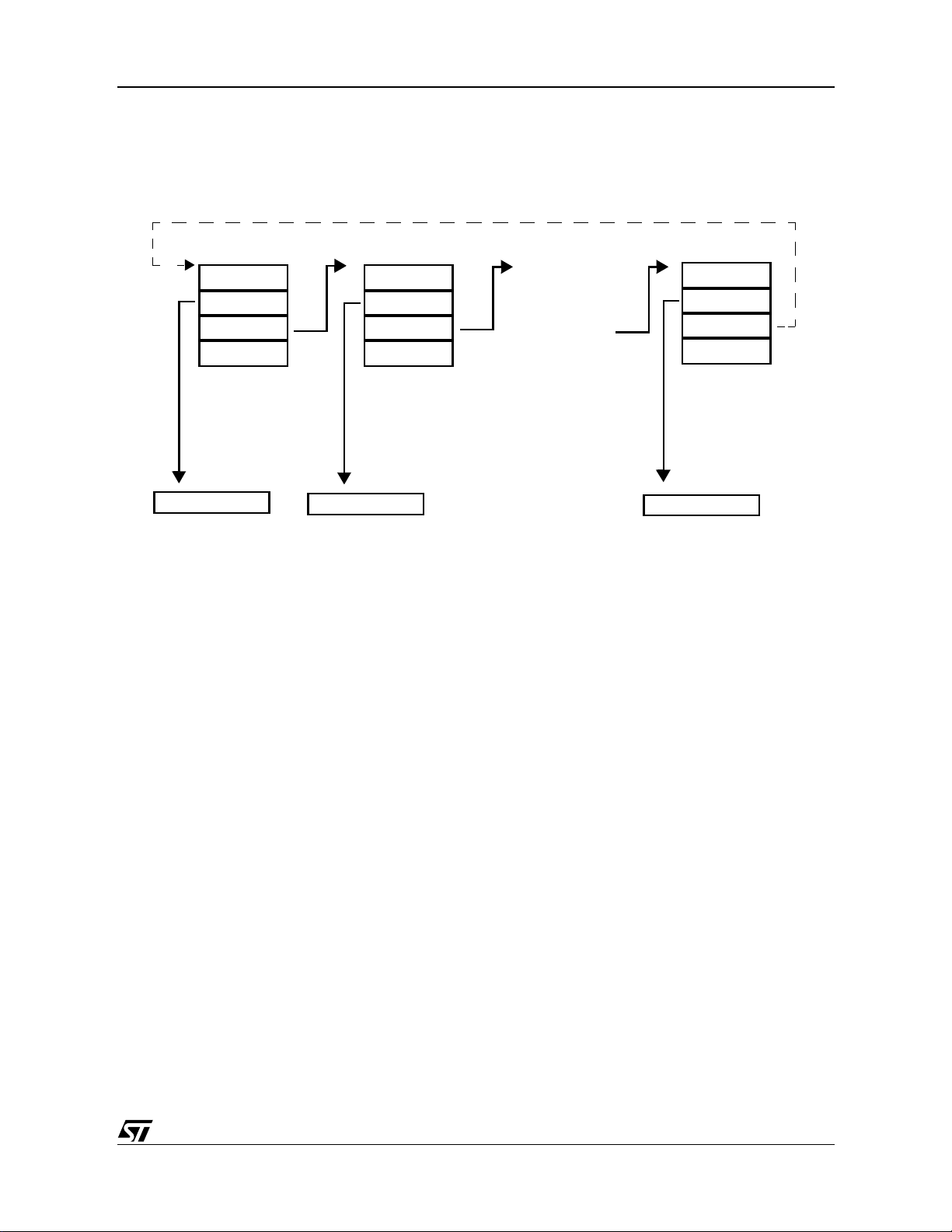

6.5.1 The DMA Descriptors Chain

The Descriptor list is the mean the CPU and the DMA_MAC use to communicate each other in order to

transmit/receive frames on the cable. This list must be properly prepared before initiating any transfer

activity to/from the cable. The Descriptor is produced by the CPU and consumed by the DMA_MAC.

DMA_Cntl

DMA_Addr

DMA_Next

Tx/Rx_Status

Descr 1

(4 X 4 Bytes)

Frame 0

DMA_Cntl

DMA_Addr

DMA_Next

Tx/Rx_S tatus

Descr 2

(4 X 4 Bytes) (4 X 4 Bytes)

Frame 1

. . .

DMA_Cntl

DMA_Addr

DMA_Next

Tx/Rx_S t at us

Descr n

Frame n

• A Descriptor is a 16-bytes element which provides the DMA_MAC with information about how to

transmit/receive a single frame and how to report the transfer status back to the CPU.

• A Descriptor can be stored in any main memory location with a 32-bit aligned address.

• The first 3 words stored in a Descriptor are expected to be the values of the 3 DMA_MAC registers

describing a DMA transfer (DMA_Cntl, DMA_Addr and DMA_Next). When the DMA_MAC fetches a

Descriptor it loads this three values into its own corresponding registers.

• The last word is to be used by the DMA_MAC to report the transfer status.

6.5.2 The Descriptor control bits

The Descriptor keeps information about a single frame transfer and how to access t he next Descriptor.

The following discussion is rela ted to 3 bits of the Descriptor: the VALID bit, the NXT_EN bit and the

NPOL_EN bit.

The Descriptor can be accessed simultaneously by the CPU and the DMA_MAC. This concurrent access

is synchronized by the VALID bit in the DM A_Cntl register. When the VALID bit is equal to 0 then the

CPU is the owner of the Des criptor. Otherwise the owner is the DMA _M AC. Since t he Des criptor can be

accessed in write mode by the owner only at any time, race conditions are guaranteed to never happen.

The NXT_EN bit enables the fetch of the Next Descriptor. When the DMA_MAC finds this bit set to 0 then

its activity is considered to be completed as soon a s the current descriptor DMA transfers have been

compl eted .

The NPOL_EN bit enables the DMA_MAC to keep polling for a non-valid Descriptor until its VALID bit is

set to one. When the DMA_MAC finds both the NPOL_EN bit and the VALID bit set to 0 then its activity is

considered to be completed.

23/81

Page 24

STLC1502

6.5.3 Transfer interrupts

The DMA_MAC can interrupt the CPU with three different levels of information about transfer completion.

The CPU can choose which interrupt needs to be enabled. The y do not exclud e each ot her though; they

can be all three enabled at the same time.

The TX_CURR_DONE (RX_CURR_ DONE) interrupt bit reports the CPU when a single Descriptor (i.e.

one frame) has been completely treated by the DMA_MAC and the CPU is agai n the owner (VALID bit

set to 0).

The TX_NEXT (RX_NEXT) in terrupt bit is set when next descriptor fetch is e nabled (NXT_EN=1 in the

current descriptor) the next Descriptor is not valid (V ALID bit is off).

The TX_DONE (RX_DONE) interrupt bit is set when a whole DMA transfer is complete. This can happen

either when the current is the last Des criptor i n t he chain (NXT_EN is off) or when the next Descriptor is

not valid yet (VALID bit is off) and the polling is disabled (NPOL_EN bit is off).

6.5.4 Frames transmission (TX)

When the CPU wants to t ransm it a set of frames on t he cable, it needs to p rovide t he DMA_M A C wi th a

Descriptor list. The CP U is expec t ed to allocat e a D es cript or for each f rame it wants to s end, to fill i t with

the DMA control information and the pointer to the frame, and to link the Descriptor in the chain. The

frames will be sent on the cable in the same order they are found in the chain.

6.5.6 Open list approach

The simplest way to construct a Descriptor chain is the open list approach. Every Descriptor but the last

one will have the DMA_Next field pointing to the next Descriptor in the chain, the NXT_EN bit and the

VALID bit on, the NPOL_EN bit on /off. The last Descriptor will be set in the same way e xcept for the

NXT_EN bit (off) and the DMA_Next field (NULL).

• The CPU starts the DMA activity loading the physical location of the first Descriptor into the DMA

Next register of the DMA_MAC and set the DMA Start register enable bit to on.

• The DMA_MAC will then keep fetching the Descriptors one by one until it finds the NXT_EN bit of the

last Descriptor set to off. Every time it completes a Descriptor (f rame) it saves the t ransfer stat us i nto

TxRx_Status, it turns the Descriptor VALID bit to off and raises the TX_CURR_DONE interrupt bit.

• When the NXT_EN bit is found to be off, that means the DMA_MAC has fetched the last Descriptor in

the chain. When it completes also this Descriptor (the end of the DMA transfer) it raises both the

TX_CURR_DONE and the TX_DONE interrupt bits.

6.5.7 Closed list approach

The approach above is easy since it doesn’t require the DMA_MAC and the CPU to synchronize their access to the Descriptor chain. The problem is that it requires the CPU to build the list every time it needs a

transfer.

A faster way to operate is building a closed Descriptor list only the first time and using the VALID bit to

mark the end of the transfe r. The polling facility could also be used to s ave the CPU from the activity of

programming the DMA Start register every time it needs to start the DMA transfer. Instead, the DMA Start

register will be activated only once and the DM A_MAC will keep poll ing the invalid descript or, raising

each time the TX_NEXT interrupt bit (if enabled), until the CPU finally sets its VALID bit to on. Since the

DMA transfer practically never ends, note that in this case the TX_DONE interrupt bit is never raised.

24/81

Page 25

STLC1502

With this approach every Descriptor will have the DMA_Next field pointing to the next Des criptor in the

chain (the last on e w ill po int to the first on e) , the NX T_EN bit, the VALID bit and the N PO L _E N bit on.

The DMA_MAC will keep fetching the Descriptors one by one until it finds one with its VALI D bit set to of f.

Every time the DMA_MAC completes a Descriptor (frame) it saves the transfer status into TxRx_Status,

it turns its VALID bit to off and raises the TX_CURR_DONE interrupt bit.

6.5.8 Frames reception (RX)

The frame reception process is somethin g that needs to be activated at the be ginning and kept always

running. For this reason the closed Descriptor list (see above) is much more useful than the open list

approach.

Again, with this approach every Descriptor will have the DMA_Next field pointing to the next Descriptor in

the chain (the last one will point to the first one), the NXT_EN bit, the VALID bit and the NPOL_EN bit on.

The CPU starts the transfer activity loading the DMA Next register of the DMA_MAC with the physical

location of the first Desc riptor and set the DMA Start register enable bit to o n.The DMA_MAC wi ll start

fetching the Descriptors one by one, driven by the frames reception from the line. Every time the

DMA_MAC completes a Descriptor (frame) it saves the transfer status into TxRx_Status, it turns its

VALID bit to off and raises the TX_CURR_DONE interrupt bit.

Eventually, the DMA_MAC will be faster than the CPU, it will wrap around the Descriptor chain and find a

Descriptor still invalid.

Then the DMA_CNT keeps polling the invalid descriptor, raising each time the TX_NE XT interrupt bit (if

enabled), until some Descriptor gets available (note that in this case some frame could be lost). In the

meantime the CPU should consume the frames received and set the VALID bit to on of all the Descriptor

released.

As soon as the DM A _CNT finds the Descript or v alid agai n, i t w ill be abl e t o co m plete t he t rans fer and t o

fetch the next Descriptor.

6.5.9 Ethernet block Register Map [0x0C680000]

The base address of the Ethernet registers is 0x0C680000

The memory map of the Dual MAC Ethernet block is shown below:

Address Register Name Notes

DMA_MAC1 Eth_base1=0x0C680000

Eth_base1+ 0x0000 DMA_ST&CNTL DMA Status and Control Register

Eth_base1+0004 DMA_INT_EN DMA Interrupt Sources Enable R egister

Eth_base1+0008 DMA_INT_STAT DMA Inter rupt Status Register

Eth_base1+000C Reserved

Eth_base1+ 0x0010 RX_DMA_START RX DMA start Register

25/81

Page 26

STLC1502

Address Register Name Notes

Eth_base1+ 0x0014 RXD_DMA_CNTL RX Data DMA Control Register

Eth_base1+ 0x0018 RXD_DMA_ADDR RX Data DMA Base Address Register

Eth_base1+ 0x001C RXD_DMA_NXT RX Data DMA Next Descriptor Address

Register

Eth_base1+ 0x0020 RX_DMA_CADDR RX DMA Current Address R egister

Eth_base1+ 0x0024 RX_DMA_CXFER RX DMA Current Transfer Count Regis-

ter

Eth_base1+ 0x0028 RX_DMA_TO RX DMA FIFO Time Out Register

Eth_base1+ 0x002C RX_DMA FIFO RX DMA FIFO Status Register

Eth_base1+ 0x0030 RXV_DMA_CNTL

RX Voice DMA Control Register

Eth_base1+ 0x0034 RXV_DMA_ADDR RX Voice DMA Base Address Register

Eth_base1+ 0x0038 RXV_DMA_NXT RX Voice DMA Next Descriptor Address

Register

Eth_base1+0x003C-

Reserved

Eth_base1+0x 004C

Eth_base1+ 0x0050 TX_DMA_START TX DMA start Register

Eth_base1+ 0x0054 TXD_DMA_CNTL TX Data DMA Control Register

Eth_base1+ 0x0058 TXD_DMA_ADDR TX Data DMA Base Address Register

Eth_base1+ 0x005C TXD_DMA_NXT TX D a ta DMA N e xt Descriptor Address

Register

Eth_base1+ 0x0060 TX_DMA_CADDR TX DMA Current Address Register

Eth_base1+ 0x0064 TX_DMA_CXFER TX DMA Current Transfer Count Regis-

ter

Eth_base1+ 0x0068 TX_DMA_TO TX DMA FIFO Time Out Register

Eth_base1+ 0x006C TX_DMA FIFO TX DMA FIFO Status Register

Eth_base1+ 0x0070 TXV_DMA_CNTL TX Voice DMA Control Register

Eth_base1+ 0x0074

26/81

TXV_DMA_AD DR TX Voice DMA Base Address Register

Page 27

STLC1502

Address Register Name Notes

Eth_base1+ 0x0078 TXV_DMA_NXT TX Voice DMA Next Descriptor Address

Register

Eth_base1+0x007C-

Reserved

Eth_base1+ 0x00FC

Eth_base1+ 0x0100 RX_FIFO_0 R X FIFO 32 bit word #0

.... ... ...

Eth_base1+ 0x013C RX_FIFO_15 RX FIFO 32 bit word #15

Eth_base1+ 0x0180-

Reserved

Eth_base1+ 0x01FC

Eth_base1+ 0x0200 TX_FIFO_0 T X FIFO 32 bit word #0

.... ... ...

Eth_base1+ 0x023C TX_FIFO_15 TX FIFO 32 bit word #15

Eth_base1+ 0x0280-

Reserved

Eth_base1+ 0x03FF

Eth_base+ 0x0400-

MAC110

Eth_base+ 0x07FF

DMA_MAC2 Eth_base2 = 0x0C680800

Eth_base2+ 0x000 DMA_ST&CNTL DMA Status and Control Register

Eth_base2+0x0004 D MA_INT_EN DMA Interrupt Sources Enable Register

Eth_base2+0x8008 DMA_INT_STAT DMA Interrupt Status Register

Eth_base2+0x000C Reserved

Eth_base2+ 0x0010 RX_DMA_START RX DMA start Register

Eth_base2+ 0x0014 RXD_DMA_CNTL RX Data DMA Control Register

Eth_base2+ 0x0018 RXD_DMA_ADDR RX Data DMA Base Address Register

Eth_base2+ 0x001C RXD_DMA_NXT RX Data DMA Next Descriptor Address

Register

Eth_base2+ 0x0020 RX_DMA_CADDR RX DMA Current Address R egister

27/81

Page 28

STLC1502

Address Register Name Notes

Eth_base2+ 0x0024 RX_DMA_CXFER RX DMA Current Transfer Count Regis-

ter

Eth_base2+ 0x0028 RX_DMA_TO RX DMA FIFO Time Out Register

Eth_base2+ 0x002C RX_DMA FIFO RX DMA FIFO Status Register

Eth_base2+ 0x0030 RXV_DMA_CNTL

RX Voice DMA Control Register

Eth_base2+ 0x0034 RXV_DMA_ADDR RX Voice DMA Base Address Register

Eth_base2+ 0x0038 RXV_DMA_NXT RX Voice DMA Next Descriptor Address

Register

Eth_base2+0x003C-

Reserved

Eth_base2+004C

Eth_base2+ 0x0050 TX_DMA_START TX DMA start Register

Eth_base2+ 0x0054 TXD_DMA_CNTL TX Data DMA Control Register

Eth_base2+ 0x0058 TXD_DMA_ADDR TX Data DMA Base Address Register

Eth_base2+ 0x005C TXD_DMA_NXT TX D a ta DMA N e xt Descriptor Address

Register

Eth_base2+ 0x0060 TX_DMA_CADDR TX DMA Current Address Register

Eth_base2+ 0x0064 TX_DMA_CXFER TX DMA Current Transfer Count Regis-

ter

Eth_base2+ 0x0068 TX_DMA_TO TX DMA FIFO Time Out Register

Eth_base2+ 0x006C TX_DMA FIFO TX DMA FIFO Status Register

Eth_base2+ 0x0070 TXV_DMA_CNTL TX Voice DMA Control Register

Eth_base2+ 0x0074

TXV_DMA_AD DR TX Voice DMA Base Address Register

Eth_base2+ 0x0078 TXV_DMA_NXT TX Voice DMA Next Descriptor Address

Register

Eth_base2+0x007C-

Reserved

Eth_base2+ 0x00FC

Eth_base2+ 0x0100 RX_FIFO_0 R X FIFO 32 bit word #0

.... ... ...

28/81

Page 29

Address Register Name Notes

Eth_base2+ 0x013C RX_FIFO_15 RX FIFO 32 bit word #15

STLC1502

Eth_base2+ 0x0180-

Reserved

Eth_base2+ 0x01FC

Eth_base2+ 0x0200 TX_FIFO_0 T X FIFO 32 bit word #0

.... ... ...

Eth_base2+ 0x023C TX_FIFO_15 TX FIFO 32 bit word #15

Eth_base2+ 0x0280-

Reserved

Eth_base2+ 0x03FF

Eth_base2+ 0x0400Eth_base2+ 0x07FF

6.6 Arbiter

The arbiter is used to ensure that, at any point in time, only one master has access to the bus. It performs this

function by observing all of the bus master requests to use the bus, and deciding which is currently the highest

priority. It has a standard interface to all bus masters and split-capable slaves in the system. However it does

not support SPLIT bus transfers.

A bus m aster m ay reques t the bus during any cycl e by setti ng its HB USRE Q output HIGH . Thi s is th en sam pled

by the arbiter on the rising edge of the clock, and passed through the priority algorithm to decide which master

will have access to the bus during the next cycle. The HGRANT then outputs change to indicate which master

currently is granted control of the bus.

The HLOCK signals may be used to ensure that during an indivisible transfer, the current grant outputs do not

change. HLOCK must be asserted at least one cycle before the l ocked transfer to prevent t he arbiter from

changing the grant signals. When more than one master requests ownership of the system bus , the priority used

for arbitration is:

• Highest: TIC

• Printer Drive Control

• DMA Controller

• Lowest: ARM7TDMI (default master)

The ARM7TDMI will periodically assume top priority on the system bus: this period can be programmed. Also,

it will assume top priority when an interrupt occurs, if the interrupt mode is enabled. During reset, and when no

other masters are requesting control of the bus, the ARM7TDMI is selected as the currently granted master.

This minimizes the delay required for the core to perform a transfer on the bus, as it does not have to wait to be

granted control of the bus before it can start a new transfer.

The system also requires a default master, which is selected when no masters are granted control of the bus,

for example, when all system bus masters are waiting for split transfers to complete. The default master performs IDLE transfers while it is granted control of the bus. The bus grant output s may change while HREADY

is LOW, but the newly granted master may only drive the bus when the current tr ansfer has completed. This

requires that bus masters only drive the bus after they detect that both their HGRANT and HREADY inputs are

set HIGH.

All registers used in the system are clocke d from the rising edge of the system clock HCLK, and use the asynchronous reset HRESETn. The arbiter control and status registers are accessed via the APB bus.

MAC110 Refer to the InSilicon MAC110 specifica-

tion (see Ref. [2])

29/81

Page 30

STLC1502

6.7 TIC-Test Interface Controller

The Test Interface Controller (TIC) is a state machine that provides an A M B A AHB bus master for system test.

It reads test write and address data from the external data bus TESTBUS (XD), and uses the External Bus Interface (part of the DRAM Controller) to drive the external bus with test read data, allowing the use of only one

set of outpu t tr istate b uffers onto TESTBUS .

The TIC is used to convert externally applied t est vect ors into internal transf ers on t he AHB bus. A three-wire

external handshake protocol is used, with t wo inputs c ontroll ing t he ty pe of v ect or that i s appl ied and a single

output that indicates when the next vector can be applied. Typicall y the TIC is the highest pri ority AMBA bus

master, which ensures test access under a ll conditions. The TIC model supports address incrementing and control vectors. This means that the address for burst transfers can automatically be generated by the TIC.

6.8 AHB-ASB bridge

The APB bridge is the only bus master on the Advanced Peripheral Bus. In fact, the APB bridge is also a slave

on the AHB. The bridge unit converts ASB transfers into APB transfers. On the APB bus only 16 bits wide data

accesses are permitted. 32 bit wide and 8 bit wide transfers are not supported. All the APB peripherals decodes

all the 16 bits of the PA bus.

APB decoder space PA(15:0)

APB decoding scheme

Every area is 128k x 16 bits but the area actually available is 32k x 16 due to the fact that the address lines on

the APB bus are 16 (PA(15:0)). That means that in every area dedicated to the several block on the APB bus

only the first FFFF is usable.

7.0 APB bus

The APB bus is a 16 bits data and 16 bi ts address bus. The blocks attached on this bus are described in the

following sections while the memory area is reported in the following figure.

All the addresses in the APB space are word aligned (addresses are multiples of four)

30/81

Page 31

Figure 8: APB Mem ory Map

0C000000

Timer

0C07FFFF

STLC1502

Miscellaneous I/O

Interrupt Controller

Dual Port SRAM

Reserved

SPI port

I2C port

UART

GPIO

0C080000

0COFFFFF

0C100000

0C17FFFF

0C180000

0C1FFFFF

0C200000

0C27FFFF

0C280000

0C2FFFFF

0C300000

0C37FFFF

0C380000

0C3FFFFF

0C400000

0C47FFFF

HPI

Watchdog Timer

EDM regs

ESM regs

Ethernet Mac DMACs

DMAC

ARM/D950 bridge

0C480000

0C4FFFFF

0C500000

0C57FFFF

0C580000

0C5FFFFF

0C600000

0C67FFFF

0C680000

0C6FFFFF

0C700000

0C7FFFFF

0C800000

0C8FFFFF

31/81

Page 32

STLC1502

7.1 Timer

The Timer module connects to the Advanced Peripheral Bus.

CKTIMER

To PIC

To EDM

PWRITE

PENABLE

BnRES

DSEL_TIMER

PA[15:0]

PRDAT A [15:0]

PWDATA [15:0]

INTCT1

INTCT2

INTCT3

INTCT4

Prescaler

Load Registers

Control Registers

Control Logic

Control Section

FRC - Free Ru nning

counter

FRC - Free Ru nning

counter

Timer Section

Figure 9: Timer block diagram

This implementation consists of two major sections comprising:

• All the control logic

• Two instantiations of the free-running counters (FRCs)

The timer module has a series of memory-mapped locations that allow the state of the timer module to be read

from and written to via the APB.

7.1.1 Timer introduction

Two timers are defined and can be selected by the Control register:

• Free-running mode:The timer wraps after reaching its zero value, and continues to count down from

the maximum value.

• Periodic timer mode:The counter generates an interrupt at a constant interval.

7.1.2 Timer operation

The timer is loaded by writing to the load register and, if enabled, counts down to zero. When zero is reached,

an interrupt is generated. The interrupt may be cleared by writing to the Clear register.

After reaching a zero count, if the timer is operating in free-running mode it continues to decrement from its maximum value. If periodic timer mode is selected, the timer reloads from the load register and continues to decrement. In this mode the timer effectively generates a periodi c interrupt. The mode is selected by a bit in the

Control register.

At any point, the current timer value may be read from the Value register.

The timer is enabled by a bit in the control register. A t reset , t he timer is di sabled, the i nt errupt i s cleared and

the Load register is undefined. The mode and prescale values are also undefined.

32/81

Page 33

Load Control

Load Register Control Register

STLC1502

Timer

16-bit Down Counter

Terminal Count

Clock

Value

Figure 10: Timer block diagram

The timer clock is generated by a prescale unit. The timer clock may be one of:

• The CKTIMER

• The CKTIMER divided by 16, generated by 4 bits of prescale

• the CKTIMER divided by 256, generated by a total of 8 bits of prescale

CKTIMER

Divide

by 16

Divide

by 16

Interrupt

Timer

Clock

Prescale

Select

Figure 11: Pre-scaler bloc k diagram

Using the recommended 2.208Mhz clock, the minimum interval between two timer interrupt is 452nsec (corresponding to the 2.208Mhz period) while the maximum interval between two timer interrupt is around 6sec.

7.1.3 Timer register map [0x0C000000]

The base address of the timer register is 0x0C000000

33/81

Page 34

STLC1502

The offset of any particular register from the base address is the following.

Address Register Name R/W Notes

TimerBase + 0x00 Timer1Load R/W Timer1Load. The Load register

contains the initial value of the timer

and is also used as the reload

value in periodic timer mode.

TimerBase + 0x04 Timer1Value R Timer1Value. The Value location

gives the current value of the timer.

TimerBase + 0x08 Timer1Control R/W Timer1Control. The Control regis-

ter provides enable/disable, mode

and prescale configurations for the

timer (see Figure 10).

TimerBase + 0x0C T imer1Clear W Timer1Clear. Writing to the Clear

location clears an interrupt generated by the counter timer.

TimerBase + 0x10 Timer2Load R/W Timer2Load. The Load register

contains the initial value of the timer

and is also used as the reload

value in periodic timer mode.

TimerBase + 0x14 Timer2Value R Timer2Value. The Value location

gives the current value of the timer.

TimerBase + 0x18 Timer2Control R/W Timer2Control. The Control regis-

ter provides enable/disable, mode

and prescale configurations for the

timer (see Figure 10).

TimerBase + 0x1C T imer2Clear W Timer2Clear. Writing to the Clear

location clears an interrupt generated by the counter timer.

TimerBase + 0x20 Timer3Load R/W Timer3Load. The Load register

contains the initial value of the timer

and is also used as the reload

value in periodic timer mode.

TimerBase + 0x24 Timer3Value R Timer3Value. The Value location

gives the current value of the timer.

34/81

Page 35

STLC1502

Address Register Name R/W Notes

TimerBase + 0x28 Timer3Control R/W Timer3Control. The Control regis-

ter provides enable/disable, mode

and prescale configurations for the

timer (see Figure 10).

TimerBase + 0x0C T imer3Clear W Timer3Clear. Writing to the Clear

location clears an interrupt generated by the counter timer.

TimerBase + 0x30 Timer4Load R/W Timer4Load. The Load register

contains the initial value of the timer

and is also used as the reload

value in periodic timer mode.

TimerBase + 0x34 Timer4Value R Timer4Value. The Value location

gives the current value of the timer.

TimerBase + 0x38 Timer4Control R/W Timer4Control. The Control regis-

ter provides enable/disable, mode

and prescale configurations for the

timer (see Figure 10).

TimerBase + 0x3C T imer4Clear W Timer4Clear. Writing to the Clear

location clears an interrupt generated by the counter timer.

7.2 Watchdog Timer

STLC1502 contains a Watchdog timer. This timer is used to reset the ARM7 in case of a software deadlock.

The watchdog timer generates a hot reset when it overflows which will restart the ARM, but the code wi ll

not be downloaded again. The timer should be cleared by the software before it overflows.

It is based on a 8 bit counter which is clocked by a slow signal coming from a 17 bit prescaler clocked by

the system clock.

So the elapsing time of the watchdog timer depend on the system clock:

SYS_CLK:

13MHz => 2.58 seconds

26MHz => 1.29 seconds

39MHz => 0.86 seconds

52MHz => 0.64 seconds

This peripheral consists of a timer that continue to run and to reset the core if the software doesn’ t clear

it before it elapses. The software can clear or disable the timer by writing the WDOG_CONTROL register

7.2.1 Watch Dog Register Map [0x0C500000]

35/81

Page 36

STLC1502

The base address of the WDT register is 0x0C500000

The memory map of the WDT peripheral is shown below:

Address Register Name R/W Notes

ESMBase + 0x00 WDTControl R/W WDT cont rol register

ESMBase + 0x04 WDT reset_stat R/W WDT reset the status register

ESMBase + 0x08 WDT max_count R/W WDT programmable max count

ESMBase + 0x0C WDT counter R WDT internal counter value

7.3 Miscellaneous I/O

All the registers not related to any module attac hed to the APB/AHB bus such as EII, Test are considered M iscellaneous I/O. Additionally, the ESM configuration register and the Dual Port register are also part of this block.

7.3.1 Miscellaneous Register Map [0x0C080 000]

The Miscellaneous register address is

0x0C080000

Address Register Name R/W Notes

MISC_regBase+ 0x00 Contr ol W This register allows to control the

reset/boot procedure and some

other control features

MISC_regBase+ 0x10 Status W This register allows DSP section

setting

MISC_regBase+ 0x20 IDENTIFICATION R This register provides informa-

tions about the device/system

7.4 Interrupt Controller

In an ARM system, two levels of interrupt are available:

• FIQ (Fast Interrupt Request) for fast, low latency interrupt handling

• IRQ (Interrupt Request) for more general interrupts

Ideally, in an ARM system, only a single FIQ source would be in use at any particular time. This provides a true

low-latency interrupt, because a single source ensures that the interrupt service routine may be executed directly without the need to determine the source of the interrupt. It also reduces the int errupt latency because the

extra banked registers, which are available for FIQ interrupts, may be used to maximum efficiency by preventing

the need for a context save.

Separate interrupt controllers are used for FIQ and IRQ.

There are 15 interrupt causes available in the IRQ controller coming from:

• Software (internally generated)

•Timer1

36/81

Page 37

STLC1502

•Timer2

•UART

• Dual Port RAM

•I2C

• Ethernet switch DMAC1

• Ethernet switch DMAC2

• SPI

•DMAC

•IRQ1/GPIO18

•IRQ2/GPIO19

•IKybd

•HPI

•Timer3

Even if only a single bit position is defined for FIQ, the interrupt controller can drive one of the interrupt source

(IRQ interrupt sources), through a register, in order to generate the FIQ interrupt.

The IRQ interrupt controller uses a bit position for each different interrupt source.

All interrupt source inputs must be active HIGH and level sensitive and it remain active until the interrupt cause

has been cancelled.

No hardware priority scheme nor any form of interrupt vectoring is provided, because thes e functions can be

provided in software.

A programmed interrupt register is also provided to generate an interrupt under software control.

Every interrupt source can be masked.

7.4.1 Interrupt control

The IRQ interrupt management is done as described in the following:

• An interrupt is generated by a given device/source;

• This cause is readable by the IRQRawStatus register;

• If not masked (the mask is set by IRQEnableSet and reset by IRQEnableClear), this interrupt will

generate a IRQ signal to the ARM and the interrupt source will be known by a read of the IRQStatus

register.

• The ARM will serve the IRQ reading at first in the IRQStatus the active interrupt requests and will

execute with a given priority the proper interrupt routine. Every routine must erase (quite soon) in

some way its interrupt request source. This causes also for the proper bit in the IRQRawStatus register and in the IRQStatus register to disappear.

The same interlock is present for the FIQ interrupt.

7.4.2 Interrupt control scheme

37/81

Page 38

STLC1502

BCLK

PWRITE

PENABLE

BnRES

DSEL_INT

PA[15:0]

PRDATA [15:0]

PWDATA [15:0]

Figure 11: Interrupt block schem e

FIQ

Control

NFIQ

NFIQ

NIRQ

IRQSource[13:0]

IRQ

NIRQ

Control

38/81

Page 39

INTERRUPT_MASK

STLC1502

Enable

IRQRawStatus

Interru p t Source

Other Interrupt Bit Slices

Figure 12: IRQ control block

7.4.3 Interrupt register map [0x0C100000]

The base address of the timer register is

The offset of any particular register from the base address is the following.

Address Register Name R/W Notes

0x0C100000

IRQStatus

Interrupt Pending

nIRQ

Int.Base + 0x00 IRQStatus R For every IRQ interrupt cause,

a ‘1’ means an active pending

interrupt that has to be served

by the ARM

Int Base+ 0x04 IRQRaw Status R For every IRQ interrupt source,

a ‘1’ means an active pending

interrupt “before” the mask (w/

o considering the mask)

Int.Base + 0x08 IRQEnabl eSet R/W Fo r every IRQ interrupt source,

a ‘0’ means that even if an

interrupt source is active, it has

to be stopped (masked). The

write operation of 1 to a given

bit, enable the corresponding

interrupt

39/81

Page 40

STLC1502

Address Register Name R/W Notes

Int.Base + 0x0C IRQSoft R/W Only the bit 1 ha s to be used.

Writing ‘1’ it generates an interrupt mapped in the bit 1 of the

IRQStatus and of the IRQRa wStatus registers. Writing ‘0’ the

software interrupt cause is

erased.

Int.Base + 0x10 FIQStatus R For the FIQ interrupt cause, ‘1’

means an active pending interrupt that has to be served by

the ARM.

Int Base + 0x14 FIQRawStatus R Fo r the IRQ interrupt source, a

‘1’ means an active pending

interrupt “before” the mask (w/

o considering the mask)

Int.Base + 0x18 FIQEnableSet R/W For the FIQ interrupt source, a

‘0’ means that even if an interrupt source is active, it has to

be stopped (masked). The

write operation of 1 to the bit0,

enables the interrupt

Int.Base + 0x1C IRQEnableClear W The write operation of 1 to a

given bit, disables the corresponding interrupt. As consequence, the corresponding bit

in the IRQEnableSet goes to 0

(interrupt disabled).

Int.Base + 0x20 FIQEnableClear W The write operation of 1 into

the bit 0 disables FIQ interrupt

cause. As a result, the bit 0 in

the FIQEnableSet goes to 0

(interrupt disabled).

Int.Base + 0x24 IRQTestSource R/W Usable wh en the bit 0 of the

IRQSourceSel is set to one. In

this case this register is the

interrupt source cause. If set,

the cause is active (interrupt

generated) while if reset, the

cause is not active.

40/81

Page 41

STLC1502

Address Register Name R/W Notes

Int Base + 0x28 IRQSourceSel R/W Select the test mode of the IRQ

cause on the interrupt controller (if the bit 0 is set). In this

case the IRQTestSource

becomes the interrupt source

cause.

Int.Base + 0x2C FIQTestSource R/W Usable when the bit 0 of the

FIQSourceSel is set to one. In

this case this register is the

interrupt source cause. If set,

the cause is active (interrupt

generated) while if reset, the

cause is not active.

Int Base + 0x30 FIQSourceSel R/W Select the test mode of the FIQ

cause on the interrupt controller (if the bit 0 is set). In this

case the FIQTestSource

becomes the interrupt source

cause. Moreover this register

contains also the selection for

the FIQ interrupt cause.

7.5 SPI-Serial Peripher al Interface

The Serial Peripheral Interface (SPI) allows full-duplex, synchronous, serial communication with external

devices. An SPI system may consist of a mas ter and one or more slaves or a system in which devices

may be either masters or slaves.

The SPI is normally used for communication between the microcontroller and external peripherals.

7.5.1 Main Features

• Full duplex, three-wire synchronous transfers

• Master mode operation (clock generation)

• Four master mode frequencies

• Four programmable master bit rates

• Programmable clock polarity and phase

• End of transfer interrupt flag

• Write collision flag protection

• Master mode fault protection capability.

The SPI is connected to external devices through 3 pins:

SMI: Master In

SMO: Master Out

SCK: Serial Clock p in

41/81

Page 42

STLC1502

When the master device transmits data to a slave device via SMO pin, the slave device responds by sending data to the master device to the SMI. This implies full duplex transmission with both data out and data

in synchronized with the same clock signal (which is provided by the master device via the SCK pin).

Thus, the byte transmitted is replaced by the byte received and eliminates the need for separate transmitempty and receiver-full bits. A status flag is used to indicate that the I/O operation is complete.

The MSB is transmitted first.

Four possible data/clock timing relationships may be chosen.

7.5.2 Programming procedure

The SPI interface contains 3 dedicated registers:

• A Control Register (CR)

• A Status Register (SR)

• A Data Register (DR)

Check the register description section for bits position and functions.

Select the SPR0 & SPR1 bits to define the serial clock baud rate.

Select the CPOL and CPHA bits to define one of the four relationships between the data transfer and the

serial clock.

The transmit sequence begins when a byte is written in the DR register. The data byte is parallely loaded

into the 8-bit shift register (from the internal bus) du ring a write cycle and then shifted out serially to the

SMO pin most significant bit first. When data transfer is complete:

The SPIF bit is set by hardware

.An interrupt is generated if the SPIE bit is set and the I bit in the CCR register is cleared.

During the last clock cycle the SPIF bit is set, a copy of the data byte received in the shift register

is moved to a buffer. When the DR register is read, the SPI peripheral returns this buffered value.

Clearing the SPIF bit is performed by the following software sequence:

1. An access to the SR register while the SPIF bit is set

2. A read to the DR register.

Note: While the SPIF bit is set, all writes to the DR register are inhibited until the SR register is read.

7.5.3 Data Transfer Format

During an SPI transfer, data is simultaneously transmitted (shifted out serially) and received (shifted in serially). The serial clock is used to synchronize the data transfer during a sequence of eight clock pulses.

Four possible timing relationships may be chosen by software, using the CPOL and CPHA bits.

The CPOL (clock polarity) bit controls the steady state value of the clock when no data is being transferred.

The combination between the CPOL and CPHA (clock phase) bits selects the data capture clock edge.

The master device applies data to its SMO pin before the capture clock edge.

CPHA bit is set:

The second edge on the S CK pin (f alling edge if the CPOL bit is r es et, rising edge if the CPOL bit is se t)

is the MSBit capture strobe. Data is latched on the occurrence of the second clock transition.

CPHA bit is reset

The first edge on the SCK pin (falling edge if CPOL bit is set, rising edge if CPOL bit is reset) is the MSBit

capture strobe. Data is latched on the occurrence of the first clock transition.

The slave select signal is necessary in case more than one slave devices are connected on the seral bus.

The slave select can be generated with a GPIO pin.

42/81

Page 43

STLC1502

7.5.4 Collision management

Collision is defined as a write of the DR register while the internal serial clock (SCK) is in the process of

transfer. The WCOL bi t in the S R regist er is set if a write co llision oc curs. No S PI inte rrupt is generat ed

when the WCOL bit is set (the WCOL bit is a status flag only). Clearing the WCOL bit is done through a

software sequence:

1-Read SR

2-Read DR

7.5.5 SPI register map [0x0C280000]

The base address of the Remap & Pause register is 0x0C280000.

43/81

Page 44

STLC1502

The offset of any particular register from the base address is the following.

Address Register Name R/W Notes

SPI_regBase+ 0x04 SPIDR R/W SPI Data I/O register.

SPI_regBase+ 0x08 SPICR R /W SPI configuration register

SPI_regBase+ 0x0C SPISR R/W SPI status register

7.6 I 2C bus interfa ce

The I2C Bus Interface serves as an interface between the microcontroller and the serial I2C bus. It provides both multimaster and slave functions, and controls all I2C bus-specific sequencing, protocol, arbitration and timing. It supports fast I2C mode (400kHz).

7.6.1 Main Features

• Parallel-bus/I2C protocol converter

• Multi-master capability

• 7-bit/10-bit Addressing

• Transmitter/Receiver flag

• End-of-byte transmission flag

• Transfer problem detection

I2C Master Features:

• Clock generation

• I2C bus busy flag

• Arbitration Lost Flag

• End of byte transmission flag

• Transmitter/Receiver Flag

• Start bit detection flag

• Start and Stop generation

I2C Slave Features:

• Stop bit detection

• I2C bus busy flag

• Detection of misplaced start or stop condition

• Programmable I2C Address detection

• Transfer problem detection

• End-of-byte transmission flag

• Transmitter/Receiver flag

7.6.2 General Description

In addition to receiving and transmitting data, this interface converts it from serial to parallel format and

vice versa, using either an interrupt or polled by software. The interface is connected to the I2C bus by a

data pin (SDAI) and by a clock pin (SCLI). It can be connected both with a standard I2C bus and a Fast

I2C bus. This selection is made by software.

The interface can operate in the following modes:

– Slave transmitter/receiver

– Master transmitter/receiver

44/81

Page 45

STLC1502

By default, it operates in slave mode. The interface automatically switches from slave to master after it

generates a START condition and from master to slave in case of arbitration loss or a STOP generation,

allowing then Multi-M a s ter c a pa bilit y.

In Master mode, it initiates a data transfer and generates the clock signal. A serial data transfer always

begins with a start condition and ends with a stop condition. Both start and stop conditions are generated

in master mode by software.

In Slave mode, the interface is capable of recognizing its own address (7 or 10 bits), and the General Call

address. The General Call address detection may be enabled or disabled by software.

Data and addresses are transferred as 8-bit bytes, MSB first. The first byte(s) following the start condition

contain the address (one in 7-bit mode, two in 10-bit mode). The address is always transmitted in Master

mode. A 9th clock pulse follows the 8 clock cycles of a byte transfer, during which the receiver must send

an acknowledge bit to the transmitter.

• Acknowledge may be enabled and disabled by software. The I 2 C interface address and/or general

call address can be selected by software. The speed of the I 2 C interface may be selected between

Standard (0-100KHz) and Fast I2C (100-400KHz).

• In transmitter mode the interface holds the clock in low before transmission to wait for the microcontroller to write the byte in the Data Register.

• In receiver mode: the interface holds the clock line low after reception to wait for the microcontroller

to read the byte in the Data Register.

• The SCL frequency (Fscl) is controlled by a programmable clock divider which depends on the I 2 C

bus mode.