Page 1

RHRP640CC, RHRP650CC, RHRP660CC

January 1998 File Number 4464

6A, 400V - 600V Hyperfast Dual Diodes

RHRP640CC, RHRP650CC and RHRP660CC are hyperfast

dual diodes with soft recovery characteristics (t

< 30ns).

rr

They have half the recovery time of ultrafast diodes and are

silicon nitride passivated ion-implanted hepaticas planar

construction.

These devices are intended for use as freewheeling/clamping

diodes and rectifiers in a variety of switching power supplies

and otherpower switching applications. Their low stored charge

and ultrafast soft recovery minimize ringing and electrical noise

in many power switching circuits reducing power loss in the

switching transistors.

Formerly developmental type TA49057.

Ordering Information

PART NUMBER PACKAGE BRAND

RHRP640CC TO-220AB RHRP640C

RHRP650CC TO-220AB RHRP650C

RHRP660CC TO-220AB RHRP660C

NOTE: When ordering, use the entire part number.

Features

• Hyperfast with Soft Recovery . . . . . . . . . . . . . . . .<30ns

• Operating Temperature . . . . . . . . . . . . . . . . . . . . 175

o

• Reverse Voltage Up To. . . . . . . . . . . . . . . . . . . . . . .600V

• Avalanche Energy Rated

• Planar Construction

• Related Literature

- TB334 “Guidelines for Soldering Surface Mount

Components to PC Boards”

Applications

• Switching Power Supplies

• Power Switching Circuits

• General Purpose

Symbol

K

C

Package

CATHODE

(FLANGE)

A

1

JEDEC TO-220AB

A

2

ANODE 2

CATHODE

ANODE 1

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

Page 2

RHRP640CC, RHRP650CC, RHRP660CC

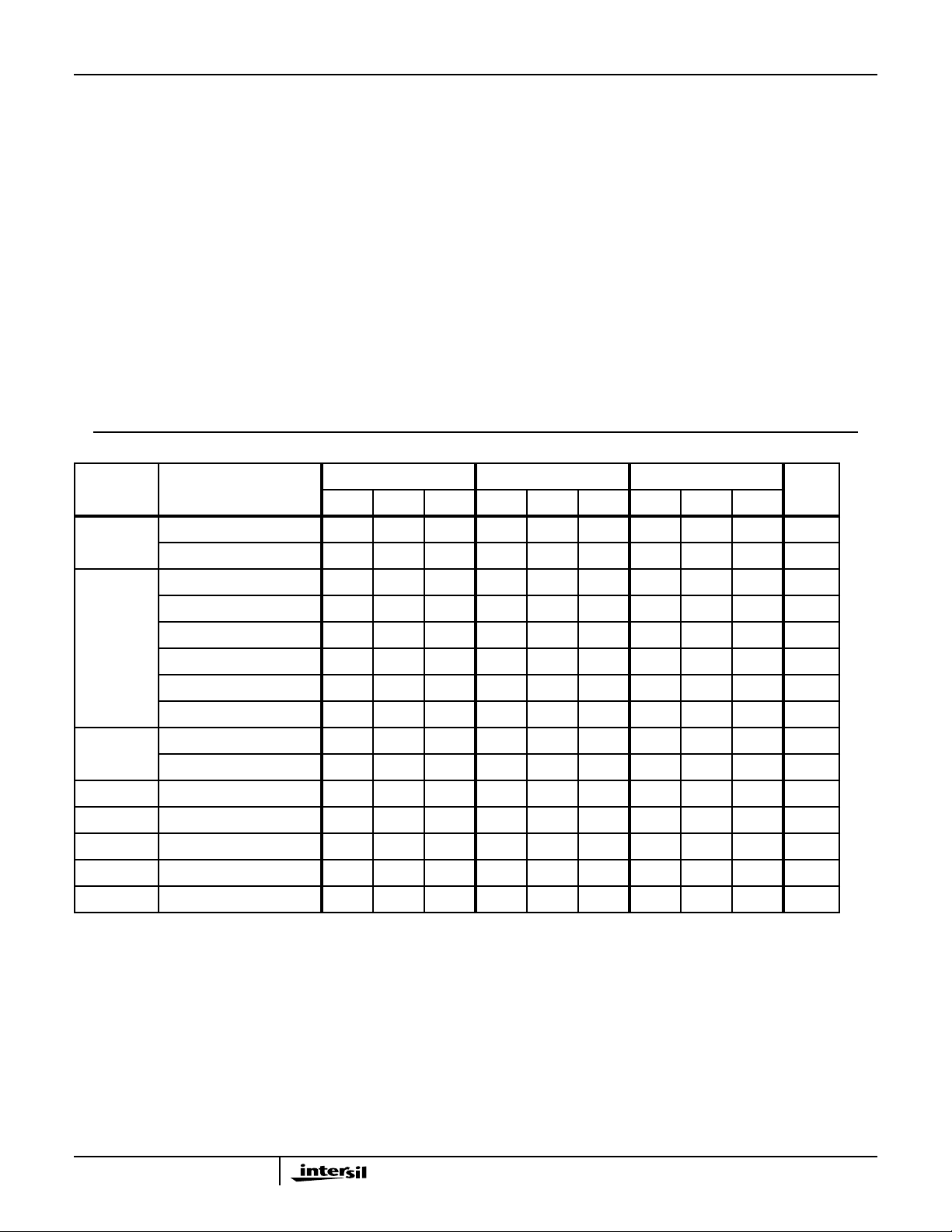

Absolute Maximum Ratings (Per Leg) T

= 25oC, Unless Otherwise Specified

C

RHRP640CC RHRP650CC RHRP660CC UNITS

Peak Repetitive Reverse Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

Working Peak Reverse Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . V

RRM

RWM

DC Blocking Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .V

Average Rectified Forward Current . . . . . . . . . . . . . . . . . . . . . . . . . . .I

F(AV)

400 500 600 V

400 500 600 V

400 500 600 V

R

666A

TC = 152oC

Repetitive Peak Surge Current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . I

FSM

12 12 12 A

Square Wave, 20kHz

Nonrepetitive Peak Surge Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . I

FSM

60 60 60 A

Halfwave, 1 phase, 60Hz

Maximum Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .P

Avalanche Energy (See Figures 10 and 11). . . . . . . . . . . . . . . . . . . . . E

Operating and Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . .T

STG,TJ

D

AVL

50 50 50 W

10 10 10 mJ

-65 to 175 -65 to 175 -65 to 175

Maximum Temperature for Soldering

Leads at 0.063in (1.6mm) from Case for 10s . . . . . . . . . . . . . . . . . . . . T

Package Body for 10s, see Tech Brief 334. . . . . . . . . . . . . . . . . . . . T

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Electrical Specifications (Per Leg) T

= 25oC, Unless Otherwise Specified

C

pkg

300

L

260

300

260

300

260

RHRP640CC RHRP650CC RHRP660CC

SYMBOL TEST CONDITION

V

F

IF = 6A - - 2.1 - - 2.1 - - 2.1 V

UNITSMIN TYP MAX MIN TYP MAX MIN TYP MAX

IF = 6A, TC = 150oC - - 1.7 - - 1.7 - - 1.7 V

I

R

VR = 400V - - 100 ------µA

VR = 500V -----100---µA

VR = 600V --------100µA

VR = 400V, TC = 150oC--500------µA

VR = 500V, TC = 150oC-----500---µA

VR = 600V, TC = 150oC--------500µA

t

rr

IF = 1A, dIF/dt = 200A/µs- -30- -30- -30ns

IF = 6A, dIF/dt = 200A/µs- -35- -35- -35ns

t

a

t

b

Q

RR

C

R

θJC

IF = 6A, dIF/dt = 200A/µs - 16 - - 16 - - 16 - ns

IF = 6A, dIF/dt = 200A/µs - 8.5 - - 8.5 - - 8.5 - ns

IF = 6A, dIF/dt = 200A/µs - 45 - - 45 - - 45 - nC

VR = 10V, IF = 0A - 20 - - 20 - - 20 - pF

J

--3--3--3oC/W

DEFINITIONS

VF = Instantaneous forward voltage (pw = 300µs, D = 2%).

= Instantaneous reverse current.

I

R

t

= Reverse recovery time (See Figure 9), summation of ta + tb.

rr

= Time to reach peak reverse current (See Figure 9).

t

a

t

= Time from peak IRM to projected zero crossing of IRM based on a straight line from peak IRM through 25% of IRM (See Figure 9).

b

= Reverse recovery charge.

Q

RR

= Junction Capacitance.

C

J

R

= Thermal resistance junction to case.

θJC

pw = pulse width.

D = duty cycle.

o

C

o

C

o

C

2

Page 3

RHRP640CC, RHRP650CC, RHRP660CC

Typical Performance Curves

30

10

, FORWARD CURRENT (A)

F

I

1.0

0.5

0 0.5

175oC 25oC100oC

1.0 2.0

VF, FORWARD VOLTAGE (V)

1.5

2.5

3.0

1000

100

10

1

REVERSE CURRENT (µA)

0.1

R,

I

0.01

0 200 400 600300 500

100

VR, REVERSE VOLTAGE (V)

175oC

100oC

25oC

FIGURE 1. FORWARD CURRENT vs FORWARD VOLTAGE FIGURE 2. REVERSE CURRENT vs REVERSE VOLTAGE

30

25

20

15

10

t, RECOVERY TIMES (ns)

5

TC = 25oC, dIF/dt = 200A/µs

t

rr

t

a

t

b

50

40

30

20

t, RECOVERY TIMES (ns)

10

TC = 100oC, dIF/dt = 200A/µs

t

rr

t

a

t

b

0

0.5

IF, FORWARD CURRENT (A)

61

0

0.5

IF, FORWARD CURRENT (A)

FIGURE 3. trr,taAND tbCURVES vs FORWARD CURRENT FIGURE 4. trr,taAND tbCURVES vs FORWARD CURRENT

75

60

45

30

t, RECOVERY TIMES (ns)

15

0

0.5

TC = 175oC, dIF/dt = 200A/µs

t

rr

t

a

t

b

IF, FORWARD CURRENT (A)

61

6

5

4

3

2

1

0

(AV), AVERAGE FORWARD CURRENT (A)

F

I

145

140 150 160 170 175165

SQ. WAVE

155

TC, CASE TEMPERATURE (oC)

DC

FIGURE 5. trr,taAND tbCURVES vs FORWARD CURRENT FIGURE 6. CURRENT DERATING CURVE

61

3

Page 4

RHRP640CC, RHRP650CC, RHRP660CC

Typical Performance Curves (Continued)

50

40

30

20

10

, JUNCTION CAPACITANCE (pF)

J

C

0

0 50 100 150 200

FIGURE 7. JUNCTION CAPACITANCE vs REVERSE VOLTAGE

Test Circuits and Waveforms

VGE AMPLITUDE and

RG CONTROL dIF/dt

1 ANDt2

CONTROL I

F

L

t

V

, REVERSE VOLTAGE (V)

R

DUT

CURRENT

R

G

V

GE

t

1

t

2

IGBT

SENSE

+

V

DD

-

0

dI

F

I

F

dt

t

rr

t

a

t

b

0.25 I

RM

I

RM

FIGURE 8. trr TEST CIRCUIT FIGURE 9. trr WAVEFORMS AND DEFINITIONS

L = 20mH

R < 0.1Ω

= 1/2LI2 [V

E

AVL

Q

= IGBT (BV

1

Q

CES

1

R(AVL)

> DUT V

/(V

R(AVL)

R(AVL)

CURRENT

SENSE

DUT

- VDD)]

)

LR

V

I

AVL

L

+

V

DD

I

L

IV

V

DD

t

0

t

1

t

2

t

FIGURE 10. AVALANCHE ENERGY TEST CIRCUIT FIGURE 11. AVALANCHE CURRENT AND VOLTAGE

WAVEFORMS

4

Page 5

RHRP640CC, RHRP650CC, RHRP660CC

TO-220AB

3 LEAD JEDEC TO-220AB PLASTIC PACKAGE

ØP

Q

D

E

1

L

1

E

H

1

D

1

b

1

A

A

1

SYMBOL

A 0.170 0.180 4.32 4.57 -

A

1

TERM. 4

o

45

b 0.030 0.034 0.77 0.86 3, 4

b

1

c 0.014 0.019 0.36 0.48 2, 3 , 4

D 0.590 0.610 14.99 15.49 -

D

1

INCHES MILLIMETERS

NOTESMIN MAX MIN MAX

0.048 0.052 1.22 1.32 -

0.045 0.055 1.15 1.39 2, 3

- 0.160 - 4.06 -

E 0.395 0.410 10.04 10.41 -

L

o

60

1

2

e

e

1

b

c

E

1

- 0.030 - 0.76 -

e 0.100 TYP 2.54 TYP 5

3

J

1

e

1

H

1

J

1

0.200 BSC 5.08 BSC 5

0.235 0.255 5.97 6.47 -

0.100 0.110 2.54 2.79 6

L 0.530 0.550 13.47 13.97 -

L

1

0.130 0.150 3.31 3.81 2

ØP 0.149 0.153 3.79 3.88 -

Q 0.102 0.112 2.60 2.84 -

NOTES:

1. These dimensions are withinallowable dimensionsof Rev.J of

JEDEC TO-220AB outline dated 3-24-87.

2. Lead dimension and finish uncontrolled in L1.

3. Lead dimension (without solder).

4. Add typically 0.002 inches (0.05mm) for solder coating.

5. Position oflead to bemeasured 0.250inches (6.35mm) frombottom of dimension D.

6. Position oflead to bemeasured 0.100inches (2.54mm) frombottom of dimension D.

7. Controlling dimension: Inch.

8. Revision 2 dated 7-97.

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However ,no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com

Sales Office Headquarters

NORTH AMERICA

Intersil Corporation

P. O. Box 883, Mail Stop 53-204

Melbourne, FL 32902

TEL: (321) 724-7000

FAX: (321) 724-7240

5

EUROPE

Intersil SA

Mercure Center

100, Rue de la Fusee

1130 Brussels, Belgium

TEL: (32) 2.724.2111

FAX: (32) 2.724.22.05

ASIA

Intersil (Taiwan) Ltd.

7F-6, No. 101 Fu Hsing North Road

Taipei, Taiwan

Republic of China

TEL: (886) 2 2716 9310

FAX: (886) 2 2715 3029

Loading...

Loading...