Page 1

NTE8212

Integrated Circuit

Schottky, 8–Bit Input/Output Port

Description:

The NTE8212 input/output port is an integrated circuit in a 24–Lead DIP type package and consists

of an 8–bit latch with three–state output buffers along with control and device selection logic. Also

included is a service request f lip–fl op f or t he c ontrol a nd g eneration o f i nterrupts t o t he m icroprocessor.

Features:

D Fully Parallel 8–Bit Data Register and Buffer

D Service Request Flip–Flop for Interrupt Generation

D Low Input Load Current: 0.25mA Max

D Three State Outputs

D Outputs Sink 15mA

D 3.65V Output High Voltge for Direct Interface to 8080A Processor

D Asynchronous Register Clear

D Replaces Buffers, Latches and Multiplexers in Microcomputer Systems

D Reduces System Package Count

Absolute Maximum Ratings: (TA = +25°C, Note 1 unless otherwise specified)

All Output or Supply Voltages –0.5V to +7V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

All Input Voltages –1.0V to +5.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output Currents 125mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating Temperature Range 0° to +70°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage Temperature Range –65° to +150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Note 1. Stress above those listed under “Absolute Maximum Ratings” may cause permanent dam-

age to the device. This is a stress rating only and functional operation of the device at these

or any other conditions above those indicated in the operational sections of this specification

is not implied. Exposure to absolute maximum rating conditions for extended periods may

affect device reliability.

Page 2

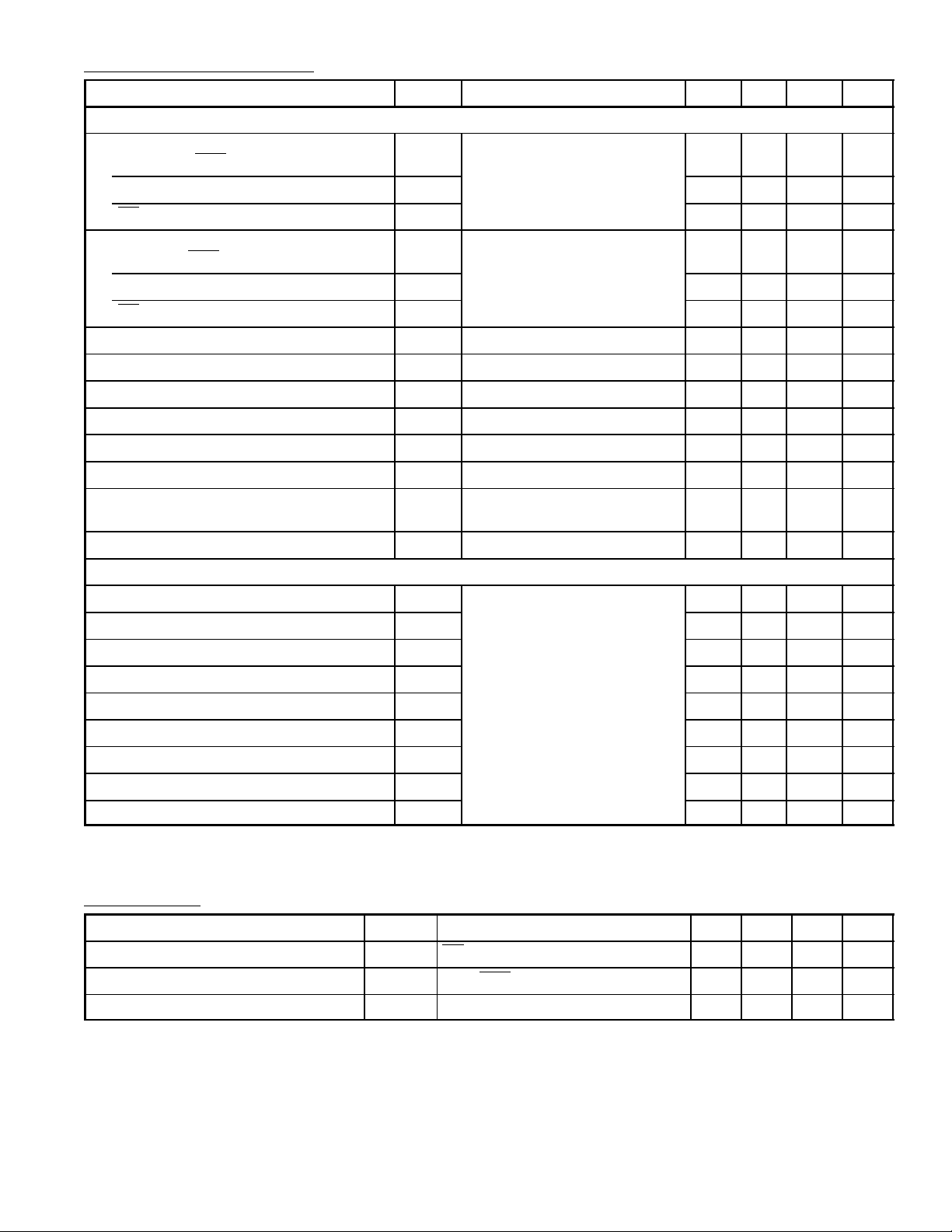

Electrical Characteristics: (TA = 0° to +70°C, VCC = 5V ±5% unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Unit

DC Characteristics

Input Load Current

STB, DS

MD Input |IL2| – – –0.75 mA

DS1 Input |IL3| – – –1.0 mA

Input Leakage Current

STB, DS, CLR, DI1 – DI8 Inputs |IH1| VR = 5.25V – – 10 µA

MD Input |IH2| – – 30 µA

DS1 Input |IH3| – – 40 µA

, CLR, DI1 – DI8 Inputs |IL1| VF = 0.45V – – –0.25 mA

2

Input Forward Voltge Clamp V

Input “Low” V oltage V

Input “High” V oltage V

Output “Low” Voltage V

Output “High” V oltage V

IC = –5mA – – –1.0 V

C

IL

IH

OLIOL

OHIOH

= 15mA – – 0.48 V

= –1mA 3.65 – – V

– – 0.85 V

2.0 – – V

Short Circuit Output Current IO5 VO = 0V, VCC = 5V –15 – –75 mA

Output Leakage Current, High Impedance

I

VO = 0.45V/5.25V – – 20 µA

O

State (DO0 – DO8)

Power Supply Current I

CC

– – 130 mA

AC Characteritics

Pulse Width t

pw

Data to Output Delay t

Write Enable to Output Delay t

data Setup Time t

we

set

Data Hold Time t

Reset to Output Delay t

Set to Output Delay t

Output Enable/Disable Time (Note 2) te/t

Clear to Output Delay t

Input Pulse Amplitude = 2.5V,

Input Rise & Fall Times = 5ns,

pd

Between 1V and 2V

Between 1V and 2V

Measurement made

at 1.5V with 15mA and 30pF

Test Load

h

r

s

d

c

30 – – ns

– – 30 ns

– – 40 ns

15 – – ns

20 – – ns

– – 40 ns

– – 30 ns

– – 45 ns

– – 55 ns

Note 2. R1 = 300Ω/10KΩ; R2 = 600Ω/1KΩ

Capacitance: (TA = +25°C, VCC = 5V, V

Parameter Symbol Test Conditions Min Typ Max Unit

Input Capacitance C

Input Capacitance C

Output Capacitance C

IN

IN

OUT

= 2.5V, f = 1MHz, Note 3 unless otherwise specified)

BIAS

DS1, MD – – 12 pF

DS2, CLR, STB, DI1 – DI

DO1 – DO

8

8

Note 3. This parameter is periodically sampled and not 100% tested.

– – 9 pF

– – 12 pF

Page 3

Functional Description:

Data Latch

The 8 flip–flops that compose the data latch are of a “D” type design. The output (Q) of the flip–flop

follows the data input (D) while the clock input (C) is high. Latching occurs when the clock (C) returns

low.

The data latch is cleared by an asynchronous reset input (CLR

(NOTE: Clock (C) overrides Reset (CLR

Output Buffer

The outputs of the data latch (Q) are connected to three–state, non–inverting output buffers. These

buffers have a common control line (EN); enabling the buffer to transmit the data from the outputs of

the data latch (Q) or disabling the buffer, forcing the output into a high impedance state (three–state).

This high–impedance state allows the designer to connect the NTE8212 directly to the microprocessor bi–directional data bus.

Control Logic

The NTE8212 has four control inputs: DS1, DS2, MD and STB. These inputs are employed to control

device selection, data latching, output buffer state and the service request flip–flop.

DS1, DS2 (Device Select)

These two inputs are employed for device selection. When DS1 is low and DS2 is high (DS1 • DS2)

the device is selected. In the selected state the output buffer is enabled and the service request flip–

flop (SR) is asynchronously set.

).)

).

Service Request Flip–Flop (SR)

The (SR) flip–flop is employed to generate and control interrupts in microcomputer systems. It is asynchronously set by the CLR input (active low). When the (SR) flip–flop is set it is in the non–interrupting

state.

The output (Q) of the (SR) flip–flop is connected to an inverting input of a “NOR” gate. The other input

of the “NOR” gate is non–inverting and is connected to the device selection logic (DS1 • DS2). The

output of the “NOR” gate (INT ) is active low (interrupting state) for connection to active low input priority generating circuits.

MD (Mode)

This input is employed to control the state of the output buffer and to determine the source of the clock

(C) to the data latch.

When MD is in the output mode (high) the output buffers are enabled and the source of clock (C) to

the data latch is from the device selection logic (DS1 • DS2).

When MD is i n the input mode (low) the output buf fer state is determined by the device selection logic

(DS1 • DS2) and the source of clock (C) to the data latch is the STB (Strobe) input.

STB (Strobe)

STB is employed as the clock (C) to the data latch for the input mode (MD = 0) and to synchronously

reset the service request (SR) flip–flop.

Note that the SR flip–flop triggers on the negative edge of STB which overrides CLR.

Page 4

Pin Connection Diagram

DS

MD

DI

DO

DI

DO

DI

DO

DI

DO

STB

GND

1

1

2

3

1

4

1

5

2

6

2

7

3

8

3

9 16

4

10

4

11

12 13

24

23

22

21

20

19

18

17

15

14

V

CC

INT

DI

8

DO

DI

7

DO

DI

6

DO

DI

5

DO

CLR

DS

8

7

6

5

2

24 13

112

1.300 (33.02) Max .520

(13.2)

.225

(5.73)

Max

.100 (2.54)

.126

(3.22)

Min

.600 (15.24)1.100 (27.94)

Loading...

Loading...