Page 1

HA13568AT

CD-ROM Combo Driver

ADE-207-261A (Z)

2nd Edition

December 1998

Description

The HA13568AT is combination of Spindle, Forcus, Tracking, Slide, Tray designed for CD-ROM and

have following functions and features.

Features

• 1.5 A sensorless spindle driver

• 0.5 A BTL focus driver

• 0.5 A BTL tracking driver

• 1.5 A H bridge slide motor driver

• 0.5 A H bridge tray motor driver

• Over temperature shut down (OTSD)

• Voltage regulator control circuit

Functions

• Sensorless driver with self start

• Soft switching drive

• Snubberless

• Low output saturation voltage

• Direct PWM slide driver

Page 2

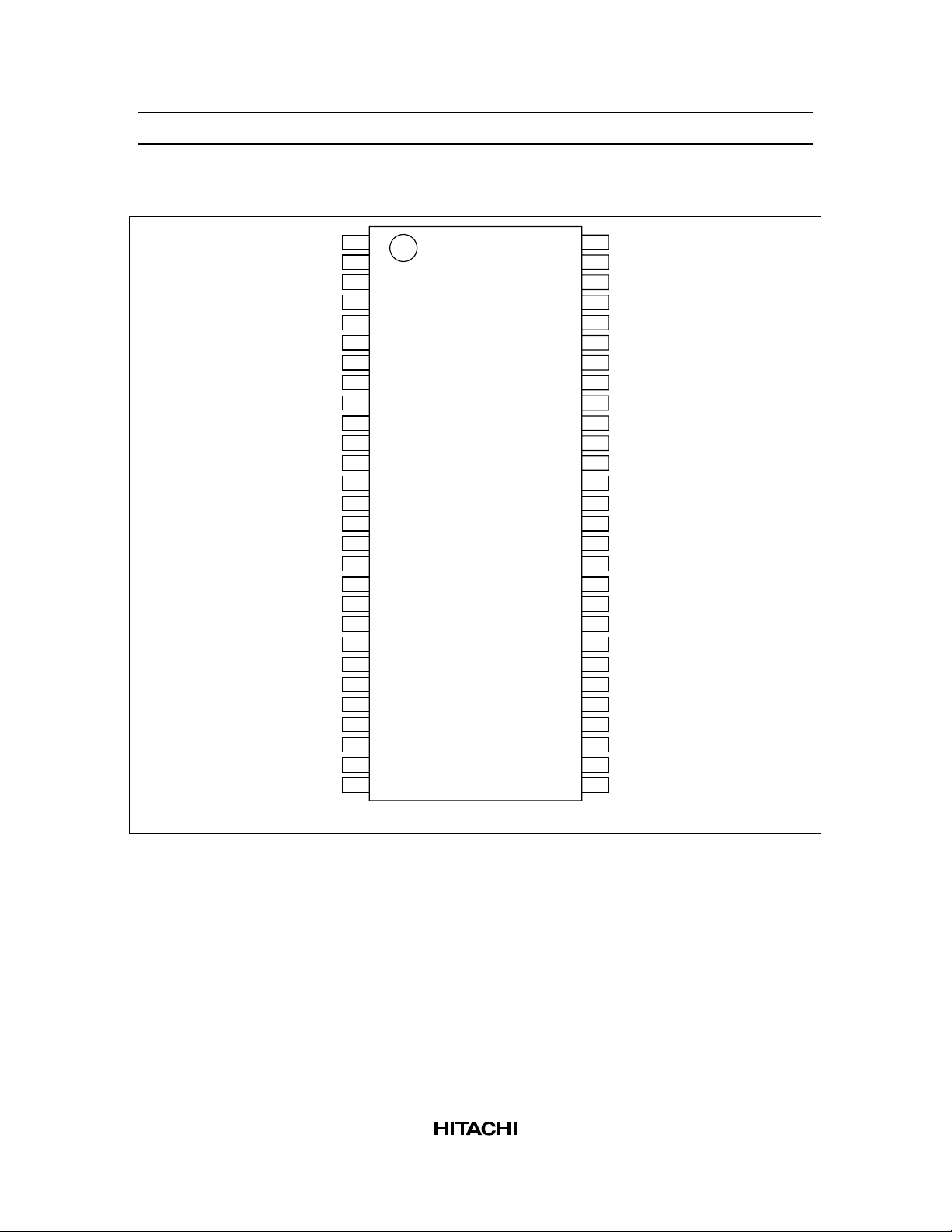

HA13568AT

Pin Arrangement

GND

FCSREF

FCSIN

FCSRS

TRRRS

VFCS

FCSP

FCGND

FCSN

TRRP

TRRN

TRYP

TRYN

VSLD

SLGND

SLDN

SLDP

VBST

B1

B2

RNF

W

VSPN

WFIL

VFIL

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

U

22

V

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

GND

TRRREF

TRRIN

NC

NC

NC

TRYLIM

TRYR

TRYF

SLDIN

SLDLIM

RT

CT2

VSS

CT3

CT1

CE

VREGF

VREGS

BRKSEL

PHASE

PC

CT

AGC

VCTL

REFIN

UFIL

GND

(Top view)

2

Page 3

HA13568AT

Pin Description

Pin No. Pin Name Function

2 FCSREF FCS driver block reference voltage

3 FCSIN FCS control input pin

4 FCSRS FCS sense pin

5 TRRRS TRR sense pin

6 VFCS FCS driver and TRR driver power supply

7 FCSP FCS driver P output

8 FCGND FCS driver and TRR driver GND

9 FCSN FCS driver N output

10 TRRP TRR driver P output

11 TRRN TRR driver N output

12 TRYP TRY driver P output

13 TRYN TRY driver N output

14 VSLD SLD driver and TRY driver power supply

15 SLGND SLD driver and TRY driver GND

16 SLDN SLD driver N output

17 SLDP SLD driver P output

18 VBST Booster output pin. This circuit generates a voltage about 1.5 V above that of the

VSPN pin.

19 B1 Booster pumping capacitor connection

20 B2

21 RNF Spindle driver current detection

22 U U phase output

23 V V phase output

24 W W phase output

25 VSPN Spindle and booster power supply

26 WFIL W phase low pass filter. Connect a filter C to this pin during GND.

27 VFIL V phase low pass filter. Connect a filter C to this pin during GND.

30 UFIL U phase low pass filter. Connect a filter C to this pin during GND.

31 REFIN Reference voltage of spindle and slide

32 VCTL Spindle control input. Generates forward torque when a DC voltage higher than

REFIN is applied, and brake when a DC voltage lower than REF is applied.

33 AGC For AGC. Holds the level used for IC internal processing fixed even if the B-EMF

level fluctuates due to the rotation speed.

34 CT Spindle center tap

35 PC Spindle driver phase compensation

3

Page 4

HA13568AT

Pin Description (cont)

Pin No. Pin Name Function

36 PHASE Outputs the B-EMF zero cross phase. Open corrector. (See the timing chart)

37 BRKSEL To select the brake mode. Lo: Short brake, Hi: Reverse full brake

(when forward torque input: BRKSEL = H)

38 VREGS Voltage regulator sense pin (VREGS ≈ 3.3 V output)

39 VREGF Voltage regulator force pin

40 CE Chip enable. Input Hi: active

41 CT1 Time constant for clock oscillator circuit. The clock oscillator frequency is

determined by the external capacitor and resistor Ct1 and Rt.

42 CT3 Time constant for PWM carrier oscillator. The carrier frequency is determined by

the external capacitor and resistor Ct3 and Rt.

43 VSS Control block power supply. 5 V

44 CT2 Time constant for start-up oscillator. The start-up oscillator frequency is

determined by the external capacitor and resistor Ct2 and Rt.

45 RT Reference voltage (3.3 V). The IC’s internal reference current is determined by

this voltage and the external resistor Rt.

46 SLDLIM SLD output maximum duty setting

47 SLDIN SLD control input pin

48 TRYF TRY driver forward input

49 TRYR TRY driver reverese input

50 TRYLIM TRY output voltage setting pin

51 NC No connection

52 NC

53 NC

54 TRRIN TRR control input pin

55 TRRREF TRR driver block reference voltage

1, 28, 29, 56, TAB GND

4

Page 5

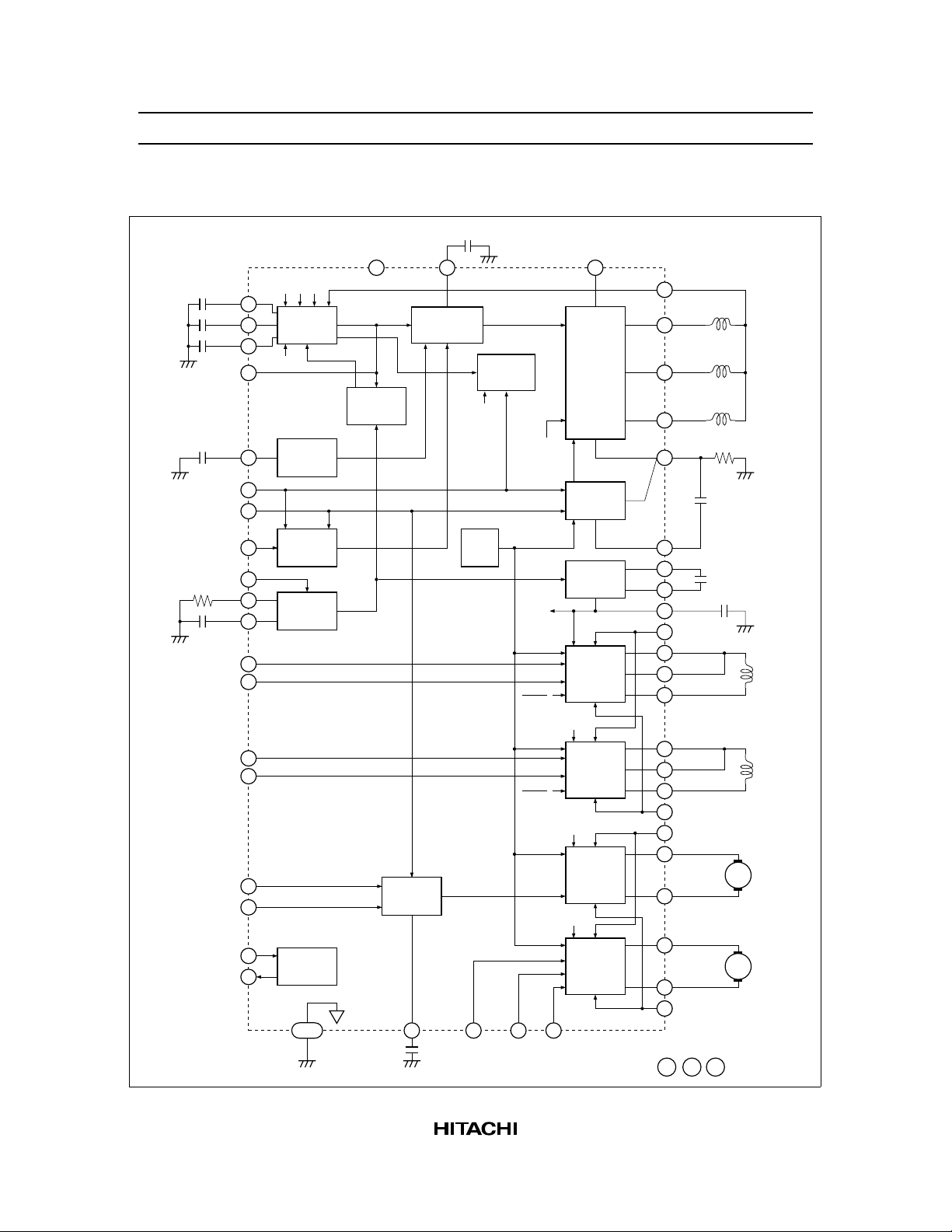

Block Diagram

UFIL

30

VFIL

27

WFIL

26

PHASE

36

CT2

VCTL

REFIN

CE

Rt

RT

CT1

FCSIN

TRRIN

SLDIN

VREGS

VREGF

44

32

31

37

40

45

41

3

2

54

55

47

46

38

39

Ct2

BRKSEL

Ct1

FCSREF

TRRREF

SLDLIM

C102

VSS VSPNAGC

WVU

B-EMF

detection

Vspn

Tmask

Mask

time

Start-up

circuit

Brake

CLK

CLK

OSC

Vreg

TAB 42 48

SLD

control

CT3

Commutation

OTSD

TRYLIM

Ct3

50

Vref

Drive

mode

TRYF

Vbst

Vfcs

2

Vfcs

2

Vbst

49

TRYR

1.5A

SPN

output

Vbst

Vbst

1.5AH

bridge

Vbst

0.5AH

bridge

253343

U

V SPN

W

Current

control

Bias

P

0.5A

BTL

N

P

0.5A

BTL

N

P

N

P

N

CT

34

U

22

V

23

W

24

RNF

21

PC

35

B1

19

B2

20

VBST

18

6

VFCS

FCSP

7

FCSRS

4

FCSN

9

TRRP

10

TRRRS

5

TRRN

11

8

FCGND

14

VSLD

SLDP

17

SLDN

16

TRYP

12

TRYN

13

15

SLGND

51 , ,52 53 : NC pin

HA13568AT

Rnf

FCS

TRR

SLD

M

TRY

M

5

Page 6

HA13568AT

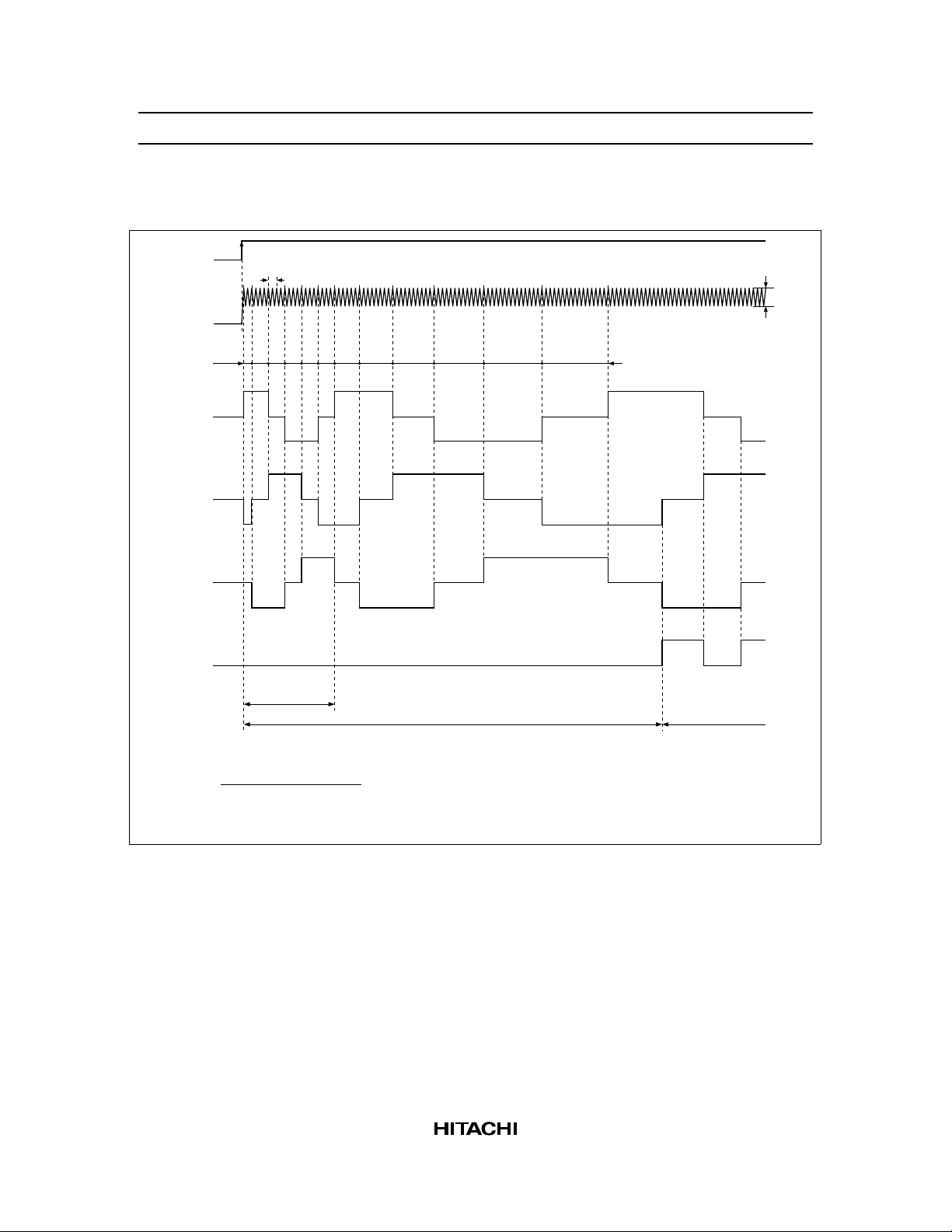

Timing Chart

1. Start-up

CE

CT2

Output

current

(U phase)

Output

current

(V phase)

Output

current

(W phase)

PHASE 0

0

0

+

0

−

+

0

−

+

0

−

Tc2

4Tc2

2Tc2

4Tc2

4Tc2

B-EMF

Mask period

4Tc2

4Tc2

6Tc2

8Tc2

10Tc2

12Tc2

Synchronous mode B-EMF mode

14Tc2

16Tc2

Vhct2

Vlct2

Note: Tc2 is as follows.

8 (Vhct2 − Vlct2) Rt Ct2

Tc2 =

Where, Vhct2

Vlct2

6

Vrt

: CT2 pin high voltage (See electrical characteristics)

: CT2 pin low voltage (See electrical characteristics)

Page 7

2. Acceleration (switching mode)

UVW

HA13568AT

Reverse

start-up

voltage

B-EMF

PHASE

Output

current

(U phase)

Output

current

(V phase)

Output

current

(W phase)

+

0

−

0

+

0

−

+

0

−

+

0

−

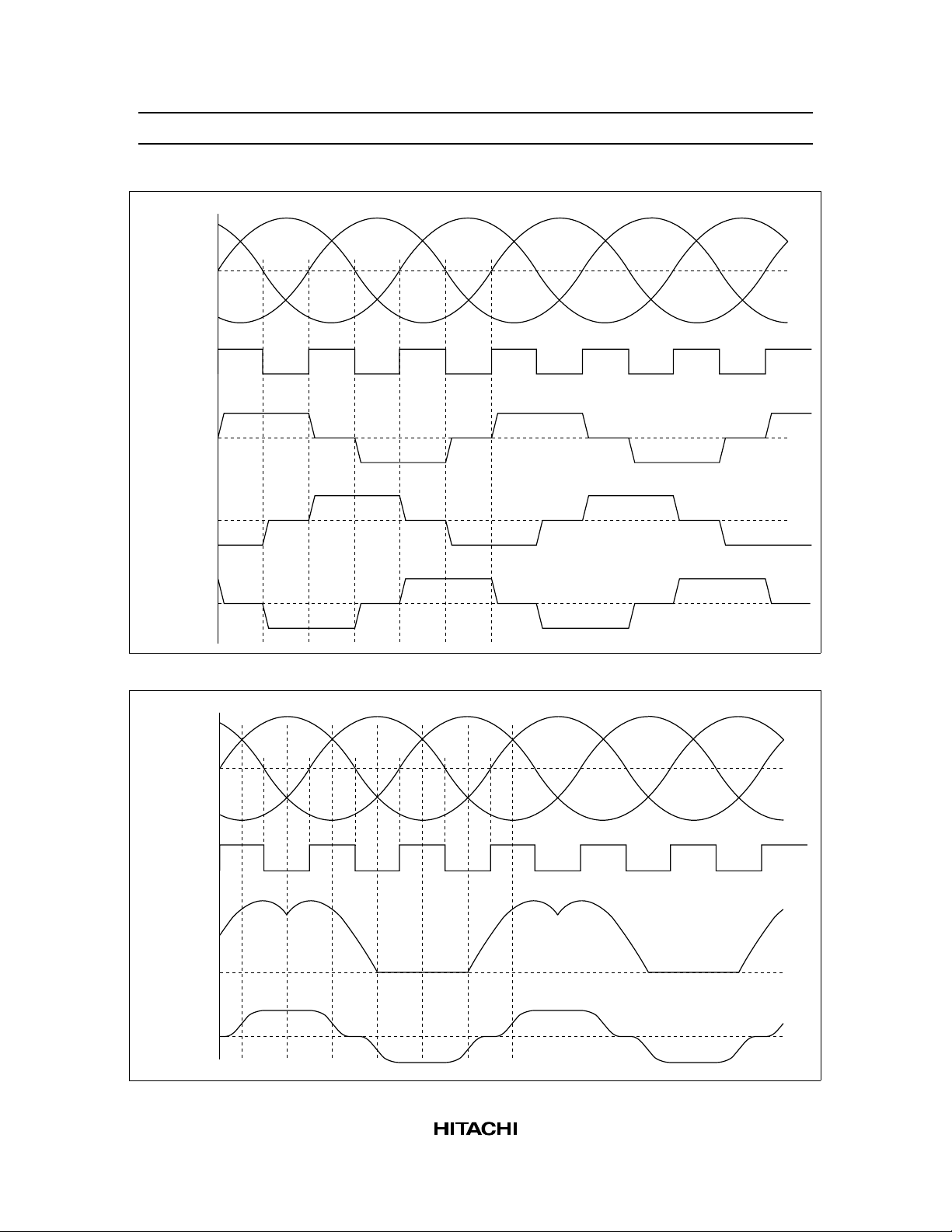

3. Running (soft switching mode)

Reverse

start-up

voltage

B-EMF

PHASE

Output

voltage

(U phase)

Output

current

(U phase)

UVW

+

0

−

0

0

+

0

−

7

Page 8

HA13568AT

Truth Table

Table 1 Overall

CE OTSD SPN Driver FCS Driver TRR Driver SLD Driver TRY Driver

LXZZZZZ

HONZZZZZ

OFF ON ON ON ON ON

Note: X: Option, Z: Hi impedance

Table 2 SPN Driver

BRKSEL VCTL SPN Driver

X > REFIN Forward torque

REFIN Z

L < REFIN Short brake

H REFIN – 0.6 V Reverse brake

Note: X: Option, Z: Hi impedance

Table 3 TRY Driver

TRYF TRYR P Output N Output

LLZZ

LHLH

HLHL

HHHH

Note: Z: Hi impedance

8

Page 9

Application

1. FCS, TRR voltage drive

HA13568AT

Cpc

Vcc

MPU

VREF

DMO

FOO

TRO

FMO

3.3V

+5V

5V

Q1

R105

R101

R102

Rt2

C109

R110

R111

R112

R113

C110

C102

C103

C104

C105

Ct2

Ct1

Ct3

AGC

UFIL

VFIL

WFIL

CT2

VREGF

VREGS

PHASE

BRKSEL

CE

VCTL

RT

CT1

REFIN

FCSIN

FCSREF

TRRIN

TRRREF

SLDIN

SLDLIM

CT3

TRYF

TRYR

TRYLIM

TAB

VSPNVSS

FCSRS

TRRRS

FCGND

SLGND

CT

RNF

PC

B1

B2

VBST

VFCS

FCSP

FCSN

TRRP

TRRN

VSLD

SLDP

SLDN

TRYP

TRYN

C101

U

V

W

C108

C106

C107Rt1

Rnf

R103

C111

R104

C112

M

SPN

FCS

TRR

SLD

TRYM

+12V

+5V

R106

R107

9

Page 10

HA13568AT

2. FCS, TRR voltage drive

FCSP

FCSRS

FCSN

TRRP

TRRRS

TRRN

FCS

RSFCS

TRR

RSTRR

R103

C111

R108

C113

R104

C112

R109

C114

DSP

FO

TO

REF

R110

R111

R112

R113

FCSIN

(Zin ≈ 12kΩ)

FCSREF

(Zin ≈ 12kΩ)

TRRIN

(Zin ≈ 12kΩ)

TRREF

(Zin ≈ 12kΩ)

Note: Other pins have the same connections as those used in application 1.

3. When used at a voltage other than 3.3 V with a voltage regulator (Vout = 3.3 to Vcc – 1 V)

Vcc (5V or 12V)

Q1

Vout

C115

Rr1

Rr2

R105

3.3V

VREGF

VREGS

+

−

3.3V

10

Note: Other pins have the same connections as those used in application 1.

Page 11

External Components

HA13568AT

Reccomended

Parts No.

R101 47 kΩ≤ 47 kΩ Filter for SPN driver control input

R102 47 kΩ≤ 47 kΩ Filter for SLD driver control input

R103 6.8 Ω — To stop FCS block oscillation

R104 6.8 Ω — To stop TRR block oscillation

R105 500 Ω≥ 100 Ω for Q1 bias

R106 20 kΩ — for TRY driver output voltage setting

R107 27 kΩ —

R108 6.8 Ω — To stop FCS block oscillation

R109 6.8 Ω — To stop TRR block oscillation

R110 to

R113

Rnf 0.25 Ω≥ 0.25 Ω SPN driver current detection resistor 1

Rt1 1.8 kΩ Rt1 + Rt2 =

Rt2 8.2 kΩ

RSFCS 1 Ω≥ 0.33 Ω for FCS driver current sense 7

RSTRR 1 Ω≥ 0.33 Ω for TRR driver current sense

Rr1 — — Voltage regulator division resistor 8

Rr2 — —

C101 0.1 µF ≥ 0.1 µF for Power supply by passing

C102 0.047 µF for B-EMF Amplitude AGC

C103 0.01 µF for B-EMF filter 6

C104

C105

C106 0.22 µF ≥ 0.22 µF for Booster pumping

C107 0.47 µF ≥ 0.47 µF for Booster output smoothing

C108 0.1 µF for SPN driver phase compensation

C109 0.01 µF Filter for SPN control input

C110 3300 pF Filter for SLD control input

C111 0.01 µF — To stop FCS block oscillation

C112 0.01 µF — To stop TRR block oscillation

C113 0.01 µF — To stop FCS block oscillation

C114 0.01 µF — To stop TRR block oscillation

C115 2.2 µF for Voltage regulator smoothing

Value

20 kΩ — for BTL gain setting 7

Reccomended

Range Purpose Note

Reference current setting and SLD driver

10 kΩ

maximum duty setting

2, 5

11

Page 12

HA13568AT

External Components (cont)

Reccomended

Parts No.

Ct1 150 pF ≥ 120 pF Time constant for CLK oscillation. Use a

Ct2 0.033 µF Time constant for start-up oscillation. Use a

Ct3 470 pF ≥ 390 pF PWM carrier oscillation time constant 5

Q1 Transistor for voltage regulator

Note: 1. The output current maximum value Iospnmax of SPN driver is controlled according to the

Value

following equation. However, Vspncl is the current limiter reference voltage. (See the electrical

characteristics)

Iospnmax =

2. The maximum duty Dmax of SLD driver output is controlled according to the following equation.

Dmax = −× 100 (%)

However,

Rt = Rt1 + Rt2, ≥

Where, Vrt : RT pin voltage (See the electrical characteristics)

Since Vrt ≈ Vhct3, Dmax is not limited at 100% when Rt1 = 0 Ω.

3. The CLK oscillation frequency is determined by the following equation.

fclk =

fclk =

Vhct3 − Vlct3

Vlct3 : CT3 pin low voltage (≈ 1.3 V)

Vhct3 : CT3 pin high voltage (≈ 3.3 V)

Vrt

Vrt

8 Ct1 Rt ∆Vct1

8 Ct1 Rt ∆Vct1

Reccomended

Range Purpose Note

capacitor with good temperature characteristics.

capacitor with good temperature characteristics.

Vspncl

Rnf

Rt2

Rt

Rt2RtVlct3

Vrt

Vlct3

Vrt

Vrt

3

4

12

Where, Vrt : RT pin voltage (See the electrical characteristics)

∆Vct1 : CT1 pin voltage amplitude (≈ 1 V)

4. The Ct2 for start-up oscillation is determined by the following equation.

1

Tc2 =

6

Ct2 =

8 Rt (Vhct2 − Vlct2)

Where, J : Spindle motor inertia (kg · cm · S2)

P : Number of spindle motor poles (Total number of S poles and N poles)

Kt : Spindle motor torque constant (kg · cm / A)

Vhct2 : CT2 pin high voltage (≈ 3.3 V)

Vlct2 : CT2 pin low voltage (≈ 1.3 V)

J

P Kt Ispnmax

Tc2 Vrt

Page 13

HA13568AT

5. The PWM oscillation frequency fpwm is determined by the following equation.

fpwm =

Where, Vhct3 : CT3 pin high voltage (≈ 3.3 V)

6. The C103 to C105 for B-EMF filter are determined by the following equation.

π ⋅ Rflt ⋅ No ⋅ P

Where, Rfill : B-EMF detection output resistor (See the electrical characteristics)

7. The FCS and TRR is determined by the following equation.

Voltage drive:

Gv =

Current drive:

Gm =

Where, R1 : Resistor of IC inside (≈30kΩ)

8. The output voltage Vout of voltage regulator is determined by the following equation.

Vout = 3.3 1 +

8 Ct3 Rt (Vhct3 − Vlct3)

Vlct3 : CT3 pin low voltage (≈ 1.3 V)

21

No : Maximum rotation speed (rpm)

R1

Rin + R2

((Rin + R2) ⋅ Rs)

R2 : Resistor of IC inside (≈7kΩ)

Rin : Resistor value inserted in the input (Ω)

Rs : Current sense resistor (Ω)

Vrt

≤ C103 ≤

R1

(R110 to R113)

Rr1

Rr2

π ⋅ Rflt ⋅ No ⋅ P

35

13

Page 14

HA13568AT

Absolute Maximum Ratings (Ta = 25°C)

Item Symbol Rating Unit Note

Supplu voltage Vss 7 V 1

SPN supply voltage Vspn 15 V 1

FCS & TRR supply voltage Vfcs 15 V 1

SLD & TRY supply voltage Vsld 15 V 1

Input voltage Vin 0 to Vss V 2

Vintrylim Vss to Vsld V

SPN output current Iospn 1.5 A 3

FCS & TRR & TRY output current Iofcs 0.5 A 3

SLD output current Iosld 1.5 A 3

Power dissipation P

T

Junction temperature Tj 160 °C1

Storage temperature range Tstg –55 to +125 °C

Note: 1. Operating voltage range is shown below.

Vss = 4.25 to 5.75 V

Vspn = 4.25 to 13.8 V

Vfcs = 4.25 to 13.8 V (However, the output high voltage is clamped at 7 V.)

Vsld = 4.25 to 13.8 V

Tjopr = 0 to +135°C

2. Applied to BRKSEL, VCTL, REFIN, CE, FCSIN, FCSREF, TRRIN, TRRREF, SLDIN, SLDLIM,

TRYF and TRYR.

3. ASO (Area of Safety Operation) of each output transistor is shown below (TBD).

5W4

14

2.0

1.5

1.0

0.5

0.2

Corrector Current Ic (A)

0.1

The voltage between Corrector and Emitter Vce (V) The voltage between Corrector and Emitter Vce (V)

ASO of SPN driver ASO of SLD driver

t = 0.1ms

t = 1ms

t = 10ms

210152015

2.0

1.5

1.0

t = 0.1ms

0.5

t = 1ms

t = 10ms

0.2

Corrector Current Ic (A)

0.1

210152015

4. Thermal resistance is shown below.

θj-tab ≤ 12°C / W (back side tab soldering area is 70% or more)

θj-a ≤ 25°C / W (mounted on 4 layer multi glass-epoxy board, back side tab soldering area is

70% or more)

Page 15

HA13568AT

Electrical Characteristics

(Ta = 25°C, Vss = 5 V, Vspn = 12 V, Vfcs = 5 V, Vsld = 12 V)

Applicable

Item Symbol Min Typ Max Unit Test Conditions

Quiescent current Iss0 — 0.7 0.9 mA CE = L VSS

Ispn0 — — 0.2 mA VSPN

Ifcs0 — — 0.01 mA VFCS

Isld0 — — 0.01 mA VSLD

Iss1 14 20 25 mA CE = H, VCTL = VSS

Ispn1 11 15 20 mA FCSIN = TRRIN = VSPN

Ifcs1 6 10 15 mA SLDIN = REFIN, VFCS

Isld1 — — 1.0 mA TRYF = TRYR = L

All load open

Iss2 20 33 60 mA CE = H, VCTL = VSS

Ispn2 11 30 50 mA FCSIN = TRRIN = VSPN

Ifcs2 7 10 15 mA SLDIN = 5 V, VFCS

Isld2 –15 –1.0 1.0 mA TRYF, TRYR = H,

L, All load open

Logic Input current Iince 0 70 100 µA Vin = 0 to 5 V BRKSEL,

input Iin — — ±10 µA CE, TRYF,

Low level voltage Vil — — 0.8 V TRYR

High level voltage Vih 2.0 — — V

Logic Low level voltage Vol — — 0.4 V Io = 1 mA PHASE

output Leak current Icer1 — — ±10 µA Vce = 15 V

SPN

driver

FCS Input resistance Rinfcs 9.6 12 14.4 kΩ FCSIN

driver Rinfcsref 9.6 12 14.4 kΩ

Output saturation

voltage

Leak current Icer2 1.3 2.2 3 mA Vce = 15 V

Current limiter

voltage

Input voltage range Vinfcs 0 — 5 V

Vsatspn — 1.25 1.75 V Iospn = 1.0 A U, V, W 1

Vspncl 238 265 292 mV Rnf = 0.25 Ω RNF 2

Pins Note

VSLD

VSLD

15

Page 16

HA13568AT

Electrical Characteristics

(Ta = 25°C, Vss = 5 V, Vspn = 12 V, Vfcs = 5 V, Vsld = 12 V) (cont)

Applicable

Item Symbol Min Typ Max Unit Test Conditions

FCS

driver

TRR Input resistance Rintrr 9.6 12 14.4 kΩ TRRIN

driver Rintrrref 9.6 12 14.4 kΩ

SLD

driver

TRY

driver

Output quiescent

voltage

Output offset

voltage

Output saturation

voltage

Voltage gain Gvfcs 11.6 12.6 13.6 dB 4

Gain band width Bfcs 100 — — kHz ∆Gv = –3 dB

Input voltage range Vintrr 0 — 5 V

Output quiescent

voltage

Output offset

voltage

Output saturation

voltage

Voltage gain Gvtrr 11.6 12.6 13.6 dB 4

Gain band width Btrr 100 — — kHz ∆Gv = –3 dB

Output saturation

voltage

Leak current Icer3 — — ±100 µA Vce = 15 V

Penetration current Iovlap — — 100 mA VSLD 8

Transient response tplh1 — — 5 µs SLDP,

time tphl1 — — 5 µs SLDN

Output saturation

voltage

Leak current Icer3 — — ±100 µA Vce = 15 V

Penetration current Iovlap — — 100 mA VSLD 8

Transient response tplh1 — — 5 µs TRYP,

time tphl1 — — 5 µs TRYN

Input current Iintrylim — — ±5 µA Vtrylim=7 to VSLD

Output voltage Vlimtry 0.1 0.7 1.0 V RL = 16Ω,

Vqfcs 2.375 2.5 2.625 V FCSIN=FCSREF=

2.5 V, VFCS=5 V

Vosfcs — — ±20 mV

Vsatfcs — 1.0 1.4 V Io = 0.33 A 1

Vqtrr 2.375 2.5 2.625 V FCSIN=TRRREF=

2.5 V, VFCS=5 V

Vostrr — — ±20 mV FCSIN = REF

Vsattrr — 1.0 1.4 V Io = 0.33 A 1

Vsatsld — 1.5 2.0 V Iosld = 0.75 A SLDP,

Vsattry — 1.0 1.4 V Iotry = 0.33 A TRYP,

Vtrylim = 7 V

Pins Note

FCSP,

FCSN

TRRP,

TRRN

SLDN

TRYN

3

3

1

1

9

16

Page 17

HA13568AT

Electrical Characteristics

(Ta = 25°C, Vss = 5 V, Vspn = 12 V, Vfcs = 5 V, Vsld = 12 V) (cont)

Applicable

Item Symbol Min Typ Max Unit Test Conditions

SPN Input current Iinspn — — ±5.0 µA Vctl = 0 to Vss–1V VCTL, 2

current REF voltage range Vref 1.6 — 3.0 V REFIN

control Dead zone voltage Vdzspn ±50 — ±120 mV Vref reference

Current control

gain

Drive Change threshold Vctl — 0.5 ±0.1 V Vref reference VCTL 5

mode voltage f

SW ↔ SOFT SW — <f

B-EMF

detection

CLK RT voltage Vrt 3.135 3.30 3.465 V RT

OSC CLK oscillation

Start-up

circuit

SLD Input current Iinsld — — ±5.0 µA Vsld = 0 to Vss–1V SLDIN

control Input voltage range Vinsld 0 — 4.0 V

Voltage

regulator

OTSD Operating

Output resistance Rflt — 10 ±20% kΩ UFIL, VFIL,

Threshold voltage

of PHASE

occurrence

frequency

Start-up oscillation

frequency

Limiter input

current

PWM oscillation

frequency

Control gain D/V 80 90 100 %/V 7

Offset voltage Vossld — — 20 mV SLDIN = REFIN

Output sink current Isinkreg 8.5 12.2 — mA VREGS = 4 V,

Output voltage Voutreg 3.135 3.30 3.465 V

temperature

Hysteresis Thys — 50 — °C

Gctl — –12 ±1.5 dB RNF

PHASE

Viemf — 40 ±50% mVpp VSPN ≥ Vss + 3VFU, V, W 6

fclk 210 240 270 kHz Rt = 10 kΩ,

fct2 437 485 534 Hz Rt = 10 kΩ,

Isldlim — — ±5.0 µA SLDLIM

fpwm 33 38 42.35 kHz Rt = 10 kΩ,

Tsd 135 160 — °C8

— ≥f

—28±50% mVpp VSPN ≤ Vss + 3V

±50% Hz SOFT SW mode U, V, W 5

CT2

–20% Hz SW mode

CT2

Ct1 = 82 pF

Ct2 = 0.033 µF

Ct3 = 470 pF

VREGF = 4 V

Pins Note

WFIL

F

CT1

CT2

17

Page 18

HA13568AT

Note: 1. The output saturation voltage is the sum of the upper and lower saturation voltages.

2. See figure 1. Where,

Gctl = 20 log

∆Vrnf

∆Vctl

Vspncl

Vrnf (V)

Reverse

torque

Forward

torque

Vdzspn

∆Vrnf

∆Vctl

Figure 1

Vref

0 Vctl (V)

Reverse brake Short brake

3. Where,

Vqfcs =

Vqtrr =

Vfcsp + Vfcsn

2

Vtrrp + Vtrrn

2

4. See figure 2. Where,

Vfcsn (Vtrrn)

∆Vfcsin

Vfcsp (Vtrrp)

(∆Vtrrin)

∆Vfcsp

(∆Vtrrp)

Gvfcs = 20 log

Gvtrr = 20 log

∆Vfcsp

∆Vfcsin

∆Vtrrp

∆Vtrrin

∆Vfcsn

∆Vfcsin

∆Vtrrn

∆Vtrrin

Vfcsp (Vtrrp) &

Vfcsn (Vtrrn)

Vref0 Vfcsin (Vtrrin)

Figure 2

5. The circuit operates in soft switching drive mode only when the control input (Vctl) is lower than

f

CT2

and f

is higher than the threshold voltage. See figure 3.

PHASE

(Hz)

SOFT SW mode

Figure 3

PHASE

f

f

CT2

SW mode

0V

SW mode

0.5V

CTL

− REFIN

6. PHASE is output only when B-EMF exceeds the threshold voltage.

18

Page 19

7. See figure 4. Where,

D/V =

∆D

∆Vin

Duty

100

(%)

SLDP = PWM

SLDN = H

HA13568AT

SLDP = H

SLDN = PWM

Vref

∆Vin

∆D

Figure 4

8. Design guide only.

9. Vlimtry = VTRYP – VTRYLIM, or VTRYN – VTRYLIM

0 Vinsld (V)

19

Page 20

HA13568AT

Reference Data

SPN Driver Output Saturation Voltage vs.

3

2

1

0

Output Saturation Voltage Vsatspn (V)

SLD Driver Output Saturation Voltage vs.

4

3

2

1

0

Output Saturation Voltage Vsatsld (V)

TRY Driver Output Saturation Voltage vs.

3

Output Current

Upper arm + Lower arm

Upper arm, Lower arm

1.00.50 1.5

Output Current Iospn (A)

Output Current

Upper arm + Lower arm

Upper arm, Lower arm

1.00.50 1.5

Output Current Iosld (A)

Output Current

FCS Driver Output Saturation Voltage vs.

3

2

1

0

Output Saturation Voltage Vsatfcs (V)

TRR Driver Output Saturation Voltage vs.

3

2

1

0

Output Saturation Voltage Vsattrr (V)

RT Voltage vs. Junction Temperature

3.6

Output Current

Upper arm + Lower arm

Upper arm, Lower arm

0.40.20 0.6

Output Current Iofcs (A)

Output Current

Upper arm + Lower arm

Upper arm, Lower arm

0.40.20 0.6

Output Current Iotrr (A)

20

2

1

Upper arm + Lower arm

0

Output Saturation Voltage Vsattry (V)

Upper arm, Lower arm

0.40.20 0.6

Output Current Iotry (A)

3.4

3.2

RT Voltage Vrt (V)

3.0

Junction Temperature Tj (°C)

75500 25 100 135

Page 21

Package Dimensions

HA13568AT

Preliminary

Top view

0.21

0.19

14.0

14.2 Max

2956

6.10

128

+0.04

−0.05

+0.03

−0.05

0.50

0.08

M

0.65 Max

0.08

1.20 Max

(7.5)

1

28

0.17 ± 0.05

0.15 ± 0.04

Unit: mm

1.0

8.10 ± 0.15

0° − 8°

0.50 ± 0.1

0.05 ± 0.05

Under view

56 29

(2.8)

Hitachi Code

JEDEC

EIAJ

(reference value)

Weight

TTP-56DT

0.32 g

21

Page 22

HA13568AT

Cautions

1. Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,

copyright, trademark, or other intellectual property rights for information contained in this document.

Hitachi bears no responsibility for problems that may arise with third party’s rights, including

intellectual property rights, in connection with use of the information contained in this document.

2. Products and product specifications may be subject to change without notice. Confirm that you have

received the latest product standards or specifications before final design, purchase or use.

3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,

contact Hitachi’s sales office before using the product in an application that demands especially high

quality and reliability or where its failure or malfunction may directly threaten human life or cause risk

of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,

traffic, safety equipment or medical equipment for life support.

4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly

for maximum rating, operating supply voltage range, heat radiation characteristics, installation

conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used

beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable

failure rates or failure modes in semiconductor devices and employ systemic measures such as failsafes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other

consequential damage due to operation of the Hitachi product.

5. This product is not designed to be radiation resistant.

6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without

written approval from Hitachi.

7. Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor

products.

Hitachi, Ltd.

Semiconductor & IC Div.

Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109

URL NorthAmerica : http:semiconductor.hitachi.com/

For further information write to:

Hitachi Semiconductor

(America) Inc.

2000 Sierra Point Parkway

Brisbane, CA 94005-1897

Tel: <1> (800) 285-1601

Fax: <1> (303) 297-0447

Europe : http://www.hitachi-eu.com/hel/ecg

Asia (Singapore) : http://www.has.hitachi.com.sg/grp3/sicd/index.htm

Asia (Taiwan) : http://www.hitachi.com.tw/E/Product/SICD_Frame.htm

Asia (HongKong) : http://www.hitachi.com.hk/eng/bo/grp3/index.htm

Japan : http://www.hitachi.co.jp/Sicd/indx.htm

Hitachi Europe GmbH

Electronic components Group

Dornacher Straße 3

D-85622 Feldkirchen, Munich

Germany

Tel: <49> (89) 9 9180-0

Fax: <49> (89) 9 29 30 00

Hitachi Europe Ltd.

Electronic Components Group.

Whitebrook Park

Lower Cookham Road

Maidenhead

Berkshire SL6 8YA, United Kingdom

Tel: <44> (1628) 585000

Fax: <44> (1628) 778322

Hitachi Asia Pte. Ltd.

16 Collyer Quay #20-00

Hitachi Tower

Singapore 049318

Tel: 535-2100

Fax: 535-1533

Hitachi Asia Ltd.

Taipei Branch Office

3F, Hung Kuo Building. No.167,

Tun-Hwa North Road, Taipei (105)

Tel: <886> (2) 2718-3666

Fax: <886> (2) 2718-8180

Copyright © Hitachi, Ltd., 1998. All rights reserved. Printed in Japan.

22

Hitachi Asia (Hong Kong) Ltd.

Group III (Electronic Components)

7/F., North Tower, World Finance Centre,

Harbour City, Canton Road, Tsim Sha Tsui,

Kowloon, Hong Kong

Tel: <852> (2) 735 9218

Fax: <852> (2) 730 0281

Telex: 40815 HITEC HX

Loading...

Loading...