Page 1

EMC2103

RPM-Based Fan

Controller with HW

Thermal Shutdown

PRODUCT FEATURES

The EMC2103 is an SMBus compliant fan controller with

up to up to 3 external and 1 internal temperature

channels. The fan driver can be operated using two

methods each with two modes. The methods include an

RPM based Fan Speed Control Algorithm and a direct

PWM drive setting. The modes include manually

programming the desired settings or using the internal

programmable temperature look-up table to select the

desired setting based on measured temperature.

The temperature monitors offer 1°C accuracy (for

external diodes) with sophisticated features to reduce

errors introduced by series resistance and beta variation

of substrate thermal diode transistors commonly found

in processors.

The EMC2103 also includes a hardware programmable

temperature limit and dedicated system shutdown

output for thermal protection of critical circuitry.

Applications

No tebook Computers

Projectors

Graphics Cards

Indu strial and Networking Equipment

Datasheet

Features

Programmable Fan Control circuit

— 4-wire fan compatible

— High and low frequency PWM

R PM based fan control algorithm

— 2.5% accuracy from 500RPM to 16k RPM

— Detects fan aging and variation

Temperature Look-Up Table

— Allows programmed fan response to temperature

— Controls fan speed or PWM drive setting

— Allows externally set temperature data to drive fan

— Supports DTS data from CPU

Up to Three External Temperature Channels

(EMC2103-2 only)

— Supports 45nm, 60nm, and 90nm CPU diodes

— Automatically detects and supports CPUs requiring BJT

or Transistor models

— Resistance error correction

— Supports discrete transistors (i.e. 2N3904)

— 1°C accurate (60°C to 125°C)

— 0.125°C resolution

H ardware Programmable Thermal Shutdown

Temperature

— Cannot be altered by software

— 65°C to 127°C Range

Prog rammable High and Low Limits for all channels

Interna l Temperature Monitor

— 2°C accuracy

— 0.125°C resolution

3 .3V Supply Voltage

SMBus 2.0 Compliant

— SMBus Alert compatible

Two dedicated GPIOs (EMC2103-2 and EMC2103-4

only)

Available in 12-pin, QFN Lead-Free RoHS Complia nt

Package (EMC2103-1 and EMC2103-3) or 16-pin,

QFN Lead-Free RoHS Compliant Package

(EMC2103-2 and EMC2103-4)

SMSC EMC2103 DATASHEET Revision 0.85 (01-29-08)

Page 2

RPM-Based Fan Controller with HW Thermal Shutdown

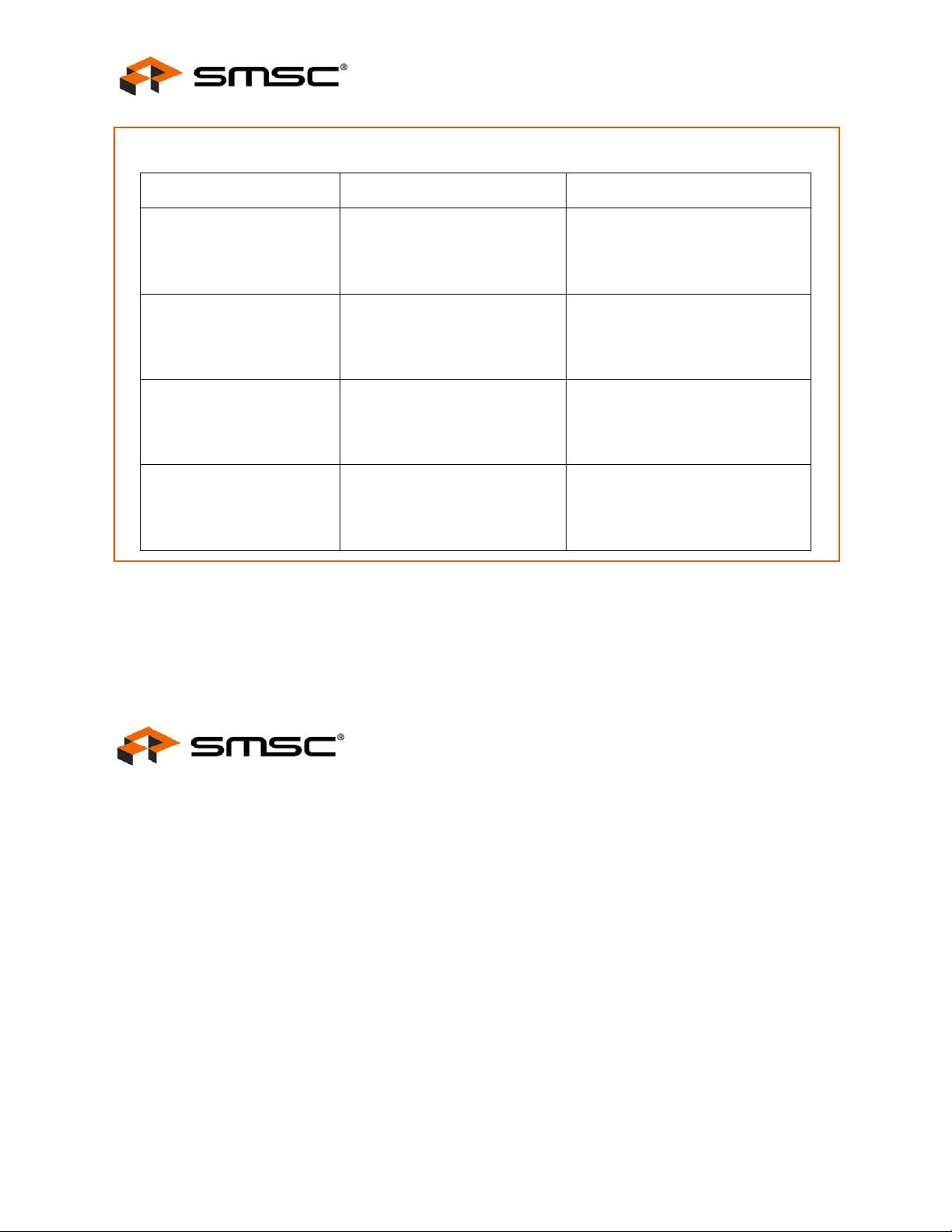

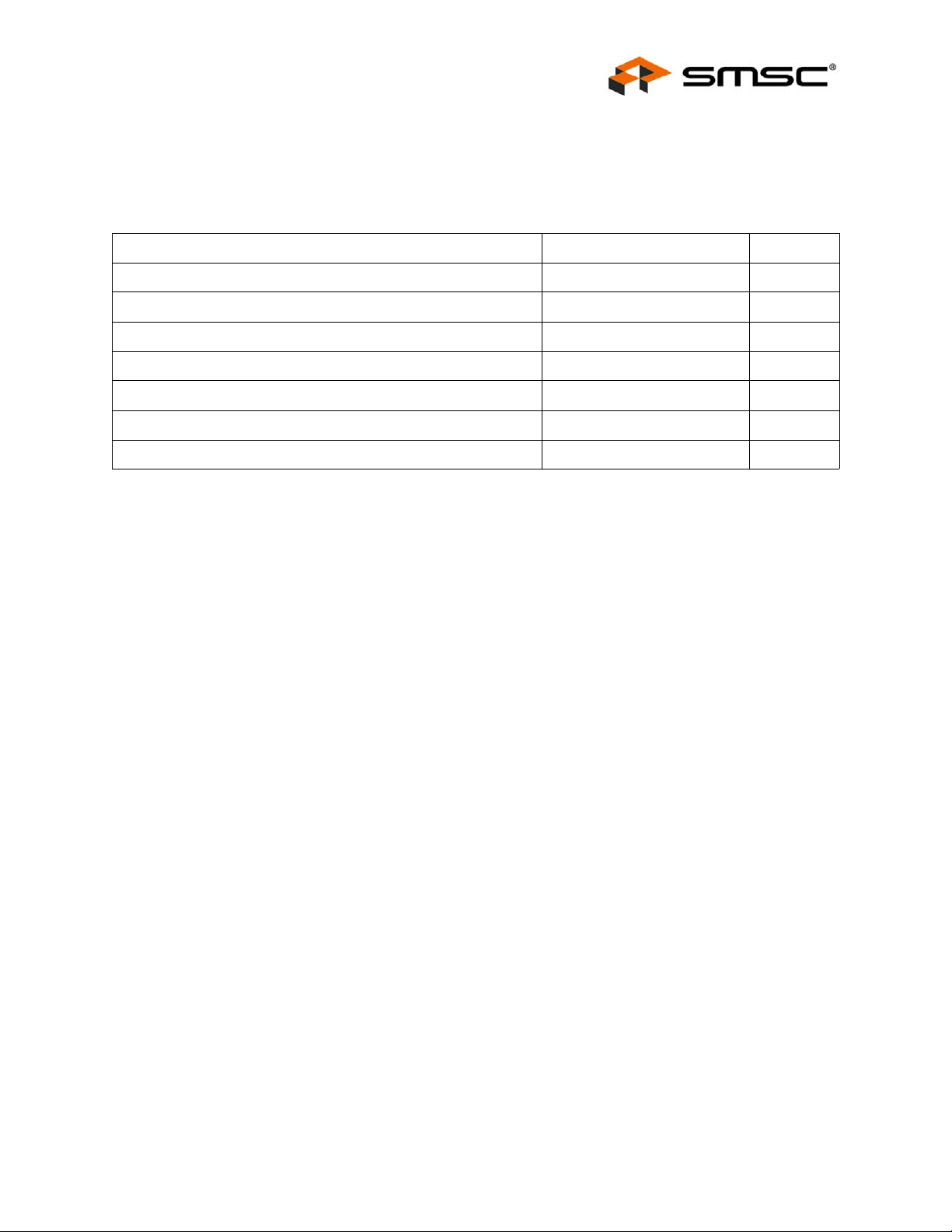

ORDER NUMBERS:

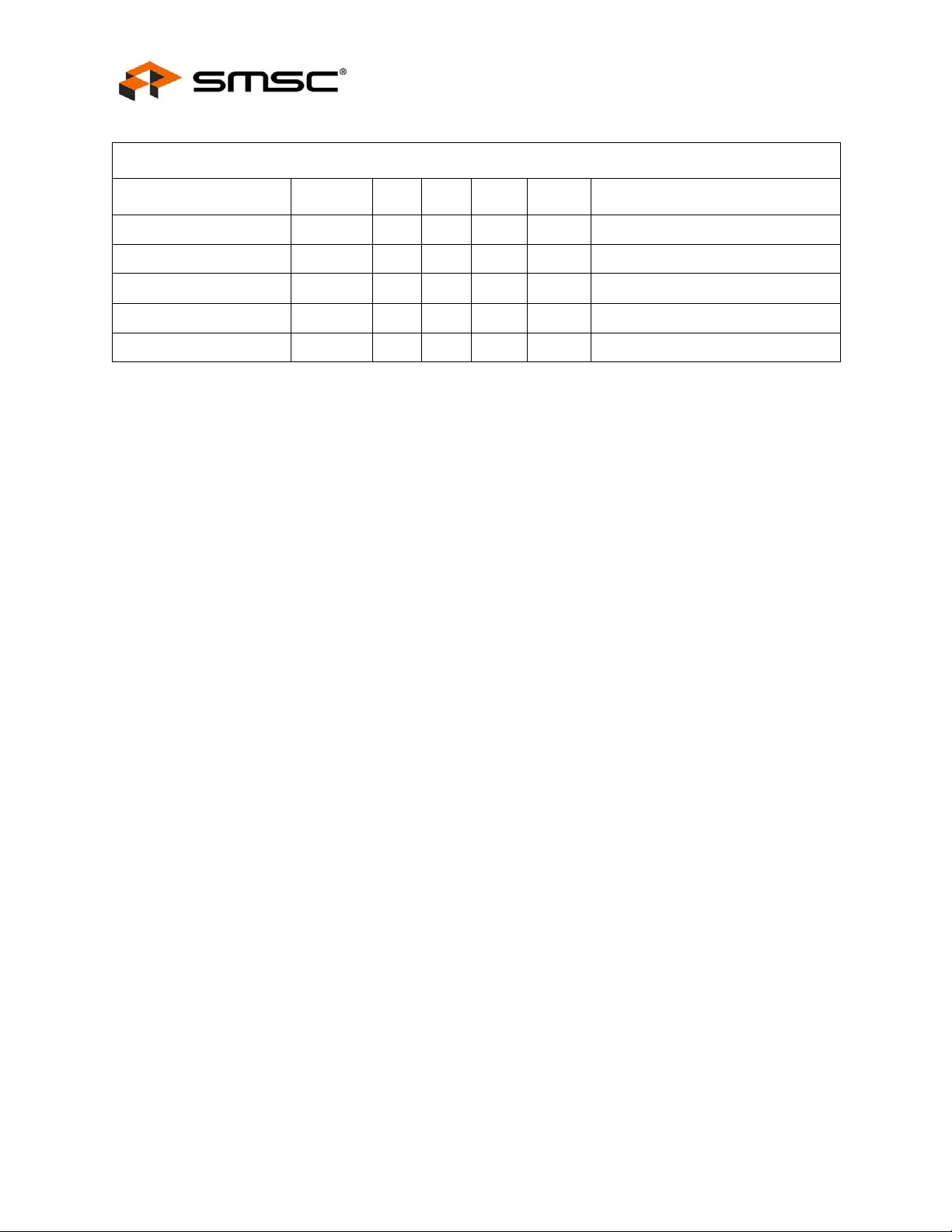

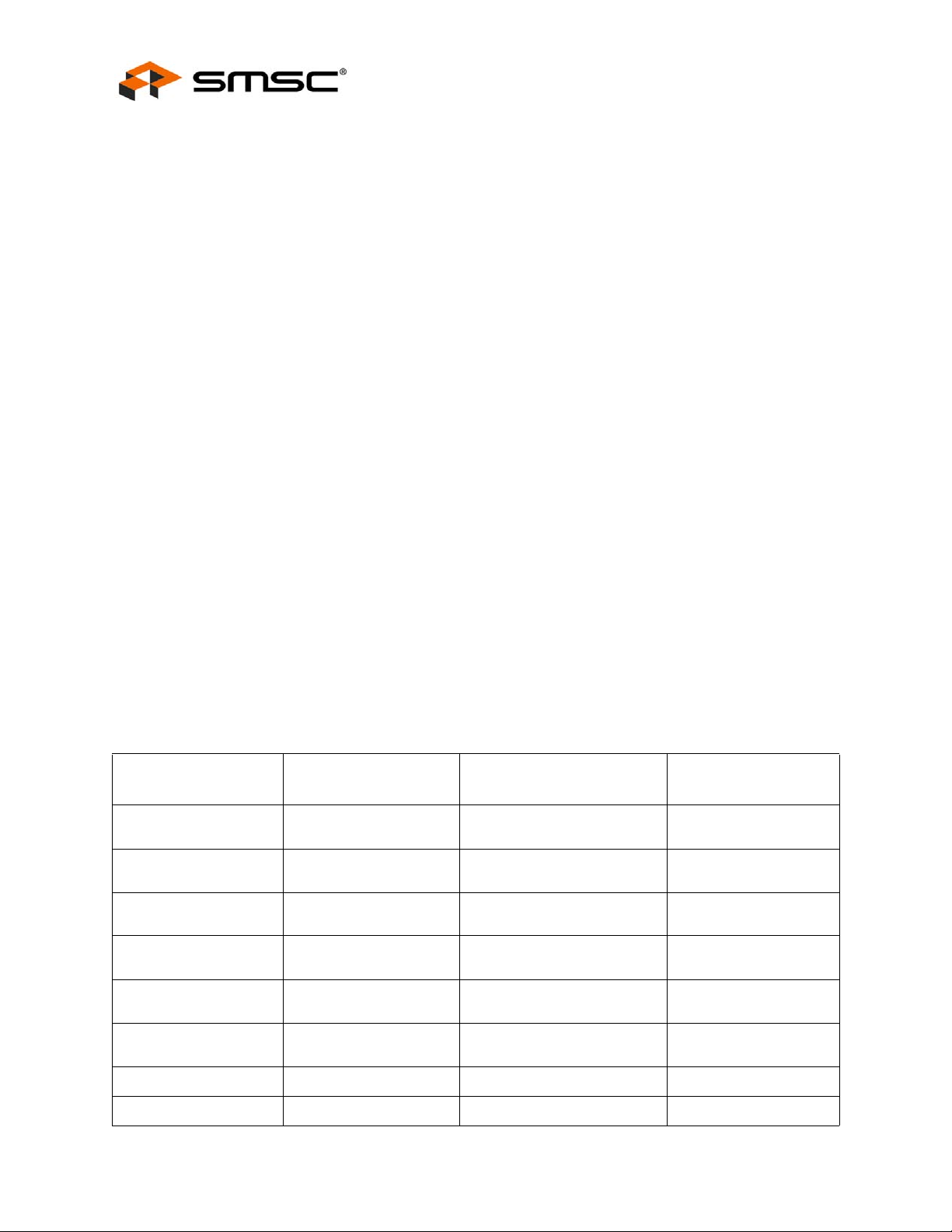

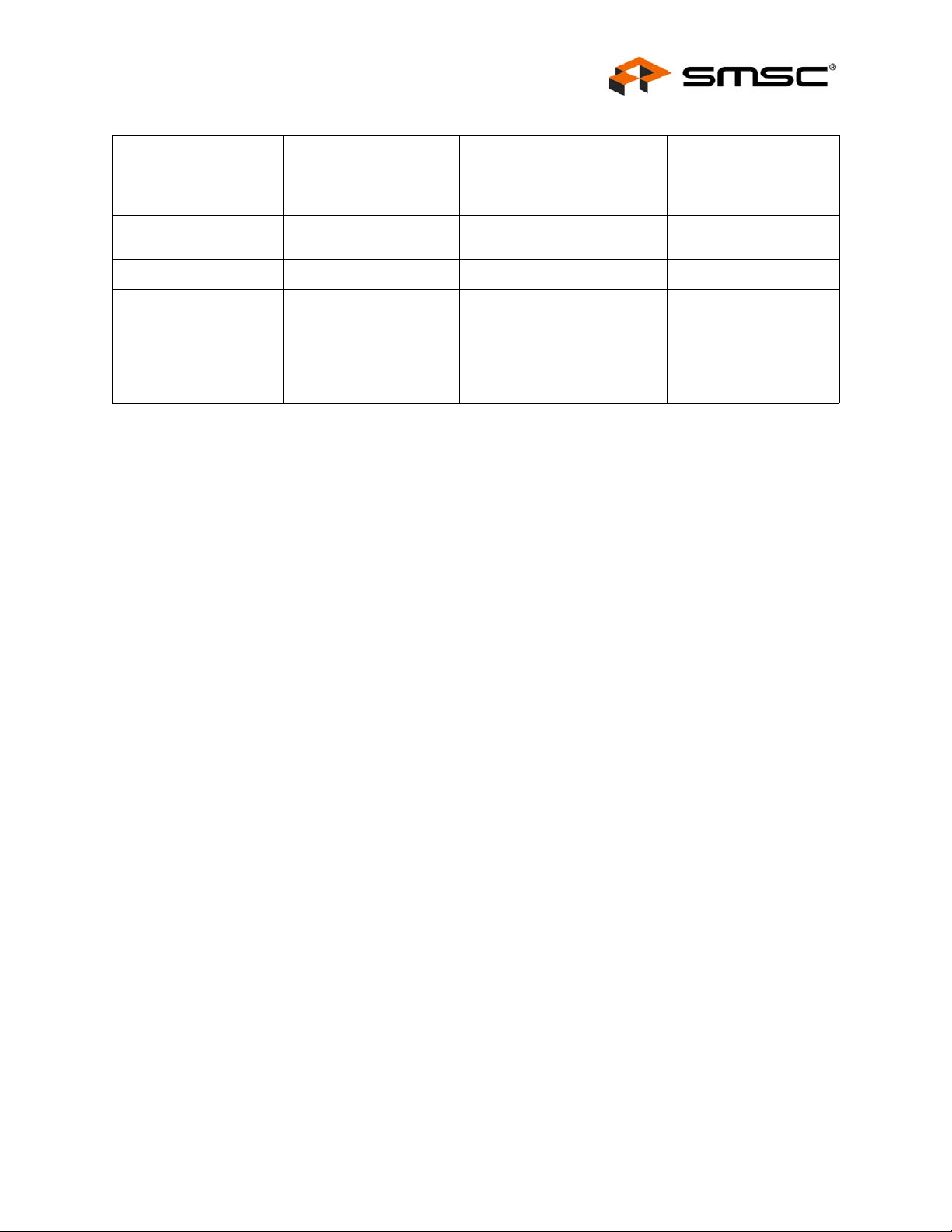

ORDERING NUMBER PACKAGE FEATURES

Datasheet

EMC2103-1-KP 12 pin, QFN Lead-Free, ROHS

Compliant

EMC2103-2-AP 16 pin, QFN Lead-Free, ROHS

Compliant

EMC2103-3-KP 12 pin, QFN Lead-Free, ROHS

Compliant

EMC2103-4-AP 16 pin, QFN Lead-Free, ROHS

Compliant

One external diode, RPM based

Fan Speed Control Algorithm, High

Frequency PWM driver, HW

Thermal / Critical shutdown,

EEPROM Load disabled

Up to three external diodes, RPM

based Fan Speed Control algorithm,

High Frequency PWM driver, HW

Thermal / Critical shutdown, 2

GPIOs, EEPROM Load disabled

One external diode, RPM based

Fan Speed Control Algorithm, High

Frequency PWM driver, HW

Thermal / Critical shutdown,

EEPROM Load enabled

Up to three external diodes, RPM

based Fan Speed Control algorithm,

High Frequency PWM driver, HW

Thermal / Critical shutdown, 2

GPIOs, EEPROM Load enabled

80 ARKAY DRIVE, HAUPPAUGE, NY 11788 (631) 435-6000, FAX (631) 273-3123

Copyright © 2008 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a mean s of illustrating typical applications. Conse quently, complete information sufficient for

construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC

reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications

before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent

rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently da ted

version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors

known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not

designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property

damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of

this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC’s website at http://www.smsc.com. SMSC is a registered

trademark of Standard Microsystems Corporation (“SMSC”). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY,

FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE

OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL

DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT;

TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD

TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

Revision 0.85 (01-29-08) 2 SMSC EMC2103

DATASHEET

Page 3

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

Table of Contents

Chapter 1 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Chapter 2 Pin Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Chapter 3 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.1 Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.2 SMBus Electrical Specifications (Client Mode). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Chapter 4 Communications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

4.1 System Management Bus Interface Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

4.2 Write Byte . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

4.3 Read Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4.4 Send Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4.5 Receive Byte. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4.6 Alert Response Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4.7 SMBus Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.8 SMBus Time-out. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Chapter 5 General Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5.1 Critical/Thermal Shutdown . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

5.1.1 SHDN_SEL Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

5.1.2 TRIP_SET Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

5.2 Fan Control Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

5.3 PWM Fan Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.4 Fan Control Look-Up Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.4.1 Programming the Look Up Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

5.4.2 DTS Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.5 RPM based Fan Speed Control Algorithm (FSC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.5.1 Programming the RPM Based Fan Speed Control Algorithm . . . . . . . . . . . . . . . . . . . . . 28

5.6 Tachometer Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

5.6.1 Stalled Fan . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

5.6.2 Aging Fan or Invalid Drive Detection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

5.7 Spin Up Routine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

5.8 Ramp Rate Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

5.9 Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

5.10 Fault Queue . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

5.11 Temperature Monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

5.11.1 Dynamic Averaging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

5.11.2 Resistance Error Correction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

5.11.3 Beta Compensation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.11.4 Digital Averaging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.12 Diode Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.12.1 Diode Faults . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

5.13 GPIOs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Chapter 6 Register Set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

6.1 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

6.1.1 Lock Entries. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

6.2 Temperature Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

6.3 Critical/Thermal Shutdown Temperature Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

6.4 Pushed Temperature Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

SMSC EMC2103 3 Revision 0.85 (01-29-08)

DATASHEET

Page 4

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

6.5 TRIP_SET Voltage Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

6.6 Ideality Factor Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

6.7 Beta Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

6.8 REC Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

6.9 Critical Temperature Limit Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

6.10 Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

6.11 Configuration 2 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

6.12 Interrupt Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

6.13 Error Status Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

6.13.1 Tcrit Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

6.14 Fan Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

6.15 Interrupt Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

6.16 Fan Interrupt Enable Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

6.17 PWM Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

6.18 PWM Base Frequency Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

6.19 Limit Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

6.20 Fan Setting Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

6.21 PWM Divide Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

6.22 Fan Configuration 1 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

6.23 Fan Configuration 2 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

6.24 Gain Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

6.25 Fan Spin Up Configuration Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

6.26 Fan Step Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

6.27 Fan Minimum Drive Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

6.28 Valid TACH Count Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

6.29 Fan Drive Fail Band Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

6.30 TACH Target Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

6.31 TACH Reading Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

6.32 Look Up Table Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.33 Look Up Table Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.34 GPIO Direction Register (EMC2103-2 Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

6.35 GPIO Output Configuration Register (EMC2103-2 Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

6.36 GPIO Input Register (EMC2103-2 Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

6.37 GPIO Output Register (EMC2103-2 Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

6.38 GPIO Interrupt Enable Register (EMC2103-2 Only). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

6.39 GPIO Status Register (EMC2103-2 Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

6.40 Software Lock Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.41 Product Features Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.42 Product ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

6.43 Manufacturer ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

6.44 Revision Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Chapter 7 Package Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

7.1 EMC2103-1 Package Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

7.2 EMC2103-2 Package Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Appendix ALook Up Table Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

A.1 Example #1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

A.2 Example #2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Appendix BRPM to Tachometer Count Look Up Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

B.1 1k RPM Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Revision 0.85 (01-29-08) 4 SMSC EMC2103

DATASHEET

Page 5

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

List of Figures

Figure 1.1 EMC2103 Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 2.1 EMC2103-1 Pin Diagram (12 Pin QFN). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 2.2 EMC2103-2 Pin Diagram (16 pin QFN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 4.1 SMBus Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 5.1 System Diagram for EMC2103 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 5.2 Block Diagram of Critical / Thermal Shutdown. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 5.3 Fan Control Look-Up Table Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 5.4 RPM based Fan Speed Control Algorithm. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 5.5 Spin Up Routine. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 5.6 Ramp Rate Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 5.7 Diode Connections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Figure 7.1 Preliminary 12 pin QFN 4mm x 4mm Package Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . 70

Figure 7.2 Preliminary 12 Pin QFN 4mm x 4mm Package Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 7.3 Recommended PCB Footprint 12-pin QFN 4mm x 4mm. . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Figure 7.4 Preliminary 16 Pin QFN 4mm x 4mm Package Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . 73

Figure 7.5 Preliminary 16 Pin QFN 4mm x 4mm Package Drawing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 7.6 Recommended PCB Footprint 16-pin QFN 4mm x 4mm. . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

SMSC EMC2103 5 Revision 0.85 (01-29-08)

DATASHEET

Page 6

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

List of Tables

Table 2.1 Pin Description for EMC2103 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 2.2 Pin Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 3.1 Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 3.2 Electrical Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 3.3 SMBus Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 4.1 Protocol Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 4.2 Write Byte Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 4.3 Read Byte Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 4.4 Send Byte Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 4.5 Receive Byte Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 4.6 Alert Response Address Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 5.1 SHDN_SEL Pin Decode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 5.2 TRIP_SET Resistor Setting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 5.3 Fan Controls Active for Operating Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 5.4 Dynamic Averaging Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 6.1 EMC2103 Register Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 6.2 Temperature Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 6.3 Temperature Data Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 6.4 Critical/Thermal Shutdown Temperature Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 6.5 Critical / Thermal Shutdown Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 6.6 Pushed Temperature Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 6.7 TRIP_SET Voltage Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 6.8 Ideality Factor Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 6.9 Ideality Factor Look-Up Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 6.10 Beta Configuration Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 6.11 Beta Compensation Look Up Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 6.12 REC Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 6.13 Limit Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 6.14 Configuration Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 6.15 Configuration 2 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 6.16 Fault Queue. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 6.17 Conversion Rate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 6.18 Interrupt Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 6.19 Error Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 6.20 Fan Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 6.21 Interrupt Enable Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 6.22 Fan Interrupt Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 6.23 PWM Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 6.24 PWM Base Frequency Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 6.25PWM_BASEx[1:0] it Decode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 6.26 Limit Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 6.27 Fan Driver Setting Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 6.28 PWM Divide Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 6.29 Fan Configuration 1 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 6.30 Range Decode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 6.31 Minimum Edges for Fan Rotation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 6.32 Update Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 6.33 Fan Configuration 2 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 6.34 Derivative Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 6.35 Error Range Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 6.36 Gain Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 6.37 Gain Decode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Revision 0.85 (01-29-08) 6 SMSC EMC2103

DATASHEET

Page 7

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

Table 6.38 Fan Spin Up Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 6.39 DRIVE_FAIL_CNT[1:0] Bit Decode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 6.40 Spin Level . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 6.41 Spin Time. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 6.42 Fan Step Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 6.43 Minimum Fan Drive Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 6.44 Valid TACH Count Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 6.45 Fan Drive Fail Band Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 6.46 TACH Target Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 6.47 TACH Reading Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 6.48 Look Up Table Configuration Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Table 6.49 Look Up Table Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 6.50 GPIO Direction Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 6.51 GPIO Output Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 6.52 GPIO Input Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 6.53 GPIO Output Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 6.54GPIO Interrupt Enable Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 6.55 GPIO Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Table 6.56 Software Lock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 6.57 Product Features Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 6.58 SHDN_SEL[2:0] Encoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 6.59 Product ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 6.60 Manufacturer ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table 6.61 Revision Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Table A.1 Look Up Table Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Table A.2 Look Up Table Example #1 Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table A.3 Fan Speed Control Table Example #1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table A.4 Fan Speed Determination for Example #1 (using settings in Table A.3) . . . . . . . . . . . . . . . . . 77

Table A.5 Look Up Table Example #2 Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table A.6 Fan Speed Control Table Example #2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table A.7 Fan Speed Determination for Example #2 (using settings in Table A.6) . . . . . . . . . . . . . . . . . 79

Table B.1 Tachometer Count to RPM Look Up Table (Range = 1000 RPM). . . . . . . . . . . . . . . . . . . . . . 80

SMSC EMC2103 7 Revision 0.85 (01-29-08)

DATASHEET

Page 8

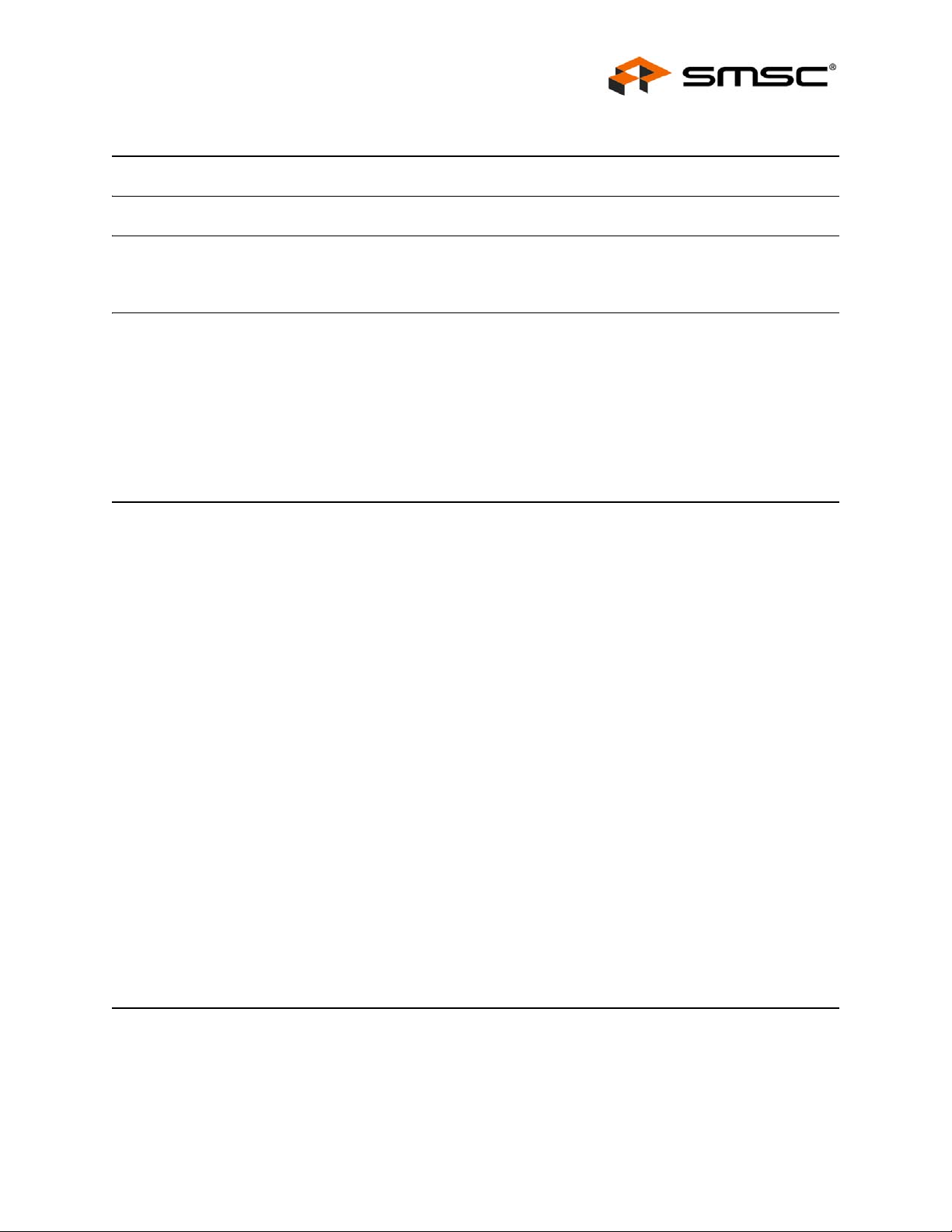

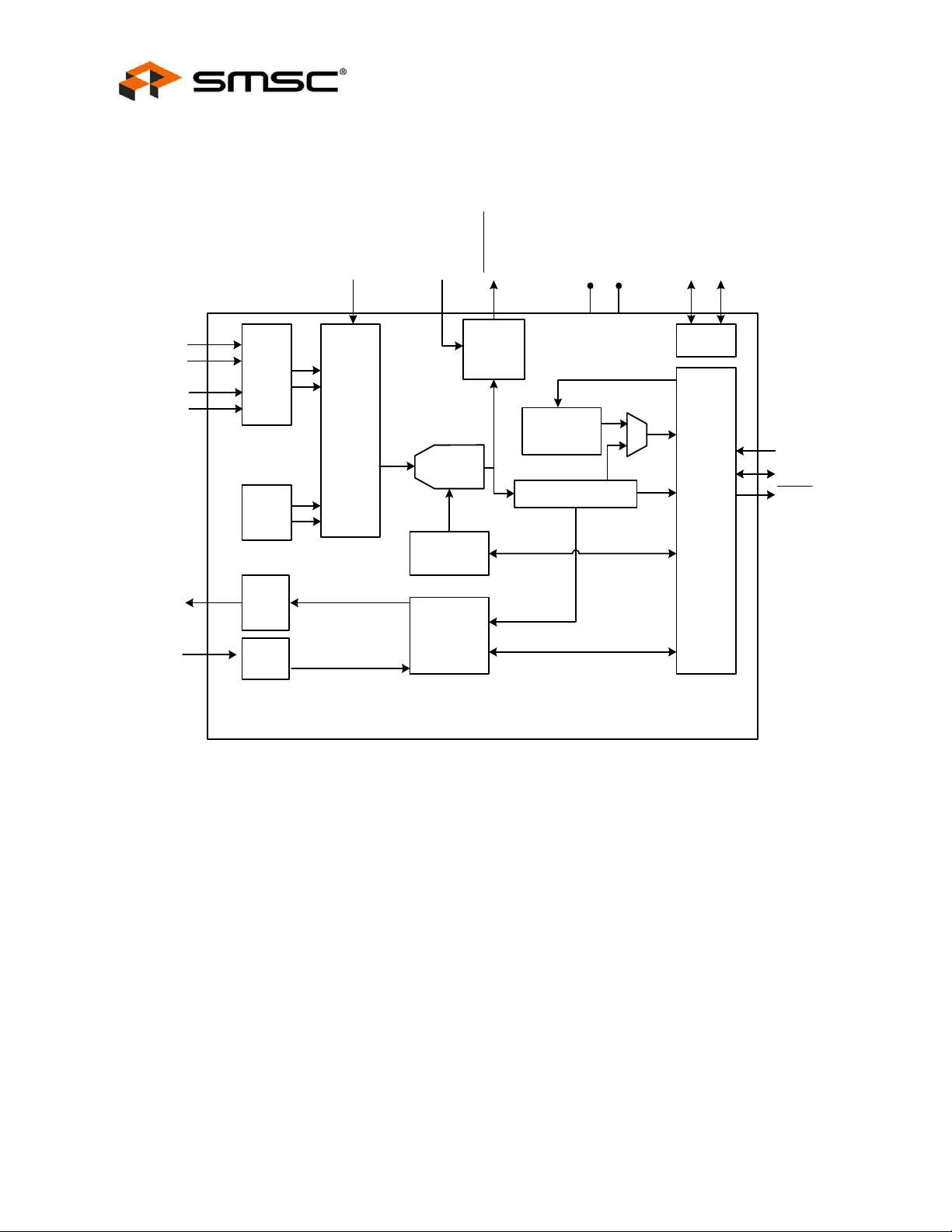

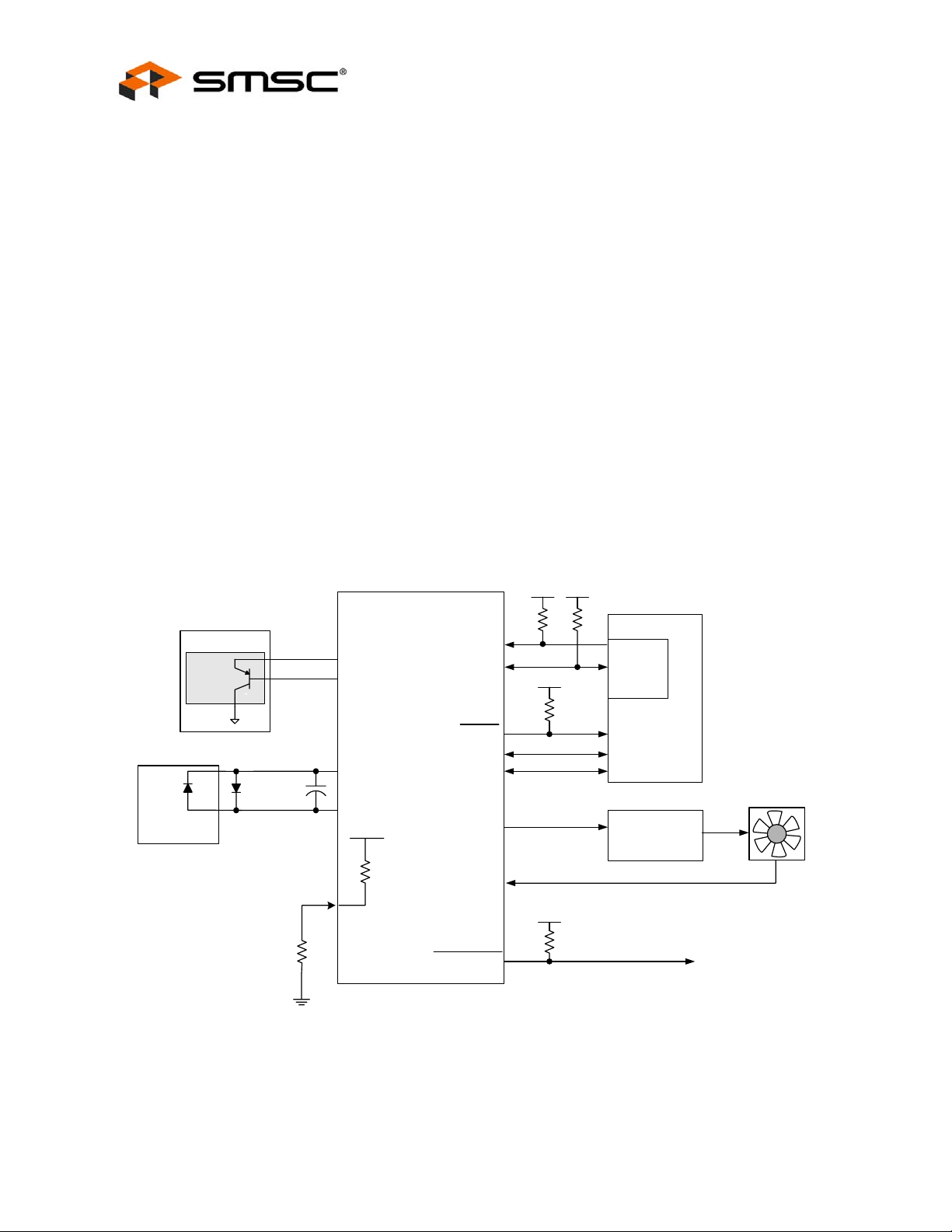

Chapter 1 Block Diagram

TRIP_SET

SHDN_SEL

RPM-Based Fan Controller with HW Thermal Shutdown

VDD

SYS_SHDN

GND

GPIO1*

GPIO2*

Datasheet

DP1

DN1

DP2 / DN3*

DN2 / DP3*

PWM

TACH

External

Temp

Diodes

Analog

Mux

Intern al

Temp

Diode

PWM

driver

Tach

* denote EMC2103-2 pins only

Figure 1.1 EMC2103 Block Diagram

Shutdown

11 bit Σ Δ

ADC

Configuration

Lookup

Table / RPM

Control

Thermal

Logic

Temp Limit

Registers

Temp Registers

GPIO

SMBus

Slave

Protocol

SMCLK

SMDATA

ALERT

Revision 0.85 (01-29-08) 8 SMSC EMC2103

DATASHEET

Page 9

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

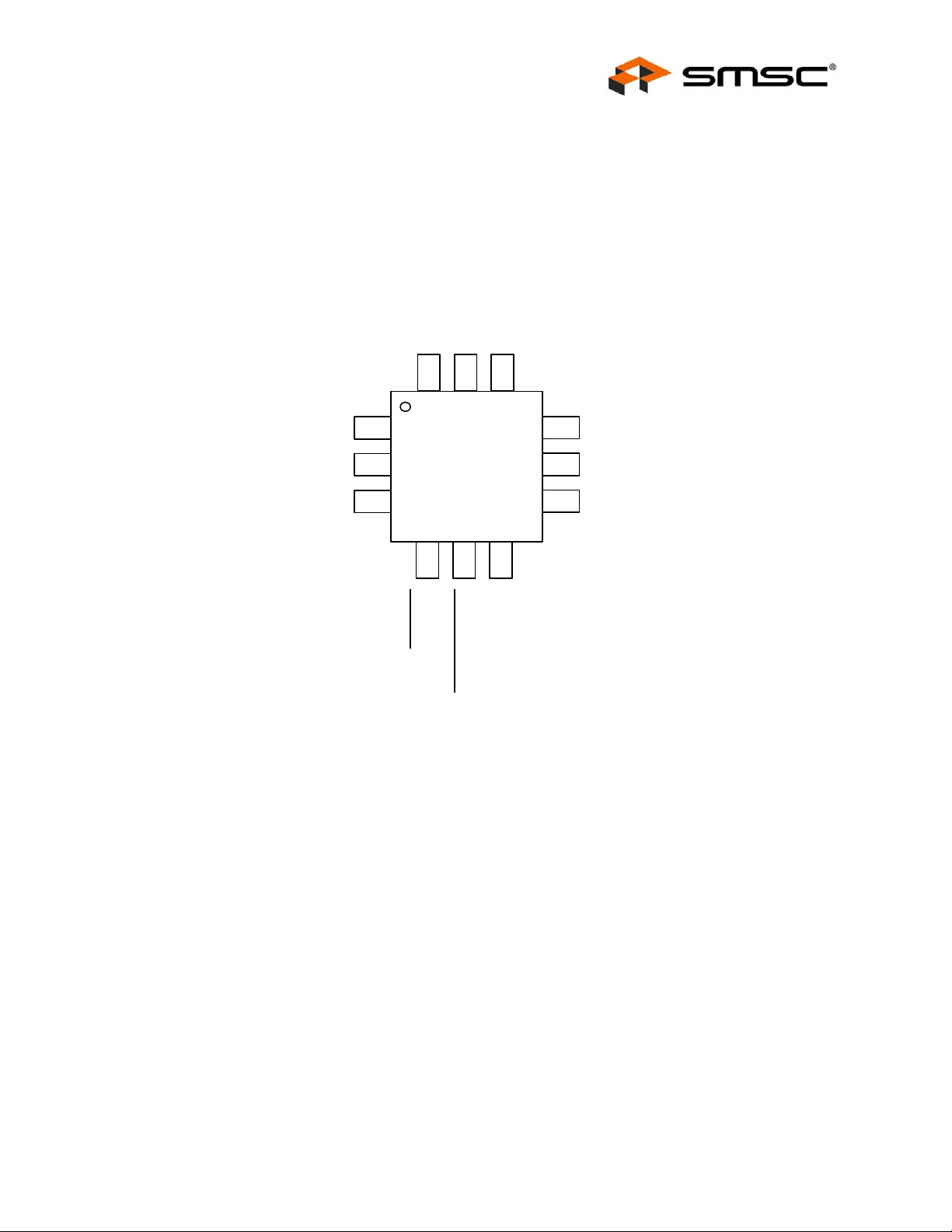

Chapter 2 Pin Layout

DN

DP

VDD

1

2

3

GND

SHDN_SEL

TRIP_SET

12

11

10

EMC2103-1

12-QFN

9

8

7

PWM

TACH

SMCLK

4

5

6

ALERT

SMDATA

SYS_SHDN

Figure 2.1 EMC2103-1 Pin Diagram (12 Pin QFN)

SMSC EMC2103 9 Revision 0.85 (01-29-08)

DATASHEET

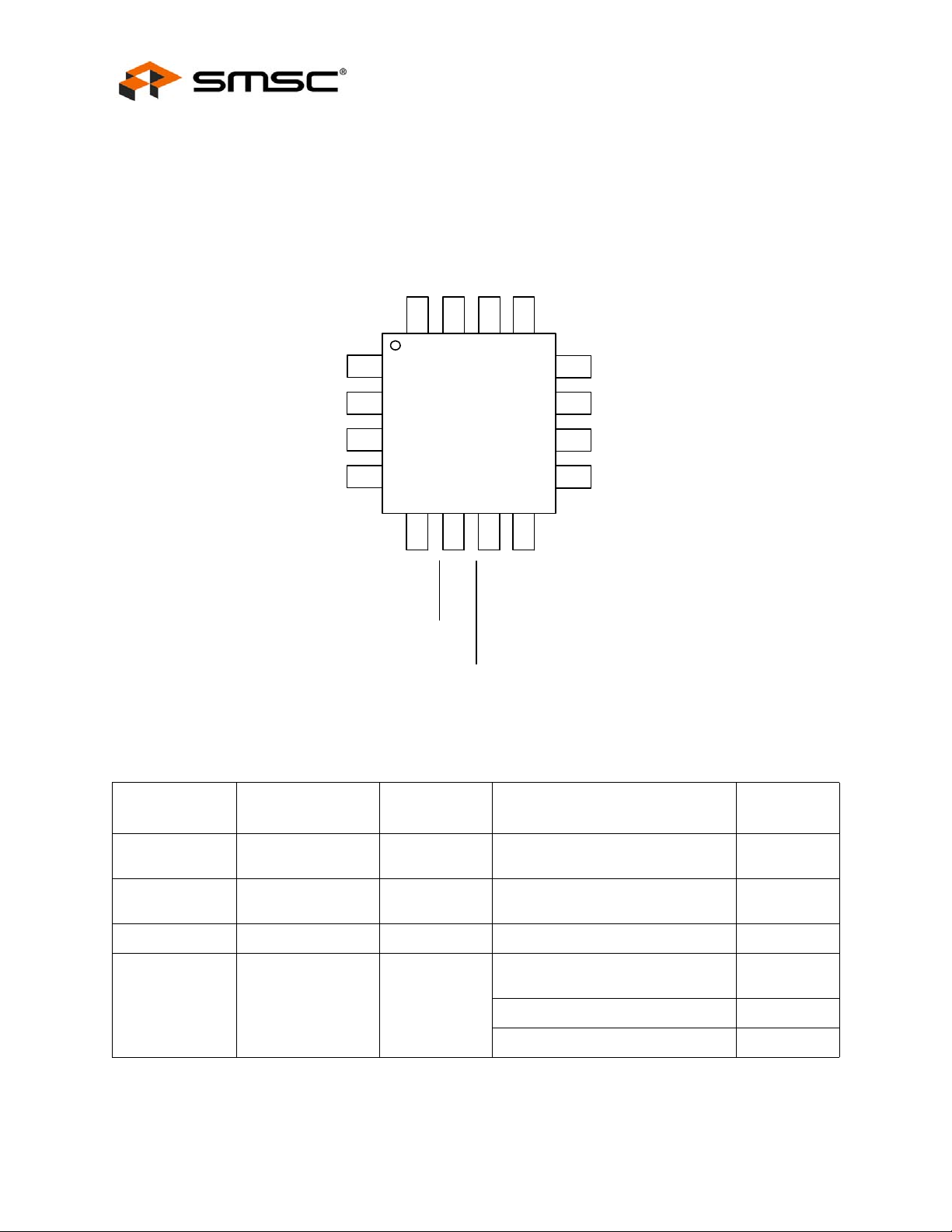

Page 10

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

DN2 / DP3

DP2 / DN3

16

15

TRIP_SET

14

SHDN_SEL

13

PIN NUMBER

EMC2103-1

DN1

DP1

VDD

GPIO1

1

2

3

EMC2103-2

16-QFN

4

5

6

7

8

GPIO2

ALERT

12

11

10

9

GND

PWM

TACH

SMCLK

SMDATA

SYS_SHDN

Figure 2.2 EMC2103-2 Pin Diagram (16 pin QFN)

Table 2.1 Pin Description for EMC2103

PIN NUMBER

EMC2103 -2 PIN NAME PIN FUNCTION PIN TYPE

11DN1

22DP1

3 3 VDD Power Supply Power

N/A 4 GPIO1

Revision 0.85 (01-29-08) 10 SMSC EMC2103

Negative (cathode) analog input for

External Diode 1.

Positive (anode) analog input for

External Diode 1.

GPI1 - General Purpose Input

(default)

GPO1 - Open Drain digital output OD (5V)

GPO1 - Push-pull digital output DO

AIO

AIO

DI (5V)

DATASHEET

Page 11

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

Table 2.1 Pin Description for EMC2103 (continued)

PIN NUMBER

EMC2103-1

PIN NUMBER

EMC2103 -2 PIN NAME PIN FUNCTION PIN TYPE

GPI2 - General Purpose Input

(default)

N/A 5 GPIO2

GPO2 - Open Drain digital output OD (5V)

GPO2 - Push-pull digital output DO

4 6 ALERT

Active low interrupt - requires

external pull-up resistor.

Active low Critical / Thermal

5 7 SYS_SHDN

Shutdown output - requires external

pull-up resistor

68SMDATA

79SMCLK

SMBus data input/output - requires

external pull-up resistor

SMBus clock input - requires

external pull-up resistor

8 10 TACH Tachometer input for the Fan DI (5V)

PWM - Open Drain PWM drive

output for the Fan

911PWM

(default)

PWM - Push-Pull PWM drive output

for the Fan

DI (5V)

OD (5V)

OD (5V)

DIOD (5V)

DI (5V)

OD (5V)

DO

10 12 GND Ground connection Power

11 13 SHDN_SEL

12 14 TRIP_SET

Selects the hardware shutdown

channel and operating mode

Voltage input to set the Critical /

Thermal Shutdown threshold

AIO

AIO

Negative (cathode) analog input for

N/A 15 DN2 / DP3

External Diode 2 and positive

(anode) analog input for External

AIO

Diode 3

Positive (anode) analog input for

N/A 16 DP2 / DN3

External Diode 2 and negative

(cathode) connection for External

AIO

Diode 3

The pin type are described in detail below. All pins labelled with (5V) are 5V tolerant.

SMSC EMC2103 11 Revision 0.85 (01-29-08)

DATASHEET

Page 12

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

Table 2.2 Pin Types

PIN TYPE DESCRIPTION

Power This pin is used to supply power or ground to the device.

DI

AIO

DO

DIOD

OD

Digital Input - this pin is used as a digital input. This pin is

5V tolerant.

Analog Input / Output - this pin is used as an I/O for analog

signals.

Push / Pull Digital Output - this pin is used as a digital

output. It can both source and sink current.

Digital Input / Open Drain Output this pin is used as an

digital I/O. When it is used as an output, It is open drain

and requires a pull-up resistor. This pin is 5V tolerant.

Open Drain Digital Output - this pin is used as a digital

output. It is open drain and requires a pull-up resistor. This

pin is 5V tolerant.

Revision 0.85 (01-29-08) 12 SMSC EMC2103

DATASHEET

Page 13

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

Chapter 3 Electrical Characteristics

Table 3.1 Absolute Maximum Ratings

Voltage on 5V tolerant pins -0.3 to 5.5 V

Voltage on VDD pin -0.3 to 4 V

Voltage on any other pin to GND -0.3 to V

Package Power Dissipation 0.8W up to T

Junction to Ambient (θ

) 50 °C/W

JA

+ 0.3 V

DD

= 85°C W

A

Operating Ambient Temperature Range -40 to 125 °C

Storage Temperature Range -55 to 150 °C

ESD Rating, All Pins, HBM 2000 V

Note: Stresses above those listed could cause permanent damage to the device. This is a stress

rating only and functional operation of the device at any other conditio n above those indicated

in the operation sections of this specification is not implied. When powering this device from

laboratory or system power supplies, it is important that the Absolute Maximum Ratings not be

exceeded or device failure can result. Some power supplies exhibit voltage spikes on their

outputs when the AC power is switched on or off. In addition, voltage transients on the AC

power line may appear on the DC output. If this possibility exi sts, it is suggested that a clamp

circuit be used.

Note: All voltages are relative to ground.

Note: θ

numbers are based on a recommended four 12 mil via s conn ecting the the rma l pad to PCB

JA

ground.

SMSC EMC2103 13 Revision 0.85 (01-29-08)

DATASHEET

Page 14

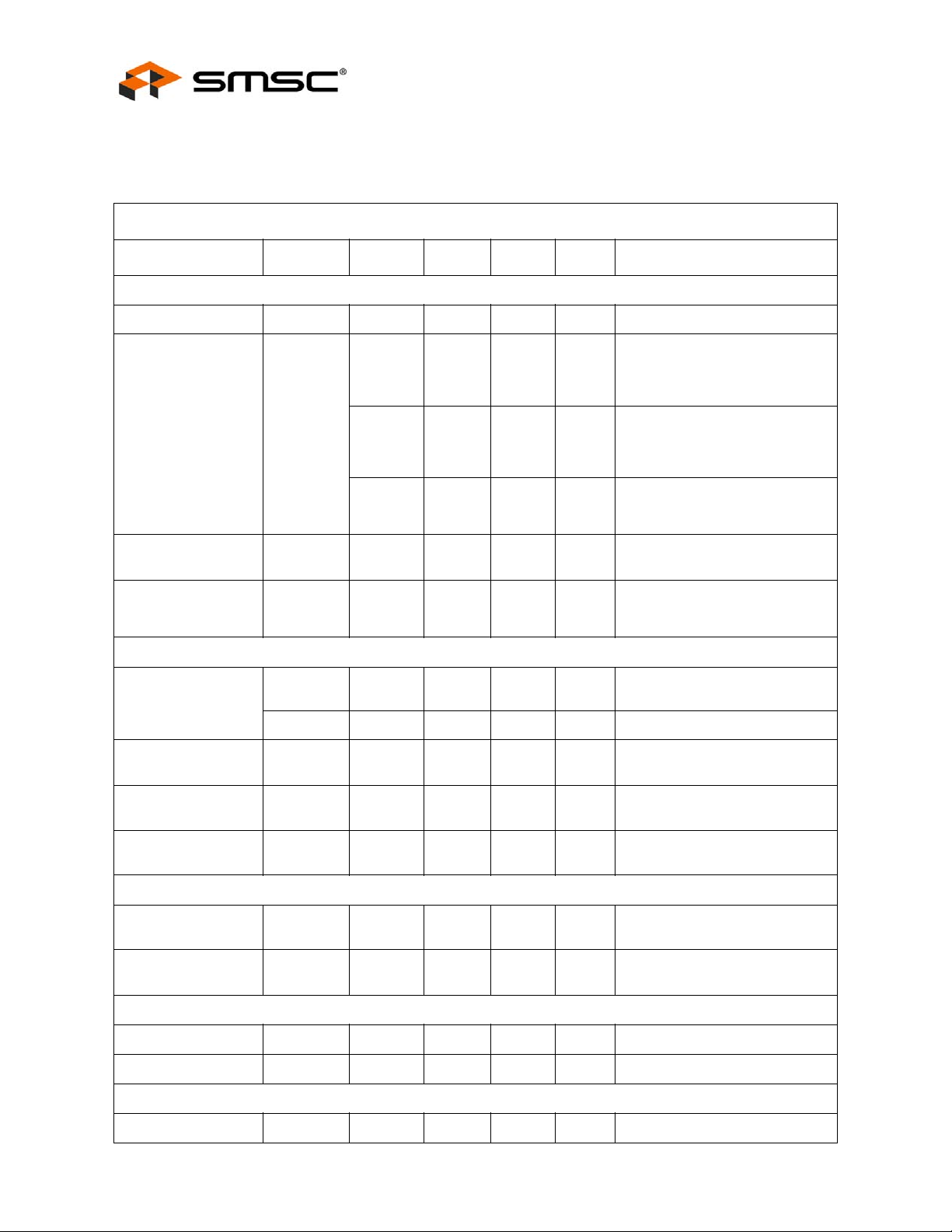

3.1 Electrical Specifications

Table 3.2 Electrical Specifications

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

VDD = 3V to 3.6V, T

= -40°C to 125°C, all Typical values at TA = 27°C unless otherwise noted.

A

CHARACTERISTIC SYMBOL MIN TYP MAX UNIT CONDITIONS

DC Power

Supply Voltage V

DD

33.33.6V

4 Conversions / second, Fan

1.3 1.8 mA

Driver active at maximum PWM

frequency, Dynamic Averaging

Enabled (EMC2103-2)

4 Conversions / second, Fan

Supply Current I

DD

11.5mA

Driver active at maximum PWM

frequency, Dynamic Averaging

Enabled (EMC2103-1)

1 Conversions / second, Fan

450 750 uA

Driver not active, Dynamic

Averaging Disabled

First Conversion

Ready

t

CONV_T

300 ms

Time after power up before all

channels updated

Time before SMBus

SMBus Delay t

SMB_D

10 ms

communications should be sent

by host

External Temperature Monitors

Temperature

±0.5 ±1 °C

Accuracy

±1 ±2 °C -40°C < T

Temperature

Resolution

Diode decoupling

capacitor

Resistance Error

Corrected

C

FILTER

R

SERIES

0.125 °C

2200 2700 pF

100 Ohm

Internal Temperature Monitor

Temperature

Accuracy

Temperature

Resolution

T

DIE

±1 ±2 °C

0.125 °C

PWM Fan Driver

PWM Resolution PWM 256 Steps

PWM Duty Cycle DUTY 0 100 %

TRIP_SET Measurement

Voltage Accuracy V

TRIP

0.5 1 %

60°C < T

30°C < TA < 100°C

DIODE

DIODE

< 125°C

< 125°C

Connected across external

diode, CPU, GPU, or AMD diode

Sum of series resistance in both

DP and DN lines

Revision 0.85 (01-29-08) 14 SMSC EMC2103

DATASHEET

Page 15

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

Table 3.2 Electrical Specifications (continued)

VDD = 3V to 3.6V, T

= -40°C to 125°C, all Typical values at TA = 27°C unless otherwise noted.

A

CHARACTERISTIC SYMBOL MIN TYP MAX UNIT CONDITIONS

T emperature Decode

Accuracy

T

TRIP

1 2 °C 5% external resistor

0.5 °C 1% external resistor

RPM Based Fan Controller

Tachometer Range TACH 480 16000 RPM

Tachometer Setting

Accuracy

Δ

TACH

±2.5 ±5 %

Digital I/O pins

Input High Voltage V

Input Low Voltage V

Output High Voltage V

Output Low Voltage V

IH

IL

OH

OL

2.0 V

0.8 V

VDD -

0.4

0.4 V 8 mA current sink

8 mA current drive

V

ALERT and SYS_SHDN pins

Leakage Current I

LEAK

±5 uA

Device powered or unpowered

TA < 85°C

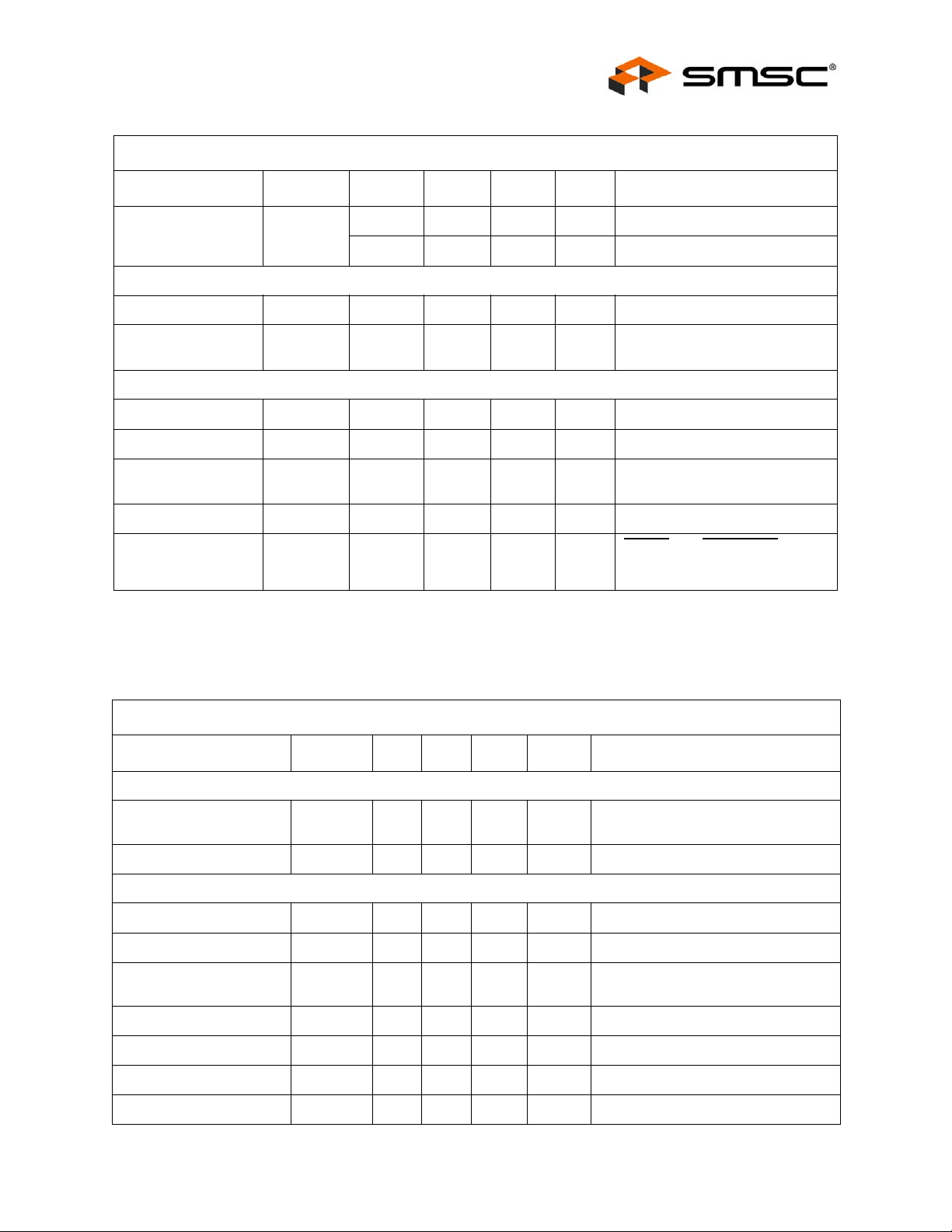

3.2 SMBus Electrical Specifications (Client Mode)

Table 3.3 SMBus Electrical Specifications

VDD= 3V to 3.6V, T

CHARACTERISTIC SYMBOL MIN TYP MAX UNITS CONDITIONS

Input High/Low Current I

Input Capacitance C

Clock Frequency f

Spike Suppression t

Bus free time Start to

Stop

Setup Time: Start t

Setup Time: Stop t

Data Hold Time t

Data Setup Time t

= -40°C to 125°C Typical values are at TA = 27°C unless otherwise noted.

A

SMBus Interface

IH / IIL

IN

410 pF

±5 uA Device powered or unpowered

TA < 85°C

SMBus Timing

SMB

SP

t

BUF

SU:STA

SU:STP

HD:DAT

SU:DAT

10 400 kHz

50 ns

1.3 us

0.6 us

0.6 us

0.6 6 us

0.6 72 us

SMSC EMC2103 15 Revision 0.85 (01-29-08)

DATASHEET

Page 16

RPM-Based Fan Controller with HW Thermal Shutdown

T able 3.3 SMBus Electrical Specifications (continu ed)

VDD= 3V to 3.6V, TA = -40°C to 125°C Typical values are at TA = 27°C unless otherwise noted.

CHARACTERISTIC SYMBOL MIN TYP MAX UNITS CONDITIONS

Datasheet

Clock Low Period t

Clock High Period t

Clock/Data Fall time t

Clock/Data Rise time t

Capacitive Load C

LOW

HIGH

FALL

RISE

LOAD

1.3 us

0.6 us

300 ns Min = 20+0.1C

300 ns Min = 20+0.1C

400 pF Total per bus line

LOAD

LOAD

ns

ns

Revision 0.85 (01-29-08) 16 SMSC EMC2103

DATASHEET

Page 17

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

Chapter 4 Communications

4.1 System Management Bus Interface Protocol

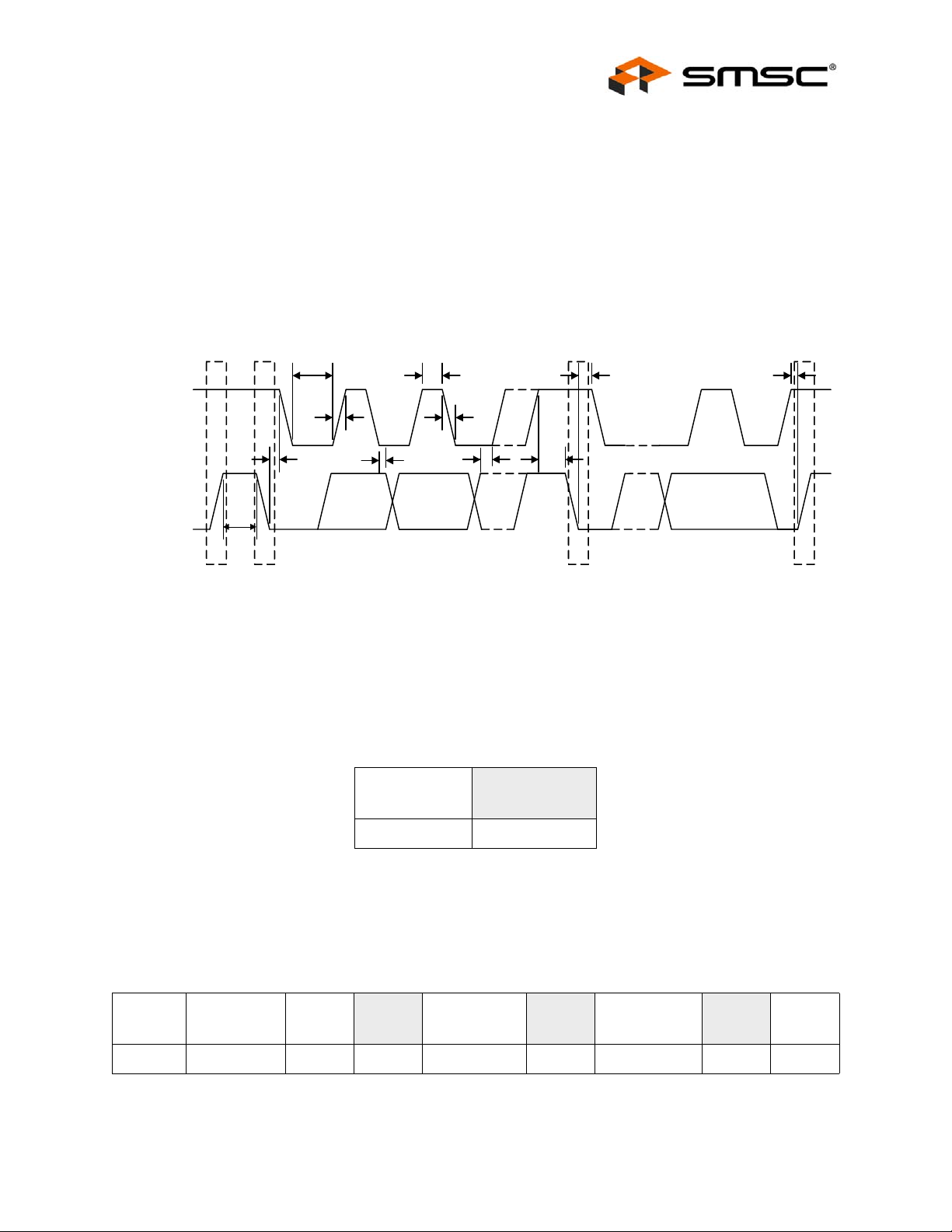

The EMC2103 communicates with a host controller, such as an SMSC SIO, through the SMBus. The

SMBus is a two-wire serial communication protocol between a computer host and its peripheral

devices. A detailed timing diagram is shown in Figure 4.1. Stretching of the SMCLK signal is supported,

however the EMC2103 will not stretch the clock signal.

SMCLK

SMDATA

T

LOW

T

T

HD:STA

T

HD:DAT

T

BUF

P

S

S - Start Condition

RISE

T

HIGH

T

FALL

T

SU:DAT

T

HD:STA

T

SU:STA

S

P - Stop Condition

T

SU:STO

P

Figure 4.1 SMBus Timing Diagram

The EMC2103 contains a single SMBus interface. The EMC2103 client interfaces are SMBus 2.0

compatible and support Send Byte, Read Byte, Receive Byte and the Alert Response Address as valid

protocols. These protocols are used as shown below.

All of the below protocols use the convention in Table 4.1.

Table 4.1 Protocol Format

DATA SENT

TO DEVICE

DATA SENT TO

THE HOST

# of bits sent # of bits sent

4.2 Write Byte

The Write Byte is used to write one byte of data to the registers as shown below Table 4.2:

Table 4.2 Write Byte Protocol

START

SLAVE

ADDRESS WR

ACK

REGISTER

ADDRESS ACK

0 -> 1 0101_110 0 0 0 -> 1 0 XXh 0 1 -> 0

SMSC EMC2103 17 Revision 0.85 (01-29-08)

DATASHEET

REGISTER

DATA ACK STOP

Page 18

4.3 Read Byte

The Read Byte protocol is used to read one byte of data from the registers as show n in Table 4.3.

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

Table 4.3 Read Byte Protocol

SLAVE

START

0 -> 1 0101_110 0 0 XXh 0 0 -> 1 0101_110 1 0 XXh 1 1 -> 0

ADDRESS WR

ACK

REGISTER

ADDRESS ACK START

SLAVE

ADDRESS RD ACK

REGISTER

DATA NACK STOP

4.4 Send Byte

The Send Byte protocol is used to set the internal address register pointer to the correct address

location. No data is transferred during the Send Byte protocol as shown in Table 4.4.

Table 4.4 Send Byte Protocol

SLA VE

START

0 -> 1 0101_110 0 0 XXh 1 1 -> 0

ADDRESS WR

ACK

REGISTER

ADDRESS ACK STOP

4.5 Receive Byte

The Receive Byte protocol is used to read data from a register when the internal register address

pointer is known to be at the right location (e.g. set via Send Byte). This is used for consecutive reads

of the same register as shown in Table 4.5.

Table 4.5 Receive Byte Protocol

START

0 -> 1 0101_110 1 0 XXh 1 1 -> 0

SLA VE

ADDRESS RD

ACK REGISTER DATA NACK STOP

4.6 Alert Response Address

The ALERT output can be used as a processor interrupt or as an SMBus Alert when configured to

operate as an interrupt.

When it detects that the ALERT

to the general address of 0001_100b. All devices with active i nterrupts will respond with their client

address as shown in Table 4.6.

Table 4.6 Alert Response Address Protocol

ALERT

START

0 -> 1 0001_100 1 0 0101_1100 1 1 -> 0

Revision 0.85 (01-29-08) 18 SMSC EMC2103

RESPONSE

ADDRESS RD

pin is asserted, the host will send the Alert Response Address (ARA)

ACK

DEVICE

ADDRESS NACK STOP

DATASHEET

Page 19

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

The EMC2103 will respond to the ARA in the following way i f the ALERT pin is asserted.

1. Send Slave Address and verify that full slav e address was sent (i.e. the SMBus communication

from the device was not prematurely stopped due to a bus contention event).

2. Set the MASK bit to clear the ALERT pin.

4.7 SMBus Address

The EMC2103 SMBus Address is fixed at 0101_110xb.

Other addresses are available. Contact SMSC for details.

Attempting to communicate with the EMC2103 SMBus interface with an invalid slave address or invalid

protocol will result in no response from the devi ce and will not affect its register contents.

4.8 SMBus Time-out

The EMC2103 includes an SMBus time-out feature. Following a 30ms period of inactivity on the

SMBus, the device will time-out and reset the SMBus interface.

SMSC EMC2103 19 Revision 0.85 (01-29-08)

DATASHEET

Page 20

Chapter 5 General Description

The EMC2103 is an SMBus compliant fan controller with one external (EMC2103-2 offers up to three

external diode channels) and one internal temperature channels. The fan driver can be operated using

two methods each with two modes. The methods include an RPM based Fan Speed Control Algorithm

and a direct PWM drive setting. The modes include manually programming the desired settings or

using the internal programmable temperature look-up table to select the desired setting based on

measured temperature.

The temperature monitors offer 1°C accuracy (for external diodes) with sophisticated features to

reduce errors introduced by series resistance and beta variation of substrate the rmal diode transistors

commonly found in processors (including support of the BJT o r transistor model for a CPU diode).

The EMC2103 allows the user to program temperatures generated from external sources to control

the fan speed. This functionality also supports DTS data from the CPU. By pushing DTS or standard

temperature values into dedicated registers, the external temperature readings can be used in

conjunction with the external diode(s) and interna l diode to control the fan speed.

The EMC2103 also includes a hardware programmable temperature limit and dedicated system

shutdown output for thermal protection of critical circuitry.

Figure 5.1 shows a system diagram of the EMC2103.

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

Thermal

diode

Optional antiparallel diode

CPU

* denotes EMC2103-2 only

EMC2103

DP1

DN1

DP2 / DN3*

DN2 / DP3*

1.5V

1.2k

TRIP_SET

SYS_SHDN

SMCLK

SMDATA

ALERT

GPIO1*

GPIO2*

PWM

TACH

VDD VDD

Figure 5.1 System Diagram for EMC2103

VDD

VDD

HOST

SMBus

Interface

Fan Drive

Circuitry

Revision 0.85 (01-29-08) 20 SMSC EMC2103

DATASHEET

Page 21

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

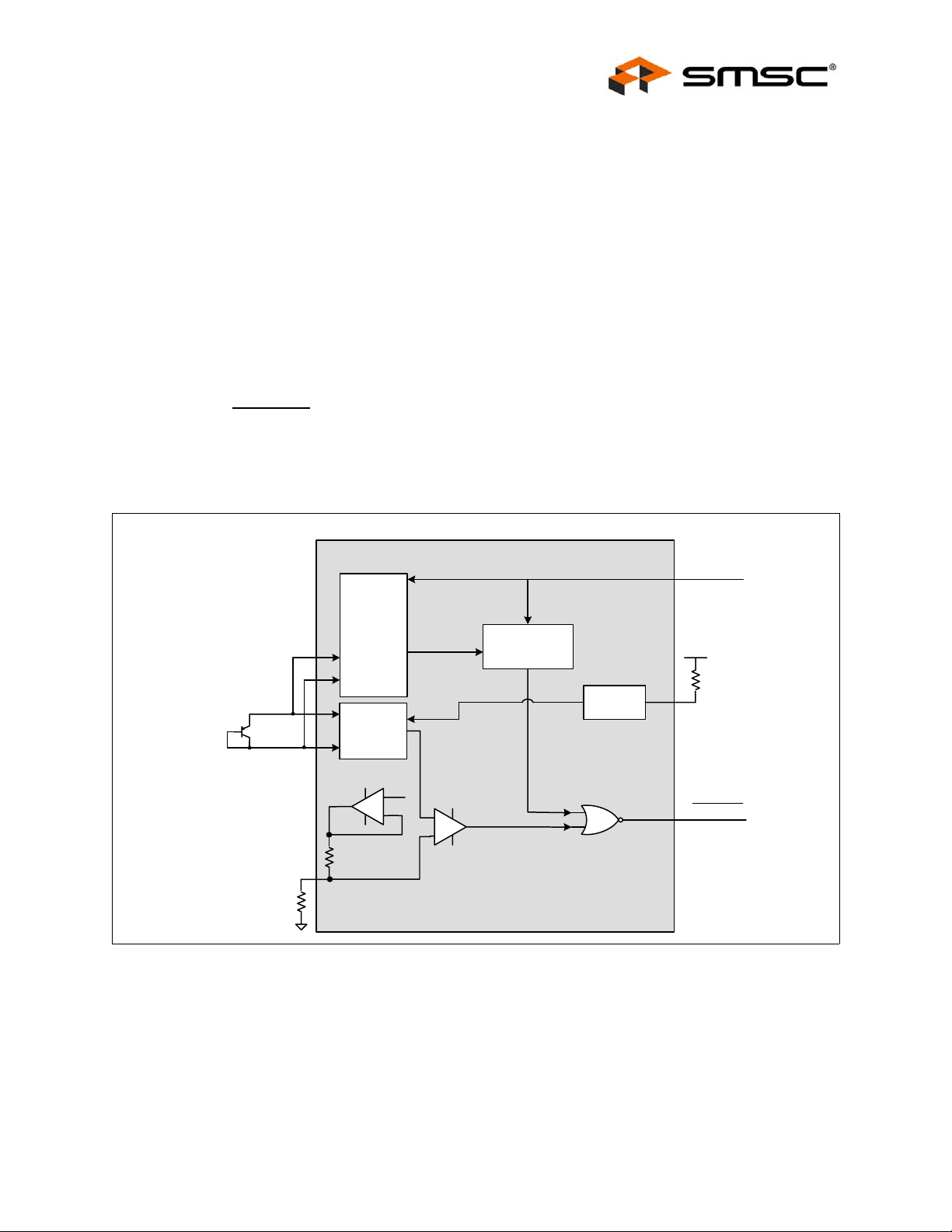

5.1 Critical/Thermal Shutdown

The EMC2103 provides a hardware Critical/Thermal Shutdown function for systems. Figure 5.2 is a

block diagram of this Critical/Thermal Shutdown function. The Critical/Thermal Shutdown function

accepts configuration information from the fixed states of the SHDN_SEL pin as described in

Section 5.1.1.

Each of the software programmed temperature limits can be optionally co nfigured to act as inputs to

the Critical / Thermal Shutdown independent of the hardware shutdown operation. When configured to

operate this way, the SYS_SHDN# pin will be asserted when the temperature meets or exceeds the

limit. The pin will be released when the temperature drops below the limit however the individual status

bits will not be cleared if set (see Section 6.13).

The analog portion of the Critical/Thermal Shutdown function monitors the hardware determined

shutdown channel (see Section 5.1.1). This measured temperature is then compared with TRIP_SET

point. This TRIP_SET point is set by the system designer with a single external resistor divider as

described in Section 5.1.2.

The SYS_SHDN is asserted when the indicated temperature meets or exceeds the temperature

threshold (TP) established by the TRIP_SET input pin for a number of consecutive measurements

defined by the fault queue. If the HW_SHDN output is asserted an d the temperature drops below the

threshold, then it will be set to a logic ‘0’ state.

H/W Thermal

Shutdown Sensor

TRIP_SET

Critical / Thermal Shutdown

Temperature

Conversion

Temperature

Conversion

Figure 5.2 Block Diagram of Critical / Thermal Shutdown

Software

Shutdown Enable

SW_SHDN

HW_SHDN

Resistor

Decode

SMBus

Traffic

VDD

SHDN_SEL

SYS_SHDN

SMSC EMC2103 21 Revision 0.85 (01-29-08)

DATASHEET

Page 22

5.1.1 S HDN_SEL Pin

The EMC2103 has a ‘strappable’ input (SHDN_SEL) allowing for configuration of the hardware

Critical/Thermal Shutdown input channel. The pull-up resistor used on this pin identifies which

configuration setting is used as shown in Table 5.1.

.

PULL UP RESISTOR MODE OF OPERATION CONFIGURATION MECHANISM

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

Table 5.1 SHDN_SEL Pin Decode

4.7k Ohm

<

6.8k Ohm

10k Ohm

15k Ohm Internal Diode Host control via SMBus

22k Ohm

>

33k Ohm

Note 5.1 For the EMC2103-1, the decode for a 22k Ohm resistor on the SHDN_SEL pin will be to

use the External Diode 1 channel in Diode Mode (the same as the decode for a 6.8k Ohm

resistor) as the hardware shutdown device.

5.1.2 TRIP_SET Pin

External Diode 1 Simple Mode Beta compensation disabled, REC

disabled - recommended for AMD

CPU diodes

External Diode 1 Diode Mode Beta compensation disabled, REC

enabled

External Diode 1 Transistor Mode Beta compensation enabled, REC

enabled - recommended for Intel

45nm and 65mn CPU diodes

External Diode 2 Transistor Mode Beta Compensation enabled, REC

enabled (EMC2103-2 only) See

Note 5.1

External Diode 1 Transistor Mode Beta compensation enabled, REC

enabled

Host control via SMBus

Host control via SMBus

Host control via SMBus

Host control via SMBus

Host control via SMBus

The EMC2103’s TRIP_SET pin is an analog input to the Critical/Thermal Shutdown block which sets

the Thermal Shutdown temperature. The system designer creates a voltage level at the input through

a simple resistor connected to GND as shown in Figure 5.2. The value of this resistor is used to create

an input voltage on the TRIP_SET pin which is translated into a temperature ranging from 65°C to

127°C as shown in Table 5.2

APPLICATION NOTE: Current only flows when the TRIP_SET pin is being mon itored. At all othe r ti mes, the intern al

reference voltage is removed and the TRIP_SET pin will be pul led down to ground.

APPLICATION NOTE: The TRIP_SET pin circuitry is designed to use a 1% resistor externally. Using a 1% resistor

will result in the Thermal / Critical Shutdown temperature being decoded correctly. If a 5%

resistor is used, then the Thermal / Critical Shutdown temperature may be decoded with as

much as ±1°C error.

Revision 0.85 (01-29-08) 22 SMSC EMC2103

DATASHEET

Page 23

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

Table 5.2 TRIP_SET Resistor Setting

T

(°C) RSET (1%) T

TRIP

65 0.0 97 1240

66 28.7 98 1330

67 48.7 99 1400

68 69.8 100 1500

69 90.9 101 1580

70 113 102 1690

71 137 103 1820

72 158 104 1960

73 182 105 2050

74 210 106 2210

75 237 107 2370

(°C) RSET (1%)

TRIP

76 261 108 2550

77 294 109 2740

78 324. 110 2940

79 348 111 3160

80 383 112 3480

81 412 113 3740

82 453 114 4120

83 487 115 4530

84 523 116 4990

85 562 117 5490

86 604 118 6040

87 649 119 6810

88 698 120 7870

89 750 121 9090

90 787 122 10700

91 845 123 12700

92 909 124 15800

93 953 125 20500

94 1020 126 29400

95 1100 127 49900

96 1150 65 Open

SMSC EMC2103 23 Revision 0.85 (01-29-08)

DATASHEET

Page 24

5.2 Fan Control Modes of Operation

The EMC2103 has four modes of operation for the fa n driver. Each mode uses Ramp Rate control and

the Spin Up Routine

1. PWM Setting Mode - in this mode of operation, the user directly controls the PWM duty cycle

setting. Updating the Fan Driver Setting Register (see Section 6.20) will instantly update the fan

drive.

This is the default mode. The PWM Setti ng Mode is enabled by clearing both the EN_ALGO

bit in the Fan Configuration Register (see Section 6.22) and the LUT_LOCK bit in the Look

Up Table Config uration Register (see Section 6.32).

Whenever the PWM Setting Mode is enabled the current drive will be changed to what was

last written into the Fan Driver Setting Register.

2. Fan Speed Control Mode (FSC) - in this mode of operation, th e user determines a fan speed and

the drive setting is automatically updated to achieve this target speed.

This mode is enabled by clearing the L UT_LOCK bit in the Look Up Table (LUT)

Configuration Register and setting the EN_ALGO bit in the Fan Configuration Register.

3. Using the Look Up Table with Fan Drive Settings (PWM Setting w/ LUT Mode) - In this mode of

operation, the user programs the Look Up Table with PWM duty cycle settings and corresponding

temperature thresholds. The fan drive is set based on the measured temperatures and the

corresponding drive settings.

This mode is enabled by programming the L ook Up Table then setting the LUT_LOCK bit

while the RPM / PWM bit is set to a ‘1’ (see Section 6.32)

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

4. Using the Look Up Table with Fan Speed Control algorithm (FSC w/ LUT Mode)- In this mode of

operation, the user programs the Look Up Table with fan speed target values and corresponding

temperature thresholds. The TACH Target Register will be set based on the measured

temperatures and the corresponding target settings. The PWM drive settings will be determined

automatically based on the RPM based Fan Speed Control Algorithm

This mode is enabled by programming the L ook Up Table then setting the LUT_LOCK bit

while the RPM / PWM bit is set to ‘0’ (see Section 6.32).

Table 5.3 Fan Controls Active for Operating Mode

DIRECT PWM

SETTING MODE FSC MODE

Fan Driver Setting (read

/ write)

Fan Driver Setting (read

only)

EDGES[1:0] EDGES[1:0]

(Fan Configuration)

- RANGE[1:0]

(Fan Configuration)

UPDATE[2:0]

(Fan Configuration)

LEVEL

(Spin Up Configuration)

UPDATE[2:0]

(Fan Configuration)

LEVEL

(Spin Up Configuration)

DIRECT PWM SETTING W/

LUT MODE FSC W/ LUT MODE

Fan Driver Setting (read only) Fan Driver Setting (read

only)

EDGES[1:0] EDGES[1:0]

- RANGE[1:0]

(Fan Configuration)

UPDATE[2:0]

(Fan Configuration)

LEVEL

(Spin Up Configuration)

UPDATE[2:0]

(Fan Configuration)

LEVEL

(Spin Up Configuration)

SPINUP_TIME[1:0]

(Spin Up Configuration)

SPINUP_TIME[1:0]

(Spin Up Configuration)

SPINUP_TIME[1:0]

(Spin Up Configuration)

SPINUP_TIME[1:0]

(Spin Up Configuration)

Fan Step Fan St ep Fan Step Fan Step

- Fan Minimum Drive Fan Minimum Drive

Revision 0.85 (01-29-08) 24 SMSC EMC2103

DATASHEET

Page 25

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

Table 5.3 Fan Controls Active for Operating Mode (continued)

DIRECT PWM

SETTING MODE FSC MODE

Valid TACH Count Valid TACH Count Valid TACH Co unt Valid TACH Count

- TACH Target (read /

write)

TACH Reading TACH Reading TACH Reading TACH Reading

- - Look Up Table Drive /

- DRIVE_FAIL_CNT [1:0]

(Spin Up Configuration) +

Fan Drive Fail Band

DIRECT PWM SETTING W/

LUT MODE FSC W/ LUT MODE

- TACH Target (read only)

Tempe rature Settings (read

only)

- DRIVE_FAIL_CNT [1:0]

Look up Table Drive /

Temperature Settings

(read only)

(Spin Up Configuration)

+ Fan Drive Fail Band

5.3 PWM Fan Driver

The EMC2103 supports a high or low frequency PWM driver. The output can be configured as either

push-pull or open drain and the frequency ranges from 9.5Hz to 26kHz in four programmable

frequency bands.

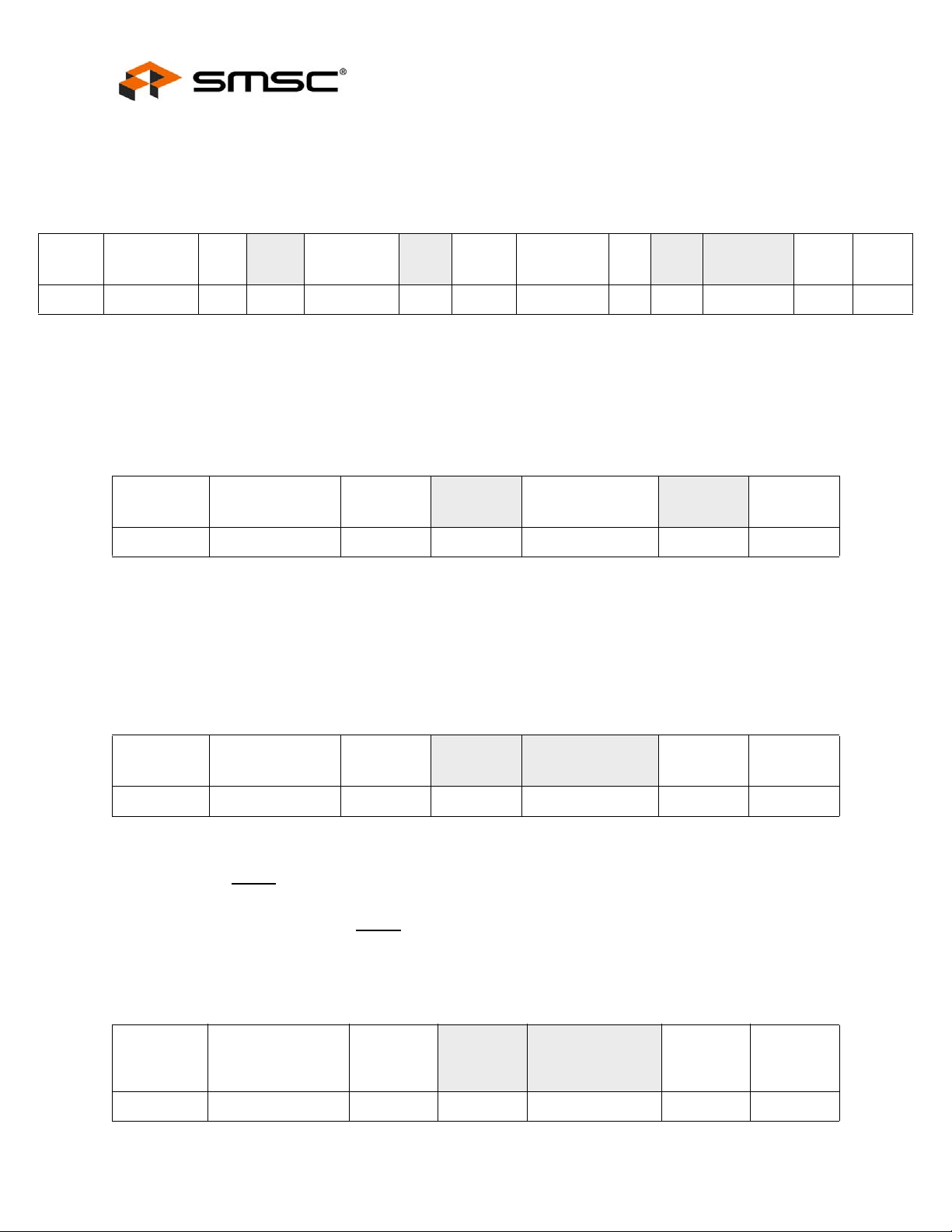

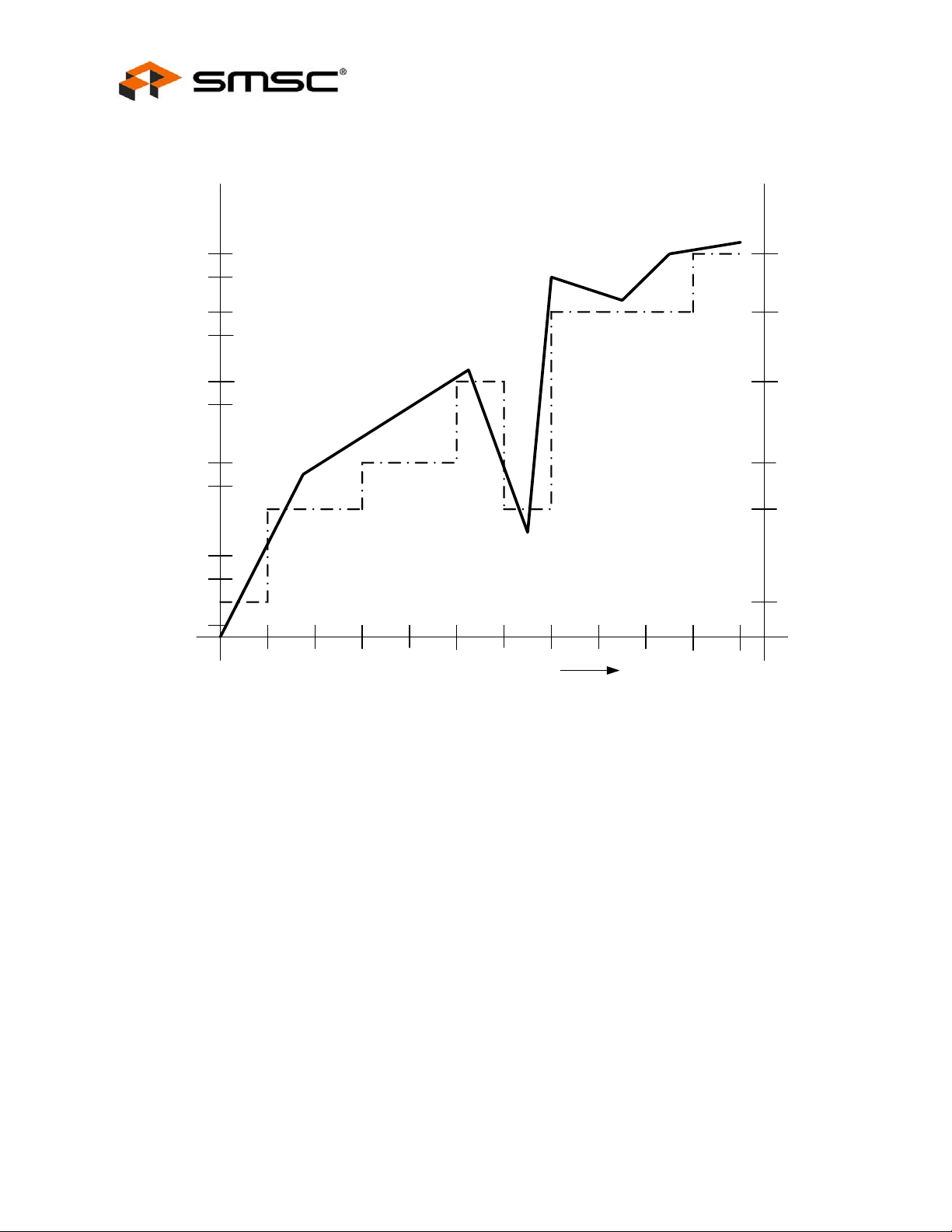

5.4 Fan Control Look-Up Table

The EMC2103 uses a look-up table to apply a user-programmable fan control profile based on

measured temperature to the fan driver. In this look-up table, each temperature channel is allowed to

control the fan drive output independently (or jointly) by programming up to eight pairs of temperature

and drive setting entries.

The user programs the look-up table based on the desired operation. If the RPM based Fan Speed

Control Algorithm is to be used (see Section5.5), then the user must program a fan spee d target for

each temperature setting of interest. Alternately, if the RPM based Fan Speed Control Algorithm is not

to be used, then the user must program a PWM setting for each temperature setting of interest.

If the measured temperature on the External Diode channel meets or exceeds any of the temperature

thresholds for any of the channels, the fan output will be automatically set to the desired setting

corresponding to the exceeded temperature. In cases where multiple te mperature channel thresholds

are exceeded, the highest fan drive setting will take precedence. Figure 5.3 shows an example of this

behavior using a single channel.

When the measured temperature drops to a point below a lower threshold minus the hysteresis value,

the fan output will be set to the corresponding lower set point.

SMSC EMC2103 25 Revision 0.85 (01-29-08)

DATASHEET

Page 26

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

Fan

Temp

Setting

T6

T6 - Hyst

T5

T5 - Hyst

T4

T4 - Hyst

T3

T3 - Hyst

T2

T2 - Hyst

T1

Averaged

Temperature

Fan

Setting

Measurement taken

Time

Figure 5.3 Fan Control Look-Up Table Example

S6

S5

S4

S3

S2

S1

5.4.1 P rogramming the Look Up Table

When the Look Up Table is used, it must be loaded and configured correctly based on the system

requirements. The following steps outline the procedure.

1. Determine whether the Look Up Table will drive a PWM duty cycle or a tachometer target value

and set the RPM / PWM bit in the Fan LUT Configuration Register (see Section 6.32).

2. Determine which mea surement channels (up to four) are to be used with the Look Up Table a nd

set the TEMP3_CFG and TEMP4_CFG bits accordingly in the Fan LUT Co nfiguration Register.

3. Fo r each step to be used in the LUT, set the Fan Setting (either PWM or TACH Target as set by

the RPM / PWM bit). If a setting is not used, then set it to FFh (if a PWM) or 00h (if a TACH Target).

Load the lowest settings first in ascending order (i.e. Fan Se tting 1 is the lowest setting greater

than “off”. Fan Setting 2 is the next highest setting, etc.). See Section 6.33.

4. For each step to be used in the LUT, set each of the measurement channel thresholds. These

values must be set in the same data format that the data is presented. If DTS is to be used, then

the format should be in temperature with a maximum threshol d of 100°C (64h). If a measurement

channel is not used, then set the threshold at FFh.

5. Update the thresh old hysteresis to be smaller than the smallest table step.

6. Con figure the RPM based Fan Speed Control Algorithm if it is to be used. See Section 5.5.1 for

more details.

Revision 0.85 (01-29-08) 26 SMSC EMC2103

DATASHEET

Page 27

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

7. Set the LUT_LOCK bit to enable the Look Up Table and begin fan control in the Fan LUT

Configuration Register.

5.4.2 D TS Support

The EMC2103 supports DTS (Intel’s Digital Temperature Sensor) data in the Fan Control Look Up

Tabl e. Intel’s DTS data is a positive number that represents the processor’s relative temperature below

a fixed value called T

CONTROL

example, a DTS value of 10°C means that the actual processor temperature is 10°C below T

or equal to 90°C.

Either or both of the Pushed Temperature Registers can be written with DTS data and used to control

the fan driver. When DTS data is entered, then the USE_DTS_Fx bit must be set in the Fan LUT

Configuration register. Once this bit is set, the DTS data entered is automatically subtracted from a

value of 100°C. This delta value is then used in the Look Up Table as standard temperature data.

which is generally equal to 100°C for Intel Mobile processors. For

CONTROL

APPLICATION NOTE: The device is designed with the assumption that T

CONTROL

is 100°C. As such, all DTS

related conversions are done based on this value including Look Up Table comparisons. If

T

CONTROL

is adjusted (i.e. T

CONTROL

thresholds should be adjusted by a value equal to T

is shifted to 105°C), then all of the Look Up Table

CONTROL

- 100°C.

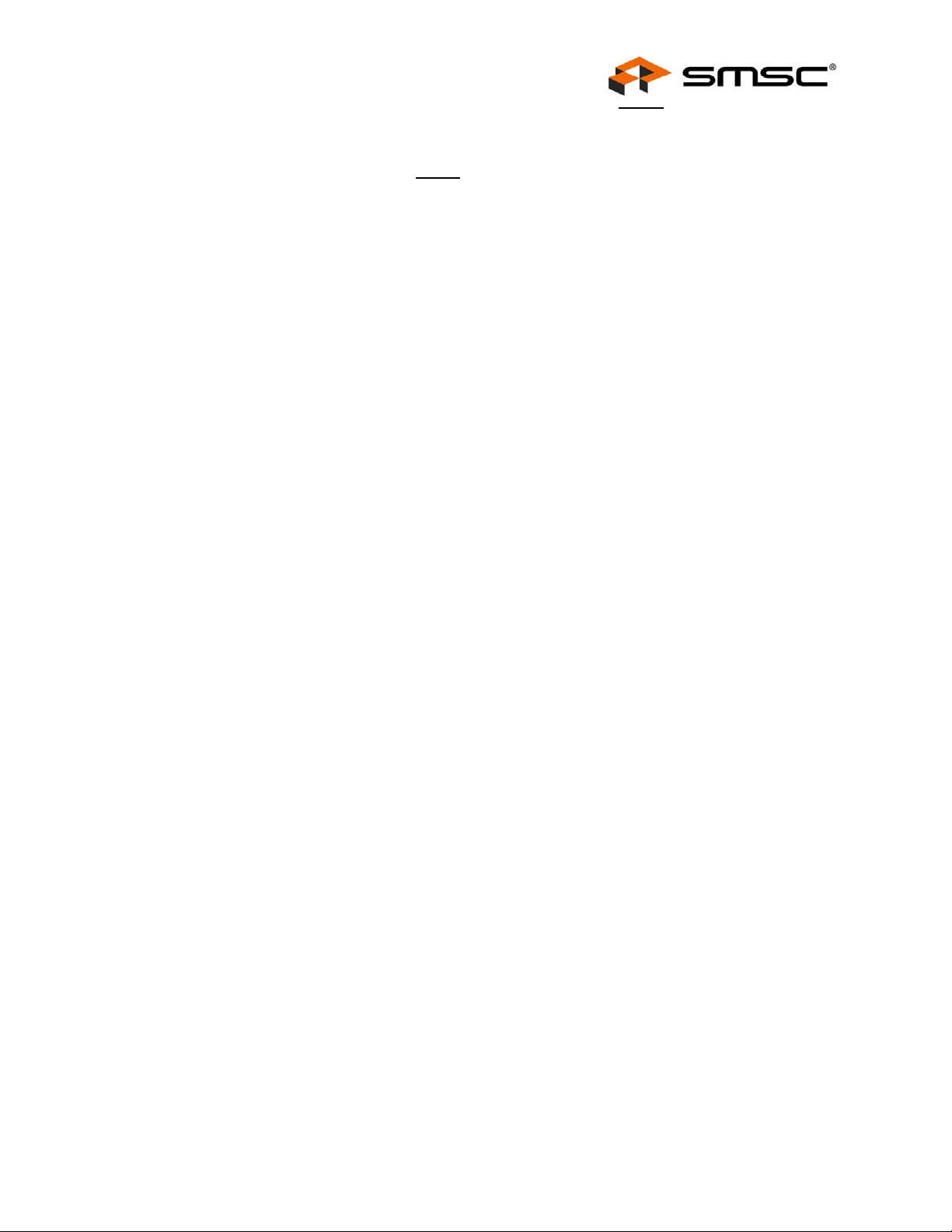

5.5 RPM based Fan Speed Control Algorithm (FSC)

The EMC2103 includes an RPM based Fan Speed Control Algorithm.

This fan control algorithm uses Proportional, In tegral, and Derivative terms to automatically approach

and maintain the system’s desired fan speed to an accuracy directly proportional to the accuracy of

the clock source. Figure 5.4 shows a simple flow diagram of the RPM based Fan Speed Control

Algorithm operation.

The desired tachometer count is set by the user inputting the desired number of 32.768KHz cycles

that occur per fan revolution. This is done by either manually setting the TACH Target Register or by

programming the Temperature Look-Up Table. The user may change the target count at any time. The

user may also set the target count to FFh in order to disable the fan driver for lower cu rrent operation.

For example, if a desired RPM rate for a 2-pole fan is 3000 RPM then the user would input the

hexidecimal equivalent of 1296 (51h in the TACH Target Register). This number represents the number

of 32.768KHz cycles that would occur during the time it takes the fan to complete a single revolution

when it is spinning at 3000RPMs. See Section 6.30 for RPM -> TACH calculations or Appendix B for

a complied table showing this information (for default conditions).

The EMC2103’s RPM based Fan Speed Control Algorithm has programmable configuration settings

for parameters such as ramp-rate control and spin up conditions. The fan driver automatically detects

and attempts to alleviate a stalled/stuck fan condition while also asserting the ALERT

EMC2103 works with fans that operate up to 16,000 RPMs and provi des a valid tachometer signal.

pin. The

SMSC EMC2103 27 Revision 0.85 (01-29-08)

DATASHEET

Page 28

Set TACH Target

Count

Measure Fan Speed

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

Ma in tain F an Driv e

Spin Up

Required

?

No

Yes

Yes

Reduce Fan Drive In c re a se F a n D riv e

TACH

Reading =

TACH

Target?

TACH

Reading <

TACH

Target?

Yes

No

No

Perform Spin Up

Routine

Ra mp Ra te Co ntr ol

Figure 5.4 RPM based Fan Speed Control Algorithm

5.5.1 P rogramming the RPM Based Fan Speed Control Algorithm

The RPM based Fan Speed Control Algorithm powers-up disabled. The following registers control the

algorithm. The EMC2103 fan control registers are pre-loaded with defaults that will work for a wide

variety of fans so only the TACH Target Register is required to set a fan speed. The other fan control

registers can be used to fine-tune the algorithm behavior based on application requirements.

Note that steps 1 - 7 are optional and need only be performed if the default settings do not provide

the desired fan response.

1. Set the Valid TACH Count Register to maximum number of tach counts to indicate the fan is

spinning.

2. Set th e Spin Up Configuration Register to the Spin Up Level and Spin Time desired.

Revision 0.85 (01-29-08) 28 SMSC EMC2103

DATASHEET

Page 29

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

3. Set the F an Step Register to the desired step size.

4. Set the F an Minimum Drive Register to the minimum drive value that will maintain fan operation.

5. Set th e Update Time, and Edges options in the Fan Configuration Register.

6. Set th e valid TACH count setting at the highest count that indicates that the fan is spinning.

7. Set the TACH Targe t Register to the desired tachometer count.

8. Enable the RPM based Fan Speed Control Algorithm by setting the EN_ALGO bit.

5.6 Tachometer Measurement

The tachometer measurement circuitry is used in conjunction with the RPM based Fan Speed Control

Algorithm to update the fan driver output. Additionally, it can be used in Direct Setting mode as a

diagnostic for host based fan control.

This method monitors the TACH signal in real time. It constantly updates the tachometer measurement

by reporting the number of clocks between a user progra mmed number of edges on the TACH signal

(see Table 8.5)

Using the Tach Period Measurement method provides fast response times for the RPM based Fan

Speed Control Algorithm and the data is presented as a count value that represents the fan RPM

period. When this method is used, all fan target values must be input as a count value for proper

operation.

APPLICATION NOTE: The Tach Period Measurement method works independently of the drive settings. If the

device is put into Direct Setting and the fan drive is set at a level that i s lower than the fan

can operate (including zero drive), then the tachometer measurement may signal a Stalled

Fan condition and assert an interrupt.

5.6.1 Stalled Fan

A Stalled fan is detected differently based on which tach method is enabled. If the Tach Period

Measurement measurement method is implemented, and if the tach counter exceeds the userprogrammable Valid TACH Count setting then it will flag the fan as stalled and trigger an interrupt.

If the RPM based Fan Speed Control Algorithm is enabled, the algorithm will automatically attempt to

restart the fan until it detects a valid tachometer level or is disabled.

The FAN_STALL Status bit indicates that a stalled fan was detected. This bit is checked conditionally

depending on the mode of operation.

When the Direct Setting Mode or Direct Setting with LUT Mode are enabled or the Spin Up Routine

is initiated, the FAN_STALL interrupt will be masked for the duration of the programmed Spin Up

Time (see Table 8.16). This is to allow the fan opportunity to reach a valid speed without generating

unnecessary interrupts.

When the Direct Setting Mode or Direct Setting w/ LUT Mode are activa ted then whenever the

TACH Reading Register value exceeds the Va lid TACH Count Register setting, the FAN_STALL

status bit will be set.

When using the RPM based Fan Speed Control Algorithm (either FSC Mode or LUT with FSC

Mode), the stalled fan condition is checked whenever the Update Time is met and the fan drive

setting is updated. It is not a continuous check.

5.6.2 A ging Fan or Invalid Drive Detection

The EMC2103 contains circuitry that detects that the programmed fan speed can be reached b y the

fan. If the target fan speed cannot be reached within a user defined band o f tach counts at maximum

drive then the DRIVE_FAIL status bit is and the ALERT

fan conditions (where the fan’s natural maximum speed degrades over time) or incorrect fan speed

settings.

SMSC EMC2103 29 Revision 0.85 (01-29-08)

pin is asserted. This is useful to detect aging

DATASHEET

Page 30

5.7 Spin Up Routine

The EMC2103 also contains programmable circuitry to control the spin up behavior of the fan driver

to ensure proper fan operation. The Spin Up Routine is initiated under the following conditions when

the Tach Period Measurement method of tach measurement is used. This applies to either the RPM

based Fan Speed Control Algorithm mode or the Direct Setting mode (with or without the Look Up

Table).

1. The TACH Target Register value changes from a value of FFh to a value that is less than the Valid

TACH Count (see Section 8.10 and Section 8.12).

2. Th e RPM based Fan Speed Control Algorithm’s measured TACH Reading Register value is greater

than the Valid TACH Count setting.

When the Spin Up Routine is operating, the fan driver is set to full scale (optional) for one quarter of

the total user defined spin up time. For the remaining spin up time, the fa n driver output is set a a user

defined level (30% through 65% drive).

After the Spin Up Routine has finished, the EMC2103 measures the TACH signal. If the measured

TACH Reading Register value is higher than the Valid TACH Count Register setting, the FAN_SPIN

status bit is set and the Spin Up Routine will automatically attempt to restart the fan.

Figure 5.5 shows an example of the Spin Up Routine in response to a programmed fan speed change

based on the first condition above.

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

Prev Target

Count = FFh

Target Count

Changed

100%

(optional)

30% through 65%

¼ of Spin U p T im e

Spin Up Time

New Target Count

Update Time

Check TACH

Figure 5.5 Spin Up Routine

Fan Step

Algorithm controlled drive

Target Count

Reached

Revision 0.85 (01-29-08) 30 SMSC EMC2103

DATASHEET

Page 31

RPM-Based Fan Controller with HW Thermal Shutdown

Datasheet

5.8 Ramp Rate Control

The PWM output drive can be configured with automatic ramp rate control. If the RPM based Fan

Speed Control Algorithm is used, then this ramp rate control is automatically used based on the fan

control derivative option settings. See Section 6.23, "Fan Configuration 2 Register". The user programs

a maximum step size for the PWM setting and an update time. The update time varies from 100ms to

1.6s while the PWM maximum step can vary from 1 PWM count to 31 PWM counts.

When a new PWM is entered, the delta from the next PWM and the previous PWM is determined. If

this delta is greater than the Max Step settings, then the PWM is incrementally adjusted every 100ms