Page 1

1

* This specification are subject to be changed without notice.

EM92600/1C

DUAL PLL FOR 45/48 MHZ CORDLESS PHONE

4.23.1995

EM92600/1C

DUAL PLL FOR 45/48 MHZ CORDLESS PHONE

GENERAL DESCRIPTION

The EM92600/1C series are developed for 45/48 MHz of 10 channels band frequency of cordless telephone

which is used in Mainland China. These devices are dual phase-locked loop frequency synthesizers contained

ROM counters for receive and transmit loops with two independent phase detect circuits. A common reference

oscillator and reference divider are share by the receive and transmit circuits.

Other features include a lock detect circuit for the transmit loop, illegal code default, a buffered oscillator output

for mixing purposes in the system, 5KHz tone output . The EM92601C is designed for easy MPU interface. It

provides the same features as the EM92600C , but accepts channel programming via a clocked, serial input

instead of parallel BCD inputs. The EM92600C is selected channels via machanical switches of parallel BCD

input.

FEATURES

• Include oscillation circuit with external X-TAL (10.240 MHz).

• Unlock detector.

• 5KHz output for guard tone.

• Standby mode for power saving.

• 2.5 to 5.5V supply range.

• Baseset/Handset changeable.

• Available in 16 pin DIP or SOP.

• SERIES

Part Number Package Channel Selection

EM92600CP DIP parallel

EM92600CM SOP parallel

EM92601CP DIP serial

EM92601CM SOP serial

PIN ASSIGNMENTS

EM92600C EM92601C

XTALO

MODE

SB

5K

D0

D1

D2

D3

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

XTALI

VDD

RIF

PDR

V

SS

PDT

LD

TIF

XTALO

MODE

SB

5K

DI

CLK

NC

EN

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

XTALI

VDD

RIF

PDR

V

SS

PDT

LD

TIF

Page 2

* This specification are subject to be changed without notice.

EM92600/1C

DUAL PLL FOR 45/48 MHZ CORDLESS PHONE

2

4.23.1995

PIN DESCRIPTIONS

Symbol Pin No. Function

XTALO O This ouput generates reference frequency when it is connected to pin 16 with

external OSC of which frequency is 10.240MHz

MODE I Base/remote changing. Internal pull down.

V

DD

=base,VSS=remote.

SB I The standby pin is uses to save power when no transmit. Internal pull down.

High: transmit and receive active

Low: receive acts only

5K O The signal derived from the reference oscillator. 5KHz output.

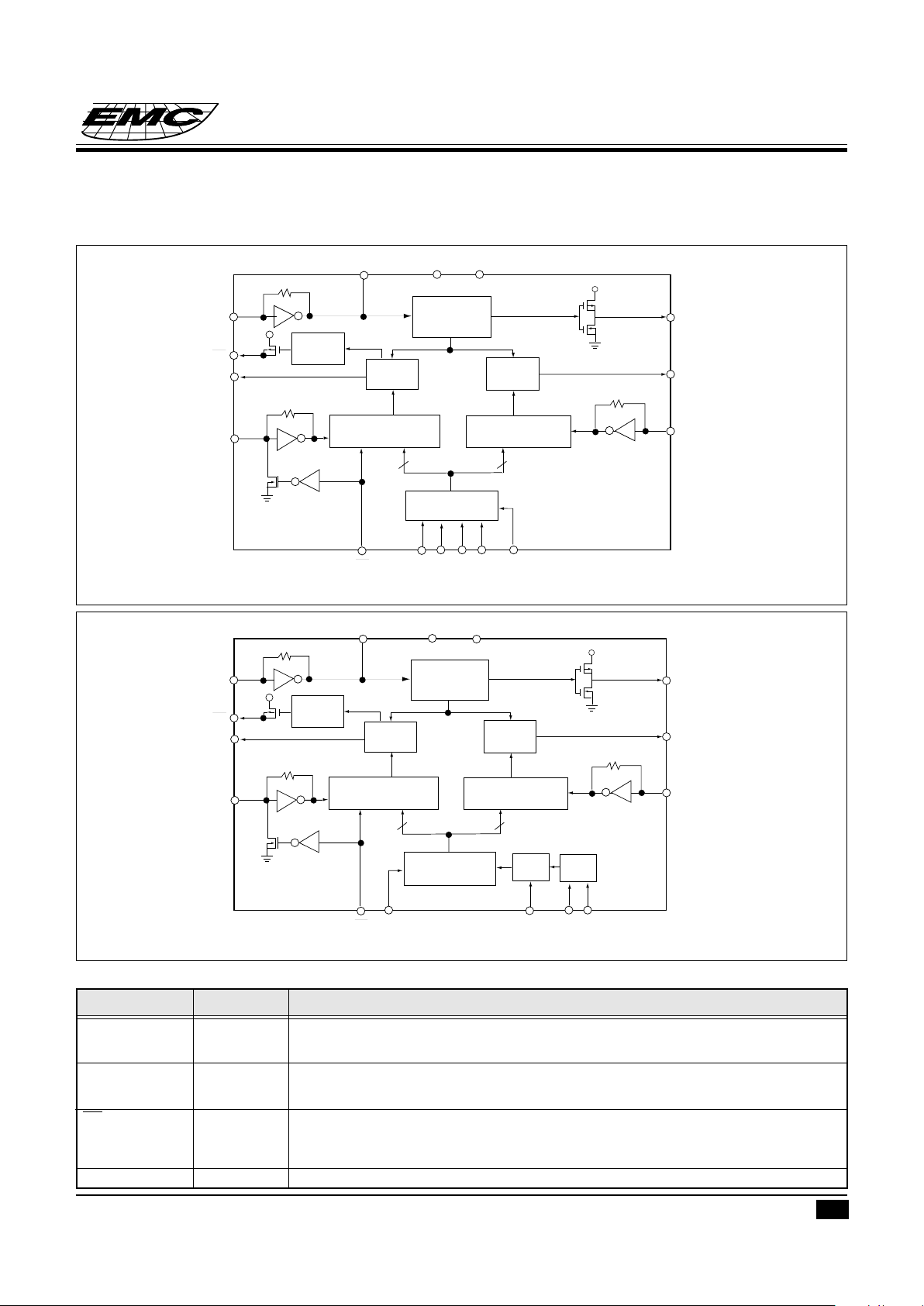

FUNCTIONAL BLOCK DIAGRAM

EM92600C block diagram

EM92601C block diagram

XTAL0

V

DD

V

SS

5K

PDR

RIF

V

DD

Reference

counter

divide by 2048

Lock

detector

phase

detector

Phase

detector

14 bits divide by N

receive counter

b27-b14

MODE

D3

SB

ROM 32*28

& decoder logic

14 bits divide by N

Transmit counter

V

DD

XTAL1

LD

PDT

TIF

b13-b0

D2D1D0

XTAL0

V

DD

V

SS

5K

PDR

RIF

V

DD

Reference

counter

divide by 2048

Lock

detector

phase

detector

Phase

detector

14 bits divide by N

receive counter

b27-b14

MODE

DICLKEN

SB

ROM 32*28

& decoder logic

14 bits divide by N

Transmit counter

V

DD

XTAL1

LD

PDT

TIF

b13-b0

4 bits

latch

4 bits

S/R

Page 3

3

* This specification are subject to be changed without notice.

EM92600/1C

DUAL PLL FOR 45/48 MHZ CORDLESS PHONE

4.23.1995

ABSOLUTE MAXIMUM RATINGS

Symbol Rating Value Unit

V

DD

DC supply voltage -0.5 to +6 V

V

IN

Input voltage -0.5 to VDD+0.5 V

I

IN,IOUT

DC current drain per pin 10.0 mA

I

DD,ISS

DC current drain VDD or VSS pins 30.0 mA

T

A

Operating temperature range -30 to +75 °C

T

STG

Storage temperature range -65 to +150 °C

Symbol I/O Function

D0 I The channel selected pin. LSB.(intenal pull down)

D1 I The channel selected pin. (internal pull down)

D2 I The channel selected pin. (internal pull down)

D3 I The channel selected pin. MSB.(internal pull down)

Di I The serial input data pin.

CLK I Clock input. Each low to high transition of the clock shifts one bit of data into

the on-chip shift register.

NC - Not connect.

EN I The enable pin controls the data transfer from the shift register to the 4-bit latch.

A low to high transition latches the data.

TIF I Input to programmable divider of Tx. AC coupling with VCO. Min input voltage

is 200mVp-p.

LD O Unlock detector output. V

DD

level: unlock.

PDT O Phase detector output for Tx. PDT detects the phase error from Tx PLL and its

output is connected to external low pass filter.

V

SS

- Ground.

PDR O Phase detector output for Rx. PDR detects the phase error from Rx PLL and its

output is connected to external low pass filter.

RIF I Input of programmable divider for Rx.AC coupling with VCO. Min input voltage

is 200mVp-p.

V

DD

- Power supply.

XTAL1 I To connect crystal ( 10.240MHz ) and capacitor.

Page 4

* This specification are subject to be changed without notice.

EM92600/1C

DUAL PLL FOR 45/48 MHZ CORDLESS PHONE

4

4.23.1995

DC ELECTRICAL CHARACTERISTICS

(T

A=

25°C unless otherwise noted )

Parameter Sym. Min. Typ. Max. Unit Condition

Operating voltage V

DD

2.5 - 5.5 V

Input voltage V

IL

- 0.8 V VDD=3V

V

IH

2.2 -

Output voltage V

OL

- 0.05 V VDD=3V

V

OH

2.95 -

Input low current I

IL

µAvIL=0

-36 - pin 16,14,9

-0.06 - pin 2~8

Input high current I

IH

µAvIH=VDD-0.5V

- 36 pin 16,14,9

- 120 pin 2~8

Output current I

OH

-0.2 - mA VOH=2.6V

I

OL

0.2 - VOL=0.4V

Standby current I

DS

- 1.5 mA VDD=3V, note1

Operating current I

DO

- 3.0 mA VDD=3V, note2

(0.2Vp-p input at RIF,TIF)

3-state leakage current I

OZ

- ±1 µAVDD=5V

Note 1: XTALin: 10.24MHz ; MODE:VDD; SB:VSS; TIF=20MHz(200 mVp-p); RIF=40MHz(200 mVp-p); others

are open.

Note 2: XTALin: 10.24MHz ; MODE:V

DD

; SB:VDD; TIF=20MHz(200 mVp-p); RIF=40MHz(200 mVp-p); others are

open.

Parameter Sym. Min. Typ. Max. Unit Condition

Output rise time T

R

200 nS VDD=3V

Output fall time T

F

200 nS VDD=3V

Input rise and fall time T

R

5 µS XTAL1

T

F

VDD=3V

Maximum frequency F

MAX

12 XTAL1

input =sine wave 0.2Vp-p 50 MHz RIF (V

DD

=3V)

OSC in 50 TIF

Setup time data to clock T

SU

EM92601C only

Enable to clock 100

200 nS

Hold time T

H

80 nS EM92601C only

clock to data

Recovery time T

REC

80 nS EM92601C only

Enable to clock

Input pulse width T

W

80 nS EM92601C only

clock and Enable

AC ELECTRICAL CHARACTERISTICS

Page 5

5

* This specification are subject to be changed without notice.

EM92600/1C

DUAL PLL FOR 45/48 MHZ CORDLESS PHONE

4.23.1995

TIMING DIAGRAM

EM92601C Timing

1.6µS

6.4±0.4mS

PDT

LD

Unlock Timing

1 st

CLK

trec

tw

Previous

Data Latched

4 th

CLK

tsu

3 rd

CLK

2 nd

CLK

1 st

CLK

tw

tsu

th

D2 D1

D0D3

Data

Clock

Enable

APPLICATION CIRCUIT

0.455MHz

2ND IF

1ST IF

2ND

MIX

1ST

MIX

BPF

BPF

TX

VCO

LPFLPF

RX

VCO

123

4

56

7

8

16 15 14

13 12 11

10

9

XTAL0

MODESB5K

DO/DI

D1/CLK

D2/NC

D3/EN

XTAL1

VDD

RIF

PDR

VSS

PDT

LD

TIF

10.24

MHz

10.240

MHz

Page 6

* This specification are subject to be changed without notice.

EM92600/1C

DUAL PLL FOR 45/48 MHZ CORDLESS PHONE

6

4.23.1995

DIVIDE RATIO AND VCO FREQUENCIES

Base Input Rx (Fref=5KHz) Tx=(Fref=5KHz)

(MODE=1) CH

D3 D2 D1 D0 FRx (MHz) FVCO(MHz) N FTx(MHz) FVCO(MHz) N

0 0 0 1 1 48.250 37.555 7511 45.250 45.250 9050

0 0 1 0 2 48.275 37.580 7516 45.275 45.275 9055

0 0 1 1 3 48.300 37.605 7521 45.300 45.300 9060

0 1 0 0 4 48.325 37.630 7526 45.325 45.325 9065

0 1 0 1 5 48.350 37.655 7531 45.350 45.350 9070

0 1 1 0 6 48.375 37.680 7536 45.375 45.375 9075

0 1 1 1 7 48.400 37.705 7541 45.400 45.400 9080

1 0 0 0 8 48.425 37.730 7546 45.425 45.425 9085

1 0 0 1 9 48.450 37.755 7551 45.450 45.450 9090

1 0 1 0 10 48.475 37.780 7556 45.475 45.475 9095

1 0 1 1 48.475 37.780 7556 45.475 45.475 9095

1 1 0 0 48.475 37.780 7556 45.475 45.475 9095

1 1 0 1 48.475 37.780 7556 45.475 45.475 9095

1 1 1 0 48.475 37.780 7556 45.475 45.475 9095

1 1 1 1 48.475 37.780 7556 45.475 45.475 9095

0 0 0 0 48.475 37.780 7556 45.475 45.475 9095

REMOTE Input Rx (Fref=5KHz) Tx=(Fref=5KHz)

(MODE=0) CH

D3 D2 D1 D0 FRx (MHz) FVCO(MHz) N FTx(MHz) FVCO(MHz) N

0 0 0 1 1 45.250 34.555 6911 48.250 48.250 9650

0 0 1 0 2 45.275 34.580 6916 48.275 48.275 9655

0 0 1 1 3 45.300 34.605 6921 48.300 48.300 9660

0 1 0 0 4 45.325 34.630 6926 48.325 48.325 9665

0 1 0 1 5 45.350 34.655 6931 48.350 48.350 9670

0 1 1 0 6 45.375 34.680 6936 48.375 48.375 9675

0 1 1 1 7 45.400 34.706 6941 48.400 48.400 9680

1 0 0 0 8 45.425 34.730 6946 48.425 48.425 9685

1 0 0 1 9 45.450 34.755 6951 48.450 48.450 9690

1 0 1 0 10 45.475 34.780 6956 48.475 48.475 9695

1 0 1 1 45.475 34.780 6956 48.475 48.475 9695

1 1 0 0 45.475 34.780 6956 48.475 48.475 9695

1 1 0 1 45.475 34.780 6956 48.475 48.475 9695

1 1 1 0 45.475 34.780 6956 48.475 48.475 9695

1 1 1 1 45.475 34.780 6956 48.475 48.475 9695

0 0 0 0 45.475 34.780 6956 48.475 48.475 9695

Loading...

Loading...