Datasheet EM6A9320BI-5, EM6A9320BI-4, EM6A9320BI-3.5, EM6A9320BI-3.3, EM6A9320BI-3.0 Datasheet (ETRON)

...Page 1

Etr onT ech

EM6A9320

4M x 32 DDR SDRAM

Etron Confidential Preliminary (Rev 0.3 7/2002)

Features

Fast clock rate: 350/333/300/285/250/200 MHz

•

Differential Clock CK & CK# input

•

4 Bi-directional DQS. Data transactions on both

•

edges of DQS (1DQS / Byte)

DLL aligns DQ and DQS transitions

•

Edge aligned data & DQS output

•

Center aligned data & DQS input

•

4 internal banks, 1M x 32-bit for each bank

•

Programmable mode and extended mode registers

•

- CAS# Latency: 3, 4, 5

- Burst length: 2, 4, 8

- Burst Type: Sequential & Interleave

Full page burst length for sequential type only

•

Start address of full page burst should be even

•

All inputs except DQ’s & DM are at the positive

•

edge of the system clock

No Write-Interrupted by Read function

•

4 individual DM control for write masking only

•

Auto Refresh and Self Refresh

•

4096 refresh cycles / 32ms

•

Power supplies up to 350/333/300/285MHz:

•

V

V

Power supplies up to 250/200MHz:

•

V

V

Interface : SSTL_2 I/O compatible

•

6WDQGDUG EDOO )%*$ SDFNDJH

•

= 2.8V ± 5%

DD

= 2.8V ± 5%

DDQ

= 2.5V ± 5%

DD

= 2.5V ± 5%

DDQ

Overview

The EM6A9320 DDR SDRAM is a high-speed CMOS

double data rate synchronous DRAM containing 128

Mbits. It is internally configured as a quad 1M x 32

DRAM with a synchronous interface (all signals are

registered on the positive edge of the clock signal, CK).

Data outputs occur at both rising edges of CK and CK#.

Read and write accesses to the SDRAM are burst

oriented; accesses start at a selected location and

continue for a programmed number of locations in a

programmed sequence.

Accesses begin with the registration of a BankActivate

command, which is then followed by a Read or Write

command.

The EM6A9320 provides programm able Read or Write

burst lengths of 2, 4, 8. An auto precharge function m ay

be enabled to provide a self-timed row prechar ge that is

initiated at the end of the burst sequence.

The refresh functions, either Auto or Self Refresh are

easy to use.

In addition, EM6A9320 features programmable DLL

option. By having a programmable mode register and

extended mode register, the system can choose the

most suitable modes to maximize its performance.

These devices are well suited f or applications requiring

high memory bandwidth, result in a device particularly

well suited to high performance main memory and

graphics applications.

Ordering Information

Part Number

EM6A9320BI-2.8 350MHz FBGA

EM6A9320BI-3.0 333MHz FBGA

EM6A9320BI-3.3 300MHz FBGA

EM6A9320BI-3.5 285MHz

EM6A9320BI-4 250MHz FBGA

EM6A9320BI-5 200MHz

Frequency Power Supply Package

V

2.8V

DD

2.8V

V

DDQ

2.5V

V

DD

V

2.5V

DDQ

FBGA

FBGA

Etron Technology, Inc.

No. 6, Technology Rd. V, Science-Based Industrial Park, Hsinchu, Taiwan 30077, R.O.C.

TEL: (886)-3-5782345 FAX: (886)-3-5778671

Etron Technology, Inc., reserves the right to make changes to its products and specifications without notice.

Page 2

Etr onT ech

A

4Mx32 DDR SDRAM

EM6A9320

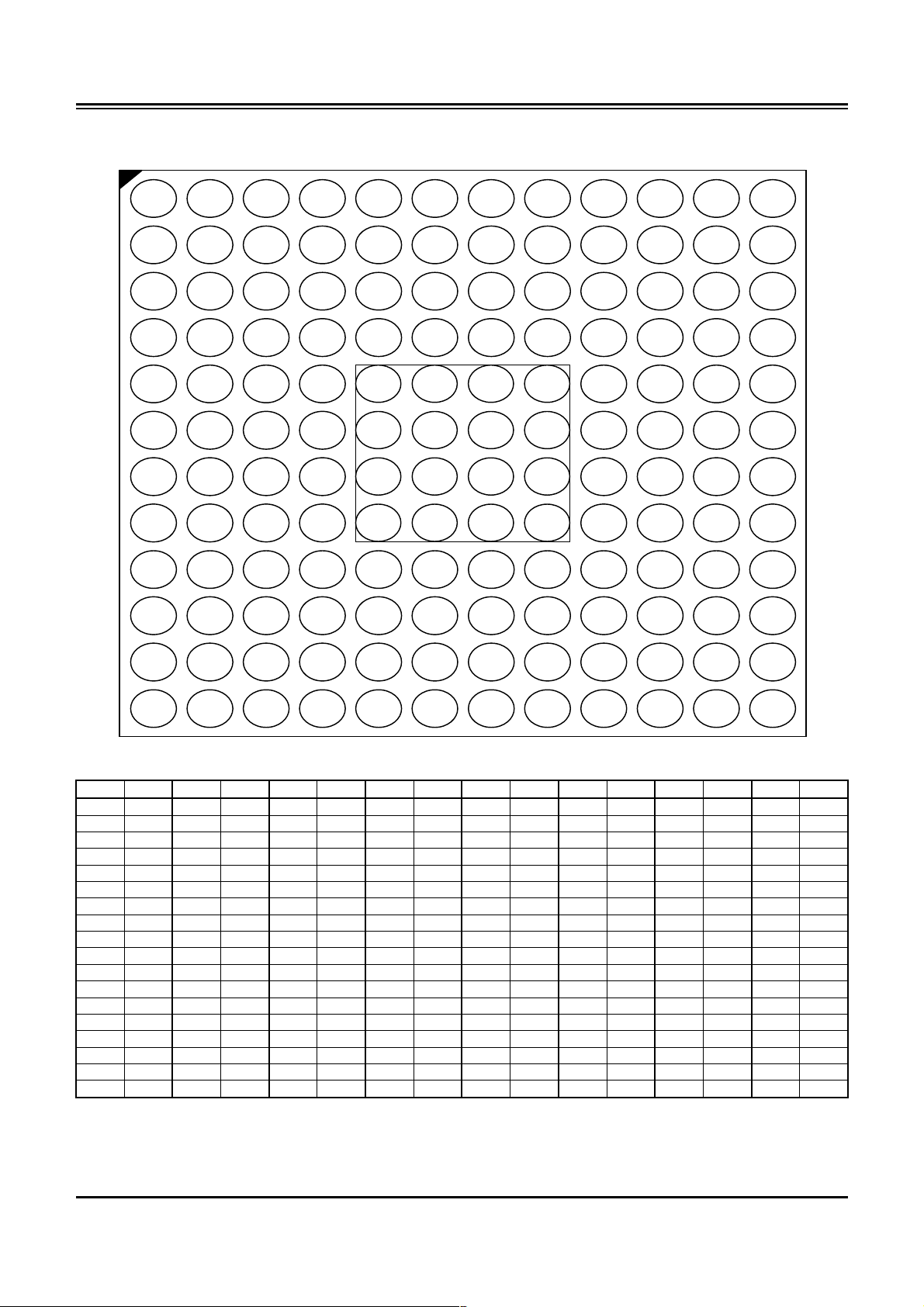

Pin Assignment (FBGA 144Ball Top View)

DQS0

A

B

DQ4

DM0

VDDQ

VSSQ

NC

DQ3

VDDQ

DQ2 DQ0

DQ1

VDDQ

DQ31 DQ29

VDDQ DQ30

DQ28 VSSQ

VDDQ

NC

12 11 10 9 8 7 6 5 4 3 2 1

DM3

VDDQ DQ27

DQS3

C

DQ6 DQ5

VSSQ VSSQ

VSSQ

VDD

VDD

VSSQ

VSSQ VSSQ

DQ26 DQ25

D

DQ7

VDDQ

VDD VSS

VSSQ

VSS

VSS

VSSQ

VSS VDD

VDDQ DQ24

E

DQ17 DQ16

VDDQ VSSQ

VSS

Thermal

VSS

Thermal

VSS

Thermal

VSS

Thermal

VSSQ VDDQ

DQ15 DQ14

F

DQ19 DQ18

VDDQ VSSQ

G

DQS2

DM2

NC

VSSQ

VSS

Thermal

VSS

Thermal

VSS

Thermal

VSS

Thermal

VSS

Thermal

VSS

Thermal

VSS

Thermal

VSS

Thermal

VSSQ VDDQ

VSSQ

NC

DQ13 DQ12

DM1

DQS1

H

DQ21 DQ20

VDDQ VSSQ

VSS

Thermal

VSS

Thermal

VSS

Thermal

VSS

Thermal

VSSQ VDDQ

DQ11 DQ10

J

DQ22 DQ23

VDDQ VSSQ

VSS VSS

VSS VSS

VSSQ VDDQ

DQ9 DQ8

K

CAS#

WE#

VDD VSS

A10 VDD

VDD NC

VSS VDD

NC NC

L

RAS#

NC

NC BA1

A2 A11

A9 A5

NC CK

CK# NC

M

CS# NC

BA0 A0

A1 A3

A4 A6

A7

AP

8/

CKE

VREF

Pin Assignment by Name (FBGA 144Ball)

Symbol Location Symbol Location Symbol Location Symbol Location Symbol Location Symbol Location Symbol Location Symbol Location

A0 M4 DQ6 C1 DQ24 D12 CK L10 VDDQ B6 VSS E5 VSS J7 VSSQ G4

A1 M5 DQ7 D1 DQ25 C12 CK# L11 VDDQ B7 VSS E6 VSS J8 VSSQ G9

A2 L5 DQ8 J12 DQ26 C11 CKE M11 VDDQ B9 VSS E7 VSS K4 VSSQ H4

A3 M6 DQ9 J11 DQ27 B12 CS# M1 VDDQ B11 VSS E8 VSS K9 VSSQ H9

A4 M7 DQ10 H12 DQ28 A9 RAS# L1 VDDQ D2 VSS F5 VSSQ A3 VSSQ J4

A5 L8 DQ11 H11 DQ29 A8 CAS# K1 VDDQ D11 VSS F6 VSSQ A10 VSSQ J9

A6 M8 DQ12 F12 DQ30 B8 WE# K2 VDDQ E3 VSS F7 VSSQ C3 NC B3

A7 M9 DQ13 F11 DQ31 A7 VREF M12 VDDQ E10 VSS F8 VSSQ C4 NC B10

A8/AP M10 DQ14 E12 DQS0 A1 VDD C6 VDDQ F3 VSS G5 VSSQ C5 NC G3

A9 L7 DQ15 E11 DQS1 G12 VDD C7 VDDQ F10 VSS G6 VSSQ C8 NC G10

A10 K5 DQ16 E2 DQS2 G1 VDD D3 VDDQ H3 VSS G7 VSSQ C9 NC K8

A11 L6 DQ17 E1 DQS3 A12 VDD D10 VDDQ H10 VSS G8 VSSQ C10 NC K11

DQ0 A6 DQ18 F2 DM0 A2 VDD K3 VDDQ J3 VSS H5 VSSQ D5 NC K12

DQ1 B5 DQ19 F1 DM1 G11 VDD K6 VDDQ J10 VSS H6 VSSQ D8 NC L2

DQ2 A5 DQ20 H2 DM2 G2 VDD K7 VSS D4 VSS H7 VSSQ E4 NC L3

DQ3 A4 DQ21 H1 DM3 A11 VDD K10 VSS D6 VSS H8 VSSQ E9 NC L9

DQ4 B1 DQ22 J1 BA0 M3 VDDQ B2 VSS D7 VSS J5 VSSQ F4 NC L12

DQ5 C2 DQ23 J2 BA1 L4 VDDQ B4 VSS D9 VSS J6 VSSQ F9 NC M2

Etron Confidential

2 Rev 0.3 July. 2002

Page 3

Etr onT ech

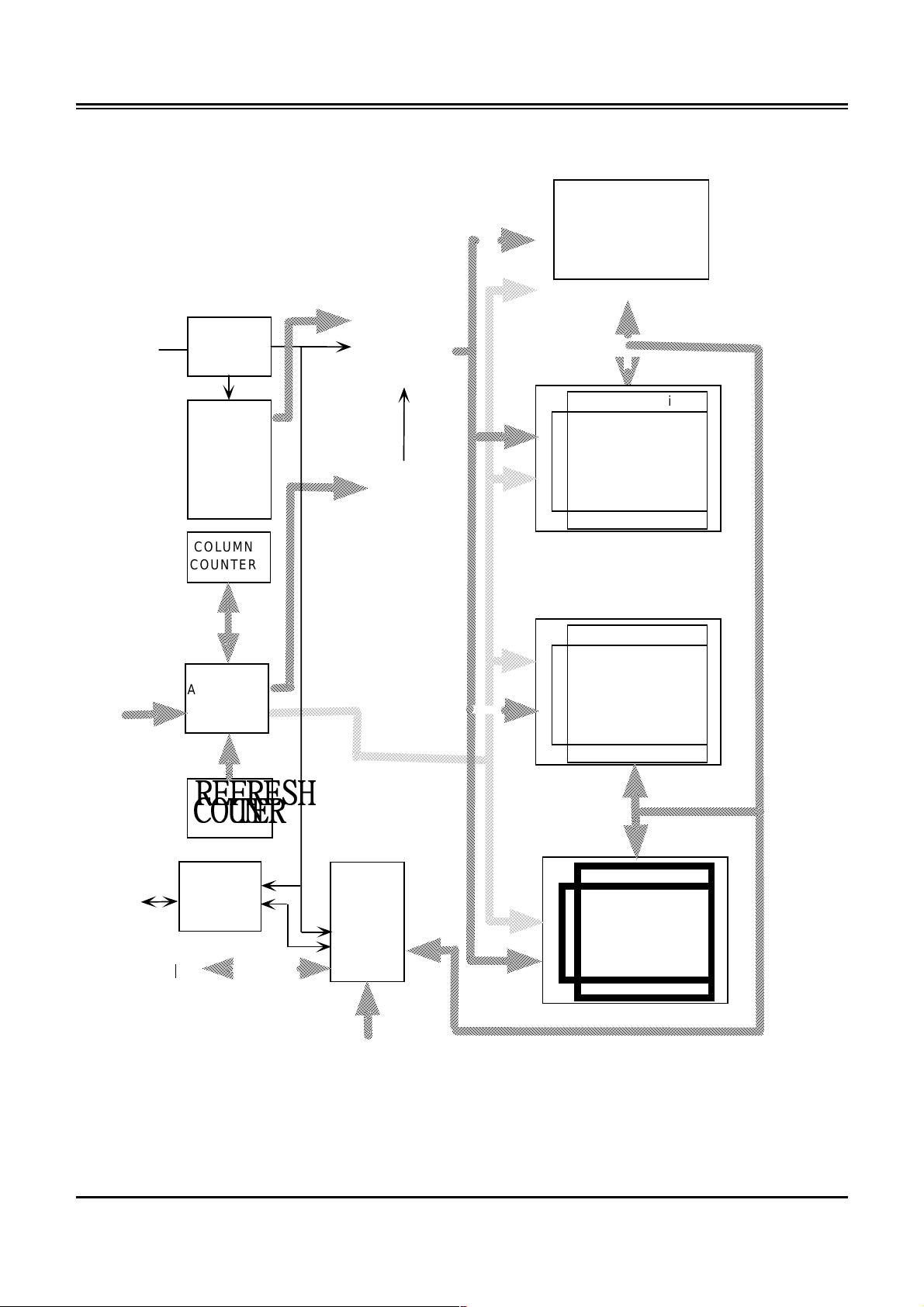

Block Diagram

4Mx32 DDR SDRAM

Column Decoder

4096 X 256 X 32

CELL ARRAY

Decoder

Row

Sense Amplifier

EM6A9320

(BANK #0)

CK

CK#

CKE

CS#

RAS#

CAS#

WE#

A8/AP

A0

A10

A11

BA0

BA1

DLL

CLOCK

BUFFER

COMMAND

DECODER

COLUMN

COUNTER

ADDRESS

BUFFER

SFGSFTI

DPVOUFS

CONTROL

SIGNAL

GENERATOR

MODE

REGISTER

Sense Amplifier

4096 X 256 X 32

CELL ARRAY

(BANK #1)

Row Decoder

Column Decoder

Column Decoder

4096 X 256 X 32

CELL ARRAY

(BANK #2)

Row Decoder

Sense Amplifier

DATA

DQ0

h

DQ31

STROBE

BUFFER

DQS0~3

Etron Confidential

Sense Amplifier

DQ

BUFFER

DM0~3

3 Rev 0.3 July. 2002

4096 X 256 X 32

CELL ARRAY

Decoder

(BANK #3)

Row

Column Decoder

Page 4

Etr onT ech

4Mx32 DDR SDRAM

EM6A9320

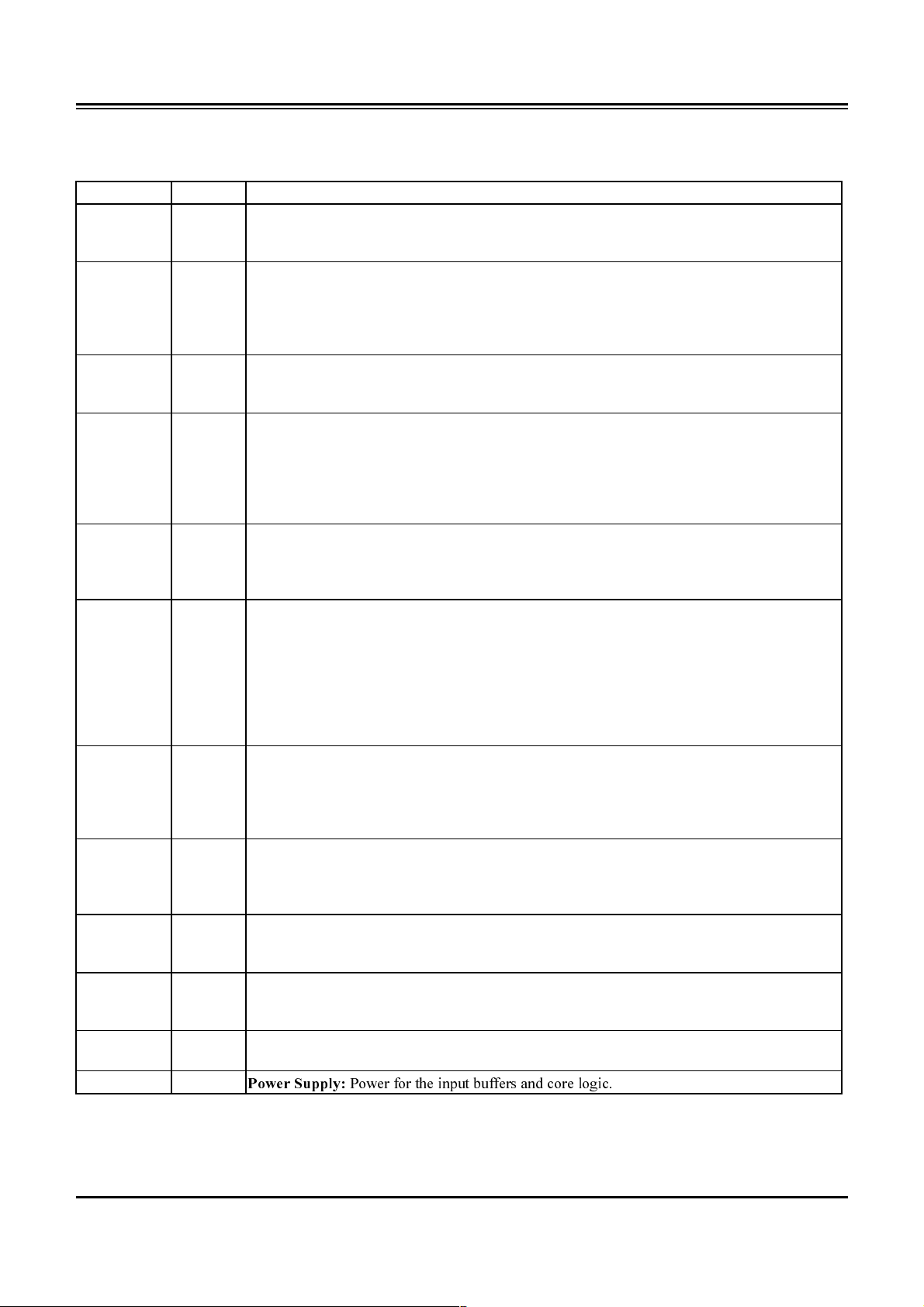

Pin Descriptions

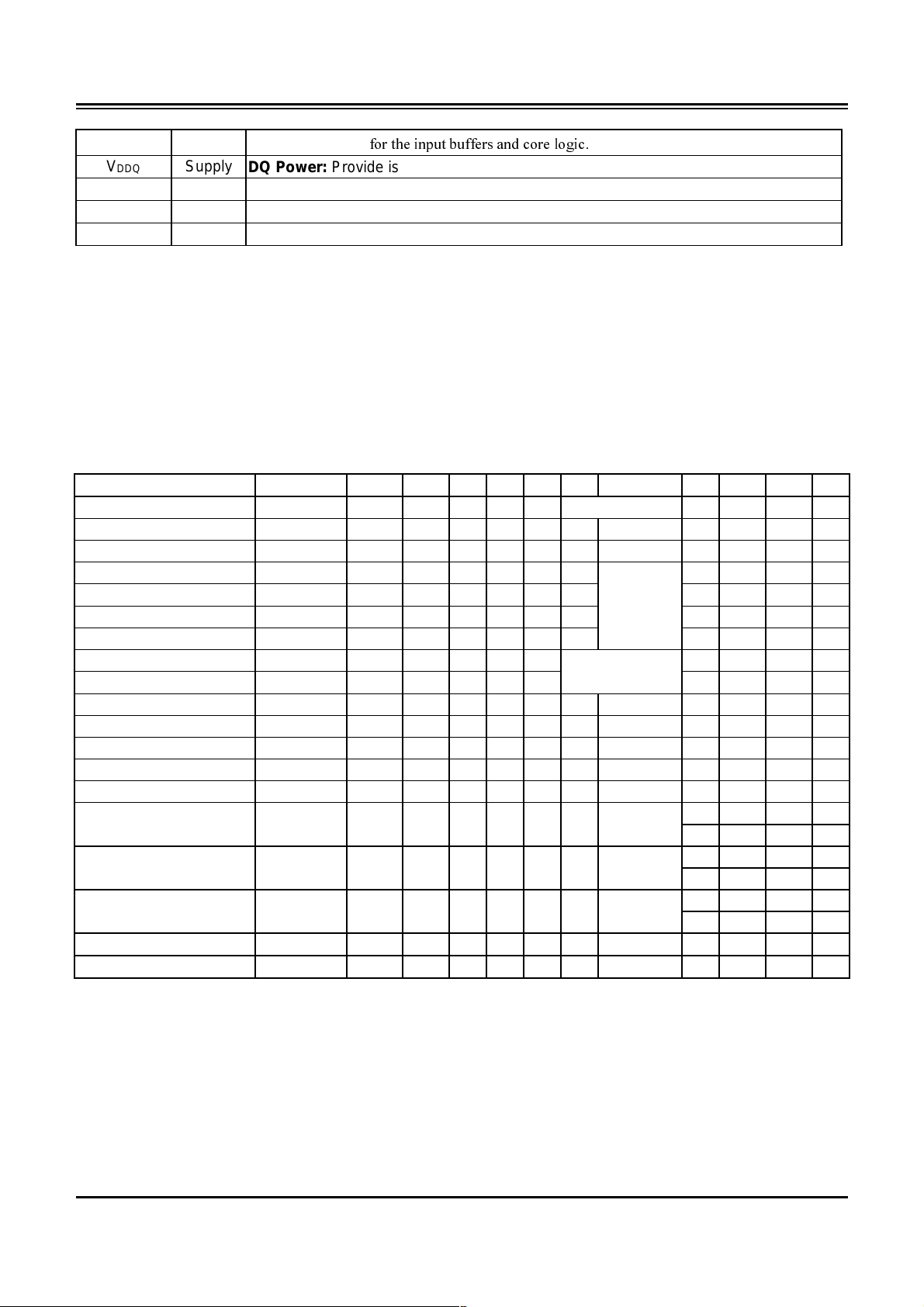

Symbol Type Description

CK, CK# Input

CKE Input

BA0, BA1 Input

A0-A11 Input

CS# Input

RAS# Input

CAS# Input

WE# Input

DQS0-DQS3 Input /

Output

DM0 - DM3 Input

DQ0 - DQ31 Input /

Output

V

DD

Supply

Table 1. Pin Details of EM6A9320

Differential Clock:

commands are sam pled on the positive edge of CK. Both CK and CK# increment the

internal burst counter and controls the output registers.

Clock Enable:

goes low synchronously with clock, the internal clock is suspended f r om the next clock

cycle and the state of output and burst address is fr ozen as long as the CKE rem ains

low. When all bank s are in the idle state, deactivating the clock controls the entry to

the Power Down and Self Refresh modes.

Bank Select:

BankPrecharge com mand is being applied. They also define which Mode Register or

Extended Mode Register is loaded during a Mode Register Set command.

Address Inputs:

address A0-A11) and Read/W rite comm and (column address A0-A7 with A8 defining

Auto Precharge) to select one location out of the 256K available in the respective

bank. During a Precharge command, A8 is sampled to deter mine if all banks ar e to be

precharged (A8 = HIGH). The addr ess inputs also pr ovide the op-code during a Mode

Register Set or Extended Mode Register Set command.

Chip Select:

command decoder. All commands are masked when CS# is sampled HIGH. CS#

provides for external bank selection on systems with multiple banks . It is considered

part of the command code.

Row Address Strobe:

conjunction with the CAS# and WE# signals and is latched at the positive edges of

CK. When RAS# and CS# are as serted "LOW" and CAS# is asserted "HIGH" either

the BankActivate command or the Precharge command is selected by the WE# signal.

When the W E# is asserted "HIGH," the BankActivate c ommand is selected and the

bank designated by BS is turned on to the active state. When the W E# is asserted

"LOW," the Precharge command is selected and the bank designated by BS is

switched to the idle state after the precharge operation.

Column Address Strobe:

conjunction with the RAS# and WE# signals and is latched at the positive edges of

CK. When RAS# is held "HIGH" and CS# is asserted "LOW" the colum n access is

started by asserting CAS# "LOW" Then, the Read or Write comm and is selected by

asserting WE# "HIGH " or “LOW".

Write Enable:

the RAS# and CAS# signals and is latched at the positive edges of CK. The WE#

input is used to select the BankActivate or Prechar ge command and Read or Write

command.

Bidirectional Data Strobe:

bytes: DQS0 to DQ0-DQ7, DQS1 to DQ8-DQ15, DQS2 to DQ16-DQ23, DQS3 to

DQ24-DQ31.

Data Input Mask:

sampled HIGH during a write cycle. DM3 masks DQ31-DQ24, DM2 masks DQ23DQ16, DM1 masks DQ15-DQ8, and DM0 masks DQ7-DQ0.

Data I/O:

edges of CK and CK#. The I/Os are byte-maskable during Writes.

3RZHU 6XSSO\

The DQ0-DQ31 input and output data are synchronized with the positive

CK, CK# are driven by the system clock. All SDRAM input

CKE activates (HIGH) and deactivates (LOW ) the CK signal. If CKE

BA0 and BA1 defines to which bank the Bank Activate, Read, W rite, or

A0-A11 are sampled during the Bank Activate command (row

CS# enables (sampled LOW) and disables (sampled HIGH) the

The RAS# signal defines the operation commands in

The CAS# signal defines the operation commands in

The W E# signal defines the operation commands in c onjunction with

The DQSx signals are mapped to the following data

DM0-DM3 are byte specific. Input data is masked when DM is

3RZHU IRU WKH LQSXW EXIIHUV DQG FRUH ORJLF

Etron Confidential

4 Rev 0.3 July. 2002

Page 5

Etr onT ech

V

SS

V

DDQ

V

SSQ

V

REF

NC -

Note: The timing reference point for the differential clocking is the cross point of the CK and CK#. For any

applications using the single ended clocking, apply V

Supply

Supply

Supply

Supply

Ground:

DQ Power:

DQ Ground:

Reference Voltage for Inputs:

No Connect:

Ground

Provide isolated power to DQs for improved noise immunity.

Provide isolated ground to DQs for improved noise immunity.

These pins should be left unconnected.

4Mx32 DDR SDRAM

IRU WKH LQSXW EXIIHUV DQG FRUH ORJLF

+0.5 x V

to CK# pin.

REF

DDQ

EM6A9320

Operation Mode

Fully synchronous operations are performed to latch the c ommands at the positive edges of CK . Table 2 shows

the truth table for the operation commands.

Table 2. Truth Table (Note (1), (2) )

Command State

BankActivate Idle

BankPrecharge Any H X X V V L X L L H L

PrechargeAll Any H X X X X H X L L H L

Write Active

Write and AutoPrecharge

Read Active

Read and Autoprecharge Active

Mode Register Set Idle H X X L L L L L L

Extended Mode Register Set

No-Operation Any H X X X X X X L H H H

Device Deselect Any H X X X X X X H X X X

Burst Stop Active

AutoRefresh Idle H H X X X X X L L L H

SelfRefresh Entry Idle H L X X X X X L L L H

SelfRefresh Exit

Power Down Mode Entry Idle/Active

Power Down Mode Exit

Data Write/

Data Mask/

Note:

Output Enable

Output Disable

1. V = Valid data, X = Don't Care, L = Low level, H = High level

2. CKE

3. These are states of bank designated by BA0, BA1signals.

4. Read burst stop with BST command for all burst types.

5. Power Down Mode can not enter in the burst operation.

When this command is asserted in the burst cycle, device state is clock suspend mode.

signal is input level when commands are provided.

n

CKE

signal is input level one clock cycle before the commands are provided.

n-1

Active

Idle H X X L H

Idle

(Self Refresh)

Any

(Power Down)

Active H X L X X X X X X X X

Active H X H X X X X X X X X

CKEn-1 CKEn DM BA1 BA0 A8 A11-A9, A7-0 CS# RAS# CAS# WE#

(3)

H X X V V Row Address L L H H

(3)

H X V V V L L H L L

(3)

H X V V V H L H L L

(3)

H X X V V L L H L H

(3)

H X X V V H

(4)

H X X X X X X L H H L

L H X X X X X

(5)

H L X X X X X

L H X X X X X

Column

Address

A0~A7

OP code

L H L H

L L L L

H X X X

L H H H

H X X X

L H H H

H X X X

L H H H

Etron Confidential

5 Rev 0.3 July. 2002

Page 6

Etr onT ech

4Mx32 DDR SDRAM

EM6A9320

Mode Register Set (MRS)

The mode register is divided into various fields depending on functionality.

Burst Length Field (A2, A1, A0)

•

This field specifies the data length of column access and selects the Burst Length.

Addressing Mode Select Field (A3)

•

The Addressing Mode can be Interleave Mode or Sequential Mode. Both Sequential Mode and

Interleave Mode support burst length of 2, 4 and 8. Full page burst length is only for Sequential mode.

CAS# Latency Field (A6, A5, A4)

•

This field specifies the number of clock cycles from the ass ertion of the Read com m and to the f irst read

data. The minimum whole value of CAS# Latency depends on the frequency of CK. The minimum whole

value satisfying the following formula must be programmed into this field.

(min)

t

CAC

Test Mode field :A7; DLL Reset Mode field : A8

•

These two bits must be programmed to "00" in normal operation.

( BA0, BA1)

•

Mode Resistor Bitmap

BA1 BA0 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

0 Mode RFU must be set to “0” DLL TM CAS Latency BT Burst Lenght

BA0 Register Mode A8 A7 Mode A3 Type

0 MRS 0 0 Normal 0 Sequential

1 EMRS 1 0 Reset DLL 1 Interleave

0 1 Test Mode

CAS# Latency X t

CK

A6 A5 A4 CAS Latency A2 A1 A0 Burst Length

0 1 0 Reserved 0 0 1 2

0 1 1 3 clocks 0 1 0 4

1 0 0 4 clocks 0 1 1 8

1 0 1 5 clocks 1 1 1 Full Page (Sequential)

All other Reserved All other Reserved

Burst Definition, Addressing Sequence of Sequential and Interleave Mode

Burst Length

2

4

8

Start Address

A2 A1 A0

X X 0 0, 1 0, 1

X X 1 1, 0 1, 0

X 0 0 0, 1, 2, 3 0, 1, 2, 3

X 0 1 1, 2, 3, 0 1, 0, 3, 2

X 1 0 2, 3, 0, 1 2, 3, 0, 1

X 1 1 3, 0, 1, 2 3, 2, 1, 0

0 0 0 0, 1, 2, 3, 4, 5, 6, 7 0, 1, 2, 3, 4, 5, 6, 7

0 0 1 1, 2, 3, 4, 5, 6, 7, 0 1, 0, 3, 2, 5, 4, 7, 6

0 1 0 2, 3, 4, 5, 6, 7, 0, 1 2, 3, 0, 1, 6, 7, 4, 5

0 1 1 3, 4, 5, 6, 7, 0, 1, 2 3, 2, 1, 0, 7, 6, 5, 4

1 0 0 4, 5, 6, 7, 0, 1, 2, 3 4, 5, 6, 7, 0, 1, 2, 3

1 0 1 5, 6, 7, 0, 1, 2, 3, 4 5, 4, 7, 6, 1, 0, 3, 2

1 1 0 6, 7, 0, 1, 2, 3, 4, 5 6, 7, 4, 5, 2, 3, 0, 1

1 1 1 7, 0, 1, 2, 3, 4, 5, 6 7, 6, 5, 4, 3, 2, 1, 0

Sequential Interleave

Etron Confidential

6 Rev 0.3 July. 2002

Page 7

Etr onT ech

4Mx32 DDR SDRAM

EM6A9320

Extended Mode Register Set (EMRS)

The Extended Mode Register Set stores the data for enabling or disabling DLL and selecting output driver

strength. The default value of the extended mode register is not defined, therefore must be written after power

up for proper operation. The extended mode regist er is written by asserting low on CS#, RAS#, CAS#, and WE#.

The state of A0, A2 ~ A5, A7 ~ A11and BA1 is written in the mode register in the same cycle as CS#, RAS#,

CAS#, and WE# going low. The DDR SDRAM should be in all bank precharge with CKE already high prior to

writing into the extended mode register. A1 and A6 are used for setting driver strength to normal, weak or

matched impedance. Two clock cycles are required to complete the write operation in the extended mode

register. The mode register contents can be changed using the same command and clock cycle requirements

during operation as long as all banks are in the idle state. A0 is used for DLL enable or disable. "High" on BA0 is

used for EMRS. Refer to the table for specific codes.

Extended Mode Resistor Bitmap

BA1 BA0 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

0 1 RFU must be set to “0” DS1 RFU must be set to “0” DS0 DLL

BA0 Mode A6 A1 Drive Strength Strength Comment A0 DLL

0 MRS

1 EMRS 0 1 SSTL-2 weak 60% 1 Disable

1 0 RFU RFU Do not use

1 1 Matched impedance 30%

0 0 Full 100%

Output driver matches impedance

0

Enable

Power up Sequence

Power up must be performed in the following sequence.

1) Apply power to V

"NOP" state and maintain CKE “LOW”.

2) Start clock and maintain stable condition for minimum 200us.

3) Issue a “NOP” command and keep CKE “HIGH”

4) Issue a “Precharge All” command.

5) Issue EMRS – enable DLL.

6) Issue MRS – reset DLL. (An additional 200 clock cycles are required to lock the DLL).

7) Precharge all banks of the device.

8) Issue two or more Auto Refresh commands.

9) Issue MRS – with A8 to low to initialize the mode register.

before or at the same time as V

DD

DDQ, VTT

and V

when all input signals are held

REF

Etron Confidential

7 Rev 0.3 July. 2002

Page 8

Etr onT ech

Absolute Maximum Rating

4Mx32 DDR SDRAM

EM6A9320

Symbol Item Rating Unit Note

VIN, V

VDD, V

Input, Output Voltage - 0.3 ~ V

OUT

Power Supply Voltage -0.3 ~ 3.6 V

DDQ

+0.3 V

DDQ

TA Ambient Temperature 0~70 °C

T

Storage Temperature - 55~150

STG

T

Soldering Temperature (10s) 240

SOLDER

C

°

C

°

PD Power Dissipation 2.0 W

I

Short Circuit Output Current 50 mA

OUT

Recommended D.C. Operating Conditions (SSTL_2 In/ O ut, TA = 0 ~ 70 °C)

Symbol Parameter Min. Typ. Max. Unit Note

VDD Power Supply Voltage

V

Power Supply Voltage(for I/O )

DDQ

V

Input Reference Voltage 0.49 x V

REF

VTT Termination Voltage V

V

Input High Voltage V

IH(DC)

V

Input Low Voltage Vssq - 0.3 - V

IL(DC)

VOH Output High Voltage Vtt + 0.76 - - V

VOL Output Low Voltage - - Vtt- 0.76 V

IIL Input Leakage Current - 5 - 5 uA

IOL Output Leakage Current - 5 - 5 uA

Note : 1. Under all conditions V

2. For CLK Frequency is 350, 333, 300, or 285MHz

3. For CLK Frequency is 250, or 200MHz

must be less than or equal to VDD.

DDQ

Capacitance (VDD = 2.8V, f = 1MHz, TA = 25 °C)

Parameter Symbol Min. Max. Unit

Input Capacitance (A0~A11, BA0, BA1) C

Input Capacitance (CK, CK#, CKE, CS#, RAS#, CAS#, WE#) C

DQ & DQS input/output capacitance C

DM0~DM3 input/output capacitance C

Note: These parameters are periodi cally sampled and are not 100% tested.

2.66 2.8 2.94 V 1,2

2.375 2.5 2.625 1,3

2.66 2.8 2.94 V 1,2

2.375 2.5 2.625 1,3

- 0.51 x V

DDQ

– 0.04 V

REF

+ 0.15 - V

REF

REF

V

REF

DDQ

REF

+ 0.04 V

V

DDQ

+ 0.3 V

- 0.15 V

I

= -15.2 mA

OH

I

= +15.2 mA

OL

4 5 pF

IN1

3 5 pF

IN2

6 8 pF

OUT

6 8 pF

IN3

Etron Confidential

8 Rev 0.3 July. 2002

Page 9

Etr onT ech

4Mx32 DDR SDRAM

D.C. Characteristics

(VDD = 2.8V ± 5% for 350, 333, 300, or 285MHz, VDD=2.5 ± 5% for 250 or 200MHz, TA = 0~70 °C)

Parameter & Test Condition Symbol

OPERATING CURRENT :

t

RC=tRC

changing once per clock cycle; Address and control inputs

changing once every two clock cycles.

OPERATING CURRENT :

Precharge; BL=4; CL=4; tRCDRD=4*t

t

CK=tCK

changing once per clock cycle

PRECHARGE POWER-DOWN STANDBY CURRENT:

All banks idle; power-down mode; t

CKE=LOW

IDLE STANDLY CURRENT :

CS#=HIGH(DESELECT); All banks idle; t

Address and control inputs changing once per clock cycle;

V

ACTIVE POWER-DOWN STANDBY CURRENT :

bank active; power-down mode; CKE=LOW; t

ACTIVE STANDBY CURRENT :

one bank active ; t

control inputs changing once per clock cycle;

DQ,DQS,and DM inputs changing twice per clock cycle

OPERATING CURRENT BURST READ :

Continuous burst; one bank active; Address and control

inputs changing once per clock cycle; t

lout=0mA;50% of data changing on every transfer

OPERATING CURRENT BURST Write :

Continuous Burst ;one bank active; address and control

inputs changing once per clock cycle; t

DQ,DQS,and DM changing twice per clock cycle; 50% of

data changing on every transfer

AUTO REFRESH CURRENT :

t

CK=tCK

SELF REFRESH CURRENT:

CKE<=0.2V;t

BURST OPERATING CURRENT 4 bank operation:

Four bank interleaving READs; BL=4;with Auto Precharge;

t

RC=tRC

inputschang only during Active, READ , or WRITE

command

(min); tCK=tCK(min); DQ,DM and DQS inputs

(min); lout=0mA; Address and control inputs

IN=VREF

for DQ, DQS and DM

RC=tRC

(min)

CK=tCK

(min); tCK=tCK(min); Address and control

(min)

One bank; Active-Precharge;

One bank; Active-Read-

; tRC=tRC(min);

CK

CK=tCK

CKE = HIGH;

CS#=HIGH;CKE=HIGH;

(max);tCK=tCK(min);Address and

t

RC=tRFC

Sell Refresh Mode ;

(min);

CK=tCK

CK=tCK

CK=tCK

(min);

(min);

one

CK=tCK

BL=2; READS;

(min);

BL=2; WRITES;

(min);

(min)

IDD0 330 320 280 260 180 160 mA

IDD1 450 440 380 360 260 240 mA

IDD2P

IDD2N 100 100 100 100 80 80 mA

IDD3P 50 50 50 50 45 40 mA

IDD3N 140 135 120 110 100 100 mA

IDD4R 560 540 480 450 440 420 mA

IDD4W

IDD5 430 430 420 410 300 280 mA

IDD6 4 4 4 4 3 3 mA

IDD7

2.8 3.0 3.3 3.5 4 5

50

50 50

470

450 400

920

890 780

Max

370

720

EM6A9320

Unit Notes

50

45 40 mA

300 270 mA

650 550 mA

Note:

1. Stress greater than those listed under "Absolute Maximum Ratings" may cause permanent

damage of the device.

2. All voltages are referenced to V

3. These parameters depend on the cycle rate and these values are measured by the cycle rate

under the minimum value of t

4. Power-up sequence is described in previous page.

Etron Confidential

SS

.

CK

and tRC. Input signals are changed one time during tCK.

9 Rev 0.3 July. 2002

Page 10

Etr onT ech

4Mx32 DDR SDRAM

EM6A9320

Decoupling Capacitance Guide Line

Symbol Parameter Value Unit

C

Decouping Capacitance between VDD and VSS 0.1+0.01 uF

DC1

C

Decouping Capacitance between V

DC2

DDQ

and V

0.1+0.01 uF

SSQ

AC Input Operating Conditions

(VDD = 2.8V ± 5% for 350, 333, 300, or 285MHz, VDD=2.5 ± 5% for 250 or 200MHz, TA = 0~70 °C)

Symbol Parameter Min Max Unit Note

VIH Input High Voltage; DQ V

VIL Input Low Voltage; DQ - V

VID Clock Input Differential Voltage; Ck & CK# 0.8 V

VIX Clock Input Crossing Point Voltage; Ck & CK# 0.5xV

AC Operating Test Conditions

(VDD = 2.8V ± 5% for 350, 333, 300, or 285MHz, VDD=2.5 ± 5% for 250 or 200MHz, TA = 0~70 °C)

Reference Level of Output Signals (V

CK & CK# signal maximum peak swing 1.5V

Output Load See Figure. A Test Load

Input Signal Levels V

Input Signals Slew Rate 1 V/ns

Input timing measurement reference level V

Output timing measurement reference level VTT

Reference Level of Input Signals 0.5 x V

RFE

+0.4 - V

REF

-0.2 0.5xV

DDQ

) 0.5 x V

+0.4 V / V

REF

REF

-0.4 V

REF

+0.6 V

DDQ

+0.2 V

DDQ

DDQ

-0.4 V

REF

DDQ

Figure A. Test Load

DQ,DQS

VΤΤ=0.5 x V

Z0=50 W

∆∆Θ

:

30pF

VREF=0.5 x VDDQ

Etron Confidential

10 Rev 0.3 July. 2002

Page 11

Etr onT ech

4Mx32 DDR SDRAM

EM6A9320

Electrical Characteristi cs and Recommended A.C. Operating Condi ti ons

0.45

0.45

-0.6

-0.6

-

0.9

0.4

0.85

0

0.35

0.4

0.4

0.4

0.9

0.9

0.4

0.4

tCLMIN

or

tCHMIN

tHP -

0.4

16

18

11

5

3

3

3

3

2

1

1

9

200

tIS +

2tCK

0.55 0.45

0.55 0.45

0.6 -0.7

0.6 -0.7

0.4 -

1.1 0.9

0.6 0.4

1.15 0.85

- 0

- 0.35

0.6 0.4

0.6 0.4

0.6 0.4

- 0.9

- 0.9

- 0.45

- 0.45

tCLMIN

tCHMIN

tHP -

-

0.45

- 15

- 17

100K 10

- 5

- 3

- 3

- 3

- 3

- 2

- 1

- 2

- 8

- 200

tIS +

-

2tCK

7.8 -

0.55

0.45 0.55

0.55

0.45 0.55

0.7

-0.7 0.7

0.7

-0.7 0.7

0.4

1.1

0.9 1.1

0.6

0.4 0.6

1.15

0.85 1.15

-

-

0.35 -

0.6

0.4 0.6

0.6

0.4 0.6

0.6

0.4 0.6

-

1.0 -

-

1.0 -

-

0.5 -

-

0.5 -

-

-

-

-

100K

-

-

-

-

-

-

-

-

-

-

-

7.8

tCLMIN

or

tCHMIN

tHP -

0.5

12

14 -

200 -

tIS +

2tCK

or

(VDD = 2.8V ± 5% for 350, 333, 300, or 285MHz, VDD=2.5 ± 5% for 250 or 200MHz, TA = 0~70 °C)

Symbol Parameter

CL = 3 3.3 10 3.3 10 3.3 10 3.5 10 4 10 5 10

tCK

tCH

t

CL

t

DQSCK

tAC

t

DQSQ

t

RPRE

t

RPST

t

DQSS

t

WPRES

t

WPREH

t

WPST

t

DQSH

t

DQSL

tIS

tIH

tDS

tDH

tHP

tQH

tRC

t

RFC

t

RAS

t

RCDRD

t

RCDWR

tRP

t

RRD

twR

t

CDLR

t

CCD

t

MRD

t

DAL

t

XSA

t

PDEX

t

REF

Clock cycle time

Clock high level width

Clock low level width

DQS-out access time from CK,CK#

Output access time from CK,CK#

DQS-DQ Skew

Read preamble

Read postamble

CK to valid DQS-in

DQS-in setup time

DQS-in hold time

DQS write postamble

DQS in high level pulse width

DQS in low level pulse width

Address and Control input set up t i me

Address and Control input hold ti me

DQ & DM setup time to DQS

DQ & DM hold time to DQS

Clock half period

Output DQS valid window

Row cycle time

Refresh row cycle time

Row active time

RAS# to CAS# Delay in Read

RAS# to CAS# Delay in Write

Row precharge time

Row active to Row active delay

Write recovery t ime

Last data in to Read command

Col. Address to Col. A ddress delay

Mode register set cycle time

Auto precharge write r ecovery + Prechar ge

Self refresh exit to read command delay

Power down exit time

Refresh interval time

CL = 4 2.86 10 3.0 10 3.3 10 3.5 10 4 10 5 10

CL = 5 2.86 5 3.0 5 3.3 5 3.5 5 4 5 5 10

2.8 3.0 3.3 3.5 4.0 5.0

Min Max Min Max Min Max Min Max Min Max Min Max

0.45

0.45

-0.6

-0.6

-

0.9

0.4

0.85

0

0.35

0.4

0.4

0.4

0.9

0.9

0.35

0.35

tCLMIN

or

tCHMIN

tHP -

0.35

20

22

14

7

5

6

4

3

2

1

1

9

200

tIS +

2tCK

-

0.55 0.45

0.55 0.45

0.6 -0.6

0.6 -0.6

0.35 -

1.1 0.9

0.6 0.4

1.15 0.85

- 0

- 0.35

0.6 0.4

0.6 0.4

0.6 0.4

- 0.9

- 0.9

- 0.35

- 0.35

tCLMIN

tCHMIN

-

- 20

- 22

100K 14

- 7

- 5

- 6

- 4

- 3

- 2

- 1

- 1

- 9

- 200

-

7.8 -

or

tHP -

0.35

tIS +

2tCK

0.55

0.55

0.6

0.6

0.35

1.1

0.6

1.15

-

-

0.6

0.6

0.6

-

-

-

-

-

-

-

-

100K

-

-

-

-

-

-

-

-

-

-

-

7.8

0.45 0.55

0.45 0.55

-0.6 0.6

-0.6 0.6

- 0.35

0.9 1.1

0.4 0.6

0.85 1.15

0 -

0.35 -

0.4 0.6

0.4 0.6

0.4 0.6

0.9 -

0.9 -

0.35 -

0.35 -

tCLMIN

or

tCHMIN

tHP -

0.35

17 19 12 100K

200 -

tIS +

2tCK

-

-

6 4 5 3 3 2 1 1 9 -

-

- 7.8

Unit

- 0.45

0 -

-

-

-

8 100K

4 2 3 2 2 2 1 2 7 -

-

7.8

ns

tCK

tCK

ns

ns

ns

tCK

tCK

tCK

ns

ns

tCK

tCK

tCK

ns

ns

ns

ns

ns

ns

tCK

tCK

tCK

tCK

tCK

tCK

tCK

tCK

tCK

tCK

tCK

tCK

tCK

ns

us

Etron Confidential

11 Rev 0.3 July. 2002

Page 12

Etr onT ech

t

t

t

t

1

3 4 5

8

4 5 6

4Mx32 DDR SDRAM

Timing Waveforms

Figure 1. AC Parameters for Read Timimg (Burst Length = 4)

CK#

CK

CMD

A0-11,

BA0-1

DQS

DQ

DQS

DQ

DQS

DQ

tCK

tIS

tIH

RD

tIS

tIH

Valid

CAS Latency = 5

CAS Latency = 4

CAS Latency = 3

Figure 2. AC Parameters for Write Timing (Burst Length=4)

2

tCH

CL

tHP

tHP

“Preamble”

“Preamble” “Postmble”

RPRE

AC

DQSQ

t

“Preamble”

DQ0 DQ1 DQ2 DQ3

“Postmble”

DQ0 DQ1 DQ2 DQ3

6 7

DQSCK

t

DQ0 DQ1 DQ2 DQ3

“Postmble”

EM6A9320

0

QHS

t

RPST

t

tQH

CK#

CK

CMD

A0-11,

BA0-1

DQS

DM

DQ

WR

Valid

t

WPRES

DQSS

t

WPREH

t

Etron Confidential

1 2 3

“Postmble” “Preamble”

t

tDH tDS

DQ0 DQ1 DQ2 DQ3

WPST

7 8 0

WR WR

Valid

“Preamble”

DQSS

DQ0

12 Rev 0.3 July. 2002

Valid

tDH

tDS

DQ1 DQ2 DQ3

tDS

Input Data Masked

DQ4 DQ5

DQ6 DQ7

tDH

“Postmble”

WPST

t

Page 13

Etr onT ech

3 4 5 6

8

A

3 4 5 6

B

C

Figure 3. Bank Activate Read or Write Command Timing

4Mx32 DDR SDRAM

CK

CMD

ROW ADR Percharge

A0-11

BA0-1

RCDRD

t

RAS

t

RD PRE ACT ACT ACT ACT

CA RA RA RA RA

ROW ADR Column ADR

BA BA BA BA BA BA

Bank ADR

tRP

RC

t

t

RRD

RCDWR

t

RAS

WR

CA

BA

RC

t

Figure 4. Burst Stop for Read (CAS Letancy = 5, Burst Length = 4)

CK#

CK

1 2

7

EM6A9320

tRP t

PRE

BA

0

CMD

A0-11,

BA0-1

DQS

DQ

RD

Burst Stop for CAS Latency = 5

Valid

fter 1 x CK Command can be

DQ0 DQ1

CMD BST

1x CK

Figure 5. Read with Auto Precharge (CAS Letancy = 5, Burst Length = 4)

CK#

CK

CMD

A0-11,

BA0-1

DQS

1 2

RDA

Valid

Begin of Auto Precharge

AS Latency = 5

ank can be Active after Auto Precharge Read with Auto Precharge

RP

t

0

ACT

Valid

DQ

Etron Confidential

13 Rev 0.3 July. 2002

DQ0 DQ1

DQ2 DQ3

Page 14

Etr onT ech

3 4

B

B

5 6

3 4 5 6

8

3 4

4Mx32 DDR SDRAM

Figure 6. Write with Auto Precharge (Burst Length = 4)

EM6A9320

CK#

CK

CMD

A0-11,

BA0-1

DQS

DQ

WRA

Valid

1 2

DQ0 DQ1

DQ2 DQ3

0

ank can be Active after Auto Precharge Write with Auto Precharge

WR

t

egin of Auto Precharge

ACT

Valid

RP

t

Figure 7. Read Burst Interrupt by Read (CAS Letancy = 5, Burst Length = 4)

CK#

CK

CMD

A0-11,

BA0-1

RDa

Valid

t

CCD

1 2

RDb

Valid

7

0

DQS

DQ

Figure 8. Write Interrupted by Write (Burst Length = 4)

CK#

CK

CMD

A0-11,

BA0-1

DQS

DQ

WRa

Valid

t

CCD

1 2

WRb

Valid

Da0 Da1

Db2 Db3 Db0 Db1

0

Figure 9. Auto Refresh Timimg

CK

Da0 Da1

Db2 Db3 Db0 Db1

RFC

t

tRP

CMD

Etron Confidential

AFRF PRE CMD

Auto Refresh Precharge

14 Rev 0.3 July. 2002

Page 15

Etr onT ech

P

P

A

M

R

w

A

Figure 10. Self Refresh Timimg

CK

200xCK

SREX

t

4Mx32 DDR SDRAM

EM6A9320

CMD

CKE

Self Refresh Entry

Self Refresh Exit After 200 x CK, Command can be active

NOP SRESREF CMD

Figure 11. Precharge Command

CK

CMD

A0-11

BA0-1

RAS

RC

t

PRE ACT ACT

RA RA

BA BA BA

tRP t

Figure 12. Power Up Sequence

CK

CMD

Power Up

wait 200uS

tRP t

REA NOP MRS

Precharge All

EMRS set Precharge All

Figure 13. Mode Register Set Timing

CK

CMD

Precharge All

1xCK

tRP t

CMD PREA MRS

MRS set

MRD

fter 1 x CK, Command can be active

Figure 14. Power Down Mode

MRD

tRP t

REA

RS set

eset DLL

ith A8=H

RE MRS

2 or more

Auto Refresh

RFC

200uS 200xCK

ARENOP EMRS

MRS set

with A8=L

CK

NOP

CMD

CKE

Etron Confidential

NOP PRE NOP

Power Down Mode Entry

CMD

PDEX

t

Power Down Mode Exit

15 Rev 0.3 July. 2002

Page 16

Etr onT ech

4Mx32 DDR SDRAM

EM6A9320

BOTTOM VIEW

PIN A1 CORN ER

123456

L

TOP VIEW

789101112

S

0.08

S

0.15

0.40~0.50 (144X)

12 11 10 9 8

C

CAB

65

43

7

PIN A1 CORN ER

21

L

- A -

1.60

C

0

2

0.

\\

- C -

SEATING P LAN E

- B -

0.15 (4x)

0.15 C

C

Ball pitch : 0.80

Ball Diameter : 0.45

0.80

8.80

Etron Confidential

16 Rev 0.3 July. 2002

Loading...

Loading...