Page 1

EtronTech

EM564166

256K x 16 Low Power SRAM

Preliminary, Rev 1.0 05/2001

Features

Single power supply voltage of 2.3V to 3.6V

•

Power down features using CE#

•

Low power dissipation

•

Data retention supply voltage: 1.0V to 3.6V

•

Direct TTL compatibility for all input and output

•

Wide operating temperature range: -40°C to 85°C

•

Standby current @ VDD = 3.6 V

•

EM564166BC-70/85

EM564166BC-70E/85E

I

Typical Maximum

1 µA 10 µA

5 µA 80 µA

DDS2

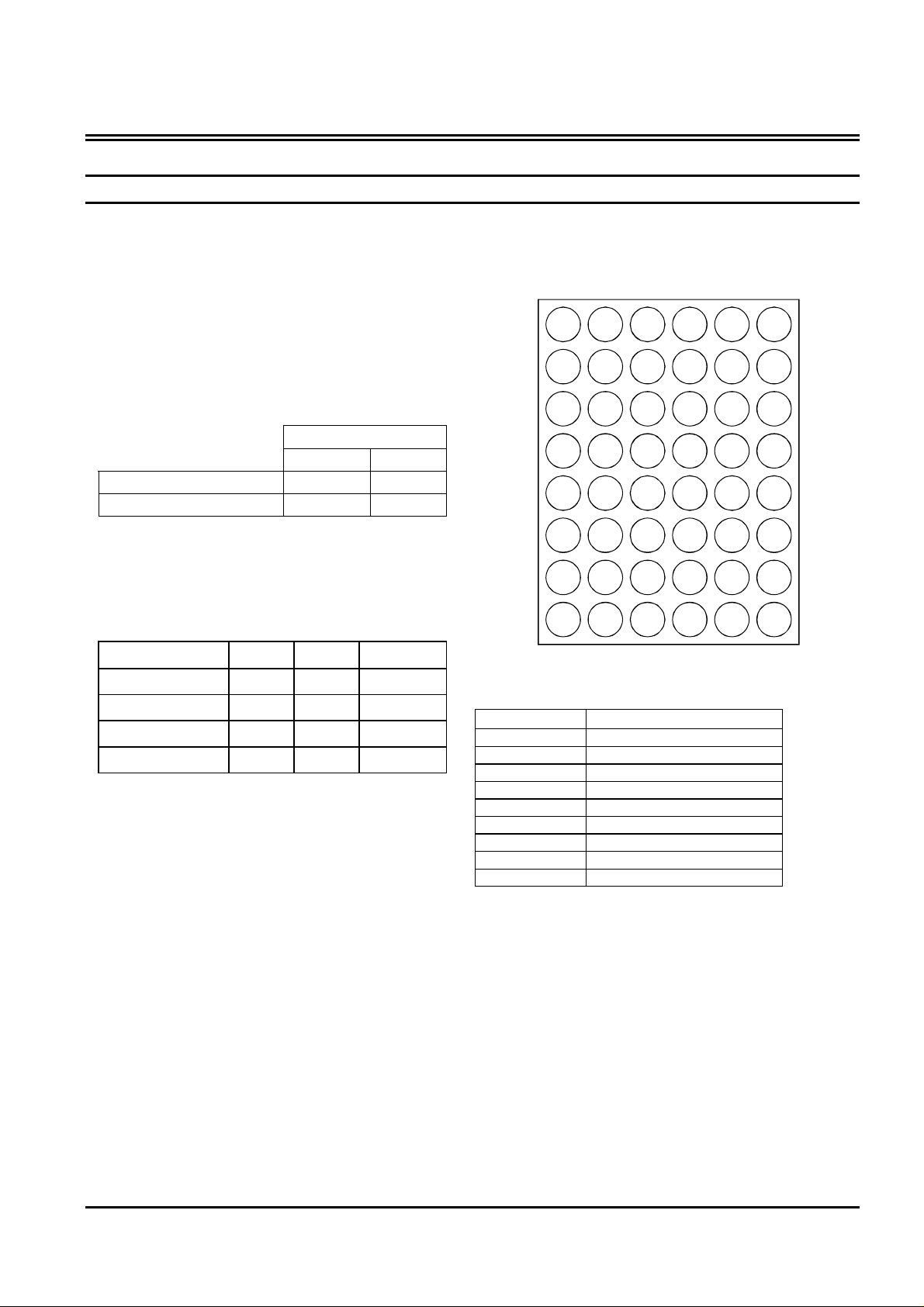

Ordering Information

Part Number Speed I

EM564166BC-70 70 ns

EM564166BC-85 85 ns

EM564166BC-70E 70 ns

EM564166BC-85E 85 ns

Package

DDS2

10 µA

10 µA

80 µA

80 µA

6x8 BGA

6x8 BGA

6x8 BGA

6x8 BGA

Overview

Pin Configuration

48-Ball BGA (CSP), Top View

1 2 3 4 5 6

A

LB# OE# A0 A1 A2 NC

B

DQ8 UB# A3 A4 CE# DQ0

C

DQ9 DQ10 A5 A6 DQ1 DQ2

D

GND DQ11 A17 A7 DQ3 VDD

E

VDD DQ12 NC A16 DQ4 GND

F

DQ14 DQ13 A14 A15 DQ5 DQ6

G

DQ15 NC A12 A13 WE# DQ7

H

NC A8 A9 A10 A11 NC

Pin Description

Symbol Function

A0 - A17 Address Inputs

DQ0 - DQ15 Data Inputs / Outputs

CE# Chip Enable Inputs

OE# Output Enable

WE# Read / Write Control Input

LB#, UB# Data Byte Control Inputs

GND Ground

V

DD

NC No Connection

Power Supply

The EM564166 is a 4,194,304-bit SRAM organized as 262,144 words by 16 bits. It is designed with advanced

CMOS technology. This Device operates from a single 2.3V to 3.6V power supply. Advanced circuit

technology provides both high speed and low power. It is automatically placed in low-power mode when chip

enable (CE#) is asserted high. There are two control inputs. CE# are used to select the device and for data

retention control, and output enable (OE#) provides fast memory access. Data byte control pin (LB#,UB#)

provides lower and upper byte access. This device is well suited to various microprocessor system applications

where high speed, low power and battery backup are required. And, with a guaranteed operating range from 40°C to 85°C, the EM564166 can be used in environments exhibiting extreme temperature conditions.

Etron Technology, Inc.

No. 6, Technology Rd. V, Science-Based Industrial Park, Hsinchu, Taiwan 30077, R.O.C.

TEL: (886)-3-5782345 FAX: (886)-3-5778671

Etron Technology, Inc., reserves the right to make changes to its products and specifications without notice.

Page 2

EtronTech

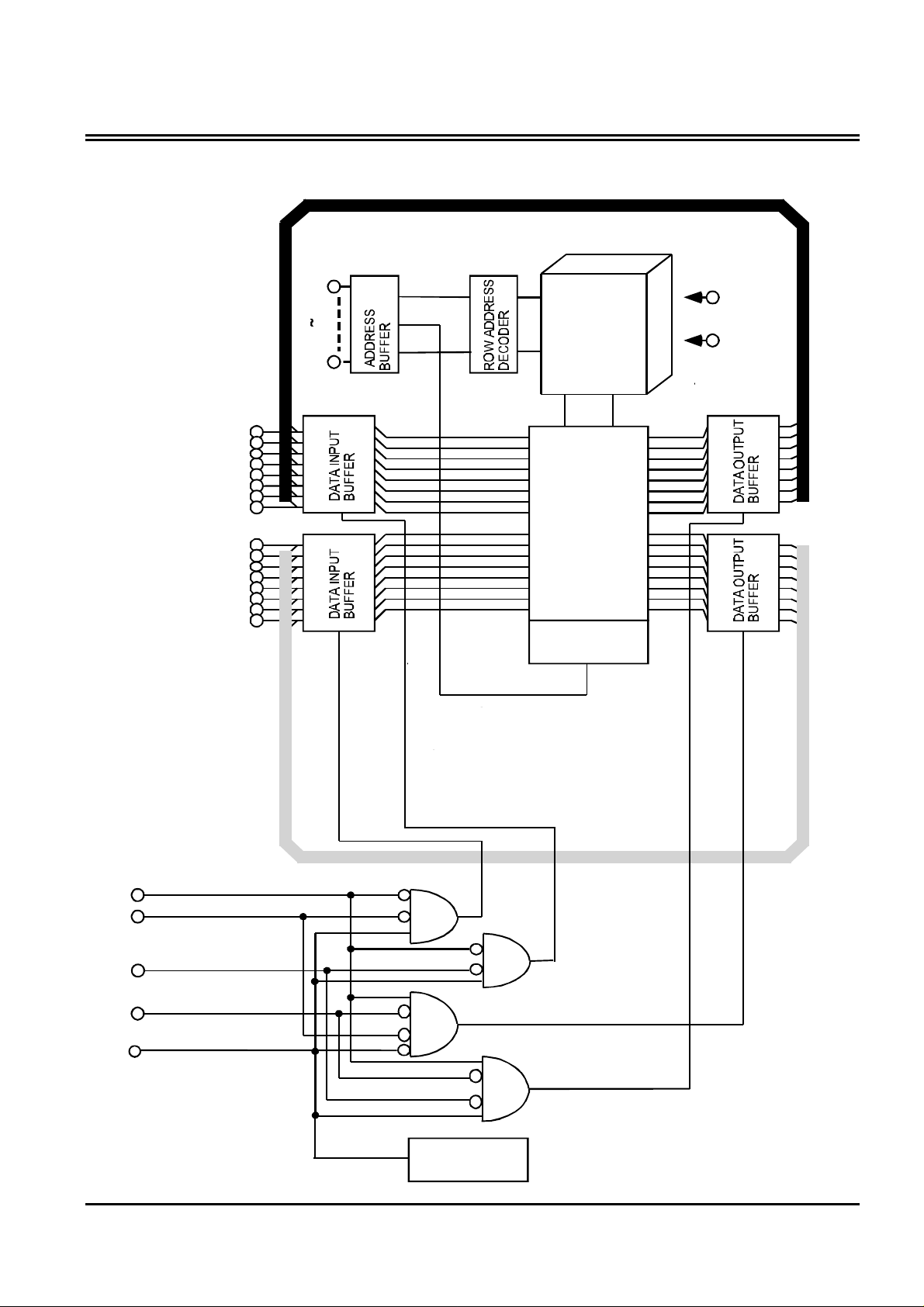

Block Diagram

EM564166

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

A0

A17

MEMORY

CELL ARRAY

2,048X128X16

(4,194,304)

SENSE AMP

COLUMN ADDRESS

DECODE R

VDD

GND

WE#

UB#

LB#

OE#

CE#

Preliminary

POWER DOWN

CIRCUIT

2 Rev 1.0

May 2001

Page 3

EtronTech

+0.5V

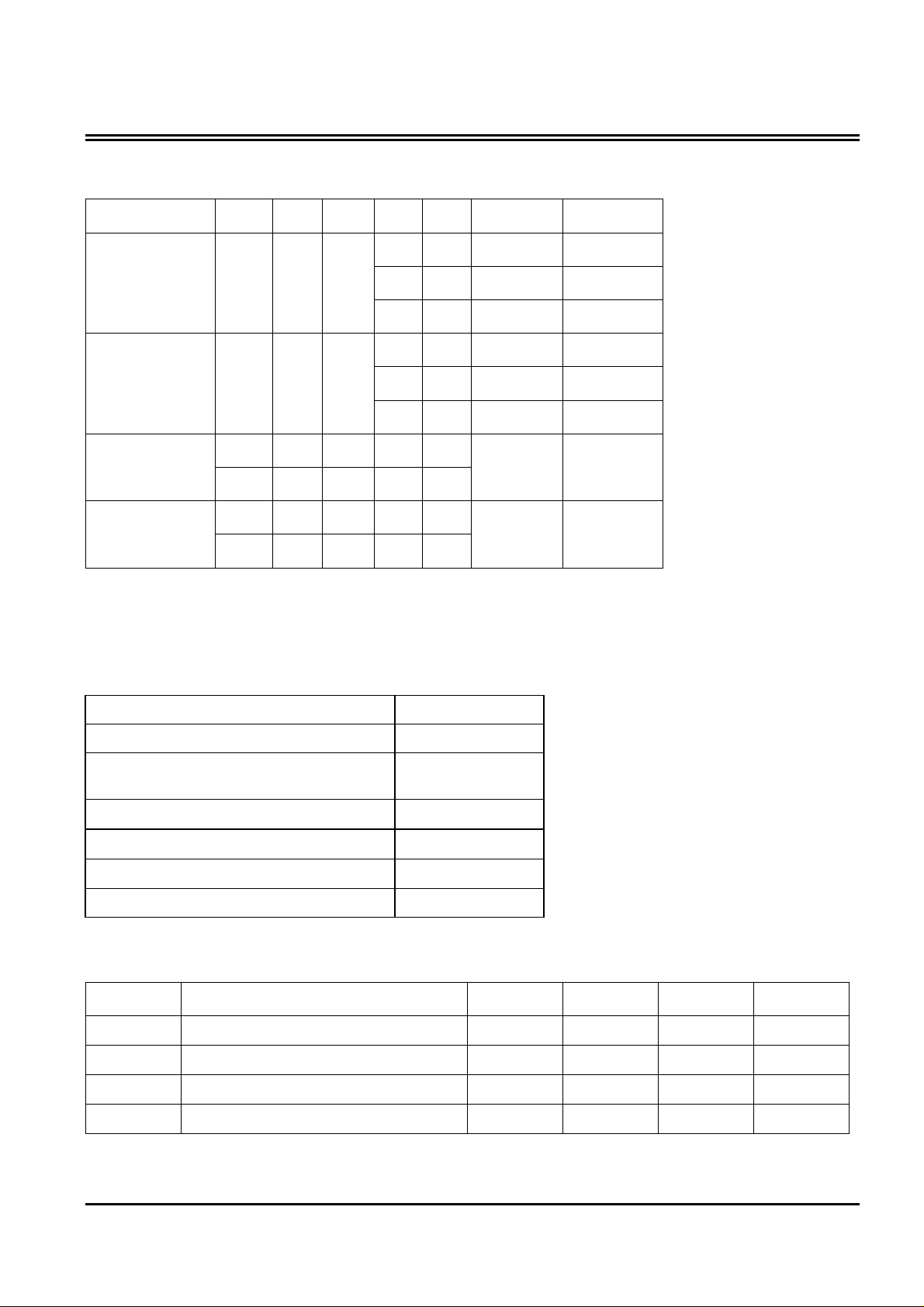

Operating Mode

Mode CE# OE# WE# LB# UB# DQ0~DQ7 DQ8~DQ15

EM564166

Read L L H

Write L X L

L H H X X

Output Deselect

Standby

L X X H H

H X X X X

X X X X X

L L D

H L High-Z D

L H D

L L DIN DIN

H L High-Z DIN

L H DIN High-Z

Note: X = don't care. H=logic high. L=logic low.

Absolute Maximum Ratings

D

OUT

High-Z

OUT

High-Z High-Z

High-Z High-Z

OUT

OUT

Supply voltage, VDD -0.3 to +4.6V

Input voltages, VIN -0.3 to +4.6V

Input and output voltages, V

Operating temperature, T

Storage temperature, T

Soldering Temperature (10s), T

Power dissipation, PD 0.6 W

STRG

I/O

OPR

SOLDER

-0.5 to VDD

-40 to +85°C

-55 to +150°C

240°C

DC Recommended Operating Conditions (Ta=-40°C to 85°C)

Symbol Parameter Min Typ Max Unit

VDD Power Supply Voltage 2.3

VIH Input High Voltage 2.2

VIL Input Low Voltage -0.3

VDR Data Retention Supply Voltage 1.0

Note:

(1) Overshoot : VDD +2.0V in case of pulse width ≤ 20ns

(2) Undershoot : -2.0V in case of pulse width ≤ 20ns

(2)

−

−

−

−

3.6 V

V

DD

(1)

+ 0.3

0.6 V

3.6 V

V

Preliminary

3 Rev 1.0

May 2001

Page 4

EtronTech

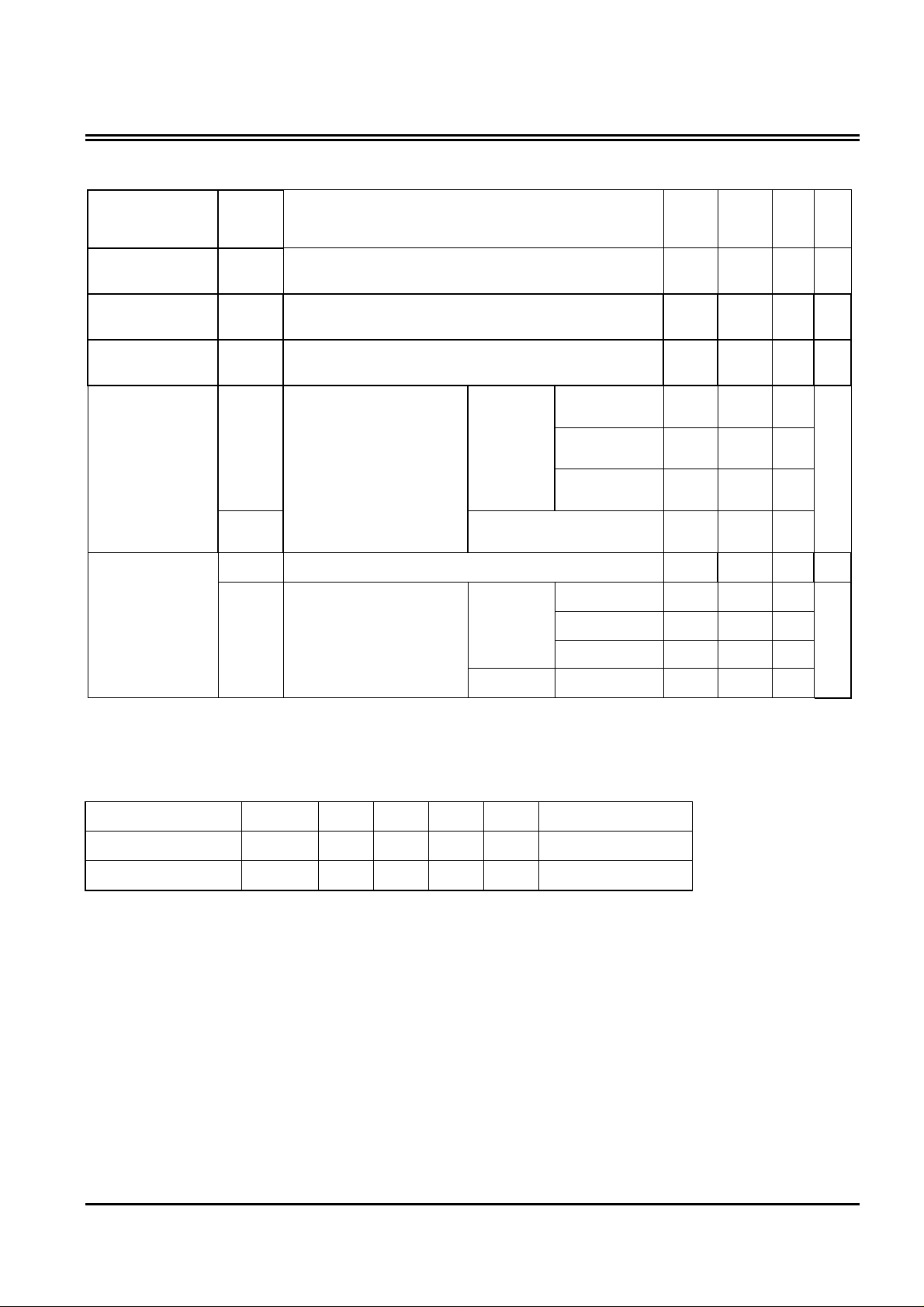

DC Characteristics (Ta = -40°C to 85°C, VDD = 2.3V to 3.6V)

EM564166

Parameter Symbol

Input low current

Output low

voltage

Output high

voltage

Operating current

I

Standby current I

Notes:

* Typical value are measured at Ta = 25°C.

-70E/85E

IIL I

VOL I

VOH I

I

DD1

I

DD2

DDS1

DDS2

Test Conditions Min Typ* Max Unit

= 0V to VDD - 1

IN

= 2.1 mA -

OL

= -1.0 mA

OH

V

= 3.6 V

DD

CE# = V

I

OUT

Other Input = V

CE# = V

CE# ≥ VDD - 0.2V

and

IL

= 0mA

IH

IH

/ V

Cycle time

IL

V

V

V

V

V

V

DD

DD

DD

DD

DD

DD

= min

Cycle time = 1µs

-70/85

= 2.7 V

= 2.3 V

= 3.6 V

= 2.7 V

= 2.3 V

= 3.6 V

VDD -

0.15

−

−

−

− −

− −

−

−

−

−

−

0.4 V

−

− −

15 25

10 15

7 12

0.5 mA

1 10

0.8

0.5

5 80

1

5

5

3

µA

V

mA

µA

Capacitance (Ta = 25°C; f = 1 MHz)

Parameter Symbol Min Typ Max Unit Test Conditions

Input capacitance CIN

Output capacitance C

Notes:

This parameter is periodically sampled and is not 100% tested.

OUT

− −

− −

10 pF VIN = GND

10 pF V

OUT

= GND

Preliminary

4 Rev 1.0

May 2001

Page 5

EtronTech

EM564166

AC Characteristics and Operating Conditions (Ta = -40°C to 85°C, VDD = 2.3V to 3.6V)

Read Cycle

EM564166

-85 -70

Min Max Min Max

70

−

85

−

−

−

−

−

85

45

45

−

−

−

35

−

−

−

−

10

3

5

−

Symbol Parameter

tRC Read cycle time 85

tAA Address access time

t

Chip Enable (CE#) Access Time

CO1

tOE Output enable access time

tBA Data Byte Control Access Time

tLZ Chip Enable Low to Output in Low-Z 10

t

Output enable Low to Output in Low-Z 3

OLZ

t

Data Byte Control Low to Output in Low-Z 5

BLZ

tHZ Chip Enable High to Output in High-Z

Unit

−

70

70

35

35

−

ns

−

−

25

t

Output Enable High to Output in High-Z

OHZ

t

Data Byte Control High to Output in High-Z

BHZ

tOH Output Data Hold Time 10

Write Cycle

Symbol Parameter

tWC Write cycle time 85

tWP Write pulse width 55

tCW Chip Enable to end of write 70

tBW Data Byte Control to end of Write 70

tAS Address setup time 0

tWR Write Recovery time 0

t

WE# Low to Output in High-Z

WHZ

tOW WE# High to Output in Low-Z 5

tDS Data Setup Time 35

35

−

35

−

−

EM564166

-85 -70

Min Max Min Max

−

−

−

−

−

−

35

−

−

−

−

−

10

70

55

60

60

0

0

−

5

30

25

25

−

−

−

−

−

−

−

30

−

−

Unit

ns

tDH Data Hold Time 0

AC Test Condition

Output load : 50pF + one TTL gate

•

Input pulse level : 0.4V, 2.4V

•

Timing measurements : 0.5 x VDD

•

tR, tF : 5ns

•

Preliminary

5 Rev 1.0

−

0

−

May 2001

Page 6

EtronTech

Read Cycle

(See Note 1)

t

RC

Address

EM564166

CE#

OE #

t

OHZ

t

HZ

t

OH

t

AA

t

CO1

t

OE

t

BA

UB# LB#

,

D

OUT

Preliminary

t

BLZ

t

OLZ

t

LZ

VALID DATA OU T

t

BHZ

6 Rev 1.0

May 2001

Page 7

EtronTech

Write Cycle1

(WE# Controlled)(See Note 4)

t

WC

Address

EM564166

WE#

CE#

UB# LB#

,

D

OUT

t

AS

t

WHZ

(See Note2) (See Note3)

t

t

CW

BW

t

WP

t

WR

t

OW

D

IN

Preliminary

(See Note 5)

t

DS

VALID DATA IN (See Note 5)

t

DH

7 Rev 1.0

May 2001

Page 8

EtronTech

Write Cycle 2

(CE# Controlled)(See Note 4)

t

WC

Address

EM564166

WE#

CE#

UB# LB#

,

D

OUT

t

AS

t

BLZ

t

LZ

t

WHZ

t

t

CW

BW

t

W P

t

DS

t

t

WR

DH

D

IN

Preliminary

(See Note 5) VALID DATA IN

8 Rev 1.0

May 2001

Page 9

EtronTech

Write Cycle3

(UB#, LB# Controlled)(See Note 4)

t

WC

Address

EM564166

WE#

CE#

UB# LB#

,

D

OUT

t

AS

t

BLZ

t

LZ

t

WHZ

t

t

CW

BW

t

W P

t

DS

t

t

WR

DH

D

IN

(See Note 5) VALID DATA IN

Note:

1. WE# remains HIGH for the read cycle.

2. If CE# goes LOW with or after WE# goes LOW, the outputs will remain at high impedance.

3. If CE# goes HIGH coincident with or before WE# goes HIGH, the outputs will remain at high impedance.

4. If OE# is HIGH during the write cycle, the outputs will remain at high impedance.

5. Because I/O signals may be in the output state at this time, input signals of reverse polarity must not be

applied.

Preliminary

9 Rev 1.0

May 2001

Page 10

EtronTech

Data Retention Characteristics (Ta = -40°C to 85°C)

EM564166

Symbol

VDR

IDR Data Retention Current

t

SDR

t

RDR

Data Retention Supply

Voltage

Chip Deselect to Data Retention Mode Time

Recovery Time

CE# Controlled Data Retention Mode

V

DD

2.7V

2.2V

V

DR

CE #

Parameter Min Typ Max Unit

CE# ≥ V

VIN ≥ V

VDD = 1.0V, CE# ≥ V

VIN ≥ V

t

SDR

- 0.2V,

DD

- 0.2V or VIN ≤ 0.2V

DD

- 0.2V,

DD

- 0.2V or VIN ≤ 0.2V

DD

Data Retention Mode

Note 1

1.0

−

0

tRC

t

RDR

3.6

−

0.5 3.5

− −

− −

V

µA

ns

ns

GND

Note:

1. CE# ≥ VDD – 0.2V or UB# = LB# ≥ VDD – 0.2V

Preliminary

10 Rev 1.0

May 2001

Page 11

EtronTech

Package Diagrams

48-Ball (6mm x 8mm) BGA

Units in mm

TOP VIEW

BOTTOM VIEW

EM564166

PIN 1 CORNER

1 2 3 4 5 6

0.10SS C

0.25

0.30 0.05(48X)

6 5 4 3 2 1

PIN 1 CORNER

C A B

- B -

0.75

3.75

- A -

0.20(4X)

0.10

- C - SEATING PLANE

Preliminary

11 Rev 1.0

May 2001

Loading...

Loading...