CTLST CAT28C256PI-12T, CAT28C256PA-15T, CAT28C256PA-12T, CAT28C256P-12T, CAT28C256NI-15T Datasheet

...

CAT28C256

32K-Bit Parallel E2PROM

FEATURES

■ Fast Read Access Times: 120/150ns

■ Low Power CMOS Dissipation:

–Active: 25 mA Max.

–Standby: 150 µA Max.

■ Simple Write Operation:

–On-Chip Address and Data Latches

–Self-Timed Write Cycle with Auto-Clear

■ Fast Write Cycle Time:

–5ms Max

■ CMOS and TTL Compatible I/O

DESCRIPTION

The CAT28C256 is a fast, low power, 5V-only CMOS

parallel E2PROM organized as 32K x 8-bits. It requires a

simple interface for in-system programming. On-chip

address and data latches, self-timed write cycle with autoclear and VCC power up/down write protection eliminate

additional timing and protection hardware. DATA Polling

and Toggle status bits signal the start and end of the selftimed write cycle. Additionally, the CAT28C256 features

hardware and software write protection.

■ Hardware and Software Write Protection

■ Automatic Page Write Operation:

–1 to 64 Bytes in 5ms

–Page Load Timer

■ End of Write Detection:

–Toggle Bit

–DATA Polling

■ 100,000 Program/Erase Cycles

■ 100 Year Data Retention

■ Commerical, Industrial and Automotive

Temperature Ranges

The CAT28C256 is manufactured using Catalyst’s advanced CMOS floating gate technology. It is designed to

endure 100,000 program/erase cycles and has a data

retention of 100 years. The device is available in JEDEC

approved 28-pin DIP, 28-pin TSOP or 32-pin PLCC

packages.

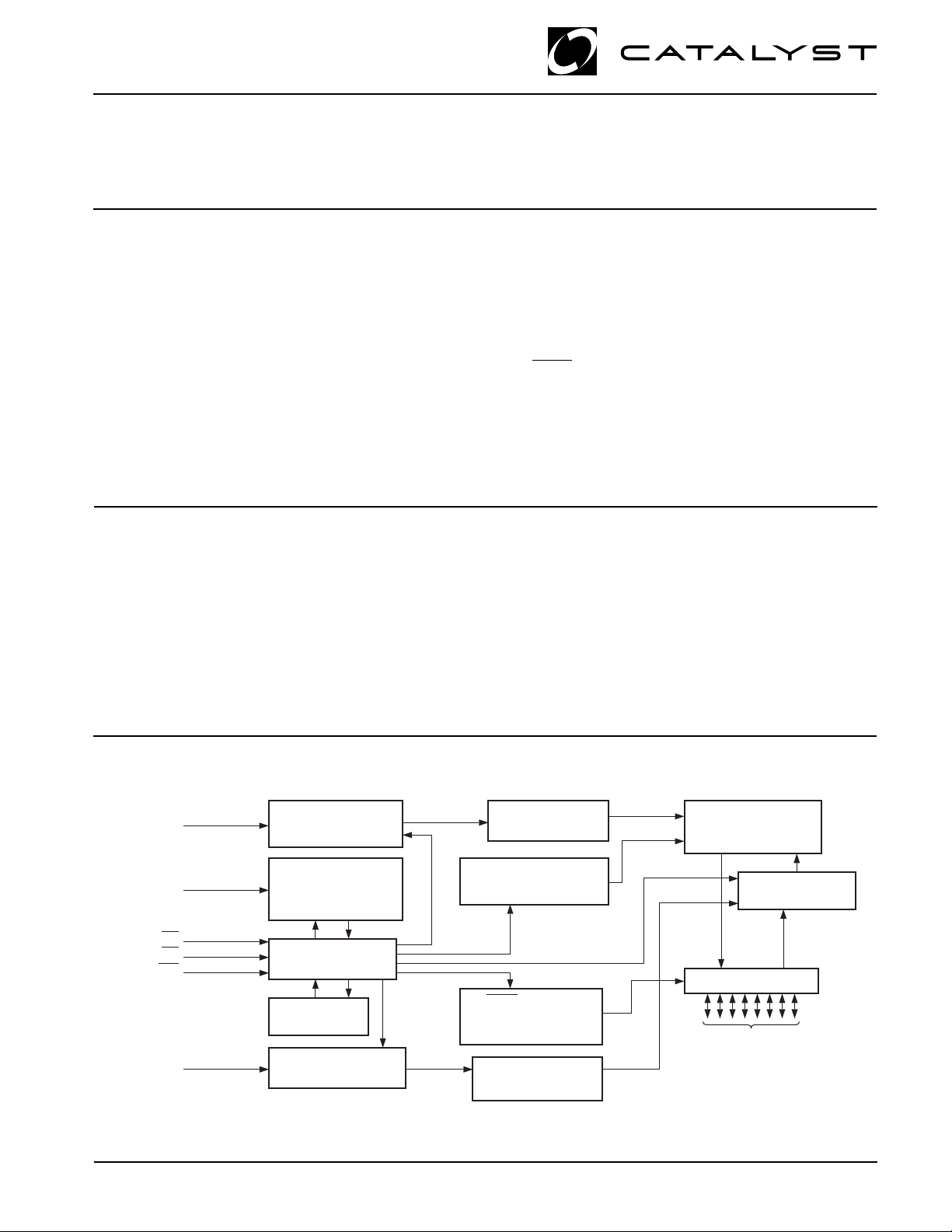

BLOCK DIAGRAM

A6–A

14

V

CC

CE

OE

WE

A0–A

5

© 1998 by Catalyst Semiconductor, Inc.

Characteristics subject to change without notice

ADDR. BUFFER

& LATCHES

INADVERTENT

WRITE

PROTECTION

CONTROL

LOGIC

TIMER

ADDR. BUFFER

& LATCHES

ROW

DECODER

HIGH VOL TAGE

GENERAT OR

DATA POLLING

AND

TOGGLE BIT

COLUMN

DECODER

1

32,768 x 8

2

PROM

E

ARRAY

64 BYTE PAGE

REGISTER

I/O BUFFERS

I/O0–I/O

7

Doc. No. 25020-0A 2/98

5096 FHD F02

CAT28C256

PIN CONFIGURATION

PLCC Package (N)DIP Package (P)

V

A

A

OE

A

11

A

A

A

13

WE

CC

14

12

A

A

A

A

A

14

12

A

A

A

A

A

A

A

A

1

28

2

27

3

7

6

5

4

3

2

1

0

0

1

2

26

4

25

24

5

23

6

22

7

21

8

20

9

19

10

18

11

17

12

13

16

14

15

TSOP Package (8mm X 13.4mm) (T13)

V

CC

WE

A

13

A

8

A

9

A

11

OE

A

10

CE

I/O

I/O

I/O

I/O

I/O

A7A12A14NC

4321323130

A

A

A

A

A

A

A

7

NC

6

I/O

5

4

3

5

6

6

5

7

4

8

3

9

2

10

1

11

0

12

13

0

14 15 16 17 18 19 20

2

SS

I/O1I/O

NC

V

A

A

I/O

I/O

I/O

V

SS

1

2

9

8

3

4

5

6

7

8

9

7

6

5

4

3

10

11

12

13

14

13

VCCWE

A

29

28

27

26

25

24

23

22

21

5

I/O3I/O4I/O

28

27

26

25

24

23

22

21

20

19

18

17

16

15

A

8

A

9

A

11

NC

OE

A

10

CE

I/O

7

I/O

6

5096 FHD F01

A

CE

I/O

I/O

I/O

I/O

I/O

GND

I/O

I/O

I/O

A

A

A

10

7

6

5

4

3

2

1

0

0

1

2

PIN FUNCTIONS

Pin Name Function

A0–A

14

I/O0–I/O

7

Address Inputs

Data Inputs/Outputs

CE Chip Enable

OE Output Enable

Doc. No. 25020-0A 2/98

Pin Name Function

WE Write Enable

V

V

CC

SS

5V Supply

Ground

NC No Connect

2

28C256 F03

CAT28C256

ABSOLUTE MAXIMUM RATINGS*

Temperature Under Bias ................. –55°C to +125°C

Storage Temperature....................... –65°C to +150°C

Voltage on Any Pin with

Respect to Ground

VCC with Respect to Ground ............... –2.0V to +7.0V

Package Power Dissipation

Capability (Ta = 25°C)................................... 1.0W

(2)

........... –2.0V to +VCC + 2.0V

*COMMENT

Stresses above those listed under “Absolute Maximum

Ratings” may cause permanent damage to the device.

These are stress ratings only, and functional operation

of the device at these or any other conditions outside of

those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum

rating for extended periods may affect device performance and reliability.

Lead Soldering Temperature (10 secs) ............ 300°C

Output Short Circuit Current

(3)

........................ 100 mA

RELIABILITY CHARACTERISTICS

Symbol Parameter Min. Max. Units Test Method

N

T

V

I

LTH

END

DR

ZAP

(1)

(1)

(1)

(1)(4)

Endurance 104 or 10

Data Retention 100 Years MIL-STD-883, Test Method 1008

ESD Susceptibility 2000 Volts MIL-STD-883, Test Method 3015

Latch-Up 100 mA JEDEC Standard 17

5

Cycles/Byte MIL-STD-883, Test Method 1033

D.C. OPERATING CHARACTERISTICS

VCC = 5V ±10%, unless otherwise specified.

Limits

Symbol Parameter Min. Typ. Max. Units Test Conditions

I

CC

VCC Current (Operating, TTL) 30 mA CE = OE = VIL, f=8MH

z

All I/O’s Open

(5)

I

CCC

VCC Current (Operating, CMOS) 25 mA CE = OE = V

, f=8MH

ILC

z

All I/O’s Open

I

SB

I

SBC

(6)

VCC Current (Standby, TTL) 1 mA CE = VIH, All I/O’s Open

VCC Current (Standby, CMOS) 150 µA CE = V

IHC

,

All I/O’s Open

I

LI

I

LO

(6)

V

IH

(5)

V

IL

V

OH

V

OL

V

WI

Note:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

(2) The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DC

voltage on output pins is VCC +0.5V, which may overshoot to VCC +2.0V for periods of less than 20 ns.

(3) Output shorted for no more than one second. No more than one output shorted at a time.

(4) Latch-up protection is provided for stresses up to 100mA on address and data pins from –1V to VCC +1V.

(5) V

(6) V

= –0.3V to +0.3V.

ILC

= VCC –0.3V to VCC +0.3V.

IHC

Input Leakage Current –10 10 µAVIN = GND to V

Output Leakage Current –10 10 µAV

= GND to VCC,

OUT

CE = V

IH

High Level Input Voltage 2 VCC +0.3 V

Low Level Input Voltage –0.3 0.8 V

High Level Output Voltage 2.4 V IOH = –400µA

Low Level Output Voltage 0.4 V IOL = 2.1mA

Write Inhibit Voltage 3.5 V

CC

3

Doc. No. 25020-0A 2/98

CAT28C256

MODE SELECTION

Mode CE WE OE I/O Power

Read L H L D

OUT

ACTIVE

Byte Write (WE Controlled) L H D

Byte Write (CE Controlled) L H D

IN

IN

ACTIVE

ACTIVE

Standby, and Write Inhibit H X X High-Z STANDBY

Read and Write Inhibit X H H High-Z ACTIVE

CAPACITANCE TA = 25°C, f = 1.0 MHz, VCC = 5V

Symbol Test Max. Units Conditions

(1)

C

I/O

(1)

C

IN

Input/Output Capacitance 10 pF V

I/O

= 0V

Input Capacitance 6 pF VIN = 0V

A.C. CHARACTERISTICS, Read Cycle

VCC=5V + 10%, Unless otherwise specified

28C256-12 28C256-15

Symbol Parameter Min. Max. Min. Max. Units

t

t

t

RC

CE

AA

Read Cycle Time 120 150 ns

CE Access Time 120 150 ns

Address Access Time 120 150 ns

t

OE

(1)

t

LZ

(1)

t

OLZ

(1)(2)

t

HZ

t

OHZ

(1)

t

OH

Note:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

(2) Output floating (High-Z) is defined as the state when the external data line is no longer driven by the output buffer.

OE Access Time 50 70 ns

CE Low to Active Output 0 0 ns

OE Low to Active Output 0 0 ns

CE High to High-Z Output 50 50 ns

(1)(2)

OE High to High-Z Output 50 50 ns

Output Hold from Address Change 0 0 ns

Doc. No. 25020-0A 2/98

4

A.C. CHARACTERISTICS, Write Cycle

VCC=5V+10%, unless otherwise specified

28C256-12 28C256-15

Symbol Parameter Min. Max. Min. Max. Units

CAT28C256

t

t

t

t

t

t

t

t

t

t

t

t

t

WC

AS

AH

CS

CH

CW

OES

OEH

WP

DS

DH

INIT

BLC

(3)

(3)

(1)

(1)(4)

Write Cycle Time 5 5 ms

Address Setup Time 0 0 ns

Address Hold Time 50 50 ns

CE Setup Time 0 0 ns

CE Hold Time 0 0 ns

CE Pulse Time 100 100 ns

OE Setup Time 0 0 ns

OE Hold Time 0 0 ns

WE Pulse Width 100 100 ns

Data Setup Time 50 50 ns

Data Hold Time 10 10 ns

Write Inhibit Period After Power-up 5 10 5 10 ms

Byte Load Cycle Time 0.1 100 0.1 100 µs

Figure 1. A.C. Testing Input/Output Waveform(2)

2.4 V

INPUT PULSE LEVELS REFERENCE POINTS

0.45 V

2.0 V

0.8 V

5096 FHD F03

Figure 2. A.C. Testing Load Circuit (example)

DEVICE

UNDER

TEST

Note:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

(2) Input rise and fall times (10% and 90%) < 10 ns.

(3) A write pulse of less than 20ns duration will not initiate a write cycle.

(4) A timer of duration t

however a transition from HIGH to LOW within t

max. begins with every LOW to HIGH transition of WE. If allowed to time out, a page or byte write will begin;

BLC

CL INCLUDES JIG CAPACITANCE

max. stops the timer.

BLC

1.3V

1N914

3.3K

OUT

CL = 100 pF

5

5096 FHD F04

Doc. No. 25020-0A 2/98

CAT28C256

DEVICE OPERATION

Read

Data stored in the CAT28C256 is transferred to the data

bus when WE is held high, and both OE and CE are

held low. The data bus is set to a high impedance state

when either CE or OE goes high. This 2-line control

architecture can be used to eliminate bus contention in

a system environment.

Figure 3. Read Cycle

t

RC

ADDRESS

t

CE

CE

t

OE

OE

V

IH

WE

DATA OUT DA TA V ALIDDA TA V ALID

HIGH-Z

t

LZ

t

OLZ

Byte Write

A write cycle is executed when both CE and WE are low,

and OE is high. Write cycles can be initiated using either

WE or CE, with the address input being latched on the

falling edge of WE or CE, whichever occurs last. Data,

conversely, is latched on the rising edge of WE or CE,

whichever occurs first. Once initiated, a byte write cycle

automatically erases the addressed byte and the new

data is written within 5 ms.

t

OHZ

t

OH

t

AA

t

HZ

28C256 F06

Figure 4. Byte Write Cycle [WE Controlled]

ADDRESS

CE

OE

WE

DATA OUT

DATA IN

t

AS

t

OES

t

CS

t

AH

t

WP

HIGH-Z

DATA VALID

t

DS

t

t

CH

DH

t

OEH

t

BLC

t

WC

5096 FHD F06

Doc. No. 25020-0A 2/98

6

CAT28C256

OE

CE

WE

ADDRESS

I/O

t

WP

t

BLC

BYTE 0 BYTE 1 BYTE 2 BYTE n BYTE n+1 BYTE n+2

LAST BYTE

t

WC

Page Write

The page write mode of the CAT28C256 (essentially an

extended BYTE WRITE mode) allows from 1 to 64 bytes

of data to be programmed within a single E2PROM write

cycle. This effectively reduces the byte-write time by a

factor of 64.

Following an initial WRITE operation (WE pulsed low, for

tWP, and then high) the page write mode can begin by

issuing sequential WE pulses, which load the address

and data bytes into a 64 byte temporary buffer. The page

address where data is to be written, specified by bits A

to A14, is latched on the last falling edge of WE. Each

byte within the page is defined by address bits A0 to A

Figure 5. Byte Write Cycle [CE Controlled]

ADDRESS

CE

t

AS

t

AH

t

CW

(which can be loaded in any order) during the first and

subsequent write cycles. Each successive byte load

cycle must begin within t

BLC MAX

of the rising edge of the

preceding WE pulse. There is no page write window

limitation as long as WE is pulsed low within t

Upon completion of the page write sequence, WE must

stay high a minimum of t

BLC MAX

for the internal automatic program cycle to commence. This programming

cycle consists of an erase cycle, which erases any data

that existed in each addressed cell, and a write cycle,

which writes new data back into the cell. A page write will

6

only write data to the locations that were addressed and

will not rewrite the entire page.

5

t

WC

t

BLC

t

OEH

BLC MAX

.

OE

t

WE

DATA OUT

DATA IN

t

CS

Figure 6. Page Mode Write Cycle

OES

HIGH-Z

DATA VALID

t

DS

t

CH

t

DH

5096 FHD F07

7

5096 FHD F10

Doc. No. 25020-0A 2/98

CAT28C256

DATA Polling

DATA polling is provided to indicate the completion of

write cycle. Once a byte write or page write cycle is

initiated, attempting to read the last byte written will

output the complement of that data on I/O7 (I/O0–I/O

are indeterminate) until the programming cycle is complete. Upon completion of the self-timed write cycle, all

I/O’s will output true data during a read cycle.

Figure 7. DATA Polling

ADDRESS

CE

WE

t

OEH

OE

Toggle Bit

In addition to the DATA Polling feature of the CAT28C256,

the device offers an additional method for determining

the completion of a write cycle. While a write cycle is in

progress, reading data from the device will result in I/O

6

toggling between one and zero. However, once the write

is complete, I/O6 stops toggling and valid data can be

read from the device.

t

t

OE

t

WC

OES

6

I/O

7

D

= X D

IN

Figure 8. Toggle Bit

WE

CE

t

OEH

OE

I/O

6

Note:

(1) Beginning and ending state of I/O6 is indeterminate.

(1)

t

OE

= X D

OUT

t

WC

OUT

(1)

= X

t

OES

28C256 F10

28C256 F11

Doc. No. 25020-0A 2/98

8

HARDWARE DATA PROTECTION

WRITE DATA: AA

ADDRESS: 5555

WRITE DATA: 55

ADDRESS: 2AAA

WRITE DATA: 80

ADDRESS: 5555

WRITE DATA: AA

ADDRESS: 5555

WRITE DATA: 55

ADDRESS: 2AAA

WRITE DATA: 20

ADDRESS: 5555

The following is a list of hardware data protection features that are incorporated into the CAT28C256.

(1) VCC sense provides for write protection when V

CC

falls below 3.5V min.

(2) A power on delay mechanism, t

(see AC charac-

INIT

teristics), provides a 5 to 10 ms delay before a write

sequence, after VCC has reached 3.5V min.

(3) Write inhibit is activated by holding any one of OE

low, CE high or WE high.

CAT28C256

(4) Noise pulses of less than 20 ns on the WE or CE

inputs will not result in a write cycle.

SOFTWARE DATA PROTECTION

The CAT28C256 features a software controlled data

protection scheme which, once enabled, requires a data

algorithm to be issued to the device before a write can be

performed. The device is shipped from Catalyst with the

software protection NOT ENABLED (the CAT28C256 is

in the standard operating mode).

Figure 9. Write Sequence for Activating Software

Data Protection

WRITE DATA: AA

ADDRESS: 5555

WRITE DATA: 55

ADDRESS: 2AAA

WRITE DATA: A0

ADDRESS: 5555

SOFTWARE DATA

PROTECTION ACTIVATED

WRITE DATA: XX

TO ANY ADDRESS

(12)

(1)

Figure 10. Write Sequence for Deactivating

Software Data Protection

Note:

(1) Write protection is activated at this point whether or not any more writes are completed. Writing to addresses must occur within t

Max., after SDP activation.

WRITE LAST BYTE

TO

LAST ADDRESS

5096 FHD F08 5096 FHD F09

BLC

9

Doc. No. 25020-0A 2/98

CAT28C256

To activate the software data protection, the device must

be sent three write commands to specific addresses with

specific data (Figure 9). This sequence of commands

(along with subsequent writes) must adhere to the page

write timing specifications (Figure 11). Once this is done,

all subsequent byte or page writes to the device must be

preceded by this same set of write commands. The data

protection mechanism is activated until a deactivate

sequence is issued regardless of power on/off transitions. This gives the user added inadvertent write protection on power-up in addition to the hardware protection provided.

Figure 11. Software Data Protection Timing

DATA

ADDRESS

CE

WE

AA

5555

55

2AAA

Figure 12. Resetting Software Data Protection Timing

To allow the user the ability to program the device with

an E2PROM programmer (or for testing purposes) there

is a software command sequence for deactivating the

data protection. The six step algorithm (Figure 10) will

reset the internal protection circuitry, and the device will

return to standard operating mode (Figure 12 provides

reset timing). After the sixth byte of this reset sequence

has been issued, standard byte or page writing can

commence.

t

A0

5555

t

WP

t

BLC

BYTE OR

PAGE

WRITES

ENABLED

WC

5096 FHD F13

DATA

ADDRESS

CE

WE

ORDERING INFORMATION

Prefix Device # Suffix

CAT

Optional

Company

ID

28C256

Product

Number

Endurance

Blank = 10,000 Cycle

H = 100,000 Cycle

AA

5555

55

2AAA

H

5555

NI T

AA

5555

55

2AAA

5555

Temperature Range

Blank = Commercial (0˚C to +70˚C)

20

t

WC80

-15

SDP

RESET

DEVICE

UNPROTECTED

5096 FHD F14

Tape & Reel

T: 500/Reel

I = Industrial (-40˚C to +85˚C)

A = Automotive (-40˚ to +105˚C)*

Package

P: PDIP

N: PLCC

Speed

12: 120ns

15: 150ns

T13: TSOP (8mmx13.4mm)

* -40˚C to +125˚C is available upon request

Notes:

(1) The device used in the above example is a CAT28C256HNI-15T (100,000 Cycle Endurance, PLCC, Industrial temperature, 150ns

Access Time, Tape & Reel).

Doc. No. 25020-0A 2/98

10

28C256 F16

Loading...

Loading...