Page 1

User's Guide

1

Mega-Post PCI-Diagnostic Card

User's Guide

Page 2

User's Guide

ansion slot. It is not necessary

l

2

INTRODUCTION

The Mega-Post PCI-Diagnostic Card is a powerful diagnostic tool for technicians and administrators to

troubleshoot various problems of IBM compatible PCs. It is easy to install, yet extremely powerful to use. With

Diagnostic Card in hand, you no longer have to go through tedious and time consuming process of

trying to figure out what is wrong with your PC hardware. The Mega-Post PCI-Diagnostic Card will tell you

exactly what is wrong with your PC in just seconds. It saves you time and money.

Our new and improved design of the Mega-Post PCI-Diagnostic Card can work with almost all

popular types of CPUs, Motherboards, and BIOSes..

Trademarks

The Mega-Post PCI-Diagnostic Card is a trademark of Handelsvertretung Ellerhorst with all rights reserved.

IBM PC, PCjr, IBM PC XT, IBM AT, and PS/2 are trademarks of international Business Machines Co., Inc.

Pentium is a trademark of Intel Corporation.

System Requirements

The Mega-Post PCI-Diagnostic Card itself only requires an empty PCI or ISA exp

to install memory chips to perform analysis. "POST Codes" can be displayed through the hexadecimal display

panel on the Diagnostic Card itself.

Tech Support

Tech Support 0049/(0)8766/9394-17

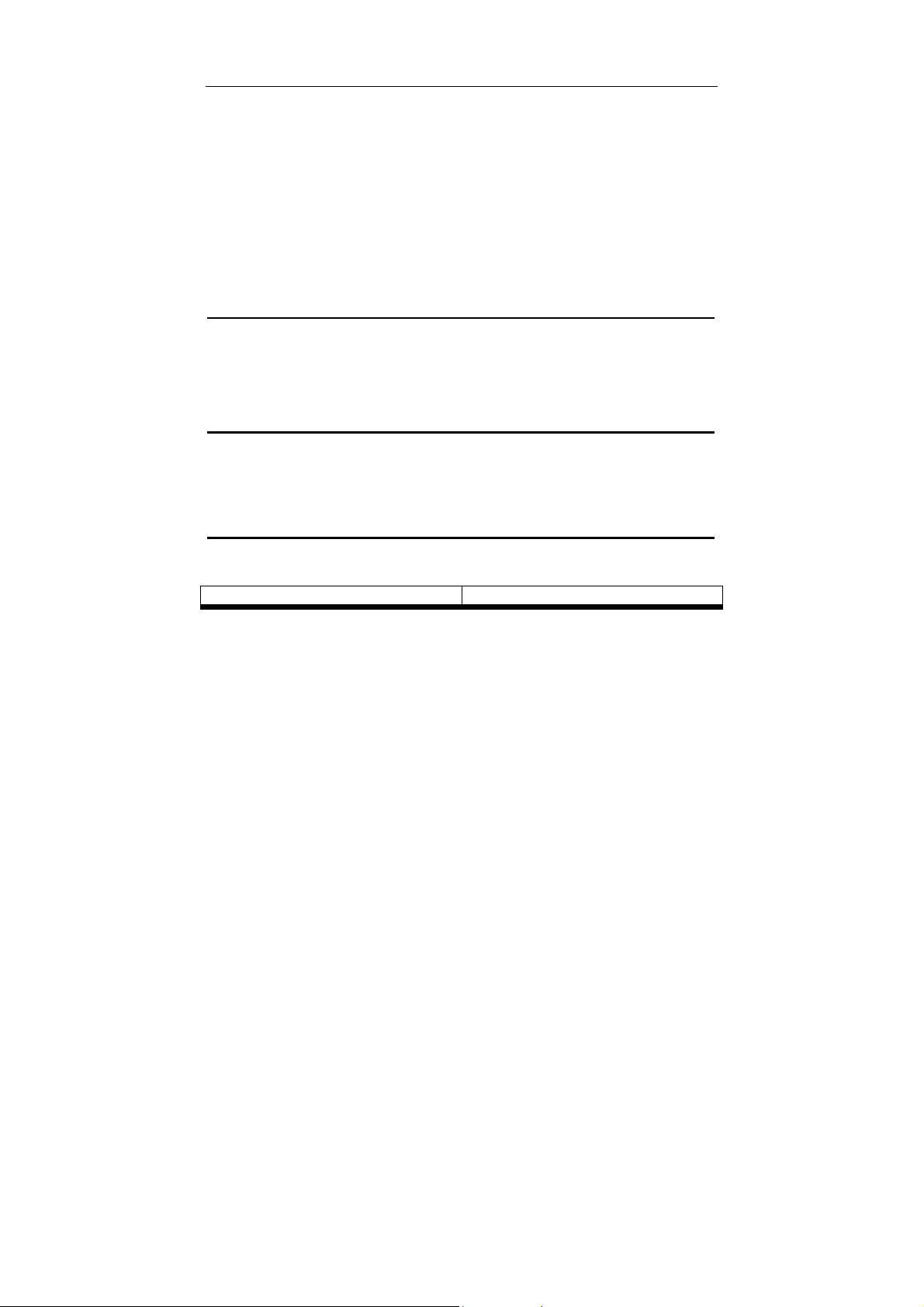

Mega-Post PCI-Diagnostic Card Indicators

'Indicators' are any light emitting diodes(LED) or hexadecimal display panel that may be

mounted on an Diagnostic Card. This section discusses the following indicators that appear on the Mega-Post

PCI-Diagnostic Card:

l Dual POST Code Display

l PCI BUS SIGNALS LEDs

POST Code Display

The POST Code Display is made up of a dual, dot matrix hexadecimal read-out that displays

Power On Self Test (POST) status codes.

Page 3

User's Guide

CLK

Motherboard Clock Signal.

2)

3)

4)

3

Power On Self-Test (POST) Codes

Most AT and 386 computers (and a few XT computers) output status codes during POST. The

Diagnostic Card displays these codes during and after POST. Refer to Appendix A for a comprehensive listing

of POST codes provided by BIOS manufacturers.

PCI Signal Definition:

Should be on when power is supplied to the

BIOS

IRDY

OSC

FRAME

RST

12V

-12V

5V

-5V

3V3

motherboard even without CPU.

BIOS Read Signal. Flashes when CPU reads BIOS code.

Device Ready. Flashes when an IRDY signal is detected.

ISA Oscillation Indicator. Indicate ISA Oscillation Signal is available.

PCI Bus Frame. Should be on under normal circumstances and flashes

when a PCI Frame Signal is detected.

Reset. After power on or reset, this indicator should be on for an half

second and then turned off.

Power Supply, 12-Volt Positive. Should be on all the time otherwise there

is a short circuit.

Power Supply, 12-Volt Negative. Should be on all the time otherwise there

is a short circuit.

Power Supply, 5-Volt Positive. Should be on all the time otherwise there is

a short circuit.

Power Supply, 5-Volt Negative. Should be on all the time otherwise there

is a short circuit.

Power Supply, 3.3-Volt. Some motherboards have 3.3V power supply to

PCI slots. This indicator should be on if the motherboard supplies 3.3V

power.

Installing the Mega-Post PCI-Diagnostic Card

Installation Procedure

TO INSTALL A Diagnostic Card:

1)

Install the Diagnostic Card in any available PCI or ISA expansion slot.

Connect the second display by flat cable

Connect the build-in speaker and motherboard with speaker cable

Power on the machine.

Page 4

User's Guide

When the machine is turned on, the hexadecimal display should show the various POST codes as

4

POST Codes

the system executes (unless it has a rare BIOS that does not display POST codes).

If the machine does not boot, system POST has detected a fatal fault and stopped. The number

showing in the hexadecimal display on the Diagnostic Card is the number of the test in which

POST failed. Refer to Appendix A for a listing of POST codes.

Troubleshooting During POST

After initial power up, Power-On Self-Test (POST) codes begin displaying on the Diagnostic

Card's hexadecimal displays (for most machines).

NOTE: A few machines use the parallel port to display POST codes instead of the Diagnostic

Card.

THE POST PROCESS

The ROM built onto the motherboard of the computer rums its built-in POST (Power-On Self-Test)

when you switch power on to the computer, press the reset button on the computer, or press Ctrl-Alt-Del (warm

boot). POST performs a tightly interwoven initialization and testing process

for each of these methods, but it typically does not test or initialize memory above 64K for warm

boot. You can get an even better idea of the detailed process by studying the POST code listings in

Appendix A.

Page 5

0.Initialize EISA registers(EISA)BIOS only).Clear 8042 keyboard controller.

AMI

Error Code

-

04

Erro

r Code

-

05

keyboard; Keyboard controller initialization. Initialize Chips; Disable

NMI,PIE,AIE,UEI, SQ

set(loop 1

-

5).

5

AMI

Award

Phoenix

AMI

AST

Award

Chips&Tech

Dell

Phoenix

Phoenix

AMI

AST

Award

Appendix A

(00)Going to give control to INT 19H boot loader.

(01)Processor register test about to start, and NMI to be disabled,286 reg. test about

to start.

(01)Processor test 1;Processor status(1FLAGS) verification; Tests the following processor

status flags carry, zero, sign, overflow. The BIOS will set each of these

flags, verify they are set then turn each flag off and verify it is off.

(01)[Beep]=none 80286 register test in -progress.

(02)NMI is disabled. Power on delay starting. Power on de- lay starting.286reg.

(02)Test CPU register.

(02)Processor test 2;Read/write/verify all CPU registers except SS,SP and BP with

data pattern FF&00.Determine status of manufacturing jumper.

(02)Test CPU register.

(02)[Beep]=1-1-3 CMOS write/read test .

(02)Verify real-mode operation(Beep)=1-1-1-3.CPU Flags test.

(02)[Beep]=1-1-3 CMOS write/read test in-progress or failure.

(03)Power on delay complete. To check soft reset/power-on. Any initialization

before keyboard BAT is in progress. ROM BIOS checksum(32K at F800:0) passed.

(03)Test 8042 keyboard controller reset.

(03)Initialize Chips; Disable NMI,PIE,AIE,UEI,SQWV, disable video, parity

checking, DMA; Reset math Coprocessor; Clear all page registers, CMOS shutdown byte;

Initialize timer 0,1 and 2 including set EISA timer to a known

state; Initialize DMA controllers 0 and 1; Initialize interrupt controller 0 and 1;Initialize EISA

extended registers. Calculate BIOS EPROM and sign-on message checksum; fail if not

Error Code-00

Error Code-01

Error Code - 02

Error Code - 03

Chips & Tech (03)ROM did not checksum.

Phoenix&Dell

AMI

AST

Award

Chips & Tech (04)DMA Controller failed.

Phoenix&Dell

AMI

AST

Chips & Tech (05)System timer bad.

Award

Phoenix&Dell (05)[Beep]=1-2-2 DMA initialization in-progress or failure.

(03)Disable Non-Maskable Interrupt(NMI).[Beep]=1-1-4 BIOS ROM checksum

in-progress or failure.

(04)Any initialization before keyboard BAT is complete. Reading keyboard SYS

bit, to check soft reset/power-on. Reading keyboard SYS bit, to check soft reset/power On.

Keyboard controller test with and without mouse passed. 8259 initialization OK.

(04)Low level keyboard communication, keyboard ID verification.

(04)Test memory refresh toggle; RAM must be periodically refreshed in order to

keep the memory from decaying. This function assures that the memory refresh

function is working properly. Test CMOS RAM I/O port interface and verify battery

power is available(bat. status=1).Reset 8042.

(04)Get the CPU type (Beep)=1-1-2-1.CPU register test. Programmable Interval

Timer test failure.

(05)Soft reset/power-on determined. Going to enable ROM. i.e. disable shadow

RAM/Cache if any. Going to enable ROM.i.e. disable shadow RAM/cache if any. Chipset

initialization over, DMA and interrupt controller disabled. CMOS pending interrupt disabled.

(05)Read keyboard input port.

(05)Keyboard controller self-test enable keyboard interface. Blank video, Initialize

processor; Clear all page registers,CMOS shutdown byte; Initialize timer 0,1 and 2 including

set EISA timer to a known state; Initialize DMA controllers 0 and 1;Initialize interrupt

controller 0 and 1; Initialize EISA extended Regis- ters.Get manufacturing status, reset if

- WV, disable video, parity checking, DMA; Reset math Co-

Page 6

Error Code

-

06

function is working properly. Initialize chips.

Appendix A

Phoenix&Dell (06)Initi

alize system hardware (Beep)=1

-1-2-

3.DMA page register write/read test

Error Code

-

07

Read/write/verify CPU registers.

Error Code

- 08

1Fh according to INT_TBL. Initialize CMOS timer.

verification in

-

progress or failure.

Award

Error Code

-

09

Check BIOS Checksum.

Phoenix&Dell (09)Set POST flay.(Beep)=1

-1-3-

2. 1st 64K RAM test in

-

progress.

Error Code

-

0A

controller.

(06)ROM is enabled. Calculating ROM BIOS checksum, and waiting for Keyboard

AMI

AST

Award

Chips & Tech (06)64K RAM Failed.

AMI

Award

Chips & Tech (07)64K RAM failed data test (Base Memory)

ACER (08)Shutdown 0.

AMI

Award

Chips & Tech (08)Interrupt Controller bad.

Phoenix&Dell (08)Initialize chipset registers with POST values. [Beep]= 1-3-1 RAM refresh

controller input buffer to be free. Calculating ROM BIOS checksum.. Video disabled and system timer test begin Video disabled and system timer counting

OK.

(06)Support chipset initialize.

(06)Test memory refresh toggle; RAM must be periodically refreshed in-order to

keep the memory from decaying. This function assures that the memory refresh

in-progress or fail.

(07)ROM BIOS checksum passed. CMOS shutdown register test to be done

next.ROM BIOS checksum passed, Keyboard controller I/B free. Going to issue the

BAT command to keyboard controller. Going to issue the BAT command to keyboard

controller.CH-2 of 8254 initialization half way.CH-2 of 8253 test OK

(07)Verifies CMOS's basis R/W functionality Test CMOS interface and battery

status; Verifies CMOS is working correctly, detects bad battery. Setup low memory;

Early chip set initialization; Memory presence test; OEM chip set routines; Clear

low 64K of memory; Test first 64K memory; clear lower 256K of memory, enable

parity checking and test parity in lower 256K; test lower 25 If the BIOS detects

error 2C,2E,or 30(base 512K RAM error),it displays 6K memory. Set up stack,beep.

(08)CMOS shutdown register test done. CMOS checksum calculation to be done

next. BAT command to keyboard controller is issued. Going to verify the BAT command.

Going to verify the BAT command. CH-2 of timer initialization over.

CH-2 delta count test OK

(08)Setup low memory; Early chip set initialization; Memory presence test; OEM

chip set routines; Clear low 64K of memory; Test first 64K memory; clear lower

256K of memory, enable parity checking and test parity in lower 256K; test lower

256K memory. Set up stack, beep. Setup interrupt vector table in lower 1K RAM

area; Initialize first 120 interrupt vectors with SPURIOUS_INT_HDLR and initialize INT 00h-

AMI

AST

Chips & Tech (09)Unexpected interrupt is occurring.

AMI

Award

Chips & Tech (0A)Timer cannot interrupt.

(09)CMOS checksum calculation is done, CMOS diag byte written. CMOS initialize to begin.

Keyboard controller BAT result verified. Keyboard command

byte to be written next.(09)Keyboard command byte to be written next. CH-1 of

timer initialization over. CH-1 delta count test OK.

(09)Verify BIOS ROM checksum, flush external cache.

(09)Program the configuration register of Cyrix CPU. OEM specific cache initialization., Early

Cache initialization; Cyrix CPU initialization; cache initialization. Test CMOS RAM

checksum; beep; also test extended storage of parameters in the motherboard chipset; if not

warm- booting; display the Test

CMOS RAM checksum message, if bad, or insert key pressed, load defaults if bad.

(0A)CMOS initialization done(if any). Keyboard command byte code is issued.

Going to write command byte data. Go- ing to write command byte data. CH-0 of

timer initialization over. CH-0 delta count test OK

(0A)Initialize the first 32 interrupt vectors. Initialize INTs 33 to 120.Early Power Management

initialization. Setup interrupt vector table in lower 1K RAM area; Initialize first 120 interrupt

vectors with SPURIOUS_INT_HDLR and initialize

INT 00h-1Fh according to INT_TBL. Initialize key- board; Detect type of keyboard

controller(optional 8242 or 8248, with Nedadon XOR gate control); Set NUM_LOCK status.

Reset keyboard test keyboard controller interface to verify it

returned AAH and responded to enable/disable commands, set keyboard buffer,

enable keyboard and keyboard interrupts for normal use, beep, halt .Initialize Video

6

Page 7

64K RAM chip or data line failure multi

-

bit.

Error Code

-

0B

BIOS Only). Test CMOS RAM checksum; beep; also test extended storage of parameters in the

find out type of video in use; Detect and initialize video adapter. 8254 timer, channel 0 test.

Phoenix&Dell (0B)Enable CPU Cable

-

Check CPU Jumpers. [Beep]=1

-3-

4 1st 64K RAM

Error Code

-

0C

NUM_LOCK status. Reset keyboard test keyboard controller interface

timer, channel 1 test.

1st 64K RAM address line failure.

Error Code

-

0D

(0D)(Beeps)=13 short,8254 timer register.

timer, channel 2 test.

AMI

Error Cod

e - 0E

Enable shadow according to setup. Test COMS

Shutdown byte.

AMI

Award

detect and initialization. Test Extended CMOS.

Error Code

-

10

Appendix A

Phoenix&Dell (0A)Initialize CPU registers. (Beep)=1-1-3-3. Perform BIOS checksum test. 1st

AMI

Award

Chips & Tech (0B)CPU protected mode.

AMI

Award

Chips & Tech (0C)DMA register failure.

Phoenix&Dell (0C)Initialize cache to initial POST value. Test DMA page registers. [Beep]=1-4-1

AMI

AST

Chips & Tech (0D) (Beeps)=14 short, Refresh failure.

Award

Phoenix&Dell (0D)[Beep]=1-4-2 1st 64K RAM parity test in progress or failure.

AST

Award

Chips & Tech (0E)(Beeps)=14 short, Keyboard controller failure.

Phoenix

AST

Chips & Tech (0F)(Beeps)=15 short, Protected mode failure.

Phoenix (0F)Initialize the local IDE

AMI

CMOS status register initialize done. Keyboard controller command byte is written.

Going to issue Pin-23,24 block- ing/ unblocking command. Going to issue pin-23,24 blocking/

nubolcking command. Refresh started. Parity status cleared

(0B)Verify the RTC time is valid or not. Detect bad battery. Read CMOS data into

BIOS stack area. Perform PnP initializations. Assign I/O & Memory for PCI devices (PCI

motherboard chipset; if not warm-booting, display the

Test CMOS RAM check- sum message, if bad, or insert key pressed, load defaults

if bad. Initialize video interface; Detect CPU clock; Read CMOS location 14b to

odd/even logic failure.

(0C)KB controller I/B free. Going to issue the BAT command to keyboard

controller. Pin-3,24 of keyboard controller is blocked/unblocked. NOP command of

key- board controller to be issued next. NOP command of key- board controller to

be issued next. System timer started. Refresh & system timer OK

(0C)Initialization of the BIOS data area(40:00-40:FF). Initialize keyboard; Detect

type of keyboard controller (optional 8242 or 8248, with Nedadon XOR gate control); Set

to verify it returned AAH and responded to enable/disable commands, set keyboard

buffer, enable keyboard and keyboard interrupts for normal use,beep,halt.8254

(0D)BAT command to keyboard controller is issued. Going to verify the BAT command. NOP

command processing is done. CMOS shutdown register test to be

done next. CMOS shutdown register test to be done next. Refresh link toggling

passed. Refresh link toggling passed.

(0D)Program some of the chipset's value. Measure CPU speed for display. Video

initialization including MDA, CGA,EGA/VGA. Initialize video interface; Detect

CPU clock; Read CMOS location 14b to find out type of video in use; Detect and initialize

video adapter. OEM specific-Initialize motherboard special chipset as

required by OEM; initialize cache controller early, when cache is separate from chipset.8254

(0E)(Beeps)=14 short, ASIC registers.

(0E)Keyboard controller BAT result verified. Any initialization after KB controller

BAT to be next. CMOS shutdown register R/W test passed. Going to calculate CMOS

checksum, and update DIAG. Goint to calculate CMOS checksum,and

update DIAG Byte. Refresh period ON/OFF 50% OK

(0E)Initialize the APIC(Multi-Processor BIOS only). Test video RAM(If Monochrome display

device found). Show startup screen message. Test video memory; Test video memory, write

sign-on message to screen. Setup shadow RAM-

(0E)Initialize I/O.(Beep)=1-1-4-3. Test 8254 timers.

(0F)initialization after KB controller BAT done. Keyboard command byte to be

written next. CMOS checksum calculation is done, DIAG byte written. CMOS Init.

To begin(If "INIT CMOS IN EVERY BOOT IS SET").CMOS initialization to begin(If "INIT

CMOS IN EVERY BOOT IS SET").

(0F)(Beeps)=15 short,CMOS RAM shutdown.

(0F)DMA channel 0 Test. Test DMA controller 0; BIOS checksum test, keyboard

(10)KB controller command byte is written. Going to issue pin-23,24

blocking/unblocking command. CMOS initia- lization done(if any). CMOS status

Error Code - 0F

7

Page 8

Compaq

(10)PPI disabled, Program timers 0 & 1.

Pho

enix&Dell (10)Initialize Power Management.(Beep)=1

-2-1-

1.Initia

-

Error Code

-

11

lize

Compaq

(11)Init(blast)VDU controllers.

Phoenix&Dell (11)Load alternate registers with POST values.(Beep)=1

-2-

2. 1st 64K RAM chip or

Error Code

-

12

Compaq

(12)Clear screen, turn on video.

0.(Beep)=1

-2-1-

3.Test both 8237 DMA controllers. 1st 64K RAM chip or data line

Error Code

-

13

Compaq

(13)Test timer 0.

Phoenix&Dell [Beep]=2

-1-

4 1st 64K RAM chi

p or data line failure

-

bit 3. Initialize PCI Bus

(14)DMA Controller.

Error Code

-

14

Compaq

(1

4)Disable RTC interrupts.

Phoenix&Dell (14)Initialize keyboard

blocking/unblocking command. CMOS initia- lization done(if any). CMOS status

register about to Init for Date and Time. CMOS status register about to Init for Date

and Time. Refresh on and about to start 64K base memory test. Confirmed refresh

ON & about to start 64K memory.

AST

Award

Chips & Tech (10)(Beeps)=19 short, IDT,GDT failure.

AMI

AST

Award

Chips & Tech (11)Register LDT failure.

AMI

AST

Award

Chips & Tech (12)Task register failure.

Phoenix&Dell (12)Restore CPU control word during warm boot. Jump to User Path

AMI

AST

Award

Chips & Tech (13)LSL instruction failure.

ACER

AMI

AST

Award

Chips & Tech (14)LAR failure.

AMI

Award

Compaq

(10)DMA controller test 0 register

(10)DMA channel 1 Test. Test DMA controller 1 with AA, 55,FF,00 pattern.8237

DMA,channel 0 test.

timers.[Beep]=2-1-1 1st 64K RAM chip or data line failure-bit 0.

(11)Pin23,24 of keyboard controller is blocked/unblocked. Going to check to check

pressing of <INS>key during power-on.CMOS status register initialized. Going to

disable DMA and Interrupt controllers. Going to disable DMA and interrupt controllers.

Address line test passed. Address line test passed.

(11)DMA controller test register 1.

(11)DMA page register test. Test DMA page registers, use I/O ports to test address

circuits. POST enables user reboot here. Test DMA page registers. FATAL DISPLAY ERRORS.8237 DMA, channel 1 test.

data line failure-bit 1.

(12)Checking for pressing of <INS>key during power-on done. Going to disable

DMA and Interrupt controllers.DMA controller#1,#2,interrupt controller#1,#2 disabled. About

to disable Video display and Init port-B. About to disable video display and Init port-B.64K

base memory test passed. 64K base memory test

passed.

(12)DMA page registers test.

(12)Call support 800-909-3424. Test 8254 timer 0 channel 0. Test DMA page

registers.

failure-bit 2.

(13)DMA controller#1,#2,interrupt controller#1,#2disa- bled. About to disable

Video display and initialize port-B. Chipset initialize/auto memory detection about

to begin. Replace first memory SIMM.(13)Chipset initialize/auto memory detection

about to begin. Check first SIMM.(13) Interrupt vectors initialized.

(13)Initialize video.

(13)Test 8254 timer 0 channel 1. Test keyboard controller.

Mastering devices.

(14)Chipset initialization/auto memory detection over. To un-compress the POST

code if compressed BIOS.8254 timer test about to start.8254 timer test about to start.8042

keyboard controller test OK.

(14)Memory refresh test.

(14)Test 8254 timer 0 counter 2. Test timer counter 2; Test 8254 timer 0 counter 2.

Test memory refresh.

controllers.[Beep]=2-2-1 1st 64K RAM chip or data line failure-bit 4.

(15)POST code is un-compressed.8254 timer about to start. CH-2 timer test

halfway.8254 CH-2 timer test to be complete.8254 CH-2 timer test to be completed. Interrupt

vectors initialized. CMOS read/write test OK.

(15)test 8259 interrupt mask bits for channel 1. Test 8259-1 mask bits; Verify 8259 channel 1

masked interrupt by alternate turning off and on the interrupt line. Test

1st 64K of system memory.

(15)Check battery power.

controller.(Beep)=1-2-2-1.Initialize 8237 DMA

Error Code - 15

8

Appendix A

8254

Page 9

Chips & Tech (15)VERW/VERR failure.

Phoenix&Dell (15)[Beep]=2

-2-

2 1st 64K RAM chip or data line failure

-

bit 5.

Compaq

Error Code

-

16

(16)Battery power was lost.

Phoenix&Dell (16)BIOS ROM checksum.(Beep)=1

-2-2-

3.

Error Code

-

17

Compaq

(17)Cler CMOS

-

DIAG

(18)Timer initialize.

Error Code

-

18

Compaq

(18)Test base memory(first 128K)

registers.[Beep]=2

-3-

1 1st 64K RAM chip or data line failure

-

bit 8.

Error Code

-

19

NMI can be cleared. 8259 Interrupt controller, channel 1 mask bits

(19)Clear and initialize base memory.

Compaq

(1A)Initialize and test VDU adapter

s.

occurring.[Beep]=2

-3-

3 1st 64K RAM chip or data line failure

-

bit A.

Error Code

-

1B

(1B)Test CMOS battery status. Test the system ROM.

Phoenix&Dell (1B)[Beep]=2

-4-

1 1st 64K RAM chip or data line failure

-

bit B.

Error Code

-

1C

Award

(1C)Test CMOS RAM checksum. Test CMOS.

Programmable Interr

upt Controller.(Beep)=1

-2 -4-

1.Base 64K address test.

Error Code

-

1D

(1D)Test DMA controller and page registers.

Appendix A

AMI

Award

Chips & Tech (16)Keyboard controller gate A20 failure.

AMI

Award

Phoenix&Dell (17)Initialize cache before memory auto-size.[Beep] =2-2-4 1st 64K RAM chip or

ACER

AMI

AST

Award

Dell

Chips & Tech (18)Shutdown during memory test.

Phoenix&Dell (18)8254 timer initialization.(Beep)=1-2-3-1. Test 8259 interrupt controllers

AMI

Award

Compaq

Phoenix&Dell (19)check memory[Beep]=2-3-2 1st 64K RAM chip or data line failure-bit 9.

AMI

Award

Chips & Tech (1A)Copyright checksum errors.

Phoenix&Dell (1A)8237 DMA controller initialization.(Beep)=1-2-3-3. Verify refresh is

(16)CH-2 timer test over.8254 CH-1 timer test to be complete. CMOS checksum/battery check

OK

(16)Test 8259-2 mask bits; Verify 8259 channel 2 masked interrupt by alternate

turning off and on the interrupt line. Setup Interrupt vectors.

Coprocessor.[Beep]=2-2-3 1st 64K RAM chip or data line failure-bit 6.

(17)CH-1 timer test over.8254 CH-0 timer test to be completed. Monochrome mode

set.

(17)Test struck 8259's interrupt bits; Turn off interrupt then verify no interrupt mask register is

on. Setup video I/O operations.

data line failure-bit 7.

Initialize 8259, reset

(18)CH-0 timer test over. About to start memory refresh. Color mode set.

(18)Testing Video memory.

(18)Test 8259 interrupt functionality; Force an interrupt and verify the interrupt occurred. Test

video memory.

(18)[Beep]= 2-3-1 1st 64K RAM chip or data line failure- bit 8

(19)82 timer test over. Memory refresh test to be done next. About to look for optional video

ROM at segment C000 and give control to the optional video ROM

if present.

(19)Test 8259 functionality. Test stuck NON-Maskable Interrupt bits(Parity/I/O check);Verify

test.

Error Code - 1A

(1A)Memory refresh line is toggling. Going to check 15 micro second ON/OFF

time. Return from optional video ROM. Optional video ROM control OK

(1A)Display CPU clock.8259 Interrupt controller, channel 2 mask bits test.

AMI

Award

Chips & Tech (1b)Shutdown during memory sizing.

ACER (1C)Memory refresh.

AMI

Chips & Tech (1C)Chip-Set initialization.

Phoenix&Dell (1C)[Beep]=2-4-1 1st 64K RAM chip or data line failure- bit C.Reset

AMI

Compaq

Phoenix&Dell (1D)[Beep]=2-4-2 1st 64K RAM chip or data line failure- bit D

(1B)Memory refresh period 30 micro second test complete. Base 64K memory test

about to start. Shadow RAM enable /disable completed. Display memory read/write

test OK.

(1C)Display memory read/write test for main display type as set in the CMOS setup

program over. Display memory read/write test for alternate display OK.

(1D)Display memory read/write test for alternate display type complete if main

display memory read/write test returns error. Video retrace check OK. Set configuration from

CMOS.

Error Code - 1E

9

Page 10

(1E)Test keyboard controller.

Compaq

Error Code

-

1F

Compaq

(1F)Test

286 protected mode.

Compaq

(20)Test real and extended memory.

refresh.(Beep)=1

-3-1-

1. Upper 16 of 32 bit test failed.

Compaq

(21)Init time

-of-

day.

Compaq

(22)Init 287 Coprocessor.

keyboard controller.(Beep)=1

- 3-1-3

Compaq

(23)Test keyboard and interface.

Compaq

Error Code

-

24

(25)Test diskette su

bsystem.

AMI Error Code

-

26

Appendix A

ACER

AMI

Award

Phoenix&Dell (1E)[Beep]=2-4-3 1st 64K RAM chip or data line failure- bit E.Base 64K RAM

AMI

Award

Phoenix&Dell (1F)[Beep]=2-4-4 1st 64K RAM chip or data line failure- bit F.

ACER

AMI

AST

Award

Phoenix&Dell (20)[Beep]=3-1-1 master DMA register test in-progress or failure. Test DRAM

AMI

Award

Phoenix&Dell (21)[Beep]=3-1-2 slave DMA register test in-progress or failure.

AMI

Award

Phoenix&Dell (22)[Beep]=3-1-3 master interrupt mask register test in- progress or fail. Test 8742

AMI

Award

Phoenix&Dell [Beep]=3-1-4 slave interrupt mask register test in-progress or fail.

ACER

AMI

Award

Compaq

Phoenix

AMI

Award

Phoenix&Dell (25)[Beep]=none interrupt vector loading in-progress.

AMI

Award

Compaq

Phoenix 6.0

(1E)Select memory type.

(1E)Global equipment byte set for proper display type.

(1E)If EISA NVM checksum is good, execute EISA initialization(EISA BIOS ONLY). Size

system memory.

test(16 bits).

(1F)Video mode set call for mono/color begins. Mode set call for mono/color OK.

Set EISA mode; If EISA non- volatile memory checksum is good, execute EISA initialization.

If not, execute ISA test an clear EISA mode flag. Test EISA configuration memory

integrity(checksum & comm.- unication interface).

(1F)Test system memory.

Error Code - 20

(20)Test 128K.

(20)Memory refresh period 30 micro second test complete. Base 64K memory/address test

started. Address line test to be done next. Video mode set

completed.

(20)Power up bus board(EISA only).

(20)Enable slot 0;Initialize slot 0(system board).(Check memory size).8259 stuck

bits test.

Error Code - 21

(21)Address line test passed. Going to do toggle parity. (21)ROM type 27256 verified. Video

display OK.

(21)Enable slots 1 through 15;Initialize slot 1.Test stuck NMI bits (parity I/O

check).

Error Code - 22

(22)Toggle parity over. Going for sequential data R/W test on 64K memory. Power

on message display OK.

(22)Enable slots 2; Initialize slot 2.Test 8259 working.

Error Code - 23

(23)Base 64K sequential data R/W test passed. Going to SET BIOS stack and to do

any setup before Interrupt vector Init. Any setup before interrupt vector Init about to

start. Power on message displayed.

(23)Enable slots 3;Initialize slot 3.Test protected mode.

(24)Test keyboard controller(8042).

(24)Setup required before vector initialization complete. Interrupt vector initialization about to

begin.

(24)Enable slots 4;Initialize slot 4.Size extended memory.

(24)reset A20 ads set default CPU speed.

(24)Set ES segment to register to 4 GB.(beep)=1-3-2-1. Verify CMOS/Configure

CMOS.

(25)Interrupt vector initialization done. Going to read Input port of 9042 for turbo

switch(if any).Going to read I/O port of 8042 for turbo switch(if any).

(25)Enable slots 5;Initialize slot 5.Test extended memory.

(26)I/O port of 8042 is read. Going to initialize global data for turbo switch. Going

to initialize global data for turbo switch.

(26)Enable slots 6;Initialize slot 6.Test protected mode exceptions.

(26)Test fixed disk subsystem.

(26)Enable A20 line. Verify/Load NVRAM parameters.

(27)Global data initialization for turbo switch is over. Any initialization before

setting video mode to be done next.

Error Code - 25

Error Code - 27

10

Page 11

Compaq

(27)initialize parallel printer.

Appendix A

Error Code

-

28

Compaq

(28)Perform search for option ROMs

DRAM.(Beep)=1

-3-3-

1.Protected mode 1.

Compaq

Error Code

-

29

(29)Test for valid system configuration.

Error Code

-

2A

Compaq

(2B)

Check for invalid time and date.

Phoenix

Award

Error Code

-

2C

(2D)Enable slots D; Initialize slot D. Detect & initialize parallel

ports. Test timer 2.

AST Error Code

-

2E

setting video mode to be done next.

Award

Phoenix&Dell (27)[Beep]=3-2-4 keyboard controller test in-progress or failure.

ACER (28)Test CPU.

AMI

Award

Phoenix&Dell (28)[Beep]=3-3-1 CMOS power-fail and checksum checks in-progress. Auto-size

(27)Enable slots 7; Initialize slot 7.Setup cache control or shadow RAM.

(28)initialization before setting video mode is complete. Going for monochrome

mode and color setting .Check extended memory.

(28)Enable slots 8;Initialize slot 8. Setup 8242.

AMI

Award

Phoenix&Dell (29)[Beep]=3-3-2 CMOS configuration info validation in- progress. Initialize POST

AMI

Award

Compaq

Phoenix

AMI

Award

Phoenix&Dell (2B)[Beep]=3-3-4 screen memory test in-progress or failure.

ACER

AMI

Award

Compaq

Dell

AMI

Phoenix& Dell (2D)[Beep]=3-4-2 screen retrace tests in-progress or failure.

AMI

Award

Dell

Phoenix

AMI

Award

Compaq

Phoenix

ACER

AMI

(29)Monochrome mode setting is done. Going for color mode setting.

(29)Enable slots 9;Initialize slot 9.

Memory Manager.

(2A)monochrome Color mode setting is done. About to go for toggle parity before

optional rom test. About to go for toggle parity before optional ROM Check.

(2A)Enable slots A; Initialize slot A.(2A)8242 initialization.

(2A)Clear screen.

(2A)Clear 512K base RAM.(Beep)=1-3-3-3.Aubo-site me- mory chips.

Error Code - 2B

(2B)Toggle parity over. About to give control for any setup required before optional

video ROM check.

(2B)Enable slots B; Initialize slot B. Initialize floppy drive and controller.

(2C)Set up interrupt controller(8259).

(2C)Processing before video ROM control is done. About to look for optional video

ROM and give control.

(2C)Enable slots C;Initialize slot C.Detect & initialize serial ports.

(2C)Boot.

(2C)[Beep]=3-4-1 screen initialization in-progress or failure.

(2C)RAM failure on address xxxx.If the BIOS detects error 2C,2E,or 30(base 512K

RAM error),it displays and additional word-bitmap(xxxx)indication the address line

or bits that failed. For example, "2C 0002"means address line 1 (bit one set) has

failed. "2E 1020 means data bits 12 and 5 (bits 12 and 5 set) have failed in the

lower 16 bits. Note that error 30 cannot occur on 386SX systems because they have

a 16 rather than 32-bit bus. The BIOS also sends the bitmap to the port-80 LED display. It first

display the check point code, followed by a delay, the high-order

byte, another delay, and then the low-order byte of the error. It repeats this sequence

continuously. Test 512 base address lines.(Beep)= 1-3-4-1 Activate interleave(if

possible).[Beep]3-4-1 screen initialization in-progress or failure.

(2D)Optional video ROM control is done. About to give control to do any processing after

video ROM returns control.

(2E)Return from processing after the video ROM control. If EGA/VGA not found

then do display memory R/W test.

(2E)Enable slots E; Initialize slot E. Initialize hard drive & controller.

(2E)[Beep]=3-4-3 search for video ROM in-progress.

(2E)See Error code "2C".Test 512K base memory.(Beep)= 1-3-4-3.Exit 1st protected mode

test.[Beep]=none search for video ROM in-progress.

(2F)EGA/VGA not found. Display memory R/W test about to begin.

(2F)Enable slots F; Initialize slot F. Detect & initialize 80x87 Co-Processor.

(2F)Write to DIAG byte.

(2F)Enable cache before system BIOS shadow.

(30)Set up Temp. interrupt.

(30)display memory R/W test passed. About to look for the retrace checking.

Virtual mode memory test about to begin.

(30)Interrupt controller#1.

Error Code - 2D

Error Code - 2F

Error Code - 30

11

Page 12

Compaq

(31)Load interrupt vectors 70

-

77.

Award

Phoenix

Compaq

Error Code

-

32

(33)Initialize Memory SIZE and RESETWD.

Error Code

-

34

Compaq

(34)Verify CMOS checksum.

Error Code

-

35

Compaq

(35)CMOS checksum not valid.

Compaq

Error Code

-

36

(36)Check battery power.

Error Code

-

37

Compaq

(37)Check for game adapters.

(38)CMOS RAM.

Error Code

-

38

Compaq

(38)Check for serial ports.

Appendix A

Award

Compaq

Dell

Phoenix

AMI

AST

Award

Phoenix&Dell (31)[Beep]=none monochromatic screen believed operable.

AMI

AST

Compaq

Dell

AMI

AST

Award

Phoenix&Dell (33)[Beep]=none 80-column color screen believed operable. Initialize dispatch

ACER

AMI

Phoenix&Dell (34)[Beep]=4-2-1 timer tick interrupt test in progress or failure. Relocate memory

AMI

Phoenix&Dell (35)[Beep]=4-2-2 shutdown test in progress or failure.

AMI

Phoenix&Dell (36)[Beep]=4-2-3 gate A20 failure. Warm start shut down. Configure EMS memory

AMI

Phoenix&Dell (37)[Beep]=1-4-2-4 unexpected interrupt in protected mode. Reinitialize the

ACER

AMI

Phoenix&Dell (38)[Beep]=4-3-1 RAM test in progress or failure above address 0FFFFh

Phoenix

(30)Get base memory & extended memory size. Size base And extended memory

from 256K to 640K and extended memory above 1MB.

(30)Clear 1st 128K bytes of RAM.

(30)[beep]=none screen believed running w/video ROM.

(30)see Error Code "2C".Unexpected shutdown.[Beep]=no- ne screen believed operable.

[Beep]=none screen believed running w/video ROM.

(31)Display memory R/W test or retrace checking failed. About to do alternate

Display memory R/W test. Virtual mode memory test started.

(31)Interrupt controller#2.

(31)Test base and extended memory; Test base memory from 256K to 640K and extended

memory above 1MB using various patterns. Detect & initialize optional

ROMs.

(32)Alternate display memory R/W test passed. About to look for the alternate

display retrace checking. Processor executing in virtual mode.

(32)Interrupt controllers for stuck interrupt.

(32)Display the Award Plug & Play BIOS extension message(PnP BIOS only).Test

EISA extended memory; If EISA mode flag is set then test EISA memory found in

slots initialization, This test is skipped in ISA mode and can be skipped with ESC

key in EISA mode.

(32)Load interrupt vectors 00-1F.

(32)[Beep]=none 40-column color screen believed operable.

(32)Test CPU bus-clock frequency.(Beep)=1-4-1-3.Deter- mine system board memory size.

[Beep]=none 40-column color screen believed operable.

(33)Video display checking over. Verification of display type with switch setting

and actual card to begin. Verification of display type with switch setting and Actual

Card to begin. Memory address line test in progress.

(33)Non-maskable interrupt for stuck interrupt(EISA,P486, P386)

(33)Call Tech Support 727-532-4151.

Manager.

(34)Set up BIOS interrupt vector.

(34)Verification of display adapter done. Display mode to be set next. Memory

address line test in progress.

option.

(35)Display mode set complete. BIOS ROM data area about to be checked.

Memory below 1MB calculated.

(36)BIOS ROM data area check over. Going to set cursor for power on message. Memory

above 1MB calculated.

option.

(37)Cursor setting for power on message id complete. Going to display the power

on message. Memory test about to start.

motherboard chipset.

Error Code - 31

Error Code - 33

(38)Power on message display complete. Going to read new cursor position.

Memory below 1MB initialized.

(38)Shadow system BIOS ROM.(Beep)=1-4-3-1.Configure wait state option.

Error Code - 39

12

Page 13

Compaq

(3A)Initialize Port. And comm. timeouts.

Compaq

(3B)Flush keyboard buffer.

Error Code

-

3C

Phoenix

speed.

Phoenix

Error Code

-

3D

(3D)Load alternate registers with CMOS values,(Beep)= 1

-4-4-

2

Phoenix 3.07

Error Code

-

3E

(3E)Get switches/jumper status from 8742.

ACER

Error Code

-

3F

in the EISA configuration.

(40)Shutdown#1.

Error Code

-

40

Initialize any serial and parallel ports (also game port).

(44)Video BIOS ROM initialize.

Error Code

-

44

AMI

Compaq

Phoenix

AMI

Award

Phoenix&Dell (3A)[Beep]=4-3-3 Interval timer channel 2 test in progress or failure.

Phoenix

AMI

Phoenix&Dell (3B)[Beep]=4-3-4 Time-Of-Day clock test in progress or failure.

ACER

AMI

Award

Phoenix&Dell (3C)[Beep]=4-4-2 Serial port test in progress or failure.

AMI

Award

Phoenix&Dell (3D)[Beep]=4-4-2 Parallel port test in progress or failure.

AMI

Award

Phoenix&Dell (3E)[Beep]=4-4-3 Math CoProcessor test in progress or failure.

AMI

Award

Dell

ACER

AMI

AST

Award

Compaq

Phoenix

AMI

AST

Award

Compaq

AMI

AST

Award

Compaq

Phoenix

AMI

Award

Compaq

(39)New cursor position read and saved. Going go display the Hit<DEL>message.

Memory above 1MB initialized.

(39)Check for parallel ports.

(39)Reinitialize the cache.(Beep)=1-4-3-1

(3A)Check memory, first 64K,one long beep. Reference string display is over.

Going to display the Hit<ESC> massage. Memory size display initiated. This will

be updated when the BIOS goes through the memory.

(3A)Check memory.

(3A)Auto-size cache.(Beep)=1-4-3-3.Retest 64K base RA M.

(3b)Hit<DEL>or<ESC>message displayed. Virtual mode memory test about to

start, About to start below 1MB memory test.

(3C)Memory size.

(3C)Memory test below 1MB completed and about to start above 1MB test.

(3C)Set flag to allow users to enter CMOS setup utility. Setup enabled.

(3C)Configure advanced chipset registers.(Beep)=1-4-4-1. Determine relative CPU

(3D)Memory test above 1MB completed.

(3D)Initialize keyboard. Install PS/2 mouse. Initialize & install mouse; Detect if

mouse is present, initialize mouse, install interrupt vectors.

(3E)About to go to real mode(shutdown).

(3E)Try to turn on level 2 cache.,

(3F)Shutdown successful and Processor in real mode.

(3F)Enable shadow RAM per CMOS RAM setup or if ME- MORY TYPE is SYS

(3F)Cache memory failure.

Error Code - 3A

Error Code - 3B

(40)Preparation for virtual mode test started. Going to verify from video memory.

CACHE memory on and about to disable A20 address line.

(40)CMOS RAM backup battery.

(40)Display virus protest disable or enable.

(40)Save RESET WD value.

(40)Set initial CPU speed.(Beep)=2-1-1-1.

(41)Returned after verifying from display memory. Going to prepare the descriptor bables.A20

address line disabled successful.

(41)CMOS RAM checksum.

(41)Initialize floppy disk drive controller.

(41)Check RAM refresh.

(42)descriptor tables prepared. Going to enter in virtual mode for memory test.486

internal cache turned on. About to start DMA controller test.

(42)Setup CMOS RAM.

(42)Initialize hard drive & controller; Initialize hard drive controller and any drives.

(42)Start write cycle of 128K RAM test.

(42)Initialize interrupt vectors.(Beep)=2-1-1-3.

(43)Entered in the virtual mode. Going to enable interrupts for diagnostics mode.

About to start DMA controller test.

(43)If it is a PnP BIOS, initialize serial & parallel ports. Detect & initialize serial/parallel ports;

(43)Reset parity checks.

Error Code - 41

Error Code - 42

Error Code - 43

Appendix A

13

Page 14

AMI

AMI

1. Test for unexpected interrupts.

memory below 1M for soft reset.

(4C)#3 shutdown.

Error Code

-

4C

Award

AMI

Award

Compaq

Phoenix

ACER

AMI

Award

Compaq

Phoenix

ACER

AMI

Award

Compaq

Phoenix

AMI

Award

Compaq

Phoenix

ACER

AMI

Phoenix

AMI

Phoenix

AMI

Phoenix

Appendix A

(44)Interrupts enabled(if post switch is on). Going to initialize data to check

memory wrap around at 0:0.

(44) Going to initialize data to check memory re-map at 0:0.

(44)Start verify cycle if 128K RAM test.

(44)Initialize BIOS interrupts.(Beep)=2-1-2-1. Verify video configuration.

(45)Set up BIOS RAM .

(45)Data initialized. Going to check for memory wrap around at 0:0 and the total

system memory size.

(45)Detect & Initialize math CoProcessor; Initialize math CoProcessor.

(45)Check for parity errors.

(45)POST device initialization.

(46)Test controller and cache memory.

(46) Memory wrap around test done. Memory size calculation over, writing patterns

to test memory.

(46)display the setup message(to press Ctrl-Alt-Esc to enter setup), and enable

setup.

(46)No RAM errors.

(46)Check ROM copying notice.(Beep)=2-1-2-3. Initialize video system.

(47)Pattern to be tested written in extended memory,640K memory.

(47)Set system speed for boot.

(47)Got a RAM error.

(47)Initialize manager for PCI Options ROMs.(Beep)=2-1- 2-4.

(48)Memory test.

(48)Patterns written in base memory. Going to find out amount of memory below

1M memory.

(48)Check Video configuration against CMOS.(Beep)=2- 1-3-

(49)Memory below 1M found and verified. Going to find out amount of memory

above 1M memory.

(49)Initialize PCI bus and devices.(Beep)=2-1-3-2.

(4A)Amount of memory above 1M found and verified. Going for BIOS ROM data

area check.

(4A)Initialize all video adapters in system.(Beep)=2-1-3-3. Start 2nd protected

mode test.

(4B) Amount of memory above 1M found and verified. Check for soft reset and

going to clear memory below 1M for reset.(If power on, go to check point#4Eh).BIOS ROM

data area check over. Going to check<ESC> and to clear

Error Code - 45

Error Code - 46

Error Code - 47

Error Code - 48

Error Code - 49

Error Code - 4A

Error Code - 4B

Phoenix

ACER

AMI

Phoenix

AMI

AMI

Phoenix

AMI

Award

ACER

(4B)Quiet-Boot start(optional).

(4C)Memory below 1M cleared.(SOFT RESET)Going to clear memory above 1M.

(4C)Shadow video BIOS ROM.(Beep)=2-1-4-1.Perform LDT instructions test.

(4D)Memory above 1M cleared. (SOFT RESET)Going to save the memory size.(GOTO check

point#52h)

Error Code - 4E

(4E)Memory test started.(NO SOFT RESET)About to display the first 64K memory

test.

(4E)If there is any error, show all the error messages on the screen & wait for user

to press<F1>.Manufacturing POST loop or display messages; Reboot if manufacturing POST

loop pin is set. Otherwise display any messages and enter

setup.

(4E)Display copying notice.(Beep)=2-1-4-3. Perform TR instruction test.

Error Code - 4F

(4F)Memory size display started. This will be updated during memory test. Going

for sequential and random memory test. Processor in real mode after shutdown.

(4F)If password is needed, ask for password. Clear the Energy Star logo(Green

BIOS only).Security check; Ask password security.

(50)#2 shutdown.

(50)Memory testing/initialization below 1M complete. Going to adjust displayed memory size

for relocation /shadow. DMA page register test complete.

Error Code - 4D

Error Code - 50

14

Page 15

Compaq

(50)Check for dual freq in CMOS.

Compaq

CMOS VDU configuration.

Phoenix (51)In

itialize EISA board.

Error Code

-

52

(52)Start VDU search.

Compaq

VDU option ROMs.

Error Code

-

54

Compaq

primary display adapter.

Compaq

(55)Initialize secondary display adapter.

Error Code

-

56

(56)No display adapters installed.

Compaq

(57)Init primary VDU mode.

ACER (58)#6 shutdown.

Error Code

-

58

(58)Start of VDU test (for each adapter).

memory size for relocation /shadow. DMA page register test complete.

AST

Award

Chips & Tech (50)Hardware initialize.

Phoenix

AMI

AST

Award

Chips & Tech (51)Timer Initialize

(50)Protected mode.

(50)Write all the CMOS values currently in the BIOS stack areas back into the

CMOS. Write CMOS; Write all CMOS values back to RAM and clear screen.

(50)Display CPU type and speed.(Beep)=2-2-1-1.(50)Per- form LSL instruction

test.[Beep]=none Custom chip set or custom platform.

(51)Memory size display adjusted due to relocation/shadow. Memory test above 1M

to follow. DMA unit-1 base register test about to start.

(51)Protected mode.

(51)Pre-boot enable; Enable parity checker; Enable NMI, Enable cache before boot. (51)Check

Appendix A

Error Code - 51

AMI

Award

Compaq

Chips & Tech (52)DMA controller initialize.

Phoenix

AMI

Award

Chips & Tech (53)Initialize interrupt controller.

ACER (54)#7 shutdown.

AMI

Chips & Tech (54)Chip-Set Initialize.

Phoenix

AMI

Award

Chips & Tech (55)EMS configuration Setup.

AMI

Compaq

Chips & Tech (56) Protected mode.

Phoenix

AMI

Chips & Tech (57)Memory size.

(52)Memory testing/initialization below 1M complete. Going to save memory size

information. Going to prepare to go back to real mode. DMA unit-1 channel OK,

about to begin CH-2.

(52)Initialize all ISA ROMs. Later PCI initializations(PCI BIOS only).PnP initializations(PnP

BIOS only).Program shadow RAM according to setup settings. Program parity according to

setup setting. Power Management initialization. Initialize option ROMs; initialize any option

ROMs present from C8000h to

EFFFFh.

(52)Test keyboard.(Beep)=2-2-1-3.(52)Perform LAR instruction test.

(53)Memory size information is saved. CPU registers are saved. Going to enter in

real mode. DMA CH-2 base register test OK.

(53)If it is not a PnP BIOS, initialize serial & parallel ports. Initialize time value in

BIOS data area. Initialize time value; Initialize time value in 40h BIOS data area. (53)Vector to

(54)Shutdown successful, CPU in real mode. Going to re- store registers saved

during preparation for shutdown. About to check F/F latch for unit-1 and unit-2. (54)Initialize

(54)Set key click if enabled.(Beep)=2-2-2-1.(54)Perform VERR instruction test.

(55)Registers restored. Going to disable gate A20 address line. F/F latch for both

units checked.

(55)Check PCI video Card-or replace video card.

(56)A20 address line disable successful. BIOS ROM data area about to be checked.

DMA unit 1 and 2 programming over and about to initialize 8259 interrupt

controller.

(56)Enable keyboard.(Beep)=2-2-2-3.Unexpected exception.

(57)A20 address line disable successful. BIOS ROM data area check halfway. BIOS

ROM data area check to be com- plete.8259 initialization over.

AMI

Compaq

Chips & Tech (58)Memory interleave configure.

Phoenix

(58)Memory size adjusted for relocation/shadow. Going to clear Hit<DEL>

message. BIOS ROM data area check over. Going to clear Hit<ESC> message.8259

mask register check OK.

(58)Test for unexpected interrupts.(Beep)=2-3-3-.(58) Perform A20 gate test.

Error Code - 53

Error Code - 55

Error Code - 57

Error Code - 59

15

Page 16

Compaq

(59)Check existence of adapter.

Compaq

(5A)Blank display, check VDU registers.

Phoenix (5A)Keyboard ready

Compaq

to

Error Code

-

5B

(5B)Start screen memory test.

Phoenix (5B)Display CPU cache.

Compaq

Error Code

-

5C

of test of adapter, clear memory.

Phoenix (5C)Test RAM between 512 and 640K.(Beep)=2

-2-4-

1. Determine if AT or KT

Error Code

-

5D

Compaq

(5D)Error detected on an adapter.

Compaq

Error Code

-

5E

(5E)test the next adapter.

Compaq

(5F)All adapters successfully

tested.

ACER (60)Set up BIOS interrupt.

Compaq

Error Code

-

60

(60)Start of memory test.

Compaq

(61)Enter protected mode.

Compaq

Error Code

-

62

AMI

Chips & Tech (59)Exiting protected mode.

Phoenix

AMI

Chips & Tech (5A)Board memory size.

AMI

Chips & Tech (5B)Shadow RAM relocated.

(59)Hit<ESC> message cleared.<Wait..> message displayed. About to start DMA

and interrupt controller test. Master 8259 mask register OK, about to start slave.

(59)Initialize POST display service.

(5A)About to check timer and keyboard interrupt level.

SETUP".(Beep)=2-2-3-3

(5B)Timer interrupt OK.

Appendix A

Error Code - 5A

test. Display prompt "press F2

enter

ACER

AMI

Chips & Tech (5C)EMS configure.

AMI

Chips & Tech (5D)Wait state configuration is set-up.

AMI

Chips & Tech (5E)1st 64K RAM re-test.

Phoenix

AMI

Chips & Tech (5F)Shadow RAM.

(5C)About to test keyboard and I/O.`

(5C)About to test keyboard interrupt. (5C)End

keyboard type.

(5D)ERROR! Timer/keyboard interrupt not in proper level.

(5E)8259 interrupt controller error.

(5E)Enter third protected mode test.

(5F)8259 interrupt controller test OK.

AMI

AST

Award

Chips & Tech (60)CMOS RAM.

Phoenix

AMI

AST

Award

Chips & Tech (61)Video.

AMI

AST

Award

Compaq

Phoenix

AMI

AST

Award

(60)DMA page register test passed. About to go for DMA #1,verify from display

memory.

(60)RAM size.

(60)Setup virus protection(Boot sector protection).

(60)Test expanded memory.(Beep)=2-3-1-1.(60)Base memory test.

(61)Display memory verification over. About to go for DMA #1 base register test.

(61)RAM test.

(61)Try to turn on level 2 cache. Set the boot up speed according to setup setting.

Last chance for chipset initialization. Last chance for power management initialization. Show

the system configuration table.

(62)DMA#1 base register test passed. About to go for DMA #2 base register test.

(62)Shadow RAM.

(62)Setup daylight saving according to setup values. Program the NUM lock, type

rate & type speed according to setup setting. Setup NUM_LOCK; Setup NUM_LOCK status

according to setup.

(62)Start memory sizing.

(62)Test extended memory address lines.(Beep)=2-3-1-3. Base memory address

test.

(63)DMA #2 base register test passed. About to go for BIOS ROM data area check. (63)Cache

memory.

(63)If there is any changes in the hardware configuration, update the ESCD information(PnP

BIOS only. Clear memory that have been used. Boot system via

INT 19h.

(63)Get CMOS size.

Error Code - 5F

Error Code - 61

Error Code - 63

16

Page 17

Chips & Tech (63)Protected mode interrupt.

ACER (64)Start test real time clock.

Compaq

Error Code

-

64

(64)Start test of real memory.

Compaq

(65)Start test of extended memory.

Compaq

Error Code

-

66

(66)Save size of real and extended memory.

Compaq

(67)Update 128K

-

Option installed CMOS bit.

Phoenix (67)Initialize Multi Processor APIC.

Error Code

-

68

Compaq

(69)Back in real mode

-

test successful.

Compaq

(6A)Back in real mode

-

error during test.

Phoenix (6A) Display external cache size.(Beep)=2

-3-3-

3.Determine memory test.

Error Code

-

6B

Chips & Tech (6B)Test Math chip.

Compaq

Erro

r Code

-

6C

(6C)End of memory test.

Compaq

(6D)Initialize KB OK display string.

& Tech (6E)Dual card.

Error Code

-

6E

(6F)Start of MEMORY TEST.

Compaq

(70)Display XXXXX KB OK.

Error Co

de - 70

Compaq

AMI

AST

Chips & Tech (64)Address line A20.

Phoenix

AMI

AST

Chips & Tech (65)Memory address lines.

AMI

AST

Chips & Tech (66)Memory Test.

Compaq

AMI

AST

Chips & Tech (67)Extended memory.

ACER (68)Test floppy disk.

Compaq

Chips & Tech (68)Timer interrupt.

Phoenix

(64)BIOS ROM data area check halfway. BIOS ROM data area check to be

complete.

(64)Copy BIOS to shadow RAM.

(64)Jump to User Patch 1.(Beep)=2-3-2-1.Shadow memory test.

(65)DMA #2 base register test passed. About to program DMA unit 1 and 2. (65)Copy

video BIOS to shadow RAM.

(66)DMA unit 1 and 2 programming over. About to initialize 8259 interrupt

controller.

(66)8254 timer channel #2.

(66)Configure advanced cache registers.(Beep)=2-3-2-3. Extended memory test.

(67)8259 initialization over. About To start keyboard test.

(67)Memory initialize.

(68)Prepare to return to real mode.

(68)Enable external and CPU caches.(Beep)=2-3-3-1. Ex- tended address test.

Chips & Tech (69)Real Time clock.

Phoenix

(69)Setup System Management Mode(SMM) area.

Chips & Tech (6A) Keyboard controller.

Appendix A

Error Code - 65

Error Code - 67

Error Code - 69

Error Code - 6A

Compaq (6B)Display error messages.

Phoenix

ACER

Chips & Tech (6C)Test serial port(RS232).

Phoenix

Chips & Tech (6D)Test parallel ports.

Compaq (6E)Determine size to test. Chips

Phoenix

Compaq

Chips & Tech (6F)Test floppy drive controller.

ACER

AMI

Chips & Tech (70)Test hard drive controller.

Phoenix

AMI

(6B)Load custom defaults(optional).

(6C)Test hard disk drive.

(6C)Display shadow message.(Beep)=2-3-4-1.Display error messages.

Error Code - 6D

(6E)Display possible high address for UMB recovery. Display non-disposable

segments.(Beep)=2-3-4-3.Configure ROM/RAM BIOS.

Error Code - 6F

(70)About to test parallel port.

(70)start of keyboard test.

(70)Display error messages.(Beep)=2-4-1-1.System time test.

controller BAT test over.

(71)Test each RAM segment.

Error Code - 71 (71)Keyboard

17

Page 18

Chips & Tech (71)Key-lock.

Compaq

Error Code

-

72

(72)High order address test.

Phoenix

(73)Global data initialization for keyboard/mouse over.

(74)About to test serial port.

Error Code

-

74

(74)Test real

-

time clock.(Beep)=2

-4-2-

1.Test for stuck keys.

(75)Start of protected mode test.

Error Code

-

75

(76)Check for keyboard errors. (Beep)=2

-4-2-

3.Initialize hardware interrupt

(78)Set real time.

Error Code

-

77

(7B)CMOS battery verification over.

(7C)scan option. RAMs.

Error Code

-

7C

AMI

Chips & Tech (72)Pointing divide.

Phoenix

AMI

Compaq

ACER

AMI

Compaq

Phoenix

AMI

Compaq

AMI

Compaq

Phoenix

AMI

Compaq

ACER

Compaq

Phoenix

AMI

Compaq

AMI

Compaq

Phoenix

AMI

Compaq

ACER

Compaq

Phoenix

AMI

Compaq

AMI

Compaq

Phoenix

AMI

Compaq

ACER

AMI

Compaq

Phoenix

AMI

Compaq

(72)Keyboard interface test over, mouse interface test started.

(72)Check for configuration errors.(Beep)=2-4-1-3.(72) Real time clock test.

(73)Exit memory test.

(74)Display 'SETUP' prompt and about to start floppy setup.

(74)Parity error on bus after memory test, system halted.

(75)Floppy setup over.

(76)Hard disk setup about to start.

(76)Prepare to enter protected mode.

vectors.

(77)Hard disk setup over.

(77)Test software exceptions.

(78)Prepare to return to real mode.

(78)Detect and test CoProcessor.

(79)About to initialize timer data area.

(79)Back in real mode-No error.

(7A)Timer data initialized and about to verify CMOS battery power.

(7A)Back in real mode-error.

(7A)Determine/Init COM channels.

(7B)Exit protected mode.

(7C)High order address test failure.

(7C)Set up hardware interrupts vectors.(Beep)=2-4-4-1.Determine LPT channels.

(7D)About to analyze POST results. About to analyze diagnostic test results for

memory.

(7D)Enter cache controller test.

(7E)CMOS memory size updated.

(7E)Exit cache controller test.

(7E)Test CoProcessor if present.(Beep)=2-4-4-3.Initialize BIOS data area.

(7F)Look for <DEL>key and get into CMOS setup if found About to check optional ROM

C000:0.

(7F)Copy System ROM to high RAM.

(80)Determine math CoProcessor is present.

(80)Keyboard test started, clearing output buffer, checking for stuck key, About to

issue keyboard reset command. About to give control to optional ROM in segment

C800 to DE00.

(80)Start of 8042 test.

(80)Disable onboard Super I/O ports and IRQs.(Beep)=3-1- 1-1.Detect floppy

controller.

(81)Keyboard reset error/stuck key found. About to issue keyboard controller interface test

command. Optional ROM control over.

(81)Do 8042 self-test.

(81)late POST device initialization.

Appendix A

Error Code - 73

Error Code - 76

Error Code - 78

Error Code - 79

Error Code - 7A

Error Code - 7B

Error Code - 7D

Error Code - 7E

Error Code - 7F

Error Code - 80

Error Code - 81

Error Code - 82

18

Page 19

AMI

AMI

Compaq

Phoenix

AMI

Compaq

Phoenix

ACER

AMI

Compaq

Phoenix

AMI

Phoenix

AMI

Compaq

Phoenix

AMI

Compaq

Phoenix

ACER

AMI

Compaq

Phoenix

AMI

Compaq

Phoenix

AMI

Compaq

Phoenix

AMI

Compaq

Phoenix

ACER

AMI

Compaq

Phoenix

AMI

Compaq

AMI

Phoenix

AMI

Phoenix

ACER

Appendix A

(82)Keyboard controller interface test over. About to write command byte and Init

circular buffer. Check for printer ports and put the addresses in global data area.

(82)Check result received.

(82)Detect and install external RS232 ports.(Beep)=3-1- 1-3.Test floppy drives.

(83)Command byte written, global data Init done. About to check for lock-key.

Check for RS232 ports and put the addresses in global data area.

(83)Error result.

(83)Configure non-MCD IDE controllers.

(84)Keyboard initialize.

(84)Lock-key checking over. About to check for memory size mismatch with

CMOS. CoProcessor detection over. 80287 check/test OK.

(84)OK 8042,Init mode=5D.

(84)Detect and install external parallels ports.(Beep)=3-1- 2-1.Fixed disk test.

(85)Memory size check done. About to display soft error and check for password or

bypass setup. About to display soft error message. If no video replace Video card. (85)Initialize

PC-compatible PnP ISA devices.

(86)Password checked. About to do programming before setup. About to give

control to system ROM at segment E000.

(86)Start keyboard test, reset keyboard.

(86)Re-initialize onboard I/O ports.(Beep)=3-1-2-3.(86)Per form external ROM

scan.

(87)Programming before setup complete. Going to uncompress SETUP code and

execute CMOS setup. System ROM E000:0 check over.

(87)Got acknowledge, read result.

(87)Configure Motherboard Configuration Devices(option- al)

(88)System #1 initialize.

(88)Returned from CMOS setup program and screen is cleared. About to do programming after

setup.

(88)Got result, check it .

(88)Initialize BIOS Data Area.(Beep)=3-1-3-1.Test key- lock/keyboard type.

(89)Programming after setup complete. Going to display power on screen message.

(89)Test for stuck keys.

(89)Enable Non-Maskable Interrupts(NMIs)

(8A)First screen message displayed. About to display <WAIT¡->message.

(8A)Key seems to be stuck.

(8A)Initialize Extended BIOS Data Area.(Beep)=3-1-3-3. wait for F1 test.

(8B)First screen message displayed <WAIT¡->message displayed. About to do

Main and Video BIOS shadow.

(8B)Test keyboard interface.

(8B)Test and initialize PS/2 mouse.

(8C)System #2 initialize.

(8C)Main and video BIOS shadow successful. Setup options programming after

CMOS setup about to start.

(8C)Got result, check it.

(8C)Initialize floppy controller.(Beep)=3-1-4-1.Final system initialization.

(8D)Setup options are programmed, mouse check and Init to be done next. Going

for hard disk, floppy reset.

(8D)End of test, no errors.

(8E)Mouse check and initialization complete. Going for hard disk controller reset.

About to go For floppy check.

(8E)Interrupt 19 boot loader.

(8F)Hard disk controller reset done. Floppy setup to be done nest.

(8F)Determine number of ATA drives(optional)

(90)Invoke interrupt 19 to boot loader.

(90)Floppy setup is over. Test for hard disk presence to be done.

Error Code - 83

Error Code - 84

Error Code - 85

Error Code - 86

Error Code - 87

Error Code - 88

Error Code - 89

Error Code - 8A

Error Code - 8B

Error Code - 8C

Error Code - 8D

Error Code - 8E

Error Code - 8F

Error Code - 90

19

Page 20

Appendix A

Compaq

(91)CMOS seems to be OK.

Compaq

on CMOS read/writ

e test.

Compaq

(94)Page registers seem OK.

Compaq

(95)DMA controller OK.

Phoenix (95)Install CD ROM for boot.

Error Code

-

96

(96)8237 DMA Initialization complete.

AMI

control will be done next.

Phoenix (97)Fix

-

up Multi Processor table.

Error Code

-

98

processing after optional ROM returns control.

Phoenix (98)Search for option ROMs. One long, two short beeps on checksum

Error Code

-

99

AMI

(9B)Returned after RS

-

232 base address. Going to de any initialization before

(9C)#B shutdown.

Error Code

-

9C

Compaq

Chips & Tech (90)Set-up RAM.

Phoenix

AMI

Chips & Tech (91)CPU speed.

Phoenix

AMI

Chips & Tech (92)Configuration check.

Phoenix

AMI

Compaq

Phoenix

ACER

AMI

Chips & Tech (94)POD Bootstrap.

Phoenix

AMI

Chips & Tech (95)Reset ICS.

AMI

Compaq

Chips & Tech (96)BIOS PEAK.

Phoenix

Chips & Tech (97)VGA power.

(90)Start of CMOS test .

(90)Initialize hard-disk controller.(Beep)=3-2-1-1

(91)Floppy setup complete. Hard disk setup to be done next.

(91)Initialize local-bus hard-disk controller.(Beep)=3-2-1-2

(92)Hard disk setup complete. About to go for BIOS ROM data area check. (92)Error

(92)Jump to User Patch 2.(Beep)= 3-2-1-3

(93)BIOS ROM data area check halfway. BIOS ROM data area check to be

completed.

(93)Start of DMA controller test.

(93)Build MPTABLE for multi processor boards.

(94)#5 shutdown.

(94)Hard disk setup complete. Going to set base and extended memory size. BIOS

ROM data area check over.

(94)Disable A20 address line.(Beep)=3-2-2-1

(95)Memory size adjusted due to mouse support, hard disk type-47.Going to verify

from display memory.

(96)Memory size adjusted due to mouse support, hard disk type-47.Going to do any

Init before C800 optical ROM control. Returned after verifying from display

memory.

(96)Clear huge ES segment register.(Beep)=3-2-2-3.

(97)Any Init before C800 optional ROM control is over. Optional ROM check &

Error Code - 91

Error Code - 92

Error Code - 93

Error Code - 94

Error Code - 95

Error Code - 97

ACER (98)#A shutdown.

AMI

Chips & Tech (98)Adapters POS.

AMI

Phoenix

AMI

Phoenix

AMI

ACER

AMI

Phoenix

(98)Optional ROM control is done. About to give control to do any required

failure.(Beep)=3-2-3-1.

(99)Any initialization required after optional ROM test over. Going to setup timer

data area and printer base address.

(99)Check for SMART Drive(optional).

(9A)Return after setting timer and printer base address. Going to set the RS-232

base address.

(9A)Shadow option ROMS.(Beep)=3-2-3-3.

Error Code - 9B

Co-Processor test.

(9C)Required initialization before co-Processor is over. Going to initialize the

CoProcessor next.

(9C)Set up Power Management.(Beep)=3-2-4-1.

Error Code - 9D

(9D)CoProcessor initialized. Going to do any initialization after CoProcessor test.

Error Code - 9A

Error Code - 9E

20

Page 21

AMI

Phoenix

Phoenix

AMI

Phoenix

AMI

Compaq

Phoenix

AMI

Compaq

AMI

Compaq

Phoenix

AMI

Compaq

AMI

Compaq

Phoenix

AMI

Compaq

AMI

Compaq

AMI

AMI

Compaq

Phoenix

AMI

Compaq

AMI

Compaq

Phoenix

Phoenix

Phoenix

Compaq

AMI

Award

Compaq

Phoenix

AMI

Award

Compaq

Compaq

Phoenix

Compaq

Compaq

Appendix A

(9E)Initialization after CoProcessor test is complete. Going to check expander

keyboard, keyboard ID and number-lock.

(9E)Enable hardware interrupts.(Beep)=3-2-4-3.

(9F)Extended keyboard check is done, ID flag set. num-lock on/off. Keyboard ID command to

be issued.

(9F)Determine number at ATA and SCSI drives.

(A0)Keyboard ID command issued. Keyboard ID flag to be reset.

(A0)Start of diskette tests.

(A0)Set time of day .(Beep)=3-3-1-1

(A1)Keyboard ID flag reset. Cache memory test to follow.

(A1)FDC reset active (3F8H bit 2)

(A2)Cache memory test over. Going to display any soft errors.

(A2)FDC reset inactive(3F8H bit 2)

(A2)Check key lock.(Beep)=3-3-1-3

(A3)Soft error display complete. Going to set the keyboard type matric rate.

(A3)FDC motoron.

(A4)Keyboard type matric rate set. Going to program memory wait states.

(A4)FDC time-out error.

(A4)Initialize Type matric rate.

(A5)Memory wait states programming over. Going to clear the screen and enable

parity/NMI.

(A5)FDC failed reset.

(A6)Screen cleared. Going to enable parity and NMI.

(A6)FDC passed reset.

(A7)NMI and parity enabled. Going to do any Initialization required before giving

control to optional ROM at E000.

(A8)Initialization before E000 ROM control over. E000 ROM to get control next.

(A8)Start of determine drive type.

(A8)Erase F2 prompt.(Beep)3-3-3-1

(A9)Returned from E000 ROM control. Going to do any init required after E000

optional ROM control.

(A9)Seek operation initiated.

(AA)Initialization after E000 optional ROM control is over. Going to display the

system configuration.

(AA)Waiting for FDC status.

(AA)Scan for F2 key stroke.(Beep)=3-3-3-3

(AC)Enter SETUP.(Beep)=3-3-4-1

(AE)Clear in-POST flag.(Beep)=3-3-4-3.Clear Boot fag.

(AF)diskette tests complete.

(B0)System configuration is displayed. Going to un-com- press SETUP code for

hot-key setup.

(B0)Spurious interrupt occurred in protect mode. Check mismatch memory.

(B0)Start of fixed drive tests.

(B0)Check for errors.(Beep)=3-4-1-1.Unknown interrupt occurred.

(B1)un-compressing of SETUP code is complete. Going to copy any code to specific area.

(B1)If unmasked NMI occurs, Press F1 to disable NMI,F2 to boot.

(B1)Combo board not found, exit.

(B2)Combo controller failed, exit.

(B2)POST done-prepare to boot operating system.(Beep)=3- 4-1-3

(B3)Testing drive 1.

(B4)Testing drive 2.

(B4)One short beep before boot.(Beep)=3-4-3-1

Error Code - 9F

Error Code - A0

Error Code - A1

Error Code - A2

Error Code - A3

Error Code - A4

Error Code - A5

Error Code - A6

Error Code - A7

Error Code - A8

Error Code - A9

Error Code - AA

Error Code - AB-AF

Error Code - B0

Error Code - B1

Error Code - B2-B5

21

Page 22

Appendix A

Award

(C0)Turn off chipset cache; OEM Specific

-

cache control.

Award

SIMM.

Award

jumper Setting). Also, Check Video memory

Compaq

Phoenix

Compaq

Phoenix

Compaq

Compaq

Phoenix

Compaq

Phoenix

Compaq

Phoenix

Compaq

Phoenix

Compaq

Phoenix

Compaq

Phoenix

Award

Compaq

Phoenix

Award

Award

Phoenix

Chips & Tech (C0)System board memory failure.

Phoenix

Chips & Tech (C1)I/O channel activated.

Phoenix

AMI

Phoenix

AMI

Award

Phoenix

Award

Phoenix

AMI

Award

Phoenix

AMI

Award

Phoenix

AMI

Award

Phoenix

AMI

Award

Phoenix

Phoenix

AMI

(B5)Drive error(error condition).

(B5)terminate Quiet-Boot(optional)

(B6)Drive failed(failed to respond).

(B6)Check password(optional).(Beep)=3-4-2-3

(B7)CMOS RAM invalid or no fixed drives, exit.

(B8)Fixed drive tests complete.

(B8)Clear global descriptor table.(Beep)=3-4-3-4

(B9)Attempt to boot diskette.

(B9)Prepare boot.

(BA)Attempt to boot fixed drive.

(BA)Initialize DMI parameters.

(BB)Boot attempt failed(diskette or fixed).

(BB)Initialize PnP option ROMs.

(BC)Boot record read, jump to boot record.

(BC)Clear parity checkers.(Beep)=3-4-4-1

(BD)Drive error, retry booting.

(BD)Display Multi-Boot menu.

(BE)Program defaults values into chipset.(BE)Chipset default initialization; Program chipset

registers with power on BIOS defaults.

(BE)Weitck CoProcessor test.

(BE)Clear screen(optional).(Beep)=3-4-4-3

(BF)Program the rest of the chipset

(BF)Chipset initialization; Program chipset registers with setup values.

(BF)Check virus and backup reminders.(Beep)=3-4-4-4

(C0)Try to boot with INT 19.(Beep)=4-1-1-1

(C1)Memory presence test; OEM specific-test to size on- board memory. Bad

(C1)Initialize POST Error Manager(PEM).

(C2)NMI is Disable. Power on delay start on.

(C2)Initialize error logging.

(C3)Check memory(Cache, Video or first 64K)

(C3)DRAM Select page, Check BIOS setting and first SIMM, Possible address line

failure.

(C3)Initialize error display function.

(C4)CMOS conflicts, check video switch, BIOS(Chipset) on the video not

initializing.

(C4)initialize system error handler.

(C5)Power on delay complete. Going to enable ROM i.c. disable Cache if any.

(C5)Early shadow; OEM Specific-Early shadow enable for fast boot.

(C5)PnPnd dual CMOS(optional)

(C6)Calculating ROM BIOS checksum.