Page 1

A

1 1

B

C

D

E

Compal Confidential

2 2

Intel Haswell rPGA Processor with Lynx Point-H

Afterburn MXM

LA-9371P

3 3

2012-09-28

REV : 0.2

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

C

2012/06/11 2013/06/11

2012/06/11 2013/06/11

2012/06/11 2013/06/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-9371P

LA-9371P

LA-9371P

E

0.2

0.2

1 53Friday, September 28, 2012

1 53Friday, September 28, 2012

1 53Friday, September 28, 2012

0.2

Page 2

A

B

C

D

E

Compal Confidential

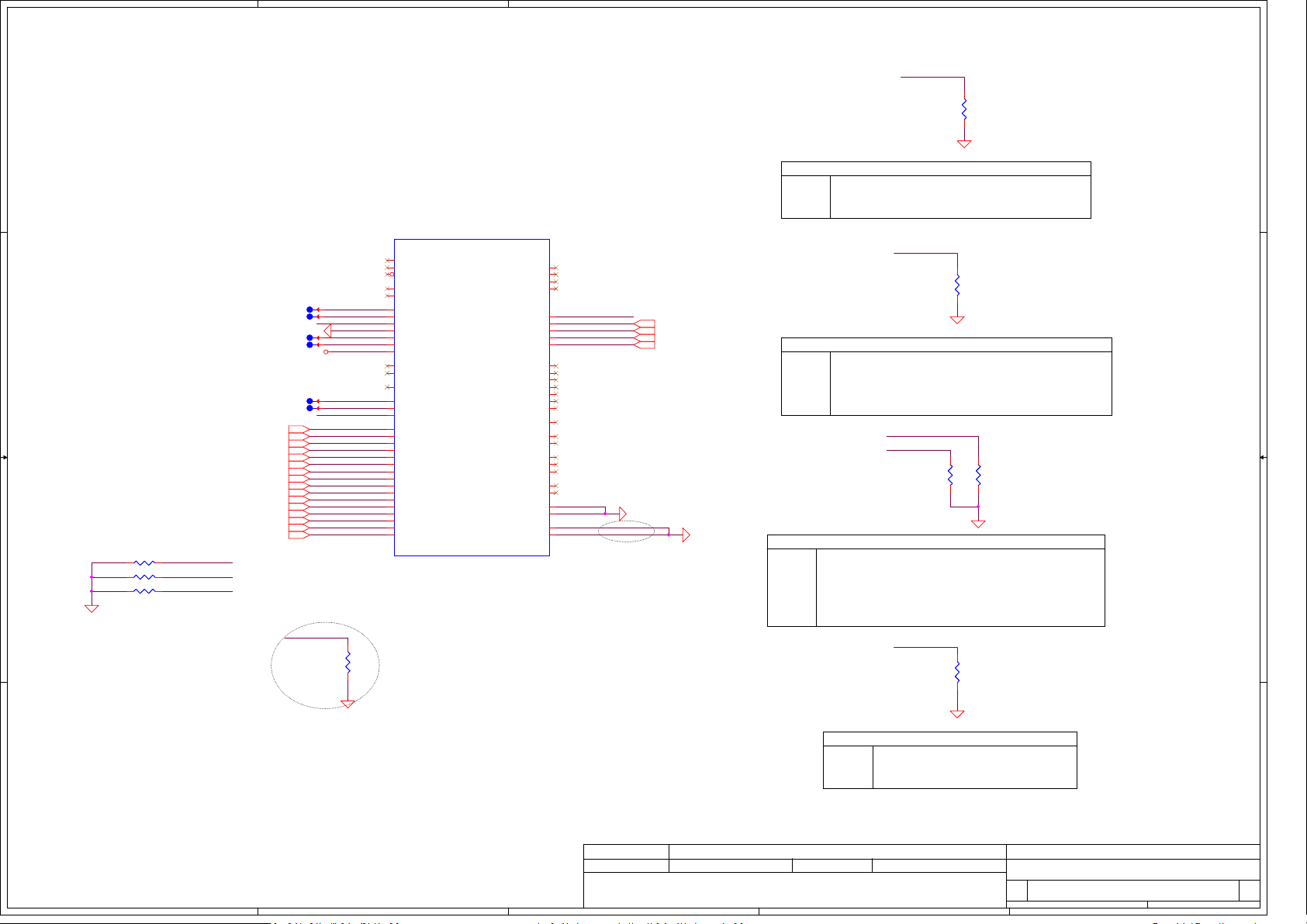

Model Name : Afterburn

File Name : LA-9371P

1 1

Ch B

DDR3-SO-DIMM2, 3

BANK 0, 1, 2, 3

Page 12

eDP Panel Conn.

P Switch

D

PI3VDP124

Dock Conn DPD

Page 33

DP Conn

2 2

3 3

daughter board

sub/B Page 6

Mini DP Conn.

sub/B Page 4

daughter board

Port 8

Card Reader

Realtek RTS5237

LS-9373P Page 4

SD/MMC Slot

LS-9373P Page 4

Dock Conn

Page 33

GLAN Intel

Clarkville

Page 29

Lan Switch

PI3L500

Page 29

ThunderBolt

Cactus Ridge

sub/B Page 2,3,4

X4

Port 3,4

daughter board

RJ45 Conn.

Page 29

Port 5Port 6

Expresscard

sub/B Page 7

Super I/O

Port 6

SMSC LPC47N217

Accelerometer

ST HP3DC2

Page 28

FAN conn.

Page 24

4 4

RTC CKT.

Power On/Off CKT.

DC/DC interface CKT.

Page 13

LS-9376P Page 4

Page 34

A

Page 36

Dock Conn

VGA Conn

Port 7

WLAN

(MINI card)

Page 25

Port 13

Page 32

Page 22

DPC

D

Page 33

Page 36

ODD

Conn.

Page 23 Page 23

TPM1.2

Infineon SLB9656

SMBus (PCH)

B

eDP MUX

PS8321

Page 36

eDPF

MXM3.0 Conn

NVidia:

PE

CRT

VGA Switch

2 to 2

CRT

MAX14885EETL

PCI-Express x 8 (ARD PCIE2.0 2.5GT/s)

Port 1

mSATA

Conn.

Page 35

CRT

Port 2

SATA HDD

Conn.

(Secondary)

Page 36

Port 4

(GEN1 1.5Gb/S

GEN2 3Gb/S

GEN3 6Gb/S)

Page 23

PEGx16

SATAx4

USB 2.0 Bus

KBC

Page 28

Touch Pad

SMSC MES1132

PS2

eDP

CRT

100MHz

100MHz

Port 0

SATA HDD

Conn.

(primary)

Page 23

Int.KBD

Intel

Haswell

rPGA Processor

rPGA947

37.5mm*37.5mm

Page 4,5,6,7,8,9,10

100MHz

2.7GT/s

Intel

Lynx Point

PCH

695pin BGA

20mm*20mm

Page 13,14,15,16,17,18,19,20,21

LPC BUS

33MHz

SPI(PCH)

Page 30

Page 38Page 38

C

DMI x4FDI x2

100MHz

5GT/s

SPI

BIOS SPI ROM x1,

16 MB

EC ROM

2MB

DDR3L 1333MHz 1.35V

USB 3.0 x4

USB 2.0 x 11

HD Audio

Page 16

HDA Codec

IDT 92HD91

Page 30

DDR3-SO-DIMM0, 1

BANK 0, 1, 2, 3

Ch A

Digital MIC

Page 22

Page 26

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I NC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I NC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I NC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIV ISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIV ISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIV ISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Combo Jack

LS-9373P Page 4

SPK conn

Page 27

2012/06/11 2013/06/11

2012/06/11 2013/06/11

2012/06/11 2013/06/11

D

Page 11

Port 1,4,5,9

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Port 1

Docking x 1

Port 2,5,6

USB conn x 3 (For I/O)

Port 0,11

Docking x 2

USB conn x 4(For I/O)

Port 6

Expresscard

Smart card Controller

Port 7

AU9540A51

FPR

Port 8

Validity VFM471

Port 10

Webcam

Port 12

WWAN SIM Card

Port 13

WLAN

Page 33

page 39

Page 33

page 39

sub/B Page 7

Page 37

Page 28

Page 22

Page 25 Page 25

daughter board

daughter board

Docking connector:

RJ45

USB30*1

USB20*1

DP*2

Parallel port

Serial port

PS/2

Line in/Line out

SATAx2

VGA

Compal Electronics, Inc.

Compal Electronics, Inc.

Custom

Custom

Custom

Compal Electronics, Inc.

Block Diagrams

Block Diagrams

Block Diagrams

LA-9371P

LA-9371P

LA-9371P

E

2 53Friday, September 28, 2012

2 53Friday, September 28, 2012

2 53Friday, September 28, 2012

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

0.2

0.2

0.2

Page 3

5

4

3

2

1

Voltage Rails

D D

State

S0

C C

SMBUS Control Table

S1

S3

S5 S4/AC

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

( O MEANS ON X MEANS OFF )

+RTCVCC

power

plane

O

O

O

O

O

Symbol Note :

B+

O

O

O

O

O

X

+5VDS

+3VDS

OO

O

O

O

X

X X X

+1.35V

+0.675VS

O

X X

X

+5VS

+3VS

+1.5VS

+VCC_CORE

+1.05VS

1.05VM

+

OO

OO

X

X

: means Digital Ground

: means Analog Ground

@ : means just reserve , no build

AMT@ : means just install for support iAMT

CONN@ : means ME part.

Layout Notes

L

07/24 update

: Question Area Mark.(Wait check)

Install below 45 level BOM structure for ver. 0.1

45@ : means just put it in the BOM of 45 level.

Install below 43 level BOM structure for ver. 0.1

DEBUG@ : means just build when PCIE port 80 CARD function enable.

Remove before MP

SOURCE

B B

A A

I2C_MAIN_CLK

I2C_MAIN_DAT

I2C_BAY_CLK

I2C_BAY_DAT

MEM_SMBCLK

MEM_SMBDATA

LAN_SMBCLK

LAN_SMBDATA

SML1_SMBCLK

SML1_SMBDATA

Stapping O ptions Fla sh

GPIO 51

Bit 1

0

0 1

1

1 1

SMSC1126

SMSC1126

Haswell

GPIO 19

Bit 0

0

0

5

Haswell

H

aswell

Boot BIOS Destination

2nd

BATT

BATT

X

V

X

V

X

X

X

X X

X X X

Reserved

RSVD

SPI

LPC

XDP

X

X

V

SODIMM

X

X

V

X

X

G-SENSOR

X

X

V

X

X

4

X

X

X

TP

V

X

NIC

X

X

X

V

X

NFC

EC

MXM

X

X

X

X

V

Issued Date

Issued Date

Issued Date

X

X

X

X

V

Compal Secret Data

Compal Secret Data

2012/06/11 2013/06/11

2012/06/11 2013/06/11

2012/06/11 2013/06/11

3

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

X

X

X

V

X

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

LA-9371P

LA-9371P

LA-9371P

3 53Friday, September 28, 2012

3 53Friday, September 28, 2012

3 53Friday, September 28, 2012

1

0.2

0.2

0.2

Page 4

5

D D

DMI_CRX_PTX_N0<14>

DMI_CRX_PTX_N1<14>

DMI_CRX_PTX_N2<14>

DMI_CRX_PTX_N3<14>

DMI_CRX_PTX_P0<14>

DMI_CRX_PTX_P1<14>

DMI_CRX_PTX_P2<14>

DMI_CRX_PTX_P3<14>

DMI_CTX_PRX_N0<14>

DMI_CTX_PRX_N1<14>

DMI_CTX_PRX_N2<14>

DMI_CTX_PRX_N3<14>

DMI_CTX_PRX_P0<14>

DMI_CTX_PRX_P1<14>

C C

B B

DMI_CTX_PRX_P2<14>

DMI_CTX_PRX_P3<14>

FDI_CSYNC<14>

FDI_INT<14>

DMI_CRX_PTX_N0

DMI_CRX_PTX_N1

DMI_CRX_PTX_N2

DMI_CRX_PTX_N3

DMI_CRX_PTX_P0

DMI_CRX_PTX_P1

DMI_CRX_PTX_P2

DMI_CRX_PTX_P3

DMI_CTX_PRX_N0

DMI_CTX_PRX_N1

DMI_CTX_PRX_N2

DMI_CTX_PRX_N3

DMI_CTX_PRX_P0

DMI_CTX_PRX_P1

DMI_CTX_PRX_P2

DMI_CTX_PRX_P3

FDI_CSYNC

FDI_INT

4

Haswell rPGA EDS

Haswell rPGA EDS

JCPU1A

JCPU1A

D21

DMI_RXN_0

C21

DMI_RXN_1

B21

DMI_RXN_2

A21

DMI_RXN_3

D20

DMI_RXP_0

C20

DMI_RXP_1

B20

DMI_RXP_2

A20

DMI_RXP_3

D18

DMI_TXN_0

C17

DMI_TXN_1

B17

DMI_TXN_2

A17

DMI_TXN_3

D17

DMI_TXP_0

C18

DMI_TXP_1

B18

DMI_TXP_2

A18

DMI_TXP_3

H29

FDI_CSYNC

J29

DISP_INT

I

I

NTEL_HASWELL_HA SWELL

NTEL_HASWELL_HA SWELL

CONN@

CONN@

3

+VCCIOA_OUT

PEG_COMP

CAD Note:

Trace width=12 mils ,Spacing=15mil

Max length= 400 mils.

E23

PEG_RCOMP

PEG_RXN_0

PEG_RXN_1

PEG_RXN_2

PEG_RXN_3

PEG_RXN_4

PEG_RXN_5

PEG_RXN_6

PEG

PEG

PEG_RXN_7

DMI FDI

DMI FDI

1 OF 9

1 OF 9

PEG_RXN_8

PEG_RXN_9

PEG_RXN_10

PEG_RXN_11

PEG_RXN_12

PEG_RXN_13

PEG_RXN_14

PEG_RXN_15

PEG_RXP_0

PEG_RXP_1

PEG_RXP_2

PEG_RXP_3

PEG_RXP_4

PEG_RXP_5

PEG_RXP_6

PEG_RXP_7

PEG_RXP_8

PEG_RXP_9

PEG_RXP_10

PEG_RXP_11

PEG_RXP_12

PEG_RXP_13

PEG_RXP_14

PEG_RXP_15

PEG_TXN_0

PEG_TXN_1

PEG_TXN_2

PEG_TXN_3

PEG_TXN_4

PEG_TXN_5

PEG_TXN_6

PEG_TXN_7

PEG_TXN_8

PEG_TXN_9

PEG_TXN_10

PEG_TXN_11

PEG_TXN_12

PEG_TXN_13

PEG_TXN_14

PEG_TXN_15

PEG_TXP_0

PEG_TXP_1

PEG_TXP_2

PEG_TXP_3

PEG_TXP_4

PEG_TXP_5

PEG_TXP_6

PEG_TXP_7

PEG_TXP_8

PEG_TXP_9

PEG_TXP_10

PEG_TXP_11

PEG_TXP_12

PEG_TXP_13

PEG_TXP_14

PEG_TXP_15

PEG_COMP

M29

PEG_CRX_GTX_N0

K28

PEG_CRX_GTX_N1

M31

PEG_CRX_GTX_N2

L30

PEG_CRX_GTX_N3

M33

PEG_CRX_GTX_N4

L32

PEG_CRX_GTX_N5

M35

PEG_CRX_GTX_N6

L34

PEG_CRX_GTX_N7

E29

PEG_CRX_GTX_N8

D28

PEG_CRX_GTX_N9

E31

PEG_CRX_GTX_N10

D30

PEG_CRX_GTX_N11

E35

PEG_CRX_GTX_N12

D34

PEG_CRX_GTX_N13

E33

PEG_CRX_GTX_N14

E32

PEG_CRX_GTX_N15

L29

PEG_CRX_GTX_P0

L28

PEG_CRX_GTX_P1

L31

PEG_CRX_GTX_P2

K30

PEG_CRX_GTX_P3

L33

PEG_CRX_GTX_P4

K32

PEG_CRX_GTX_P5

L35

PEG_CRX_GTX_P6

K34

PEG_CRX_GTX_P7

F29

PEG_CRX_GTX_P8

E28

PEG_CRX_GTX_P9

F31

PEG_CRX_GTX_P10

E30

PEG_CRX_GTX_P11

F35

PEG_CRX_GTX_P12

E34

PEG_CRX_GTX_P13

F33

PEG_CRX_GTX_P14

D32

PEG_CRX_GTX_P15

H35

PEG_CTX_GRX_C_N0

H34

PEG_CTX_GRX_C_N1

J33

PEG_CTX_GRX_C_N2

H32

PEG_CTX_GRX_C_N3

J31

PEG_CTX_GRX_C_N4

G30

PEG_CTX_GRX_C_N5

C33

PEG_CTX_GRX_C_N6

B32

PEG_CTX_GRX_C_N7

B31

PEG_CTX_GRX_C_N8

A30

PEG_CTX_GRX_C_N9

B29

PEG_CTX_GRX_C_N10

A28

PEG_CTX_GRX_C_N11

B27

PEG_CTX_GRX_C_N12

A26

PEG_CTX_GRX_C_N13

B25

PEG_CTX_GRX_C_N14

A24

PEG_CTX_GRX_C_N15

J35

PEG_CTX_GRX_C_P0

G34

PEG_CTX_GRX_C_P1

H33

PEG_CTX_GRX_C_P2

G32

PEG_CTX_GRX_C_P3

H31

PEG_CTX_GRX_C_P4

H30

PEG_CTX_GRX_C_P5

B33

PEG_CTX_GRX_C_P6

A32

PEG_CTX_GRX_C_P7

C31

PEG_CTX_GRX_C_P8

B30

PEG_CTX_GRX_C_P9

C29

PEG_CTX_GRX_C_P10

B28

PEG_CTX_GRX_C_P11

C27

PEG_CTX_GRX_C_P12

B26

PEG_CTX_GRX_C_P13

C25

PEG_CTX_GRX_C_P14

B24

PEG_CTX_GRX_C_P15

12

RC124.9_0402_1% RC124.9_0402_1%

2

PEG_CRX_GTX_P[0..15]

PEG_CRX_GTX_N[0..15]

PEG_CTX_GRX_P[0..15]

PEG_CTX_GRX_N[0..15]

PEG_CTX_GRX_C_P0

PEG_CTX_GRX_C_N0 PEG_CTX_GRX_N0

PEG_CTX_GRX_C_P1

PEG_CTX_GRX_C_N1

PEG_CTX_GRX_C_P2

PEG_CTX_GRX_C_N2

PEG_CTX_GRX_C_P3

PEG_CTX_GRX_C_N3

PEG_CTX_GRX_C_P4

PEG_CTX_GRX_C_N4

PEG_CTX_GRX_C_P5

PEG_CTX_GRX_C_N5

PEG_CTX_GRX_C_P6

PEG_CTX_GRX_C_N6

PEG_CTX_GRX_C_P7

PEG_CTX_GRX_C_N7

PEG_CTX_GRX_C_P8

PEG_CTX_GRX_C_N8

PEG_CTX_GRX_C_P9

PEG_CTX_GRX_C_N9

PEG_CTX_GRX_C_P10

PEG_CTX_GRX_C_N10

PEG_CTX_GRX_C_P11

PEG_CTX_GRX_C_N11

PEG_CTX_GRX_C_P12

PEG_CTX_GRX_C_N12

PEG_CTX_GRX_C_P13

PEG_CTX_GRX_C_N13

PEG_CTX_GRX_C_P14

PEG_CTX_GRX_C_N14

PEG_CTX_GRX_C_P15

PEG_CTX_GRX_C_N15

12

CC1 0.22U_0402_6.3V6KCC1 0.22U_0402_6.3V6K

12

CC2 0.22U_0402_6.3V6KCC2 0.22U_0402_6.3V6K

12

CC3 0.22U_0402_6.3V6KCC3 0.22U_0402_6.3V6K

12

CC4 0.22U_0402_6.3V6KCC4 0.22U_0402_6.3V6K

12

CC5 0.22U_0402_6.3V6KCC5 0.22U_0402_6.3V6K

12

CC6 0.22U_0402_6.3V6KCC6 0.22U_0402_6.3V6K

12

CC7 0.22U_0402_6.3V6KCC7 0.22U_0402_6.3V6K

12

CC8 0.22U_0402_6.3V6KCC8 0.22U_0402_6.3V6K

12

CC9 0.22U_0402_6.3V6KCC9 0.22U_0402_6.3V6K

12

CC10 0.22U_0402_6.3V6KCC10 0.22U_0402_6.3V6K

12

CC11 0.22U_0402_6.3V6KCC11 0.22U_0402_6.3V6K

12

CC12 0.22U_0402_6.3V6KCC12 0.22U_0402_6.3V6K

12

CC13 0.22U_0402_6.3V6KCC13 0.22U_0402_6.3V6K

12

CC14 0.22U_0402_6.3V6KCC14 0.22U_0402_6.3V6K

12

CC15 0.22U_0402_6.3V6KCC15 0.22U_0402_6.3V6K

12

CC16 0.22U_0402_6.3V6KCC16 0.22U_0402_6.3V6K

1 2

CC17 0.22U_0402_6.3V6KCC17 0.22U_0402_6.3V6K

1 2

CC18 0.22U_0402_6.3V6KCC18 0.22U_0402_6.3V6K

1 2

CC19 0.22U_0402_6.3V6KCC19 0.22U_0402_6.3V6K

1 2

CC20 0.22U_0402_6.3V6KCC20 0.22U_0402_6.3V6K

1 2

CC21 0.22U_0402_6.3V6KCC21 0.22U_0402_6.3V6K

1 2

CC22 0.22U_0402_6.3V6KCC22 0.22U_0402_6.3V6K

1 2

CC23 0.22U_0402_6.3V6KCC23 0.22U_0402_6.3V6K

1 2

CC24 0.22U_0402_6.3V6KCC24 0.22U_0402_6.3V6K

1 2

CC25 0.22U_0402_6.3V6KCC25 0.22U_0402_6.3V6K

1 2

CC26 0.22U_0402_6.3V6KCC26 0.22U_0402_6.3V6K

1 2

CC27 0.22U_0402_6.3V6KCC27 0.22U_0402_6.3V6K

1 2

CC28 0.22U_0402_6.3V6KCC28 0.22U_0402_6.3V6K

1 2

CC29 0.22U_0402_6.3V6KCC29 0.22U_0402_6.3V6K

1 2

CC30 0.22U_0402_6.3V6KCC30 0.22U_0402_6.3V6K

1 2

CC31 0.22U_0402_6.3V6KCC31 0.22U_0402_6.3V6K

1 2

CC32 0.22U_0402_6.3V6KCC32 0.22U_0402_6.3V6K

PEG_CRX_GTX_P[0..15] <35>

PEG_CRX_GTX_N[0..15] <35>

PEG_CTX_GRX_P[0..15] <35>

PEG_CTX_GRX_N[0..15] <35>

PEG_CTX_GRX_P0

PEG_CTX_GRX_P1

PEG_CTX_GRX_N1

PEG_CTX_GRX_P2

PEG_CTX_GRX_N2

PEG_CTX_GRX_P3

PEG_CTX_GRX_N3

PEG_CTX_GRX_P4

PEG_CTX_GRX_N4

PEG_CTX_GRX_P5

PEG_CTX_GRX_N5

PEG_CTX_GRX_P6

PEG_CTX_GRX_N6

PEG_CTX_GRX_P7

PEG_CTX_GRX_N7

PEG_CTX_GRX_P8

PEG_CTX_GRX_N8

PEG_CTX_GRX_P9

PEG_CTX_GRX_N9

PEG_CTX_GRX_P10

PEG_CTX_GRX_N10

PEG_CTX_GRX_P11

PEG_CTX_GRX_N11

PEG_CTX_GRX_P12

PEG_CTX_GRX_N12

PEG_CTX_GRX_P13

PEG_CTX_GRX_N13

PEG_CTX_GRX_P14

PEG_CTX_GRX_N14

PEG_CTX_GRX_P15

PEG_CTX_GRX_N15

1

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

3

2012/06/11 2013/06/11

2012/06/11 2013/06/11

2012/06/11 2013/06/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

DMI,PEG

DMI,PEG

DMI,PEG

LA-9371P

LA-9371P

LA-9371P

1

4 53Friday, September 28, 2012

4 53Friday, September 28, 2012

4 53Friday, September 28, 2012

0.2

0.2

0.2

of

Page 5

5

SM_DRAMPWROK with DDR Power Gating Topology

+5VDS

CC35

CC35

1 2

0.1U_0402_10V6K

0.1U_0402_10V6K

UC1

20120923 HP's request

20120810 HP's request

D D

C C

KBC_PROC_HOT#

PM_DRAM_PWRGD<14>

1 2

+3VS

RC9 100K_0402_1%RC9 100K_0402_1%

+VCCIO_OUT

RC23 62_0402_5%RC23 62_0402_5%

13

D

D

2

G

Q59

G

Q59

S

S

2N7002KW_SOT323-3

2N7002KW_SOT323-3

PWR_GD<30,31,46>

1 2

CLK_CPU_SSC_DPLL#<15>

CLK_CPU_SSC_DPLL<15>

KBC_PROC_HOT

PCH_THERMTRIP#_R<18,35>

H_PM_SYNC<14>

H_CPUPWRGD<18>

CPU_PLTRST#<18>

CLK_CPU_DPLL#<15>

CLK_CPU_DPLL<15>

CLK_CPU_DMI#<15>

CLK_CPU_DMI<15>

KBC_PROC_HOT_R<24,46>

UC1

1

2

RUN_ON_CPU1.5VS3#<9>

RC26 56_0402_5%RC26 56_0402_5%

RC27

RC27

5

P

B

4

O

A

G

74AHC1G09GW_TSSOP5

74AHC1G09GW_TSSOP5

3

Part Number = SA00003Y000

Part Number = SA00003Y000

2

G

G

KBC_PROC_HOT_R

T120PAD @T120PAD @

T118PAD @T118PAD @

H_PECI<30>

1 2

390_0402_1%

390_0402_1%

1 2

20120911 Delete RC30 as HP's request

4

+1.35VS

12

RC5

RC5

1.8K_0402_1%

1.8K_0402_1%

12

39_0402_5%

39_0402_5%

RC10

RC10

@

@

3.3K_0402_1%

3.3K_0402_1%

RC12

RC12

1 2

13

D

D

QC1

QC1

2N7002K_SOT23-3

2N7002K_SOT23-3

S

S

CPU_DETECT#

H_CATERR#

H_PECI

T1PAD @T1PAD @

KBC_PROC_HOT_R

H_THERMTRIP#

H_PM_SYNC

H_CPUPWRGD

PM_DRAM_PWRGD_CPU

CPU_PLTRST#

PM_DRAM_PWRGD_CPU

Haswell rPGA EDS

Haswell rPGA EDS

CONN@

CONN@

JCPU1B

JCPU1B

AP32

SKTOCC

AN32

CATERR

AR27

PECI

AK31

FC_AK31

AM30

PROCHOT

AM35

THERMTRIP

AT28

PM_SYNC

AL34

PWRGOO D

AC10

SM_DRAMPW ROK

AT26

PLTRSTIN

G28

DPLL_REF _CLKN

H28

DPLL_REF _CLKP

F27

SSC_DPLL _REF_CLKN

E27

SSC_DPLL _REF_CLKP

D26

BCLKN

E26

BCLKP

INTEL_HASWELL_HASWELL

INTEL_HASWELL_HASWELL

3

+VCCIO_OUT

Place near JXDP1

ON/OFFBTN#<13,14,30>

CPU_PWR_DEBUG<9>

DDR_XDP_WAN_SMBDAT<11,12,13,16,28,38>

DDR_XDP_WAN_SMBCLK<11,12,13,16,28,38>

H_CPUPWRGD H_CPUPWRGD_XDP

PM_PWROK<14,30>

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

1

CC34

CC34

CC33

CC33

2

2

RC5 need to close to JCPU1

1 2

RC13 1K_0402_1%RC13 1K_0402_1%

1 2

RC107

RC107

20120925 HP's request

0_0402_5%

0_0402_5%

CFG0<8>

CFG1<8>

CFG2<8>

CFG3<8>

CFG4<8>

CFG5<8>

CFG6<8>

CFG7<8>

XDP_PREQ#

XDP_PRDY#

CFG0

CFG1

CFG2

CFG3

XDP_OBS0

XDP_OBS1

CFG4

CFG5

CFG6

CFG7

PM_PWROK_XDP

XDP_TCLK

2

+VCCIO_OUT +VCCIO_OUT

JXDP1

JXDP1

1

GND0

3

OBSFN_A0

5

OBSFN_A1

7

GND2

9

OBSDATA_A 0

11

OBSDATA_A 1

13

GND4

15

OBSDATA_A 2

17

OBSDATA_A 3

19

GND6

21

OBSFN_B0

23

OBSFN_B1

25

GND8

27

OBSDATA_B 0

29

OBSDATA_B 1

31

GND10

33

OBSDATA_B 2

35

OBSDATA_B 3

37

GND12

39

PWRGOO D/HOOK0

41

HOOK1

43

VCC_OBS_ AB

45

HOOK2

47

HOOK3

49

GND14

51

SDA

53

SCL

55

TCK1

57

TCK0

59

GND16

SAMTE_BSH-030-01-L-D-A

SAMTE_BSH-030-01-L-D-A

ITPCLK#/HO OK5

RESET#/HOO K6

GND1

OBSFN_C0

OBSFN_C1

GND3

OBSDATA_C0

OBSDATA_C1

GND5

OBSDATA_C2

OBSDATA_C3

GND7

OBSFN_D0

OBSFN_D1

GND9

OBSDATA_D0

OBSDATA_D1

GND11

OBSDATA_D2

OBSDATA_D3

GND13

ITPCLK/HOOK 4

VCC_OBS_ CD

DBR#/HOOK 7

GND15

TRST#

GND17

CONN@

CONN@

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

TD0

54

56

TDI

58

TMS

60

CFG17

CFG16

CFG8

CFG9

CFG10

CFG11

CFG19

CFG18

CFG12

CFG13

CFG14

CFG15

XDP_RST#_R

XDP_DBRESET#

XDP_TDO

XDP_TRST#

XDP_TDI

XDP_TMS

RC105 1K_0402_1%RC105 1K_0402_1%

1

CFG17 <8>

CFG16 <8>

CFG8 <8>

CFG9 <8>

CFG10 <8>

CFG11 <8>

CFG19 <8>

CFG18 <8>

CFG12 <8>

CFG13 <8>

CFG14 <8>

CFG15 <8>

12

RC16 1K_0402_1%RC16 1K_0402_1%

PLT_RST#

12

CFG3

PLT_RST# <13,14,25,28,29,30,35,37,39>

#4/16 change by HP requirement

1 2

@

@

RC22 0_0402_5%

MISC

MISC

THERMAL

THERMAL

DDR3

DDR3

PWR

PWR

CLOCK

CLOCK

2 OF 9

2 OF 9

SM_RCOMP_ 0

SM_RCOMP_ 1

SM_RCOMP_ 2

SM_DRAMRST

JTAG

JTAG

BPM_N_0

BPM_N_1

BPM_N_2

BPM_N_3

BPM_N_4

BPM_N_5

BPM_N_6

BPM_N_7

AP3

SM_RCOMP0

AR3

SM_RCOMP1

AP2

SM_RCOMP2

AN3

DDR3_DRAMRST#_CPU

AR29

XDP_PRDY#

PRDY

AT29

XDP_PREQ#

PREQ

AM34

XDP_TCLK

TCK

AN33

XDP_TMS

TMS

AM33

XDP_TRST#

TRST

AM31

XDP_TDI

TDI

AL33

XDP_TDO

TDO

AP33

XDP_DBRESET#

DBR

AR30

XDP_OBS0

AN31

XDP_OBS1

AN29

XDP_OBS2_R

AP31

XDP_OBS3_R

AP30

XDP_OBS4_R

AN28

XDP_OBS5_R

AP29

XDP_OBS6_R

AP28

XDP_OBS7_R

For ESD concern, please place close to CPU

RC36 0_0402_5%@RC36 0_0402_5%@

RC38 0_0402_5%@RC38 0_0402_5%@

RC40 0_0402_5%@RC40 0_0402_5%@

RC43 0_0402_5%@RC43 0_0402_5%@

RC45 0_0402_5%@RC45 0_0402_5%@

RC47 0_0402_5%@RC47 0_0402_5%@

XDP_DBRESET# <13,14>

1 2

1 2

1 2

1 2

1 2

1 2

DDR3_DRAMRST#_CPU

KBC_DS3_EN<25,29,30,44,9>

RC22 0_0402_5%

BSS138W-7-F_SOT323-3

BSS138W-7-F_SOT323-3

S

S

4.99K_0402_1%

4.99K_0402_1%

G

G

2

12

RC28

RC28

2

G

G

QC2

QC2

D

D

13

1 2

RC25 3.3K_0402_5%RC25 3.3K_0402_5%

13

D

D

QC3

QC3

2N7002K_SOT23-3

2N7002K_SOT23-3

S

S

CPU_DRAM_RST# <11>

20120725 for S3 resume as HP's request

DDR_RST_EN <16>

PU/PD for JTAG signals

SSC CLOCK TERMINATION, IF NOT USED, stuff RC20,RC21

H_CPUPWRGD

B B

CAD Note:

Avoid stub in the PWRGD path

20120911 Delete RC66 as HP's request

A A

5

4

while placing resistors RC25 & RC130

12

RC55

RC55

10K_0402_1%

10K_0402_1%

CRB Rev 0.7 is depop

3

CRB Rev 0.7 no pull up

DDR3 COMPENSATION SIGNALS

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

CAD Note:

Trace width=12~15 mil, Spcing=20 mils

Max trace length= 500 mil

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAWI NG IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONI CS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETENT DI VISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER TH IS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER TH IS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COM PAL ELECTRONICS, INC. NEITHER TH IS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIR D PARTY WITHOUT PRIOR WRITT EN CONSENT OF COMPAL ELECTRONICS, INC.

1 2

RC59 100_0402_1%RC59 100_0402_1%

1 2

RC61 75_0402_1%RC61 75_0402_1%

1 2

RC65 100_0402_1%RC65 100_0402_1%

Compal Secret Data

Compal Secret Data

2012/06/11 2013/06/11

2012/06/11 2013/06/11

2012/06/11 2013/06/11

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

XDP_DBRESET#

RC52 1K_0402_1%RC52 1K_0402_1%

XDP_TDO

RC57 51_0402_1%RC57 51_0402_1%

XDP_TCLK

RC60 51_0402_1%RC60 51_0402_1%

XDP_TRST#

RC62 51_0402_1%RC62 51_0402_1%

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

PM,XDP,CLK

PM,XDP,CLK

PM,XDP,CLK

12

12

12

12

LA-9371P

LA-9371P

LA-9371P

1

+3VS

+1.05VS

0.2

0.2

5 53Friday, September 28, 2012

5 53Friday, September 28, 2012

5 53Friday, September 28, 2012

0.2

Page 6

5

D D

DDR_A_D[0..63]<11>

C C

B B

+SM_VREF_CA

+DIMM01_VREF_DQ

+DIMM23_VREF_DQ

20120710 Change by HP request

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

AR15

SA_DQ_0

AT14

SA_DQ_1

AM14

SA_DQ_2

AN14

SA_DQ_3

AT15

SA_DQ_4

AR14

SA_DQ_5

AN15

SA_DQ_6

AM15

SA_DQ_7

AM9

SA_DQ_8

AN9

SA_DQ_9

AM8

SA_DQ_10

AN8

SA_DQ_11

AR9

SA_DQ_12

AT9

SA_DQ_13

AR8

SA_DQ_14

AT8

SA_DQ_15

AJ9

SA_DQ_16

AK9

SA_DQ_17

AJ6

SA_DQ_18

AK6

SA_DQ_19

AJ10

SA_DQ_20

AK10

SA_DQ_21

AJ7

SA_DQ_22

AK7

SA_DQ_23

AF4

SA_DQ_24

AF5

SA_DQ_25

AF1

SA_DQ_26

AF2

SA_DQ_27

AG4

SA_DQ_28

AG5

SA_DQ_29

AG1

SA_DQ_30

AG2

SA_DQ_31

J1

SA_DQ_32

J2

SA_DQ_33

J5

SA_DQ_34

H5

SA_DQ_35

H2

SA_DQ_36

H1

SA_DQ_37

J4

SA_DQ_38

H4

SA_DQ_39

F2

SA_DQ_40

F1

SA_DQ_41

D2

SA_DQ_42

D3

SA_DQ_43

D1

SA_DQ_44

F3

SA_DQ_45

C3

SA_DQ_46

B3

SA_DQ_47

B5

SA_DQ_48

E6

SA_DQ_49

A5

SA_DQ_50

D6

SA_DQ_51

D5

SA_DQ_52

E5

SA_DQ_53

B6

SA_DQ_54

A6

SA_DQ_55

E12

SA_DQ_56

D12

SA_DQ_57

B11

SA_DQ_58

A11

SA_DQ_59

E11

SA_DQ_60

D11

SA_DQ_61

B12

SA_DQ_62

A12

SA_DQ_63

AM3

SM_VREF

F16

SA_DIMM_VREFDQ

F13

SB_DIMM_VREFDQ

I

I

NTEL_HASWELL_HASWELL

NTEL_HASWELL_HASWELL

3 OF 9

3 OF 9

4

Haswell rPGA EDS

Haswell rPGA EDS

JCPU1C

JCPU1C

CONN@

CONN@

SA_CK_N_0

SA_CK_P_0

SA_CKE_0

SA_CK_N_1

SA_CK_P_1

SA_CKE_1

SA_CK_N_2

SA_CK_P_2

SA_CKE_2

SA_CK_N_3

SA_CK_P_3

SA_CKE_3

SA_CS_N_0

SA_CS_N_1

SA_CS_N_2

SA_CS_N_3

SA_ODT_0

SA_ODT_1

SA_ODT_2

SA_ODT_3

SA_BS_0

SA_BS_1

SA_BS_2

SA_RAS

SA_WE

SA_CAS

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

SA_MA_15

SA_DQS_N_0

SA_DQS_N_1

SA_DQS_N_2

SA_DQS_N_3

SA_DQS_N_4

SA_DQS_N_5

SA_DQS_N_6

SA_DQS_N_7

SA_DQS_P_0

SA_DQS_P_1

SA_DQS_P_2

SA_DQS_P_3

SA_DQS_P_4

SA_DQS_P_5

SA_DQS_P_6

SA_DQS_P_7

RSVD

VSS

AC7

U4

M_CLK_A_DDR#0

V4

M_CLK_A_DDR0

AD9

DDR_CKE0_DIMMA

U3

M_CLK_A_DDR#1

V3

M_CLK_A_DDR1

AC9

DDR_CKE1_DIMMA

U2

M_CLK_A_DDR#2

V2

M_CLK_A_DDR2

AD8

DDR_CKE2_DIMMA

U1

M_CLK_A_DDR#3

V1

M_CLK_A_DDR3

AC8

DDR_CKE3_DIMMA

M7

DDR_CS0_DIMMA#

L9

DDR_CS1_DIMMA#

M9

DDR_CS2_DIMMA#

M10

DDR_CS3_DIMMA#

M8

M_A_ODT0

L7

M_A_ODT1

L8

M_A_ODT2

L10

M_A_ODT3

V5

DDR_A_BS0

U5

DDR_A_BS1

AD1

DDR_A_BS2

V10

U6

DDR_A_RAS#

U7

DDR_A_WE#

U8

DDR_A_CAS#

V8

DDR_A_MA0

AC6

DDR_A_MA1

V9

DDR_A_MA2

U9

DDR_A_MA3

AC5

DDR_A_MA4

AC4

DDR_A_MA5

AD6

DDR_A_MA6

AC3

DDR_A_MA7

AD5

DDR_A_MA8

AC2

DDR_A_MA9

V6

DDR_A_MA10

AC1

DDR_A_MA11

AD4

DDR_A_MA12

V7

DDR_A_MA13

AD3

DDR_A_MA14

AD2

DDR_A_MA15

AP15

DDR_A_DQS#0

AP8

DDR_A_DQS#1

AJ8

DDR_A_DQS#2

AF3

DDR_A_DQS#3

J3

DDR_A_DQS#4

E2

DDR_A_DQS#5

C5

DDR_A_DQS#6

C11

DDR_A_DQS#7

AP14

DDR_A_DQS0

AP9

DDR_A_DQS1

AK8

DDR_A_DQS2

AG3

DDR_A_DQS3

H3

DDR_A_DQS4

E3

DDR_A_DQS5

C6

DDR_A_DQS6

C12

DDR_A_DQS7

M_CLK_A_DDR#0 <11>

M_CLK_A_DDR0 <11>

DDR_CKE0_DIMMA <11>

M_CLK_A_DDR#1 <11>

M_CLK_A_DDR1 <11>

DDR_CKE1_DIMMA <11>

M_CLK_A_DDR#2 <11>

M_CLK_A_DDR2 <11>

DDR_CKE2_DIMMA <11>

M_CLK_A_DDR#3 <11>

M_CLK_A_DDR3 <11>

DDR_CKE3_DIMMA <11>

DDR_CS0_DIMMA# <11>

DDR_CS1_DIMMA# <11>

DDR_CS2_DIMMA# <11>

DDR_CS3_DIMMA# <11>

M_A_ODT0 <11>

M_A_ODT1 <11>

M_A_ODT2 <11>

M_A_ODT3 <11>

DDR_A_BS0 <11>

DDR_A_BS1 <11>

DDR_A_BS2 <11>

DDR_A_RAS# <11>

DDR_A_WE# <11>

DDR_A_CAS# <11>

DDR_A_MA[0..15] <11>

DDR_A_DQS#[0..7] <11>

DDR_A_DQS[0..7] <11>

3

DDR_B_D[0..63]<12>

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

AR18

SB_DQ_0

AT18

SB_DQ_1

AM17

SB_DQ_2

AM18

SB_DQ_3

AR17

SB_DQ_4

AT17

SB_DQ_5

AN17

SB_DQ_6

AN18

SB_DQ_7

AT12

SB_DQ_8

AR12

SB_DQ_9

AN12

SB_DQ_10

AM11

SB_DQ_11

AT11

SB_DQ_12

AR11

SB_DQ_13

AM12

SB_DQ_14

AN11

SB_DQ_15

AR5

SB_DQ_16

AR6

SB_DQ_17

AM5

SB_DQ_18

AM6

SB_DQ_19

AT5

SB_DQ_20

AT6

SB_DQ_21

AN5

SB_DQ_22

AN6

SB_DQ_23

AJ4

SB_DQ_24

AK4

SB_DQ_25

AJ1

SB_DQ_26

AJ2

SB_DQ_27

AM1

SB_DQ_28

AN1

SB_DQ_29

AK2

SB_DQ_30

AK1

SB_DQ_31

L2

SB_DQ_32

M2

SB_DQ_33

L4

SB_DQ_34

M4

SB_DQ_35

L1

SB_DQ_36

M1

SB_DQ_37

L5

SB_DQ_38

M5

SB_DQ_39

G7

SB_DQ_40

J8

SB_DQ_41

G8

SB_DQ_42

G9

SB_DQ_43

J7

SB_DQ_44

J9

SB_DQ_45

G10

SB_DQ_46

J10

SB_DQ_47

A8

SB_DQ_48

B8

SB_DQ_49

A9

SB_DQ_50

B9

SB_DQ_51

D8

SB_DQ_52

E8

SB_DQ_53

D9

SB_DQ_54

E9

SB_DQ_55

E15

SB_DQ_56

D15

SB_DQ_57

A15

SB_DQ_58

B15

SB_DQ_59

E14

SB_DQ_60

D14

SB_DQ_61

A14

SB_DQ_62

B14

SB_DQ_63

I

I

NTEL_HASWELL_HASWELL

NTEL_HASWELL_HASWELL

JCPU1D

JCPU1D

4 OF 9

4 OF 9

CONN@

CONN@

2

Haswell rPGA EDS

Haswell rPGA EDS

RSVD

SB_CKN0

SB_CK0

SB_CKE_0

SB_CKN1

SB_CK1

SB_CKE_1

SB_CKN2

SB_CK2

SB_CKE_2

SB_CKN3

SB_CK3

SB_CKE_3

SB_CS_N_0

SB_CS_N_1

SB_CS_N_2

SB_CS_N_3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_BS_0

SB_BS_1

SB_BS_2

SB_RAS

SB_WE

SB_CAS

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SB_DQS_N_0

SB_DQS_N_1

SB_DQS_N_2

SB_DQS_N_3

SB_DQS_N_4

SB_DQS_N_5

SB_DQS_N_6

SB_DQS_N_7

SB_DQS_P_0

SB_DQS_P_1

SB_DQS_P_2

SB_DQS_P_3

SB_DQS_P_4

SB_DQS_P_5

SB_DQS_P_6

SB_DQS_P_7

VSS

AG8

Y4

M_CLK_B_DDR#0

AA4

M_CLK_B_DDR0

AF10

DDR_CKE0_DIMMB

Y3

M_CLK_B_DDR#1

AA3

M_CLK_B_DDR1

AG10

DDR_CKE1_DIMMB

Y2

M_CLK_B_DDR#2

AA2

M_CLK_B_DDR2

AG9

DDR_CKE2_DIMMB

Y1

M_CLK_B_DDR#3

AA1

M_CLK_B_DDR3

AF9

DDR_CKE3_DIMMB

P4

DDR_CS0_DIMMB#

R2

DDR_CS1_DIMMB#

P3

DDR_CS2_DIMMB#

P1

DDR_CS3_DIMMB#

R4

M_B_ODT0

R3

M_B_ODT1

R1

M_B_ODT2

P2

M_B_ODT3

R7

DDR_B_BS0

P8

DDR_B_BS1

AA9

DDR_B_BS2

R10

R6

DDR_B_RAS#

P6

DDR_B_WE#

P7

DDR_B_CAS#

R8

DDR_B_MA0

Y5

DDR_B_MA1

Y10

DDR_B_MA2

AA5

DDR_B_MA3

Y7

DDR_B_MA4

AA6

DDR_B_MA5

Y6

DDR_B_MA6

AA7

DDR_B_MA7

Y8

DDR_B_MA8

AA10

DDR_B_MA9

R9

DDR_B_MA10

Y9

DDR_B_MA11

AF7

DDR_B_MA12

P9

DDR_B_MA13

AA8

DDR_B_MA14

AG7

DDR_B_MA15

AP18

DDR_B_DQS#0

AP11

DDR_B_DQS#1

AP5

DDR_B_DQS#2

AJ3

DDR_B_DQS#3

L3

DDR_B_DQS#4

H9

DDR_B_DQS#5

C8

DDR_B_DQS#6

C14

DDR_B_DQS#7

AP17

DDR_B_DQS0

AP12

DDR_B_DQS1

AP6

DDR_B_DQS2

AK3

DDR_B_DQS3

M3

DDR_B_DQS4

H8

DDR_B_DQS5

C9

DDR_B_DQS6

C15

DDR_B_DQS7

T3 PAD~D@T3 PA D~D@

M_CLK_B_DDR#0 <12>

M_CLK_B_DDR0 <12>

DDR_CKE0_DIMMB <12>

M_CLK_B_DDR#1 <12>

M_CLK_B_DDR1 <12>

DDR_CKE1_DIMMB <12>

M_CLK_B_DDR#2 <12>

M_CLK_B_DDR2 <12>

DDR_CKE2_DIMMB <12>

M_CLK_B_DDR#3 <12>

M_CLK_B_DDR3 <12>

DDR_CKE3_DIMMB <12>

DDR_CS0_DIMMB# <12>

DDR_CS1_DIMMB# <12>

DDR_CS2_DIMMB# <12>

DDR_CS3_DIMMB# <12>

M_B_ODT0 <12>

M_B_ODT1 <12>

M_B_ODT2 <12>

M_B_ODT3 <12>

DDR_B_BS0 <12>

DDR_B_BS1 <12>

DDR_B_BS2 <12>

DDR_B_RAS# <12>

DDR_B_WE# <12>

DDR_B_CAS# <12>

1

DDR_B_MA[0..15] <12>

DDR_B_DQS#[0..7] <12>

DDR_B_DQS[0..7] <12>

+SM_VREF_CA +DIMM23_VREF_DQ+DIMM01_VREF_DQ

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

CC84

CC84

2

Layout Notes

A A

5

L

Place CC84,CC85,CC86 close to JCPU1

0.1U_0402_16V4Z

1

CC85

CC85

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

1

CC86

CC86

2

20120802 HP's request

4

20120710 Change by HP request

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2012/06/11 2013/06/11

2012/06/11 2013/06/11

2012/06/11 2013/06/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

DDRIII

DDRIII

DDRIII

LA-9371P

LA-9371P

LA-9371P

6 53Friday, September 28, 2012

6 53Friday, September 28, 2012

6 53Friday, September 28, 2012

1

0.2

0.2

0.2

Page 7

5

D D

4

3

2

1

COMPENSATION PU FOR eDP

+VCCIOA_OUT

EDP_COMP

CAD Note:Trace width=20 mils ,Spacing=25mil,

Haswell rPGA EDS

Haswell rPGA EDS

T28

DDIB_TXBN_0

U28

DDIB_TXBP_0

T30

C C

DDIB_TXBN_1

U30

DDIB_TXBP_1

U29

DDIB_TXBN_2

V29

DDIB_TXBP_2

U31

DDIB_TXBN_3

V31

DDIB_TXBP_3

T34

DDIC_TXCN_0

U34

DDIC_TXCP_0

U35

DDIC_TXCN_1

V35

DDIC_TXCP_1

U32

DDIC_TXCN_2

T32

DDIC_TXCP_2

U33

DDIC_TXCN_3

V33

DDIC_TXCP_3

P29

DDID_TXDN_0

R29

DDID_TXDP_0

N28

DDID_TXDN_1

P28

DDID_TXDP_1

P31

DDID_TXDN_2

R31

DDID_TXDP_2

N30

DDID_TXDN_3

P30

DDID_TXDP_3

INTEL_HASWELL_HAS WELL

INTEL_HASWELL_HAS WELL

eDP

eDP

CONN@

CONN@

EDP_AUXN

EDP_AUXP

EDP_HPD

EDP_RCOMP

EDP_DISP_UT IL

EDP_TXN_0

EDP_TXP_0

EDP_TXN_1

EDP_TXP_1

FDI_TXN_0

FDI_TXP_0

FDI_TXN_1

FDI_TXP_1

DDI

DDI

8 OF 9

8 OF 9

JCPU1H

JCPU1H

M27

EDP_CPU_C_AUX#

N27

EDP_CPU_C_AUX

P27

EDP_HPD

E24

EDP_COMP

R27

P35

EDP_CPU_C_LANE_N0

R35

EDP_CPU_C_LANE_P0

N34

EDP_CPU_C_LANE_N1

P34

EDP_CPU_C_LANE_P1

P33

R33

N32

P32

C126 0.1U_0402_25V6C126 0.1U_0402_25V6

C127 0.1U_0402_25V6C127 0.1U_0402_25V6

T119 PAD@T119 PAD@

C128 0.1U_0402_25V6C128 0.1U_0402_25V6

C129 0.1U_0402_25V6C129 0.1U_0402_25V6

C130 0.1U_0402_25V6C130 0.1U_0402_25V6

C131 0.1U_0402_25V6C131 0.1U_0402_25V6

1 2

1 2

1 2

1 2

1 2

1 2

Max length=100 mils.

FDI_CTX_PRX_N0

FDI_CTX_PRX_P0

FDI_CTX_PRX_N1

FDI_CTX_PRX_P1

+VCCIO_OUT

HPD INVERSION FOR EDP

B B

CPU_EDP_HPD#<36>

2

G

G

100K_0402_5%

100K_0402_5%

12

RC79

RC79

12

RC7724.9_0402_1% RC7724.9_0402_1%

EDP_CPU_AUX# <36>

EDP_CPU_AUX <36>

EDP_CPU_LANE_N0 <36>

EDP_CPU_LANE_P0 <36>

EDP_CPU_LANE_N1 <36>

EDP_CPU_LANE_P1 <36>

FDI_CTX_PRX_N0 <14>

FDI_CTX_PRX_P0 <14>

FDI_CTX_PRX_N1 <14>

FDI_CTX_PRX_P1 <14>

12

RC78

RC78

10K_0402_5%

10K_0402_5%

20120807 Change RC78 to 10K as HP's request

EDP_HPD

13

D

D

QH1

QH1

BSS138W-7-F_SOT323-3

BSS138W-7-F_SOT323-3

S

S

SB000002X00

SB000002X00

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

3

2012/06/11 2013/06/11

2012/06/11 2013/06/11

2012/06/11 2013/06/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet

Compal Electronics, Inc.

CPU-FDI,eDP,DDI

CPU-FDI,eDP,DDI

CPU-FDI,eDP,DDI

LA-9371P

LA-9371P

LA-9371P

1

7 53Friday, September 28, 2012

7 53Friday, September 28, 2012

7 53Friday, September 28, 2012

0.2

0.2

0.2

of

Page 8

5

4

3

2

1

CFG STRAPS for CPU

CFG2

D D

PEG Static Lane Reversal - CFG2 is for the 16x

1:(Default) Normal Operation; Lane #

CFG2

definition matches socket pin map definition

0:Lane Reversed

Haswell rPGA EDS

Haswell rPGA EDS

JCPU1I

JCPU1I

AT1

RSVD_TP

AT2

RSVD_TP

AD10

RSVD

A34

RSVD_TP

A35

RSVD_TP

T15 PAD~D@T15 PAD ~D@

T12 PAD~D@T12 PAD ~D@

T16 PAD~D@T16 PAD ~D@

C C

12

B B

RC84 49.9_0402_1%RC84 49.9_0402_1%

RC85 49.9_0402_1%RC85 49.9_0402_1%

RC86 49.9_0402_1%RC86 49.9_0402_1%

H_CPU_TESTLO

12

CFG_RCOMP

12

H_CPU_RSVD

T17 PAD~D@T17 PAD~D@

T26 PAD~D@T26 PAD ~D@

T28 PAD~D@T28 PAD ~D@

CFG0<5>

CFG1<5>

CFG2<5>

CFG3<5>

CFG4<5>

CFG5<5>

CFG6<5>

CFG7<5>

CFG8<5>

CFG9<5>

CFG10<5>

CFG11<5>

CFG12<5>

CFG13<5>

CFG14<5>

CFG15<5>

+VCC_CORE

H_CPU_RSVD

H_CPU_TESTLO

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

W29

RSVD_TP

W28

RSVD_TP

G26

TESTLO_G26

W33

RSVD

AL30

RSVD

AL29

RSVD

F25

VCC

C35

RSVD_TP

B35

RSVD_TP

AL25

RSVD_TP

W30

RSVD_TP

W31

RSVD_TP

W34

TESTLO

AT20

CFG_0

AR20

CFG_1

AP20

CFG_2

AP22

CFG_3

AT22

CFG_4

AN22

CFG_5

AT25

CFG_6

AN23

CFG_7

AR24

CFG_8

AT23

CFG_9

AN20

CFG_10

AP24

CFG_11

AP26

CFG_12

AN25

CFG_13

AN26

CFG_14

AP25

CFG_15

INTEL_HASWELL_HAS WELL

INTEL_HASWELL_HAS WELL

CONN@

CONN@

CFG_RCOMP

9 OF 9

9 OF 9

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

CFG_16

CFG_18

CFG_17

CFG_19

RSVD

FC_G6

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

VSS

VSS

C23

B23

D24

D23

AT31

CFG_RCOMP

AR21

CFG16

AR23

CFG18

AP21

CFG17

AP23

CFG19

AR33

G6

AM27

AM26

F5

AM2

K6

E18

U10

P10

B1

NC

A2

AR1

E21

E20

AP27

AR26

AL31

AL32

CFG16 < 5>

CFG18 < 5>

CFG17 < 5>

CFG19 < 5>

20120710 Delete RC106/RC107

CFG4

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2

CFG[6:5]

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

CFG4

Display Port Presence Strap

CFG6

CFG5

PCIE Port Bifurcation Straps

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

CFG9

1K_0402_1%

1K_0402_1%

12

@RC106

@

RC106

CFG7

1K_0402_1%

1K_0402_1%

12

RC80

RC80

1K_0402_1%

1K_0402_1%

12

RC81

RC81

1K_0402_1%

1K_0402_1%

1K_0402_1%

1K_0402_1%

12

12

@RC83

@RC82

@

RC82

@

RC83

1K_0402_1%

1K_0402_1%

12

@RC87

@

RC87

2012/09/21 For a Intel Sighting

PEG DEFER TRAINING

1: (Default) PEG Train immediately

CFG7

following xxRESETB de assertion

0: PEG Wait for BIOS for training

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELEC TRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRAN SFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSE NT OF COMPAL ELECTRONICS, INC.

3

2012/06/11 2013/06/11

2012/06/11 2013/06/11

2012/06/11 2013/06/11

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

CPU-RSVD,CFG

CPU-RSVD,CFG

CPU-RSVD,CFG

LA-9371P

LA-9371P

LA-9371P

1

8 53Friday, September 28, 2012

8 53Friday, September 28, 2012

8 53Friday, September 28, 2012

0.2

0.2

0.2

Page 9

5

+1.35VS Source

4

3

2

1

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AA26

AA28

AA34

AA30

AA32

AB26

AB29

AB25

AB27

AB28

AB30

AB31

AB33

AB34

AB32

AC26

AB35

AC28

AD25

AC30

AD28

AC32

AD31

AC34

AD34

AD26

AD27

AD29

AD30

AD32

AD33

AD35

AE26

AE32

AE28

AE30

AG28

AG34

AE34

AF25

AF26

AF27

AF28

AF29

AF30

AF31

AF32

AF33

AF34

AF35

AG26

AH26

AH29

AG30

AG32

AH32

AH35

AH25

AH27

AH28

AH30

AH31

AH33

AH34

AJ25

AJ26

AJ27

AJ28

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

G25

H25

J25

K25

L25

M25

N25

P25

R25

T25

U25

U26

V25

V26

W26

W27

+VCC_CORE

B+

4/20 change by HP

requirement

D D

C C

SVID ALERT

KBC_DS3_EN<25,29,30,44,5>

SLP_S3#<14,30,31,34,39,44>

RC90 4.7K_0402_5%RC90 4.7K_0402_5%

1 2

20120911 Delete RC93

as HP's request

20K_0402_5%

20K_0402_5%

5

CAD Note: Place the PU resistors close to CPU

RC60 close to CPU 300 - 1500mils

12

R461

R461

RUN_ON_CPU1.5VS3#

34

DMN66D0LDW-7_SOT363-6

DMN66D0LDW-7_SOT363-6

QC5B

QC5B

SVID DATA

CAD Note: Place the PU resistors close to CPU

RC63 close to CPU 300 - 1500mils

+VCC_CORE

100_0402_1%

B B

VCC_SENSE

VCCSENSE<46>

VSSSENSE<10,46>

100_0402_1%

12

RC101

RC101

CAD Note: RC102 SHOULD BE PLACED CLOSE TO CPU

VCCSENSE

20120911 Delete RC102, RC103 as HP's request

100_0402_1%

100_0402_1%

12

CAD Note: RC103 SHOULD BE PLACED CLOSE TO CPU

RC104

RC104

VSSSENSE

B+ +1.35VS

12

RC88

@

@

RC88

100K_0402_5%

100K_0402_5%

RUN_ON_CPU1.5VS3

61

DMN66D0LDW-7_SOT363-6

DMN66D0LDW-7_SOT363-6

2

QC5A

QC5A

RUN_ON_CPU1.5VS3# <5>

+1.35V

SI7326DN-T1-GE3_PAK1212-8-5

SI7326DN-T1-GE3_PAK1212-8-5

5

RC92

RC92

330K_0402_5%

330K_0402_5%

QC4

QC4

12

1

2

3

12

4

1

CC39

CC39

2

0.1U_0402_25V6

0.1U_0402_25V6

RUN_ON_CPU1.5VS3 <11,12>

R6

R6

@

@

20K_0402_5%

20K_0402_5%

D

D

S

S

RESISTOR STUFFING OPTIONS ARE

PROVIDED FOR TESTING PURPOSES

+1.35VS

RC89

RC89

470_0603_5%

470_0603_5%

1 2

13

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

G

G

Q2

Q2

2N7002K_SOT23-3

2N7002K_SOT23-3

CC42

CC42

2

RUN_ON_CPU1.5VS3#

20120725 HP's request

VDDQ DECOUPLING

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

CC43

CC43

CC44

CC44

2

2

Haswell rPGA EDS

Haswell rPGA EDS

CONN@

CONN@

JCPU1E

JCPU1E

K27

RSVD

L27

RSVD

T27

RSVD

V27

+1.35VS

CC38 0.1U_0402_10V6KCC38 0.1U_0402_10V6K

12

CC40 0.1U_0402_10V6KCC40 0.1U_0402_10V6K

12

+VCC_CORE

VCCSENSE

+VCCIO_OUT

T54

@ T54

@

PAD~D

PAD~D

+VCCIOA_OUT

VR_SVID_ALRT#<46>

VR_SVID_CLK<46>

+1.05VS

12

RC98

RC98

150_0402_1%

150_0402_1%

CPU_PWR_DEBUG

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

1

CC45

CC45

CC46

CC46

2

2

10U_0603_6.3V6M

1

1

CC47

CC47

CC48

CC48

CC49

CC49

2

2

VR_SVID_DAT<46>

CPU_PWR_DEBUG<5>

T50 PAD~D@T50 PAD~D@

T51 PAD~D@T51 PAD~D@

T52 PAD~D@T52 PAD~D@

T53 PAD~D@T53 PAD~D@

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

10U_0603_6.3V6M

1

2

330U_D2_2V_Y

330U_D2_2V_Y

1

1

+

+

CC41

CC41

CC51

CC51

CC50

CC50

2

2

VR_SVID_ALRT#

VR_SVID_CLK

VR_SVID_DAT

+VCC_CORE

330U_D2_2V_Y

330U_D2_2V_Y

1

+

+

CC87

CC87

2

@

@

20120806 Add CC87 as Intel's reply

RSVD

AB11

VDDQ

AB2

VDDQ

AB5

VDDQ

AB8

VDDQ

AE11

VDDQ

AE2

VDDQ

AE5

VDDQ

AE8

VDDQ

AH11

VDDQ

K11

VDDQ

N11

VDDQ

N8

VDDQ

T11

VDDQ

T2

VDDQ

T5

VDDQ

T8

VDDQ

W11

VDDQ

W2

VDDQ

W5

VDDQ

W8

VDDQ

N26

RSVD

K26

VCC

AL27

RSVD

AK27

RSVD

AL35

VCC_SENSE

E17

RSVD

AN35

VCCIO_OUT

A23

RSVD

F22

VCOMP_OUT

W32

RSVD

AL16

RSVD

J27

RSVD

AL13

RSVD

AM28

VIDALERT

AM29

VIDSCLK

AL28

VIDSOUT

AP35

VSS

H27

PWR_DEBUG

AP34

VSS

AT35

RSVD_TP

AR35

RSVD_TP

AR32

RSVD_TP

AL26

RSVD_TP

AT34

VSS

AL22

VSS

AT33

VSS

AM21

VSS

AM25

VSS

AM22

VSS

AM20

VSS

AM24

VSS

AL19

VSS

AM23

VSS

AT32

VSS

Y25

VCC

Y26

VCC

Y27

VCC

Y28

VCC

Y29

VCC

Y30

VCC

Y31

VCC

Y32

VCC

Y33

VCC

Y34

VCC

Y35

VCC

I

I

NTEL_HASWELL_HASWELL

NTEL_HASWELL_HASWELL

5 OF 9

5 OF 9

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

CH2

CH2

CH1

CH1

1

1

1

2

2

2

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

22U_0805_6.3V6M

CH3

CH3

CH4

CH4

1

1

2

2

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

CH5

CH5

CH6

CH6

1

1

2

2

2012/06/11 2013/06/11

2012/06/11 2013/06/11

2012/06/11 2013/06/11

22U_0805_6.3V6M

22U_0805_6.3V6M

CH8

CH8

CH7

CH7

1

1

2

2

Compal Secret Data

Compal Secret Data

Compal Secret Data

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

22U_0805_6.3V6M

CH10

CH10

CH9

CH9

1

1

2

2

Deciphered Date

Deciphered Date

Deciphered Date

22U_0805_6.3V6M

22U_0805_6.3V6M

CH11

CH11

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet of

2

Date: Sheet of

Compal Electronics, Inc.

CPU- PWR

CPU- PWR

CPU- PWR

LA-9371P

LA-9371P

LA-9371P

1

9 53Friday, September 28, 2012

9 53Friday, September 28, 2012

9 53Friday, September 28, 2012

0.2

0.2

0.2

of

Page 10

5

4

3

2

1

D D

C C

B B

Haswell rPGA EDS

Haswell rPGA EDS

A10

VSS

A13

VSS

A16

VSS

A19

VSS

A22

VSS

A25

VSS

A27

VSS

A29

VSS

A3

VSS

A31

VSS

A33

VSS

A4

VSS

A7

VSS

AA11

VSS

AA25

VSS

AA27

VSS

AA31

VSS

AA29

VSS

AB1

VSS

AB10

VSS

AA33

VSS

AA35

VSS

AB3

VSS

AC25

VSS

AC27

VSS

AB4

VSS

AB6

VSS

AB7

VSS

AB9

VSS

AC11

VSS

AD11

VSS

AC29

VSS

AC31

VSS

AC33

VSS

AC35

VSS

AD7

VSS

AE1

VSS

AE10

VSS

AE25

VSS

AE29

VSS

AE3

VSS

AE27

VSS

AE35

VSS

AE4

VSS

AE6

VSS

AE7

VSS

AE9

VSS

AF11

VSS

AF6

VSS

AF8

VSS

AG11

VSS

AG25

VSS

AE31

VSS

AG31

VSS

AE33

VSS

AG6

VSS

AH1

VSS

AH10

VSS

AH2

VSS

AG27

VSS

AG29

VSS

AH3

VSS

AG33

VSS

AG35

VSS

AH4

VSS

AH5

VSS

AH6

VSS

AH7

VSS

AH8

VSS

AH9

VSS

AJ11

VSS

AJ5

VSS

AK11

VSS

AK25

VSS

AK26

VSS

AK28

VSS

AK29

VSS

AK30

VSS

AK32

VSS

E19

VSS

NTEL_HASWELL_HA SWELL

NTEL_HASWELL_HA SWELL

I

I

JCPU1F

JCPU1F

6 OF 9

6 OF 9

CONN@

CONN@

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AK34

AK5

AL1

AL10

AL11

AL12

AL14

AL15

AL17

AL18

AL2

AL20

AL21

AL23

E22

AL3

AL4

AL5

AL6

AL7

AL8

AL9

AM10

AM13

AM16

AM19

E25

AM32

AM4

AM7

AN10

AN13

AN16

AN19

AN2

AN21

AN24

AN27

AN30

AN34

AN4

AN7

AP1

AP10

AP13

AP16

AP19

AP4

AP7

W25

AR10

AR13

AR16

AR19

AR2

AR22

AR25

AR28

AR31

AR34

AR4

AR7

AT10

AT13

AT16

AT19

AT21

AT24

AT27

AT3

AT30

AT4

AT7

B10

B13

B16

B19

B2

B22

Haswell rPGA EDS

Haswell rPGA EDS

B34

VSS

B4

VSS

B7

VSS

C1

VSS

C10

VSS

C13

VSS

C16

VSS

C19

VSS

C2

VSS

C22

VSS

C24

VSS

C26

VSS

C28

VSS

C30

VSS

C32

VSS

C34

VSS

C4

VSS

C7

VSS

D10

VSS

D13

VSS

D16

VSS

D19

VSS

D22

VSS

D25

VSS

D27

VSS

D29

VSS

D31

VSS

D33

VSS

D35

VSS

D4

VSS

D7

VSS

E1

VSS

E10

VSS

E13

VSS

E16

VSS

E4

VSS

E7

VSS

F10

VSS

F11

VSS

F12