Page 1

A

ZZZ0

ZZZ0

PCB

PCB

MB

MB

1 1

B

C

D

E

Compal Confidential

2 2

PICASSO M Schematics Document

Nvdia(T30S) + LPDDRII

QAJA0-LA-8511P

2012-01-18

※

3 3

4 4

A

The content in this document contains confidential information of Compal Electronics, Inc.

that is protected under all applicable trade secrets laws and regulations.

If you are not the intended recipient or otherwise authorized to receive such information,

please do not copy, distribute or otherwise use the information contained herein and please

destroy this communication accordingly.

B

REV: 1.0

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

2012/06/202011/06/20

2012/06/202011/06/20

2012/06/202011/06/20

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

Picasso 2 R04

Picasso 2 R04

Wednesday, January 18, 2012

Wednesday, January 18, 2012

Wednesday, January 18, 2012

Picasso 2 R04

E

1.0

1.0

1

1

1

1.0

38

38

38

Page 2

A

B

C

D

E

Compal Confidential

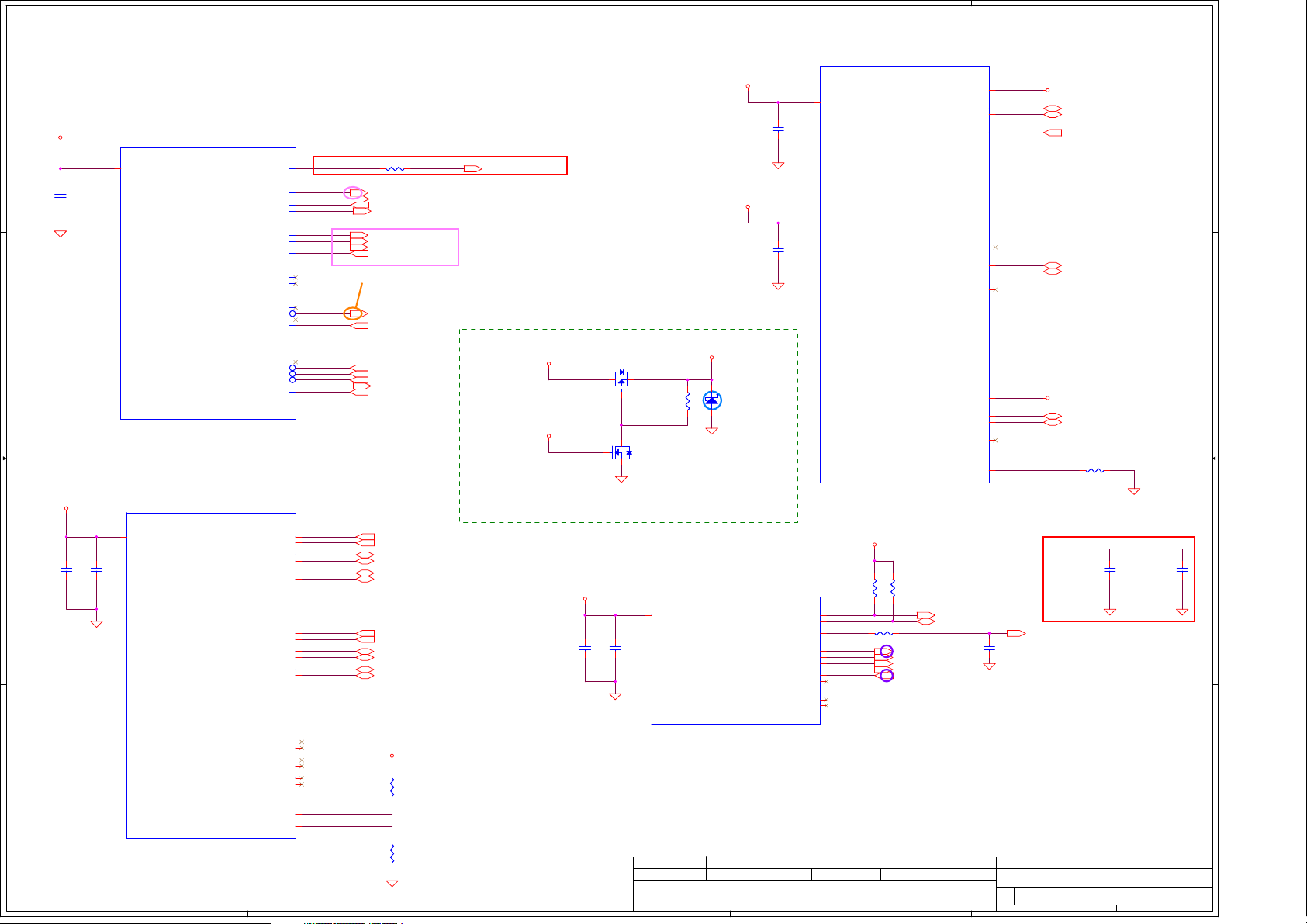

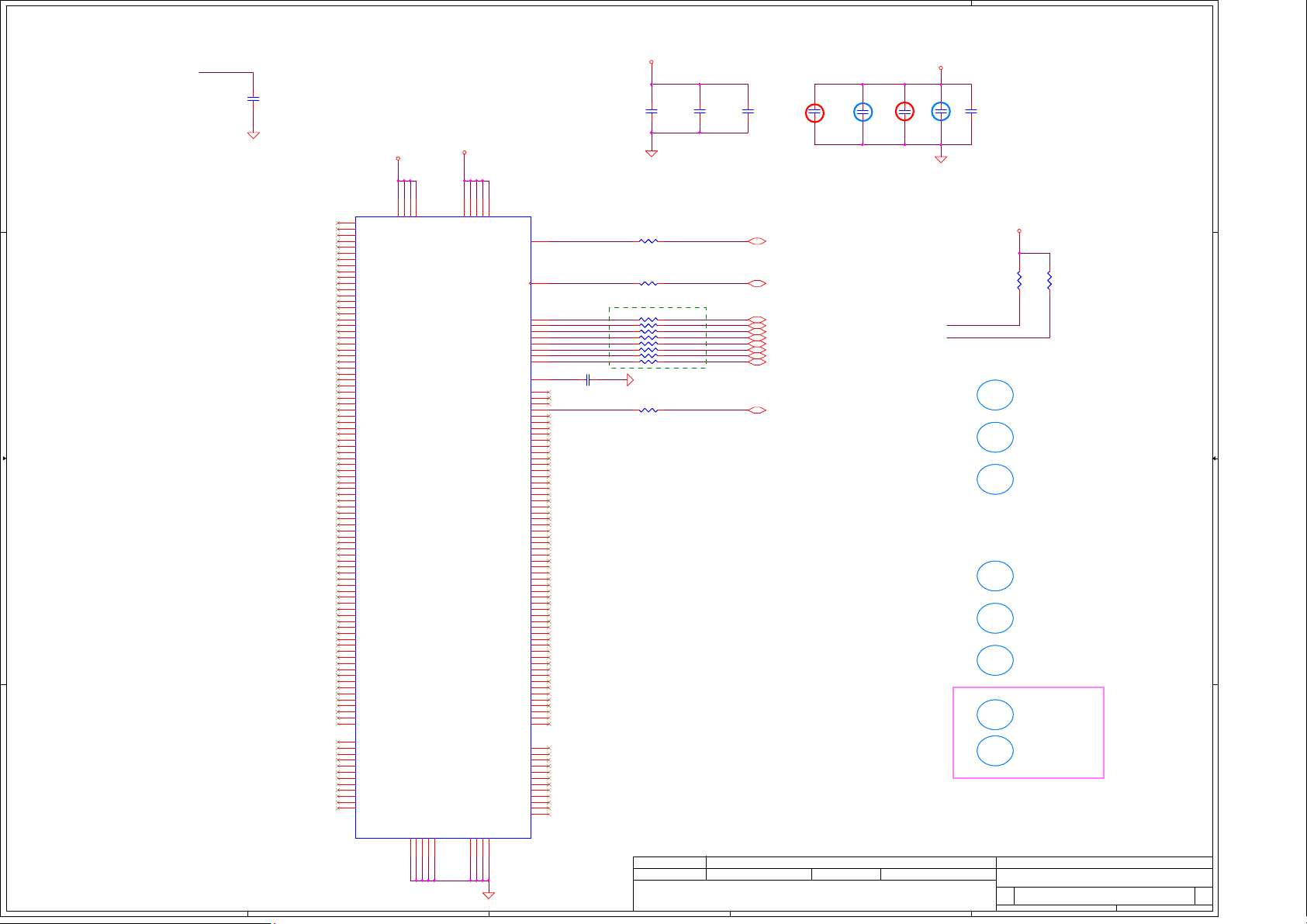

Model Name : NVIDIA T30S System Block Diagram

26MHz

32KHz

1 1

PMIC

T

PS659110

Power ON

VIN

P.31~P.33

2 2

Micro HDMI

P.19

HDMI Switch

(1.8V/3.3V)

CORE_PWR_REQ

CPU_PWR_REQ

SYS_RESET_N

PMU_32K_IN

PWR_I2C

HDMI_DDC

P.13

Nvidia

T30S

JTAG

I

2S

UART4

UART2

LPDDR2

512MB/1GB

Debug

Test Point

Audience

eS305

Broadcom

BCM47511

P.9

P.7

Audio Codec

WM8903

P.14 P.15

GPS Antenna

P.21

BT/WLAN Antenna

Audio AMP

APA2010

P.15

MIC & Audio Jack

P.15

Speaker x 2

(1W)

P.15

UART3

SDIO

DAP

USB2

10.1" LCD

1920*1200

Touch Panel

Control

P.13

LVDS Transmitter

(V105A)

P.12

Client

Micro USB

3 3

P.20

Signal Switch

P.20

Host

AzureWave

AW-AH660

P.22

3G Modem Module

P.18

P-Senser

3G Modem Antenna

SIM Card

P.18

IQS12800100TSR

P.16

Dock/B

Light Sensor

STK2203

Func/B

E-Compass

AKM8975

Dock/B

CAMERA

5M(CJAA525)

2M(CBFA152)

P.17

EEPROM

P.10

CIS(MIPI)

CAM_I2C

eMMC

SDIO4

(1.8V)

P.11

SDIO1

(3.3V)

Micro SD slot

P.20

I2C

CAM_I2C CAM_I2C CAM_I2C

GYRO Sensor

MPU-3050

IME

4 4

A

B

G-Sensor

KXTF9-4100

P.16

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

2012/06/202011/06/20

2012/06/202011/06/20

2012/06/202011/06/20

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

SYSTEM BLOCK

SYSTEM BLOCK

SYSTEM BLOCK

Picasso 2 R04

Picasso 2 R04

Wednesday, January 18, 2012

Wednesday, January 18, 2012

Wednesday, January 18, 2012

Picasso 2 R04

E

1.0

1.0

2

2

2

1.0

38

38

38

Page 3

5

4

3

2

1

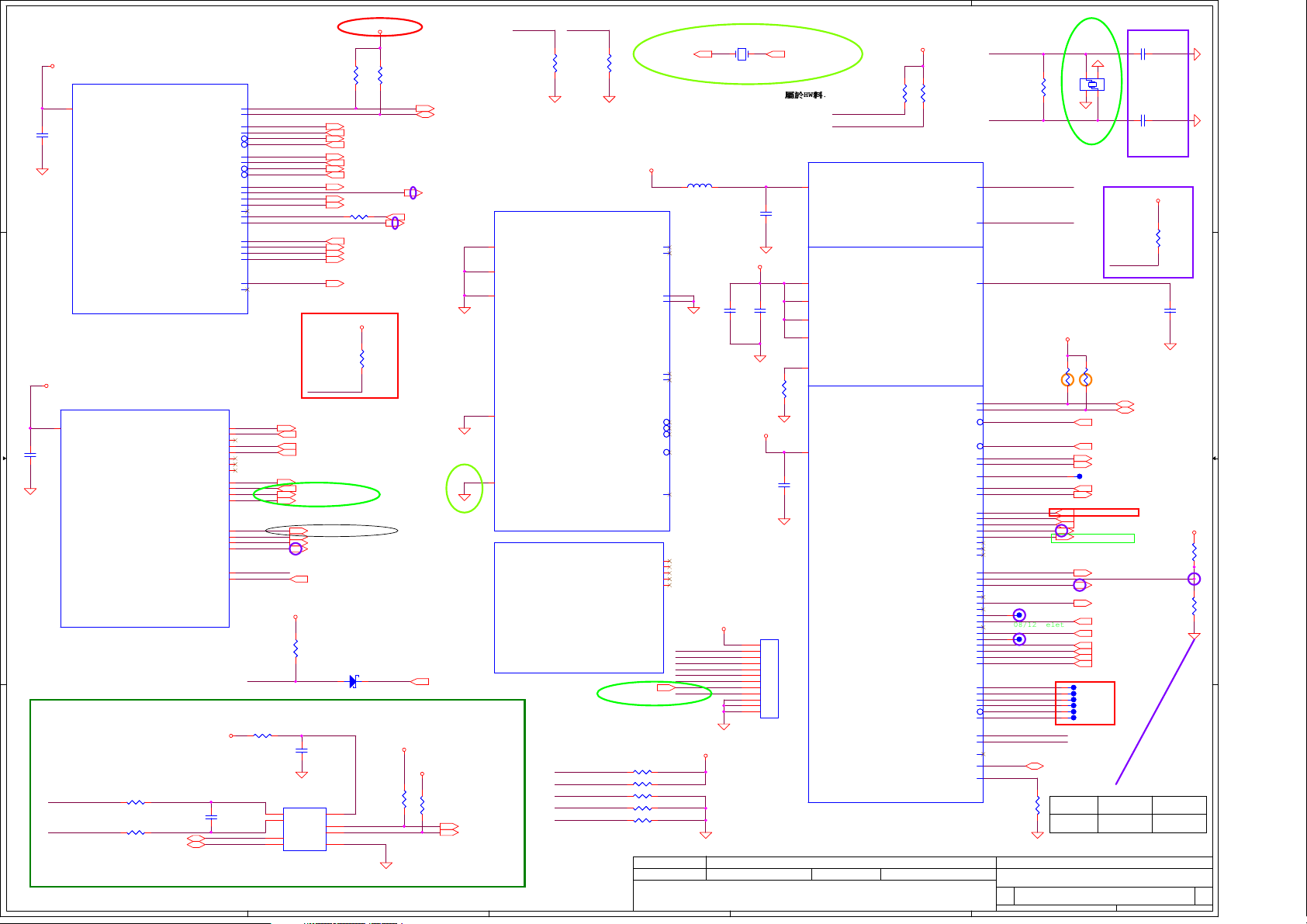

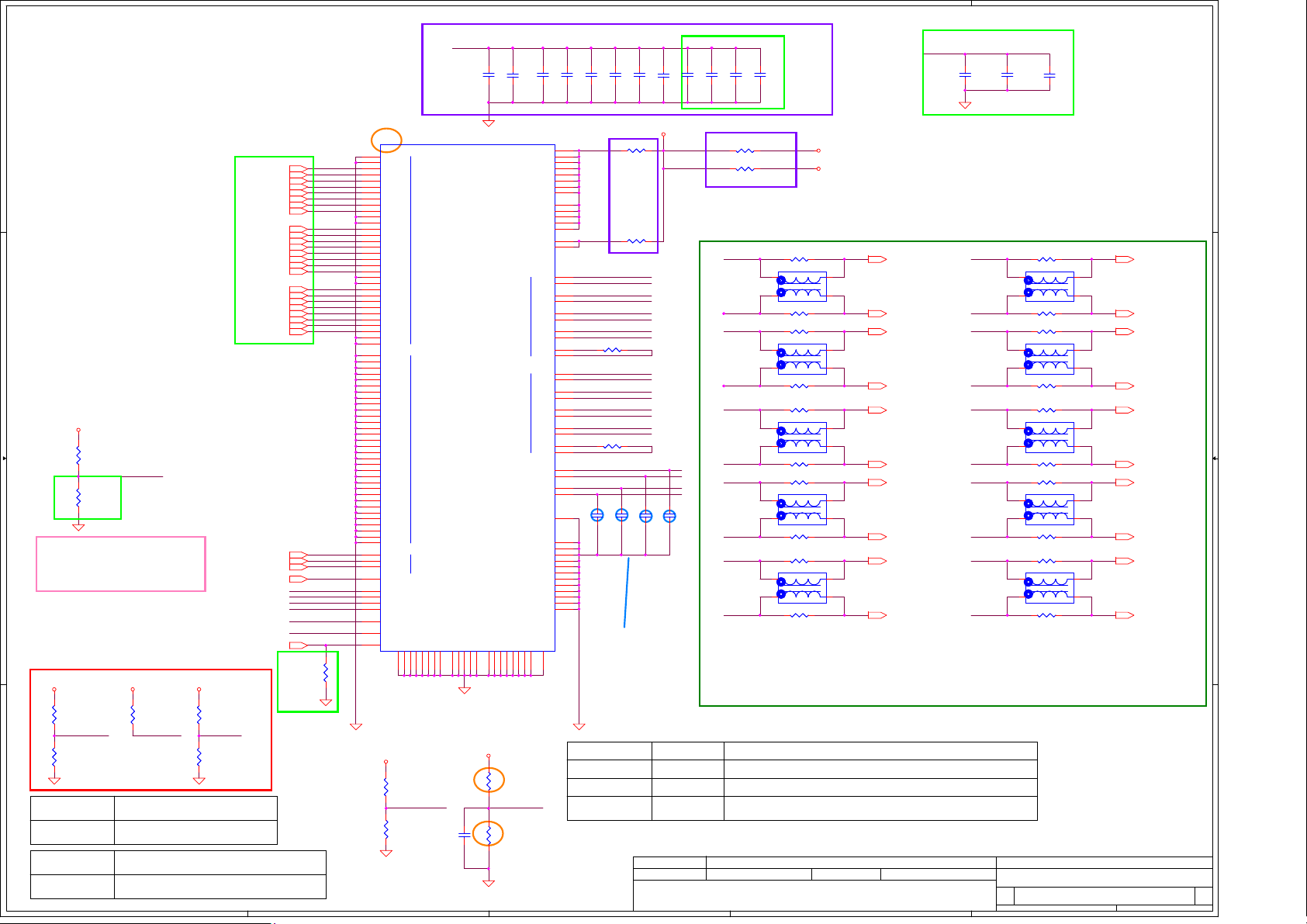

Voltage Rails

Power Plane Description

VIN

B+

+VDD_1V2_RTC_TEGRA

VDD_1V2_SOC

D D

+AVDD_1V1_PLL_TEGRA

+VDD_1V8_PMU_VRTC

+VDD_1V8_SYS_TEGRA System power rail

+AVDD_3V3_USB_TEGRA

+VDD_2V85_EMMC Core voltage for EMMC

+VDD_1V8_CAM_TEGRA

+AVDD_3V3_HDMI_S

VDD_1V8_GEN

+VDD_3V3_DDR_RX_TEGRA DDR RX power rail

+3VS 3.3V switched power rail for standby mode

+5VS

+VDD_LED_BL

+VDD_3V3_SDMMC1_TEGRA

+VDD_VCM_3V3

+VDD_1V2_DDR_MEM DDR power rail

C C

Adapter power supply (19V)

AC or battery power rail for power circuit.

Power for RTC and always-on core logic.

Power for remainder of core logic

AVDD_PLL power rail

RTC power rail

USB power rail

Core voltage for CAMERA

HDMI power rail

1.8V switched power rail for standby mode

5V switched power rail for standby mode

LED power rail

Micro SD power rail

CAMERA power rail

Board ID

PICASSO 2

GEN1_I2C <+VDD_1V8_SENSOR >

Device

Gyro

E Compass

Light Senser

Address<Write,Read>

0xD0 , 0xD1

0x18 , 0x19

0x38 , 0x39

PICASSO M

LPDDR2

B B

GEN2_I2C / TS_I2C < +VDD_3V3_GMI_TEGRA >

Device Address<Write,Read>

Touch Screen

0x98 , 0x99

CAM_I2C < +VDD_1V8_CAM_TEGRA >

Camera 5M

Camera 2M

Flash LED

Address<Write,Read>Device

0x78 , 0x79

0x20 , 0x21

0x66 , 0x67

LVDS strap pin

PWR_I2C < +VDD_1V8_SYS_TEGRA>

Address<Write,Read>Device

Thermal Senser

ES305

A A

Codec

PMU

TPS62361

BATT Conn

EEPROM (Low level) 0xA0 , 0xA1

5

0x98 , 0x99

0x3E

0x34 , 0x35

0x2D

0x60

0xAA , 0xAB

xA2 , 0xA3EEPROM (High level)

0

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

2012/06/202011/06/20

2012/06/202011/06/20

2012/06/202011/06/20

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

Picasso 2 R04

Picasso 2 R04

Tuesday, January 17, 2012

Tuesday, January 17, 2012

Tuesday, January 17, 2012

Picasso 2 R04

1

1.0

1.0

3

3

3

1.0

38

38

38

Page 4

5

R453

NV_LCD_PCLK LCD_PCLK_R

+VDD_3V3_LCD_TEGRA

D D

C C

B B

2

1

C2

C2

C1

1

2

4.7U_0402_6.3V6MC14.7U_0402_6.3V6M

R453

12

47_0402_5%

47_0402_5%

U1I

U1I

8/21 LCD

8/21 LCD

(1.8/3.3V)

(1.8/3.3V)

AG23

VDDIO_LCD_1

AH24

VDDIO_LCD_2

0.1U_0201_10V6K

0.1U_0201_10V6K

+AVDD_3V3_HDMI_S

VDD_1V8_GEN

L49 27NH_LQG15HS27NJ02D_5%_0402L49 27NH_LQG15HS27NJ02D_5%_0402

1 2

1

C165

C165

12P_0201_50V8J

12P_0201_50V8J

2

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

L1

L1

AVDD_HDMI_R

1 2

MPZ1005S300CT_2P

MPZ1005S300CT_2P

C7

C7

0.1U_0201_10V6K

0.1U_0201_10V6K

L2

L2

AVDD_HDMI_PLL

1 2

MPZ1005S300CT_2P

MPZ1005S300CT_2P

C8

C8

0.1U_0201_10V6K

0.1U_0201_10V6K

1

C164

C164

12P_0201_50V8J

12P_0201_50V8J

2

LCD_PCLK

LCD_WR*

LCD_HSYNC

LCD_VSYNC

LCD_D00

LCD_D01

LCD_D02

LCD_D03

LCD_D04

LCD_D05

LCD_D06

LCD_D07

LCD_D08

LCD_D09

LCD_D10

LCD_D11

LCD_D12

LCD_D13

LCD_D14

LCD_D15

LCD_D16

LCD_D17

LCD_D18

LCD_D19

LCD_D20

LCD_D21

LCD_D22

LCD_D23

LCD_PWR0

LCD_PWR1

LCD_PWR2

LCD_SCK

LCD_CS0*

LCD_CS1*

LCD_SDOUT

LCD_SDIN

LCD_DC0

LCD_DC1

CRT_HSYNC

CRT_VSYNC

DDC_SCL

DDC_SDA

HDMI_INT

2

1

2

1

LCD_DE

LCD_M1

AP8

AT8

10/03 Co-lay SOT-23 and SC-7 0

SB93413000000 and SB000009O0 0

Q6

Q6

AO3413_SOT23-3

AO3413_SOT23-3

D

S

D

S

1 3

G

G

+3VS

A A

VDD_1V8_GEN

2

2

G

G

Q2

Q2

D

D

1 3

2

13

G

G

D

D

S

S

@

@

NTS4101PT1G_SC70-3

NTS4101PT1G_SC70-3

S

S

10MIL

0.1A

EN_HDMI_3V3#

Q3

Q3

BSS138W-7-F_SOT323-3

BSS138W-7-F_SOT323-3

5

3.3V

+AVDD_3V3_HDMI_S

12

R27

R27

1M_0201_1%

1M_0201_1%

AD2

4

LCD_PCLK <12>

+VDD_3V3_GMI_TEGRA

RF

PD

NV_LCD_PCLK

AN21

PU

AK24

PD

AR19

PU

AK20

PU

AL17

PD

AR17

PD

AP26

PD

AM18

PD

AN19

PD

AJ23

PD

AR23

PD

AK16

PD

AK22

PD

AU21

PD

AM26

PD

AR21

PD

AU27

PD

AT18

PD

AJ17

PD

AH18

PD

AL21

PD

AM22

PD

AJ19

PD

AT20

PD

AT24

PD

AN27

PD

AU23

PD

AR27

PD

AM24

PD

AM20

PD

AN17

PD

AP20

PD

AN25

PU

AK26

PU

AL23

PU

AP18

PU

AM28

PU

AR25

PD

AL27

PD

AP24

PU

AK18

PU

AJ21

Z

AH20

Z

AT26

Z

AN23

U1K

U1K

10/21 HDMI

10/21 HDMI

AVDD_HDMI

(3.3V)

(3.3V)

AVDD_HDMI_PLL

(1.8V)

(1.8V)

U1J

U1J

9/21 VDAC

9/21 VDAC

(2.8V)

(2.8V)

AVDD_VDAC

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

LCD_DE <12>

LCD_HSYNC <12>

LCD_VSYNC <12>

LCD_D00 <12>

LCD_D01 <12>

LCD_D02 <12>

LCD_D03 <12>

LCD_D04 <12>

LCD_D05 <12>

LCD_D06 <12>

LCD_D07 <12>

LCD_D08 <12>

LCD_D09 <12>

LCD_D10 <12>

LCD_D11 <12>

LCD_D12 <12>

LCD_D13 <12>

LCD_D14 <12>

LCD_D15 <12>

LCD_D16 <12>

LCD_D17 <12>

LCD_D18 <12>

LCD_D19 <12>

LCD_D20 <12>

LCD_D21 <12>

LCD_D22 <12>

LCD_D23 <12>

DDC_SCL_R <19>

DDC_SDA_R <19>

HDMI_DET_T30S < 19>

9/29 Leakage Issue

Modify R10&R11 from mount to unmount

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

4

U1E

U1E

4/21 GMI

4/21 GMI

(1.8/3.3V)

(1.8/3.3V)

P12

VDDIO_GMI_1

T12

2

C147

C147

1

C4

C3

1

2

3300P_0201_16V6K

3300P_0201_16V6K

4.7U_0402_6.3V6MC34.7U_0402_6.3V6M

VDDIO_GMI_2

2

1

0.1U_0201_10V6KC40.1U_0201_10V6K

11/6 Add for COMPAL EMI request.

2.2K_0201_1%

2.2K_0201_1%

GEN2_I2C_SCL

GEN2_I2C_SDA

AR9

HDMI_TXCN

AN9

HDMI_TXCP

AP12

HDMI_TXD0N

AN13

HDMI_TXD0P

AR13

HDMI_TXD1N

AP14

HDMI_TXD1P

AU11

HDMI_TXD2N

AT12

HDMI_TXD2P

HDMI_PROBE

HDMI_RSET

VDAC_R

VDAC_G

VDAC_B

VDAC_VREF

VDAC_RSET

AR11

AM8

AH14

AJ13

AH12

AN11

AM12

HDMI_PROBE

HDMI_RSET

12

R26

R26

1K_0201_1%

1K_0201_1%

3

Z

NAND_D0

J7

GMI_AD00

Z

BOOT_PD

K6

GMI_AD01

Z

J3

GMI_AD02

Z

H2

GMI_AD03

Z

NAND_D4

P4

GMI_AD04

Z

NAND_D5

P6

GMI_AD05

Z

NAND_D6

N3

GMI_AD06

Z

NAND_D7

R3

GMI_AD07

PD

G3

GMI_AD08

PD

E1

GMI_AD09

PD

J5

GMI_AD10

PD

J1

GMI_AD11

Z

PCB_ID0

F2

GMI_AD12

Z

PCB_ID1

F4

GMI_AD13

Z

PCB_ID2

P2

GMI_AD14

Z

R5

GMI_AD15

P8

GMI_A16

M8

GMI_A17

N9

GMI_A18

R9

GMI_A19

PU

R11

GMI_CS0*

GMI_CS1*

GMI_CS2*

GMI_CS3*

GMI_CS4*

GMI_CS6*

GMI_CS7*

GMI_ADV*

GMI_RST*

GMI_WAIT

GMI_IORDY

GEN2_I2C_SCL

GEN2_I2C_SDA

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

+VDD_3V3_GMI_TEGRA

12

12

R11

@ R11

@

T1PAD@ T1PAD@

R10

@R10

@

2.2K_0201_1%

2.2K_0201_1%

HDMI_TXCN <19>

HDMI_TXCP <19>

HDMI_TXD0N <19>

HDMI_TXD0P <19>

HDMI_TXD1N <19>

HDMI_TXD1P <19>

HDMI_TXD2N <19>

HDMI_TXD2P <19>

+VDD_1V8_SDMMC4_TEGRA

2

1

C6

C5

C5

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

1

2

0.1U_0201_10V6KC60.1U_0201_10V6K

GMI_CLK

GMI_WP*

GMI_OE*

GMI_WR*

GMI_DQS

P10

G5

K8

H4

M10

L9

M4

L1

L5

N5

L3

R7

M2

M6

L7

D2

E3

E7

VDDIO_SDMMC4

PU

1

1

PU

PU

PU

1

0

0

PU

PU

PU

1

1

Z

Z

Z

U1F

U1F

5/21 SDMM4

5/21 SDMM4

(1.2/1.8V)

(1.2/1.8V)

BOARD_ID0

BOARD_ID1

BOOT_PD

FORCE_RECOVERY#

NOR_BOOT

LCD_PWM_OUT <13>

DISPOFF# <13,31>

EN_T30S_FUSE_3V3 <23>

LCD_DCR <13>

EN_SENSOR_3V3 <23>

VIB_EN_T30S <20>

TS_PWR_EN <13>

EN_VDDLCD_T30S <13>

EN_WIFI_VDD <22>

TS_INT# <13>

CHARGER_STAT <27>

R158 0_0201_5%R158 0_0201_5%

12

POUT_3G_1 <20>

TEMP_ALERT# <7>

POUT_WIFI < 16>

EN_HDMI_5V0 <19>

3G_DISABLE# <18>

3G_WAKE# <18>

POUT_3G <20>

TS_RST# <13>LVDS_SHTDN# <12>

GEN2_I2C_SCL <13>

GEN2_I2C_SDA <13>

VOL_UP#<7,20>

VOL_DOWN#<7,20>

SDMMC4 : eMMC

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

EN_P_SENSOR

SDMMC4_DAT0

SDMMC4_DAT1

SDMMC4_DAT2

SDMMC4_DAT3

SDMMC4_DAT4

SDMMC4_DAT5

SDMMC4_DAT6

SDMMC4_DAT7

SDMMC4_CLK

SDMMC4_CMD

SDMMC4_RST*

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

2

8/22 Change BOM structure to LPDDR2 & EMMC

EN_SENSOR_3V3

EN_P_SENSOR <20>

100K_0201_5%

100K_0201_5%

100K_0201_5%

100K_0201_5%

100K_0201_5%

100K_0201_5%

+VDD_1V8_SYS_TEGRA

1

2

74AUP1G02GW_TSSOP5

74AUP1G02GW_TSSOP5

08/16 Change U55 footprint

08/16 Delete U56 footprint

Add

Z

B6

Z

G9

Z

C5

Z

B4

Z

A5

Z

D6

Z

C7

Z

D8

PU

F8

PU

H10

Z

B8

2012/06/202011/06/20

2012/06/202011/06/20

2012/06/202011/06/20

12

R18

R18

TS_PWR_EN

12

R12

R12

EN_WIFI_VDD

12

R17

R17

9/15 Modify R23 from 100K to 47K.

9/15 Add R90 for FORCE_RECOVERY issue

9/19 Modify Q44 part number to SB00000J500 .

5

U55

U55

B

4

Vcc

Y

A

G

3

EMMC_DA0 <11>

EMMC_DA1 <11>

EMMC_DA2 <11>

EMMC_DA3 <11>

EMMC_DA4 <11>

EMMC_DA5 <11>

EMMC_DA6 <11>

EMMC_DA7 <11>

EMMC_CLK <11>

EMMC_CMD <11>

EMMC_RST# <11>

1

NAND_D0

BOOT_PD

NAND_D4

NAND_D5

NAND_D6

NAND_D7

NAND_D4

NAND_D5

NAND_D6

NAND_D7

R1 100K_0201_5%R1 100K_0201_5%

R2 100K_0201_5%R2 100K_0201_5%

X76_SAM_1GB@

X76_SAM_1GB@

R38 100K_0201_5%

R38 100K_0201_5%

R43 100K_0201_5%@R43 100K_0201_5%@

R84 100K_0201_5%@R84 100K_0201_5%@

R85 100K_0201_5%@R85 100K_0201_5%@

X76_ELP_1GB@

X76_ELP_1GB@

R5 100K_0201_5%

R5 100K_0201_5%

R6 100K_0201_5%

R6 100K_0201_5%

R7 100K_0201_5%

R7 100K_0201_5%

R8 100K_0201_5%

R8 100K_0201_5%

8/22 Change BOM structure

PCB_ID0

PCB_ID1

PCB_ID2

BOARD_ID0

BOARD_ID1

PCB_ID0

PCB_ID1

PCB_ID2

BOARD_ID0

BOARD_ID1

NOR_BOOT

12

R54

R54

1M_0201_1%

1M_0201_1%

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

R63 100K_0201_5%

R63 100K_0201_5%

QAJ70@

QAJ70@

R87 100K_0201_5%

R87 100K_0201_5%

NH660@

NH660@

R100 100K_0201_5%

R100 100K_0201_5%

LTE@

LTE@

R78 100K_0201_5%

R78 100K_0201_5%

R88 100K_0201_5%

R88 100K_0201_5%

R152 100K_0201_5%

R152 100K_0201_5%

QAJ50@

QAJ50@

R153 100K_0201_5%

R153 100K_0201_5%

AH663@

AH663@

R154 100K_0201_5%

R154 100K_0201_5%

NONLTE@

NONLTE@

R79 100K_0201_5%

R79 100K_0201_5%

@

@

R89 100K_0201_5%

R89 100K_0201_5%

@

@

R22 100K_0201_5%R22 100K_0201_5%

+VDD_3V3_GMI_TEGRA

12

R23

R23

47K_0201_1%

47K_0201_1%

R90 47K_0201_1%

R90 47K_0201_1%

1 2

13

D

D

Q44

Q44

2

G

S TR DMN3150LW-7 1N SOT-323-3

G

S TR DMN3150LW-7 1N SOT-323-3

S

S

Vth=1.4V

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

T30S(1/5)LCD/CRT/HDMI/NAND

T30S(1/5)LCD/CRT/HDMI/NAND

T30S(1/5)LCD/CRT/HDMI/NAND

Picasso 2 R04

Picasso 2 R04

Tuesday, January 17, 2012

Tuesday, January 17, 2012

Tuesday, January 17, 2012

Picasso 2 R04

1

12

12

+VDD_3V3_GMI_TEGRA

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

FORCE_RECOVERY#

+VDD_3V3_GMI_TEGRA

+VDD_3V3_GMI_TEGRA

+VDD_3V3_GMI_TEGRA

T21 PAD@T21 PAD

@

4

38

4

38

4

38

1.0

1.0

1.0

Page 5

5

4

3

2

1

Acer request

VDD_1V2_MEM

U1D

1

D D

SDMMC1 : SD card

U1P

+VDD_3V3_SDMMC1_TEGRA

C17

C17

1

2

C C

U1P

17/21 SDMMC1

17/21 SDMMC1

(1.8/2.8~3.3V)

(1.8/2.8~3.3V)

R1

VDDIO_SDMMC1

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

SDMMC1_DAT0

SDMMC1_DAT1

SDMMC1_DAT2

SDMMC1_DAT3

SDMMC1_CLK

SDMMC1_CMD

SDMMC1_COMP_PU

SDMMC1_COMP_PD

GPIO_PV2

GPIO_PV3

CLK2_OUT

CLK2_REQ

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

PU

U7

PU

W11

PU

U1

PU

Y10

PU

T6

PU

T8

SDMMC1_COMP_PU

AF10

SDMMC1_COMP_PD

U9

Z

Y6

Z

W9

PD

U3

Z

U5

9/22

Add U1.U3 GPIO to control Power CP function.

SDMMC_DAT0 <20>

SDMMC_DAT1 <20>

SDMMC_DAT2 <20>

SDMMC_DAT3 <20>

SDMMC_CLK <20>

SDMMC_CMD <20>

+VDD_3V3_SDMMC1_TEGRA

R29 33.2_0402_1%R29 33.2_0402_1%

1 2

R30 33.2_0402_1%R30 33.2_0402_1%

1 2

CP_GPIO <27>

SDMMC3 : WIFI

U1O

+VDD_1V8_SDMMC3_TEGRA

C26

C26

1

1

C25

C25

2

2

0.1U_0201_10V6K

0.1U_0201_10V6K

<BOM Structure>

<BOM Structure>

<BOM Structure>

B B

A A

<BOM Structure>

U1O

6/21 SDMMC3

6/21 SDMMC3

M36

VDDIO_SDMMC3

(1.8/2.8~3.3V)

(1.8/2.8~3.3V)

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

<BOM Structure>

<BOM Structure>

U1M

U1M

15/21 HSIC

15/21 HSIC

(1.2V)

(1.2V)

Y2

VDDIO_HSIC

U1N

U1N

16/21 IC_USB

16/21 IC_USB

AB8

AVDD_IC_USB

(1.8/3.0V)

(1.8/3.0V)

5

SDMMC3_DAT0

SDMMC3_DAT1

SDMMC3_DAT2

SDMMC3_DAT3

SDMMC3_DAT4

SDMMC3_DAT5

SDMMC3_DAT6

SDMMC3_DAT7

SDMMC3_CLK

SDMMC3_CMD

SDMMC3_COMP_PU

SDMMC3_COMP_PD

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

HSIC_DATA

HSIC_STROBE

HSIC_REXT

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

IC_USB_DN

IC_USB_DP

IC_USB_REXT

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

PU

N33

PU

L37

PU

M34

PU

P34

PU

J37

PU

N29

PU

M32

PU

M28

9/26 Modify BOARD_ID3 from U1.J37 to U1.R37

PU

J35

PU

M30

L35

N35

AC5

AD6

AD10

AD4

AE3

AD8

SDMMC3_COMP_PU

SDMMC3_COMP_PD

4

WFMMC_DAT0 <22>

WFMMC_DAT1 <22>

WFMMC_DAT2 <22>

WFMMC_DAT3 <22>

T17PAD@ T17PAD@

WFMMC_CLK <22>

WFMMC_CMD <22>

R31 33.2_0402_1%

R31 33.2_0402_1%

1 2

R32 33.2_0402_1%

R32 33.2_0402_1%

1 2

1

C10

C10

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

1

C14

C14

2

0.1U_0201_10V6K

0.1U_0201_10V6K

1

C18

C18

2

0.1U_0201_10V6K

0.1U_0201_10V6K

1

C30

C30

2

0.1U_0201_10V6K

0.1U_0201_10V6K

2

C205

C205

1

33P 50V J NPO 0201

33P 50V J NPO 0201

+VDD_1V8_SDMMC3_TEGRA

1

1

C11

C11

C12

C12

C13

2

1

C22

C22

2

1

C19

C19

2

1

C108

C108

2

2

C215

C215

1

3

C13

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

33P 50V J NPO 0201

33P 50V J NPO 0201

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

1

1

C15

C15

C16

C16

2

2

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

1

1

C20

C20

C21

C21

2

2

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

1

1

C110

C110

2

Issued Date

Issued Date

Issued Date

+VDD_1V0_DDR_HS_TEGRA

0.1U_0201_10V6K

0.1U_0201_10V6K

C109

C109

2

0.1U_0201_10V6K

0.1U_0201_10V6K

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

VDD_1V2_MEM

+VDD_3V3_DDR_RX_TEGRA

U1D

3/21 DDR MEMORY

3/21 DDR MEMORY

(1.2/1.25/1.35/1.5V)

(1.2/1.25/1.35/1.5V)

M14

VDDIO_DDR_01

M16

VDDIO_DDR_02

M18

VDDIO_DDR_03

M20

VDDIO_DDR_04

M22

VDDIO_DDR_05

M24

VDDIO_DDR_06

N15

VDDIO_DDR_07

N17

VDDIO_DDR_08

N19

VDDIO_DDR_09

N21

VDDIO_DDR_10

N23

VDDIO_DDR_11

P26

VDDIO_DDR_12

R25

VDDIO_DDR_13

T26

VDDIO_DDR_14

(2.8/3.3V)

(2.8/3.3V)

A15

VDD_DDR_RX

1

C23

C23

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

(1.05V)

(1.05V)

K12

VDD_DDR_HS_1

L23

VDD_DDR_HS_2

1

C24

C24

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

E29

DDR_DQ00

F28

DDR_DQ01

B30

DDR_DQ02

E25

DDR_DQ03

A29

DDR_DQ04

C25

DDR_DQ05

D24

DDR_DQ06

F24

DDR_DQ07

F14

DDR_DQ08

C15

DDR_DQ09

D14

DDR_DQ10

H14

DDR_DQ11

C13

DDR_DQ12

C11

DDR_DQ13

D12

DDR_DQ14

A9

DDR_DQ15

D30

DDR_DQ16

K24

DDR_DQ17

G27

DDR_DQ18

H24

DDR_DQ19

E27

DDR_DQ20

G29

DDR_DQ21

H28

DDR_DQ22

J25

DDR_DQ23

K14

DDR_DQ24

F10

DDR_DQ25

L15

DDR_DQ26

J15

DDR_DQ27

H12

DDR_DQ28

G11

DDR_DQ29

C9

DDR_DQ30

E9

DDR_DQ31

F26

DDR_DM0

E13

DDR_DM1

C29

DDR_DM2

J13

DDR_DM3

B26

DDR_DQS0N

A27

DDR_DQS0P

A11

DDR_DQS1N

B12

DDR_DQS1P

K26

DDR_DQS2N

H26

DDR_DQS2P

E11

DDR_DQS3N

F12

DDR_DQS3P

J23

DDR_A00

C23

DDR_A01

E21

DDR_A02

A23

DDR_A03

E23

DDR_A04

B18

DDR_A05

A17

DDR_A06

F18

DDR_A07

B14

DDR_A08

C17

DDR_A09

F16

DDR_A10

G17

DDR_A11

J17

DDR_A12

H18

DDR_A13

J19

DDR_A14

J21

DDR_RAS*

H20

DDR_CAS*

H22

DDR_WE*

F20

DDR_BA0

G21

DDR_BA1

F22

DDR_BA2

C21

DDR_CS0*

D20

DDR_CS1*

G23

DDR_ODT0

L19

DDR_ODT1

B20

DDR_CKE0

E19

DDR_CKE1

D18

DDR_CLK*

C19

DDR_CLK

K20

DDR_RESET

C27

DDR_QUSE0

D26

DDR_QUSE1

G15

DDR_QUSE2

H16

DDR_QUSE3

DDR_COMP_PU

DDR_COMP_PU

DDR_COMP_PD

2012/06/202011/06/20

2012/06/202011/06/20

2012/06/202011/06/20

2

E17

DDR_COMP_PD

E15

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Tuesday, January 17, 2012

Date: Sheet of

Tuesday, January 17, 2012

Date: Sheet of

Tuesday, January 17, 2012

DDR_A_D0 <9>

DDR_A_D1 <9>

DDR_A_D2 <9>

DDR_A_D3 <9>

DDR_A_D4 <9>

DDR_A_D5 <9>

DDR_A_D6 <9>

DDR_A_D7 <9>

DDR_A_D8 <9>

DDR_A_D9 <9>

DDR_A_D10 < 9>

DDR_A_D11 < 9>

DDR_A_D12 < 9>

DDR_A_D13 < 9>

DDR_A_D14 < 9>

DDR_A_D15 < 9>

DDR_A_D16 < 9>

DDR_A_D17 < 9>

DDR_A_D18 < 9>

DDR_A_D19 < 9>

DDR_A_D20 < 9>

DDR_A_D21 < 9>

DDR_A_D22 < 9>

DDR_A_D23 < 9>

DDR_A_D24 < 9>

DDR_A_D25 < 9>

DDR_A_D26 < 9>

DDR_A_D27 < 9>

DDR_A_D28 < 9>

DDR_A_D29 < 9>

DDR_A_D30 < 9>

DDR_A_D31 < 9>

DDR_A_DM0 <9>

DDR_A_DM1 <9>

DDR_A_DM2 <9>

DDR_A_DM3 <9>

DDR_A_DQS#0 <9>

DDR_A_DQS0 <9>

DDR_A_DQS#1 <9>

DDR_A_DQS1 <9>

DDR_A_DQS#2 <9>

DDR_A_DQS2 <9>

DDR_A_DQS#3 <9>

DDR_A_DQS3 <9>

DDR_A_MA0 <9>

DDR_A_MA1 <9>

DDR_A_MA2 <9>

DDR_A_MA3 <9>

DDR_A_MA4 <9>

DDR_A_MA5 <9>

DDR_A_MA6 <9>

DDR_A_MA7 <9>

DDR_A_MA8 <9>

DDR_A_MA9 <9>

M_CS#0 <9>

M_CS#1 <9>

M_CKE0 <9>

M_CKE1 <9>

M_CLK_DDR#0 <9>

M_CLK_DDR0 <9>

DDR_RESET

QUSE0

QUSE1

QUSE2

QUSE3

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

T30S(2/5)OSC/PLL/SYS/DDR

T30S(2/5)OSC/PLL/SYS/DDR

T30S(2/5)OSC/PLL/SYS/DDR

T3PAD@ T3PAD@

R33 0_0201_5%R33 0_0201_5%

1 2

R34 0_0201_5%R34 0_0201_5%

1 2

R35 49.9_0402_1%R35 49.9_0402_1%

1 2

R36 49.9_0402_1%R36 49.9_0402_1%

1 2

Picasso 2 R04

Picasso 2 R04

Picasso 2 R04

1

5

5

5

VDD_1V2_MEM

38

38

38

1.0

1.0

1.0

Page 6

A

U1Q is not place on grid , need check connection

1 1

+VDD_1V8_AUDIO_TEGRA

1

C28

C28

2

0.1U_0201_10V6K

0.1U_0201_10V6K

2 2

+AVDD_1V2_DSI_CSI_TEGRA

3 3

1

C31

C31

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

U1Q

U1Q

13/21 AUDIO

13/21 AUDIO

(1.8/3.3V)

(1.8/3.3V)

G33

VDDIO_AUDIO

U1H

U1H

7/21 DSI/CSI

7/21 DSI/CSI

(1.2V)

(1.2V)

AF2

AVDD_DSI_CSI

1

C32

C32

2

0.1U_0201_10V6K

0.1U_0201_10V6K

CLK1_OUT

DAP1_SCLK

DAP1_FS

DAP1_DOUT

DAP1_DIN

DAP2_SCLK

DAP2_FS

DAP2_DOUT

DAP2_DIN

SPDIF_IN

SPDIF_OUT

SPI1_SCK

SPI1_CS0*

SPI1_MOSI

SPI1_MISO

SPI2_SCK

SPI2_CS0*

SPI2_CS1*

SPI2_CS2*

SPI2_MOSI

SPI2_MISO

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

CSI_CLKAN

CSI_CLKAP

CSI_D1AN

CSI_D1AP

CSI_D2AN

CSI_D2AP

CSI_CLKBN

CSI_CLKBP

CSI_D1BN

CSI_D1BP

CSI_D2BN

CSI_D2BP

E35

L29

B34

D32

A33

H34

K30

F34

C33

L31

J31

G35

H36

L33

F36

K32

J33

B32

F30

D36

E37

AP2

AN3

AJ5

AJ3

AL9

AK10

AR7

AN7

AK4

AL3

AT6

AP6

AUDIO_CLK

PD

PD

PD

PD

PD

PD

PD

PD

PU

PU

PU

PU

PU

PD

PU

PU

PU

PU

PD

PD

B

RF note

R37 0_0201_5%R37 0_0201_5%

1 2

AUDIO_SEL <14>

AUDIO_RST# <14>

ES305_INT_R <14>

ENABLE_USB_HOST <20,27>

8/24 Modify Off-Page type.

AUDIO_SCLK2 <14>

AUDIO_FS2 < 14>

AUDIO_DOUT2 <14>

AUDIO_DIN2 <14>

AUDIO_CLK_R <15>

10/24 Add BATT_LEARN GPIO to Power request.

10/03 Add D18 on +T30S_USB1 to protect CPU.

BATT_LEARN <27>

COMPASS_DRDY <20>

10/19 Modify D18 from +T30S_ USB1 to VBUS_USB

12/2 Modify D18 from moun to @,Add Zener on samll board.

SC400003Z00

LIGHT_INT <20>

HP_DET# <20>

CDC_IRQ# <15>

EN_ES305_OSC <14>

GYRO_INT_R <16>

+T30S_USB1

+AVDD_3V3_USB_TEGRA

USB VBUS overvoltage protection

5M_CAM_CLK#_R <17>

5M_CAM_CLK_R <17>

5M_CAM_DA1#_R < 17>

5M_CAM_DA1_R <17>

5M_CAM_DA2#_R < 17>

5M_CAM_DA2_R <17>

2M_CAM_CLK#_R <17>

2M_CAM_CLK_R <17>

2M_CAM_DA1#_R < 17>

2M_CAM_DA1_R <17>

2M_CAM_DA2#_R < 17>

2M_CAM_DA2_R <17>

+VDD_1V8_CAM_TEGRA

AO3413_SOT23-3

AO3413_SOT23-3

2

G

G

1

C34

C34

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

C

Q18

Q18

D

D

1 3

2

13

1

C35

C35

2

G

G

D

D

S

S

0.1U_0201_10V6K

0.1U_0201_10V6K

S

S

10MIL

3.3V

0.1A

R42

R42

1M_0201_1%

1M_0201_1%

EN_T30S_USB1

Q5

Q5

BSS138W-7-F_SOT323-3

BSS138W-7-F_SOT323-3

U1G

U1G

18/21 CAM

18/21 CAM

(1.8/2.8 ~ 3.3V)

(1.8/2.8 ~ 3.3V)

AL11

VDDIO_CAM

+AVDD_3V3_USB_TEGRA

+AVDD_1V8_USB_PLL_TEGRA

VBUS_USB

12

D18

D18

BZT52-B5V6S_SOD323-2

BZT52-B5V6S_SOD323-2

2 1

D

U1L

U1L

11/21 USB

11/21 USB

(3.3V)

(3.3V)

AB6

AVDD_USB

1

C27

C27

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

(1.8V)

(1.8V)

V2

AVDD_USB_PLL

1

C29

C29

2

0.1U_0201_10V6K

0.1U_0201_10V6K

@

@

+VDD_1V8_CAM_TEGRA

12

12

R40

CAM_I2C_SCL

CAM_I2C_SDA

CAM_MCLK

GPIO_PBB0

GPIO_PBB3

GPIO_PBB4

GPIO_PBB5

GPIO_PBB6

GPIO_PBB7

GPIO_PCC1

GPIO_PCC2

R40

2.2K_0201_1%

2.2K_0201_1%

Z

AK14

Z

AN15

Z

R72 0_0201_5%R72 0_0201_5%

AG15

Z

AM10

Z

AM14

Z

AL15

Z

AJ15

Z

AM16

Z

AT14

PU

AU15

PU

AR15

R41

R41

2.2K_0201_1%

2.2K_0201_1%

CAM_I2C_SCL <17,26,35>

1 2

CAM_I2C_SDA <17,26,35>

2M_CAM_RST# <17>

5M_CAM_PWDN <17>

5M_CAM_RST# <17>

2M_CAM_PWDN <17>

DOCK_DET# <20>

9/26 Swap U1.AM16 to U1.AM10 for WAKE UP issue

AF8

USB1_VBUS

AL5

USB1_DN

AM4

USB1_DP

AU5

USB1_ID

AH6

USB2_VBUS

AG3

USB2_DN

AG1

USB2_DP

AJ7

USB2_ID

AR5

USB3_VBUS

AF4

USB3_DN

AE5

USB3_DP

AK12

USB3_ID

AE9

USB_REXT

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

1

C372

C372

2

10P_0201_50V8J

10P_0201_50V8J

USB_REXT

CAM_MCLK <17>

E

+T30S_USB1

USB1_DN <20>

USB1_DP <20>

USB1_ID <20>

3G_USB_DN <18>

3G_USB_DP <18>

+T30S_USB1

USB_HOST_DN <20>

USB_HOST_DP <20>

R39

R39

12

1K_0201_1%

1K_0201_1%

CAM_I2C_SCL CAM_I2C_SDA

RF note

1

C186

C186

2

39P_0201_50V8J

39P_0201_50V8J

1

C187

C187

2

39P_0201_50V8J

39P_0201_50V8J

T30S-R-A3-1.4G_FCCSP681

AJ1

DSI_CLKAN

AK2

DSI_CLKAP

AN1

DSI_D1AN

AM2

DSI_D1AP

AH8

DSI_D2AN

AG9

4 4

A

DSI_D2AP

AG7

DSI_CSI_RUP

AT4

DSI_CSI_RDN

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

+AVDD_1V2_DSI_CSI_TEGRA

DSI_CSI_RUP

DSI_CSI_RDN

12

R44

R44

453_0402_1%

453_0402_1%

12

R45

R45

49.9_0402_1%

49.9_0402_1%

B

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

T30S-R-A3-1.4G_FCCSP681

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

2012/06/202011/06/20

2012/06/202011/06/20

2012/06/202011/06/20

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

T30S(3/5)USB/SDIO/UART/AUDIO

T30S(3/5)USB/SDIO/UART/AUDIO

T30S(3/5)USB/SDIO/UART/AUDIO

Picasso 2 R04

Picasso 2 R04

Tuesday, January 17, 2012

Tuesday, January 17, 2012

Tuesday, January 17, 2012

Picasso 2 R04

E

6

6

6

1.0

1.0

1.0

38

38

38

Page 7

A

+VDD_1V8_UART_TEGRA

U1R

U1R

14/21 UART

14/21 UART

(1.8/3.3V)

(1.8/3.3V)

AC37

1

C38

C38

2

0.1U_0201_10V6K

0.1U_0201_10V6K

+VDD_1V8_BB_TEGRA

V6

1

2

0.1U_0201_10V6K

0.1U_0201_10V6K

NV_THERM_DP

NV_THERM_DN

VDDIO_UART

U1S

U1S

12/21 BB

12/21 BB

VDDIO_BB

(1.8/3.3V)

(1.8/3.3V)

max current is 350uA

VR1 =17mV

R59 100_0201_1%R59 100_0201_1%

12

1000P_0201_16V7K

1000P_0201_16V7K

R61 100_0201_1%R61 100_0201_1%

12

PWR_I2C_SCL<10,14,15,26,32,34>

PWR_I2C_SDA<10,14,15,26,32,34>

A

1 1

2 2

C43

C43

3 3

4 4

GEN1_I2C_SCL

GEN1_I2C_SDA

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

ULPI_DATA0

ULPI_DATA1

ULPI_DATA2

ULPI_DATA3

ULPI_DATA4

ULPI_DATA5

ULPI_DATA6

ULPI_DATA7

ULPI_CLK

ULPI_DIR

ULPI_NXT

ULPI_STP

DAP3_DIN

DAP3_DOUT

DAP3_FS

DAP3_SCLK

GPIO_PV0

GPIO_PV1

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

+3VS

C46

C46

UART2_TXD

UART2_RXD

UART2_RTS*

UART2_CTS*

UART3_TXD

UART3_RXD

UART3_RTS*

UART3_CTS*

GPIO_PU0

GPIO_PU1

GPIO_PU2

GPIO_PU3

GPIO_PU4

GPIO_PU5

GPIO_PU6

DAP4_DIN

DAP4_DOUT

DAP4_FS

DAP4_SCLK

CLK3_OUT

CLK3_REQ

THERMD_F_P

12

THERMD_F_N

PWR_I2C_SCL

PWR_I2C_SDA

AA7

AC7

V8

AC3

V4

AC11

AF6

AA9

AC1

W3

AC9

V10

AA1

W5

Y4

AA3

Y8

AA5

PU

PU

PU

PU

PU

PU

PU

PU

Z

Z

Z

PD

PD

PD

PD

Z

Z

1 2

49.9_0402_1%

49.9_0402_1%

Open Drain

AH30

AE29

AN35

AG29

AG31

AJ31

AE33

AJ35

AK36

AJ37

AK34

AF36

AN37

AG33

AM36

AG37

AJ33

AF34

AG35

AF28

AL35

AH32

AF32

ON_KEY#

+VDD_1V8_BB_TEGRA

ON_KEY#

R57

R57

2.2K_0201_1%

2.2K_0201_1%

Z

Z

PU

PU

PU

PU

PU

PU

PU

PU

Z

Z

Z

Z

Z

Z

DEBUG_UART1_RX_R

Z

PD

PD

PD

PD

0

Z

100K_0201_5%

100K_0201_5%

EN_SENSOR_1V8#

DEBUG_UART1_TX <20>

DEBUG_UART1_RX <20>

WAKE_UP_ACIN <27>

SIM_DET <18>

AUDIO_UART4_TX <14>

AUDIO_UART4_RX <14>

EN_VDD_GPS <21>

EN_SENSOR_1V8# <23>

CAM_LED_EN_NV <35>

WF_RST# <22>

BT_WAKEUP <22>

EN_SENSOR_3V3_2 <23>

9/27

ADD EN_SENSOR_3V3_2 to U1.AA3

WAKE_UP_VBUS <27>

12

R164

R164

100K_0201_5%

100K_0201_5%

1

C45

C45

2

0.1U_0201_10V6K

0.1U_0201_10V6K

U4

U4

2

VDD

D+

3

D-

THERM#

ALERT#

8

SCL

7

SDA

GND

NCT1008CMT3R2G_WDFN8_2X2

NCT1008CMT3R2G_WDFN8_2X2

B

+VDD_1V8_SENSOR

12

R46

R46

GPS_UART_TXD <21>

GPS_UART_RXD < 21>

GPS_UART_RTS# < 21>

GPS_UART_CTS# <21>

BT_UART_TXD <22>

BT_UART_RXD <22>

BT_UART_RTS# <22>

BT_UART_CTS# <22>

BT_RST# <22>

GPS_PWRON <21>

GPS_RESET# <18,21>

R149

R149

1 2

0_0201_5%

0_0201_5%

BT_PCM_IN <22>

BT_PCM_OUT <22>

BT_PCM_SYNC <22>

BT_PCM_CLK <22>

CLK_12M_ES305 <14>

+VDD_1V8_BB_TEGRA

12

R77

R77

D20

D20

RB751V-40_SOD323-2

RB751V-40_SOD323-2

12

+3VS_TH

100K_0201_5%

100K_0201_5%

1

4

6

5

B

12

R47

R47

2.2K_0201_1%

2.2K_0201_1%

GEN1_I2C_SCL <16,20>

GEN1_I2C_SDA <16,20>

9/22

C

hange EN_3V3_MODEM from AE35 to AF36.

9/26

Change BT_PD# from Y36 to AJ33

EN_3V3_MODEM <18,30>

DEBUG_UART1_RX <20>

BT_PD# <22>

ONKEY# <20,32>

VDD_1V8_PMU_VRTC

+3VS

12

12

R58

R58

R60

R60

100K_0201_5%

100K_0201_5%

AP_OVERHEAT# < 32>

TEMP_ALERT# <4>

Thermal

19/21 PEX

19/21 PEX

(1.05V)

(1.05V)

AN29

AVDD_PEXB

(1.05V)

(1.05V)

AM30

VDD_PEXB

(1.05V)

(1.05V)

AN31

AVDD_PEX_PLL

(3.3V)

(3.3V)

AL29

HVDD_PEX

(3.3V)

(3.3V)

AK28

VDDIO_PEX_CTL

U1U

U1U

20/21 SPARE

20/21 SPARE

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

BT_RST# GPS_RESET#

12

R56

R56

100K_0201_5%

100K_0201_5%

100K_0201_5%

100K_0201_5%

U1T

U1T

JTAG_TDI

JTAG_TMS

JTAG_RTCK

JTAG_TCK

JTAG_TRST#

C

Y1

12

R75

R75

For PMU RTCCLK , Load BOM

VDD_1V8_GEN

PEX_L5_TXN

PEX_L5_TXP

PEX_L5_RXN

PEX_L5_RXP

PEX_CLK3N

PEX_CLK3P

PEX_L2_CLKREQ*

PEX_L2_PRSNT*

PEX_L2_RST*

PEX_WAKE*

PEX_TERMP

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

SPARE_1

SPARE_2

SPARE_3

SPARE_4

SPARE_5

HOT_RST#<20>

R155

R155

1 2

10K_0201_5%

10K_0201_5%

R159

R159

1 2

10K_0201_5%

10K_0201_5%

R160

R160

1 2

10K_0201_5%

10K_0201_5%

R161 100K_0201_5%R161 100K_0201_5%

R162 100K_0201_5%@R162 100K_0201_5%@

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

MPZ1005S300CT_2P

MPZ1005S300CT_2P

AC27

AD28

AG19

AL33

AM34

12

12

Issued Date

Issued Date

Issued Date

L3

L3

1 2

AT30

AU29

AP30

AR29

AT34

AR33

AR31

AT32

AU33

AP32

AP36

JTAG_TRST#

JTAG_TDI

JTAG_TMS

JTAG_TCK

JTAG_RTCK

JTAG_TDO

ONKEY#

+VDD_1V8_SYS_TEGRA

Y1

1 2

32.768KHZ_12.5P_1TJF125DP1A000D

32.768KHZ_12.5P_1TJF125DP1A000D

AVDD_OSC

C39

C39

+AVDD_1V1_PLL_TEGRA

1

1

C41

C41

C42

C42

2

2

0.1U_0201_10V6K

0.1U_0201_10V6K

0_0201_5%

0_0201_5%

Z

Z

+VDD_1V8_SYS_TEGRA

Z

Z

+VDD_1V8_SYS_TEGRA

JDBUG1

JDBUG1

1

2

3

4

5

6

7

8

9

10

11

12

ACES_87036-1001-CP

ACES_87036-1001-CP

CONN@

CONN@

1

2

3

4

5

6

7

8

9

10

GND

GND

1

2

0.1U_0201_10V6K

0.1U_0201_10V6K

R53

R53

屬屬屬屬屬屬屬屬HW料料料料

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

1 2

1

C44

C44

2

PMU_OSC32KOUT <32>PMU_OSC32KIN<32>

P36

B24

K18

A21

AG5

AF30

Y32

0.1U_0201_10V6K

0.1U_0201_10V6K

Compal Secret Data

Compal Secret Data

Compal Secret Data

D

.

CORE_PWR_REQ

CPU_PWR_REQ

U1C

U1C

2/21 OSC, PLL & SYS

2/21 OSC, PLL & SYS

AVDD_OSC

(1.8V)

(1.8V)

D

eep Sleep : OFF

AVDD_PLLA_P_C_S

(1.1V)

(1.1V)

AVDD_PLLX

(1.1V)

(1.1V)

AVDD_PLLM

(1.1V)

(1.1V)

AVDD_PLLU_D

(1.05V)

(1.05V)

AVDD_PLLE

(1.8V)

(1.8V)

VDDIO_SYS

Deep Sleep : ON

Deciphered Date

Deciphered Date

Deciphered Date

D

100K_0201_5%

100K_0201_5%

(1.1V)

(1.1V)

+VDD_1V8_SYS_TEGRA

12

12

R48

R48

R49

R49

100K_0201_5%

100K_0201_5%

CORE_PWR_REQ

TEST_MODE_EN

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

2012/06/202011/06/20

2012/06/202011/06/20

2012/06/202011/06/20

E

14

G

G

09/15 Add for Acer request.

12

12

R51

R51

PMU_RESET_OUT_1V8# <32>

PMU_INT# <32>

PMU_CLK_32K <32>

SC_LOCK# <20>

VOL_UP# <4,20>

VOL_DOWN# <4,20>

EN_CAM_2V8 <17>

BOARD_ID_WP <10>

9/26 Change BT_PD# to AJ33

SD_DET# <20>

LINE_OUT_DET# <20>

BT_IRQ# <22>

HDMI_CEC <19>

9/26

Change from J37 to R37.

XTAL_IN

XTAL_OUT

PLL_S_PLL_LF

PWR_I2C_SCL

PWR_I2C_SDA

SYS_RESET*

PWR_INT*

CPU_PWR_REQ

SYS_CLK_REQ

CLK_32K_IN

CLK_32K_OUT

KB_COL00

KB_COL01

KB_COL02

KB_COL03

KB_COL04

KB_COL05

KB_COL06

KB_COL07

KB_ROW00

KB_ROW01

KB_ROW02

KB_ROW03

KB_ROW04

KB_ROW05

KB_ROW06

KB_ROW07

KB_ROW08

KB_ROW09

KB_ROW10

KB_ROW11

KB_ROW12

KB_ROW13

KB_ROW14

KB_ROW15

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRST*

JTAG_RTCK

THERM_DN

THERM_DP

OWR

HDMI_CEC

8/25 Modify C36&C37 from 12P to 8P.

10/11 Modify C36&C37 from 8P to 10P.

T30S_XTAL_IN

12

R50

R50

2M_0201_5%

2M_0201_5%

T30S_XTAL_OUT

T30S_XTAL_IN

R33

T30S_XTAL_OUT

R35

PLL_S_PLL_LF

R27

10/19 Modify R51 and R52 to 1K ohm

V36

V30

U31

P28

T32

Y34

W27

T30

AB32

U37

U29

AD32

AD36

AC31

Y30

AD30

W35

AC33

R37

W29

R31

U35

V34

U33

AE35

AA35

AA37

AA29

Y36

P30

AC29

P32

AB30

AA31

AC35

Y28

AA33

W33

AD34

E31

C31

R29

V32

V28

+VDD_1V8_SYS_TEGRA

1K_0201_1%

1K_0201_1%

Z

Z

Z

SYS_CLK_REQ

0

PU

PU

PU

PU

PU

PU

PU

PU

9/22 Swap AD36 & W29 GPIO function.

Default pull up& pull down swap

PD

PD

PD

PD

we not use Audio LDO

PD

PD

PD

9/22 Change EN_3V3_MODEM to AF36

PD

T10PAD@ T10PAD@

PD

PD

08/12 Delete EN_ACER_USB_CHARGE

PD

PD

T14PAD@ T14PAD@

PD

PD

PD

PD

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRST#

JTAG_RTCK

NV_THERM_DN

NV_THERM_DP

Z

TEST_MODE_EN

0_0201_5%

0_0201_5%

R62

R62

1 2

9/28 Change Net name from Board_ID3 to PCB_ID3

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

T30S(4/5) UART/OSC/PLL

T30S(4/5) UART/OSC/PLL

T30S(4/5) UART/OSC/PLL

Picasso 2 R04

Picasso 2 R04

Tuesday, January 17, 2012

Tuesday, January 17, 2012

Tuesday, January 17, 2012

Picasso 2 R04

E

C36

C36

1 2

10P_0201_50V8J

10P_0201_50V8J

G

G

Y10

Y10

26MHZ_10PF_7M26000039

26MHZ_10PF_7M26000039

3 2

C37

C37

1 2

10P_0201_50V8J

10P_0201_50V8J

+VDD_1V8_SYS_TEGRA

12

R91

R91

100K_0201_5%

100K_0201_5%

LINE_OUT_DET#

1

C40

C40

2

@

@

R52

R52

1K_0201_1%

1K_0201_1%

PWR_I2C_SCL <10,14,15,26,32,34>

PWR_I2C_SDA <10,14,15,26,32,34>

CORE_PWR_REQ <27,32>

CPU_PWR_REQ < 32>

T2PAD@ T2PAD@

CLK_32K_OUT <22>

+VDD_1V8_SYS_TEGRA

WAKEUP_LED <27>

EN_CAM_1V8# <23>

UART_SW <20>

SHORT_DET <15>

WF_WAKE# <22>

G_ACC_INT <16>

T4PAD@ T4PAD@

T5PAD@ T5PAD@

T6PAD@ T6PAD@

T7PAD@ T7PAD@

T8PAD@ T8PAD@

T9PAD@ T9PAD@

PCB_ID3

PICASSO_M PICASSO_2

H LPCB_ID3

7

7

7

0.1U_0201_10V6K

0.1U_0201_10V6K

10K_0201_5%

10K_0201_5%

PICASSO_M@

PICASSO_M@

R195

R195

1 2

10K_0201_5%

10K_0201_5%

PICASSO_2@

PICASSO_2@

R163

R163

1 2

1.0

1.0

1.0

38

38

38

Page 8

5

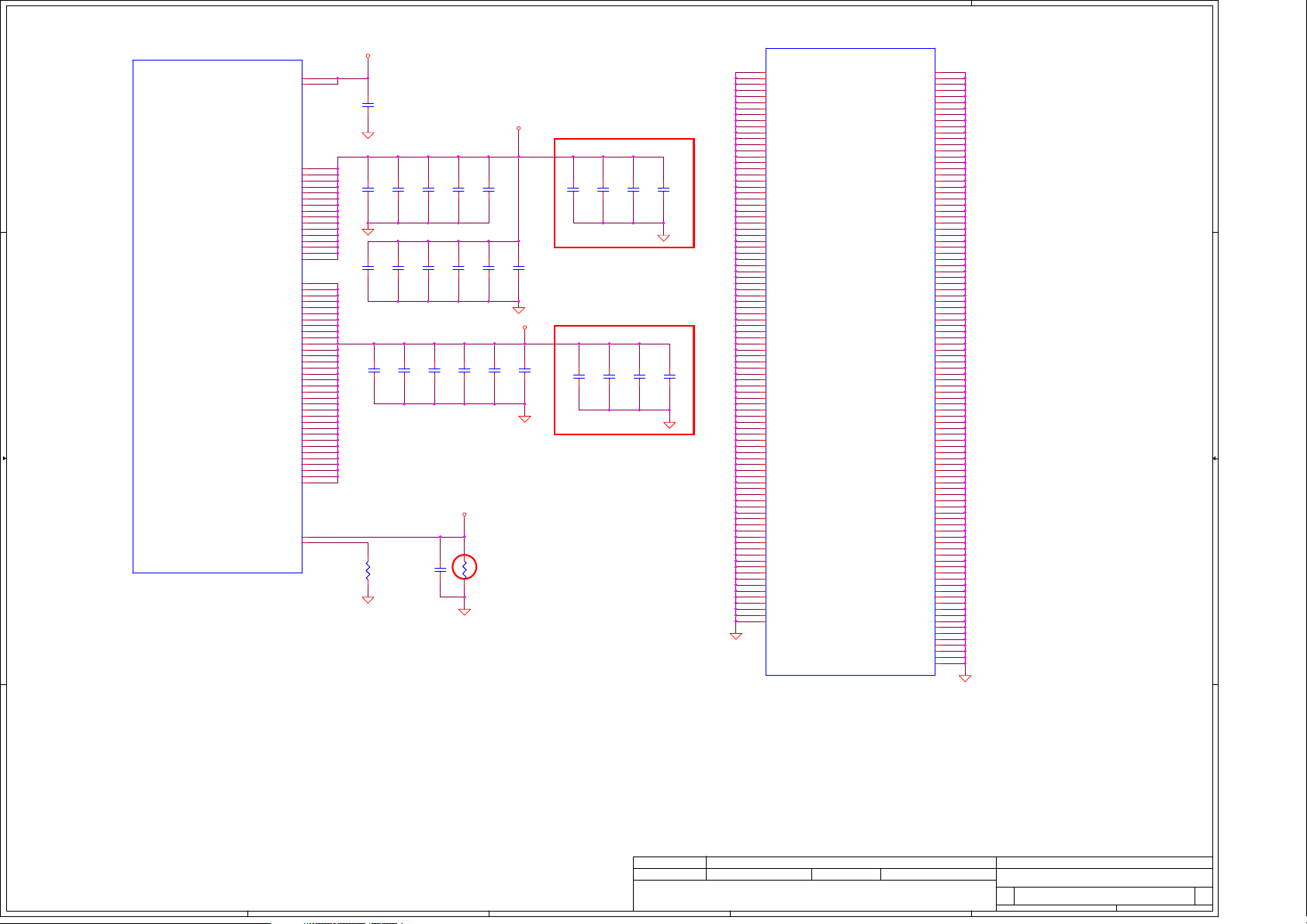

U1A

U1A

1/21 CORE POWER

1/21 CORE POWER

D D

C C

B B

(1.0 ~ 1.2V)

(1.0 ~ 1.2V)

VDD_RTC_1

VDD_RTC_2

(0.9 ~ 1.0V)

(0.9 ~ 1.0V)

VDD_CPU_01

VDD_CPU_02

VDD_CPU_03

VDD_CPU_04

VDD_CPU_05

VDD_CPU_06

VDD_CPU_07

VDD_CPU_08

VDD_CPU_09

VDD_CPU_10

VDD_CPU_11

VDD_CPU_12

VDD_CPU_13

VDD_CPU_14

VDD_CPU_15

VDD_CPU_16

(1.0 ~ 1.2V)

(1.0 ~ 1.2V)

VDD_CORE_01

VDD_CORE_02

VDD_CORE_03

VDD_CORE_04

VDD_CORE_05

VDD_CORE_06

VDD_CORE_07

VDD_CORE_08

VDD_CORE_09

VDD_CORE_10

VDD_CORE_11

VDD_CORE_12

VDD_CORE_13

VDD_CORE_14

VDD_CORE_15

VDD_CORE_16

VDD_CORE_17

VDD_CORE_18

VDD_CORE_19

VDD_CORE_20

VDD_CORE_21

VDD_CORE_22

VDD_CORE_23

VDD_CORE_24

VDD_CORE_25

VDD_CORE_26

VDD_CORE_27

VDD_CORE_28

VDD_CORE_29

VDD_CORE_30

VDD_CORE_31

VDD_CORE_32

VDD_CORE_33

VDD_CORE_34

(3.3V)

(3.3V)

VPP_FUSE

(3.3V)

(3.3V)

VPP_KFUSE

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

AH26

AJ25

AB12

AB14

AB16

AB18

AB20

AD12

AD14

AD16

AD18

AF14

AF16

T20

V18

V20

Y18

Y20

AB22

AB24

AB26

AD20

AD22

AD24

AD26

AF18

AF20

AF22

AF24

P14

P16

P18

P20

P22

T14

T16

T18

T22

T24

V12

V14

V16

V22

V24

V26

W25

Y12

Y14

Y16

Y22

Y24

Y26

AU17

AU9

+VDD_1V2_RTC_TEGRA

C47

C47

C49

C49

C53

C53

VPP_KFUSE

R64

R64

10K_0201_5%

10K_0201_5%

4

1

2

0.1U_0201_10V6K

0.1U_0201_10V6K

1

1

1

C51

C51

C52

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

1

C55

C55

2

0.1U_0201_10V6K

0.1U_0201_10V6K

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

1

C61

C61

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

+VDD_3V3_FUSE_TEGRA

C65

C65

C52

C56

C56

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

1

2

0.1U_0201_10V6K

0.1U_0201_10V6K

C50

C50

2

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

1

1

C54

C54

2

2

0.1U_0201_10V6K

0.1U_0201_10V6K

1

1

C59

C59

C60

C60

2

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

1 2

VDD_1V0_GEN

1

1

C48

C48

2

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

1

C57

C57

2

C63

C63

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

R65

R65

10K_0201_5%

10K_0201_5%

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

VDD_1V2_SOC

1

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

1

C58

C58

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

1

C64

C64

2

0.1U_0201_10V6K

0.1U_0201_10V6K

1

2

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

1

C62

C62

2

12

12/12 Modify R65 from @ to mount.

3

Acer request 07/04

1

1

C88

C88

C101

C101

C102

C102

2

2

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

Acer request 07/04

1

1

C104

C104

C105

C105

C106

2

C106

2

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

2

U1B

U1B

21/21 GND

21/21 GND

AU7

GND_100

B10

GND_101

B16

GND_102

B2

GND_103

B22

GND_104

B28

GND_105

B36

GND_106

C1

GND_107

C3

GND_108

C35

GND_109

C37

GND_110

D10

GND_111

D16

GND_112

D22

GND_113

D28

GND_114

D34

GND_115

D4

GND_116

E33

GND_117

1

1

C103

C103

2

2

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

1

1

C107

C107

2

2

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

0.1U_0201_10V6K

E5

GND_118

F32

GND_119

F6

GND_120

G1

GND_121

G13

GND_122

G19

GND_123

G25

GND_124

G31

GND_125

G37

GND_126

G7

GND_127

H30

GND_128

H32

GND_129

H6

GND_130

H8

GND_131

J11

GND_132

J27

GND_133

J29

GND_134

J9

GND_135

K10

GND_136

K16

GND_137

K2

GND_138

K22

GND_139

K28

GND_140

K34

GND_141

K36

GND_142

K4

GND_143

L11

GND_144

L13

GND_145

L17

GND_146

L21

GND_147

L25

GND_148

L27

GND_149

M12

GND_150

M26

GND_151

N1

GND_152

N11

GND_153

N13

GND_154

N25

GND_155

N27

GND_156

N31

GND_157

N37

GND_158

N7

GND_159

P24

GND_160

R13

GND_161

R15

GND_162

R17

GND_163

R19

GND_164

R21

GND_165

R23

GND_166

T10

GND_167

T2

GND_168

T28

GND_169

T34

GND_170

T36

GND_171

T4

GND_172

U11

GND_173

U13

GND_174

U15

GND_175

U17

GND_176

U19

GND_177

U21

GND_178

U23

GND_179

U25

GND_180

U27

GND_181

W1

GND_182

W13

GND_183

W15

GND_184

W17

GND_185

W19

GND_186

W21

GND_187

W23

GND_188

W31

GND_189

W37

GND_190

W7

GND_191

A13

GND_1

A19

GND_2

A25

GND_3

A3

GND_4

A31

GND_5

A35

GND_6

A7

GND_7

AA11

GND_8

AA13

GND_9

AA15

GND_10

AA17

GND_11

AA19

GND_12

AA21

GND_13

AA23

GND_14

AA25

GND_15

AA27

GND_16

AB10

GND_17

AB2

GND_18

AB28

GND_19

AB34

GND_20

AB36

GND_21

AB4

GND_22

AC13

GND_23

AC15

GND_24

AC17

GND_25

AC19

GND_26

AC21

GND_27

AC23

GND_28

AC25

GND_29

AE1

GND_30

AE11

GND_31

AE13

GND_32

AE15

GND_33

AE17

GND_34

AE19

GND_35

AE21

GND_36

AE23

GND_37

AE25

GND_38

AE27

GND_39

AE31

GND_40

AE37

GND_41

AE7

GND_42

AF12

GND_43

AF26

GND_44

AG11

GND_45

AG13

GND_46

AG17

GND_47

AG21

GND_48

AG25

GND_49

AG27

GND_50

AH10

GND_51

AH16

GND_52

AH2

GND_53

AH22

GND_54

AH28

GND_55

AH34

GND_56

AH36

GND_57

AH4

GND_58

AJ11

GND_59

AJ27

GND_60

AJ29

GND_61

AJ9

GND_62

AK30

GND_63

AK32

GND_64

AK6

GND_65

AK8

GND_66

AL1

GND_67

AL13

GND_68

AL19

GND_69

AL25

GND_70

AL31

GND_71

AL37

GND_72

AL7

GND_73

AM32

GND_74

AM6

GND_75

AN33

GND_76

AN5

GND_77

AP10

GND_78

AP16

GND_79

AP22

GND_80

AP28

GND_81

AP34

GND_82

AP4

GND_83

AR1

GND_84

AR3

GND_85

AR35

GND_86

AR37

GND_87

AT10

GND_88

AT16

GND_89

AT2

GND_90

AT22

GND_91

AT28

GND_92

AT36

GND_93

AU13

GND_94

AU19

GND_95

AU25

GND_96

AU3

GND_97

AU31

GND_98

AU35

GND_99

T30S-R-A3-1.4G_FCCSP681

T30S-R-A3-1.4G_FCCSP681

1

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

2012/06/202011/06/20

2012/06/202011/06/20

2012/06/202011/06/20

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

T30S(5/5)PWR_GND_NC

T30S(5/5)PWR_GND_NC

T30S(5/5)PWR_GND_NC

Picasso 2 R04

Picasso 2 R04

Tuesday, January 17, 2012

Tuesday, January 17, 2012

Tuesday, January 17, 2012

Picasso 2 R04

1

1.0

1.0

8

8

8

1.0

38

38

38

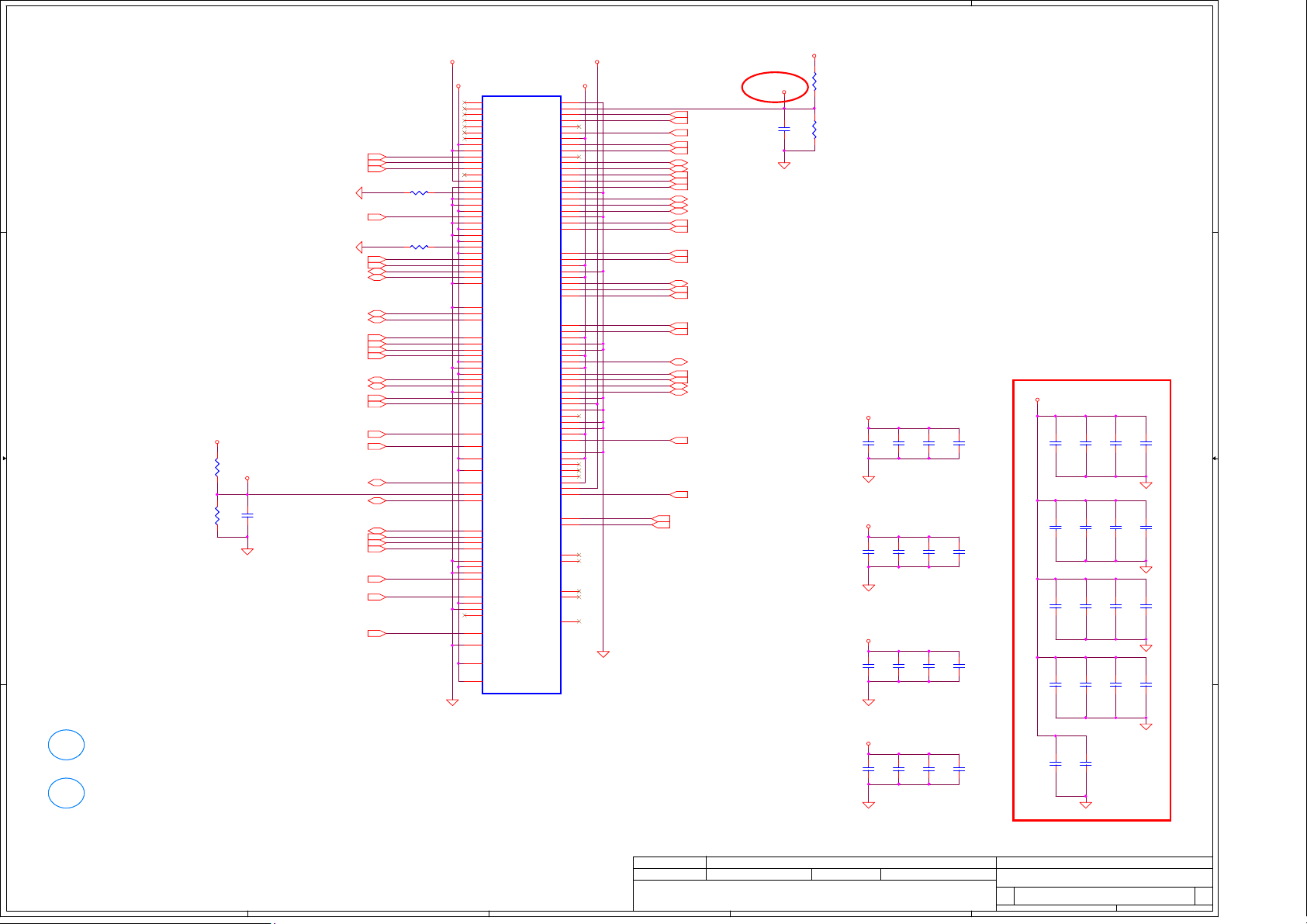

Page 9

5

4

3

2

1

Follow NV design

ET NAME BALL NAME

N

A0 P3

A1 N3

A2 M3

A3 M2

A4 M1

A5 G2

D D

C C

B B

A A

A6 F2

A7 F3

A8 E3

A9 E2

CKE0 K1

CKE1 K2

CLK J3

CLK# H3

CS0 L1

CS1 L2

DM0 K5

DM1 H5

DQ0 M9

DQ1 N8

DQ10 F7

DQ11 F9

DQ12 F6

DQ13 G9

DQ14 F8

DQ15 E8

DQ2 M8

DQ3 M7

DQ4 L9

DQ5 L7

DQ6 L8

DQ7 M6

DQ8 G7

DQ9 G8

DQS0 L6

DQS0# L5

DQS1 G6

DQS1# G5

Layer 2

DM2 N7

DM3 E7

DQ16 T8

DQ17 N6

DQ18 P7

DQ19 N5

DQ20 T7

DQ21 T9

DQ22 R8

DQ23 P6

DQ24 D6

DQ25 B8

DQ26 E5

DQ27 E6

DQ28 D7

DQ29 B7

DQ30 C8

DQ31 B9

DQS2 P8

DQS2# P9

DQS3 D8

DQS3# D9

U7

U7

X76_SAM_1GB@

X76_SAM_1GB@

SA00004YY20

SA00004YY20

U7

U7

X76_ELP_1GB@

X76_ELP_1GB@

SA000050Z10

SA000050Z10

+VDD_1V2_DDR_MEM

12

R68

R68

100K_0201_5%

100K_0201_5%

100K_0201_5%

100K_0201_5%

+VRAM_VREFA

12

R69

R69

( 1GB Samsung )

( 1GB Elpida )

1

C68

C68

0.1U_0201_10V6K

0.1U_0201_10V6K

2

DDR_A_D29<5>

DDR_A_D25<5>

DDR_A_D31<5>

DDR_A_D30<5>

DDR_A_D24<5>

DDR_A_D28<5>

DDR_A_DQS3<5>

DDR_A_DQS#3<5>

DDR_A_MA9<5>

DDR_A_MA8<5>

DDR_A_D26<5>

DDR_A_D27<5>

DDR_A_DM3<5>

DDR_A_D15<5>

DDR_A_MA6<5>

DDR_A_MA7<5>

DDR_A_D12<5>

DDR_A_D10<5>

DDR_A_D14<5>

DDR_A_D11<5>

DDR_A_MA5<5>

DDR_A_DQS#1<5>

DDR_A_DQS1<5>

DDR_A_D8<5>

DDR_A_D9<5>

DDR_A_D13<5>

M_CLK_DDR#0<5>

DDR_A_DM1<5>

M_CLK_DDR0<5>

+VDD_1V8_DDR_MEM +VDD_1V8_DDR_MEM

R70

R70

1 2

240_0402_1%

240_0402_1%

R71

R71

1 2

240_0402_1%

240_0402_1%

+VDD_1V2_DDR_MEM

A1

A2

A9

A10

B1

B2

B3

B5

B6

B7

B8

B9

B10

C1

C2

C3

C5

C6

C7

C8

C9

C10

D1

D2

D3

D5

D6

D7

D8

D9

D10

E1

E2

E3

E5

E6

E7

E8

E9

E10

F1

F2

F3

F5

F6

F7

F8

F9

F10

G1

G2

G3

G5

G6

G7

G8

G9

G10

H1

H2

H3

H5

H6

J1

J2

J3

J5

J6

J7

U7

U7

NU

NU

NU

NU

NU

NC

NC

VDD2

VDD1

DQ31

DQ29

DQ26

NU

VDD1

VSS

ZQ1

Vss

VSS

VDDQ

DQ25

VSS

VDDQ

VSS

VDD2

ZQ0

VDDQ

DQ30

DQ27

DQS3

/DQS3

VSS

VSS

CA9

CA8

DQ28

DQ24

DM3

DQ15

VDDQ

VSS

NC

CA6

CA7

VSS

DQ11

DQ13

DQ14

DQ12

VDDQ

VDD2

CA5

VREFCA

/DQS1

DQS1

DQ10

DQ9

DQ8

VSS

NC

VSS

/CK

DM1

VDDQ

VSS

NC

CK

VSS

VDDQ

VDD2

EDB8132B2MA-6D-F_FBGA134

EDB8132B2MA-6D-F_FBGA134

X76_ELP_512M@

X76_ELP_512M@

VREFDQ

CKE0

CKE1

VDDQ

/DQS0

DQS0

VDDQ

DQ19

DQ23

VDDQ

VDD2

VDDQ

DQ17

DQ20

DQS2

/DQS2

VDD1

VDDQ

DQ22

VDDQ

VDD2

VDD1

DQ16

DQ18

DQ21

VSS

NC

DM0

/CS0

/CS1

NC

DQ5

DQ6

DQ7

VSS

CA4

CA3

CA2

VSS

DQ4

DQ2

DQ1

DQ3

VSS

NC

CA1

DM2

DQ0

VSS

VSS

CA0

VSS

VSS

NC

VSS

VSS

VSS

NU

NC

NC

NU

NU

NU

NU

NU

+VDD_1V2_DDR_MEM

J8

J9

K1

K2

K3

K5