Page 1

A

COMPALCONFIDENTIAL

B

C

D

E

1 1

PCBNO:

LA‐7903P(DA60000Q410)

BOMP/N:

MODELNAME:

GPIOMAP:

E4_VC_GPIO_map_rev_1.1

QXW00

4619FT31L01/L02

Korbel14UMA

IvyBridge+PantherPOINT(QM77w/Vpro)

2 2

2012‐03‐22

REV:1.0(A00)

@:NopopComponent

CONN@:ConnectorComponent

MBType

TPM

BOMP/N

43*

1@

3@

5@

3 3

TPMDIS 2@

2@ 4@TCM

5@

3@

HM77w/oVpro

QM77w/Vpro

PCHXDP

HDMILOGO

4 4

PXDP@

46@

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

MB PCB

MB PCB

Part Number Description

Part Number Description

A

PCB 0LH LA-7903P REV1 M/B UMA

PCB 0LH LA-7903P REV1 M/B UMA

DA60000Q410

DA60000Q410

B

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

C

D

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC MB A7903

SCHEMATIC MB A7903

SCHEMATIC MB A7903

4019FT

4019FT

4019FT

161Monday, April 02, 2012

161Monday, April 02, 2012

161Monday, April 02, 2012

E

B

B

B

of

of

of

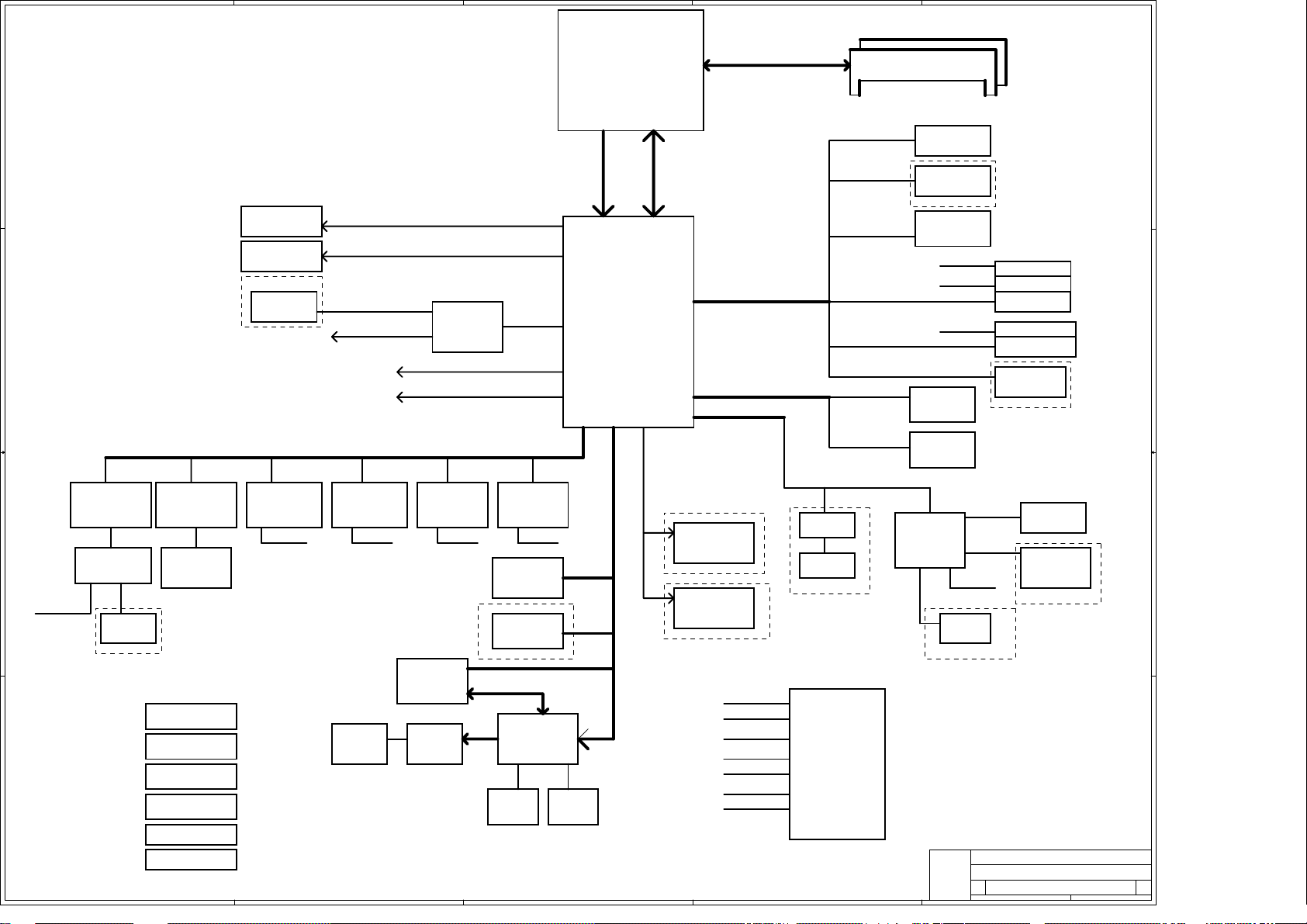

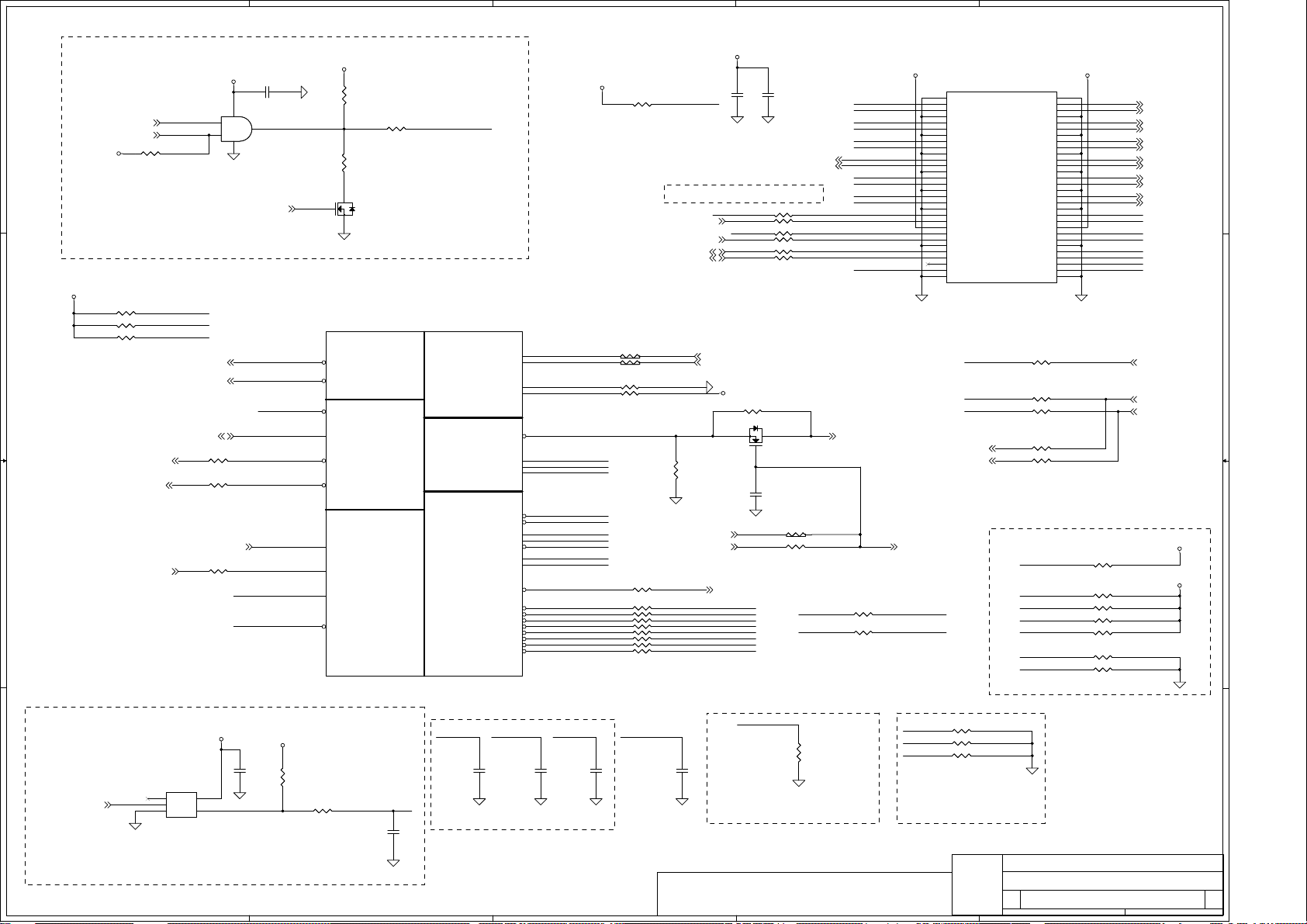

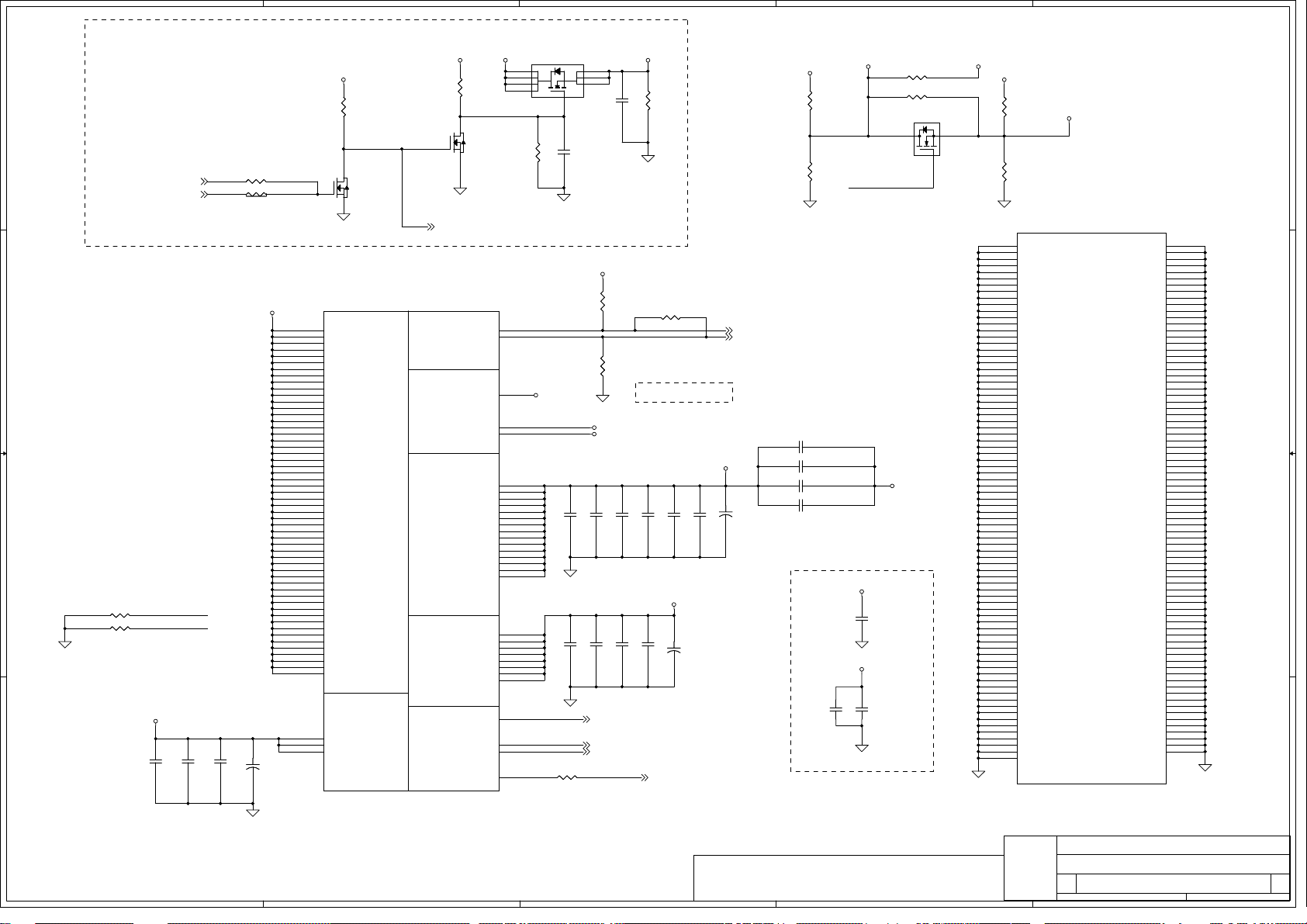

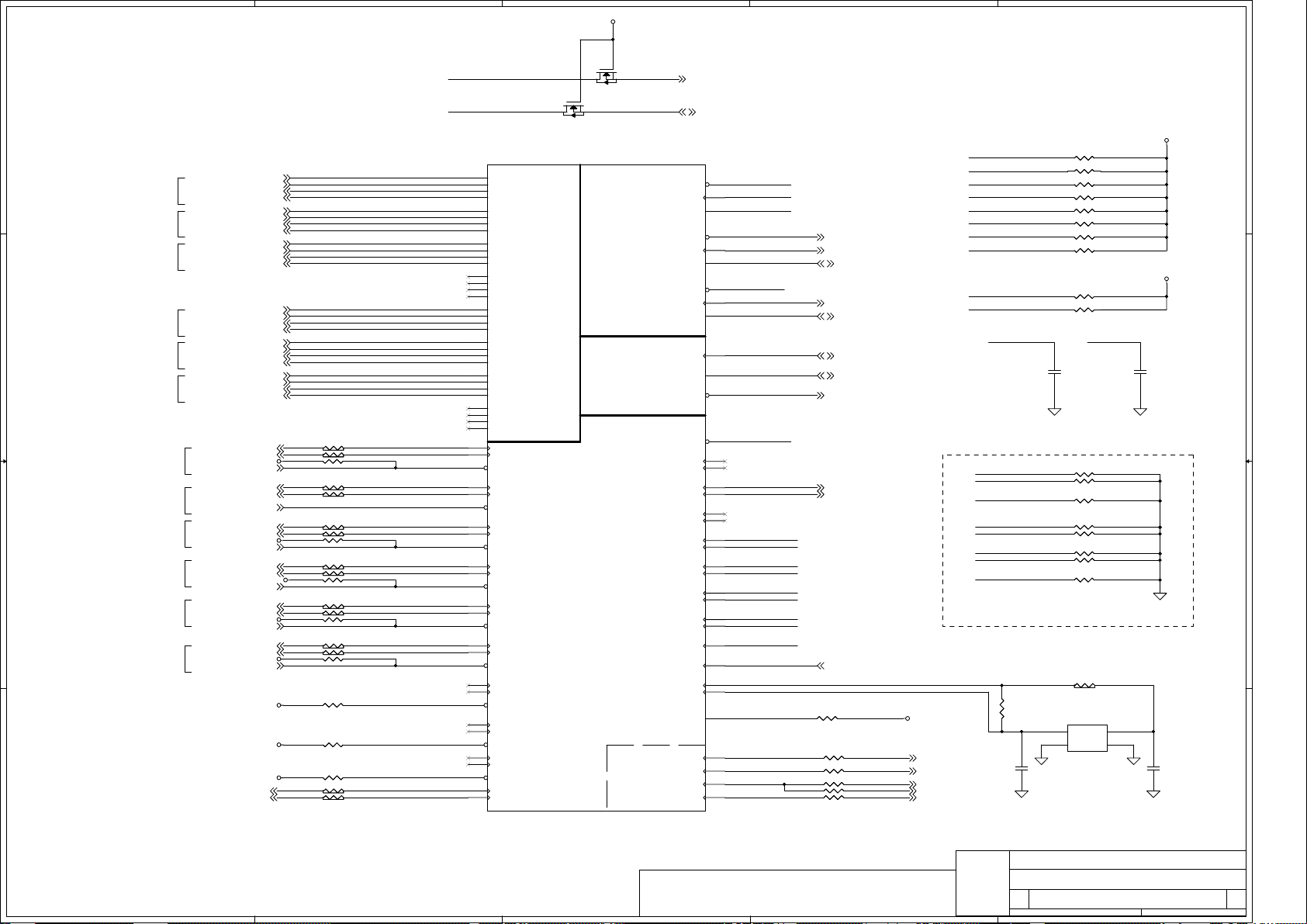

Page 2

A

B

C

D

E

Intel

IvyBridge

Processorr

MemoryBUS

1.5VDDRIII1333/1600MHz

DDRIII‐DIMMX4

BANK0,1,2,3,4,5,6,7

P12‐13

rPGA989Socket

1 1

FDIx8 DMIGen2x4

LVDSCONN

P23

HDMICONN

P25

OnIOboard

CRTCONN

P37

2 2

VGA

DockingVGA

ForMB/DOCK

VideoSwitch

PI3V713‐AZLEX

DockingDPC

DockingDPD

PCIEBUS

1/2MiniCard

WLAN/WiFi

SMSCSIO

ECE5048

EMC4021PWMFAN

Port2Port5Port3Port6

P39

Port7

Hanksville

Intel82579

CardReader

OZ600FJ0

Smartcard

Expresscard

1/2MiniCard

PP

P30~31

USBport6USBport10

DockingLAN

LANSWITCH

PI3L720

3 3

RJ45

onIOboard

4 4

A

P31

P37

DC/DCInterface

SDXC/MMC

CPUXDPPort

PCHXDPPort

WiFiON/OFF

LED

FFSLNG3DM

P33

P7

P14

P37

P42

P43

www.schematic-x.blogspot.com

P27

B

LVDS

DPB

VGA

P23

Port1

FullMiniCard

WWAN

USBport5USBport4

ChinaTCM1.2

SSX44B

P32

DiscreteTPM

AT97SC3204

P32

Option

BCBUS

SMSCKBC

ECE5055

TPCONN KBCONN

P41 P41

INTEL

PantherPOINT‐M

BGA989Balls

QM77

LPCBus

P34P34P34P35P33

P40P22P22

C

P14~21

SPIBus

P6‐11

W25Q64BVSSIG

64M8Ksector

W25Q32BVSSIG

32M4Ksector

USB

SATA3.0

P14

P14

DockingDPC

DockingDPD

DAI

USB2.0[3,8]

SATAport5

DOCKLAN

USB3.0[4]

USBport11

USBport12

USBport13

USBport2

USBport1

USBport0.9

Port0

Port1

HDAudioI/F

MDC

P37

RJ11

onIOboard

DOCKING

D

P38

BT4.0

Camera

ThroughLVDSCable

Fingerprint

CONN

SATAport4

USB3.0port3

USB3.0port2

HDDCONN

P27

ODDCONN

P28

HDACodec

92HD90B2

P29

Dig.MIC

ThroughLVDSCable

P41

P24

P41

E‐SATA

USB3.0Port

USB2.0Port

P36

USB3.0Port

USB2.0Port

P36

USB2.0

P37

onIOboard

INT.Speaker

P29

ComboJack

DAI

P37

onAudioboard

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

SCHEMATIC MB A7903

SCHEMATIC MB A7903

SCHEMATIC MB A7903

4019FT

4019FT

4019FT

E

261Monday, April 02, 2012

261Monday, April 02, 2012

261Monday, April 02, 2012

of

of

of

B

B

B

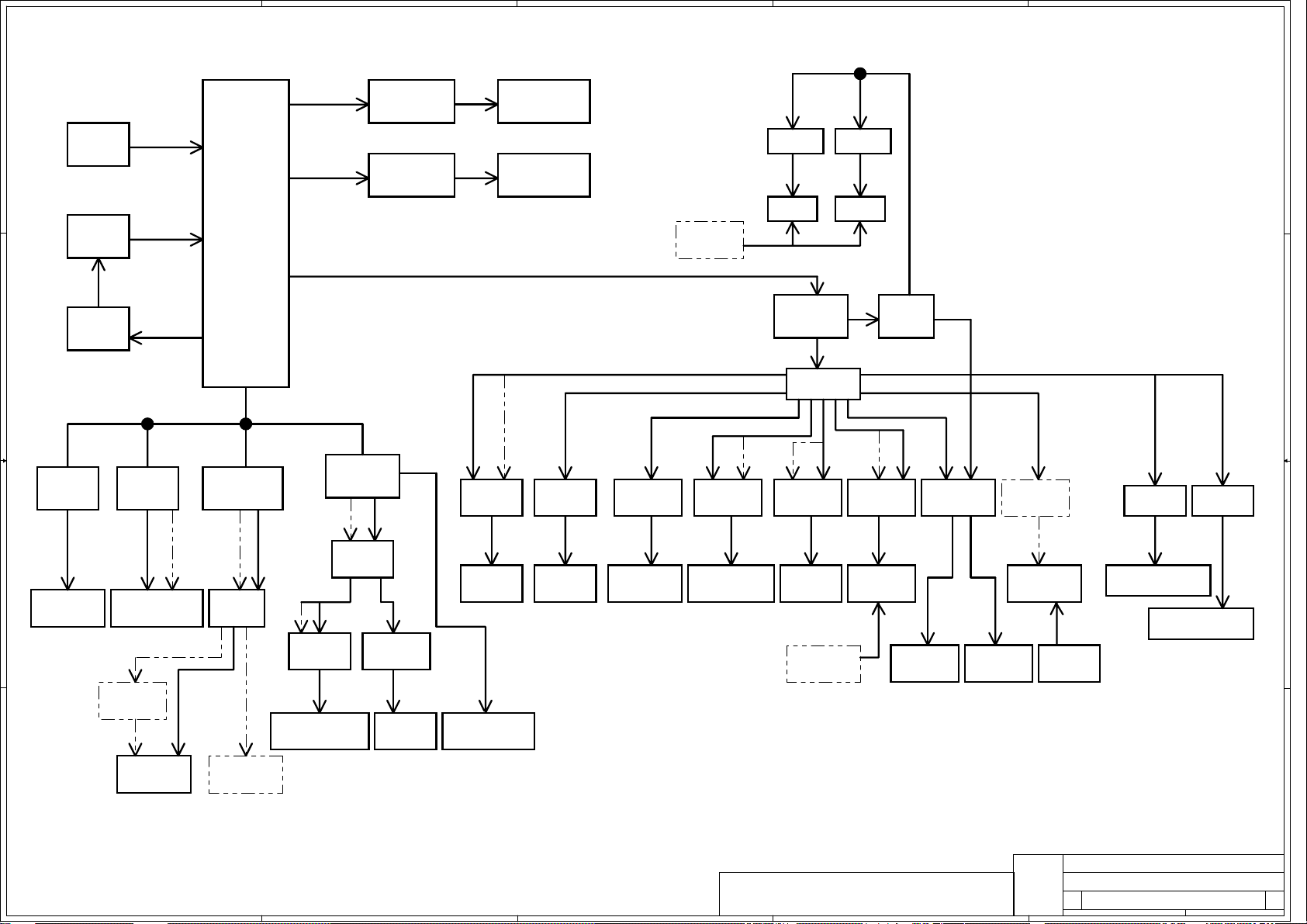

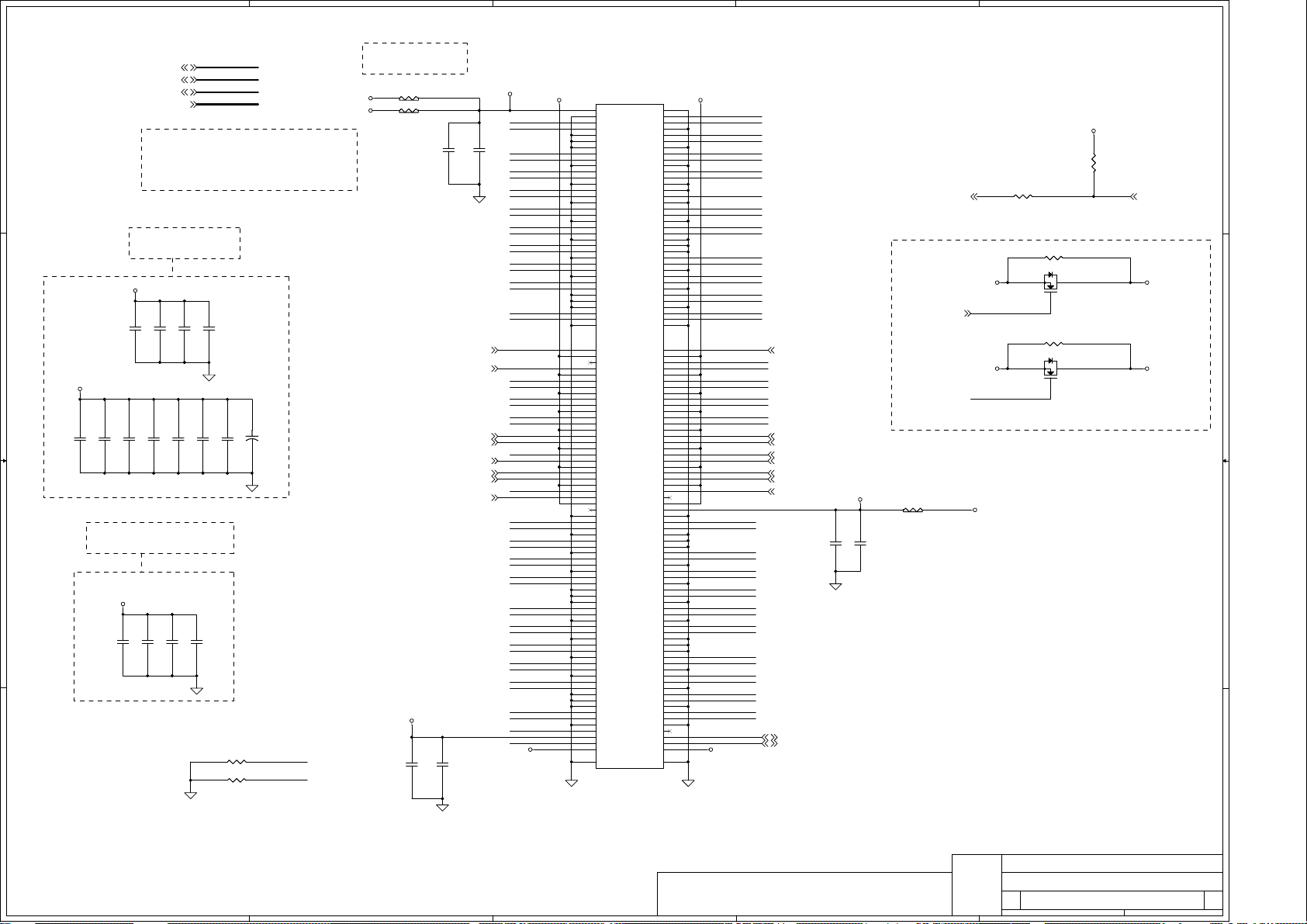

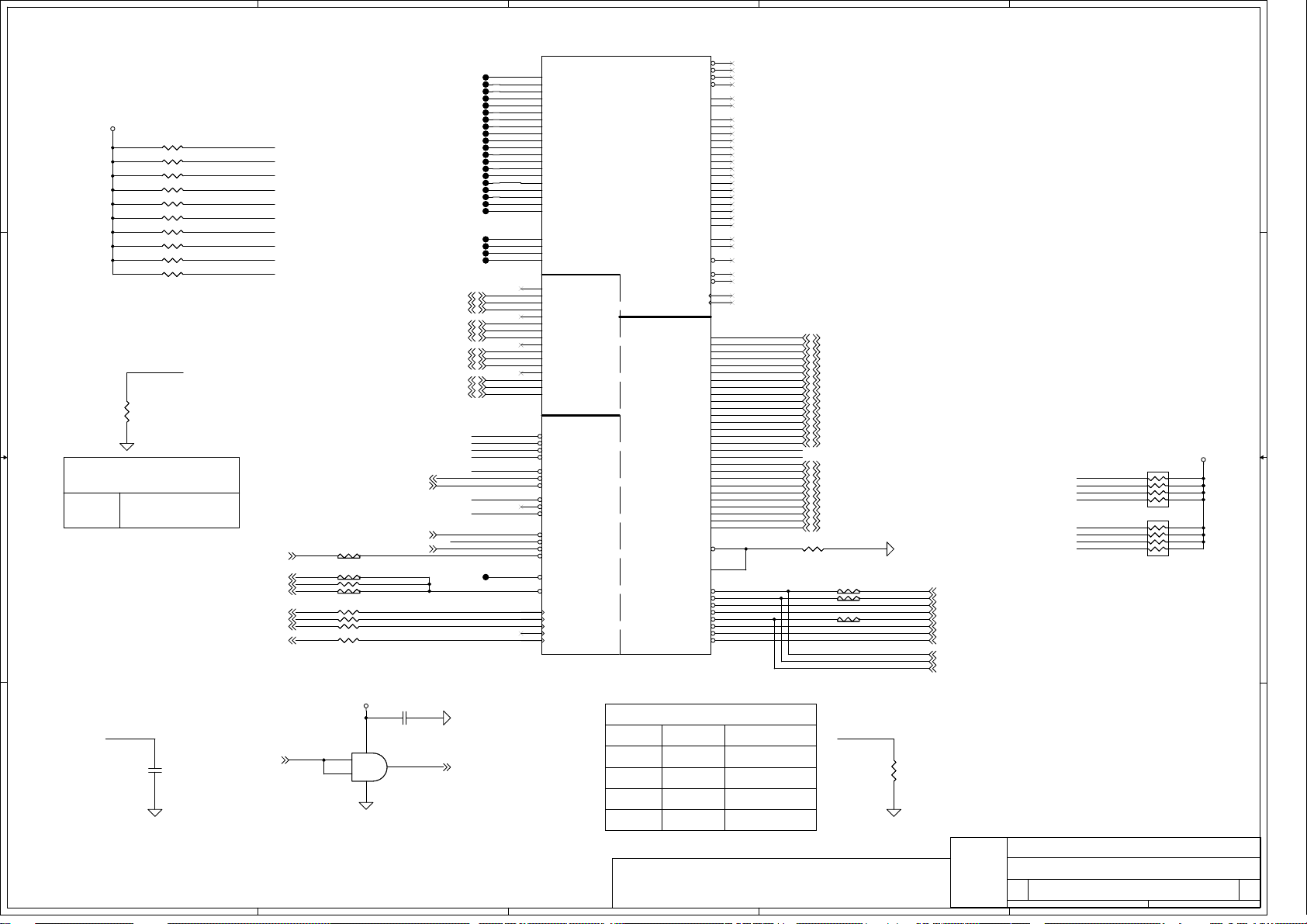

Page 3

5

4

3

2

1

POWER STATES

State

S0 (Full ON) / M0

D D

S3 (Suspend to RAM) / M3

S4 (Suspend to DISK) / M3 ON ON OFF

S5 (SOFT OFF) / M3 ON ON OFFLOW HIGHLOW

S3 (Suspend to RAM) / M-OFF

S4 (Suspend to DISK) / M-OFF

S5 (SOFT OFF) / M-OFF

Signal

SLP

S3#

HIGH

LOW HIGH HIGH ON ON ON OFF

LOW HIGH HIGH

LOW HIGH HIGH LOW ON ONOFF OFF OFF

LOW LOW LOW ON OFF OFF OFF OFF

LOW LOW LOW LOW ON OFF OFF OFF OFF

SLP

SLP

S5#

S4#

HIGH HIGH

LOW

LOW

HIGH

SLP

A#

HIGH

HIGH

ALWAYS

PLANE

ON

M

PLANE

ON

SUS

RUN

PLANE

PLANE

ON ON ON

OFF

OFF

CLOCKS

OFF

OFF

OFF

USB 3.0 PORT#

1

2

3 JUSB2 (Left side)

4

Connetion

NA

JUSB1 (Left side)

DOCKING

PCH

USB PORT#

0

1

2

3

4

5

6

*1

7

*1

8

JUSB (Right side-IO/B)

JUSB (Left side)

JESA1 (Leftt side ESATA)

MLK DOCK

WLAN

WWAN

JMINI3(Flash)-for w/ Vpro

DOCKING

NA

DESTINATION

PM TABLE

C C

power

plane

State

S0

S3

S5 S4/AC

S5 S4/AC don't exist

B B

+15V_ALW

+5V_ALW

+3.3V_ALW_PCH

+3.3V_RTC_LDO

ON

ON

+3.3V_SUS

+1.5V_MEM

ON ON

ON

OFF

OFFOFF

+5V_RUN

+3.3V_RUN

+1.8V_RUN

+1.5V_RUN

+0.75V_DDR_VTT

+VCC_CORE

+1.05V_RUN_VTT

+1.05V_RUN

OFFON

OFF

OFF

needtoupdatePowerStatusand

PMTable

+3.3V_M +3.3V_M

+1.05V_M

ON

ON

ON

+1.05V_M

(M-OFF)

ON

OFF

OFF

OFFOFF

SATA

SATA 0

SATA 1

SATA 2

SATA 3

SATA 4

DESTINATION

HDD

ODD/ E3 Module Bay

NA

NA

ESATA

9

10 Express card

11

12

13 BIO

*1: HM76 don't support port 6,7

PCI EXPRESS

Lane 1

Lane 2

Lane 3

SATA 5

Dock

Lane 4

JUSB (Right side-Audio/B)

Bluetooth

Camera

DESTINATION

MINI CARD-1 WWAN

MINI CARD-2 WLAN

Express card

None

UMA DP/HDMI Port

Port B

Port C

A A

Port D

Connetion

MB HDMI Conn

Dock DP port 2

Dock DP port 1

Lane 5

Lane 6

Lane 7

Lane 8 None

1/2vMINI CARD-3 PCIE

MMI

10/100/1G LOM

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC MB A7903

SCHEMATIC MB A7903

SCHEMATIC MB A7903

4019FT

4019FT

4019FT

361Monday, April 02, 2012

361Monday, April 02, 2012

361Monday, April 02, 2012

1

B

B

B

of

of

of

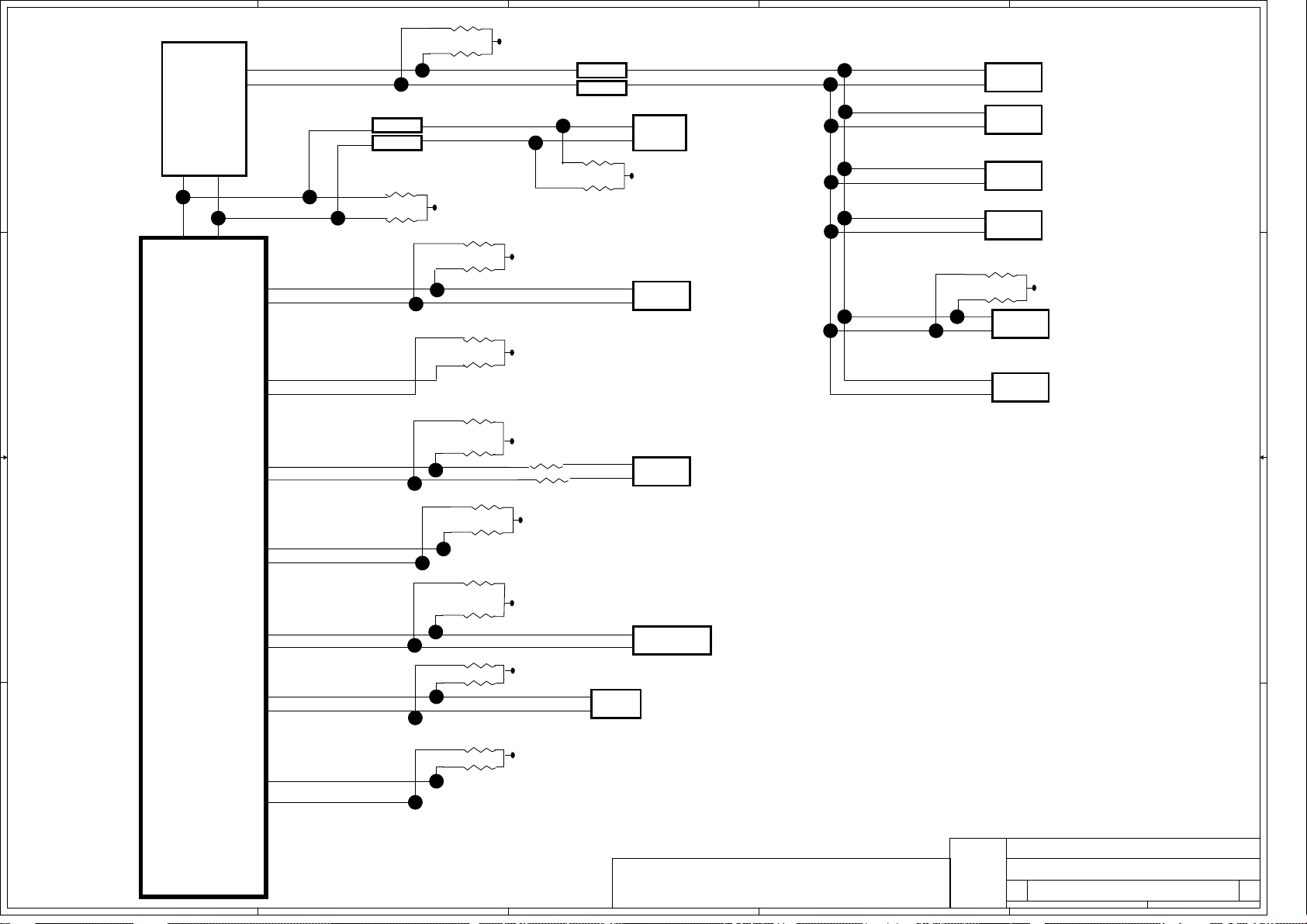

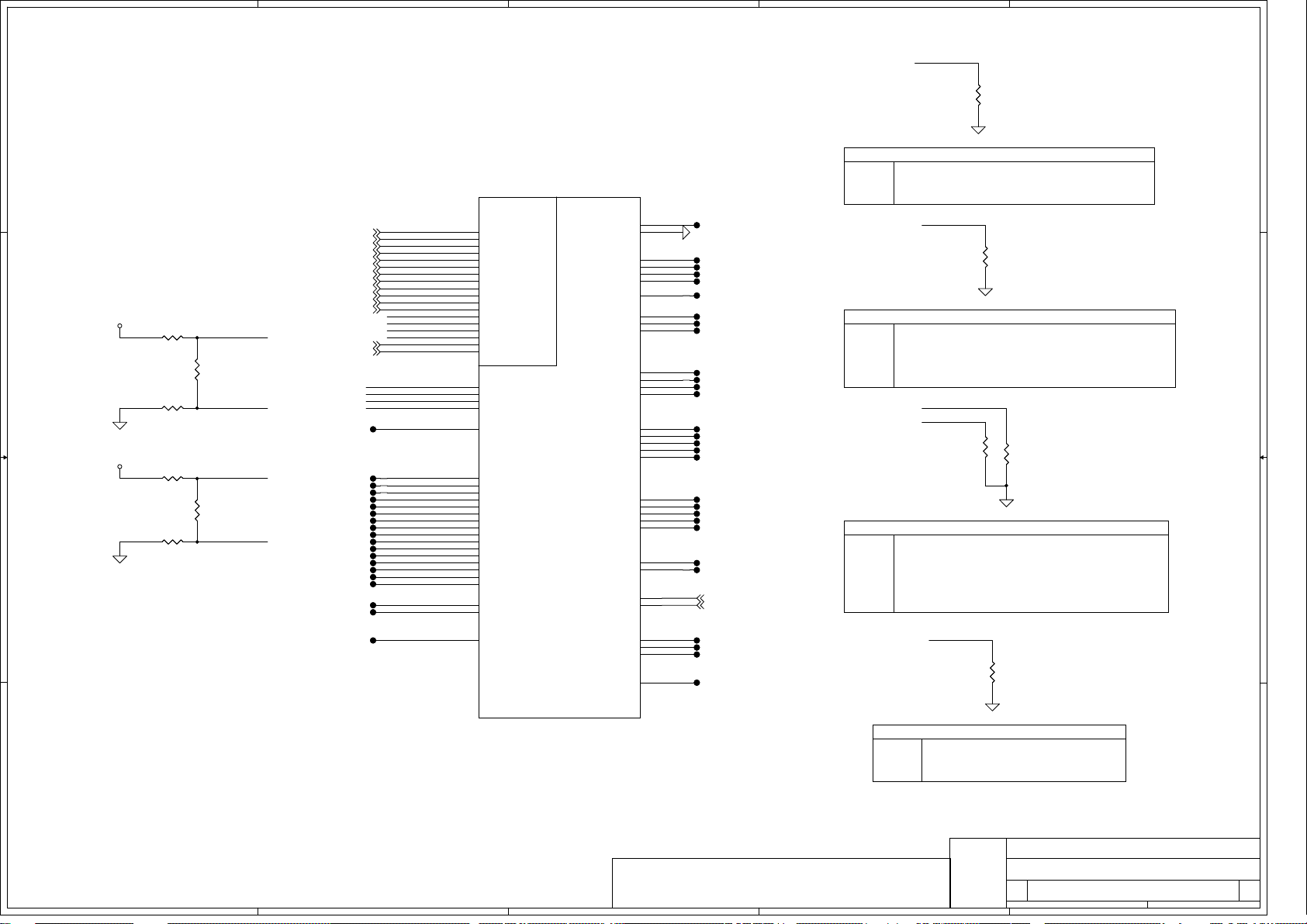

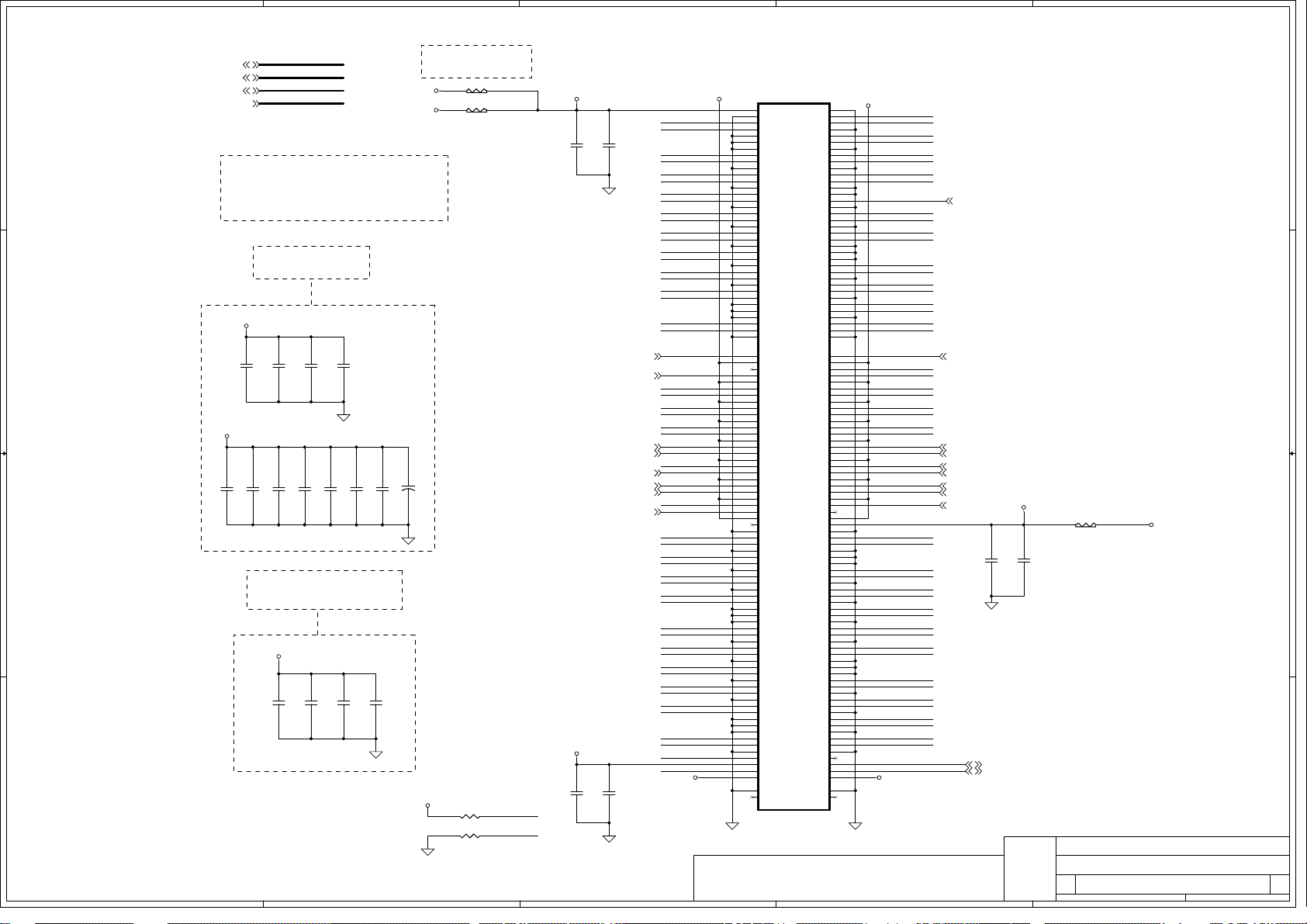

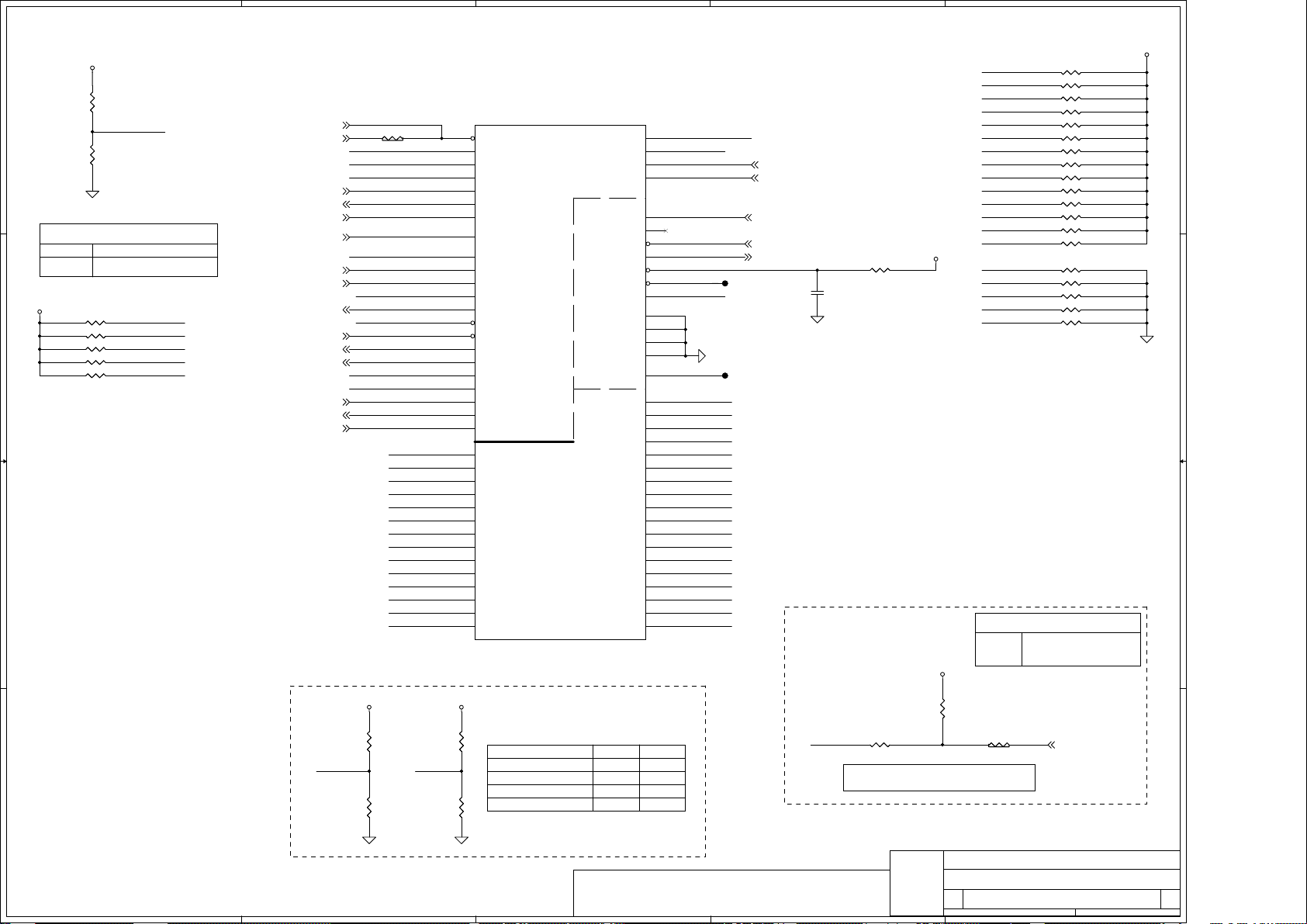

Page 4

5

4

3

2

1

EN_INVPWR

D D

ADAPTER

1.05V_0.8V_PWROK

BATTERY

+PWR_SRC

CHARGER

C C

FDC654P

(Q21)

ISL95836

(PU700)

+BL_PWR_SRC

+VCC_GFXCORE

+5V_RUN

+5V_HDD

Pop option

SIO_SLP_S3#

ALWON

RT8205

(PU100)

MODC_EN

SI3456BDVSI3456BDV

(Q30)(Q27)

+5V_MOD

+5V_ALW

+3.3V_ALW

RUN_ON

0.75V_DDR_VTT_ON

SIO_SLP_S3#

SYN470

(PU300)

+1.8V_RUN

AO4728

(QC3)

RT8207

(PU200)

DDR_ON

+1.5V_MEM

SIO_SLP_S3#

SIO_SLP_S4#

NTGS4141N

(Q59)

ISL95836

(PU700)

B B

1.05V_0.8V_PWROK

+VCC_CORE

TPS51212

(PU500)

CPU_VTT_ON

SIO_SLP_S3#

+1.05V_RUN_VTT +1.05V_M

SIO_SLP_S3#

SI4164

(Q63)

PJP8

TPS51212

(PU400)

SIO_SLP_A#

Pop option

SIO_SLP_S3#

CPU1.5V_S3_GATE

1.05V_VTTPWRGD

TPS51461

(PU7)

+VCC_SA

AUX_EN_WOWL

SI3456

(Q38)

+3.3V_WLAN

PCH_ALW_ON

SI3456

(Q49)

+3.3V_ALW_PCH

SIO_SLP_S5#

SUS_ON

S13456

(Q54)

+3.3V_M

SIO_SLP_S4#

SIO_SLP_LAN#

SI3456

(Q34) (U78)

+3.3V_LAN+3.3V_SUS

Pop option

AUX_ON

+3.3V_RUN

SIO_SLP_S3#

SIO_SLP_S3#

TPS22966

+5V_RUN

SIO_SLP_A#

SI3456

(Q58)

+3.3V_M

R206

+3.3V_SUS

MCARD_MISC_PWREN

SI3456

(Q42)

+3.3V_PCIE_FLASH

+3.3V_PCIE_WWAN

MCARD_WWAN_PWREN

SI3456

(Q40)

+0.75V_DDR_VTT+1.5V_RUN+1.5V_CPU_VDDQ

+1.05V_RUN

A A

+1.0V_LAN

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC MB A7903

SCHEMATIC MB A7903

SCHEMATIC MB A7903

4019FT

4019FT

4019FT

1

461Monday, April 02, 2012

461Monday, April 02, 2012

461Monday, April 02, 2012

B

B

B

of

of

of

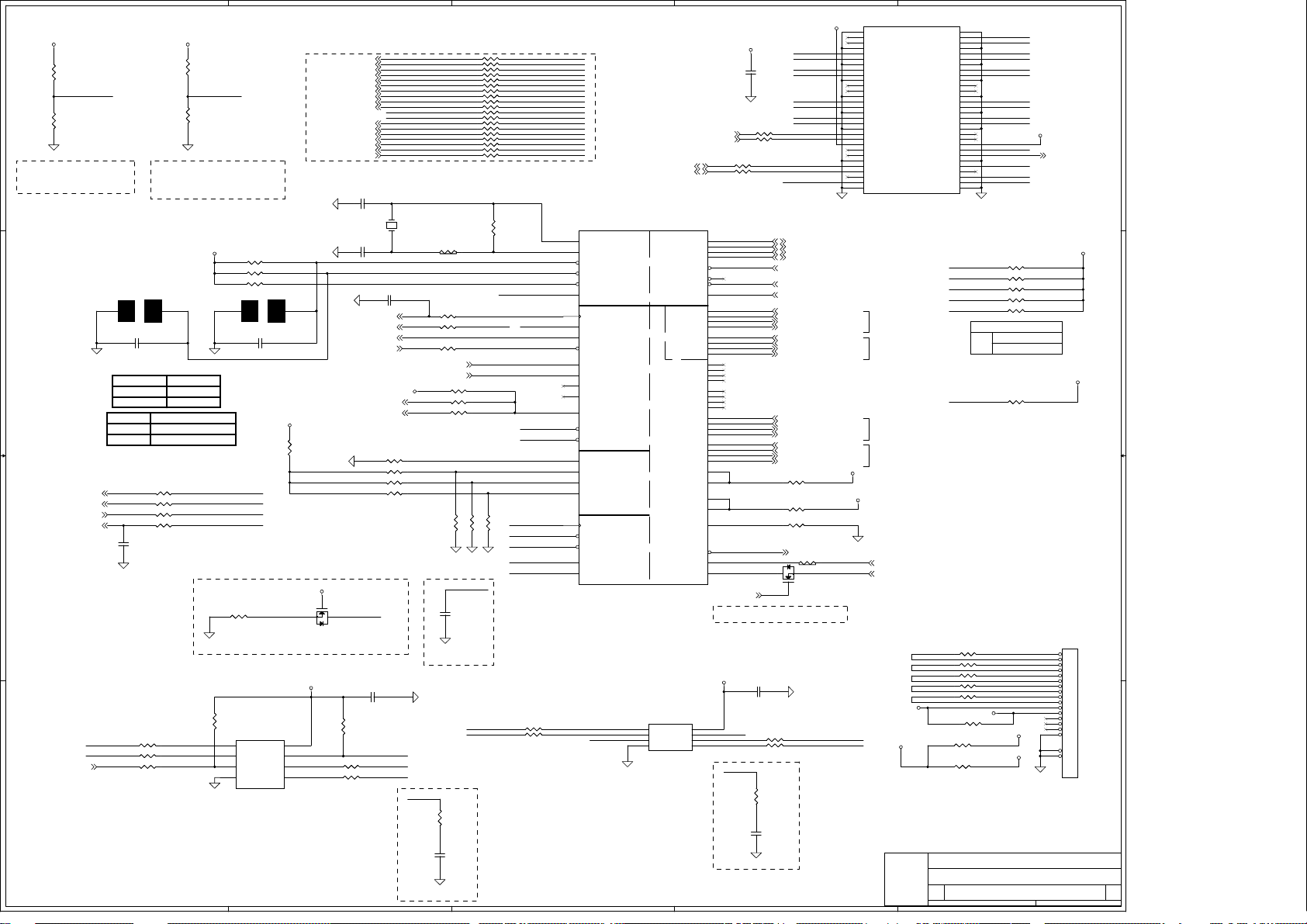

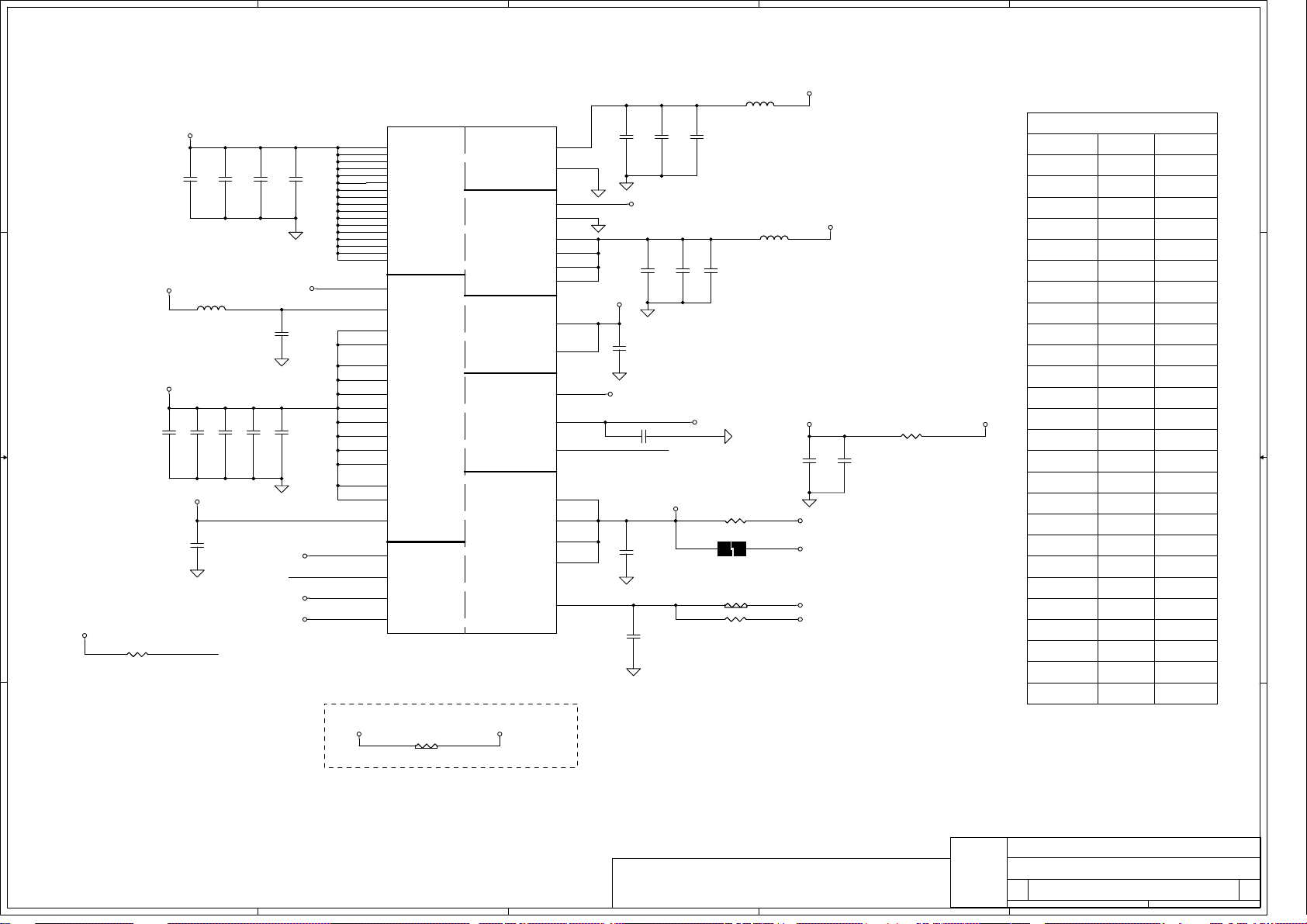

Page 5

5

SMBUS Address [0x9a]

H14

C9

MEM_SMBCLK

MEM_SMBDATA

PCH

D D

3A

C C

C8

G12

E14M16

SML1_SMBDATA

SML1_SMBCLK

B6A5

3A

1A

1A

1B

1B

B4

A3

B5

A4

DOCK_SMB_CLK

DOCK_SMB_DAT

LCD_SMBCLK

LCD_SMDATA

4

DMN66D0L

DMN66D0L

2.2K

2.2K

2.2K

2.2K

LAN_APE_SMB_DATA0

LAN_APE_SMB_CLK0

+3.3V_ALW_PCH

+3.3V_ALW_PCH

2.2K

2.2K

2.2K

2.2K

+3.3V_ALW

+3.3V_ALW

DMN66D0L

DMN66D0L

L09

L10

2.2K

2.2K

127

129

3

BCM LOM

+3.3V_LAN

DOCKING

SMBUS Address [**]

SMBUS Address

APR_EC: 0x48

SPR_EC: 0x70

MSLICE_EC: 0x72

USB: 0x59

AUDIO: 0x34

SLICE_BATTERY: 0x17

SLICE_CHARGER: 0x13

202

200

202

200

2

DIMM1

DIMM2

53

51

53

51

XDP1

XDP2

SMBUS Address [A0]

SMBUS Address [A4]

SMBUS Address [TBD]

SMBUS Address [TBD]

1

10K

G Sensor

WWAN

+3.3V_RUN

SMBUS Address [3B]

SMBUS Address [TBD]

10K

4

6

30

32

2.2K

KBC

A56

1C1CB59

PBAT_SMBCLK

2.2K

PBAT_SMBDAT

+3.3V_ALW

100 ohm

100 ohm

7

6

BATTERY

CONN

SMBUS Address [0x16]

2.2K

A50

1E

B53

B B

MEC 5055

1E

A49

2B

B52

2B

SIO_LAN_SMBCLK

SIO_LAN_SMBDAT

2.2K

2.2K

CARD_SMBCLK

CARD_SMBDAT

2.2K

2.2K

B50

A47

CHARGER_SMBCLK

CHARGER_SMBDAT

1G

1G

2.2K

2.2K

2.2K

B7

A7

BAY_SMBDAT

BAY_SMBCLK

2D

A A

2D

+3.3V_ALW

+3.3V_SUS

+3.3V_ALW

+3.3V_ALW

10

9

7

8

Charger

Express card

SMBUS Address [TBD]

SMBUS Address [0x12]

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC MB A7903

SCHEMATIC MB A7903

SCHEMATIC MB A7903

4019FT

4019FT

4019FT

561Monday, April 02, 2012

561Monday, April 02, 2012

561Monday, April 02, 2012

1

B

B

B

of

of

of

Page 6

5

D D

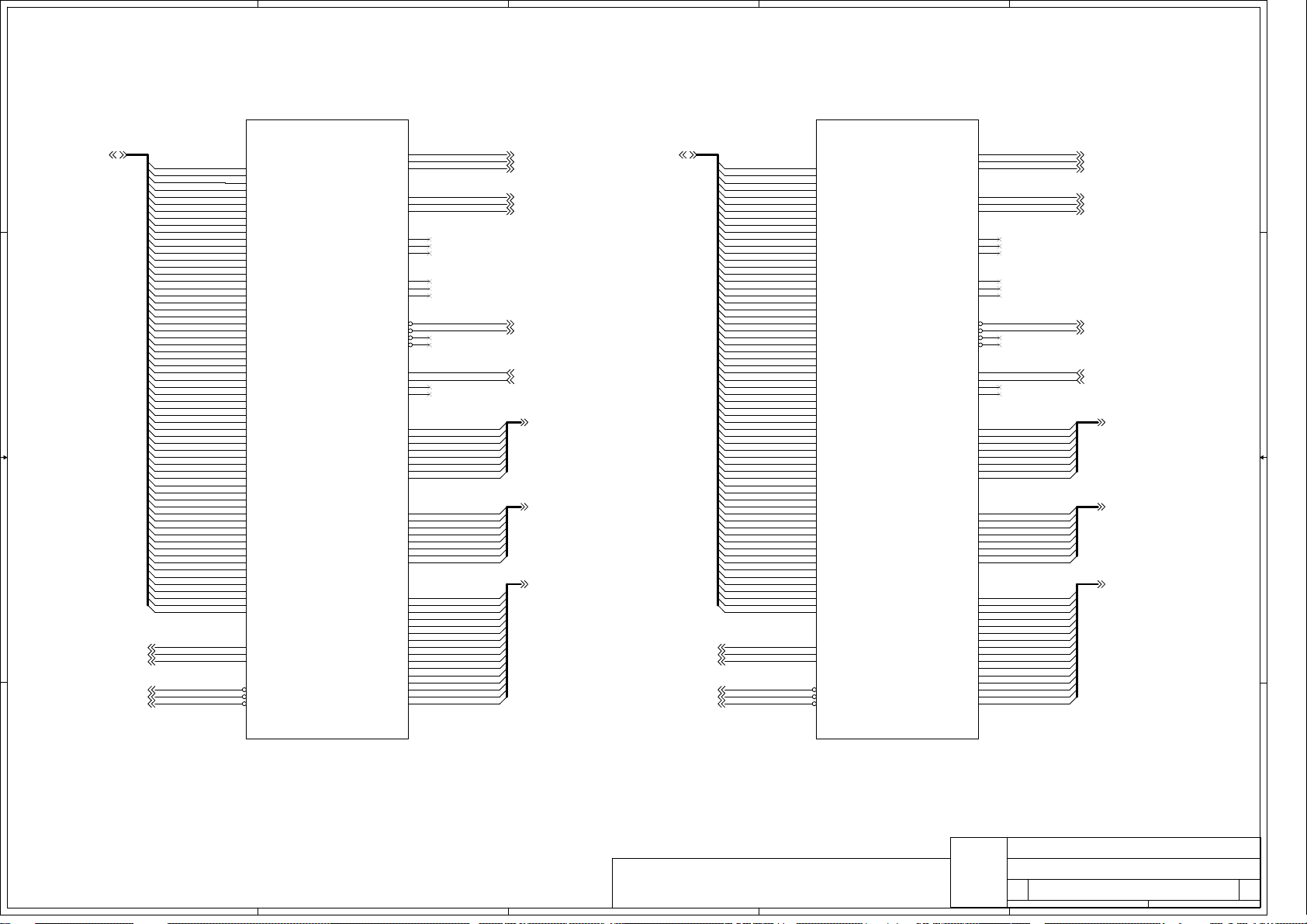

DMI_CRX_PTX_N0<16>

DMI_CRX_PTX_N1<16>

DMI_CRX_PTX_N2<16>

DMI_CRX_PTX_N3<16>

DMI_CRX_PTX_P0<16>

DMI_CRX_PTX_P1<16>

DMI_CRX_PTX_P2<16>

DMI_CRX_PTX_P3<16>

DMI_CTX_PRX_N0<16>

DMI_CTX_PRX_N1<16>

DMI_CTX_PRX_N2<16>

DMI_CTX_PRX_N3<16>

DMI_CTX_PRX_P0<16>

DMI_CTX_PRX_P1<16>

DMI_CTX_PRX_P2<16>

DMI_CTX_PRX_P3<16>

FDI_CTX_PRX_N0<16>

FDI_CTX_PRX_N1<16>

FDI_CTX_PRX_N2<16>

FDI_CTX_PRX_N3<16>

C C

B B

FDI_CTX_PRX_N4<16>

FDI_CTX_PRX_N5<16>

FDI_CTX_PRX_N6<16>

FDI_CTX_PRX_N7<16>

FDI_CTX_PRX_P0<16>

FDI_CTX_PRX_P1<16>

FDI_CTX_PRX_P2<16>

FDI_CTX_PRX_P3<16>

FDI_CTX_PRX_P4<16>

FDI_CTX_PRX_P5<16>

FDI_CTX_PRX_P6<16>

FDI_CTX_PRX_P7<16>

FDI_FSYNC0<16>

FDI_FSYNC1<16>

FDI_INT<16>

FDI_LSYNC0<16>

FDI_LSYNC1<16>

(1)EDP_COMPIOuse4miltracetoRC1

(2)EDP_ICOMPOuse12miltoRC1

DMI_CRX_PTX_N0

DMI_CRX_PTX_N1

DMI_CRX_PTX_N2

DMI_CRX_PTX_N3

DMI_CRX_PTX_P0

DMI_CRX_PTX_P1

DMI_CRX_PTX_P2

DMI_CRX_PTX_P3

DMI_CTX_PRX_N0

DMI_CTX_PRX_N1

DMI_CTX_PRX_N2

DMI_CTX_PRX_N3

DMI_CTX_PRX_P0

DMI_CTX_PRX_P1

DMI_CTX_PRX_P2

DMI_CTX_PRX_P3

FDI_CTX_PRX_N0

FDI_CTX_PRX_N1

FDI_CTX_PRX_N2

FDI_CTX_PRX_N3

FDI_CTX_PRX_N4

FDI_CTX_PRX_N5

FDI_CTX_PRX_N6

FDI_CTX_PRX_N7

FDI_CTX_PRX_P0

FDI_CTX_PRX_P1

FDI_CTX_PRX_P2

FDI_CTX_PRX_P3

FDI_CTX_PRX_P4

FDI_CTX_PRX_P5

FDI_CTX_PRX_P6

FDI_CTX_PRX_P7

FDI_FSYNC0

FDI_FSYNC1

FDI_INT

FDI_LSYNC0

FDI_LSYNC1

EDP_COMP

4

JCPU1A

JCPU1A

B27

DMI_RX#[0]

B25

DMI_RX#[1]

A25

DMI_RX#[2]

B24

DMI_RX#[3]

B28

DMI_RX[0]

B26

DMI_RX[1]

A24

DMI_RX[2]

B23

DMI_RX[3]

G21

DMI_TX#[0]

E22

DMI_TX#[1]

F21

DMI_TX#[2]

D21

DMI_TX#[3]

G22

DMI_TX[0]

D22

DMI_TX[1]

F20

DMI_TX[2]

C21

DMI_TX[3]

A21

FDI0_TX#[0]

H19

FDI0_TX#[1]

E19

FDI0_TX#[2]

F18

FDI0_TX#[3]

B21

FDI1_TX#[0]

C20

FDI1_TX#[1]

D18

FDI1_TX#[2]

E17

FDI1_TX#[3]

A22

FDI0_TX[0]

G19

FDI0_TX[1]

E20

FDI0_TX[2]

G18

FDI0_TX[3]

B20

FDI1_TX[0]

C19

FDI1_TX[1]

D19

FDI1_TX[2]

F17

FDI1_TX[3]

J18

FDI0_FSYNC

J17

FDI1_FSYNC

H20

FDI_INT

J19

FDI0_LSYNC

H17

FDI1_LSYNC

A18

eDP_COMPIO

A17

eDP_ICOMPO

B16

eDP_HPD#

C15

eDP_AUX

D15

eDP_AUX#

C17

eDP_TX[0]

F16

eDP_TX[1]

C16

eDP_TX[2]

G15

eDP_TX[3]

C18

eDP_TX#[0]

E16

eDP_TX#[1]

D16

eDP_TX#[2]

F15

eDP_TX#[3]

TYCO_2134146-3_IVYBRIDGE~D

TYCO_2134146-3_IVYBRIDGE~D

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

DMI

DMI

Intel(R) FDI

Intel(R) FDI

eDP

eDP

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PCI EXPRESS* - GRAPHICS

PCI EXPRESS* - GRAPHICS

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

LinkCIS

3

PEG_COMP

J22

J21

H22

(1)PEG_RCOMPO(H22)use4milconnecttoPEG_ICOMPI,then

use4milconnecttoRC2.

K33

M35

(2)PEG_ICOMPOuse12milconnecttoRC2

L34

J35

J32

H34

H31

G33

G30

F35

E34

E32

D33

D31

B33

C32

J33

L35

K34

H35

H32

G34

G31

F33

F30

E35

E33

F32

D34

E31

C33

B32

M29

M32

M31

L32

L29

K31

K28

J30

J28

H29

G27

E29

F27

D28

F26

E25

M28

M33

M30

L31

L28

K30

K27

J29

J27

H28

G28

E28

F28

D27

E26

D25

2

JCPU1I

JCPU1I

T35

VSS161

T34

VSS162

T33

VSS163

T32

VSS164

T31

VSS165

T30

VSS166

T29

VSS167

T28

VSS168

T27

VSS169

T26

VSS170

P9

VSS171

P8

VSS172

P6

VSS173

P5

VSS174

P3

VSS175

P2

VSS176

N35

VSS177

N34

VSS178

N33

VSS179

N32

VSS180

N31

VSS181

N30

VSS182

N29

VSS183

N28

VSS184

N27

VSS185

N26

VSS186

M34

VSS187

L33

VSS188

L30

VSS189

L27

VSS190

L9

VSS191

L8

VSS192

L6

VSS193

L5

VSS194

L4

VSS195

L3

VSS196

L2

VSS197

L1

VSS198

K35

VSS199

K32

VSS200

K29

VSS201

K26

VSS202

J34

VSS203

J31

VSS204

H33

VSS205

H30

VSS206

H27

VSS207

H24

VSS208

H21

VSS209

H18

VSS210

H15

VSS211

H13

VSS212

H10

VSS213

H9

VSS214

H8

VSS215

H7

VSS216

H6

VSS217

H5

VSS218

H4

VSS219

H3

VSS220

H2

VSS221

H1

VSS222

G35

VSS223

G32

VSS224

G29

VSS225

G26

VSS226

G23

VSS227

G20

VSS228

G17

VSS229

G11

VSS230

F34

VSS231

F31

VSS232

F29

VSS233

VSS

VSS

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

F22

F19

E30

E27

E24

E21

E18

E15

E13

E10

E9

E8

E7

E6

E5

E4

E3

E2

E1

D35

D32

D29

D26

D20

D17

C34

C31

C28

C27

C25

C23

C10

C1

B22

B19

B17

B15

B13

B11

B9

B8

B7

B5

B3

B2

A35

A32

A29

A26

A23

A20

A3

1

+1.05V_RUN_VTT +1.05V_RUN_VTT

1 2

RC1 24.9_0402_1%~DRC1 24.9_0402_1%~D

DPCompensation

eDP_COMPIOandICOMPOsignalsshouldbeshortednear

A A

ballsandroutedwithtypicalimpedance<25mohms

EDP_COMP

PEGCompensation

PEG_ICOMPIandRCOMPOsignalsshouldbeshortedandrouted

with‐maxlength=500mils‐typicalimpedance=43mohms

PEG_ICOMPOsignalsshouldberoutedwith‐maxlength=500mils

‐typicalimpedance=14.5mohms

1 2

RC2 24.9_0402_1%~DRC2 24.9_0402_1%~D

PEG_COMP

TYCO_2134146-3_IVYBRIDGE~D

TYCO_2134146-3_IVYBRIDGE~D

LinkCIS

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC MB A7903

SCHEMATIC MB A7903

SCHEMATIC MB A7903

4019FT

4019FT

4019FT

661Monday, April 02, 2012

661Monday, April 02, 2012

661Monday, April 02, 2012

1

B

B

B

of

of

of

Page 7

5

4

3

2

1

FollowDGRev0.71SM_DRAMPWROKtopology

+3.3V_ALW_PCH

D D

+1.05V_RUN_VTT

C C

B B

RUNPWROK<39,40>

PM_DRAM_PWRGD<16>

+3.3V_ALW_PCH

RC126 56_0402_5%~D@RC126 56_0402_5%~D@

RC128 49.9_0402_1%~D@RC128 49.9_0402_1%~D@

RC44 62_0402_5%~DRC44 62_0402_5%~D

1 2

RC18 200_0402_1%~DRC18 200_0402_1%~D

1 2

1 2

1 2

H_PROCHOT#<40,51,52>

H_THERMTRIP#<22>

H_CPUPWRGD<18>

H_THERMTRIP#

H_CATERR#

H_PROCHOT#

CPU_DETECT#<39>

PECI_EC<40>

VR1TOPOLOGY

1 2

RC57 56_0402_5%~DRC57 56_0402_5%~D

1 2

RC129 0_0402_5%~DRC129 0_0402_5%~D

placeRC129nearCPU

H_PM_SYNC<16>

1 2

RC25 1K_0402_5%~DRC25 1K_0402_5%~D

0.1U_0402_25V6K~D

0.1U_0402_25V6K~D

5

1

P

B

O

2

A

G

74AHC1G09GW_TSSOP5~D

74AHC1G09GW_TSSOP5~D

3

RUN_ON_CPU1.5VS3#<11,42>

Close to JCBU1

VCCPWRGOOD_0_R

PM_DRAM_PWRGD_CPU

PCH_PLTRST#_R

CC156

CC156

1 2

4

UC2

UC2

H_CATERR#

H_PROCHOT#_R

H_THERMTRIP#_R

+1.5V_CPU_VDDQ

200_0402_1%~D

200_0402_1%~D

12

RC12

RC12

RUNPWROK_AND PM_DRAM_PWRGD_CPU

2

G

G

JCPU1B

JCPU1B

C26

PROC_SELECT#

AN34

SKTOCC#

AL33

CATERR#

AN33

PECI

AL32

PROCHOT#

AN32

THERMTRIP#

AM34

PM_SYNC

AP33

UNCOREPWRGOOD

V8

SM_DRAMPWROK

AR33

RESET#

1 2

RC28 130_0402_1%~DRC28 130_0402_1%~D

39_0402_5%~D

39_0402_5%~D

@RC64

@

RC64

1 2

SSM3K7002FU_SC70-3~D

SSM3K7002FU_SC70-3~D

@

@

13

D

D

QC1

QC1

S

S

MISCTHERMALPWR MANAGEMENT

MISCTHERMALPWR MANAGEMENT

TYCO_2134146-3_IVYBRIDGE~D

TYCO_2134146-3_IVYBRIDGE~D

LinkCIS

CLOCKS

CLOCKS

DDR3

MISC

DDR3

MISC

JTAG & BPM

JTAG & BPM

BCLK

BCLK#

DPLL_REF_CLK

DPLL_REF_CLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PRDY#

PREQ#

TRST#

DBR#

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

+3.3V_ALW_PCH

SYS_PWROK_XDP

1 2

RC124 1K_0402_1%~D@ RC124 1K_0402_1%~D@

SIO_PWRBTN#_R<14,16>

DDR_XDP_WAN_SMBDAT<12,13,14,15,27,34>

DDR_XDP_WAN_SMBCLK<12,13,14,15,27,34>

RC13 0_0402_5%~D@ RC13 0_0402_5%~D@

CPU_DMI

A28

CPU_DMI#

A27

CPU_DPLL

A16

CPU_DPLL#

A15

R8

SM_RCOMP0

AK1

SM_RCOMP1

A5

SM_RCOMP2

A4

XDP_PRDY#

AP29

XDP_PREQ#

AP27

XDP_TCLK

AR26

TCK

XDP_TMS

AR27

TMS

TDO

XDP_TRST#

AP30

XDP_TDI_R

AR28

TDI

XDP_TDO_R

AP26

XDP_DBRESET#_R

AL35

XDP_OBS0_R

AT28

XDP_OBS1_R

AR29

XDP_OBS2_R

AR30

XDP_OBS3_R

AT30

XDP_OBS4_R

AP32

XDP_OBS5_R

AR31

XDP_OBS6_R

AT31

XDP_OBS7_R

AR32

1 2

RC15 0_0402_5%~D@ RC15 0_0402_5%~D@

1 2

RC16 1K_0402_1%~DRC16 1K_0402_1%~D

1 2

RC17 1K_0402_1%~DRC17 1K_0402_1%~D

1 2

DDR3_DRAMRST#_CPU

RC26 0_0402_5%~DRC26 0_0402_5%~D

RC30 0_0402_5%~DRC30 0_0402_5%~D

RC31 0_0402_5%~DRC31 0_0402_5%~D

RC33 0_0402_5%~DRC33 0_0402_5%~D

RC34 0_0402_5%~DRC34 0_0402_5%~D

RC36 0_0402_5%~DRC36 0_0402_5%~D

RC37 0_0402_5%~DRC37 0_0402_5%~D

RC38 0_0402_5%~DRC38 0_0402_5%~D

RC39 0_0402_5%~DRC39 0_0402_5%~D

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

12

DDR_HVREF_RST_PCH<15>

DDR_HVREF_RST_GATE<40>

ForESDconcern,pleaseputnearCPU

+1.05V_RUN_VTT

0.1U_0402_25V6K~D

0.1U_0402_25V6K~D

0.1U_0402_25V6K~D

0.1U_0402_25V6K~D

1

1

CC65

CC65

CC66

CC66

2

2

PlacenearJXDP1

TheresistorforHOOK2shouldbeplaced

suchthatthestubisverysmallonCFG0net

SYS_PWROK<16,39>

4.99K_0402_1%~D

4.99K_0402_1%~D

12

RC50

RC50

H_CPUPWRGD

CLK_CPU_DMI <15>

CLK_CPU_DMI# <15>H_SNB_IVB#<18>

XDP_DBRESET# <14,16>

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

XDP_OBS4

XDP_OBS5

XDP_OBS6

XDP_OBS7

1 2

RC5 1K_0402_1%~DRC5 1K_0402_1%~D

1 2

RC6 0_0402_5%~DRC6 0_0402_5%~D

CFG0

1 2

RC7 1K_0402_1%~DRC7 1K_0402_1%~D

1 2

RC9 0_0402_5%~D@RC9 0_0402_5%~D@

1 2

RC125 0_0402_5%~DRC125 0_0402_5%~D

1 2

RC127 0_0402_5%~DRC127 0_0402_5%~D

+1.05V_RUN_VTT

1 2

RC48 0_0402_5%~D@RC48 0_0402_5%~D@

D

S

D

S

13

G

G

BSS138W-7-F_SOT323-3~D

BSS138W-7-F_SOT323-3~D

2

0.047U_0402_16V4Z~D

0.047U_0402_16V4Z~D

CC177

CC177

1

2

1 2

RC46 0_0402_5%~D@ RC46 0_0402_5%~D@

1 2

RC47 0_0402_5%~D@ RC47 0_0402_5%~D@

QC2

QC2

DDR_HVREF_RST

XDP_TDI_R

XDP_TDO_R XDP_TDO

XDP_PREQ#

XDP_PRDY#

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

CFG10<9>

CFG11<9>

CFG10

CFG11

XDP_OBS4

XDP_OBS5

XDP_OBS6

XDP_OBS7

H_CPUPWRGD_XDP

CFD_PWRBTN#_XDP

SYS_PWROK_XDP

DDR_XDP_SMBDAT_R1

DDR_XDP_SMBCLK_R1

XDP_TCLK

DDR3_DRAMRST# <12>

1 2

RC23 0_0402_5%~DRC23 0_0402_5%~D

1 2

RC24 0_0402_5%~DRC24 0_0402_5%~D

+1.05V_RUN_VTT +1.05V_RUN_VTT

JXDP1

JXDP1

1

GND0

3

OBSFN_A0

5

OBSFN_A1

7

GND2

9

OBSDATA_A0

11

OBSDATA_A1

13

GND4

15

OBSDATA_A2

17

OBSDATA_A3

19

GND6

21

OBSFN_B0

23

OBSFN_B1

25

GND8

27

OBSDATA_B0

29

OBSDATA_B1

31

GND10

33

OBSDATA_B2

35

OBSDATA_B3

37

GND12

39

PWRGOOD/HOOK0

41

HOOK1

43

VCC_OBS_AB

45

HOOK2

47

HOOK3

49

GND14

51

SDA

53

SCL

55

TCK1

57

TCK0

59

GND16

SAMTE_BSH-030-01-L-D-A CONN@

SAMTE_BSH-030-01-L-D-A CONN@

CLK_XDP_ITP<9>

CLK_XDP_ITP#<9>

DDR_HVREF_RST <12>

XDP_TDI

ITPCLK#/HOOK5

RESET#/HOOK6

XDP_RST#_R

RC8 1K_0402_1%~DRC8 1K_0402_1%~D

CLK_XDP

RH107 0_0402_5%~DRH107 0_0402_5%~D

CLK_XDP#

RH106 0_0402_5%~DRH106 0_0402_5%~D

ITPCLK/HOOK4

RH109 0_0402_5%~D@ RH109 0_0402_5%~D@

RH108 0_0402_5%~D@ RH108 0_0402_5%~D@

GND1

OBSFN_C0

OBSFN_C1

GND3

OBSDATA_C0

OBSDATA_C1

GND5

OBSDATA_C2

OBSDATA_C3

GND7

OBSFN_D0

OBSFN_D1

GND9

OBSDATA_D0

OBSDATA_D1

GND11

OBSDATA_D2

OBSDATA_D3

GND13

VCC_OBS_CD

DBR#/HOOK7

GND15

TD0

TRST#

TDI

TMS

GND17

1 2

1 2

1 2

1 2

XDP_DBRESET#

XDP_TMS

XDP_TDI

XDP_PREQ#

XDP_TDO

XDP_TCLK

XDP_TRST#

2

CFG16

4

CFG17

6

8

CFG0

10

CFG1

12

14

CFG2

16

CFG3

18

20

CFG8

22

CFG9

24

26

CFG4

28

CFG5

30

32

CFG6

34

CFG7

36

38

CLK_XDP

40

CLK_XDP#

42

44

XDP_RST#_RXDP_HOOK2

46

XDP_DBRESET#

48

50

XDP_TDO

52

XDP_TRST#

54

XDP_TDI

56

XDP_TMS

58

60

12

PU/PDforJTAGsignals

RC19 1K_0402_1%~DRC19 1K_0402_1%~D

RC27 51_0402_1%~DRC27 51_0402_1%~D

RC29 51_0402_1%~DRC29 51_0402_1%~D

RC32 51_0402_1%~D@ RC32 51_0402_1%~D@

RC35 51_0402_1%~DRC35 51_0402_1%~D

RC40 51_0402_1%~DRC40 51_0402_1%~D

RC41 51_0402_1%~DRC41 51_0402_1%~D

12

12

12

12

12

12

12

CFG16 <9>

CFG17 <9>

CFG0 <9>

CFG1 <9>

CFG2 <9>

CFG3 <9>

CFG8 <9>

CFG9 <9>

CFG4 <9>

CFG5 <9>

CFG6 <9>

CFG7 <9>

PLTRST_XDP# <17>

CLK_CPU_ITP <15>

CLK_CPU_ITP# <15>

+3.3V_RUN

+1.05V_RUN_VTT

BufferedresettoCPU

+3.3V_RUN

UC1

UC1

1

5

NC

VCC

A A

PCH_PLTRST#<14,17>

2

A

GND3Y

SN74LVC1G07DCKR_SC70-5~D

SN74LVC1G07DCKR_SC70-5~D

Opendrainbuffer

5

4

0.1U_0402_25V6K~D

0.1U_0402_25V6K~D

1

CC140

CC140

2

PCH_PLTRST#_BUF

+1.05V_RUN_VTT

75_0402_1%~D

75_0402_1%~D

12

RC4

RC4

1 2

RC10 43_0402_5%~DRC10 43_0402_5%~D

PCH_PLTRST#_R

1

2

4

100P_0402_50V8J~D

100P_0402_50V8J~D

CC142

CC142

H_THERMTRIP#PECI_EC H_CPUPWRGD

100P_0402_50V8J~D

100P_0402_50V8J~D

1

CC143

CC143

2

1

2

ESDrequest

100P_0402_50V8J~D

100P_0402_50V8J~D

CC144

CC144

100P_0402_50V8J~D

100P_0402_50V8J~D

1

CC141

CC141

2

3

PlaceclosedJCPU1

XDP_DBRESET#

0.047U_0402_16V4Z~D

0.047U_0402_16V4Z~D

1

2

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

VCCPWRGOOD_0_R

@CE13

@

CE13

AvoidstubinthePWRGDpath

whileplacingresistorsRC25&RC130

10K_0402_5%~D

10K_0402_5%~D

12

RC130

RC130

SM_RCOMP0

1 2

RC42 140_0402_1%~DRC42 140_0402_1%~D

SM_RCOMP1

1 2

RC43 25.5_0402_1%~DRC43 25.5_0402_1%~D

SM_RCOMP2

1 2

RC45 200_0402_1%~DRC45 200_0402_1%~D

SM_RCOMP2‐‐>15mil

SM_RCOMP1/0‐‐>20mil

Maxlength500mils

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC MB A7903

SCHEMATIC MB A7903

SCHEMATIC MB A7903

4019FT

4019FT

4019FT

1

761Monday, April 02, 2012

761Monday, April 02, 2012

761Monday, April 02, 2012

B

B

B

of

of

of

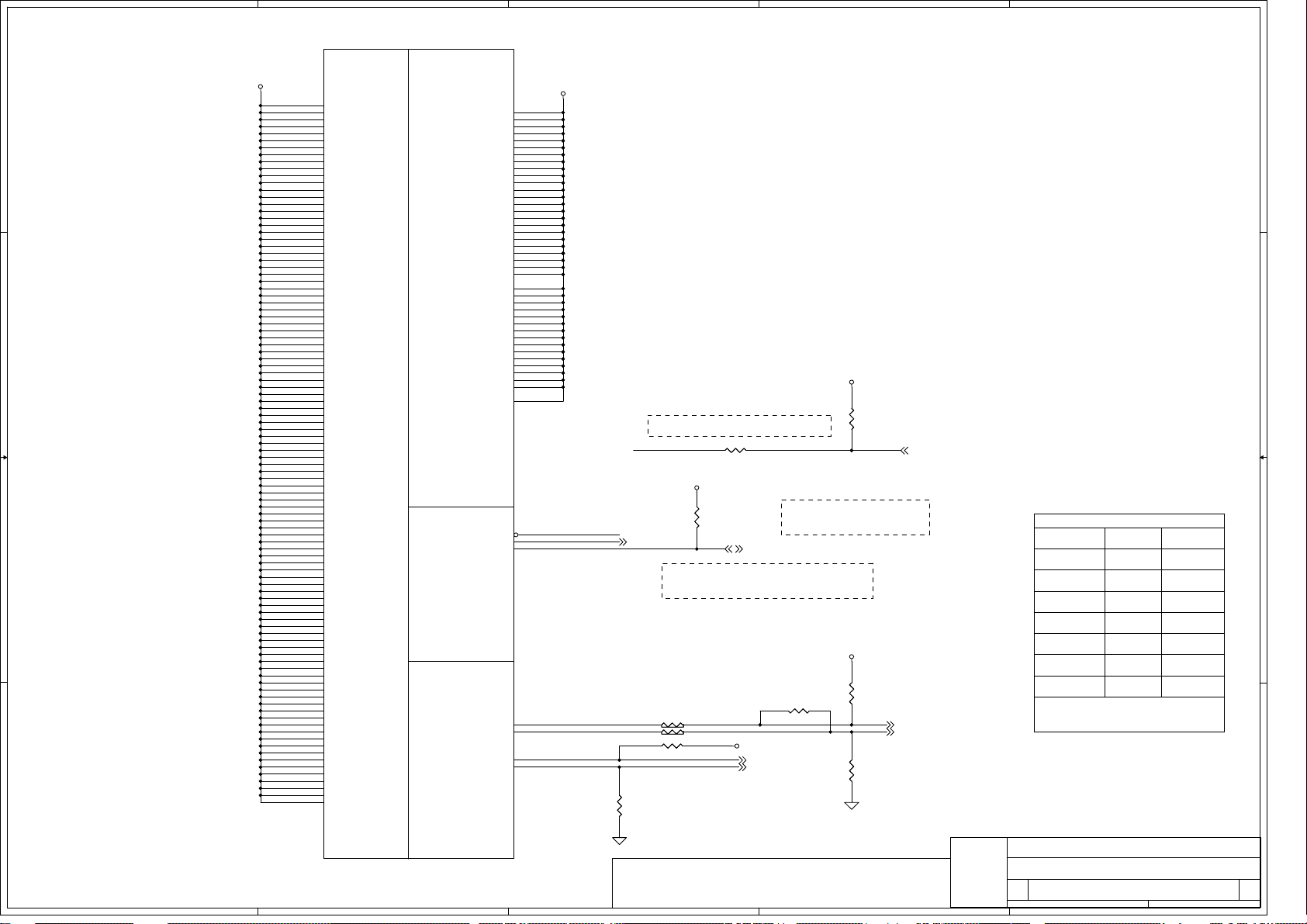

Page 8

5

JCPU1C

D D

JCPU1C

4

3

JCPU1D

JCPU1D

2

1

DDR_A_D[0..63]<12>

C C

B B

DDR_A_BS0<12>

DDR_A_BS1<12>

DDR_A_BS2<12>

DDR_A_CAS#<12>

DDR_A_RAS#<12>

DDR_A_WE#<12>

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_CAS#

DDR_A_RAS#

DDR_A_WE#

M10

AG6

AG5

AP11

AN11

AL12

AM12

AM11

AL11

AP12

AN12

AJ14

AH14

AL15

AK15

AL14

AK14

AJ15

AH15

AE10

AF10

C5

SA_DQ[0]

D5

SA_DQ[1]

D3

SA_DQ[2]

D2

SA_DQ[3]

D6

SA_DQ[4]

C6

SA_DQ[5]

C2

SA_DQ[6]

C3

SA_DQ[7]

F10

SA_DQ[8]

F8

SA_DQ[9]

G10

SA_DQ[10]

G9

SA_DQ[11]

F9

SA_DQ[12]

F7

SA_DQ[13]

G8

SA_DQ[14]

G7

SA_DQ[15]

K4

SA_DQ[16]

K5

SA_DQ[17]

K1

SA_DQ[18]

J1

SA_DQ[19]

J5

SA_DQ[20]

J4

SA_DQ[21]

J2

SA_DQ[22]

K2

SA_DQ[23]

M8

SA_DQ[24]

N10

SA_DQ[25]

N8

SA_DQ[26]

N7

SA_DQ[27]

SA_DQ[28]

M9

SA_DQ[29]

N9

SA_DQ[30]

M7

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

AK6

SA_DQ[34]

AK5

SA_DQ[35]

AH5

SA_DQ[36]

AH6

SA_DQ[37]

AJ5

SA_DQ[38]

AJ6

SA_DQ[39]

AJ8

SA_DQ[40]

AK8

SA_DQ[41]

AJ9

SA_DQ[42]

AK9

SA_DQ[43]

AH8

SA_DQ[44]

AH9

SA_DQ[45]

AL9

SA_DQ[46]

AL8

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

SA_BS[0]

SA_BS[1]

V6

SA_BS[2]

AE8

SA_CAS#

AD9

SA_RAS#

AF9

SA_WE#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

SA_CK[0]

SA_CLK#[0]

SA_CKE[0]

SA_CK[1]

SA_CLK#[1]

SA_CKE[1]

SA_CK[2]

SA_CLK#[2]

SA_CKE[2]

SA_CK[3]

SA_CLK#[3]

SA_CKE[3]

SA_CS#[0]

SA_CS#[1]

SA_CS#[2]

SA_CS#[3]

SA_ODT[0]

SA_ODT[1]

SA_ODT[2]

SA_ODT[3]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AB6

AA6

V9

AA5

AB5

V10

AB4

AA4

W9

AB3

AA3

W10

AK3

AL3

AG1

AH1

AH3

AG3

AG2

AH2

C4

G6

J3

M6

AL6

AM8

AR12

AM15

D4

F6

K3

N6

AL5

AM9

AR11

AM14

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

M_CLK_DDR#0

DDR_CKE0_DIMMA

M_CLK_DDR1

M_CLK_DDR#1

DDR_CKE1_DIMMA

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

M_ODT0

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

M_CLK_DDR0 <12>

M_CLK_DDR#0 <12>

DDR_CKE0_DIMMA <12>

M_CLK_DDR1 <12>

M_CLK_DDR#1 <12>

DDR_CKE1_DIMMA <12>

DDR_CS0_DIMMA# <12>

DDR_CS1_DIMMA# <12>

M_ODT0 <12>

M_ODT1 <12>

DDR_A_DQS#[0..7] <12>

DDR_A_DQS[0..7] <12>

DDR_A_MA[0..15] <12>

DDR_B_D[0..63]<13>

DDR_B_BS0<13>

DDR_B_BS1<13>

DDR_B_BS2<13>

DDR_B_CAS#<13>

DDR_B_RAS#<13>

DDR_B_WE#<13>

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

DDR_B_CAS#

DDR_B_RAS#

DDR_B_WE#

AM5

AM6

AR3

AP3

AN3

AN2

AN1

AP2

AP5

AN9

AT5

AT6

AP6

AN8

AR6

AR5

AR9

AJ11

AT8

AT9

AH11

AR8

AJ12

AH12

AT11

AN14

AR14

AT14

AT12

AN15

AR15

AT15

AA9

AA7

AA10

AB8

AB9

C9

SB_DQ[0]

A7

SB_DQ[1]

D10

SB_DQ[2]

C8

SB_DQ[3]

A9

SB_DQ[4]

A8

SB_DQ[5]

D9

SB_DQ[6]

D8

SB_DQ[7]

G4

SB_DQ[8]

F4

SB_DQ[9]

F1

SB_DQ[10]

G1

SB_DQ[11]

G5

SB_DQ[12]

F5

SB_DQ[13]

F2

SB_DQ[14]

G2

SB_DQ[15]

J7

SB_DQ[16]

J8

SB_DQ[17]

K10

SB_DQ[18]

K9

SB_DQ[19]

J9

SB_DQ[20]

J10

SB_DQ[21]

K8

SB_DQ[22]

K7

SB_DQ[23]

M5

SB_DQ[24]

N4

SB_DQ[25]

N2

SB_DQ[26]

N1

SB_DQ[27]

M4

SB_DQ[28]

N5

SB_DQ[29]

M2

SB_DQ[30]

M1

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

SB_BS[0]

SB_BS[1]

R6

SB_BS[2]

SB_CAS#

SB_RAS#

SB_WE#

SB_CK[0]

SB_CLK#[0]

SB_CKE[0]

SB_CK[1]

SB_CLK#[1]

SB_CKE[1]

SB_CK[2]

SB_CLK#[2]

SB_CKE[2]

SB_CK[3]

SB_CLK#[3]

SB_CKE[3]

SB_CS#[0]

SB_CS#[1]

SB_CS#[2]

SB_CS#[3]

SB_ODT[0]

SB_ODT[1]

SB_ODT[2]

SB_ODT[3]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

M_CLK_DDR0

AE2

AD2

R9

AE1

AD1

R10

AB2

AA2

T9

AA1

AB1

T10

AD3

AE3

AD6

AE6

AE4

AD4

AD5

AE5

D7

F3

K6

N3

AN5

AP9

AK12

AP15

C7

G3

J6

M3

AN6

AP8

AK11

AP14

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

M_CLK_DDR2

M_CLK_DDR#2

DDR_CKE2_DIMMB

M_CLK_DDR3

M_CLK_DDR#3

DDR_CKE3_DIMMB

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

M_ODT2

M_ODT3M_ODT1

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

M_CLK_DDR2 <13>

M_CLK_DDR#2 <13>

DDR_CKE2_DIMMB <13>

M_CLK_DDR3 <13>

M_CLK_DDR#3 <13>

DDR_CKE3_DIMMB <13>

DDR_CS2_DIMMB# <13>

DDR_CS3_DIMMB# <13>

M_ODT2 <13>

M_ODT3 <13>

DDR_B_DQS#[0..7] <13>

DDR_B_DQS[0..7] <13>

DDR_B_MA[0..15] <13>

TYCO_2134146-3_IVYBRIDGE~D

TYCO_2134146-3_IVYBRIDGE~D

TYCO_2134146-3_IVYBRIDGE~D

A A

LinkCIS LinkCIS

TYCO_2134146-3_IVYBRIDGE~D

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC MB A7903

SCHEMATIC MB A7903

SCHEMATIC MB A7903

4019FT

4019FT

4019FT

861Monday, April 02, 2012

861Monday, April 02, 2012

861Monday, April 02, 2012

1

B

B

B

of

of

of

Page 9

5

4

3

2

1

CFGStrapsforProcessor

CFG2

D D

PEGStaticLaneReversal‐CFG2isforthe16x

1:(Default)NormalOperation;Lane#

JCPU1E

JCPU1E

T39 PAD~D@T39 PAD~D@

T1 PAD~D@T1 PAD~D@

T2 PAD~D@T2 PAD~D@

T3 PAD~D@T3 PAD~D@

T4 PAD~D@T4 PAD~D@

T5 PAD~D@T5 PAD~D@

T6 PAD~D@T6 PAD~D@

T7 PAD~D@T7 PAD~D@

T8 PAD~D@T8 PAD~D@

T11 PAD~D@T11 PAD~D@

T13 PAD~D@T13 PAD~D@

T15 PAD~D@T15 PAD~D@

T16 PAD~D@T16 PAD~D@

T17 PAD~D@T17 PAD~D@

T18 PAD~D@T18 PAD~D@

T19 PAD~D@T19 PAD~D@

T20 PAD~D@T20 PAD~D@

T21 PAD~D@T21 PAD~D@

T23 PAD~D@T23 PAD~D@

T24 PAD~D@T24 PAD~D@

T25 PAD~D@T25 PAD~D@

T27 PAD~D@T27 PAD~D@

T32 PAD~D@T32 PAD~D@T43PAD~D @T43PAD~D @

T34 PAD~D@T34 PAD~D@

CLK_XDP_ITP <7>

CLK_XDP_ITP# <7>

T49 PAD~D@T49 PAD~D@

T50 PAD~D@T50 PAD~D@

T51 PAD~D@T51 PAD~D@

T53 PAD~D@T53 PAD~D@

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD37

RSVD38

RSVD39

RSVD40

RSVD51

RSVD52

BCLK_ITP

BCLK_ITP#

KEY

AH27

AH26

L7

AG7

AE7

AK2

W8

AT26

AM33

AJ27

T8

J16

H16

G16

AR35

AT34

AT33

AP35

AR34

B34

A33

A34

B35

C35

AJ32

AK32

AN35

AM35

AT2

AT1

AR1

B1

CFG0<7>

CFG1<7>

CFG2<7>

CFG3<7>

CFG4<7>

CFG5<7>

CFG6<7>

CFG7<7>

CFG8<7>

CFG9<7>

CFG10<7>

+VCC_GFXCORE

1 2

+VCC_CORE

RC122 49.9_0402_1%~D@RC122 49.9_0402_1%~D@

RC123 49.9_0402_1%~D@RC123 49.9_0402_1%~D@

RC120 49.9_0402_1%~D@RC120 49.9_0402_1%~D@

RC121 49.9_0402_1%~D@RC121 49.9_0402_1%~D@

1 2

1 2

1 2

C C

B B

VAXG_VAL_SENSE

100_0402_1%~D

100_0402_1%~D

12

@RC69

@

RC69

VSSAXG_VAL_SENSE

VCC_VAL_SNESE

100_0402_1%~D

100_0402_1%~D

12

@RC71

@

RC71

VSS_VAL_SNESE

CFG11<7>

CFG16<7>

CFG17<7>

T22PAD~D @T22PAD~D @

T28PAD~D @T28PAD~D @

T29PAD~D @T29PAD~D @

T30PAD~D @T30PAD~D @

T31PAD~D @T31PAD~D @

T33PAD~D @T33PAD~D @

T35PAD~D @T35PAD~D @

T36PAD~D @T36PAD~D @ T26 PAD~D@T26 PAD~D@

T37PAD~D @T37PAD~D @

T38PAD~D @T38PAD~D @

T40PAD~D @T40PAD~D @

T41PAD~D @T41PAD~D @

T42PAD~D @T42PAD~D @

T44PAD~D @T44PAD~D @

T45PAD~D @T45PAD~D @

T46PAD~D @T46PAD~D @

T47PAD~D @T47PAD~D @

T48PAD~D @T48PAD~D @

T52PAD~D @T52PAD~D @

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

VAXG_VAL_SENSE

VSSAXG_VAL_SENSE

VCC_VAL_SNESE

VSS_VAL_SNESE

AK28

CFG[0]

AK29

CFG[1]

AL26

CFG[2]

AL27

CFG[3]

AK26

CFG[4]

AL29

CFG[5]

AL30

CFG[6]

AM31

CFG[7]

AM32

CFG[8]

AM30

CFG[9]

AM28

CFG[10]

AM26

CFG[11]

AN28

CFG[12]

AN31

CFG[13]

AN26

CFG[14]

AM27

CFG[15]

AK31

CFG[16]

AN29

CFG[17]

AJ31

VAXG_VAL_SENSE

AH31

VSSAXG_VAL_SENSE

AJ33

VCC_VAL_SENSE

AH33

VSS_VAL_SENSE

AJ26

RSVD5

F25

RSVD8

F24

RSVD9

F23

RSVD10

D24

RSVD11

G25

RSVD12

G24

RSVD13

E23

RSVD14

D23

RSVD15

C30

RSVD16

A31

RSVD17

B30

RSVD18

B29

RSVD19

D30

RSVD20

B31

RSVD21

A30

RSVD22

C29

RSVD23

J20

RSVD24

B18

RSVD25

J15

RSVD27

CFG

CFG

VCC_DIE_SENSE

VSS_DIE_SENSE

RSVD_NCTF1

RSVD_NCTF2

RSVD_NCTF3

RSVD_NCTF4

RSVD_NCTF5

RSVD_NCTF6

RSVD_NCTF7

RSVD_NCTF8

RESERVED

RESERVED

RSVD_NCTF9

RSVD_NCTF10

RSVD_NCTF11

RSVD_NCTF12

RSVD_NCTF13

CFG2

CFG4

CFG[6:5]

definitionmatchessocketpinmapdefinition

0:LaneReversed

1:Disabled;NoPhysicalDisplayPort

attachedtoEmbeddedDisplayPort

0:Enabled;AnexternalDisplayPortdeviceis

connectedtotheEmbeddedDisplayPort

11:(Default)x16‐Device1functions1and2disabled

10:x8,x8‐Device1function1enabled;function2

disabled

01:Reserved‐(Device1function1disabled;function

2enabled)

00:x8,x4,x4‐Device1functions1and2enabled

1K_0402_1%~D

1K_0402_1%~D

@RC51

@

12

RC51

CFG4

1K_0402_1%~D

1K_0402_1%~D

12

@RC52

@

RC52

DisplayPortPresenceStrap

CFG6

CFG5

1K_0402_1%~D

1K_0402_1%~D

1K_0402_1%~D

1K_0402_1%~D

12

@RC54

@

12

RC54

@RC53

@

RC53

PCIEPortBifurcationStraps

CFG7

1K_0402_1%~D

1K_0402_1%~D

12

@RC56

@

RC56

TYCO_2134146-3_IVYBRIDGE~D

TYCO_2134146-3_IVYBRIDGE~D

LinkCIS

PEGDEFERTRAINING

1:(Default)PEGTrainimmediately

CFG7

followingxxRESETBdeassertion

0:PEGWaitforBIOSfortraining

A A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC MB A7903

SCHEMATIC MB A7903

SCHEMATIC MB A7903

4019FT

4019FT

4019FT

961Monday, April 02, 2012

961Monday, April 02, 2012

961Monday, April 02, 2012

1

B

B

B

of

of

of

Page 10

5

JCPU1F

JCPU1F

4

POWER

POWER

3

2

1

+VCC_CORE

53A

AG35

VCC1

AG34

VCC2

AG33

D D

C C

B B

A A

5

VCC3

AG32

VCC4

AG31

VCC5

AG30

VCC6

AG29

VCC7

AG28

VCC8

AG27

VCC9

AG26

VCC10

AF35

VCC11

AF34

VCC12

AF33

VCC13

AF32

VCC14

AF31

VCC15

AF30

VCC16

AF29

VCC17

AF28

VCC18

AF27

VCC19

AF26

VCC20

AD35

VCC21

AD34

VCC22

AD33

VCC23

AD32

VCC24

AD31

VCC25

AD30

VCC26

AD29

VCC27

AD28

VCC28

AD27

VCC29

AD26

VCC30

AC35

VCC31

AC34

VCC32

AC33

VCC33

AC32

VCC34

AC31

VCC35

AC30

VCC36

AC29

VCC37

AC28

VCC38

AC27

VCC39

AC26

VCC40

AA35

VCC41

AA34

VCC42

AA33

VCC43

AA32

VCC44

AA31

VCC45

AA30

VCC46

AA29

VCC47

AA28

VCC48

AA27

VCC49

AA26

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

TYCO_2134146-3_IVYBRIDGE~D

TYCO_2134146-3_IVYBRIDGE~D

CORE SUPPLY

CORE SUPPLY

SENSE LINES SVID

SENSE LINES SVID

LinkCIS

4

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCCIO9

VCCIO10

VCCIO11

VCCIO12

VCCIO13

VCCIO14

VCCIO15

VCCIO16

VCCIO17

VCCIO18

VCCIO19

VCCIO20

VCCIO21

VCCIO22

VCCIO23

VCCIO24

VCCIO25

VCCIO26

VCCIO27

VCCIO28

VCCIO29

VCCIO30

VCCIO31

VCCIO32

PEG AND DDR

PEG AND DDR

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

VCCIO40

VIDALERT#

VIDSCLK

VIDSOUT

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

8.5A

AH13

AH10

AG10

AC10

Y10

U10

P10

L10

J14

J13

J12

J11

H14

H12

H11

G14

G13

G12

F14

F13

F12

F11

E14

E12

E11

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

J23

AJ29

AJ30

AJ28

AJ35

AJ34

B10

A10

+1.05V_RUN_VTT

H_CPU_SVIDALRT#

VIDSCLK

VIDSOUT

VCCSENSE_R

VSSSENSE_R

VTT_SENSE

VSSIO_SENSE_R

+1.05V_RUN_VTT

75_0402_1%~D

75_0402_1%~D

12

RC60

RC60

Note:PlacethePUresistorsclosetoCPU

RC61closetoCPU300‐1500mils

H_CPU_SVIDALRT#

VIDSCLK <51>

PlaceRC67,RC68nearCPU

RC67 0_0402_5%~D@ RC67 0_0402_5%~D@

1 2

RC68 0_0402_5%~D@ RC68 0_0402_5%~D@

1 2

RC98 10_0402_1%~DRC98 10_0402_1%~D

10_0402_1%~D

10_0402_1%~D

12

RC133

RC133

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

1 2

RC61 43_0402_5%~DRC61 43_0402_5%~D

+1.05V_RUN_VTT

130_0402_1%~D

130_0402_1%~D

12

RC63

RC63

H_CPU_SVIDALRT#mustberoutedbetweenthe

VIDSOUTandVIDSCLKlinestoreducecrosstalk.

18milsspacingtoothers.

12

CADNote:PlacethePU

resistorsclosetoCPU

RC63closetoCPU300‐1500mils

VIDSOUT <51>

RC75

@RC75

@

1 2

100_0402_1%~D

100_0402_1%~D

+1.05V_RUN_VTT

VTT_SENSE <49>

VSSIO_SENSE_R <49>

+VCC_CORE

12

12

VIDALERT_N <51>

100_0402_1%~D

100_0402_1%~D

RC66

RC66

VCCSENSE <51>

VSSSENSE <51>

100_0402_1%~D

100_0402_1%~D

RC70

RC70

2

IccmaxcurrentchangedforPDDGRev0.7

CPUPowerRailTable

VoltageRail Voltage

VCC 530.65‐1.3

VCCIO 1.05 8.5

5AtoMemcontroller(+1.5V_CPU_VDDQ)

5‐6Ato2DIMMs/channel

2‐5Ato+1.5V_RUN&+0.75V_DDR_VTT

S0Iccmax

Current(A)

260.0‐1.1VAXG

31.8VCCPLL

51.5VDDQ

60.65‐0.9VCCSA

12‐161.5+1.5V_MEM

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC MB A7903

SCHEMATIC MB A7903

SCHEMATIC MB A7903

4019FT

4019FT

4019FT

10 61Monday, April 02, 2012

10 61Monday, April 02, 2012

10 61Monday, April 02, 2012

1

of

of

of

B

B

B

Page 11

5

4

3

2

1

+1.5V_CPU_VDDQSource

+PWR_SRC_S

330K_0402_5%~D

+3.3V_ALW2

100K_0402_5%~D

100K_0402_5%~D

12

RC74

RC74

D D

RUN_ON_CPU1.5VS3#

DMN66D0LDW-7_SOT363-6~D

DMN66D0LDW-7_SOT363-6~D

61

QC4A

SIO_SLP_S3#<16,27,35,39,42,47,48,49>

CPU1.5V_S3_GATE<40>

RC82 0_0402_5%~D@ RC82 0_0402_5%~D@

RC79 0_0402_5%~D@ RC79 0_0402_5%~D@

1 2

1 2

QC4A

2

330K_0402_5%~D

5

+1.5V_MEM +1.5V_CPU_VDDQ

12

RC72

RC72

RUN_ON_CPU1.5VS3

DMN66D0LDW-7_SOT363-6~D

DMN66D0LDW-7_SOT363-6~D

3

QC4B

QC4B

4

8

7

6

5

QC3

QC3

AO4304L_SO8

AO4304L_SO8

4

1M_0402_5%~D

1M_0402_5%~D

12

RC143

RC143

1

2

0.022U_0402_25V7K~D

0.022U_0402_25V7K~D

CC136

CC136

1

2

3

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

20K_0402_5%~D

20K_0402_5%~D

12

CC135

CC135

1

2

RC73

RC73

12

12

1K_0402_1%~D

1K_0402_1%~D

1K_0402_1%~D

1K_0402_1%~D

@RC80

@

RC80

@RC81

@

RC81

+V_DDR_SMREF

RUN_ON_CPU1.5VS3

1 2

RC135 0_0402_5%~D@RC135 0_0402_5%~D@

1 2

RC134 0_0402_5%~D@RC134 0_0402_5%~D@

NTR4503NT1G_SOT23-3~D

NTR4503NT1G_SOT23-3~D

+1.5V_MEM

@

@

@QC5

@

1

+V_DDR_REF

+1.5V_CPU_VDDQ

1K_0402_1%~D

1K_0402_1%~D

12

RC84

RC84

12

1K_0402_1%~D

1K_0402_1%~D

RC78

RC78

+V_SM_VREF_CNT

QC5

3

2

RUN_ON_CPU1.5VS3# <7,42>

+VCC_GFXCORE

100_0402_1%~D

100_0402_1%~D

12

RC99

100_0402_1%~D

100_0402_1%~D

12

+DIMM0_1_VREF_CPU

+DIMM0_1_CA_CPU

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

1

CC161

CC161

2

2

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

@CC168

@

CC168

1

1

2

2

VCCSA_SENSE <50>

VCCSA_VID_0 <50>

VCCSA_VID_1 <50>

RC99

1 2

100_0402_1%~D

100_0402_1%~D

RC100

RC100

+V_SM_VREFshould

have10miltracewidth

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

1

CC163

CC163

CC162

CC162

2

2

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

CC170

CC170

CC169

CC169

1

1

2

2

VCCP_PWRCTRL <49>

RC76

@RC76

@

+1.5V_CPU_VDDQ

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

1

CC164

CC164

CC165

CC165

2

2

+VCC_SA

330U_D2_2VM_R6M~D

330U_D2_2VM_R6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

CC171

CC171

1

CC172

CC172

+

+

2

VCC_AXG_SENSE <51>

VSS_AXG_SENSE <51>

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

330U_D2_2VM_R6M~D

330U_D2_2VM_R6M~D

1

+

+

CC166

CC166

CC167

CC167

2

CC178 0.1U_0402_10V7K~DCC178 0.1U_0402_10V7K~D

12

CC179 0.1U_0402_10V7K~DCC179 0.1U_0402_10V7K~D

12

CC149 0.1U_0402_10V7K~DCC149 0.1U_0402_10V7K~D

12

CC150 0.1U_0402_10V7K~DCC150 0.1U_0402_10V7K~D

12

+1.5V_CPU_VDDQ

+1.5V_MEM

1

CC153

CC153

@

@

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

2

ESDRequest

6A

1

CC151

CC151

@

@

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

2

1

CC152

CC152

@

@

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

2

+1.5V_MEM

POWER

+VCC_GFXCORE

C C

B B

+DIMM0_1_VREF_CPU

1 2

RC96 1K_0402_1%~D@RC96 1K_0402_1%~D@

RC97 1K_0402_1%~D@RC97 1K_0402_1%~D@

A A

1 2

+DIMM0_1_CA_CPU

+1.8V_RUN

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

CC173

CC173

2

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1

1

CC174

CC174

2

2

330U_D2_2.5VM_R6M~D

330U_D2_2.5VM_R6M~D

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1

CC176

CC176

CC175

CC175

+

+

2

33A

1.2A

AT24

AT23

AT21

AT20

AT18

AT17

AR24

AR23

AR21

AR20

AR18

AR17

AP24

AP23

AP21

AP20

AP18

AP17

AN24

AN23

AN21

AN20

AN18

AN17

AM24

AM23

AM21

AM20

AM18

AM17

AL24

AL23

AL21

AL20

AL18

AL17

AK24

AK23

AK21

AK20

AK18

AK17

AJ24

AJ23

AJ21

AJ20

AJ18

AJ17

AH24

AH23

AH21

AH20

AH18

AH17

JCPU1G

JCPU1G

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

VAXG37

VAXG38

VAXG39

VAXG40

VAXG41

VAXG42

VAXG43

VAXG44

VAXG45

VAXG46

VAXG47

VAXG48

VAXG49

VAXG50

VAXG51

VAXG52

VAXG53

VAXG54

B6

VCCPLL1

A6

VCCPLL2

A2

VCCPLL3

TYCO_2134146-3_IVYBRIDGE~D

TYCO_2134146-3_IVYBRIDGE~D

POWER

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

VREFMISC

VREFMISC

GRAPHICS

GRAPHICS

DDR3 -1.5V RAILS

DDR3 -1.5V RAILS

SA RAIL

SA RAIL

VCCSA_SENSE

1.8V RAIL

1.8V RAIL

LinkCIS

VAXG_SENSE

SM_VREF

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

VCCSA_VID[0]

VCCSA_VID[1]

VCCIO_SEL

AK35

AK34

AL1

+V_SM_VREF_CNT

+DIMM0_1_VREF_CPU

B4

+DIMM0_1_CA_CPU

D1

5A

AF7

AF4

AF1

AC7

AC4

AC1

Y7

Y4

Y1

U7

U4

U1

P7

P4

P1

6A

M27

M26

L26

J26

J25

J24

H26

H25

H23

C22

C24

1 2

A19

RC140 0_0402_5%~D@ RC140 0_0402_5%~D@

DepopRC140forES2CPU

JCPU1H

JCPU1H

AT35

VSS1

AT32

VSS2

AT29

VSS3

AT27

VSS4

AT25

VSS5

AT22

VSS6

AT19

VSS7

AT16

VSS8

AT13

VSS9

AT10

VSS10

AT7

VSS11

AT4

VSS12

AT3

VSS13

AR25

VSS14

AR22

VSS15

AR19

VSS16

AR16

VSS17

AR13

VSS18

AR10

VSS19

AR7

VSS20

AR4

VSS21

AR2

VSS22

AP34

VSS23

AP31

VSS24

AP28

VSS25

AP25

VSS26

AP22

VSS27

AP19

VSS28

AP16

VSS29

AP13

VSS30

AP10

VSS31

AP7

VSS32

AP4

VSS33

AP1

VSS34

AN30

VSS35

AN27

VSS36

AN25

VSS37

AN22

VSS38

AN19

VSS39

AN16

VSS40

AN13

VSS41

AN10

VSS42

AN7

VSS43

AN4

VSS44

AM29

VSS45

AM25

VSS46

AM22

VSS47

AM19

VSS48

AM16

VSS49

AM13

VSS50

AM10

VSS51

AM7

VSS52

AM4

VSS53

AM3

VSS54

AM2

VSS55

AM1

VSS56

AL34

VSS57

AL31

VSS58

AL28

VSS59

AL25

VSS60

AL22

VSS61

AL19

VSS62

AL16

VSS63

AL13

VSS64

AL10

VSS65

AL7

VSS66

AL4

VSS67

AL2

VSS68

AK33

VSS69

AK30

VSS70

AK27

VSS71

AK25

VSS72

AK22

VSS73

AK19

VSS74

AK16

VSS75

AK13

VSS76

AK10

VSS77

AK7

VSS78

AK4

VSS79

AJ25

VSS80

TYCO_2134146-3_IVYBRIDGE~D

TYCO_2134146-3_IVYBRIDGE~D

VSS

VSS

LinkCIS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AJ22

AJ19

AJ16

AJ13

AJ10

AJ7

AJ4

AJ3

AJ2

AJ1

AH35

AH34

AH32

AH30

AH29

AH28

AH25

AH22

AH19

AH16

AH7

AH4

AG9

AG8

AG4

AF6

AF5

AF3

AF2

AE35

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE9

AD7

AC9

AC8

AC6

AC5

AC3

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

Y9

Y8

Y6

Y5

Y3

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

U9

U8

U6

U5

U3

U2

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

5

4

3

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC MB A7903

SCHEMATIC MB A7903

SCHEMATIC MB A7903

4019FT

4019FT

4019FT

1

11 61Monday, April 02, 2012

11 61Monday, April 02, 2012

11 61Monday, April 02, 2012

B

B

B

of

of

of

Page 12

5

4

3

2

1

AllVREFtracesshould

DDR_A_DQS#[0..7]<8>

DDR_A_D[0..63]<8>

DDR_A_DQS[0..7]<8>

DDR_A_MA[0..15]<8>

D D

PopulateRD1,De‐PopulateRD7forIntelDDR3

VREFDQmultiplemethodsM1

PopulateRD7,De‐PopulateRD1forIntelDDR3

VREFDQmultiplemethodsM3

+V_DDR_REFA_M3

+V_DDR_REF

have10miltracewidth

1 2

RD7 0_0402_5%~D@ RD7 0_0402_5%~D@

1 2

RD1 0_0402_5%~D@ RD1 0_0402_5%~D@

2.2U_0603_6.3V6K~D

2.2U_0603_6.3V6K~D

1

1

CD1

CD1

2

2

LayoutNote:

PlacenearJDIMM1

+1.5V_MEM

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1

C C

+1.5V_MEM

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

2

2

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

CD7

CD7

CD9

CD9

CD8

CD8

1

1

2

2

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1

CD3

CD3

2

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

CD10

CD10

1

2

1U_0402_6.3V6K~D

1

1

CD4

CD4

CD5

CD5

CD6

CD6

2

2

10U_0603_6.3V6M~D

CD11

CD11

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

2

CD51

CD51

330U_SX_2VY~D

330U_SX_2VY~D

1

CD13

CD13

CD14

CD14

1

+

+

2

2

10U_0603_6.3V6M~D

10U_0603_6.3V6M~D

1

2

DDR_CKE0_DIMMA<8>

DDR_A_BS2<8>

M_CLK_DDR0<8>

M_CLK_DDR#0<8>

DDR_A_BS0<8>

DDR_A_WE#<8>

DDR_A_CAS#<8>

DDR_CS1_DIMMA#<8>

LayoutNote:

PlacenearJDIMM1.203,204

B B

+0.75V_DDR_VTT

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

1

1

CD17

CD17

2

2

A A

1

1

CD19

CD19

CD18

CD18

2

2

RD2 10K_0402_5%~DRD2 10K_0402_5%~D

RD3 10K_0402_5%~DRD3 10K_0402_5%~D

1U_0402_6.3V6K~D

1U_0402_6.3V6K~D

CD20

CD20

1 2

1 2

DIMM1_SA0

DIMM1_SA1

+3.3V_RUN

1

2

0.1U_0402_25V6K~D

0.1U_0402_25V6K~D