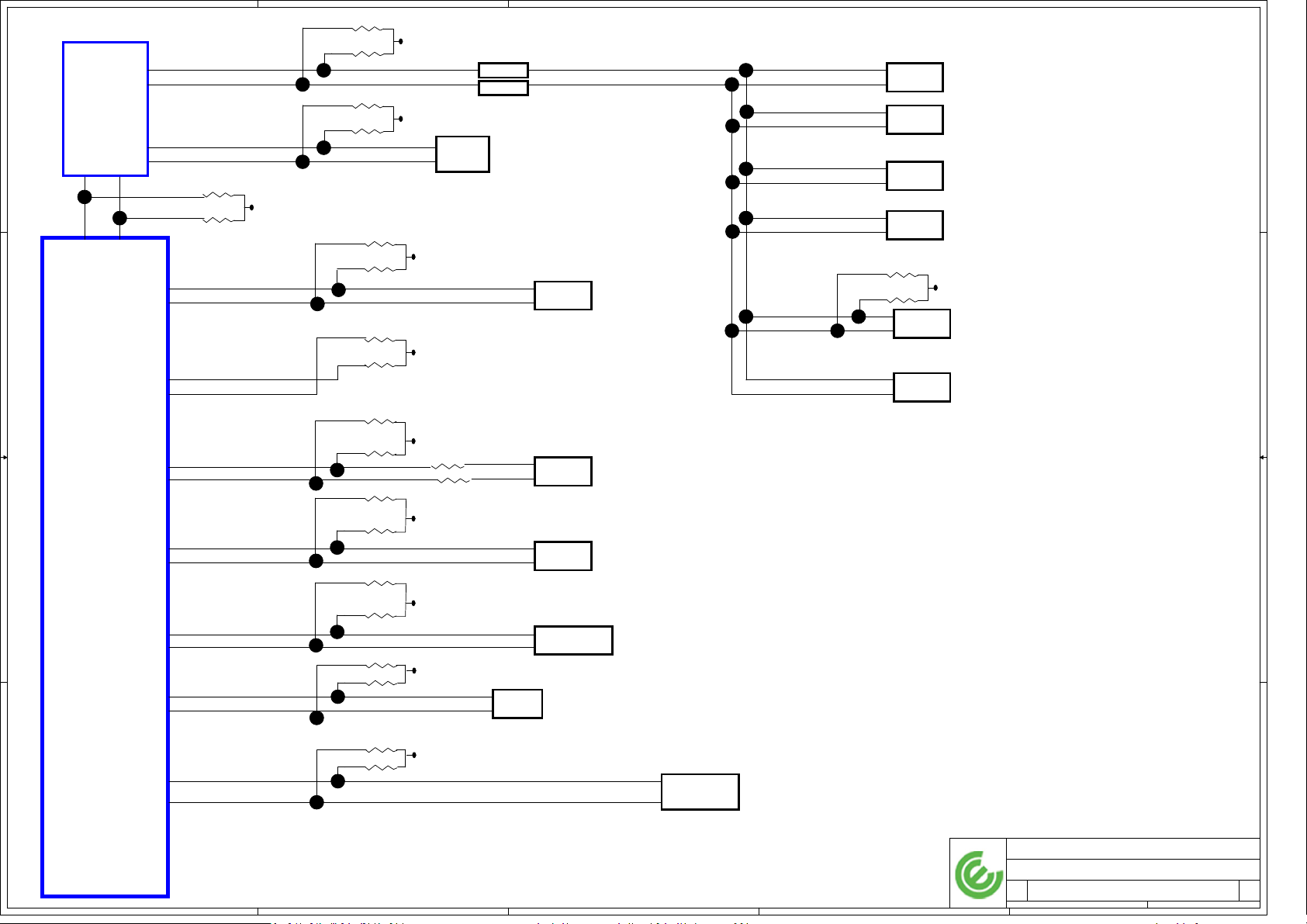

Page 1

A

B

C

D

E

COMPAL CONFIDENTIAL

QA

1 1

PCB NO :

BOM P/N :

GPIO MAP: E4_VC_GPIO_map_rev_1.1

L

A-7781P (DA60000OP10)

4319EK31L01

MODEL NAME :

L80

2 2

Dalmore 14 UMA

I

y Bridge + Panther POINT

@

v

2012-02-24

REV : 1.0 (A00)

@ : Nopop Component

3 3

CONN@ : Connector Component

MB Type

ATG Non-TPM

BOM P/N

L52

L01TPM

L02Non-TPM

1@

2@

5@ATG TPM L51

5@

1@

2@

4 4

M

M

PCB

B

B

PCB

P

P

art Number

art Number

D

D

A60000OP10

A60000OP10

Description

Description

PCB 0LD LA-7781P REV1 M/B UMA

PCB 0LD LA-7781P REV1 M/B UMA

A

P

ROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

T

RADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

B

E

TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

N

EITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

P

A

RTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

B

C

D

D

E

LL CONFIDENTIAL/PROPRIETARY

C

C

C

mpal Electronics, Inc.

o

o

o

mpal Electronics, Inc.

T

T

T

tle

i

i

i

tle

tle

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

mpal Electronics, Inc.

C

C

C

ver Sheet

o

o

o

ver Sheet

ver Sheet

L

L

L

-7781

-7781

-7781

A

A

A

E

1

1

1

1Friday, February 24, 2012

1Friday, February 24, 2012

6

6

6

1Friday, February 24, 2012

o

o

o

f

f

f

1

1

1

0

0

0

.

.

.

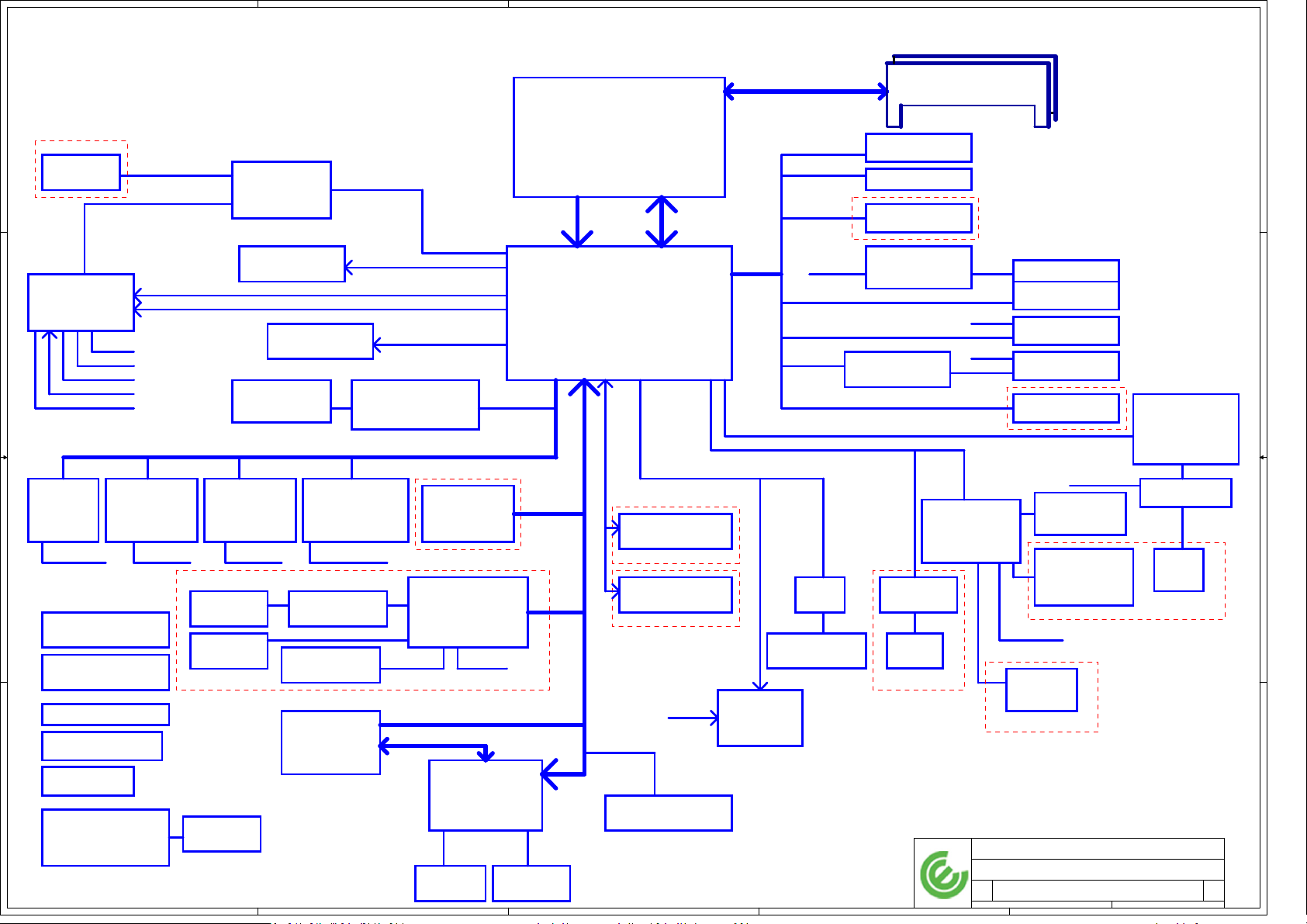

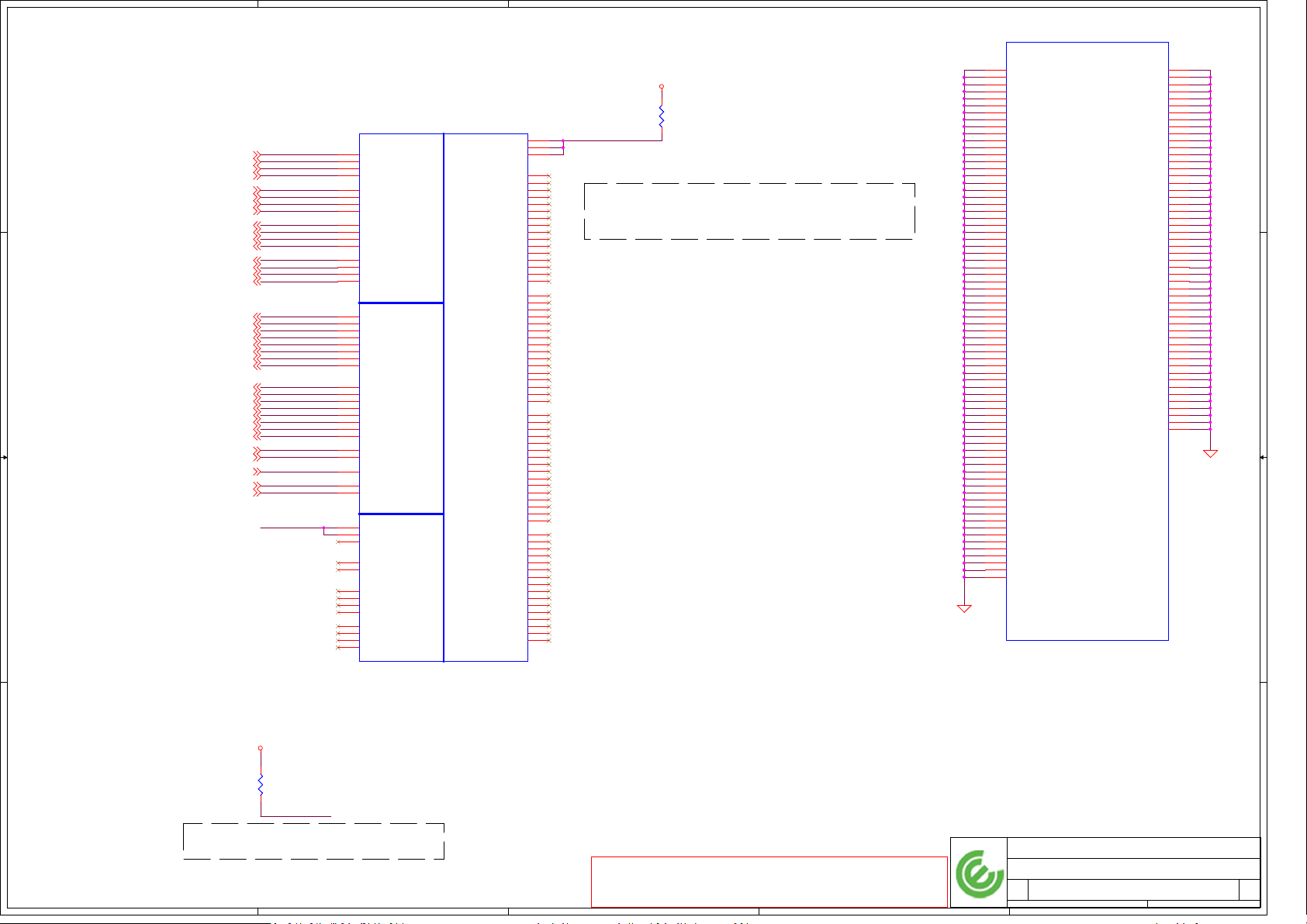

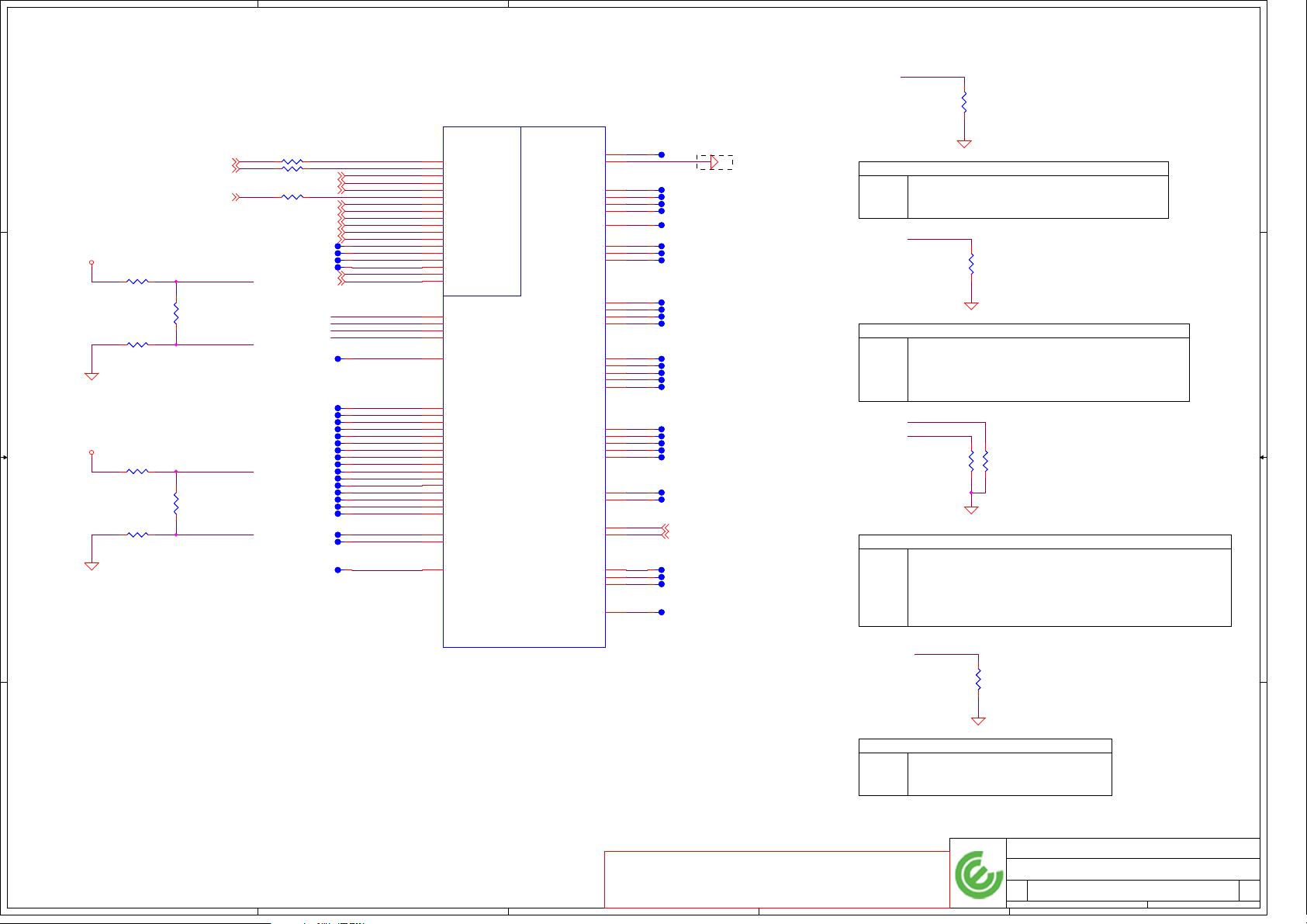

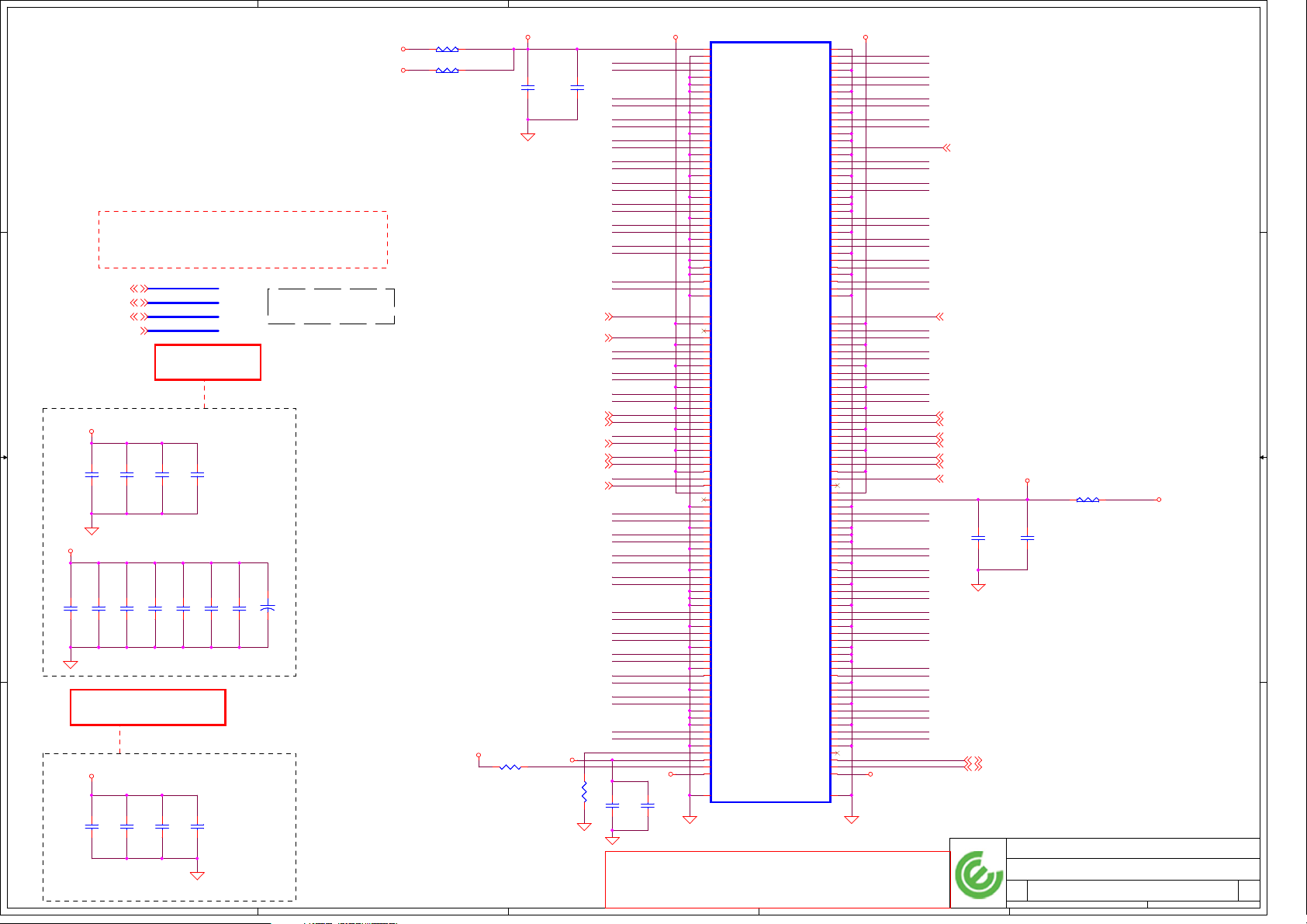

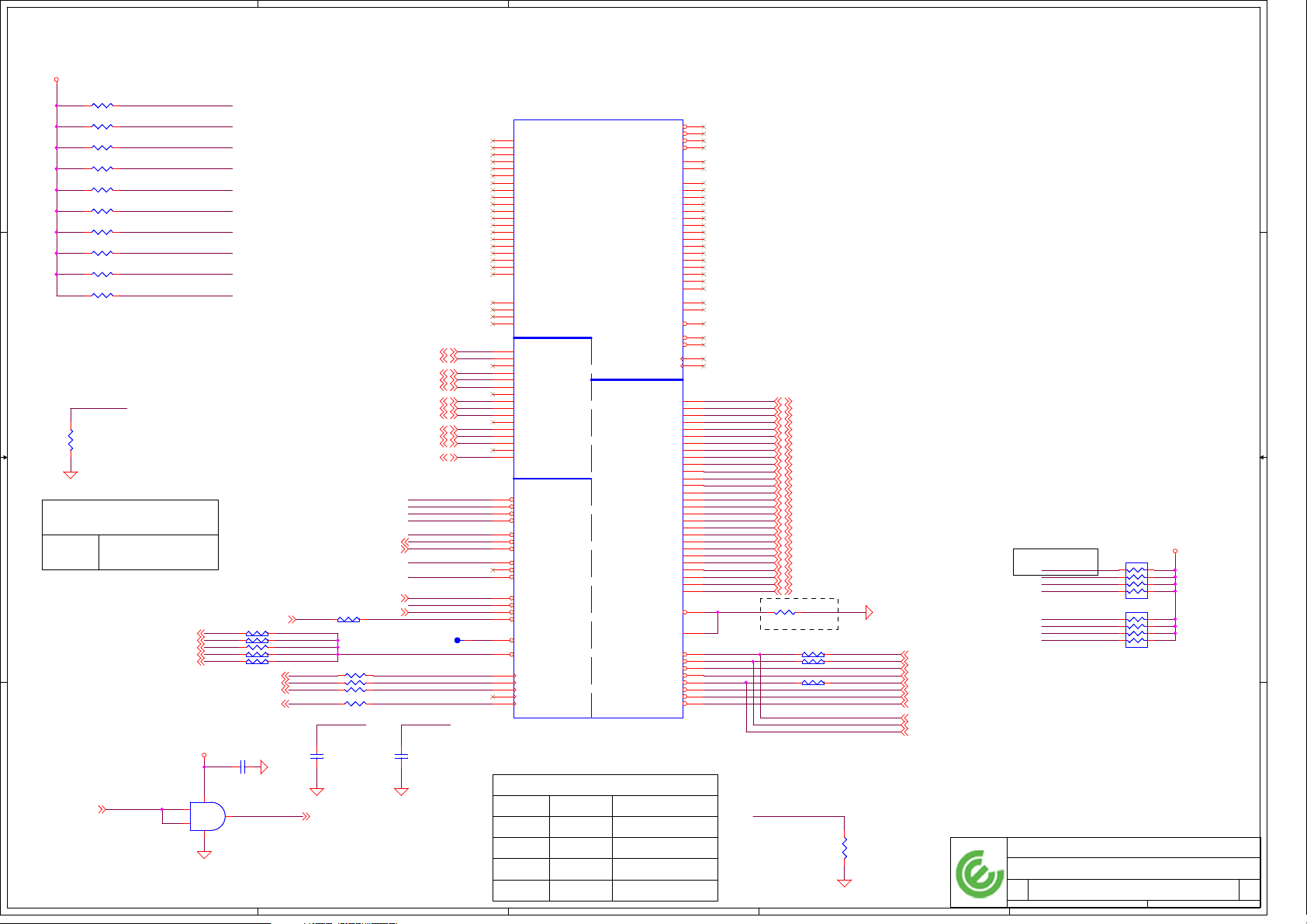

Page 2

A

B

ck Diagram

lo

1 1

On IO board

CRT CONN

VGA

VGA

For MB/DOCK

Video Switch

PI3V713-AZLEX

PAGE 23

HDMI CONN

PAGE 25

DOCKING PORT

PAGE 37

D

2 2

EXPRESS

Card

USB10

3 3

AI

U

SB2.0 [3,6]

S

ATA5

D

O

CK LAN

U

SB3.0 [4]

1/2 Mini Card

PP

PCIE5

1/2 Mini Card

PAGE 33

USB8

Smart Card

LVDS CONN

SDXC/MMC

PCIE2

WLAN

PAGE 33 PAGE 33PAGE 34

PAGE 32

Full Mini Card

WWAN

USB5USB4

TDA8034HN

CPU XDP Port

PCH XDP Port

W

Fi ON/OFF

i

RFID

Fingerprint

CONN

SMSC SIO

D

C

/DC Interface

L

E

4 4

D

Thermal

GUARDIAN III

EMC4021

PWM FAN

PAGE 22

PAGE 22

A

ECE5048

B

PAGE 22

Card Reader

OZ600FJ0

PCI Express BUS

F

B

O

P_USB

BC BUS

PCIE1PCIE3

PAGE 38

VGA

DPB

DPC

D

D

P

LVDS

PAGE 32

100MHz

tion

p

China TCM1.2

SSX44B

PAGE 31

USH

BCM5882

USB7

U

SH Module

SMSC KBC

MEC5055

TP CONN

PAGE 40 PAGE 40

PCIE x1

LPC BUS

33MHz

PAGE 39

KB CONN

Ivy Bridge

rPGA CPU

FDI

Lane x 8

I

TEL

N

P

nther Point-M

a

B

G

A

SPI

W25Q64CVSSIG

64M 4K sector

W25Q32BVSSIG

32M 4K sector

Discrete TPM

AT97SC3204

C

Memory BUS (DDR3)

1333/1600 MHz

PAGE 6-11

D

M

I2

L

a

ne x 4

U

SB

PAGE 14-21

PCI Express BUS

H

D Audio I/F

S

-ATA 0/1 6GB/s, S-ATA 2/3/4/5 3GB/s

PAGE 14

PAGE 14

FFS LNG3DM

P

IE4

C

E-Module

PAGE 27

PAGE 31

C

S

ATA

PI5USB1457A USB

Power Share

100MHz

HDD

PAGE 26

PAGE 26

D

DDRIII-DIMM X2

BANK 0, 1, 2, 3, 4 ,5 ,6 ,7

Touch Screen

BT 4.0

PAGE 22

PAGE 40

Camera

SATA Repeater

PS8513B

PAGE 36

PAGE 35

HDA Codec

9

M

D

C

RJ11

on IO board

D

E

PAGE 12-13

T

ough Cable

r

E-SATA

U

SB3.0

U

SB3.0

on IO board

USB 2.0 Port

USB3.0/2.0

USB3.0/2.0+PS

USB Port

PAGE 36

PAGE 35

PAGE 35

Intel Lewisville

DOCK LAN

INT.Speaker

HD93

2

PAGE 28

Combo Jack

D

I

A

D

i

g.

PAGE 28

T

o

Docking side

MIC

T

ough LVDS Cable

r

D

E

LL CONFIDENTIAL/PROPRIETARY

C

C

C

mpal Electronics, Inc.

o

o

o

mpal Electronics, Inc.

T

T

T

tle

i

i

i

tle

tle

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

mpal Electronics, Inc.

U

U

U

MA Block Diagram

M

M

A Block Diagram

A Block Diagram

L

L

L

-7781

-7781

A

A

A

-7781

E

2

2

2

82579LM

LAN SWITCH

PAGE 30

PI3L720

RJ45

on IO board

1Friday, February 24, 2012

1Friday, February 24, 2012

6

6

6

1Friday, February 24, 2012

o

o

o

f

f

f

PAGE 30

1

1

1

0

0

.

.

.0

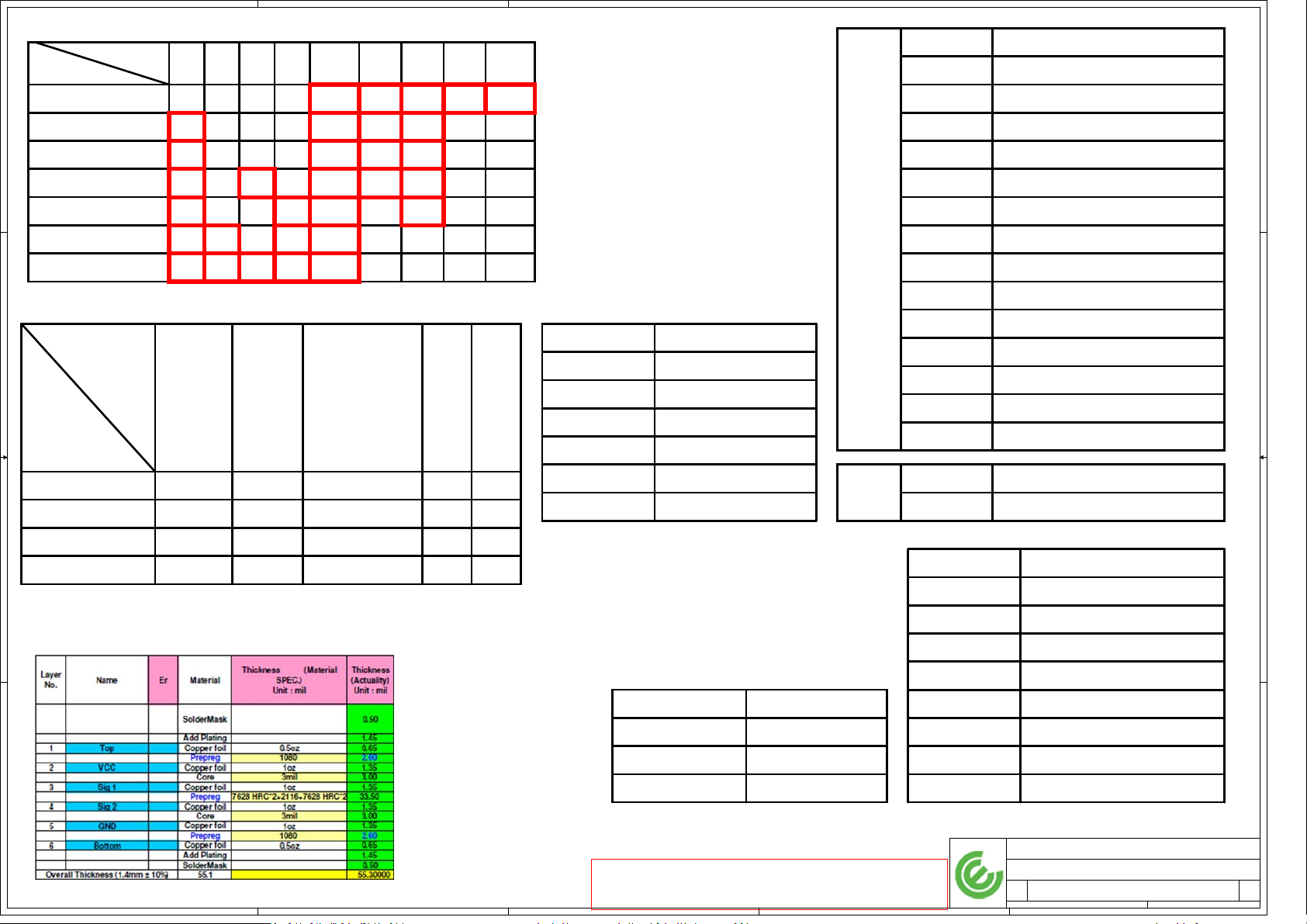

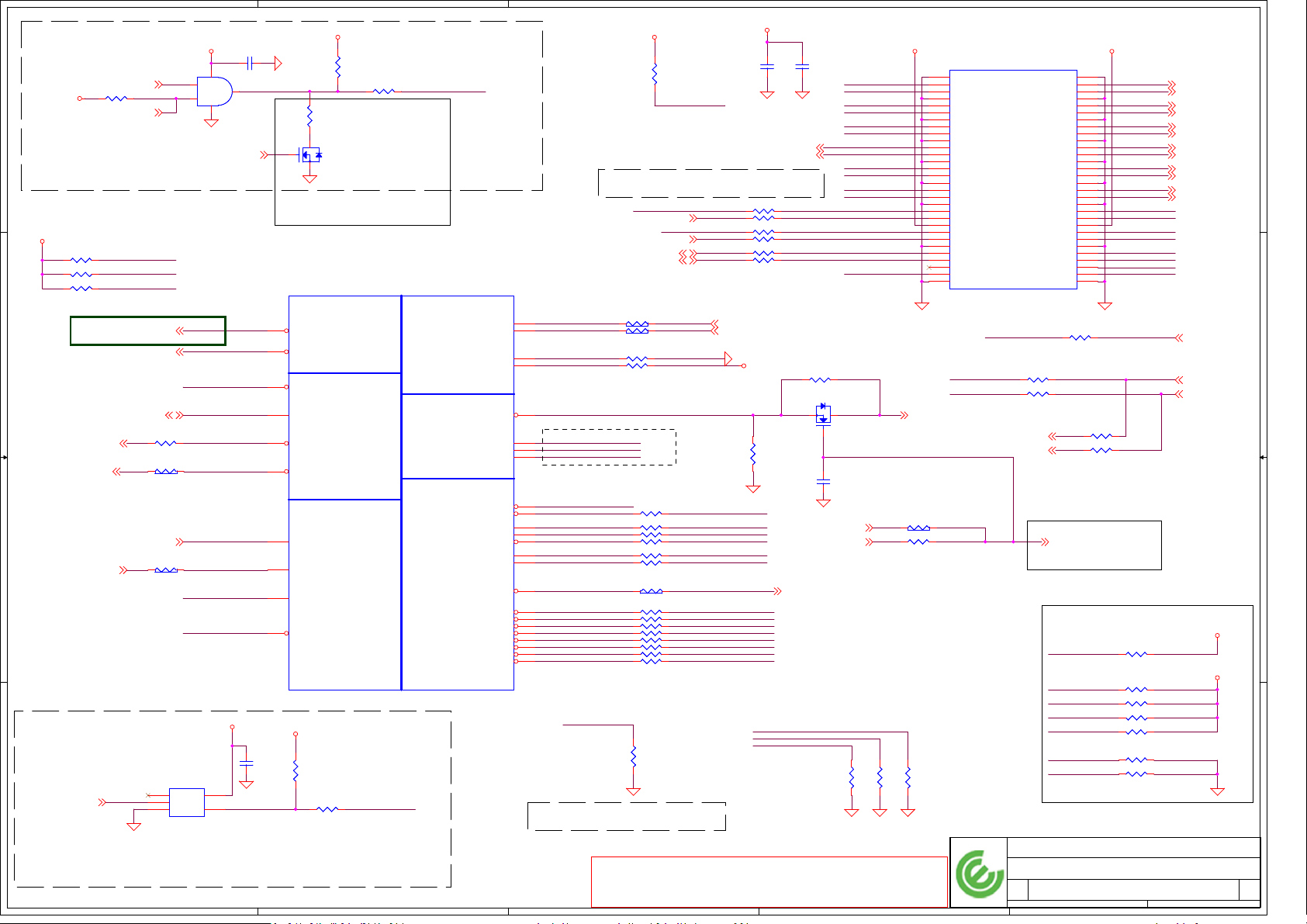

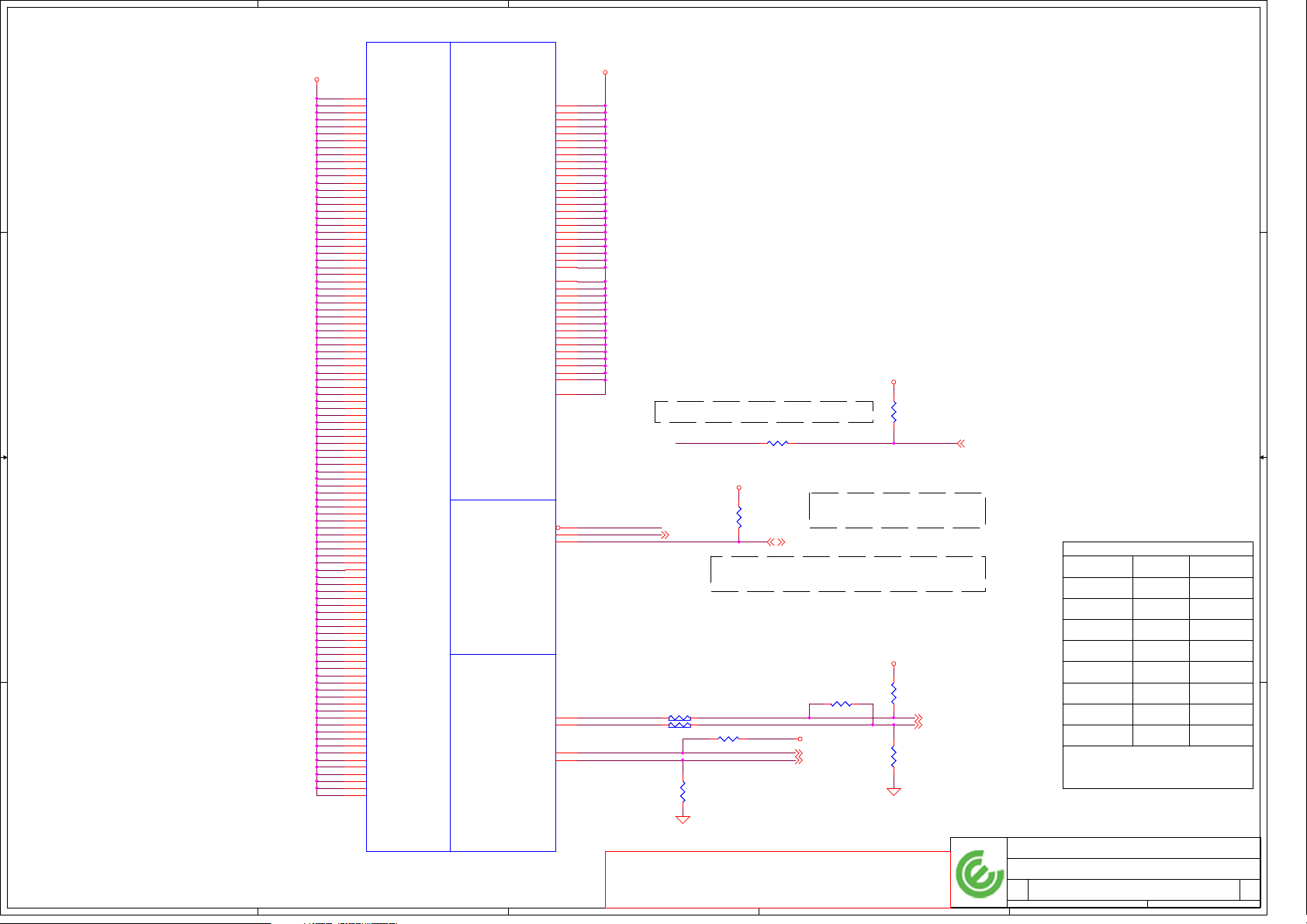

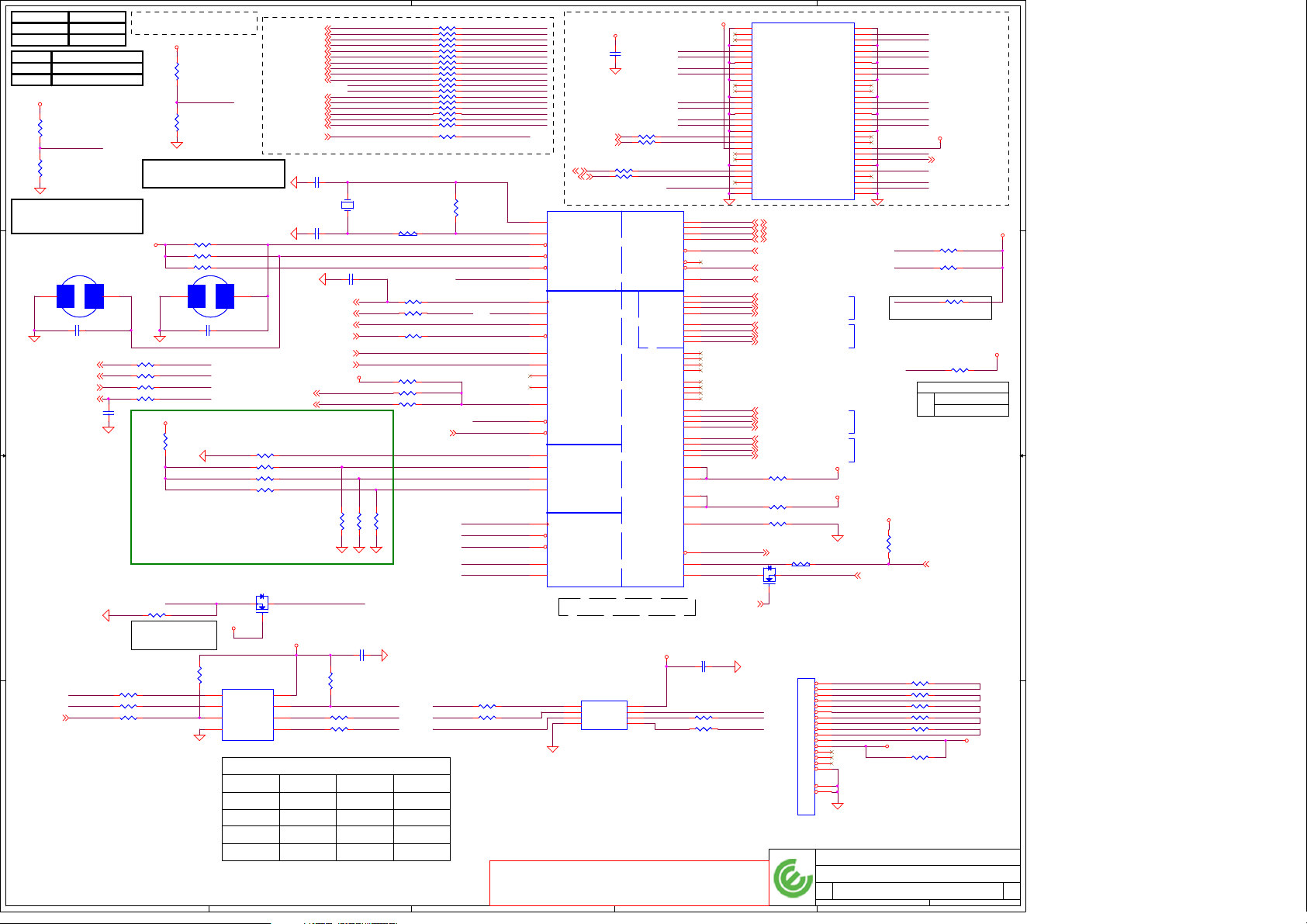

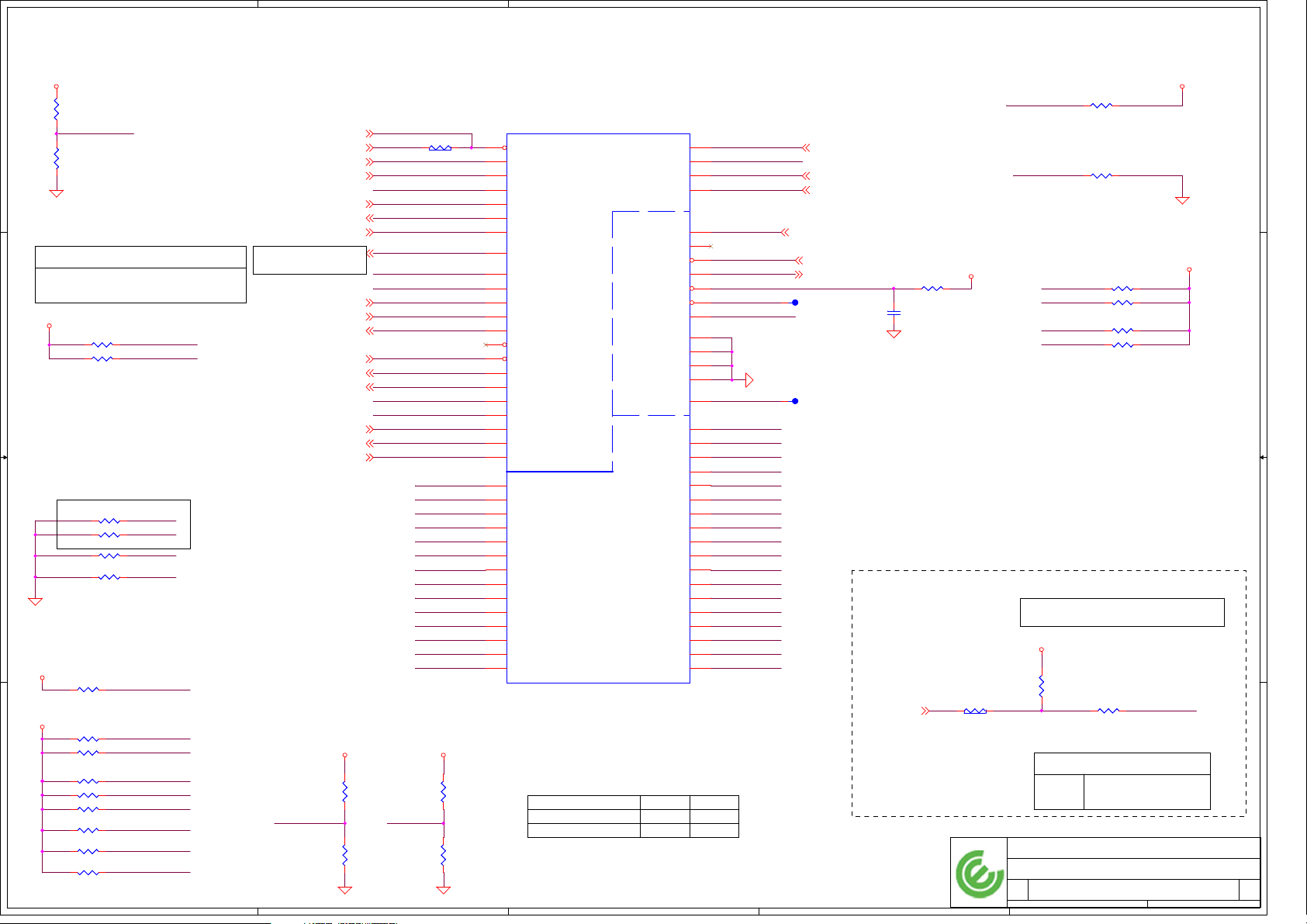

Page 3

5

4

3

2

1

POWER STATES

CH

S

H

USB PORT#

0

1

2

3

4

5

6

7

8

9

1

0

11

1

2

3

1

0

1

JUSB1 (Right side Top)

JUSB2 (Right side Bottom)

J

E

DOCKING

WLAN

WWAN

D

O

U

S

JMINI3(Flash)

J

U

E

x

Bluetooth

Camera

LCD Touch

S

L

P

SLP

S3#

S4#

H

IGH HIGH

HIGH

L

O

W HIGH HIGH ON ON ON OFF

LOW HIGH HIGH

LOW

LOW

LOW HIGH HIGH LOW ON ONOFF OFF OFF

LOW LOW LOW ON OFF OFF OFF OFF

LOW LOW LOW LOW ON OFF OFF OFF OFF

+PWR_SRC_S

+5V_ALW

+3.3V_ALW_PCH

+3.3V_RTC_LDO

O

N

ower

p

plane

Signal

State

S

(Full ON) / M0

0

D D

S3 (Suspend to RAM) / M3

S4 (Suspend to DISK) / M3 ON ON OFF

S5 (SOFT OFF) / M3 ON ON OFFLOW HIGHLOW

S

3

(Suspend to RAM) / M-OFF

S4 (Suspend to DISK) / M-OFF

S5 (SOFT OFF) / M-OFF

P

TABLE

M

C C

State

S

0

S

3

S

L

SLP

S5#

H

+

3

+1.5V_MEM

P

A#

HIGH

HIGH

GH

I

.3V_SUS

ON ON

ON

ALWAYS

PLANE

+5V_RUN

+3.3V_RUN

+1.8V_RUN

+1.5V_RUN

+0.75V_DDR_VTT

+VCC_CORE

+1.05V_RUN_VTT

+1.05V_RUN

ON

M

PLANE

ON

OFFON

SUS

RUN

PLANE

PLANE

ON ON ON

OFF

OFF

+

+

3.3V_M

1

.05V_M

ON

ON

+

3

+1.05V_M

(M-OFF)

ON

OFF

CLOCKS

OFF

OFF

O

FF

.3V_M

S

A

TA

SATA 0

ATA 1

S

SATA 2

SATA 3

S

A

TA 4

SATA 5

D

E

STINATION

HDD

O

DD/ E3 Module Bay

N

A

N

A

E

S

ATA

Dock

P

U

DESTINATION

SA1 (Right side ESATA)

CKING

H->BIO

SB (Left side)

press card

B

O

I

NA

S5 S4/AC

S

5

S4/AC don't exist

B B

A A

5

ON

OFF

OFFOFF

OFF

OFF

ON

OFF

OFFOFF

need to update Power Status and PM

Table

4

P

C

U

A DP/HDMI Port

M

Port B

Port C

P

o

rt D

P

ROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

Connetion

MB HDMI Conn

Dock DP port 2

Dock DP port 1

2

I EXPRESS

Lane 1

L

ane 2

Lane 3

Lane 4

L

ne 5

a

Lane 6

L

ne 7

a

MINI CARD-1 WWAN

M

Express card

E

1

MMI

10/100/1G LOM

Lane 8 None

D

ELL CONFIDENTIAL/PROPRIETARY

T

T

T

tle

i

i

i

tle

tle

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

D

STINATION

E

NI CARD-2 WLAN

I

3 Module Bay (USB3)

/2vMINI CARD-3 PCIE

C

C

C

mpal Electronics, Inc.

o

o

o

mpal Electronics, Inc.

mpal Electronics, Inc.

I

I

I

ndex and Config.

n

n

dex and Config.

dex and Config.

L

L

L

-7781

-7781

A

A

A

-7781

1

1

1

1

0

0

.

.

3

3

3

.0

1Friday, February 24, 2012

1Friday, February 24, 2012

6

6

6

1Friday, February 24, 2012

o

o

o

f

f

f

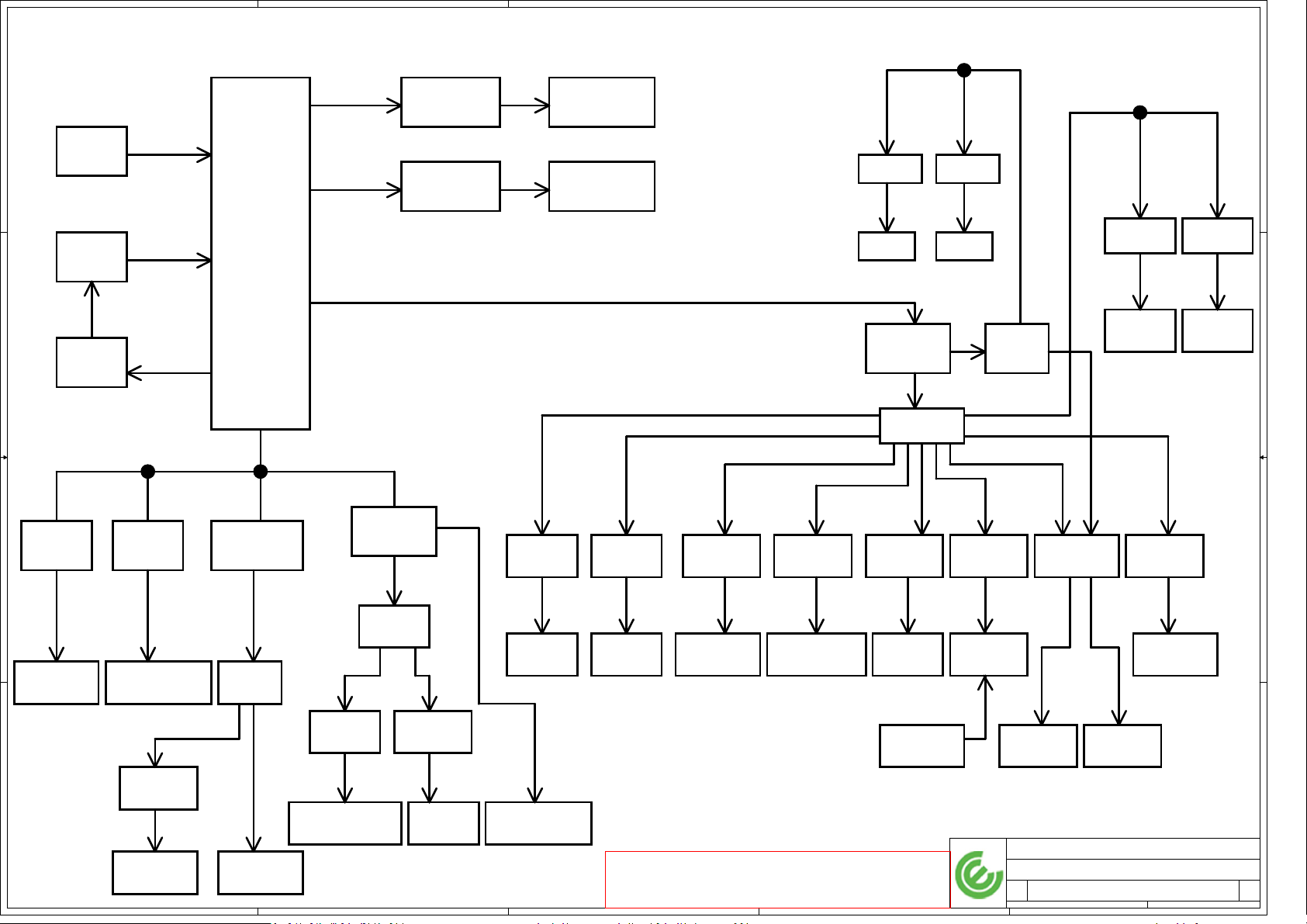

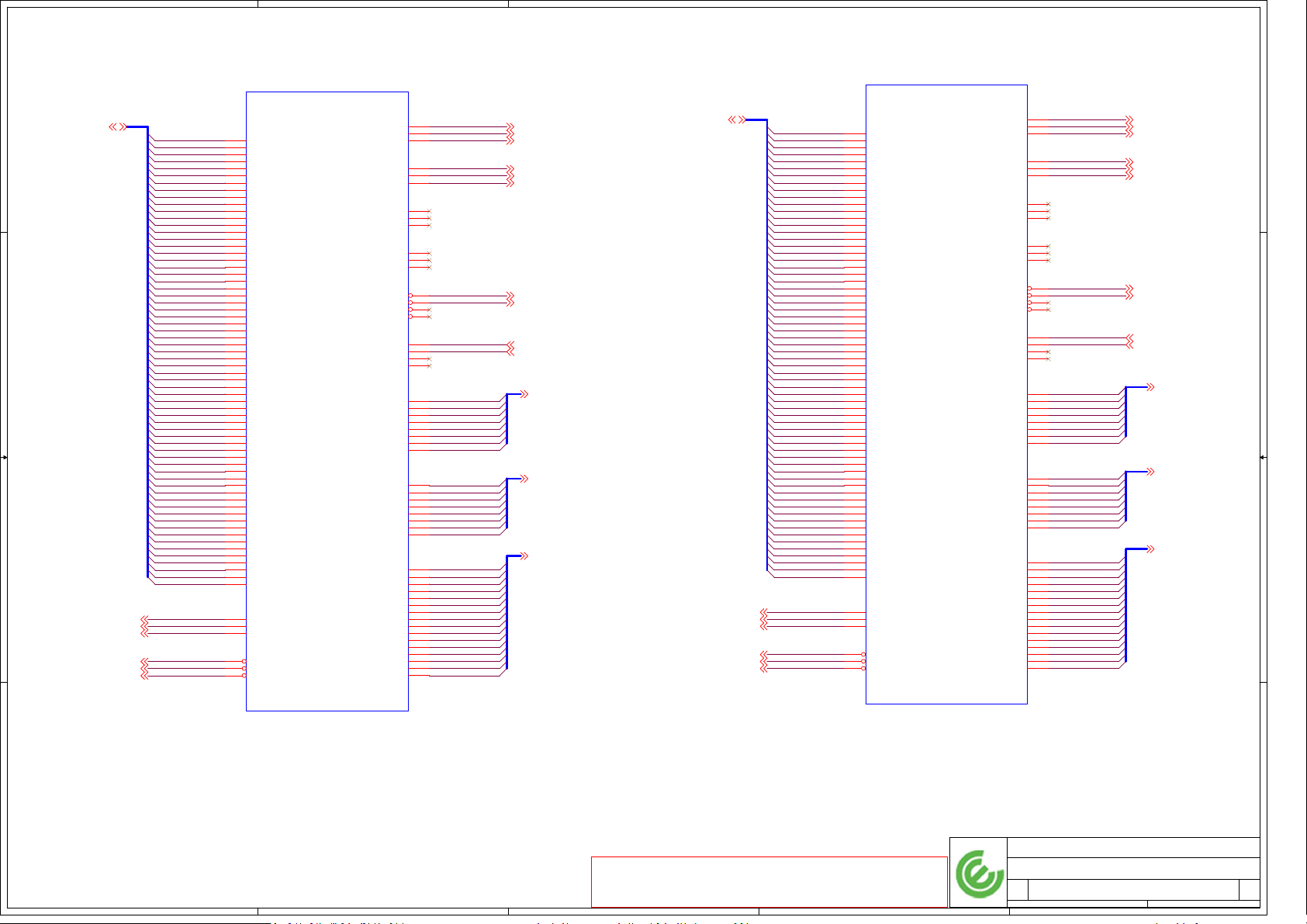

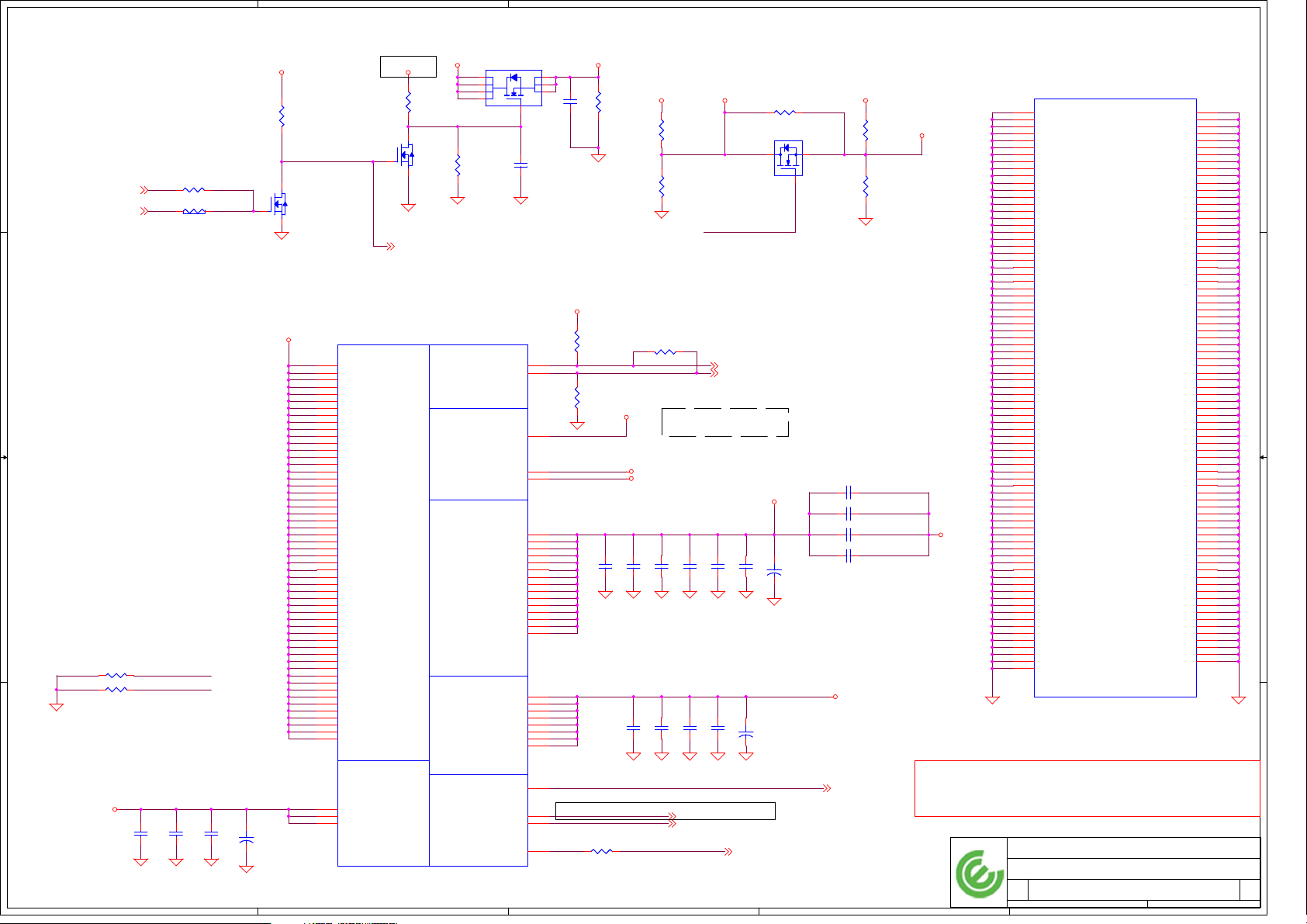

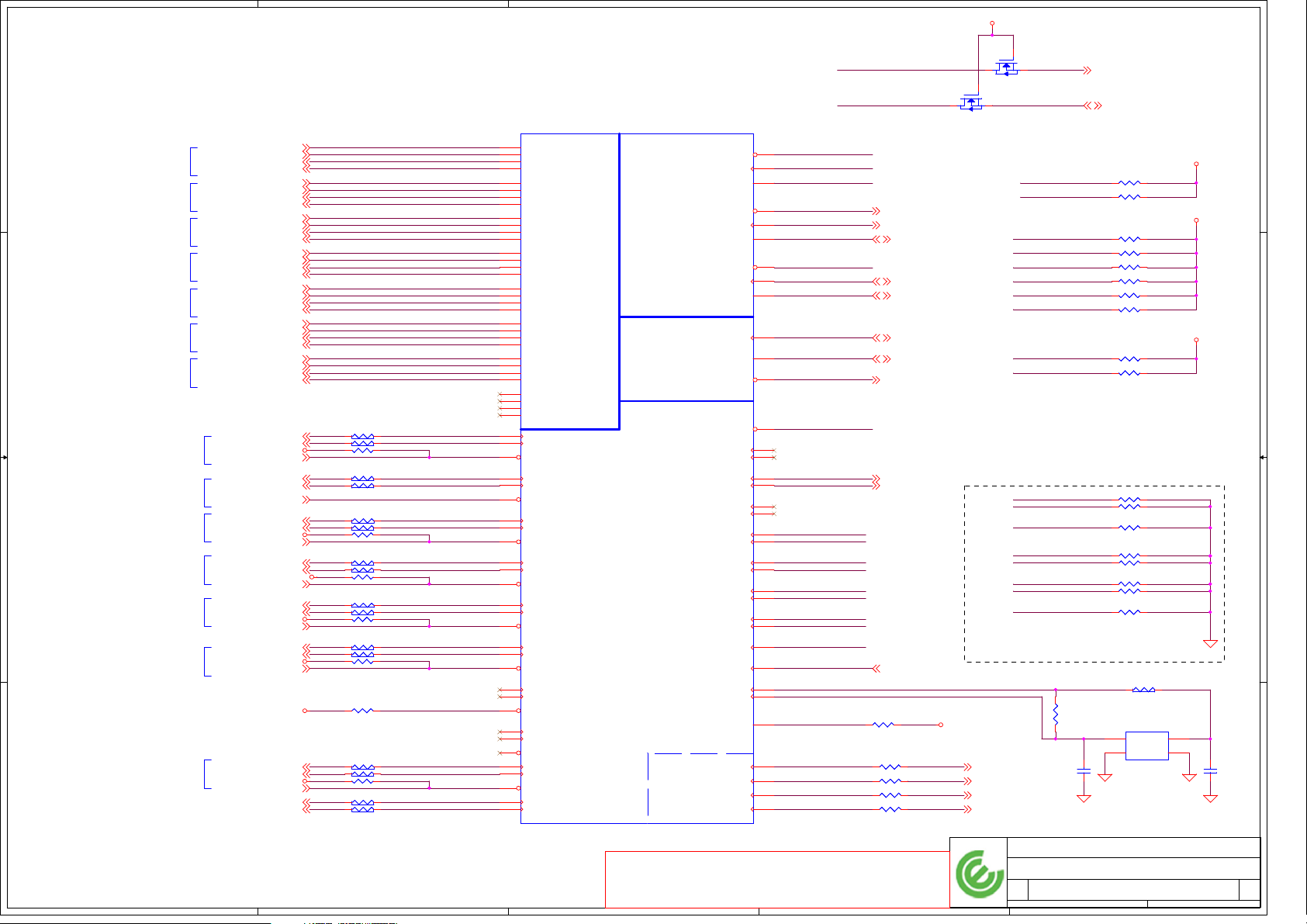

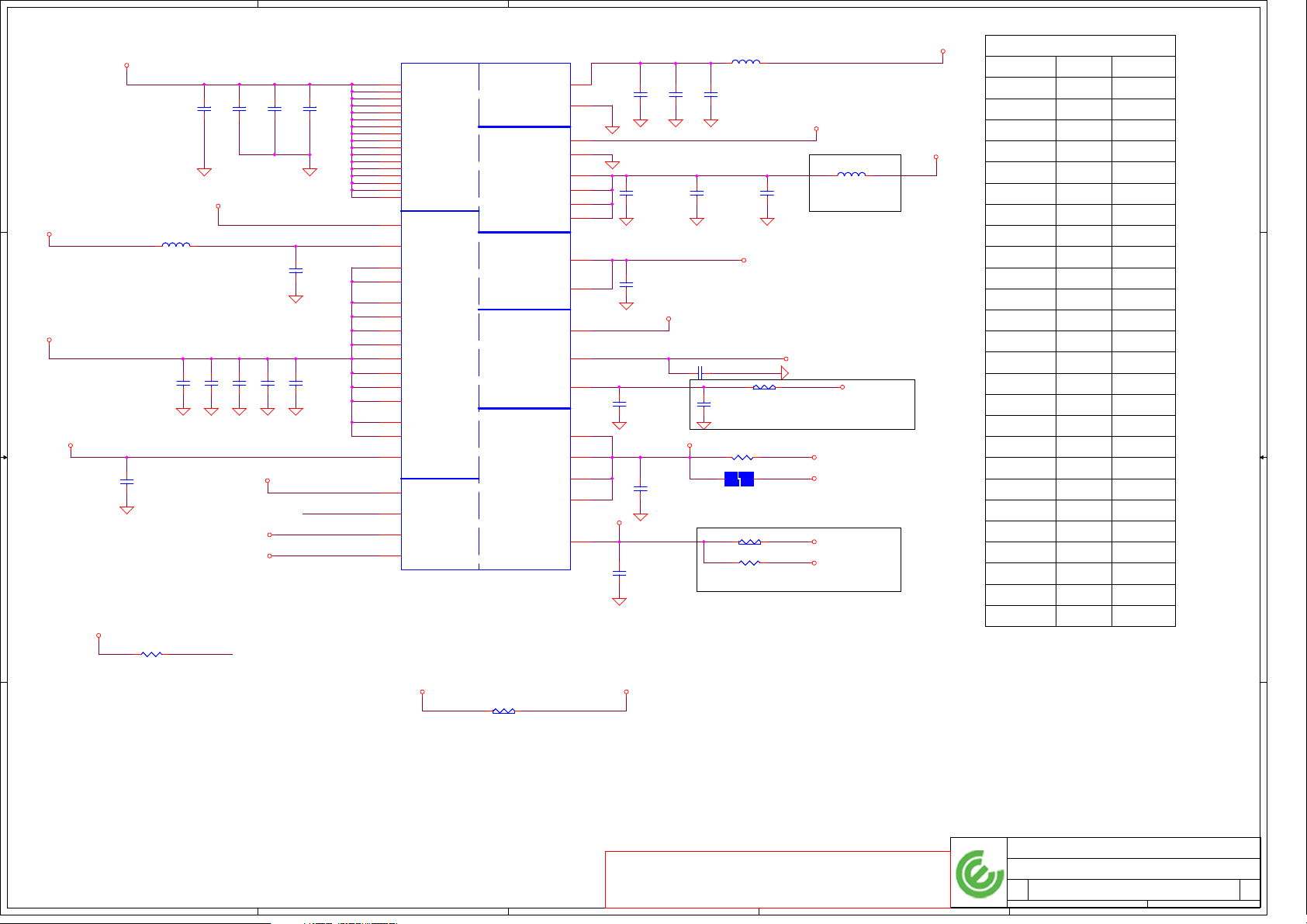

Page 4

5

E

N_INVPWR

D D

4

F

D

C654P

(

21)

Q

+

B

L_PWR_SRC

3

2

DC_EN

O

O_SLP_S3#

I

S

M

1

ADAPTER

S

I3456BDVSI3456BDV

+

V_MOD

5

(Q30)(Q27)

S

I

(Q42)

ARD_MISC_PWREN

C

M

3456

S

I

(Q40)

ARD_WWAN_PWREN

C

M

3456

B

A

TTERY

+PWR_SRC

1

.

05V_0.8V_PWROK

I

SL95836

(PU700)

+

CC_GFXCORE

V

+

5

V_HDD

A

LWON

IO_SLP_A#

S

S

I

3456

(

58)

Q

+3.3V_M

+

.3V_WWAN

3

+

O_SLP_S3#

I

S

+

5

3.3V_FLASH

V_RUN

C C

B B

A A

I

L95836

S

(

PU700)

05V_0.8V_PWROK

.

1

+

CC_CORE

V

C

H

ARGER

T

P

S51212

T

(PU500)

U_VTT_ON

P

C

+

1

.05V_RUN_VTT +1.05V_M

S

O_SLP_S3#

I

S

I

4164

(Q63)

S51212

P

(PU400)

O_SLP_A#

I

S

P

op option

S

O_SLP_S3#

I

A

O

4728

(QC3)

R

T

8207

(

P

U200)

R_ON

D

D

+

1

.5V_MEM

S

O_SLP_S3#

I

NTGS4141N

(

59)

Q

IO_SLP_S3#

S

S

8033

Y

(

P

U300)

+

1

0.75V_DDR_VTT_ON

.8V_RUN

T

P

(

P

+

V

05V_VTTPWRGD

.

1

S51461

U600)

CC_SA

S

I

(Q38)

+

3

.3V_WLAN

X_EN_WOWL

U

A

3456

H_ALW_ON

C

P

S

I

3456

(Q49)

+

.3V_ALW_PCH

3

RT8205

(

PU100)

+

3

.3V_ALW

S

1

3456

(Q54)

+

3

.3V_SUS

S_ON

U

S

+

3.3V_M

+

V_ALW

5

O_SLP_LAN#

I

S

S

I3456

(Q34) (U78)

+

3

.3V_LAN

P

p option

o

+

.3V_RUN

3

O_SLP_S3#

I

S

TPS22966

+

.05V_RUN

1

5

+

1.0V_LAN

+

1

.5V_RUN+1.5V_CPU_VDDQ

4

+

0

.75V_DDR_VTT

P

ROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

T

RADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

B

E

TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

N

EITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

P

A

RTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

2

D

E

LL CONFIDENTIAL/PROPRIETARY

C

C

C

mpal Electronics, Inc.

o

o

o

mpal Electronics, Inc.

T

T

T

tle

i

i

i

tle

tle

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

mpal Electronics, Inc.

P

P

P

ower Rail

o

o

wer Rail

wer Rail

L

L

L

-7781

-7781

A

A

A

-7781

4

4

4

1

o

o

o

f

f

f

1

1

1

0

0

.

.

.0

1Friday, February 24, 2012

1Friday, February 24, 2012

6

6

6

1Friday, February 24, 2012

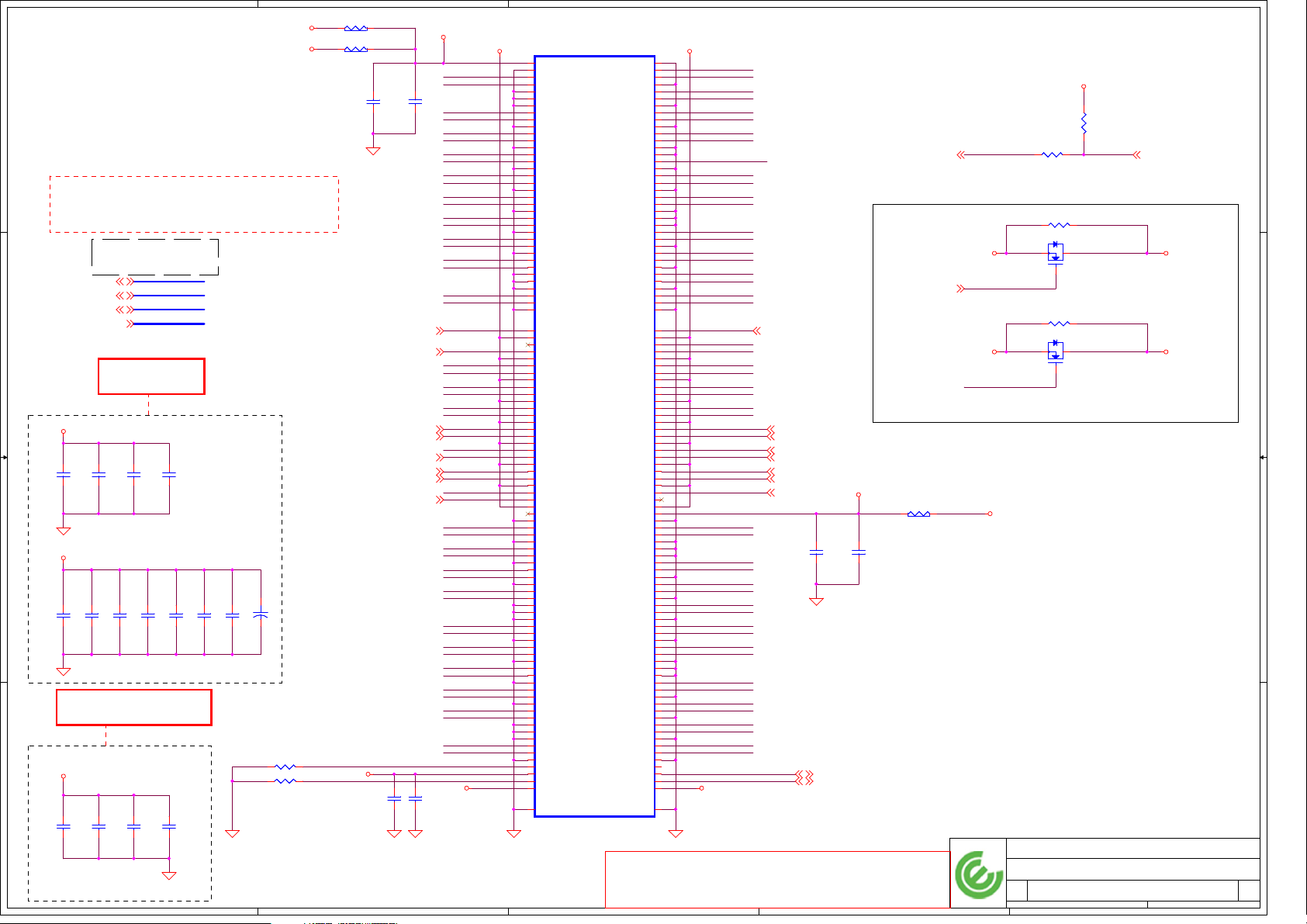

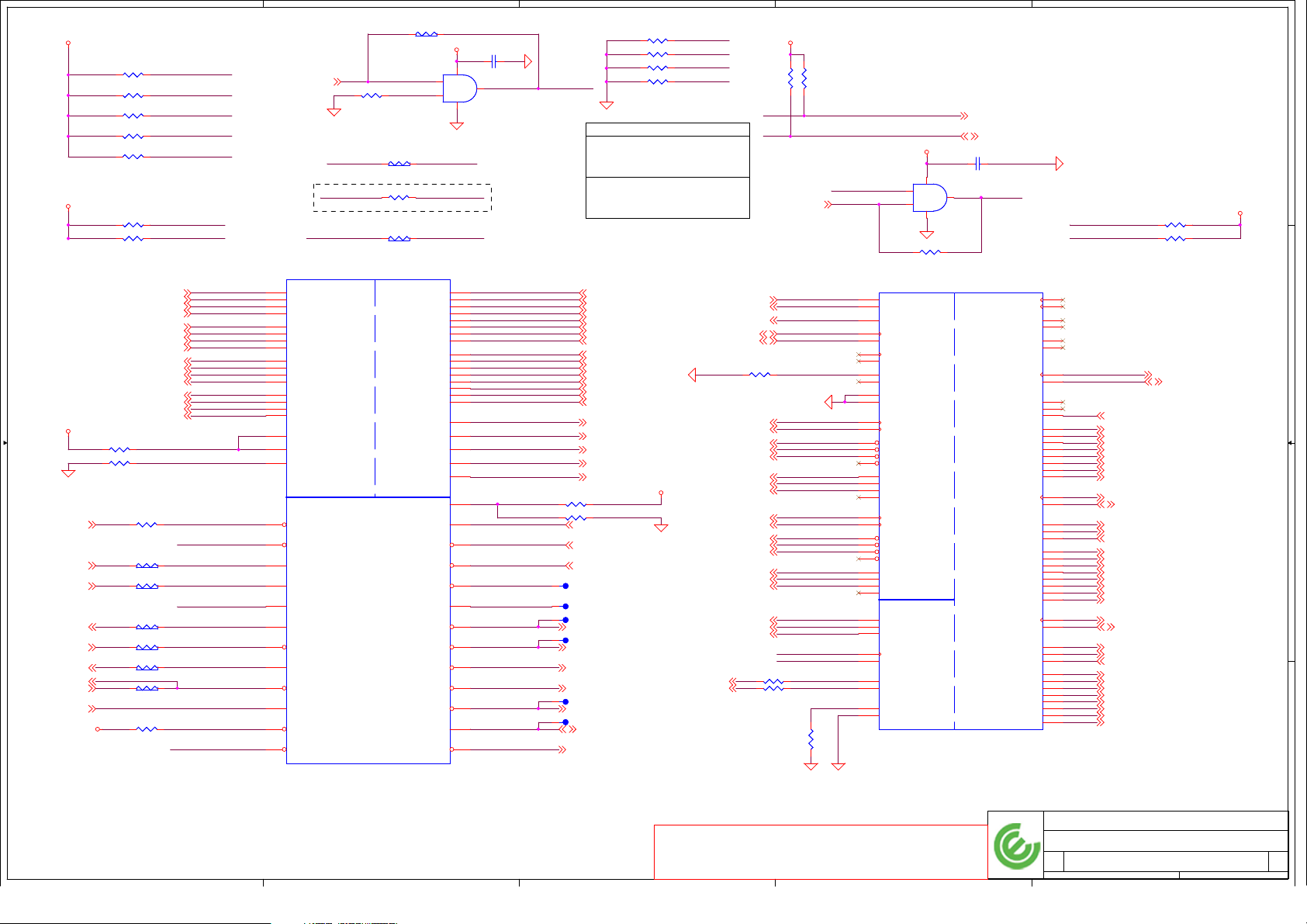

Page 5

5

S

MBUS Address [0x9a]

B

4

A3

B5

A4

A56

MEM_SMBCLK

M

M_SMBDATA

E

L

N_SMBCLK

A

LAN_SMBDATA

2.2K

2

2K

.

D

O

CK_SMB_CLK

D

O

CK_SMB_DAT

L

CD_SMBCLK

LCD_SMDATA

P

B

AT_SMBCLK

PBAT_SMBDAT

+

3.3V_ALW_PCH

H14

C

9

P

H

D D

C C

C

C

8

G12

E

14M16

S

M

L1_SMBDATA

S

ML1_SMBCLK

B

6A5

3

A

3A

1A

1A

1B

1B

K

BC

1C1CB59

2.

2.2K

2

.

2.2K

2K

2K

2

2

2

2.2K

2

.

.2K

.

2

2

.

4

2K

2K

2K

.

2K

.

2K

+3.3V_ALW_PCH

+

3.3V_LAN

2

8

3

1

LOM

+

3.3V_ALW

+

3.3V_ALW

+

3.3V_ALW

1

0 ohm

0

1

0

0 ohm

2N7002

2

7002

N

S

BUS Address [C8]

M

127

1

29

7

6

D

OCKING

BATTERY

CONN

3

S

MBUS Address

A

R_EC: 0x48

P

SPR_EC: 0x70

MSLICE_EC: 0x72

USB: 0x59

AUDIO: 0x34

SLICE_BATTERY: 0x17

SLICE_CHARGER: 0x13

S

MBUS Address [0x16]

2

2

202

2

2

02

00

0

0

5

3

5

1

5

3

5

1

30

3

2

D

IMMA

D

IMMB

XDP1

XDP2

1

0

K

1

K

0

4

G

6

SMBUS Address [A0]

SMBUS Address [A4]

S

MBUS Address [TBD]

SMBUS Address [TBD]

+

3.3V_RUN

Sensor

W

AN

W

S

M

BUS Address [3B]

SMBUS Address [TBD]

1

+

A

2.2K

50

U

B53

A

9

4

B52

B50

A47

B

7

A7

SH_SMBCLK

U

S

H_SMBDAT

CARD_SMBCLK

CARD_SMBDAT

C

HARGER_SMBCLK

CHARGER_SMBDAT

BAY_SMBDAT

BAY_SMBCLK

2

.

2K

2

2K

.

2

.2K

2

.

2K

2

.

2K

2

.

2K

4

1E

B B

M

E

C 5065

A A

1E

2B

2B

1G

1G

2

D

2

D

5

3.3V_ALW

+

3.3V_SUS

+

3.3V_ALW

+

3.3V_ALW

M

9

9

L

U

S

H

S

M

BUS Address [0xa4]

7

8

Express card

9

8

C

h

arger

SMBUS Address [0x12]

S

BUS Address [TBD]

M

2

9

E

3 Module Bay

3

0

3

S

M

BUS Address [0xd2]

C

C

C

mpal Electronics, Inc.

o

o

o

mpal Electronics, Inc.

T

T

T

tle

i

i

i

tle

tle

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

mpal Electronics, Inc.

S

S

S

MBUS TOPOLOGY

M

M

BUS TOPOLOGY

BUS TOPOLOGY

L

L

L

-7781

-7781

A

A

A

-7781

5

5

5

1

1

1

1

0

0

.

.

.0

1Friday, February 24, 2012

1Friday, February 24, 2012

6

6

6

1Friday, February 24, 2012

o

o

o

f

f

f

Page 6

5

4

3

2

1

(1)PEG_RCOMPO (H22) use 4mil connect to PEG_ICOMPI, then use 4mil connect to RC2.

(2)PEG_ICOMPO use 12mil connect to RC2

+

.05V_RUN_VTT

1

12

C

C

2

2

R

R

24.9_0402_1%~D

D D

DM

D

M

I_CRX_PTX_N0<16>

D

M

I_CRX_PTX_N1<16>

D

M

I_CRX_PTX_N2<16>

D

M

I_CRX_PTX_N3<16>

D

I_CRX_PTX_P0<16>

M

D

I_CRX_PTX_P1<16>

M

D

M

I_CRX_PTX_P2<16>

D

MI_CRX_PTX_P3<16>

D

M

I_CTX_PRX_N0<16>

D

I_CTX_PRX_N1<16>

M

D

I_CTX_PRX_N2<16>

M

D

I_CTX_PRX_N3<16>

M

D

M

I_CTX_PRX_P0<16>

D

M

I_CTX_PRX_P1<16>

D

M

I_CTX_PRX_P2<16>

D

I_CTX_PRX_P3<16>

M

F

D

I_CTX_PRX_N0<16>

F

D

I_CTX_PRX_N1<16>

F

I_CTX_PRX_N2<16>

D

F

I_CTX_PRX_N3<16>

D

F

D

C C

B B

I_CTX_PRX_N4<16>

F

D

I_CTX_PRX_N5<16>

F

I_CTX_PRX_N6<16>

D

F

I_CTX_PRX_N7<16>

D

F

D

I_CTX_PRX_P0<16>

F

D

I_CTX_PRX_P1<16>

F

I_CTX_PRX_P2<16>

D

F

D

I_CTX_PRX_P3<16>

F

DI_CTX_PRX_P4<16>

F

D

I_CTX_PRX_P5<16>

F

I_CTX_PRX_P6<16>

D

F

I_CTX_PRX_P7<16>

D

F

D

I_FSYNC0<16>

F

I_FSYNC1<16>

D

F

D

I_INT<16>

F

I_LSYNC0<16>

D

F

D

I_LSYNC1<16>

(1) EDP_COMPIO use 4mil trace to RC1

(2) EDP_ICOMPO use 12mil to RC1

I_CRX_PTX_N0

D

M

I_CRX_PTX_N1

D

I_CRX_PTX_N2

M

D

MI_CRX_PTX_N3

D

M

I_CRX_PTX_P0

D

I_CRX_PTX_P1

M

D

I_CRX_PTX_P2

M

D

M

I_CRX_PTX_P3

D

MI_CTX_PRX_N0

D

I_CTX_PRX_N1

M

D

I_CTX_PRX_N2

M

D

I_CTX_PRX_N3

M

D

I_CTX_PRX_P0

M

D

M

I_CTX_PRX_P1

D

M

I_CTX_PRX_P2

D

I_CTX_PRX_P3

M

F

I_CTX_PRX_N0

D

F

I_CTX_PRX_N1

D

F

I_CTX_PRX_N2

D

F

I_CTX_PRX_N3

D

F

I_CTX_PRX_N4

D

F

D

I_CTX_PRX_N5

F

I_CTX_PRX_N6

D

F

D

I_CTX_PRX_N7

F

I_CTX_PRX_P0

D

F

I_CTX_PRX_P1

D

F

I_CTX_PRX_P2

D

F

I_CTX_PRX_P3

D

F

D

I_CTX_PRX_P4

F

D

I_CTX_PRX_P5

F

D

I_CTX_PRX_P6

F

I_CTX_PRX_P7

D

F

I_FSYNC0

D

F

DI_FSYNC1

F

I_INT

D

F

I_LSYNC0

D

F

I_LSYNC1

D

E

P_COMP

D

PU1A

PU1A

C

C

J

J

B27

M

I_RX#[0]

D

B25

M

I_RX#[1]

D

A25

M

I_RX#[2]

D

B24

M

I_RX#[3]

D

B28

I_RX[0]

M

D

B26

I_RX[1]

M

D

A24

I_RX[2]

M

D

B23

I_RX[3]

M

D

G21

I_TX#[0]

M

D

E22

I_TX#[1]

M

D

F21

I_TX#[2]

M

D

D21

I_TX#[3]

M

D

G22

I_TX[0]

M

D

D22

I_TX[1]

M

D

F20

I_TX[2]

M

D

C21

I_TX[3]

M

D

A21

D

I0_TX#[0]

F

H19

D

I0_TX#[1]

F

E19

D

I0_TX#[2]

F

F18

D

I0_TX#[3]

F

B21

I1_TX#[0]

D

F

C20

I1_TX#[1]

D

F

D18

D

I1_TX#[2]

F

E17

I1_TX#[3]

D

F

A22

D

I0_TX[0]

F

G19

D

I0_TX[1]

F

E20

I0_TX[2]

D

F

G18

I0_TX[3]

D

F

B20

I1_TX[0]

D

F

C19

I1_TX[1]

D

F

D19

I1_TX[2]

D

F

F17

I1_TX[3]

D

F

J18

DI0_FSYNC

F

J17

I1_FSYNC

D

F

H20

I_INT

D

F

J19

D

I0_LSYNC

F

H17

D

I1_LSYNC

F

A18

e

D

P_COMPIO

A17

e

D

P_ICOMPO

B16

e

D

P_HPD#

C15

e

D

P_AUX

D15

e

P_AUX#

D

C17

e

P_TX[0]

D

F16

e

P_TX[1]

D

C16

e

P_TX[2]

D

G15

e

P_TX[3]

D

C18

e

P_TX#[0]

D

E16

e

D

P_TX#[1]

D16

e

D

P_TX#[2]

F15

e

D

P_TX#[3]

TYCO_2013620-3_IVYBRIDGE

TYCO_2013620-3_IVYBRIDGE

G_ICOMPI

G_ICOMPO

G_RCOMPO

G_RX#[0]

PE

G_RX#[1]

PE

E

G_RX#[2]

P

G_RX#[3]

PE

G_RX#[4]

PE

G_RX#[5]

PE

G_RX#[6]

PE

G_RX#[7]

PE

G_RX#[8]

PE

G_RX#[9]

PE

G_RX#[10]

G_RX#[11]

G_RX#[12]

G_RX#[13]

G_RX#[14]

G_RX#[15]

PE

G_RX[0]

PE

G_RX[1]

PE

G_RX[2]

PE

G_RX[3]

PE

G_RX[4]

P

G_RX[5]

E

P

G_RX[6]

E

P

G_RX[7]

E

P

G_RX[8]

E

P

G_RX[9]

E

P

G_RX[10]

E

P

E

G_RX[11]

P

E

G_RX[12]

P

E

G_RX[13]

P

G_RX[14]

E

P

G_RX[15]

E

P

G_TX#[0]

E

P

G_TX#[1]

E

P

G_TX#[2]

E

P

G_TX#[3]

E

P

E

G_TX#[4]

P

E

G_TX#[5]

P

E

G_TX#[6]

P

G_TX#[7]

E

P

G_TX#[8]

E

P

G_TX#[9]

E

P

E

G_TX#[10]

P

E

G_TX#[11]

P

E

G_TX#[12]

P

G_TX#[13]

E

P

G_TX#[14]

E

P

G_TX#[15]

E

P

E

G_TX[0]

P

E

G_TX[1]

P

G_TX[2]

E

P

G_TX[3]

E

P

G_TX[4]

E

P

G_TX[5]

E

P

E

G_TX[6]

P

E

G_TX[7]

P

E

G_TX[8]

P

G_TX[9]

E

P

G_TX[10]

E

P

E

G_TX[11]

P

E

G_TX[12]

P

E

G_TX[13]

P

G_TX[14]

E

P

E

G_TX[15]

J22

J21

H22

K33

M35

L34

J35

J32

H34

H31

G33

G30

F35

E34

E32

D33

D31

B33

C32

J33

L35

K34

H35

H32

G34

G31

F33

F30

E35

E33

F32

D34

E31

C33

B32

M29

M32

M31

L32

L29

K31

K28

J30

J28

H29

G27

E29

F27

D28

F26

E25

M28

M33

M30

L31

L28

K30

K27

J29

J27

H28

G28

E28

F28

D27

E26

D25

PE

PE

PE

DMI

DMI

ntel(R) FDI

ntel(R) FDI

I

I

DP

DP

e

e

PE

PE

PE

PE

PE

PE

CI EXPRESS* - GRAPHICS

CI EXPRESS* - GRAPHICS

P

P

24.9_0402_1%~D

P

E

G_COMP

P

G Compensation

E

P

EG_ICOMPI and R COMPO signals s hould be shorte d and routed

with - max leng th = 500 mils - typical impeda nce = 43 mohms

PEG_ICOMPO sign als should be r outed with - ma x length = 500 mils

- typical imped ance = 14.5 moh ms

J

J

PU1I

PU1I

C

C

T35

V

S

S161

T34

V

S

S162

T33

V

S163

S

T32

V

S164

S

T31

V

SS165

T30

V

S

S166

T29

V

S

S167

T28

V

S168

S

T27

V

S169

S

T26

V

S

S170

P9

V

S

S171

P8

V

S

S172

P6

V

S

S173

P5

V

S

S174

P3

V

S175

S

P2

V

S176

S

N35

V

SS177

N34

V

S

S178

N33

V

S179

S

N32

V

S180

S

N31

V

S

S181

N30

V

S

S182

N29

V

S183

S

N28

V

S184

S

N27

V

S185

S

N26

V

S

S186

M34

V

S187

S

L33

V

S188

S

L30

V

SS189

L27

V

S

S190

L9

V

S191

S

L8

V

S192

S

L6

V

S

S193

L5

V

S194

S

L4

V

S195

S

L3

V

S

S196

L2

V

S

S197

L1

V

S198

S

K35

V

SS199

K32

V

S

S200

K29

V

S

S201

K26

S202

S

V

J34

S

S203

V

J31

S

S204

V

H33

S

S205

V

H30

S206

S

V

H27

SS207

V

H24

S208

S

V

H21

S

S209

V

H18

S

S210

V

H15

S

S211

V

H13

S

S212

V

H10

S

S213

V

H9

S

S214

V

H8

S215

S

V

H7

S216

S

V

H6

S217

S

V

H5

S218

S

V

H4

S219

S

V

H3

S

S220

V

H2

S

S221

V

H1

S

S222

V

G35

S

S223

V

G32

S224

S

V

G29

S

S225

V

G26

SS226

V

G23

S227

S

V

G20

S228

S

V

G17

S229

S

V

G11

S230

S

V

F34

S231

S

V

F31

S232

S

V

F29

S

S233

V

TYCO_2013620-3_IVYBRIDGE

TYCO_2013620-3_IVYBRIDGE

F22

S234

S

V

F19

S235

S

V

E30

S

S236

V

E27

S

S237

V

E24

S

S238

V

E21

S239

S

V

E18

S240

S

V

E15

S241

S

V

E13

S242

S

V

E10

S

S243

V

E9

S

S244

V

E8

S

S245

V

E7

S246

S

V

E6

S

S247

V

E5

S

S248

V

E4

S

S249

V

E3

SS250

V

E2

S251

S

V

E1

S252

S

V

D35

S253

S

V

D32

S254

S

V

D29

S255

S

V

D26

S

S256

V

D20

S

S257

V

D17

S

S258

V

C34

S

S259

V

C31

S

S260

V

C28

S

S261

V

C27

S262

S

V

C25

S263

S

V

C23

S264

S

V

C10

S265

S

V

C1

S266

S

V

B22

S267

S

V

B19

S268

S

V

V

V

SS

S

S

B17

S269

S

V

B15

S270

S

V

B13

S

S271

V

B11

S272

S

V

B9

S

S273

V

B8

S

S274

V

B7

S

S275

V

B5

S

S276

V

B3

S

S277

V

B2

S

S278

V

A35

S

S279

V

A32

S

S280

V

A29

S

S281

V

A26

S

S282

V

A23

S

S283

V

A20

S

S284

V

A3

S

S285

V

D

Compensation

P

+

.05V_RUN_VTT

1

12

R

R

C1

C1

24.9_0402_1%~D

A A

e

D

P_COMPIO and IC OMPO signals sh ould be shorted near

balls and route d with typical impedance <25 m ohms

5

24.9_0402_1%~D

E

DP_COMP

D

LL CONFIDENTIAL/PROPRIETARY

E

C

C

C

mpal Electronics, Inc.

mpal Electronics, Inc.

o

o

o

T

T

tle

tle

i

i

P

ROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

4

3

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

mpal Electronics, Inc.

I

I

I

y Bridge (1/6)

v

v

v

y Bridge (1/6)

y Bridge (1/6)

L

L

L

-7781

-7781

A

A

A

-7781

1

1

1

1

.

0

0

0

.

6

6

6

.

1Friday, February 24, 2012

1Friday, February 24, 2012

6

6

6

1Friday, February 24, 2012

o

o

o

f

f

f

Page 7

5

llow DG Rev0.71 SM_DRAMPWROK topology

Fo

+

3

.3V_ALW_PCH

C

C

156 0.1U_0402_25V6K~D

156 0.1U_0402_25V6K~D

C

C

1 2

5

U

U

C

C

2

2

1

U

NPWROK<39,40>

R

+

.3V_ALW_PCH

3

D D

+

.05V_RUN_VTT

1

C C

B B

ffered reset to CPU

u

B

A A

P

1 2

R

R

18 200_0402_1%~D

18 200_0402_1%~D

C

C

M

P

2

1

C

C

126 56_0402_5%~D@

126 56_0402_5%~D@

R

R

1 2

R

R

128 49.9_0402_1%~D@

128 49.9_0402_1%~D@

C

C

1 2

44 62_0402_5%~D

44 62_0402_5%~D

C

C

R

R

ollow check list 0.5

F

PROCHOT#<40,51,52>

_

H

_

THERMTRIP#<22>

H

_

CPUPWRGD<18>

H

C

H_PLTRST#<14,17>

_DRAM_PWRGD<16>

H

_THERMTRIP#

H

_

CATERR#

H

PROCHOT#

_

SNB_IVB#<18>

_

H

P

U_DETECT#<39>

C

CI_EC<40>

E

P

R1 TOPOLOGY

V

1 2

R

R

C

C

57 56_0402_5%~D

57 56_0402_5%~D

1 2

R

R

129 0_0402_5%~D@

129 0_0402_5%~D@

C

C

_

PM_SYNC<16>

H

1 2

R

R

C

C

25 0_0402_5%~D@

25 0_0402_5%~D@

5

1

2

3

P

B

2

A

N_ON_CPU1.5VS3#<11,42>

U

R

H

_CATERR#

H

_PROCHOT#_R

C

H

_THERMTRIP#_R

H

PM_SYNC

_

V

C

P

M

P

C

H_PLTRST#_R

U

U

1

C

C

1

V

N

C

C

C

A

G

Y

D

N

SN74LVC1G07DCKR_SC70-5~D

SN74LVC1G07DCKR_SC70-5~D

pen drain buffer

O

R

4

O

G

74AHC1G09GW_TSSOP5~D

74AHC1G09GW_TSSOP5~D

3

ose to JCBU1

l

CPWRGOOD_0_R

_DRAM_PWRGD_CP U

+

3

.3V_RUN

1

2

5

P

H_PLTRST#_BUF

C

4

NPWROK_AND

U

0.1U_0402_25V6K~D

0.1U_0402_25V6K~D

+

.5V_CPU_VDDQ

1

RC

64

39_0402_5%~D

39_0402_5%~D

1 2

13

D

D

Q

Q

C

2

G

G

NTEL suggest RC64 and QC1 NO stuff by default

I

J

J

C26

AN34

AL33

AN33

AL32

AN32

AM34

AP33

V8

AR33

TYCO_2013620-3_IVYBRIDGE

TYCO_2013620-3_IVYBRIDGE

+

1

.05V_RUN_VTT

C

C

C

C

140

140

C

SSM3K7002FU_SC70-3~D

SSM3K7002FU_SC70-3~D

S

S

C

C

PU1B

PU1B

R

OC_SELECT#

P

K

TOCC#

S

TERR#

A

C

E

CI

P

OCHOT#

R

P

ERMTRIP#

H

T

_SYNC

M

P

COREPWRGOOD

N

U

M

_DRAMPWROK

S

SET#

E

R

75_0402_1%~D

75_0402_1%~D

R

R

12

C

C

4

4

1 2

R

R

C10 43_0402_5%~D

C10 43_0402_5%~D

4

12

RC

RC

12

12

200_0402_1%~D

200_0402_1%~D

1 2

28 130_0402_1%~D

28 130_0402_1%~D

C

C

R

R

@RC64

@

1

@

1

@

MISCTHERMALPWR MANAGEMENT

MISCTHERMALPWR MANAGEMENT

P

C

H_PLTRST#_R

4

P

_DRAM_PWRGD_CP U

M

P

D

P

LL_REF_CLK#

D

LOCKS

LOCKS

C

C

M

S

S

S

S

DR3

DR3

D

D

MISC

MISC

TAG & BPM

TAG & BPM

J

J

C

B

C

B

LL_REF_CLK

_DRAMRST#

M

_RCOMP[0]

_RCOMP[1]

M

_RCOMP[2]

M

DY#

R

P

EQ#

R

P

T

T

R

ST#

T

T

B

D

P

M#[0]

B

P

M#[1]

B

M#[2]

P

B

M#[3]

P

B

M#[4]

P

B

M#[5]

P

B

M#[6]

P

B

P

M#[7]

B

3

+

.3V_ALW_PCH

3

1

124

@RC124

@

RC

1K_0402_5%~D

1K_0402_5%~D

2

S

S_PWROK_XDP

Y

e resistor for HOOK2 should be placed

h

T

such that the s tub is very sma ll on CFG0 net

H

_

CPUPWRGD

S

O_PWRBTN#_R<14,16>

I

C

FG0_R

S_PWROK<16,39>

Y

S

R_XDP_WAN_SM BDAT<12,13,14,15,27,34>

D

D

R_XDP_WAN_SM BCLK<12,13,14,15,27,34>

D

D

C

P

LK

LK#

C

M

D

T

D

R#

C

U_DMI#

P

A27

C

P

U_DPLL

A16

C

P

U_DPLL#

A15

emove DPLL Ref clock (for eDP only)

R

D

R3_DRAMRST#_CPU

D

R8

S

M_RCOMP0

AK1

S

_RCOMP1

M

A5

S

_RCOMP2

M

A4

SM_RCOMP2 --> 15mil

SM_RCOMP1/0 --> 20mil

X

P_PRDY#

D

AP29

X

D

P_PREQ#

AP27

X

P_TCLK

D

AR26

K

X

D

P_TMS

AR27

S

X

P_TRST#

D

AP30

X

P_TDI_R

D

AR28

I

X

P_TDO_R

D

AP26

O

X

P_DBRESET#_R

D

AL35

X

D

P_OBS0_R

AT28

X

D

P_OBS1_R

AR29

X

D

P_OBS2_R

AR30

X

DP_OBS3_R

AT30

X

P_OBS4_R

D

AP32

X

P_OBS5_R

D

AR31

X

P_OBS6_R

D

AT31

X

D

P_OBS7_R

AR32

or ESD concern, please put near CPU

F

V

void stub in th e PWRGD path

A

while placing r esistors RC25 & RC130

U_DMI

A28

1 2

13 0_0402_5%~D@

13 0_0402_5%~D@

C

C

R

R

1 2

C

C

15 0_0402_5%~D@

15 0_0402_5%~D@

R

R

1 2

R

R

16 1K_0402_5%~D

16 1K_0402_5%~D

C

C

1 2

C

C

17 1K_0402_5%~D

17 1K_0402_5%~D

R

R

a

x 500mils

M

1 2

R

R

27 0_0402_5%~D@

E

E27 0_0402_5%~D@

1 2

28 0_0402_5%~D@

28 0_0402_5%~D@

E

E

R

R

1 2

R

R

29 0_0402_5%~D@

E

E

29 0_0402_5%~D@

1 2

30 0_0402_5%~D@

E

E

30 0_0402_5%~D@

R

R

1 2

E31 0_0402_5%~D@RE31 0_0402_5%~D@

R

1 2

32 0_0402_5%~D@

32 0_0402_5%~D@

E

E

R

R

2

26 0_0402_5%~D@

26 0_0402_5%~D@

1 2

30 0_0402_5%~D@

30 0_0402_5%~D@

1 2

31 0_0402_5%~D@

31 0_0402_5%~D@

1 2

33 0_0402_5%~D@

33 0_0402_5%~D@

1 2

34 0_0402_5%~D@

34 0_0402_5%~D@

1 2

36 0_0402_5%~D@

36 0_0402_5%~D@

1 2

37 0_0402_5%~D@

37 0_0402_5%~D@

1 2

38 0_0402_5%~D@

38 0_0402_5%~D@

1 2

39 0_0402_5%~D@

39 0_0402_5%~D@

12

3

1

C

C

130

130

R

R

10K_0402_5%~D

10K_0402_5%~D

R

R

C

C

C

C

R

R

R

R

C

C

R

R

C

C

R

R

C

C

C

C

R

R

C

C

R

R

C

C

R

R

R

R

C

C

CPWRGOOD_0_R

C

ROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

P

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

R

R

C

C

R

R

C

C

R

R

C

C

C

C

R

R

R

R

125 0_0402_5%~D@

125 0_0402_5%~D@

C

C

127 0_0402_5%~D@

127 0_0402_5%~D@

C

C

R

R

L

K_CPU_DMI <15>

C

K_CPU_DMI# <15>

L

C

C

C

R

R

4.99K_0402_1%~D

4.99K_0402_1%~D

X

P_PREQ#_R

D

X

P_TCLK_R

D

X

D

P_TMS_R

X

D

P_TRST#_R

X

P_TDI

D

X

D

P_TDO

X

P_DBRESET#

D

X

D

P_OBS0

X

P_OBS1

D

X

P_OBS2

D

X

DP_OBS3

X

P_OBS4

D

X

D

P_OBS5

X

P_OBS6

D

X

P_OBS7

D

+1

.05V_RUN_VTT

0.1U_0402_25V6K~D

0.1U_0402_25V6K~D

1

2

ace near JXDP1

l

P

1 2

5 1K_0402_5%~D@

5 1K_0402_5%~D@

1 2

6 0_0402_5%~D@

6 0_0402_5%~D@

1 2

7 1K_0402_5%~D@

7 1K_0402_5%~D@

1 2

9 0_0402_5%~D@

9 0_0402_5%~D@

1 2

1 2

+

1

.05V_RUN_VTT

1

50

50

2

S

_RCOMP2

M

S

_RCOMP1

M

S

M

_RCOMP0

0.1U_0402_25V6K~D

0.1U_0402_25V6K~D

1

C

C

C

C

C

C

C

C

66

66

65

65

2

F

G10<9>

C

G11<9>

F

C

1 2

48 0_0402_5%~D@

C

RC

48 0_0402_5%~D@

R

S

S

G

G

2

1

2

D

R_HVREF_RST_PCH<15>

D

R_HVREF_RST_GATE<40>

D

D

X

D

P_DBRESET# <14,16>

2

X

D

P_PREQ#_R

X

D

P_PRDY#

X

P_OBS0

D

X

P_OBS1

D

X

DP_OBS2

X

D

P_OBS3

C

F

G10

C

F

G11

X

D

P_OBS4

X

D

P_OBS5

X

P_OBS6

D

X

P_OBS7

D

H

CPUPWRGD_XDP

_

C

D_PWRBTN#_XDP

F

X

D

P_HOOK2

S

Y

S_PWROK_XDP

D

D

R_XDP_SMBDAT_R1

D

R_XDP_SMBCLK_R1

D

X

D

P_TCLK_R

D

D

13

Q

Q

C

C

2

2

BSS138W-7-F_SOT323-3~D

BSS138W-7-F_SOT323-3~D

D

R_HVREF_RST

D

C

C

177

C

C

177

0.047U_0402_16V4Z~D

0.047U_0402_16V4Z~D

46 0_0402_5%~D@RC46 0_0402_5%~D@

RC

47 0_0402_5%~D@

C

C

47 0_0402_5%~D@

R

R

12

12

42

43

45

42

C

C

R

R

140_0402_1%~D

140_0402_1%~D

45

43

C

C

RC

RC

R

R

25.5_0402_1%~D

25.5_0402_1%~D

2

+

.05V_RUN_VTT

1

R3_DRAMRST# <12>

D

D

1 2

1 2

12

200_0402_1%~D

200_0402_1%~D

J

J

DP1

DP1

X

X

1

G

D0

N

3

O

B

SFN_A0

5

O

B

SFN_A1

7

G

D2

N

9

O

SDATA_A0

B

11

O

B

SDATA_A1

13

G

N

D4

15

O

SDATA_A2

B

17

O

SDATA_A3

B

19

G

N

D6

21

O

B

SFN_B0

23

O

B

SFN_B1

25

D8

N

G

27

SDATA_B0

B

O

29

B

SDATA_B1

O

31

N

D10

G

33

B

SDATA_B2

O

35

SDATA_B3

B

O

37

D12

N

G

39

W

RGOOD/HOOK0

P

41

O

OK1

H

43

C

C_OBS_AB

V

45

O

OK2

H

47

OK3

O

H

49

D14

N

G

51

A

D

S

53

C

L

S

55

C

K1

T

57

C

K0

T

59

D16

N

G

SAMTE_BSH-030-01-L-D-A CONN@

SAMTE_BSH-030-01-L-D-A CONN@

X

P_RST#_R

D

C

K_XDP

L

H

H

107 0_0402_5%~D@

107 0_0402_5%~D@

R

R

C

L

K_XDP#

106 0_0402_5%~D@

106 0_0402_5%~D@

H

H

R

R

L

K_XDP_ITP<9>

C

K_XDP_ITP#<9>

L

C

D

tle

Title

i

i

tle

T

T

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

1

+

.05V_RUN_VTT

1

2

N

D1

G

B

SFN_C0

O

SFN_C1

B

O

D3

N

G

SDATA_C0

B

O

B

SDATA_C1

O

N

D5

G

B

SDATA_C2

O

SDATA_C3

B

O

D7

N

G

SFN_D0

B

O

B

SFN_D1

O

D9

N

G

SDATA_D0

B

O

SDATA_D1

B

O

N

D11

G

B

SDATA_D2

O

B

SDATA_D3

O

N

D13

G

PCLK/HOOK4

T

I

PCLK#/HOOK5

T

I

C_OBS_CD

C

V

SET#/HOOK6

E

R

R#/HOOK7

B

D

N

D15

G

D

0

T

R

ST#

T

D

I

T

S

M

T

D17

N

G

1 2

R

R

8 1K_0402_5%~DPXDP@

8 1K_0402_5%~DPXDP@

C

C

1 2

1 2

R

R

R

R

D

R_HVREF_RST <12>

D

3 control

M

/PD for JTAG signals

U

P

X

P_DBRESET#

D

X

P_TMS

D

X

D

P_TDI_R

X

P_PREQ#

D

X

D

P_TDO_R

X

D

P_TCLK

X

D

P_TRST#

LL CONFIDENTIAL/PROPRIETARY

E

C

C

C

C

G16

F

4

C

G17

F

6

8

CF

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

1 2

109 0_0402_5%~D@

109 0_0402_5%~D@

H

H

1 2

H

H

108 0_0402_5%~D@

108 0_0402_5%~D@

o

o

o

v

v

v

I

I

I

L

L

L

G0_R

C

G1_R

F

C

G2

F

C

G3

F

C

F

G8

C

F

G9

C

G4

F

C

G5_R

F

C

G6

F

C

G7

F

C

K_XDP

L

C

K_XDP#

L

X

DP_RST#_R

X

P_DBRESET#

D

X

P_TDO

D

X

P_TRST#_R

D

X

P_TDI

D

X

P_TMS_R

D

19 1K_0402_5%~D

19 1K_0402_5%~D

C

C

R

R

C

C

R

R

C

C

R

R

C

C

R

R

C

C

R

R

R

R

C

C

R

R

C

C

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

y Bridge (1/6)

y Bridge (1/6)

y Bridge (1/6)

-7781

A

A

A

-7781

-7781

12

27 51_0402_1%~D

27 51_0402_1%~D

12

29 51_0402_1%~D

29 51_0402_1%~D

12

32 51_0402_1%~D@

32 51_0402_1%~D@

12

35 51_0402_1%~D

35 51_0402_1%~D

12

40

40

12

51_0402_1%~D

1

51_0402_1%~D

12

51_0402_1%~D

51_0402_1%~D

41

41

F

G16 <9>

C

F

G17 <9>

C

C

G0_R <9>

F

G1_R <9>

F

C

C

F

G2 <9>

C

G3 <9>

F

F

G8 <9>

C

G9 <9>

F

C

C

G4 <9>

F

C

G5_R <9>

F

C

F

G6 <9>

G7 <9>

F

C

TRST_XDP# <17>

L

P

K_CPU_ITP <15>

L

C

K_CPU_ITP# <15>

L

C

+

3

+

.05V_RUN_VTT

1

7

7

7

o

o

o

.3V_RUN

f

f

f

0

.

.

.

0

0

1

1

1

1Friday, February 24, 2012

1Friday, February 24, 2012

6

6

6

1Friday, February 24, 2012

Page 8

5

JC

JC

PU1C

PU1C

D D

C C

B B

R_A_D[0..63]<12>

D

D

D

R_A_BS0<12>

D

D

R_A_BS1<12>

D

DR_A_BS2<12>

D

D

R_A_CAS#<12>

D

D

R_A_RAS#<12>

D

DR_A_WE#<12>

D

D

D

D

D

D

D

D

D

D

D

D

D

D

DR_A_D6

D

D

D

D

D

D

D

D

D

D

D

DR_A_D12

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

DR_A_D38

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

D

R_A_BS0

D

D

R_A_BS1

D

D

D

R_A_BS2

D

D

R_A_CAS#

D

R_A_RAS#

D

D

R_A_WE#

D

R_A_D0

R_A_D1

R_A_D2

R_A_D3

R_A_D4

R_A_D5

R_A_D7

R_A_D8

R_A_D9

R_A_D10

R_A_D11

R_A_D13

R_A_D14

R_A_D15

R_A_D16

R_A_D17

R_A_D18

R_A_D19

R_A_D20

R_A_D21

R_A_D22

R_A_D23

R_A_D24

R_A_D25

R_A_D26

R_A_D27

R_A_D28

R_A_D29

R_A_D30

R_A_D31

R_A_D32

R_A_D33

R_A_D34

R_A_D35

R_A_D36

R_A_D37

R_A_D39

R_A_D40

R_A_D41

R_A_D42

R_A_D43

R_A_D44

R_A_D45

R_A_D46

R_A_D47

R_A_D48

R_A_D49

R_A_D50

R_A_D51

R_A_D52

R_A_D53

R_A_D54

R_A_D55

R_A_D56

R_A_D57

R_A_D58

R_A_D59

R_A_D60

R_A_D61

R_A_D62

R_A_D63

AP11

AN11

AL12

AM12

AM11

AL11

AP12

AN12

AJ14

AH14

AL15

AK15

AL14

AK14

AJ15

AH15

AE10

AF10

G10

N10

M10

AG6

AG5

AK6

AK5

AH5

AH6

AK8

AK9

AH8

AH9

AE8

AD9

AF9

C5

S

_DQ[0]

A

D5

S

A

_DQ[1]

D3

S

_DQ[2]

A

D2

S

_DQ[3]

A

D6

S

_DQ[4]

A

C6

S

_DQ[5]

A

C2

S

A

_DQ[6]

C3

S

A

_DQ[7]

F10

S

A

_DQ[8]

F8

S

_DQ[9]

A

S

_DQ[10]

A

G9

S

_DQ[11]

A

F9

S

_DQ[12]

A

F7

S

A

_DQ[13]

G8

S

A

_DQ[14]

G7

S

A

_DQ[15]

K4

S

A

_DQ[16]

K5

S

_DQ[17]

A

K1

S

_DQ[18]

A

J1

S

_DQ[19]

A

J5

S

A

_DQ[20]

J4

S

A

_DQ[21]

J2

S

A

_DQ[22]

K2

S

A

_DQ[23]

M8

S

_DQ[24]

A

S

_DQ[25]

A

N8

S

A

_DQ[26]

N7

S

A

_DQ[27]

S

_DQ[28]

A

M9

S

_DQ[29]

A

N9

S

_DQ[30]

A

M7

S

A

_DQ[31]

S

A

_DQ[32]

S

_DQ[33]

A

S

_DQ[34]

A

S

_DQ[35]

A

S

A

_DQ[36]

S

A

_DQ[37]

AJ5

S

A

_DQ[38]

AJ6

S

_DQ[39]

A

AJ8

S

A_DQ[40]

S

A

_DQ[41]

AJ9

S

A

_DQ[42]

S

_DQ[43]

A

S

_DQ[44]

A

S

A

_DQ[45]

AL9

S

A

_DQ[46]

AL8

S

_DQ[47]

A

S

_DQ[48]

A

S

A

_DQ[49]

S

A

_DQ[50]

S

_DQ[51]

A

S

_DQ[52]

A

S

_DQ[53]

A

S

A

_DQ[54]

S

_DQ[55]

A

S

_DQ[56]

A

S

A

_DQ[57]

S

A

_DQ[58]

S

_DQ[59]

A

S

A

_DQ[60]

S

A

_DQ[61]

S

_DQ[62]

A

S

A

_DQ[63]

_BS[0]

SA

SA

_BS[1]

V6

SA_BS[2]

_CAS#

SA

SA

_RAS#

SA

_WE#

4

CLK_DDR0

_

M

AB6

S

_CK[0]

A

_CLK#[0]

SA

S

_CKE[0]

A

SA

_CK[1]

SA

_CLK#[1]

SA

_CKE[1]

S

A

_CK[2]

S

A

_CLK#[2]

S

_CKE[2]

A

S

A

_CK[3]

S

A

_CLK#[3]

S

_CKE[3]

A

S

_CS#[0]

A

S

_CS#[1]

A

S

_CS#[2]

A

S

A

_CS#[3]

S

_ODT[0]

A

S

_ODT[1]

A

S

A

_ODT[2]

S

_ODT[3]

A

S

A

_DQS#[0]

S

_DQS#[1]

A

S

_DQS#[2]

A

S

_DQS#[3]

A

S

A

_DQS#[4]

S

A

_DQS#[5]

S

_DQS#[6]

A

S

_DQS#[7]

A

S

_DQS[0]

A

S

_DQS[1]

A

S

_DQS[2]

A

S

A

_DQS[3]

S

A

_DQS[4]

S

_DQS[5]

A

S

A

_DQS[6]

S

A

_DQS[7]

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

S

_MA[0]

A

S

_MA[1]

A

S

A

_MA[2]

S

A

_MA[3]

S

A

_MA[4]

S

_MA[5]

A

S

_MA[6]

A

S

A

_MA[7]

S

A

_MA[8]

S

A

_MA[9]

S

A

_MA[10]

S

_MA[11]

A

S

_MA[12]

A

S

_MA[13]

A

S

_MA[14]

A

S

_MA[15]

A

AA6

V9

AA5

AB5

V10

AB4

AA4

W9

AB3

AA3

W10

AK3

AL3

AG1

AH1

AH3

AG3

AG2

AH2

C4

G6

J3

M6

AL6

AM8

AR12

AM15

D4

F6

K3

N6

AL5

AM9

AR11

AM14

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

CLK_DDR#0

_

M

D

R_CKE0_DIMMA

D

_

CLK_DDR1

M

CLK_DDR#1

_

M

D

R_CKE1_DIMMA

D

R_CS0_DIMMA#

D

D

D

R_CS1_DIMMA#

D

ODT0

_

M

ODT1

_

M

D

R_A_DQS#0

D

D

R_A_DQS#1

D

R_A_DQS#2

D

D

R_A_DQS#3

D

D

R_A_DQS#4

D

D

R_A_DQS#5

D

D

R_A_DQS#6

D

D

R_A_DQS#7

D

D

R_A_DQS0

D

D

R_A_DQS1

D

D

R_A_DQS2

D

D

D

R_A_DQS3

D

R_A_DQS4

D

D

D

R_A_DQS5

D

R_A_DQS6

D

D

R_A_DQS7

D

D

D

R_A_MA0

D

D

R_A_MA1

D

R_A_MA2

D

D

D

R_A_MA3

D

D

R_A_MA4

D

R_A_MA5

D

D

D

R_A_MA6

D

D

R_A_MA7

D

R_A_MA8

D

D

D

R_A_MA9

D

R_A_MA10

D

D

R_A_MA11

D

D

D

R_A_MA12

D

R_A_MA13

D

D

D

R_A_MA14

D

D

R_A_MA15

D

CLK_DDR0 <12>

M_

CLK_DDR#0 <12>

M_

D

R_CKE0_DIMMA <12>

D

CLK_DDR1 <12>

_

M

_CLK_DDR#1 <12>

M

R_CKE1_DIMMA <12>

D

D

R_CS0_DIMMA# <12>

D

D

R_CS1_DIMMA# <12>

D

D

ODT0 <12>

_

M

ODT1 <12>

_

M

R_A_DQS#[0..7] <12>

D

D

R_A_DQS[0..7] <12>

D

D

R_A_MA[0..15] <12>

D

D

3

D

R_B_D[0..63]<13>

D

R_B_BS0<13>

D

D

DR_B_BS1<13>

D

R_B_BS2<13>

D

D

D

R_B_CAS#<13>

D

DR_B_RAS#<13>

D

R_B_WE#<13>

D

D

D

R_B_D0

D

D

R_B_D1

D

D

R_B_D2

D

D

R_B_D3

D

D

D

R_B_D4

D

R_B_D5

D

R_B_D6

D

D

D

D

R_B_D7

D

D

R_B_D8

D

D

R_B_D9

D

D

R_B_D10

D

D

R_B_D11

D

D

R_B_D12

D

R_B_D13

D

D

R_B_D14

D

D

R_B_D15

D

R_B_D16

D

D

D

R_B_D17

D

D

R_B_D18

D

D

R_B_D19

D

D

R_B_D20

D

D

R_B_D21

D

D

R_B_D22

D

R_B_D23

D

D

R_B_D24

D

D

D

R_B_D25

D

D

R_B_D26

D

D

R_B_D27

D

R_B_D28

D

D

D

R_B_D29

D

D

R_B_D30

D

D

R_B_D31

D

D

D

R_B_D32

D

R_B_D33

D

D

R_B_D34

D

D

D

R_B_D35

D

D

R_B_D36

D

R_B_D37

D

D

R_B_D38

D

D

R_B_D39

D

D

D

R_B_D40

D

R_B_D41

D

D

D

R_B_D42

D

R_B_D43

D

D

DR_B_D44

D

R_B_D45

D

D

R_B_D46

D

D

D

R_B_D47

D

D

R_B_D48

D

R_B_D49

D

D

R_B_D50

D

D

DR_B_D51

D

D

R_B_D52

D

R_B_D53

D

D

R_B_D54

D

D

D

R_B_D55

D

R_B_D56

D

D

D

R_B_D57

D

D

R_B_D58

D

R_B_D59

D

D

R_B_D60

D

D

R_B_D61

D

D

D

R_B_D62

D

R_B_D63

D

R_B_BS0

D

D

D

D

R_B_BS1

D

D

R_B_BS2

D

R_B_CAS#

D

D

D

R_B_RAS#

D

R_B_WE#

D

AM5

AM6

AJ11

AH11

AJ12

AH12

AT11

AN14

AR14

AT14

AT12

AN15

AR15

AT15

AA10

D10

K10

AR3

AP3

AN3

AN2

AN1

AP2

AP5

AN9

AT5

AT6

AP6

AN8

AR6

AR5

AR9

AT8

AT9

AR8

AA9

AA7

AB8

AB9

2

J

J

PU1D

PU1D

C

C

CLK_DDR2

_

M

AE2

S

_CK[0]

B

S

B

C9

_DQ[0]

B

S

A7

B

_DQ[1]

S

B

_DQ[2]

S

C8

_DQ[3]

B

S

A9

_DQ[4]

B

S

A8

B

_DQ[5]

S

D9

B

_DQ[6]

S

D8

B

_DQ[7]

S

G4

B

_DQ[8]

S

F4

_DQ[9]

B

S

F1

_DQ[10]

B

S

G1

_DQ[11]

B

S

G5

B

_DQ[12]

S

F5

B

_DQ[13]

S

F2

B

_DQ[14]

S

G2

B

_DQ[15]

S

J7

_DQ[16]

B

S

J8

_DQ[17]

B

S

_DQ[18]

B

S

K9

_DQ[19]

B

S

J9

_DQ[20]

B

S

J10

B

_DQ[21]

S

K8

B

_DQ[22]

S

K7

B

_DQ[23]

S

M5

B

_DQ[24]

S

N4

_DQ[25]

B

S

N2

B_DQ[26]

S

N1

_DQ[27]

B

S

M4

_DQ[28]

B

S

N5

_DQ[29]

B

S

M2

_DQ[30]

B

S

M1

B

_DQ[31]

S

_DQ[32]

B

S

B

_DQ[33]

S

B

_DQ[34]

S

B

_DQ[35]

S

B

_DQ[36]

S

B

_DQ[37]

S

B

_DQ[38]

S

B

_DQ[39]

S

_DQ[40]

B

S

B

_DQ[41]

S

_DQ[42]

B

S

_DQ[43]

B

S

_DQ[44]

B

S

_DQ[45]

B

S

_DQ[46]

B

S

_DQ[47]

B

S

_DQ[48]

B

S

_DQ[49]

B

S

_DQ[50]

B

S

_DQ[51]

B

S

_DQ[52]

B

S

_DQ[53]

B

S

_DQ[54]

B

S

_DQ[55]

B

S

_DQ[56]

B

S

_DQ[57]

B

S

_DQ[58]

B

S

_DQ[59]

B

S

_DQ[60]

B

S

_DQ[61]

B

S

_DQ[62]

B

S

_DQ[63]

B

S

S

B

_BS[0]

S

_BS[1]

B

R6

S

B

_BS[2]

S

_CAS#

B

S

B

_RAS#

S

_WE#

B

_CLK#[0]

S

B

_CKE[0]

S

_CK[1]

B

S

_CLK#[1]

B

S

B

_CKE[1]

B

_CK[2]

S

B

_CLK#[2]

S

B_CKE[2]

S

_CK[3]

B

S

_CLK#[3]

B

S

_CKE[3]

B

S

B

_CS#[0]

S

B

_CS#[1]

S

B

_CS#[2]

S

B

_CS#[3]

S

S

_ODT[0]

B

S

B

_ODT[1]

_ODT[2]

B

S

_ODT[3]

B

S

S

_DQS#[0]

B

S

B

_DQS#[1]

S

B

_DQS#[2]

_DQS#[3]

B

S

S

_DQS#[4]

B

S

B

_DQS#[5]

S

_DQS#[6]

B

S

_DQS#[7]

B

S

B

_DQS[0]

S

B

_DQS[1]

S

_DQS[2]

B

B

_DQS[3]

S

S

B

_DQS[4]

S

_DQS[5]

B

S

_DQS[6]

B

DR SYSTEM MEMORY B

DR SYSTEM MEMORY B

S

B

_DQS[7]

D

D

B

_MA[0]

S

B

_MA[1]

S

B

_MA[2]

S

_MA[3]

B

S

B

_MA[4]

S

_MA[5]

B

S

_MA[6]

B

S

_MA[7]

B

S

_MA[8]

B

S

B

_MA[9]

S

_MA[10]

B

S

B

_MA[11]

S

B

_MA[12]

S

B

_MA[13]

S

B

_MA[14]

S

_MA[15]

B

S

AD2

R9

AE1

AD1

R10

AB2

AA2

T9

AA1

AB1

T10

AD3

AE3

AD6

AE6

AE4

AD4

AD5

AE5

D7

F3

K6

N3

AN5

AP9

AK12

AP15

C7

G3

J6

M3

AN6

AP8

AK11

AP14

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

CLK_DDR#2

_

M

R_CKE2_DIMMB

D

D

CLK_DDR3

_

M

CLK_DDR#3

_

M

R_CKE3_DIMMB

D

D

R_CS2_DIMMB#

D

D

R_CS3_DIMMB#

D

D

ODT2

_

M

ODT3

_

M

R_B_DQS#0

D

D

D

R_B_DQS#1

D

D

R_B_DQS#2

D

R_B_DQS#3

D

D

R_B_DQS#4

D

D

D

R_B_DQS#5

D

R_B_DQS#6

D

D

DR_B_DQS#7

D

R_B_DQS0

D

D

D

R_B_DQS1

D

D

R_B_DQS2

D

R_B_DQS3

D

D

R_B_DQS4

D

D

D

R_B_DQS5

D

R_B_DQS6

D

D

D

R_B_DQS7

D

R_B_MA0

D

D

D

R_B_MA1

D

D

R_B_MA2

D

D

R_B_MA3

D

R_B_MA4

D

D

D

R_B_MA5

D

D

R_B_MA6

D

R_B_MA7

D

D

R_B_MA8

D

D

R_B_MA9

D

D

D

R_B_MA10

D

DR_B_MA11

D

R_B_MA12

D

D

D

R_B_MA13

D

D

R_B_MA14

D

R_B_MA15

D

D

1

_

CLK_DDR2 <13>

M

M_

CLK_DDR#2 <13>

DD

R_CKE2_DIMMB <13>

CLK_DDR3 <13>

M_

_

CLK_DDR#3 <13>

M

D

R_CKE3_DIMMB <13>

D

R_CS2_DIMMB# <13>

D

D

D

R_CS3_DIMMB# <13>

D

ODT2 <13>

_

M

_

ODT3 <13>

M

R_B_DQS#[0..7] <13>

D

D

R_B_DQS[0..7] <13>

D

D

R_B_MA[0..15] <13>

D

D

TYCO_2013620-3_IVYBRIDGE

TYCO_2013620-3_IVYBRIDGE

TYCO_2013620-3_IVYBRIDGE

A A

ROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

P

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

TYCO_2013620-3_IVYBRIDGE

2

LL CONFIDENTIAL/PROPRIETARY

E

D

mpal Electronics, Inc.

o

o

o

mpal Electronics, Inc.

mpal Electronics, Inc.

C

C

tle

i

i

i

tle

tle

T

T

T

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

C

y Bridge (1/6)

v

v

v

y Bridge (1/6)

y Bridge (1/6)

I

I

I

-7781

A

A

A

-7781

-7781

L

L

L

1Friday, February 24, 2012

6

6

6

1Friday, February 24, 2012

8

8

8

1

1Friday, February 24, 2012

f

f

f

o

o

o

0

.

.

.

0

0

1

1

1

Page 9

5

D D

C

F

G0_R<7>

C

F

G1_R<7>

C

G5_R<7>

F

+

CC_GFXCORE

V

V

XG_VAL_SENSE

1 2

R

R

C

C

122 49.9_0402_ 1%~D@

122 49.9_0402_ 1%~D@

CC_CORE

V

C

C

R

R

R

R

C

C

R

R

C

C

1 2

123 49.9_0402_ 1%~D@

123 49.9_0402_ 1%~D@

1 2

120 49.9_0402_ 1%~D@

120 49.9_0402_ 1%~D@

1 2

121 49.9_0402_ 1%~D@

121 49.9_0402_ 1%~D@

C C

+

B B

A

12

@

@

C

C

R

R

100_0402_1%~D

100_0402_1%~D

V

S

SAXG_VAL_SENSE

V

C_VAL_SNESE

C

12

C

C

@

@

R

R

100_0402_1%~D

100_0402_1%~D

V

S_VAL_SNESE

S

69

69

71

71

1 2

36 0_0402_5%~D@

36 0_0402_5%~D@

E

E

R

R

1 2

34 0_0402_5%~D@

34 0_0402_5%~D@

E

E

R

R

1 2

35 0_0402_5%~D@

35 0_0402_5%~D@

E

E

R

R

C

F

G2<7>

C

F

G3<7>

C

F

G4<7>

C

G6<7>

F

C

G7<7>

F

C

G8<7>

F

C

G9<7>

F

C

FG10<7>

C

F

G11<7>

9

9

PAD~D@

PAD~D@

T

T

0 PAD~D@

0 PAD~D@

1

1

T

T

T

T

1

1

2 PAD~D@

2 PAD~D@

4 PAD~D@

4 PAD~D@

1

1

T

T

C

G16<7>

F

C

G17<7>

F

2PAD~D @

2PAD~D @

2

2

T

T

2

2

8PAD~D @

8PAD~D @

T

T

T

T

2

2

9PAD~D @

9PAD~D @

0PAD~D @

0PAD~D @

3

3

T

T

3

3

1PAD~D @

1PAD~D @

T

T

T

T

3PAD~D @

3

3

3PAD~D @

T

T

5PAD~D @

3

35PAD~D @

T

T

3

3

6PAD~D @

6PAD~D @

T

T

3

7PAD~D @

7PAD~D @

3

T

T

8PAD~D @

3

3

8PAD~D @

T

T

4

4

0PAD~D @

0PAD~D @

4

4

1PAD~D @

1PAD~D @

T

T

T

T

2PAD~D @

2PAD~D @

4

4

T

T

4

4

3PAD~D @

3PAD~D @

T

T

4PAD~D @

4PAD~D @

4

4

5PAD~D @

4

4

5PAD~D @

T

T

T

T

6PAD~D @

4

4

6PAD~D @

7PAD~D @

7PAD~D @

4

4

T

T

8PAD~D @

4

4

8PAD~D @

T

T

T

T

2PAD~D @

2PAD~D @

5

5

4

C

FG0

C

G1

F

C

FG2

C

F

G3

C

F

G4

C

F

G5

C

F

G6

C

G7

F

C

G8

F

C

G9

F

C

G10

F

C

F

G11

C

F

G12

C

F

G13

C

F

G14

C

F

G15

C

F

G16

C

F

G17

V

XG_VAL_SENSE

A

V

SAXG_VAL_SENSE

S

V

C_VAL_SNESE

C

V

S_VAL_SNESE

S

AK28

AK29

AL26

AL27

AK26

AL29

AL30

AM31

AM32

AM30

AM28

AM26

AN28

AN31

AN26

AM27

AK31

AN29

AJ31

AH31

AJ33

AH33

AJ26

F25

F24

F23

D24

G25

G24

E23

D23

C30