Page 1

A

B

C

D

E

ϯD>>EϭϯΗhD

COMPAL CONFIDENTIAL

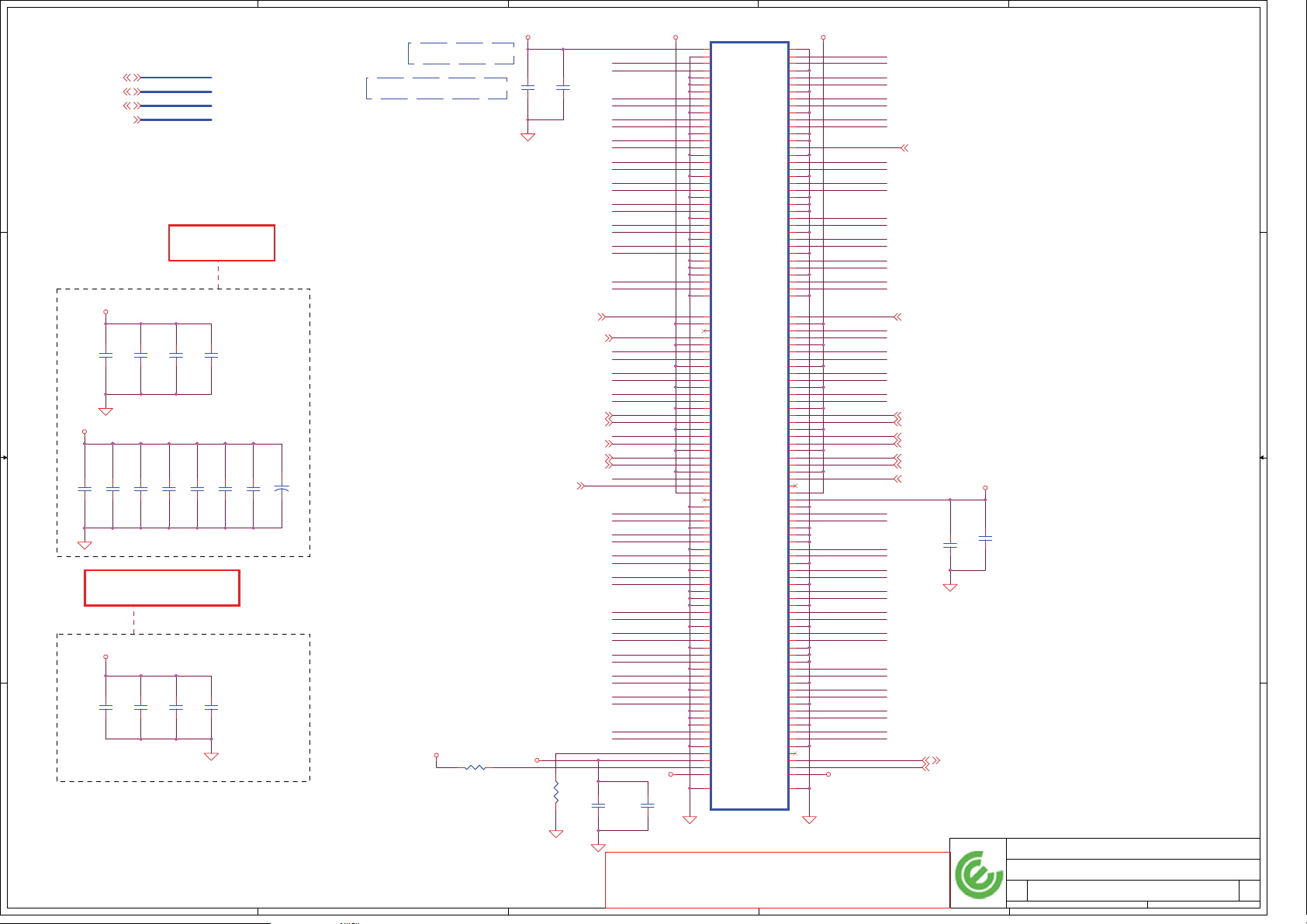

BGA Sandy Bridge +

PAL70

1 1

PCB NO :

BOM P/N :

O MAP Version 1010

GPI

MODEL NAM

E :

LA-6611P (DAA

43XXXXXXLXX

00001W10)

FCBGA PCH Cougar Point-M

2010-01-21

REV

: 1.0(A00)

Items R1 P/N R3 P/N

CPU 2.5G SA00004EL2L SA00004EL3L

CPU 2.6G SA00004EM2L SA00004EM3L

CPU 2.7G SA00004F02L SA00004F03L

CPU 2.1G SA00004KP1L SA00004KP2L

PCH SA00004IW2L SA00004IW3L

LAN SA00003SI4L SA00003SI5L

USH SA00003AO1L SA00003AO2L

@ : Nopop Component

DdLJƉĞ

Ϯϱ'WhdWDEdD/^td

2 2

Ϯϱ'WhdWDEdD/^t^W/

Ϯϱ'WhdWD/^dDE

Ϯϱ'WhdWD/^dDEt^W/

Ϯϱ'WhdWD/^dD/^

Ϯϱ'WhdWD/^dD^/t^W/

Ϯϲ'WhdWDEdD/^td

Ϯϲ'WhdWDEdD/^t^W/

Ϯϲ'WhdWD/^dDE

3 3

Ϯϲ'WhdWD/^dDEt^W/

Ϯϲ'WhdWD/^dD/^

Ϯϲ'WhdWD/^dD^/t^W/

Ϯϳ'WhdWDEdD/^td

Ϯϳ'WhdWDEdD/^t^W/

Ϯϳ'WhdWD/^dDE

Ϯϳ'WhdWD/^dDEt^W/

Ϯϳ'WhdWD/^dD/^

4 4

Ϯϳ'WhdWD/^dD^/t^W/

KDWE

ϰϯϭϵϯϰϯϭ>Ϭϲ

ϰϯϭϵϯϰϯϭ>Ϭϯ

ϰϯϭϵϯϰϯϭ>ϭϱ

ϰϯϭϵϯϰϯϭ>Ϭϳ

ϰϯϭϵϯϰϯϭ>Ϭϰ

ϰϯϭϵϯϰϯϭ>ϭϲ

ϰϯϭϵϯϰϯϭ>Ϭϴ

ϰϯϭϵϯϰϯϭ>Ϭϱ

ϰϯϭϵϯϰϯϭ>ϭϳ

ϭΛ ϮΛ

*

*

*

*

*

*

ϯΛ ϰΛ

*

*

*

*

*

*

*

*

*

*

*

*

**

**

*

*

**

**

*

*

**

**

*

*

dWD dD

tŝƚŚ^W/

ϱΛ

*

*

*

*

*

*

*

*

*

tŝƚŚd

ϲΛ

*

*

*

*

*

*

*

*

*

MB PC

MB PC

B

B

Part Number Description

Part Number Description

DAA00001W00

DAA00001W00

PCB PAL70 LA6611

PCB PAL70 LA6611

DELL CONFIDENTIAL/PROPRIETA

al Electronics, Inc.

al Electronics, Inc.

al Electronics, Inc.

Comp

Comp

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

A

B

C

D

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Comp

Cover

Cover

Cover

LA-6611P

LA-6611P

LA-6611P

nesday, January 26, 2011

nesday, January 26, 2011

nesday, January 26, 2011

Sheet

Sheet

Sheet

164Wed

164Wed

164Wed

E

RY

1.0

1.0

1.0

of

of

of

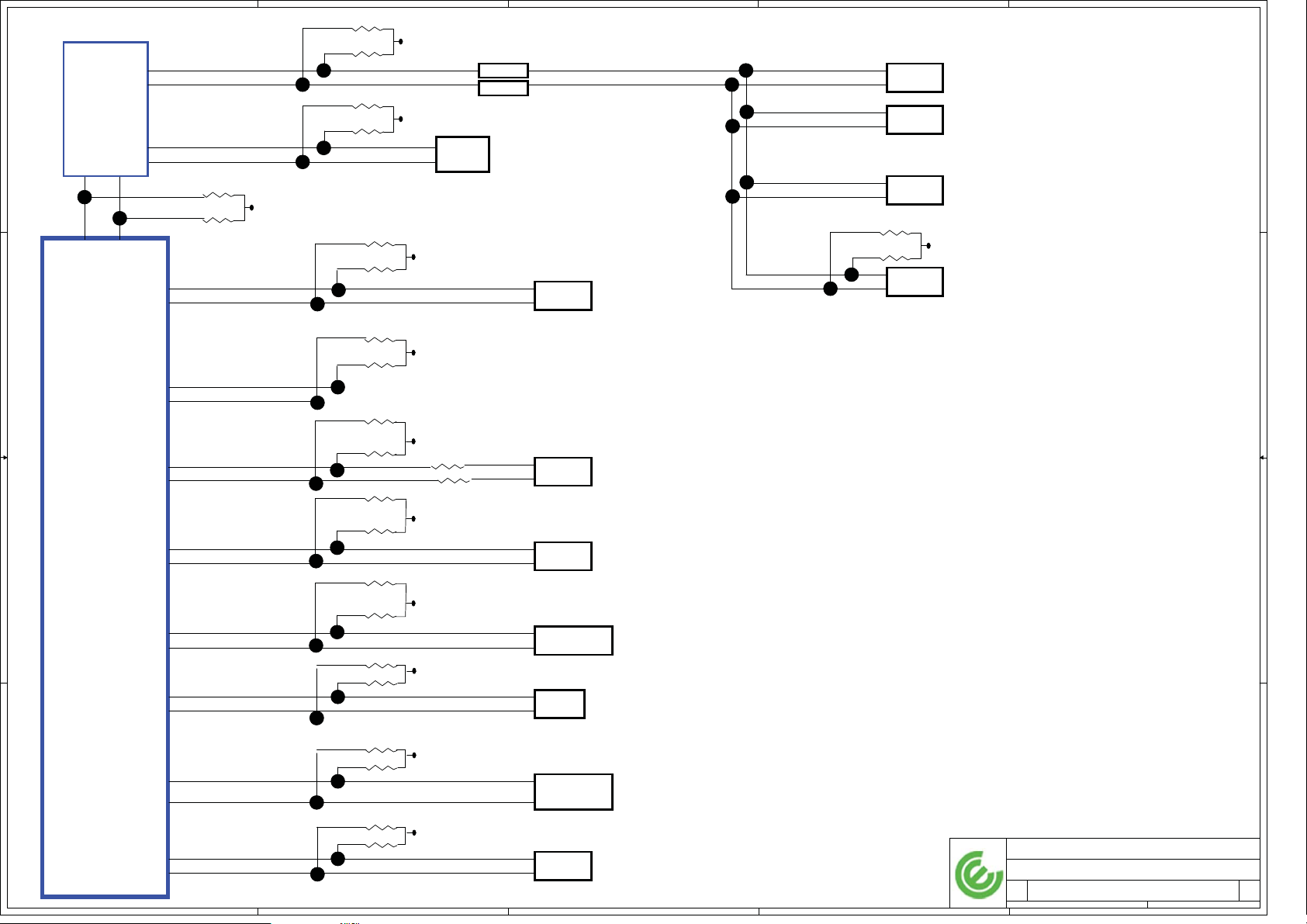

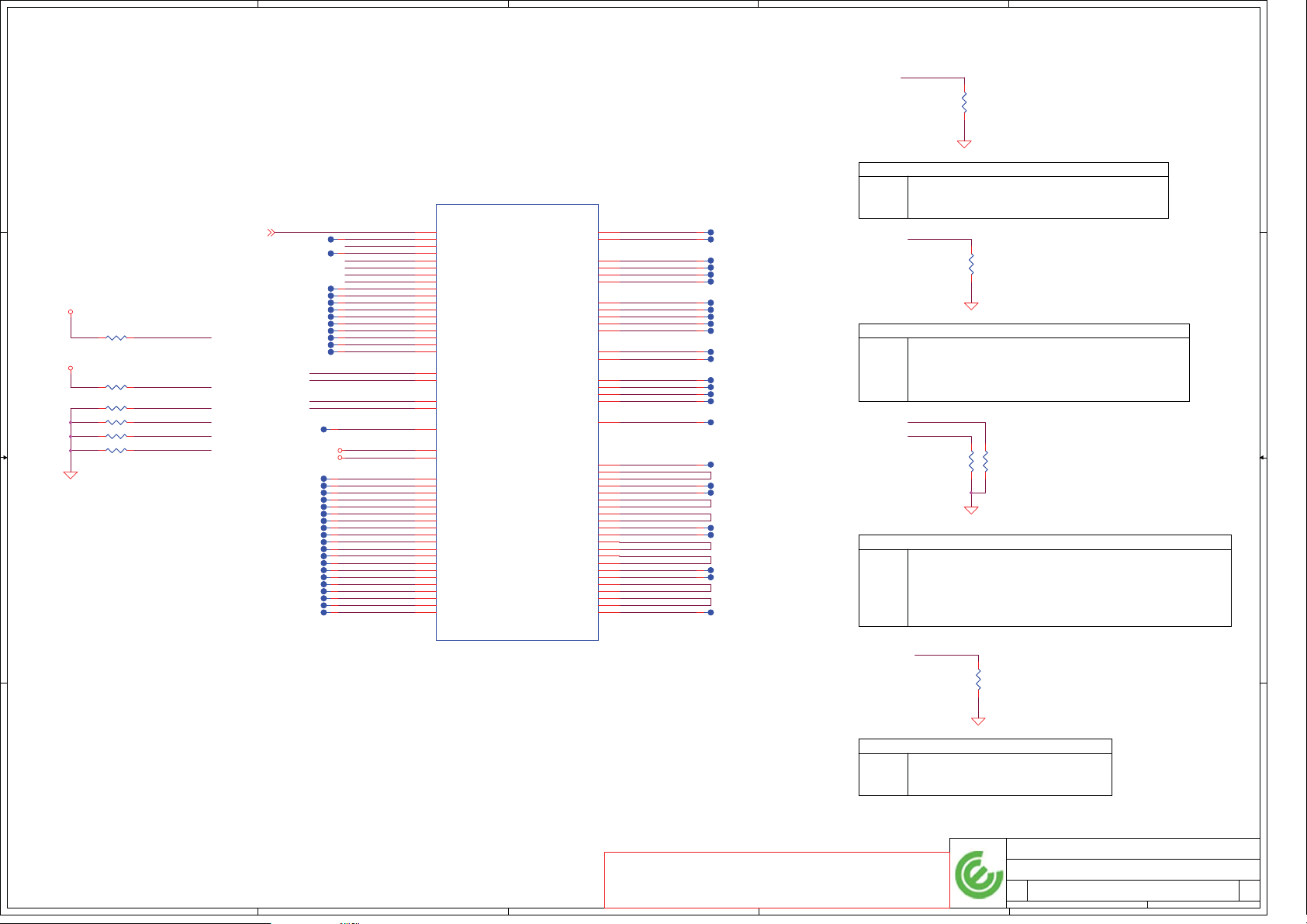

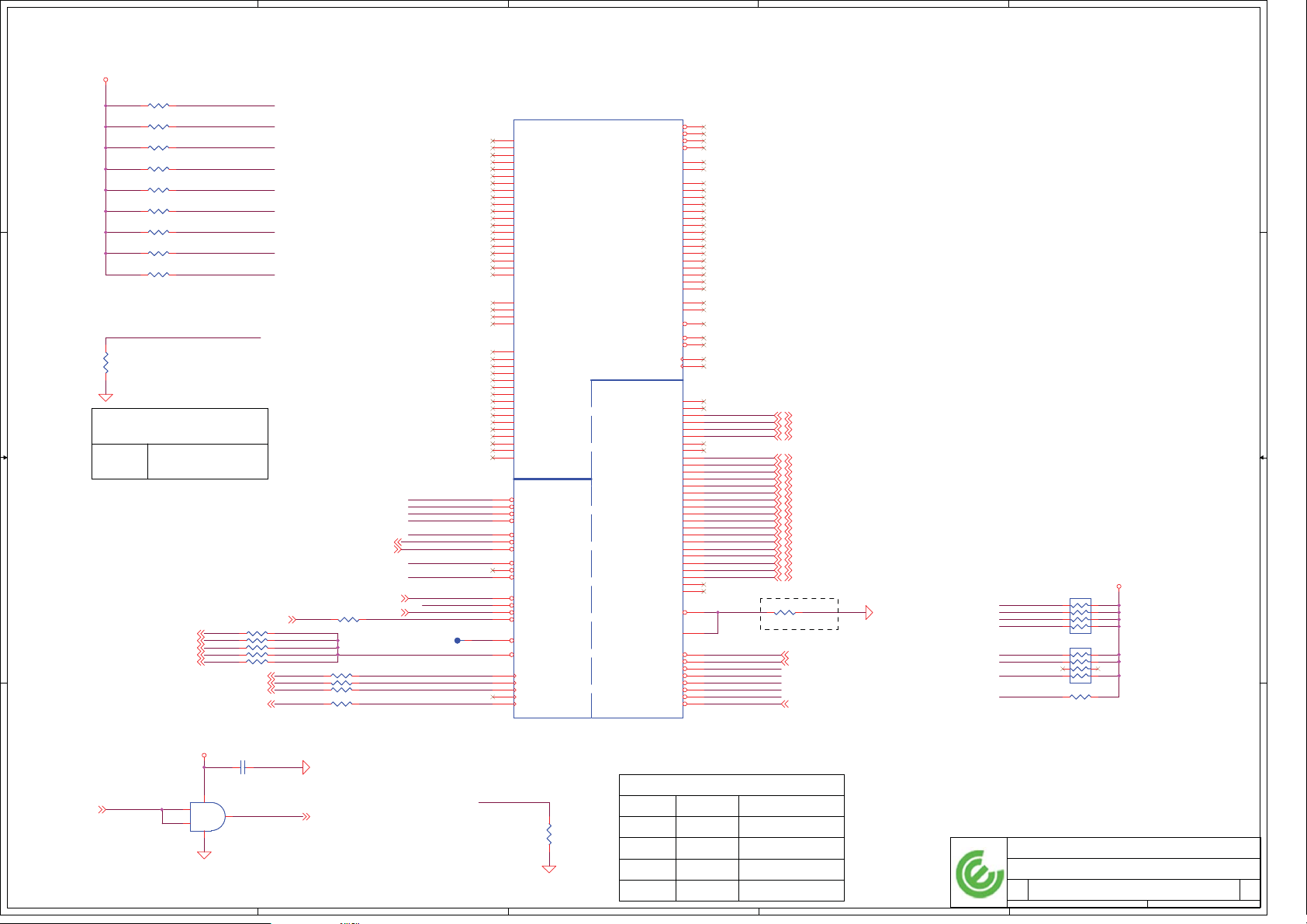

Page 2

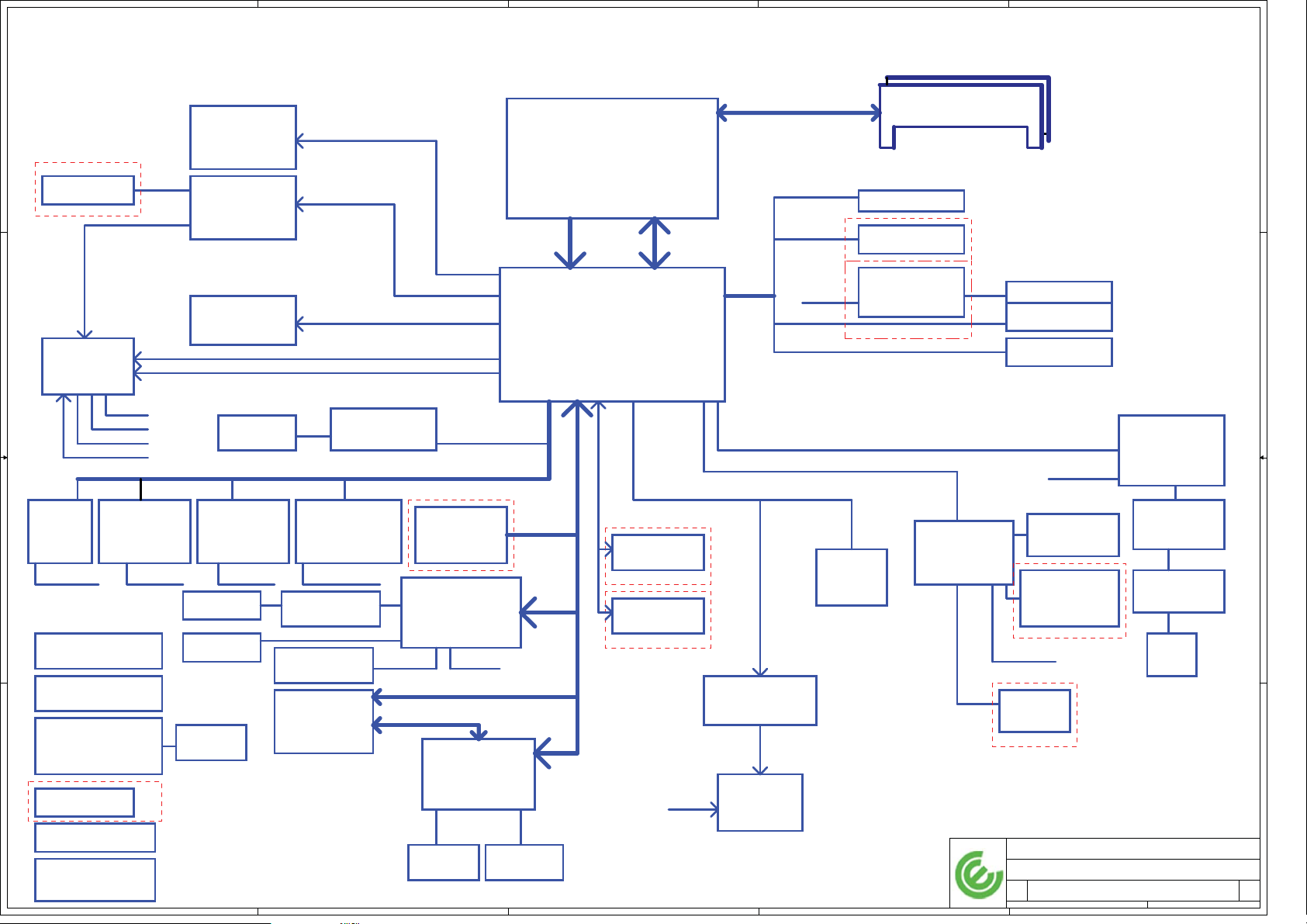

Block Diagram

A

Compal confidential

B

Model: PAL70

C

D

E

Memory BUS (DDR3)

1066/1333MH

1 1

Sandy B

idge

r

z

DDRIII-DIMM X2

BA

NK 0, 1, 2, 3, 4 ,5 ,6 ,7

page 12~13

LVDS CONN

page 24

CRT CONN

/K

VGA

2 2

3 3

DOCKING

RT

PO

page 41

DAI

USB

SATA

LAN

DOCK

ni Card

EXPRESS

Card

page 38 page 37page 37page 37

USB

CPU ITP Por

PCH ITP Por

1/2 Mi

page 7

page 14

Flas

USB

t

t

PCIE

h

Thermal

GUARDIAN III

EMC4022

4 4

WiFi ON/OFF

DC/DC Inte

Powe

SW & LED

page 45

r On/Off

page 46

page 22

/K

rface

A

For MB/Dock

Video Switch

PI3V712-AZLE

page 25

HDMI CONN

page 26

C

SDX

page 36 page 36

PCIE

ni Card

1/2 Mi

Smart

RFID

FAN

page 22

WLA

USB

Card

page 34

page 34

N

Card reader

OZ600FJ0LN

PCI Exp

PCIEPCIE

ini Card

Full M

TD

Fingerprint

CONN

WWAN

USB

A8034HN

page 34

page 23

/UWB

SMSC SIO

E5028

EC

page 42

ress BUS

Optio

FP_USB

BC BUS

B

LVDS

VGA

DPB

DP

C

DPD

PCIE x1

n

CB

SSX35B

page 35

TPM1

M5882

page 34~35

USB

.2

USH

BC

SMSC KBC

ME

C5055

page 43

page 44 page 44

KB CONNTP CONN

4MB (Socket

BGA CPU

1023 pins

COUGAR POIN

LPC BUSChina TPM1.2

FDI

x 8

Lane

INTEL

BGA

SP

I

G1)

page 6~11

DMI

x 4

Lane

USB

T-M

page 14~21

HD Audio I/F

S-ATA 0/1 6GB/s, S-ATA 2/3/4/5 3GB/s

page 14

ector

E

page 14

ector

PCIE

E

TA Repeater

SA

MAX4951BECTP+

Module

E-

page 29

page 29

W25X64Z

64M 4K s

W25X16Z

16M 4K s

C

SATA

PCI Exp

BT

Camera

SATA Repeater

MAX4951BECTP+

ress BUS

HDD

page 28

D

page 44

page 24

page 14

HDA Codec

92H

D

Troug

h LVDS Cable

E-SATA

USB

page 40

B

US

page 39

l Lewisville

Inte

DOCK LAN

T.Speaker

IN

page 30

82579LM

LAN

PI3L720

90B2

page 30

HeadPhone &

Tr

MIC Jack

/K

DAI

To Dock

ing side

Dig.

MIC

Trough LVDS Cable

DELL CONFIDENTIAL

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

Co

Co

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Co

UMA Block

UMA Block

UMA Block

LA

LA

LA

-6611P

-6611P

dnesday, January 26, 2011

dnesday, January 26, 2011

dnesday, January 26, 2011

-6611P

Diagram

Diagram

Diagram

E

page 32

SWITCH

page 32

ansformer

page 33

RJ4

5

page 33

/PROPRIETARY

264We

264We

264We

of

of

of

0.3

0.3

0.3

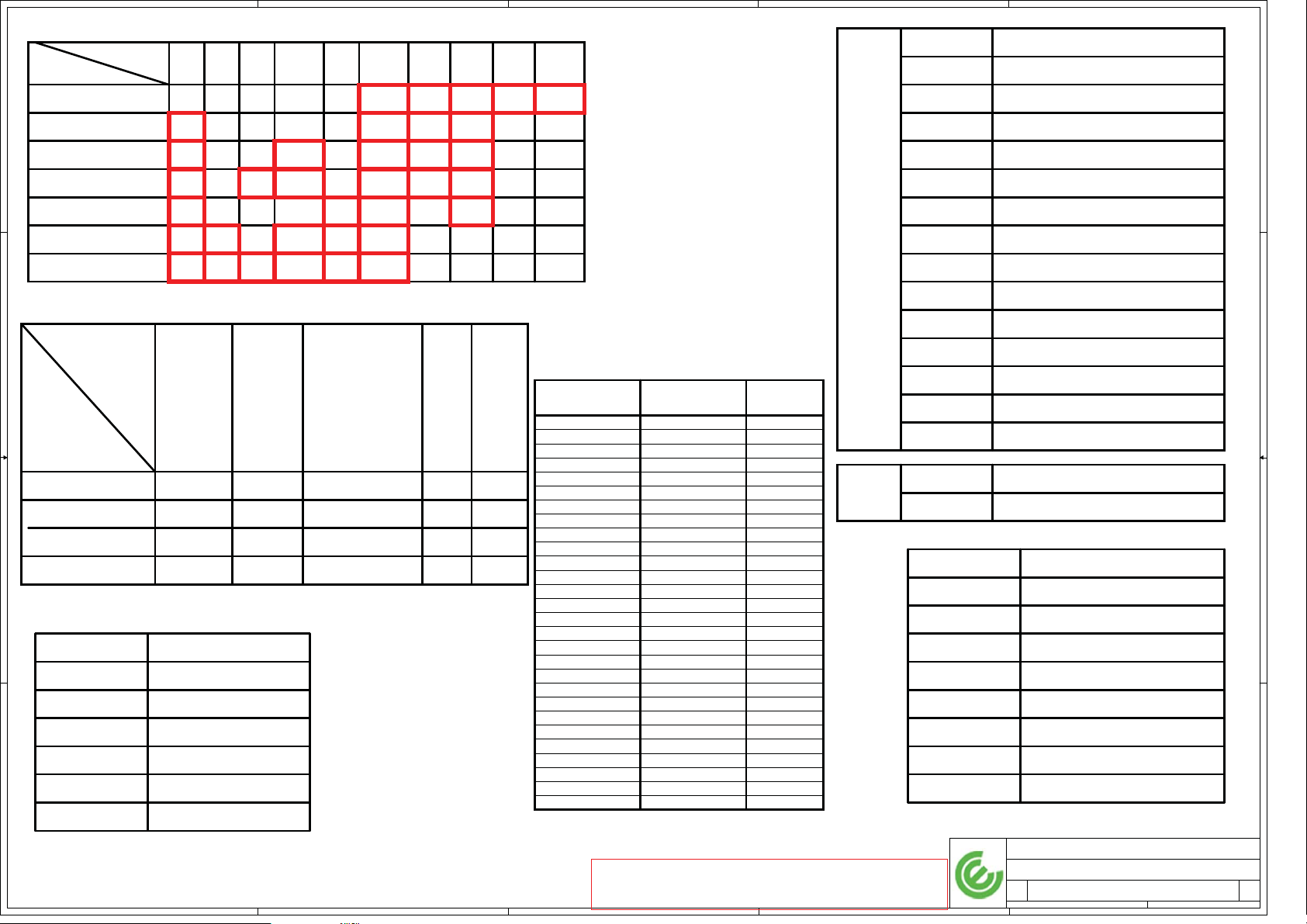

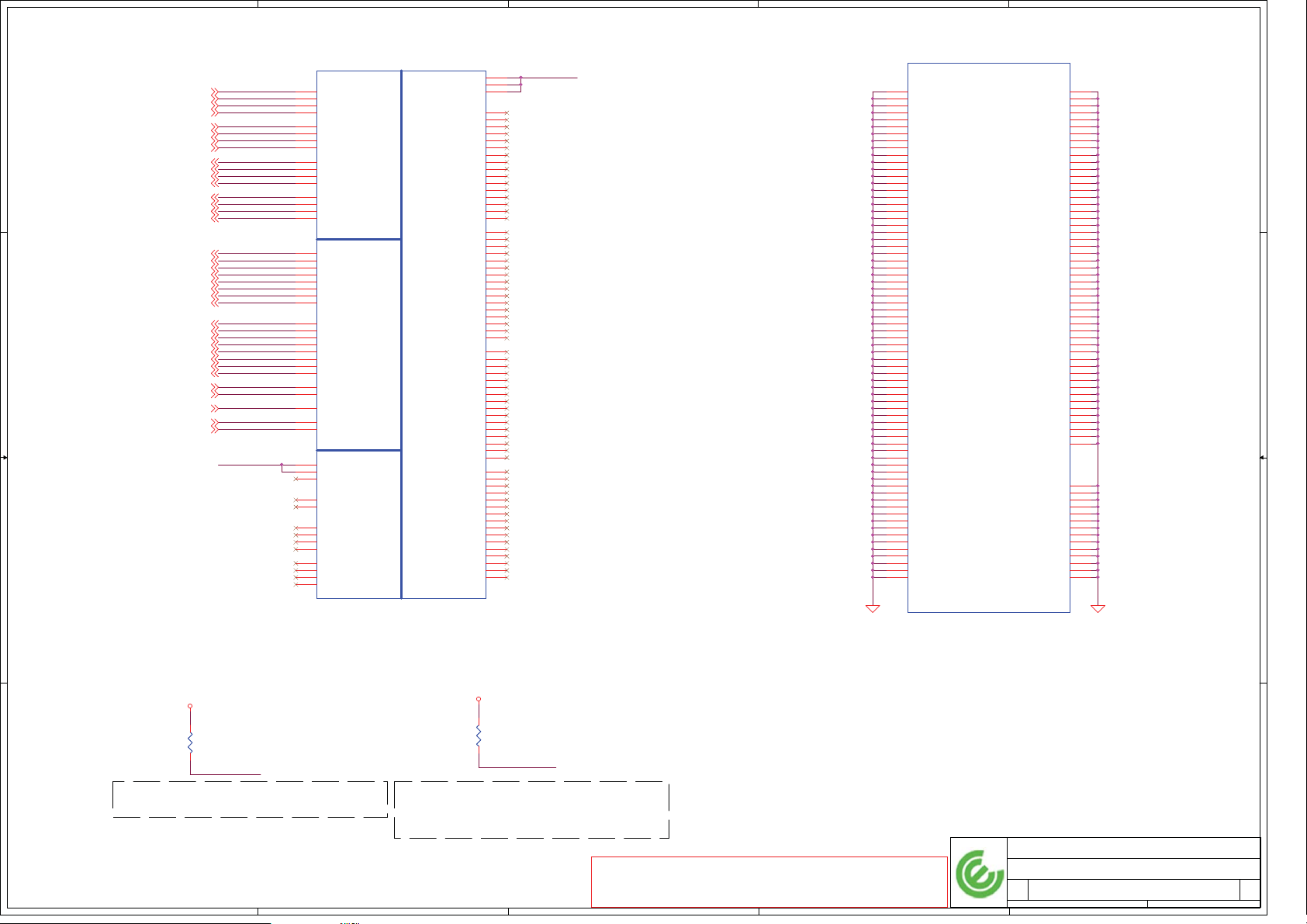

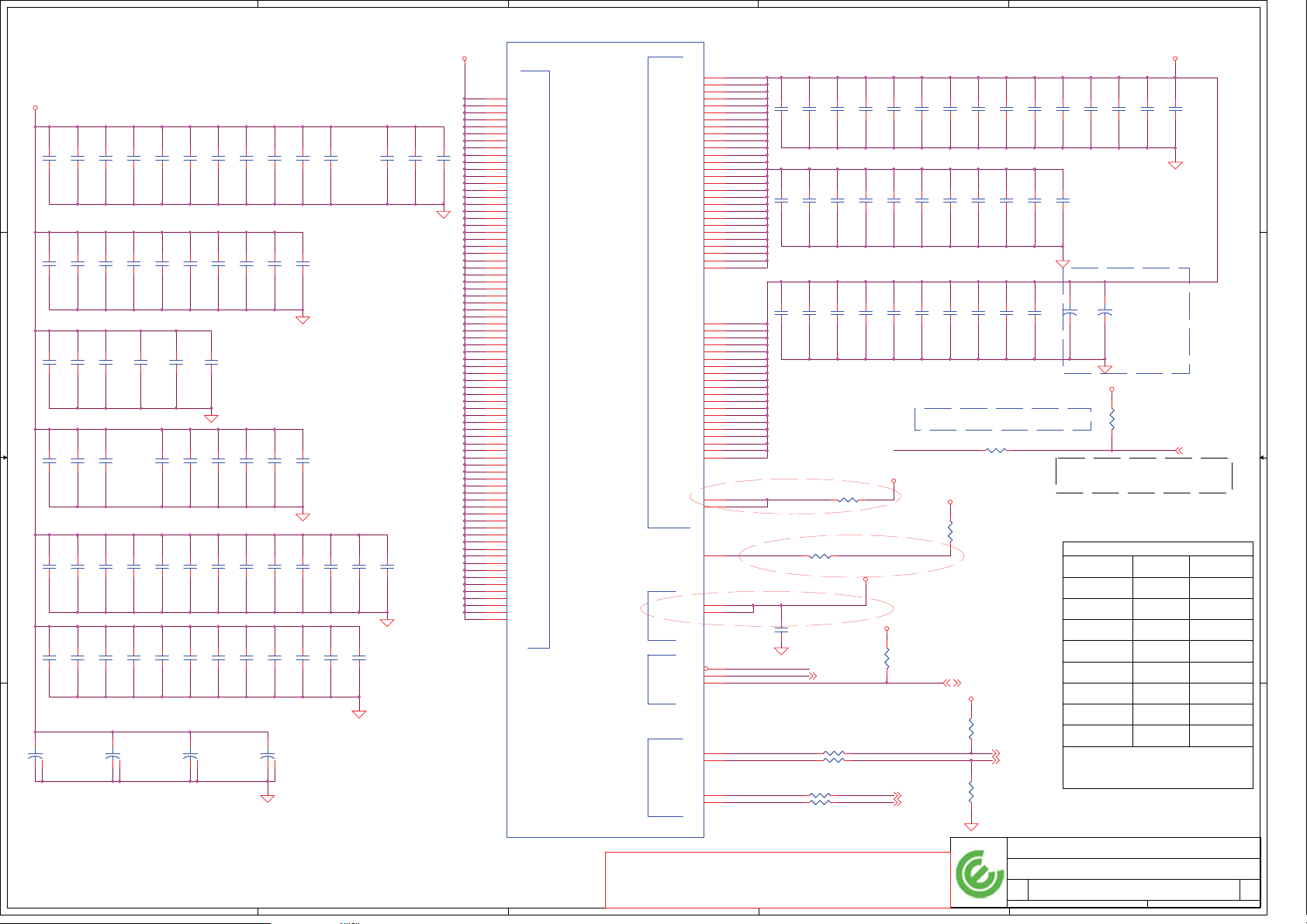

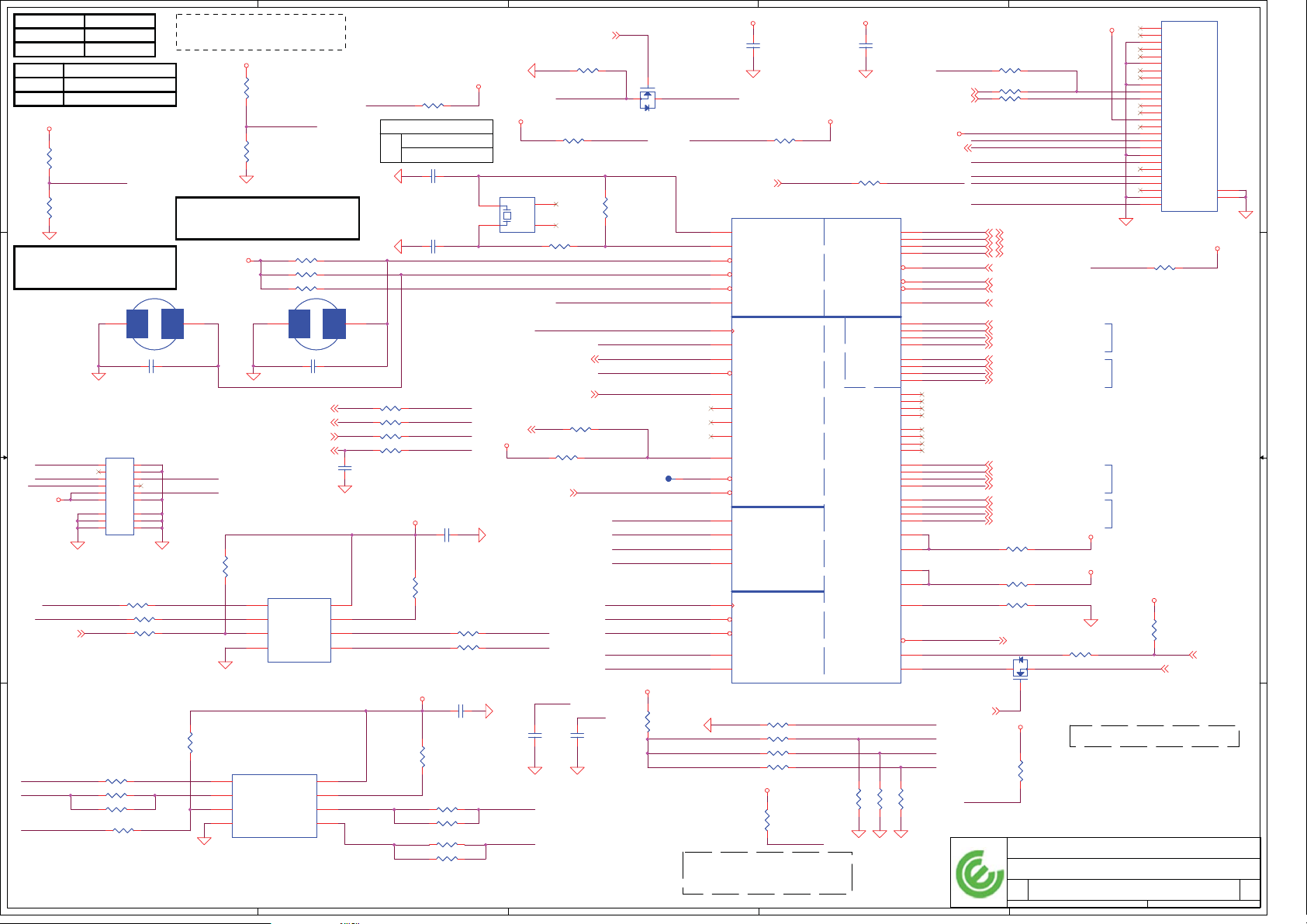

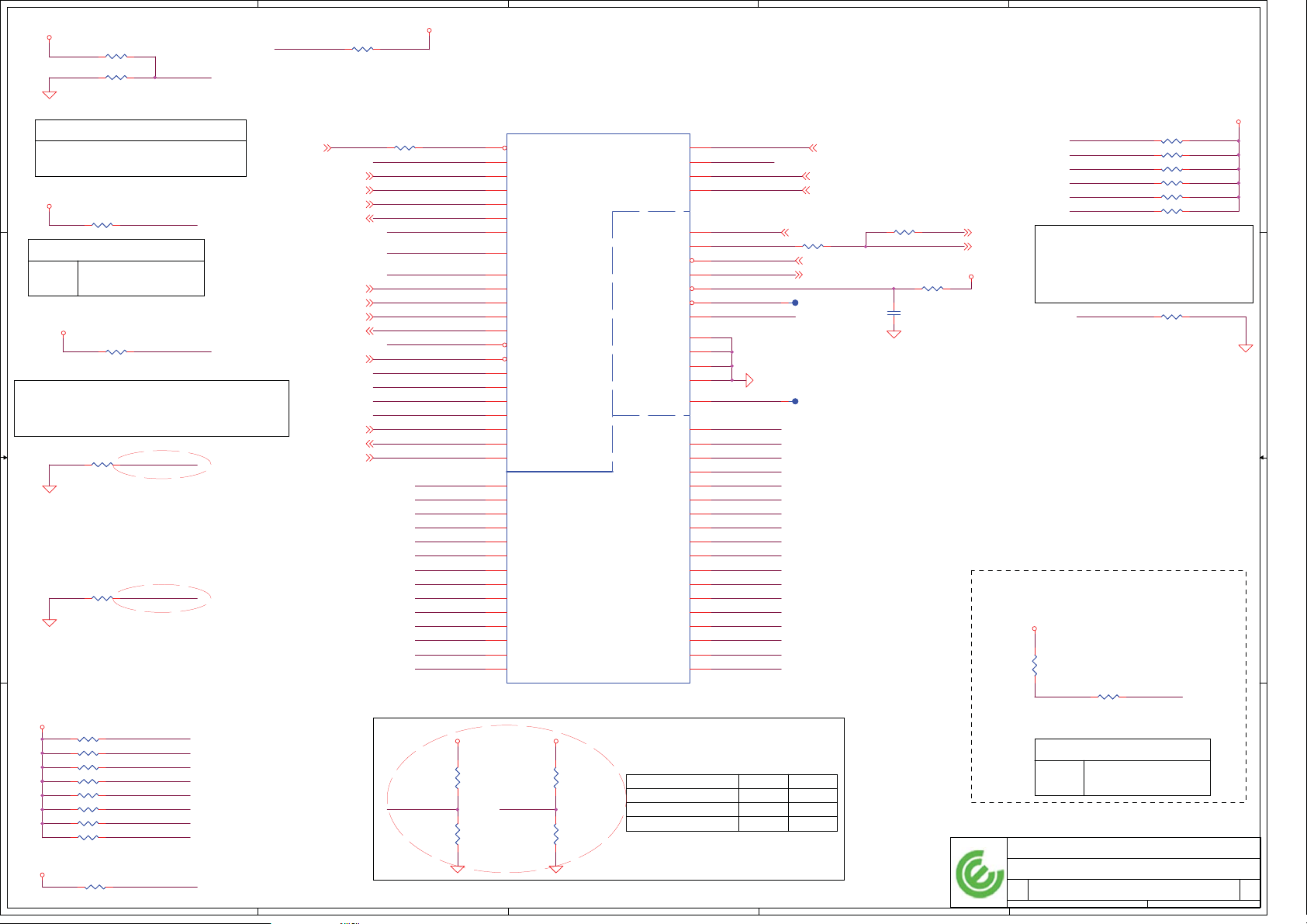

Page 3

5

4

3

2

1

State

ATES

Signal

SLP

SLP

SLP

#

S4#

S3

HIGH

HIGH

W HIGH HIGH HIGH ON ON ON OFF

LO

LOW

LOW HIGH HIGHLOW

LOW

LOW HIGH HIGH HIGH LOW ON ONOFF OFF OFF

LOW LOW LOW LOW ON OFF OFF OFF OFF

LOW LOW LOW LOW LOW ON OFF OFF OFF OFF

S4

S5#

STATE#

HIGH HIGH

HIG

H

SLP

M#

HIG

HIGH

H

ALWAYS

PLANE

ON

M

PLANE

ON

SUS

RUN

PLANE

PLANE

ON ON ON

OFF

OFF

CLOCKS

OFF

OFF

OFF

PCH

USB PORT#

0

1

2

3

4

5

6

7

DESTINA

T

ION

JUSB1 (Ext Right Side)

none

Right Side (ESA

TA)

none

WLAN/WIMAX

WWAN/UWB

Flash

USH->BIO

POWER ST

S0 (

Full ON) / M0

D D

S3 (Suspend to RAM) / M1

S4 (Suspend to DISK) / M1 ON ON OFF

S5 (SOFT OFF) / M1 ON ON OFFLOW LOW HIGHLOW

(Suspend to RAM) / M-OFF

S3

S4 (Suspend to DISK) / M-OFF

S5 (SOFT OFF) / M-OFF

DOCKING8

PM T

ABLE

C C

pow

plane

State

S0

S3

S5 S4/AC

S4/AC don't exist

S5

B B

SATA

TA 0

SA

SATA

1

SATA 2

SATA 3

4

A A

SATA

SATA 5

+15V_ALW

+5V_ALW

+3.3V_ALW_PCH

r

e

+3.3V_RTC_LDO

ON

ON

DESTINAT

HDD

ODD/ E3 Module Bay

NA

NA

ESATA

k

Doc

5

V_SUS

+3.3

+1.5V_MEM

ON ON

ON

OFF

OFFOFF

ION

+5V_RUN

+3.3V_RUN

+1.8V_RUN

+1.5V_RUN

+0.75V_DDR_VTT

+VCC_CORE

+1.05V_RUN_VTT

+1.05V_RUN

OFFON

OFF

OFF

4

+3.3

+1.

V_M

05V_M

ON

ON

ON

V_M

+3.3

+1.05V_M

(M-OFF)

ON

OFF

OFF

OFFOFF

Stack up

Thickness

Layer

SolderMask

Add Plating

Top/L1(signal)

Prepreg

Core

L3(IN1)

Prepreg

L4(IN2)

Core

L5(GND2)

Prepreg

L6(IN3)

Core

L7(IN4)

Prepreg

L8(VCC)

Core

L9(IN5)

Prepreg

L10(IN6) 0.5oz 0.65

Core 3mil 3.09

L11(GND3) 0.5oz

Prepreg

Bottom/L12(signal)

Add Plating

SolderMask

Overall Thickness

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

(Material SPEC.)

Unit : mil

min 0.4

1.30

0.5oz(0.68)

1080LRC

0.5oz

3mil

0.5oz

1080LRC+1080

1oz

3mil

1oz

1080HRC

0.5oz

6mil

0.5oz

1080HRC

1oz

3mil

1oz

1080LRC+1080

1080LRC 2.65

0.5oz(0.68)

1.30

min 0.4

1.36mm+/-10%

3

Thickness

(Actuality)

Unit : mil

0.50

1.05

0.65

2.65

0.65

3.09

0.65

5.1

1.35

3.09

1.35

2.90

0.65

6

0.65

2.90

1.35

3.09

1.35

5.1

0.65

0.65

1.05

0.50

53.36

USH

2

9

DOCKING

10 Express car

11

12

13

Bluetooth

Cam

none

0

1

PCI EXPRESS

Lane 1

Lane 2

Lane 3

Lane 4

Lane 5

Lane 6

Lane 7

Lane 8 N

DELL CONFIDENTIAL

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

d

era

BIO

NA

DESTINAT

MI

NI CARD-1 WWAN

MI

NI CARD-2 WLAN

Express car

ION

d

E3 Module Bay (USB3)

1/

2vMINI CARD-3 PCIE

MMI

10/100/1G LOM

one

/PROPRIETARY

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

Co

Co

Co

and Config.

and Config.

and Config.

Index

Index

Index

LA

LA

LA

-6611P

-6611P

dnesday, January 26, 2011

dnesday, January 26, 2011

dnesday, January 26, 2011

-6611P

1

0.3

0.3

364We

364We

364We

0.3

of

of

of

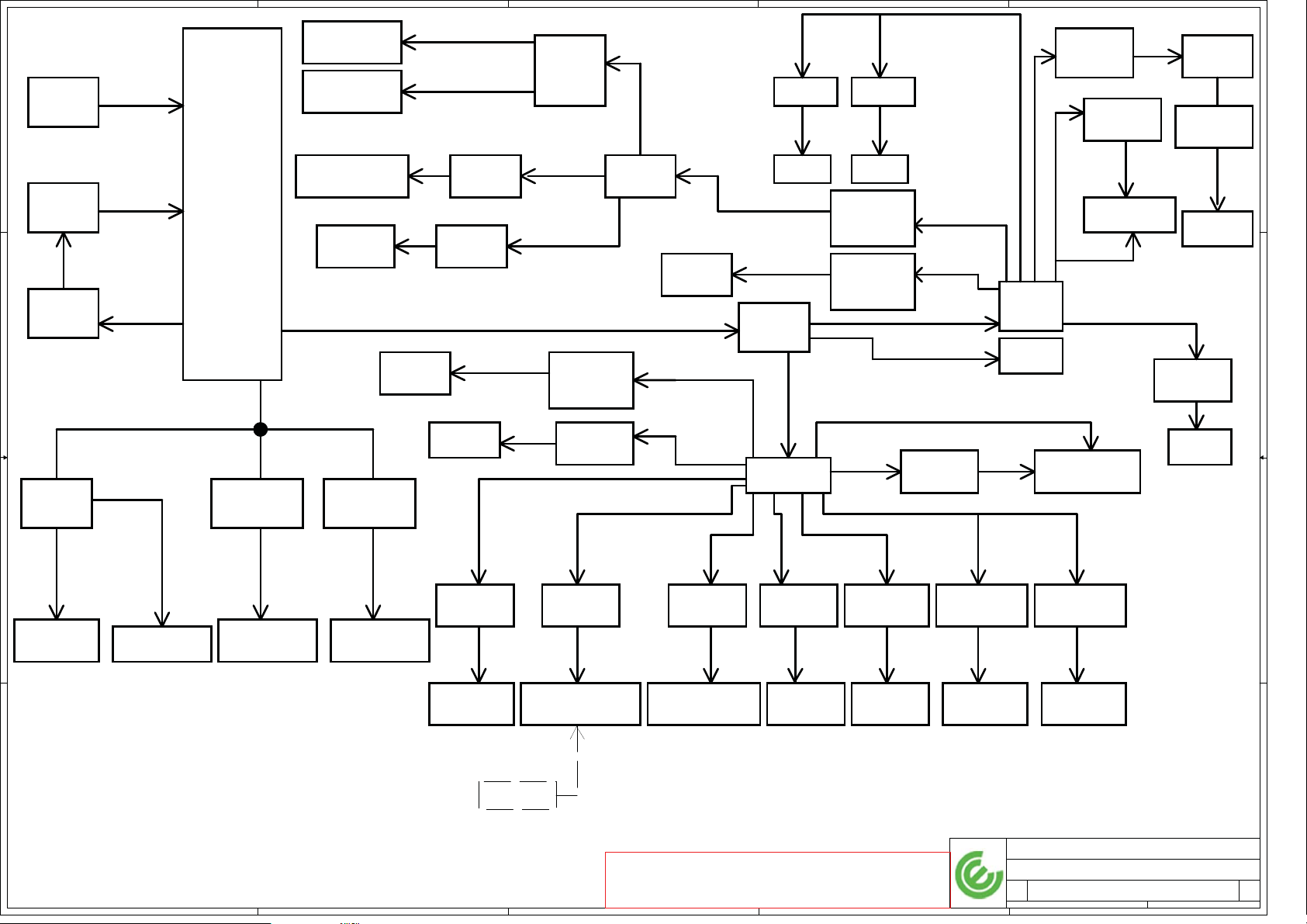

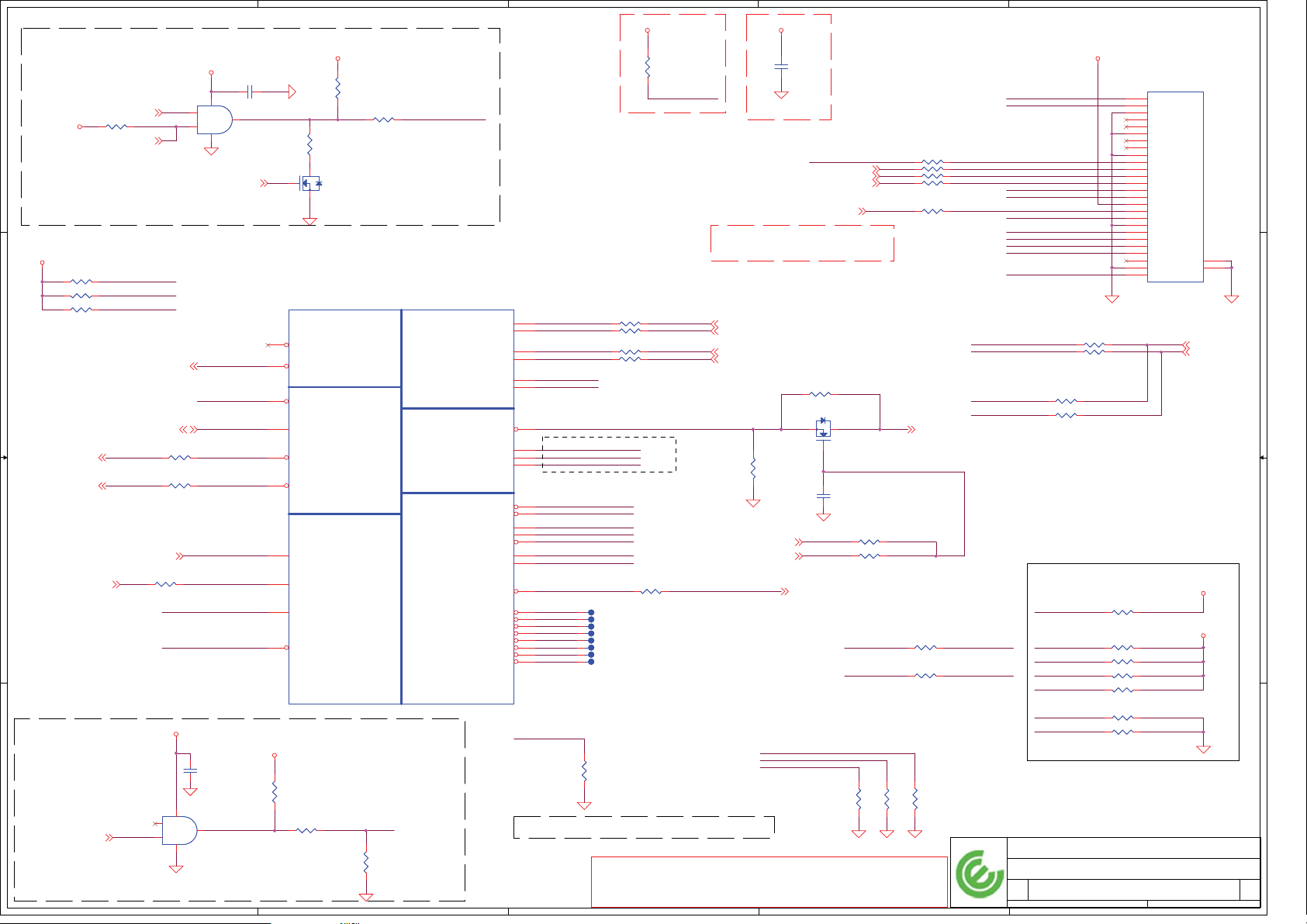

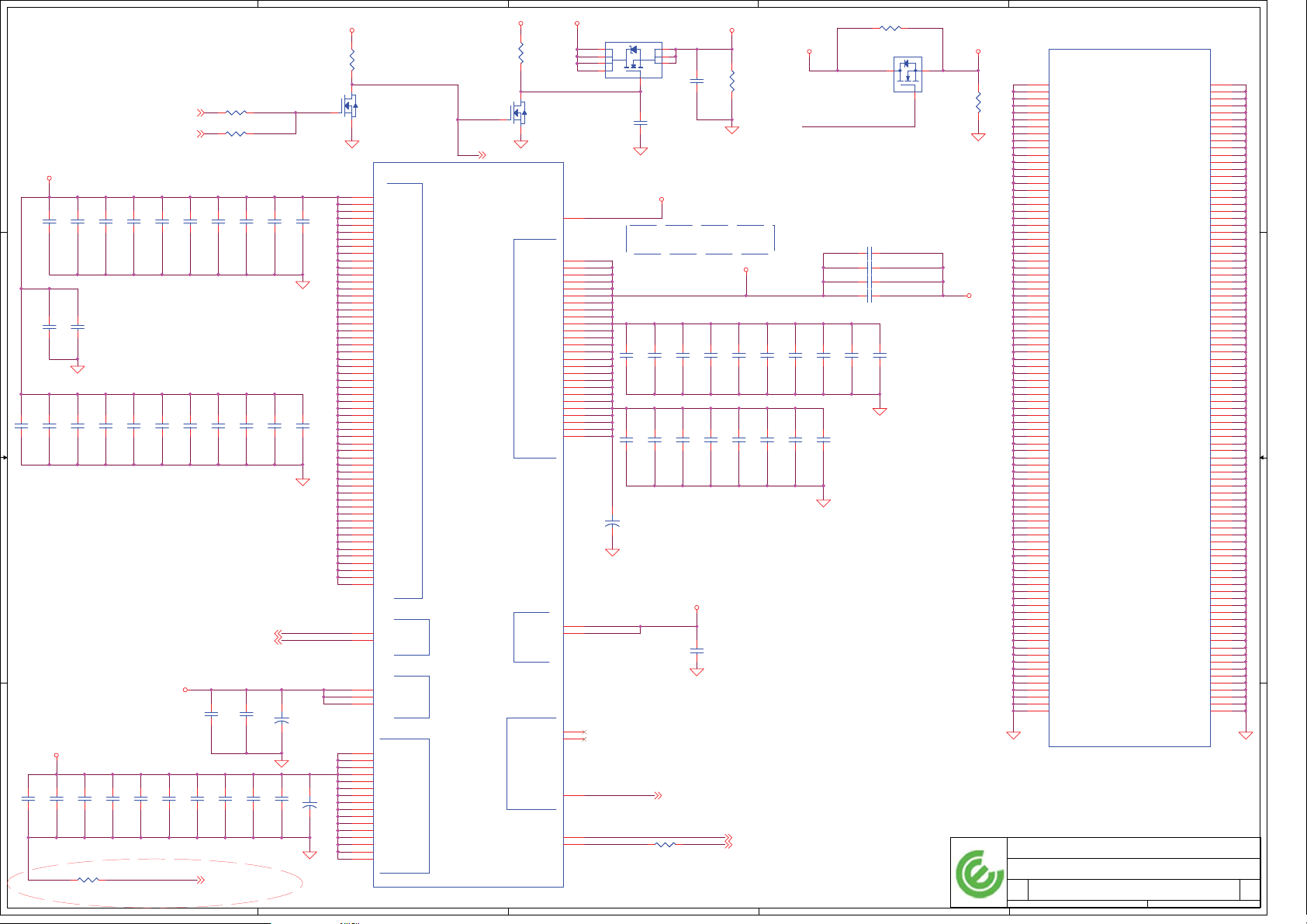

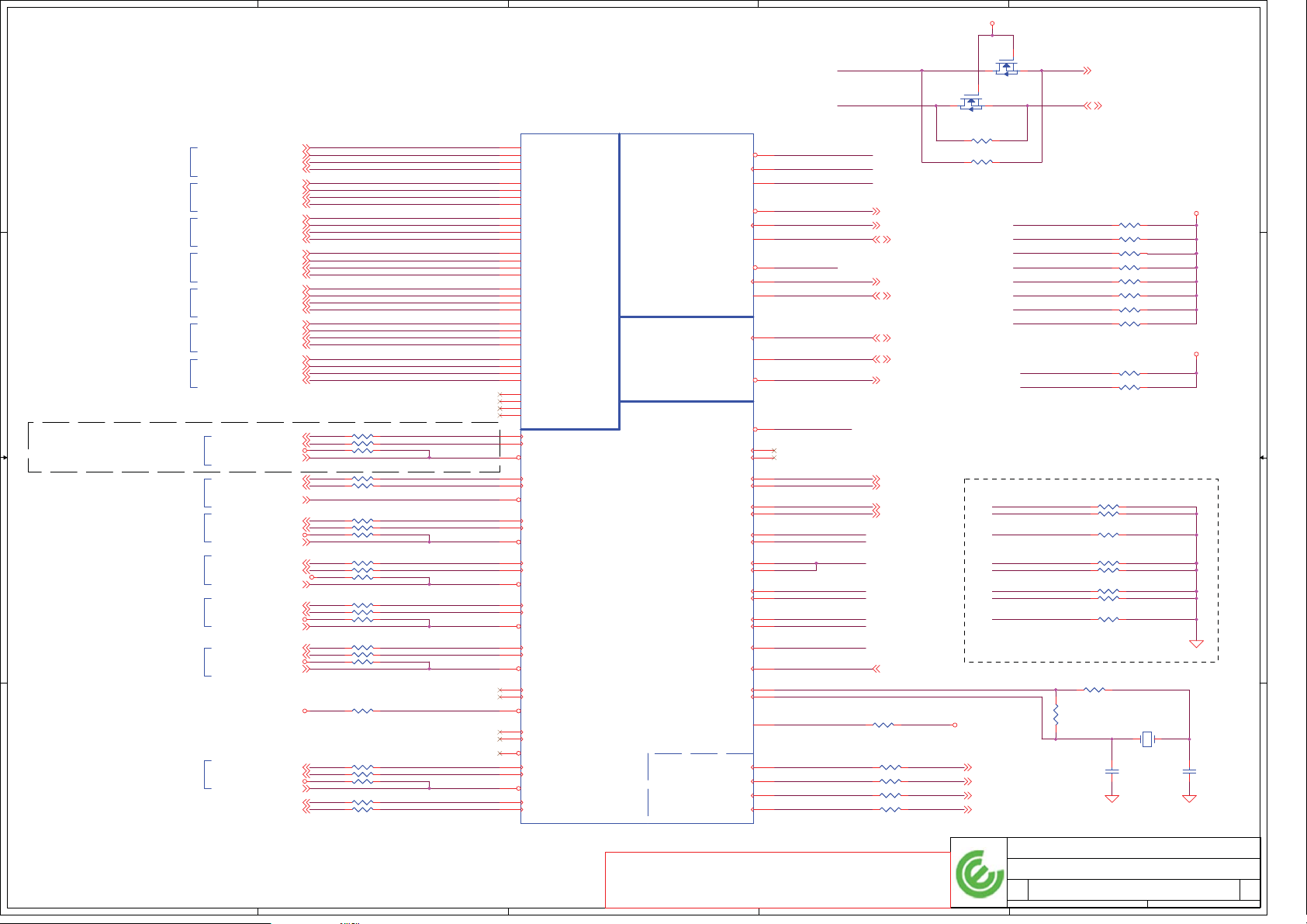

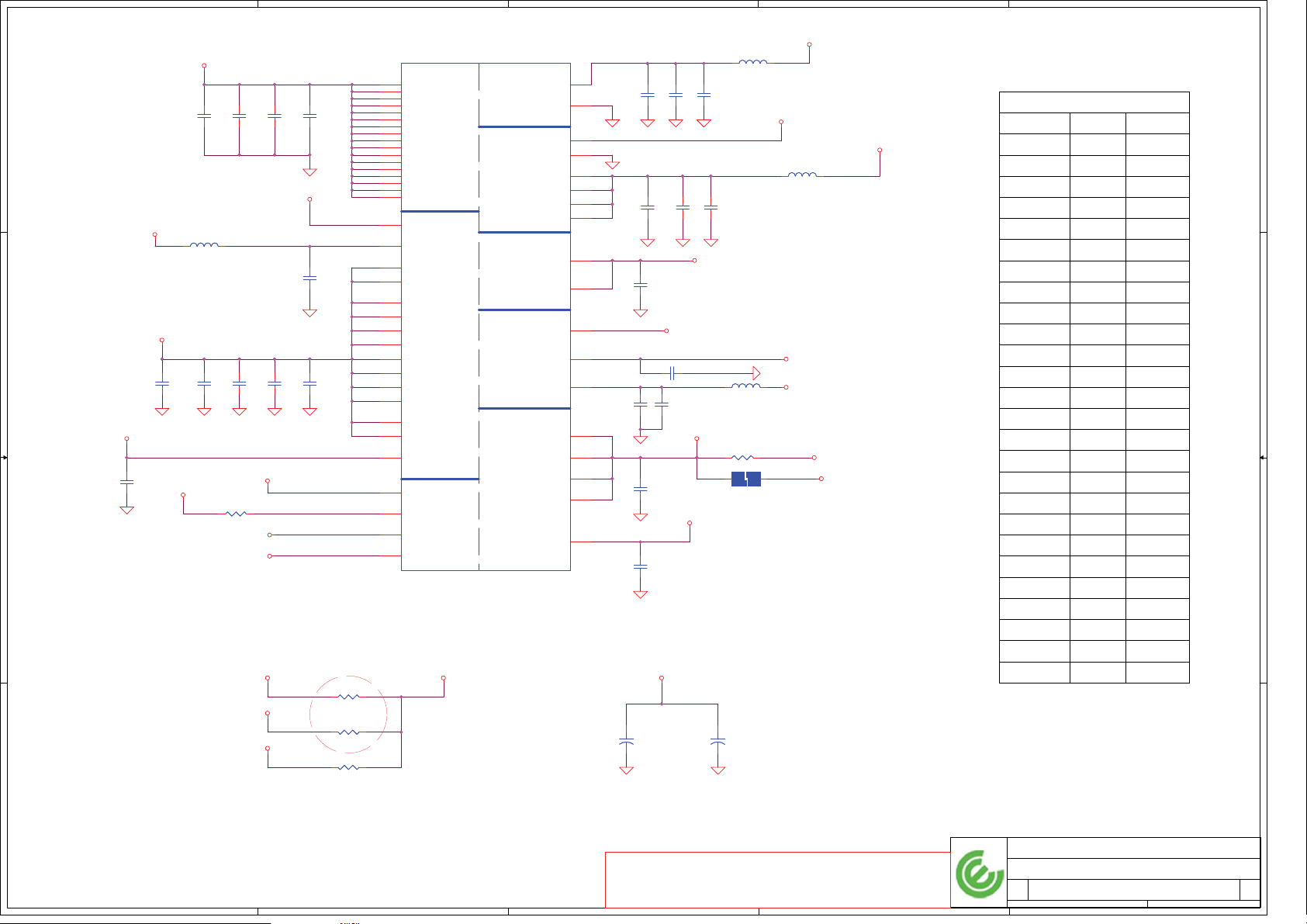

Page 4

5

+V_DDR_REF

ADAPTER

D D

+0.75V_DDR_VT

4

TPS51206

(PU5

)

T

3

N

HDDC_E

2

ODD_MOD

SI

3456BDVSI3456BDV

(Q

30)@(Q27)

SN1003055

(PU7

)

S

M3K7002F

S

@(QH4)

1

+1

.05V_RU

N_VTT

SI

4164DY

(Q63)

AO

V_CPU_VDDQ

+1.5

+PWR_SRC

BAT

TERY

V_RUN

+1.5

CHARG

ER

C C

V_RUN

+1.8

4728L

(QC3)

NTGS4144

(Q

59)

1.5V_R

UN_ENABLE

ALWON

TPS51311

(PU4

+3.

3V_SUS

3456BDV

SI

(Q

MA

X17511

)

(PU9

B B

VP_VR_ON

IM

+VCC_CORE

+V

CC_GFXCORE

IS

L95870A

U13)

(P

VTT_ON

CPU_

+0.

8V_VCC_SA

FDC654P

(Q21)

NVPWR

EN_I

+BL_

PWR_SRC

_WOWL

AUX_EN

SI

3456BDV

(Q38)

WWAN_PWREN

MCARD_

SI

3456BDV

(Q40)

5V_MEM

+1.

)

54)

MC

ARD_PCIE_BKT_PWREN

+1.

RUN_O

05V_M

SUS_ON

S13456

(

Q42)

N

+5V_HDD

MAX17020

)

(PU2

3V_ALW

+3.

AUX_ON

SI

3456

(Q34) (Q55)

+5V_

MOD

SN1003055

(PU3

SN1003055

(PU6

PCH

_ALW_ON

RUN_ON

NTM

)

)

S4920

PJP6

SI

3456BDV

(Q

49)

3

A_ON

SI

3456BDV

58)

(Q

+5V_

+15V

ALW

_ALW

+3.

3V_ALW_PCH

SI

ALW_ENABLE

+5V_

RUN_O

EN_LCDPWR

3456BDV

18)

(Q

ALW_PCH

N

05V_RUN

+1.

4164DY

SI

(Q50)

+5V_RUN

3V_WLAN

+3.

A A

5

4

+3.3

+3.

Pop option

V_RUN

3V_PCIE_WWAN

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3V_PCIE_FLASH

+3.

3

+3.

3V_LAN

+3.3

V_RUN

2

+3.3V_M

DELL CONFIDENTIAL

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

+LCDVDD

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

Co

Co

Co

Power

Power

Power

LA

LA

LA

-6611P

-6611P

dnesday, January 26, 2011

dnesday, January 26, 2011

dnesday, January 26, 2011

-6611P

/PROPRIETARY

Rail

Rail

Rail

1

0.3

0.3

464We

464We

464We

0.3

of

of

of

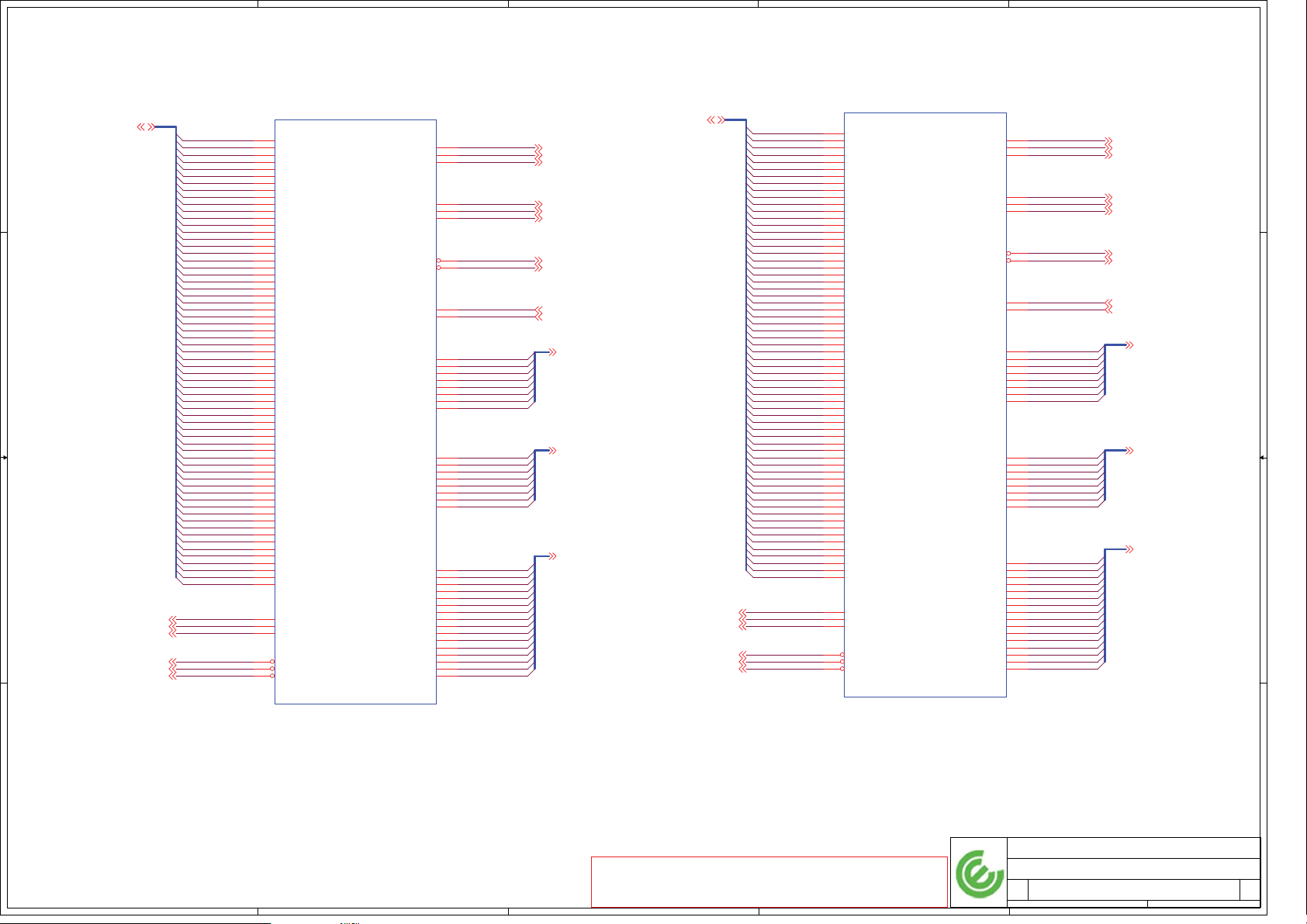

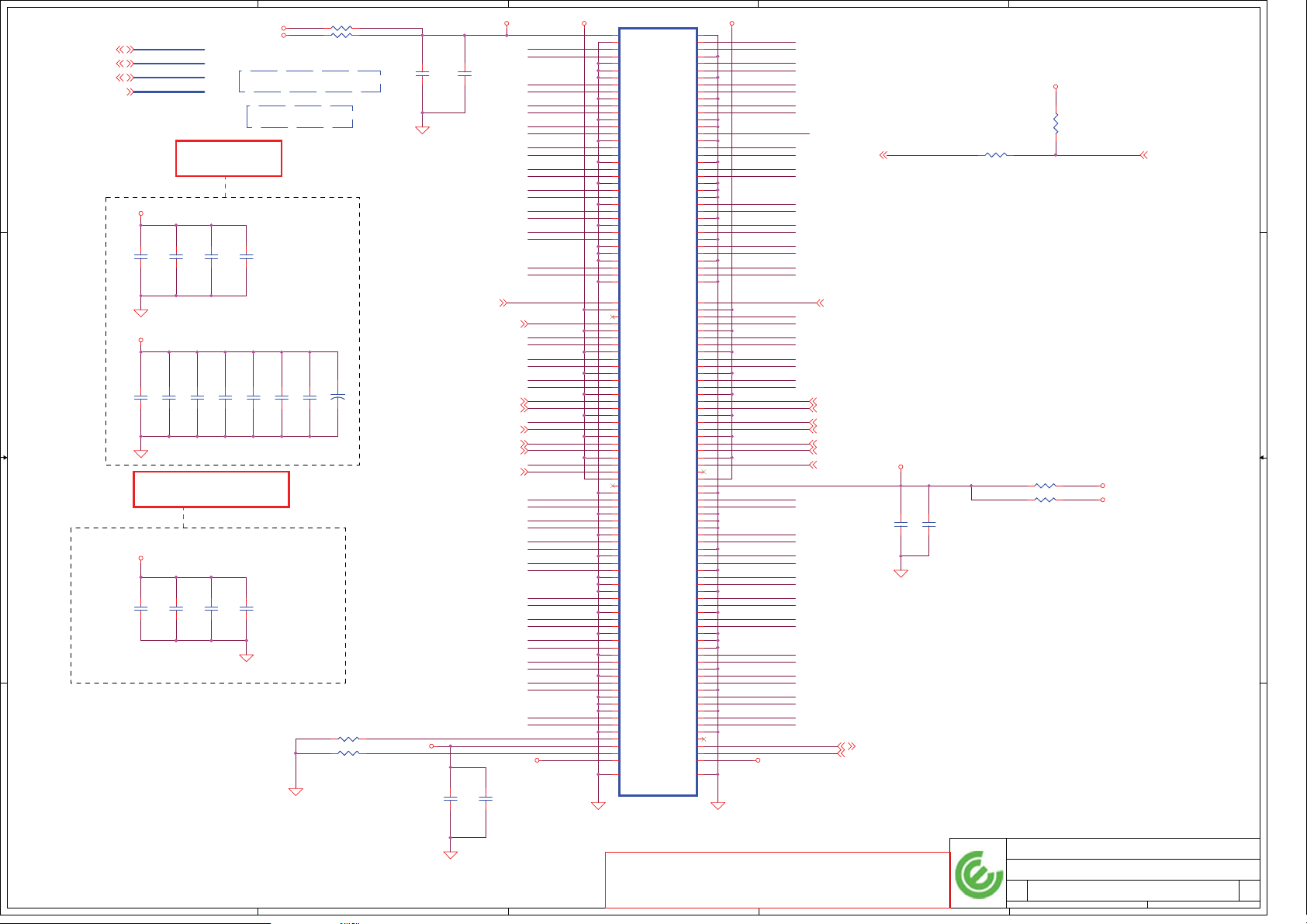

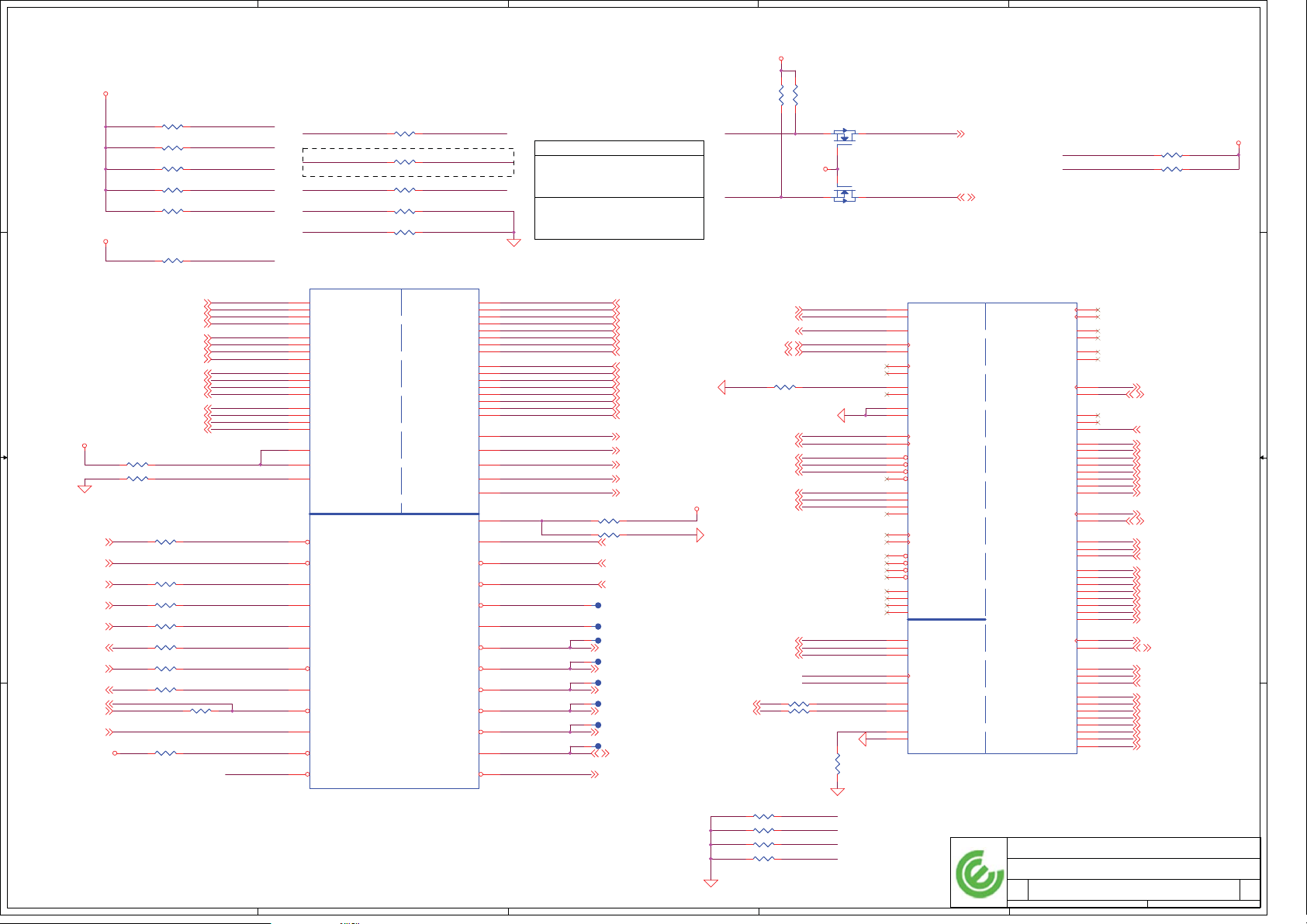

Page 5

5

SMBUS Address [0x9a]

H14

C9

MEM_SMBC LK

MEM_

SMBDATA

PCH

D D

N_SMBCLK

2.2K

B4

A3

B5

A4

LA

LAN_SMBDATA

2.2K

DOCK_

SMB_CLK

DOCK_SMB_DAT

_SMBCLK

LCD

LCD_SMDATA

+3.3V_ALW_PCH

C8

G12

M16E14

SM

L1_SMBDATA

SM

L1_SMBCLK

B6A5

3A

3A

1A

1A

C C

1B

1B

4

2.2K

2.2K

2.2K

2.2K

+3.3V_ALW_PCH

+3.3V_LAN

28

31

LOM

2N7002

2N7002

SMBUS Address [C8]

DDR_X

DDR_XDP_WAN_SMBDAT

2.2K

2.2K

+3.3V_ALW

127

129

DOCKING

2.2K

2.2K

+LCD_VDD

Keep pull up only for PWM LCD

3

DP_WAN_SMBCLK

SMBUS Address

APR_EC: 0x48

SPR_EC: 0x70

MSLICE_EC: 0x72

USB: 0x59

AUDIO: 0x34

SLICE_BATTERY: 0x17

SLICE_CHARGER: 0x13

202

200

202

200

2

MMA

DI

DI

MMB

30

32

WWAN

SMBUS Address [A0]

SMBUS Address [A4]

SMBUS Address [TBD]

1

2.2K

G Se

+3.3V_RUN

nsor

SMBUS Address [TBD]

2.2K

14

13

2.2K

4

+3.3V_ALW

100 ohm

100 ohm

+3.3V_ALW

+3.3V_ALW

+3.3V_ALW

+3.3V_ALW

+3.3V_RUN

7

6

M9

L9

7

8

10

9

31

32

8

9

ERY

BATT

CONN

USH

x

press card

E

ger

Char

Module Bay

E3

A/D,

D/A

converter

SMBUS Address [0x16]

SMBUS Address [0xa4]

SMBUS Address [TBD]

SMBUS Address [0x12]

SMBUS Address [0xd2]

SMBUS Address [0x30]

3

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

Co

Co

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

Co

US TOPOLOGY

US TOPOLOGY

US TOPOLOGY

SMB

SMB

SMB

LA

LA

LA

-6611P

-6611P

dnesday, January 26, 2011

dnesday, January 26, 2011

dnesday, January 26, 2011

-6611P

0.3

0.3

564We

564We

564We

1

0.3

of

of

of

KBC

A56

1C1CB59

PBA

T_SMBCLK

PBAT_SMBDAT

2.2K

2.2K

2.2K

A50

1E

B53

B B

C 5055

ME

1E

A49

2B

B52

2B

SMBCLK

USH_

USH_S

MBDAT

CARD_S

MBCLK

CARD_SMBDAT

2.2K

2.2K

2.2K

B50

1G

A47

1G

R_SMBCLK

CHARGE

CHARGER_SMBDAT

2.2K

2.2K

B7

_SMBDAT

A7

BAY

BAY_SMBCLK

2D

A A

2D

2.2K

2.2K

B49

B48

DAI_SMBCLK

DAI_SMBDAT

2A

2A

5

2.2K

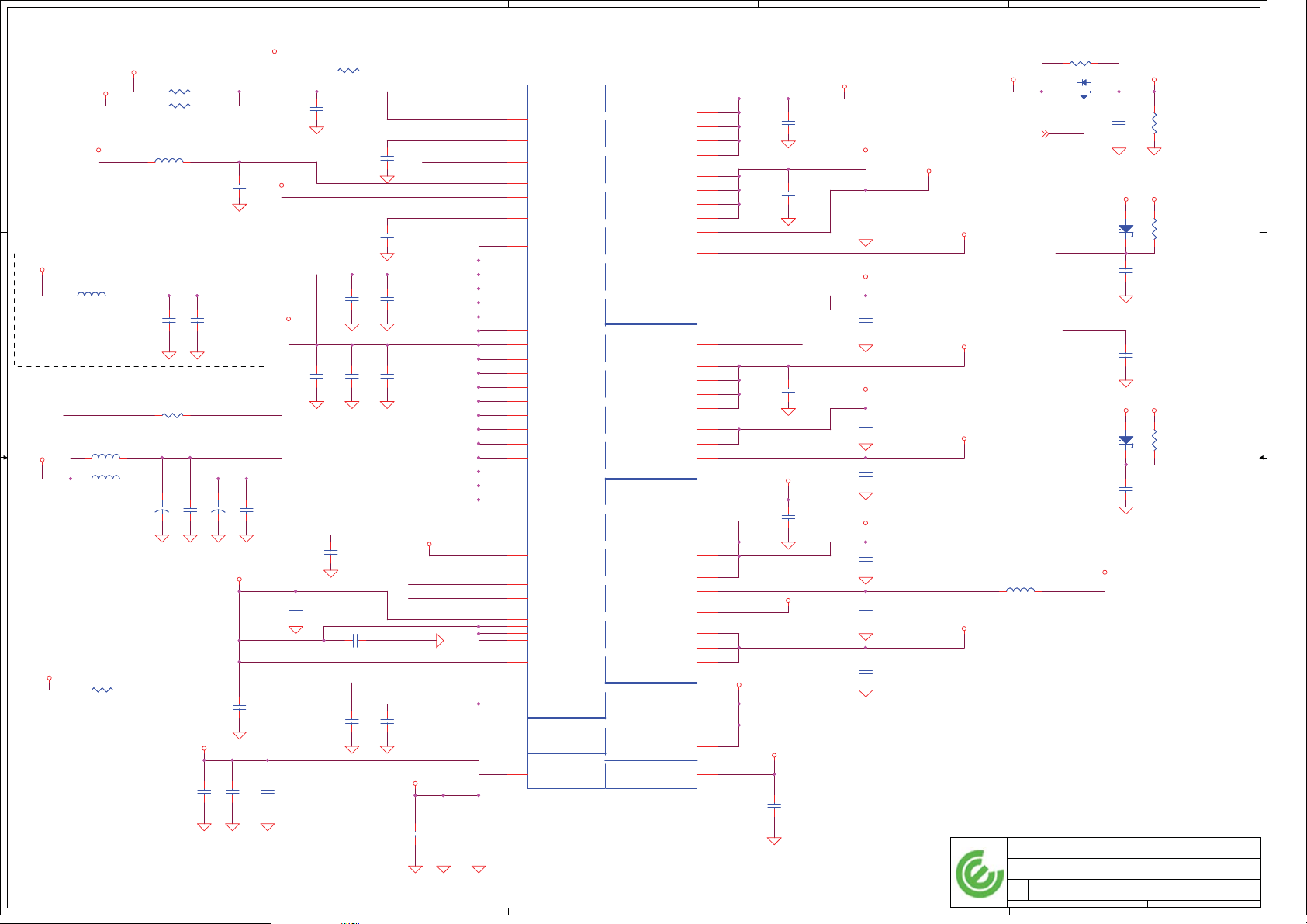

Page 6

5

;ϭͿW'ͺZKDWK;'ϰͿƵƐĞϰŵŝůĐŽŶŶĞĐƚƚŽW'ͺ/KDW/ƚŚĞŶƵƐĞϰŵŝůĐŽŶŶĞĐƚƚŽZϮ

;ϮͿW'ͺ/KDWKƵƐĞϭϮŵŝůĐŽŶŶĞĐƚƚŽZϮ

U1A

U1A

_CRX_PTX_N0

DMI

_CRX_PTX_N016

_CRX_PTX_N116

DMI

DMI

_CRX_PTX_N216

_CRX_PTX_N316

D D

C C

B B

DMI

DMI

_CRX_PTX_P016

_CRX_PTX_P116

DMI

I

_CRX_PTX_P216

DM

_CRX_PTX_P316

DMI

_CTX_PRX_N016

DMI

DMI

_CTX_PRX_N116

DMI

_CTX_PRX_N216

_CTX_PRX_N316

DMI

_CTX_PRX_P016

DMI

DMI

_CTX_PRX_P116

_CTX_PRX_P216

DMI

DMI

_CTX_PRX_P316

FDI_

CTX_PRX_N016

CTX_PRX_N116

FDI_

FDI_

CTX_PRX_N216

CTX_PRX_N316

FDI_

FDI_

CTX_PRX_N416

FDI_

CTX_PRX_N516

FDI_

CTX_PRX_N616

FDI_

CTX_PRX_N716

CTX_PRX_P016

FDI_

FDI_

CTX_PRX_P116

CTX_PRX_P216

FDI_

FDI_

CTX_PRX_P316

FDI_

CTX_PRX_P416

CTX_PRX_P516

FDI_

FDI_

CTX_PRX_P616

CTX_PRX_P716

FDI_

_FSYNC016

FDI

FDI

_FSYNC116

I_INT16

FD

_LSYNC016

FDI

FDI

_LSYNC116

;ϭͿWͺKDW/KƵƐĞϰŵŝůƚƌĂĐĞƚŽZϭ

;ϮͿWͺ/KDWKƵƐĞϭϮŵŝůƚŽZϭ

DMI

_CRX_PTX_N1

DMI

DMI

_CRX_PTX_N2

DMI

_CRX_PTX_N3

DMI

_CRX_PTX_P0

_CRX_PTX_P1

DMI

DMI

_CRX_PTX_P2

I

_CRX_PTX_P3

DM

DMI

_CTX_PRX_N0

_CTX_PRX_N1

DMI

DMI

_CTX_PRX_N2

_CTX_PRX_N3

DMI

DMI

_CTX_PRX_P0

_CTX_PRX_P1

DMI

DMI

_CTX_PRX_P2

_CTX_PRX_P3

DMI

CTX_PRX_N0

FDI_

FDI_

CTX_PRX_N1

CTX_PRX_N2

FDI_

FDI_

CTX_PRX_N3

CTX_PRX_N4

FDI_

FDI_

CTX_PRX_N5

FDI_

CTX_PRX_N6

CTX_PRX_N7

FDI_

FDI_

CTX_PRX_P0

CTX_PRX_P1

FDI_

FDI_

CTX_PRX_P2

CTX_PRX_P3

FDI_

FDI_

CTX_PRX_P4

FDI_

CTX_PRX_P5

CTX_PRX_P6

FDI_

FDI_

CTX_PRX_P7

FDI

_FSYNC0

_FSYNC1

FDI

FD

I_INT

FDI

_LSYNC0

_LSYNC1

FDI

EDP_CO

MP

W11

AC9

W10

AC8

AA11

AC12

AA10

AG8

AD2

AG11

AG4

AC3

AC4

AE11

AC1

AE10

M2

DMI

_RX#[0]

P6

_RX#[1]

DMI

P1

DMI

_RX#[2]

P10

I

_RX#[3]

DM

N3

DMI

_RX[0]

P7

_RX[1]

DMI

P3

DMI

_RX[2]

P11

_RX[3]

DMI

K1

DMI

_TX#[0]

M8

DMI

_TX#[1]

N4

DMI

_TX#[2]

R2

_TX#[3]

DMI

K3

DM

I_TX[0]

M7

DM

I_TX[1]

P4

I_TX[2]

DM

T3

I_TX[3]

DM

U7

I0_TX#[0]

FD

FD

I0_TX#[1]

W1

I0_TX#[2]

FD

AA6

I0_TX#[3]

FD

W6

I1_TX#[0]

FD

V4

FD

I1_TX#[1]

Y2

I1_TX#[2]

FD

I1_TX#[3]

FD

U6

FDI

0_TX[0]

0_TX[1]

FDI

W3

FDI

0_TX[2]

AA7

0_TX[3]

FDI

W7

FDI

1_TX[0]

T4

1_TX[1]

FDI

AA3

1_TX[2]

FDI

FDI

1_TX[3]

FDI

0_FSYNC

1_FSYNC

FDI

U11

FD

I_INT

0_LSYNC

FDI

1_LSYNC

FDI

AF3

eDP

_COMP IO

e

P_ICOMPO

D

_HPD

eDP

eD

P_AUX#

AF4

P_AUX

eD

eDP

_TX#[0 ]

eDP

_TX#[1 ]

_TX#[2 ]

eDP

AE7

eDP

_TX#[3 ]

eDP

_TX[0]

AA4

_TX[1]

eDP

eDP

_TX[2]

AE6

eDP

_TX[3]

SANDY

SANDY

4

-BRIDGE_BGA1023~D

-BRIDGE_BGA1023~D

PEG

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

ICOMPI

ICOMPO

RCOMPO

_

RX#[0]

RX#[1]

RX#[2]

RX#[3]

RX#[4]

RX#[5]

RX#[6]

RX#[7]

RX#[8]

RX#[9]

RX#[10]

RX#[11]

RX#[12]

RX#[13]

RX#[14]

RX#[15]

RX[0]

RX[1]

RX[2]

RX[3]

RX[4]

RX[5]

RX[6]

RX[7]

RX[8]

RX[9]

RX[10]

RX[11]

RX[12]

RX[13]

RX[14]

RX[15]

TX#[0]

TX#[1]

TX#[2]

TX#[3]

TX#[4]

TX#[5]

TX#[6]

TX#[7]

TX#[8]

TX#[9]

TX#[10]

TX#[11]

TX#[12]

TX#[13]

TX#[14]

TX#[15]

TX[0]

_

TX[1]

TX[2]

TX[3]

TX[4]

TX[5]

TX[6]

TX[7]

TX[8]

TX[9]

TX[10]

TX[11]

TX[12]

TX[13]

TX[14]

TX[15]

G3

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

PEG_

PEG_

PEG_

DMI Intel(R) FDI DP

DMI Intel(R) FDI DP

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PEG_

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_

PEG_

PEG_

PEG_

COMP

3

2

U1I

U1I

BG

17

VSS[181]

21

BG

VSS[182]

BG

24

VSS[183]

BG

28

184]

VSS[

37

BG

VSS[185]

BG

41

VSS[186]

45

BG

VSS[187]

BG

49

VSS[188]

53

BG

VSS[189]

9

BG

VSS[190]

C2

9

VSS[191]

C3

5

VSS[192]

C4

0

VSS[193]

0

D1

VSS[194]

4

D1

VSS[195]

D1

8

VSS[196]

D2

2

VSS[197]

6

D2

VSS[198]

9

D2

VSS[199]

D3

5

VSS[200]

D4

VSS[201]

D4

0

VSS[202]

3

D4

VSS[203]

6

D4

VSS[204]

D5

0

VSS[205]

4

D5

VSS[206]

8

D5

VSS[207]

D6

VSS[208]

E2

5

VSS[209]

9

E2

VSS[210]

E3

VSS[211]

5

E3

VSS[212]

0

E4

VSS[213]

F13

VSS[214]

F15

VSS[215]

F19

VSS[216]

F29

VSS[217]

F35

VSS[218]

F40

VSS[219]

F55

VSS[220]

G4

8

VSS[221]

1

G5

VSS[222]

G6

VSS[223]

1

G6

VSS[224]

H1

0

VSS[225]

H1

4

VSS[226]

H1

7

VSS[227]

1

H2

VSS[228]

H4

VSS[229]

H5

3

VSS[230]

8

H5

VSS[231]

J1

VSS[232]

J49

VSS[233]

J55

VSS[234]

1

K1

VSS[

235]

1

K2

VSS[236]

1

K5

VSS[237]

K8

VSS[238]

L16

VSS[239]

L20

VSS[240]

L22

VSS[241]

L26

VSS[242]

L30

VSS[243]

L34

VSS[244]

L38

VSS[245]

L43

VSS[246]

L48

VSS[247]

L61

VSS[248]

1

M1

VSS[249]

M1

5

VSS[250]

S

S

ANDY-BRIDGE_BGA1023~D

ANDY-BRIDGE_BGA1023~D

VSS

VSS

VSS[2

VSS[2

VSS[2

VSS[

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[2

VSS[3

VSS[3

VSS_NCTF_

VSS_NCTF_

VSS_NCTF_

VSS_NCTF_

VSS_NCTF_

VSS_NCTF_

VSS_NCTF_

VSS_NCTF_

VSS_NCTF_

VSS_NCTF_

NCTF

NCTF

VSS_NCTF_

VSS_NCTF_

VSS_NCTF_

VSS_NCTF_

1

M4

51]

M58

52]

M6

53]

N1

2

54]

N17

55]

N21

56]

N25

57]

N28

58]

N33

59]

N36

60]

N40

61]

N43

62]

N47

63]

N48

64]

N51

65]

N52

66]

N56

67]

N61

68]

P14

69]

P16

70]

P18

71]

P21

72]

P58

73]

P59

74]

P9

75]

R17

76]

R20

77]

R4

78]

R46

79]

T1

80]

T47

81]

T50

82]

T51

83]

T52

84]

T53

85]

T55

86]

T56

87]

U13

88]

U8

89]

V20

90]

V61

91]

W13

92]

W15

93]

W18

94]

W21

95]

W46

96]

W8

97]

Y4

98]

Y47

99]

Y58

00]

Y59

01]

A5

1

A57

2

BC61

3

BD3

4

BD59

5

BE4

6

BE58

7

BG5

8

BG57

9

C3

10

C58

11

D59

12

E1

13

E61

14

WŽŵƉĞŶƐĂƚŝŽŶ

.05V_RUN_VTT

+1

12

RC1

RC1

~D

~D

24.9_0402_1%

24.9_0402_1%

MP

EDP_CO

A A

ĞWͺKDW/KĂŶĚ/KDWKƐŝŐŶĂůƐƐŚŽƵůĚďĞƐŚŽƌƚĞĚŶĞĂƌďĂůůƐĂŶĚ

ƌŽƵƚĞĚǁŝƚŚƚLJƉŝĐĂůŝŵƉĞĚĂŶĐĞфϮϱŵŽŚŵƐ

5

4

W'ŽŵƉĞŶƐĂƚŝŽŶ

+1

.05V_RUN_VTT

12

RC2

RC2

24.9_0402_1%

24.9_0402_1%

~D

~D

PEG_

COMP

W'ͺ/KDW/ĂŶĚZKDWKƐŝŐŶĂůƐƐŚŽƵůĚďĞƐŚŽƌƚĞĚĂŶĚƌŽƵƚĞĚ

ǁŝƚŚͲŵĂdžůĞŶŐƚŚсϱϬϬŵŝůƐͲƚLJƉŝĐĂůŝŵƉĞĚĂŶĐĞсϰϯŵŽŚŵƐ

W'ͺ/KDWKƐŝŐŶĂůƐƐŚŽƵůĚďĞƌŽƵƚĞĚǁŝƚŚͲŵĂdžůĞŶŐƚŚсϱϬϬŵŝůƐ

ͲƚLJƉŝĐĂůŝŵƉĞĚĂŶĐĞсϭϰϱŵŽŚŵƐ

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

DELL CONFIDENTIAL

C

C

C

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

o

o

Title

Tit

Tit

le

le

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

o

Sa

Sa

Sa

ndy Bridge (1/6)

ndy Bridge (1/6)

ndy Bridge (1/6)

-6611P

-6611P

-6611P

LA

LA

LA

esday, Januar y 26, 2011

esday, Januar y 26, 2011

esday, Januar y 26, 2011

/PROPRIETARY

664W edn

664W edn

664W edn

of

of

1

of

0.3

0.3

0.3

Page 7

5

+1

OK_AND

F49

C57

C49

A48

C45

D45

C48

B46

BE45

D44

12

2

G

G

U1B

U1B

PROC

PROC

CATE

PECI

PROCHO

THERMT

SYNC

PM_

UNCOREPW

SM_

DRAMPWROK

RESET#

75_0402_1%

75_0402_1%

RC4

RC4

~

~

D

D

1 2

RC10

RC10

43_0402_5%

43_0402_5%

.5V_CPU_VDDQ

RC64

RC64

39_0402_5%

39_0402_5%

1 2

13

D

D

QC1

QC1

SM3K7002FU_SC70-3~D

SM3K7002FU_SC70-3~D

S

S

S

S

_SELECT#

_DETECT#

RR#

T#

RIP#

RGOOD

PCH_PL

~D

~D

&ŽůůŽǁ'ZĞǀϬϳϭ^DͺZDWtZK<ƚŽƉŽůŽŐLJ

D D

+3

.3V_ALW_PCH

.05V_RUN_VTT

+1

1 2

RC

1 2

RC

1 2

RC

RC

C C

H_PRO

HERMTRIP#22

H_T

B B

H_CPUPW

RUNPWR

1 2

18 200_0402_5%~D

18 200_0402_5%~D

RC

RC

_

DRAM_PWRGD16

PM

126 56_0402_5%~D@RC126 56_0402_5%~D@

128 49.9_0402_1%~D@RC128 49.9_0402_1%~D@

44 62_0402_5%~D

44 62_0402_5%~D

CHOT#43,53,55

RGD18

H_T

H_CAT

H_PRO

H_PM

ƵĨĨĞƌĞĚƌĞƐĞƚƚŽWh

A A

PCH_PL

TRST#14,17

5

+3

.3V_ALW_PCH

5

OK42,43

HERMTRIP#

CPU_DET

ƉůĂĐĞZϭϮϵŶĞĂƌWh

RC

RC

1

B

2

A

3

N_CPU1.5VS3#11,45

RUN_O

ERR#

CHOT#

EDS 1.0 SNB_IVB# -> PROC_SELECT#

ECT#42

H_CAT

H_PECI18

H_PRO

1 2

RC

RC

57 56_0402_5%~D

57 56_0402_5%~D

ůŽƐĞƚŽhϭ

RC

RC

129 0_0402_5%~D

129 0_0402_5%~D

_SYNC16

1 2

25 0_0402_5%~D

25 0_0402_5%~D

+3

1

2

H_

1 2

H_PM

VC

CPWRGOOD _0_R

DRAM_PWRGD_CPU

PM_

TRST#_R

PCH_PL

.3V_RUN

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1

CC14

CC14

0

0

2

5

P

NC

PCH_PL

4

Y

A

G

UC1

UC1

3

SN74LVC1G07DCKR_SC70-5~D

SN74LVC1G07DCKR_SC70-5~D

CC

CC

156

156

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

1 2

P

RUNPWR

4

O

G

UC2

UC2

C1G09GW_TSSOP5~D

C1G09GW_TSSOP5~D

74AH

74AH

ERR#

CHOT#_R

HERMTRIP#_R

T

_SYNC

+1

TRST#_BUF

.05V_RUN_VTT

4

200_0402_5%

200_0402_5%

12

RC12

RC12

~D

~D

1 2

RC

RC

28 130_0402_5%~D

28 130_0402_5%~D

~D

~D

SANDY

SANDY

-BRIDGE_BGA1023~D

-BRIDGE_BGA1023~D

TRST#_R

0_0402_5%

0_0402_5%

12

@

@

RC11

RC11

~D

~D

4

DRAM_PWRGD_CPU

PM_

DP

LL_REF_CLK

LL_REF_CLK#

DP

BC

DRAMRST#

SM_

SM_

SM_

SM_

BCLK

BCLK

LK_ITP

BC

LK_ITP#

RCOMP[0]

RCOMP[1]

RCOMP[2]

PRDY#

PREQ#

TCK

TMS

TRST#

TDO

DBR#

BP

M#[0]

M#[1]

BP

BP

M#[2]

M#[3]

BP

BP

M#[4]

M#[5]

BP

BP

M#[6]

BP

M#[7]

#

TDI

MISC THERMAL

MISC THERMAL

CLOCKS

CLOCKS

DDR3

MISC

DDR3

MISC

PWR MANAGEMENT

PWR MANAGEMENT

JTAG & BPM

JTAG & BPM

ǀŽŝĚƐƚƵďŝŶƚŚĞWtZ'ƉĂƚŚǁŚŝůĞƉůĂĐŝŶŐƌĞƐŝƐƚŽƌƐZϮϱΘZϭϯϬ

CPU_DM

J3

H2

AG3

AG1

N59

N58

AT30

BF44

BE43

BG43

N5

N5

L56

L55

J58

M6

L59

K58

G58

E55

E59

G55

G59

H60

J59

J61

VC

I

I#

CPU_DM

CPU_DPL

L

CPU_DPL

L#

XDP_ITP

CLK_

CLK_

XDP_ITP#

DRAMRST#_CPU

DDR3_

SM_

RCOMP0

RCOMP1

SM_

SM_

RCOMP2

^DͺZKDWϮͲͲхϭϱŵŝů

^DͺZKDWϭϬͲͲхϮϬŵŝů

XDP_PRDY

3

XDP_PREQ

5

XDP_TCL

XDP_TM

XDP_TRST#

XDP_TDI

0

XDP_TDO

XDP_DBRESET#

CPWRGOOD _0_R

3

+3

.3V_ALW_PCH

12

RC

124

@RC124

@

1K_0402_5%~D

1K_0402_5%~D

PWROK_XDP

SYS_

+1

.05V_RUN_VTT

1

2

0.

0.

1U_0402_16V4Z~D

1U_0402_16V4Z~D

CC65

CC65

2

WůĂĐĞŶĞĂƌ:yWϭ

H_CPUPW

RGD

_PWRBTN#_R14,16

SIO

09

CFG

PWROK16,42

SYS_

XDP#17

PLTRST_

dŚĞƌĞƐŝƐƚŽƌĨŽƌ,KK<ϮƐŚŽƵůĚďĞƉůĂĐĞĚ

ƐƵĐŚƚŚĂƚƚŚĞƐƚƵďŝƐǀĞƌLJƐŵĂůůŽŶ&'ϬŶĞƚ

1 2

13 0_0402_5%~D

13 0_0402_5%~D

RC

RC

1 2

RC

RC

15 0_0402_5%~D

15 0_0402_5%~D

1 2

16 0_0402_5%~D

16 0_0402_5%~D

RC

RC

1 2

RC

RC

17 0_0402_5%~D

17 0_0402_5%~D

DĂdžϱϬϬŵŝůƐ

#

#

K

S

_R

_R

_R

RC

RC

T128 P

T128 P

T131 P

T131 P

T129 P

T129 P

T130 P

T130 P

T125 P

T125 P

T126 PAD~D@ T126 PAD~D@

T107 P

T107 P

T127 PAD~D@ T127 PAD~D@

12

130

130

RC

RC

10K_0402_5%~D

10K_0402_5%~D

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

12

26 0_0402_5%~D

26 0_0402_5%~D

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

3

CPU_DMI 15

CLK_

CLK_

CPU_DMI# 15

CLK_

CPU_DPLL 15

CPU_DPLL# 15

CLK_

4.

4.

99K_0402_1%~D

99K_0402_1%~D

DDR_HVREF

DDR_HVREF

XDP_DBRESET#

RC50

RC50

12

_RST_PCH15

_RST_GATE43

XDP_DBRESET#

RCOMP2

SM_

SM_RCOMP1

SM_

RCOMP0

1 2

RC

48 0_0402_5%~D@RC48 0_0402_5%~D@

S

S

G

G

2

0.047U_0402_16V4Z~D

0.047U_0402_16V4Z~D

CC

CC

1

177

177

2

RC

RC

RC

D

D

13

QC2

QC2

SS138W-7-F_SOT323-3~D

SS138W-7-F_SOT323-3~D

B

B

46 0_0402_5%~D

46 0_0402_5%~D

47 0_0402_5%~D@RC47 0_0402_5%~D@

1 2

1 2

14,16

XDP_TDO

140_0402_1%

140_0402_1%

12

~D

~D

RC

RC

5 1K_0402_5%~D

5 1K_0402_5%~D

6 0_0402_5%~D

6 0_0402_5%~D

RC

RC

RC

RC

7 1K_0402_5%~D

7 1K_0402_5%~D

9 0_0402_5%~D@RC9 0_0402_5%~D@

RC

8 1K_0402_5%~D

8 1K_0402_5%~D

RC

RC

DDR_HVREF

_R

1 2

23 0_0402_5%~D

23 0_0402_5%~D

RC

RC

_R

1 2

RC

RC

24 0_0402_5%~D

24 0_0402_5%~D

25.

25.

5_0402_1%~D

5_0402_1%~D

12

RC43

RC43

RC42

RC42

2

1 2

1 2

1 2

1 2

1 2

DDR3_

DRAMRST# 12

_RST

200_0402_1%

200_0402_1%

12

RC45

RC45

~D

~D

1

+1

.05V_RUN_VTT

#

CLK_

CLK_

CLK_

CLK_

XDP

XDP#

XDP_ITP

XDP_ITP#

XDP_PREQ

XDP_PRDY

#

H_CPUPW

RGD_XDP

PWRBTN#_XDP

CFD_

XDP_HO

OK2

PWROK_XDP

SYS_

XDP

CLK_

CLK_

XDP#

XDP_RST#

_R

XDP_DBRESET#

XDP_TDO

XDP_TRST#

XDP_TDI

S

XDP_TM

XDP_TCL

K

RH

109 0_0402_5%~D@RH109 0_0402_5%~D@

108 0_0402_5%~D@RH108 0_0402_5%~D@

RH

1 2

1 2

RH10

RH10

12

RH10

RH10

12

1

OBSFN_

2

OBSFN_

3

D

GN

4

OBSDATA_

5

OBSDATA_

6

GND

7

OBSDATA_

8

OBSDATA_

9

GND

10

HOOK

0

11

HOOK

1

12

HOOK

2

13

3

HOOK

14

4

HOOK

15

HOOK

5

16

VCCOBS_

17

6

HOOK

18

7

HOOK

19

GND

20

TDO

21

TRSTn

22

TDI

23

TMS

TCK124GND

25

GND

26

TCK0

MOLEX_52435-2671

MOLEX_52435-2671

70_0402_5%~D

70_0402_5%~D

60_0402_5%~D

60_0402_5%~D

WhWĨŽƌ:d'ƐŝŐŶĂůƐ

XDP_TDIXDP_TDI

XDP_TDO

XDP_DBRESET#

XDP_TM

XDP_TDI

XDP_PREQ

XDP_TDO

XDP_TCL

XDP_TRST#

RC

RC

S

RC27 51_0402_1%~DRC27 51_0402_1%~D

_R

RC29 51_0402_1%~DRC29 51_0402_1%~D

#

RC

RC

RC

K

RC40

RC40

RC41

RC41

DELL CONFIDENTIAL

C

C

C

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

o

o

Tit

Tit

Title

le

le

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

o

Sa

Sa

Sa

ndy Bridge (2/6)

ndy Bridge (2/6)

ndy Bridge (2/6)

LA

LA

LA

esday, Januar y 26, 2011

esday, Januar y 26, 2011

esday, Januar y 26, 2011

12

19 1K_0402_5%~D

19 1K_0402_5%~D

32 51_0402_1%~D@RC32 51_0402_1%~D@

35 51_0402_1%~D

35 51_0402_1%~D

12

12

12

12

12

51_0402_1%

51_0402_1%

12

51_0402_1%

51_0402_1%

+1

/PROPRIETARY

-6611P

-6611P

-6611P

1

P1

@

P1

@

JXD

JXD

A0

A1

A[0]

A[1]

A[2]

A[3]

AB

27

28

GND

CLK_

CLK_

.3V_RUN

+3

.05V_RUN_VTT

~D

~D

~D

~D

764W edn

764W edn

764W edn

of

of

of

CPU_ITP 15

CPU_ITP# 15

0.3

0.3

0.3

Page 8

5

U1C

D D

C C

B B

DDR_A_

D[0..63]12

BS012

DDR_A_

DDR_A_

BS112

DDR_A_

BS212

DDR_A_

CAS#12

RAS#12

DDR_A_

DDR_A_WE#12

DDR_A_

DDR_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

A_

A_

BS0

BS1

BS2

CAS#

RAS#

WE#

U1C

D0

AG6

SA_DQ

AJ10

AT13

AY13

AY17

AT48

AY48

AY53

AT54

BF36

AT41

AJ6

AL6

AJ8

AL8

AL7

AP6

AU6

AV9

AR6

AP8

BC7

BB7

BA7

BA9

BB9

9

[0]

[1]

SA_DQ

[2]

SA_DQ

SA_DQ

[3]

SA_DQ

[4]

SA_DQ

[5]

[6]

SA_DQ

[7]

SA_DQ

SA_DQ

[8]

SA_DQ

[9]

[10]

SA_DQ

[11]

SA_DQ

SA_DQ

[12]

[13]

SA_DQ

SA_DQ

[14]

[15]

SA_DQ

[16]

SA_DQ

SA_DQ

[17]

[18]

SA_DQ

[19]

SA_DQ

[20]

SA_DQ

SA_DQ

[21]

[22]

SA_DQ

[23]

SA_DQ

[24]

SA_DQ

[25]

SA_DQ

SA_DQ

[26]

[27]

SA_DQ

SA_DQ

[28]

[29]

SA_DQ

SA_DQ

[30]

[31]

SA_DQ

[32]

SA_DQ

SA_DQ

[33]

[34]

SA_DQ

SA_DQ

[35]

[36]

SA_DQ

SA_DQ

[37]

SA_DQ

[38]

SA_DQ

[39]

[40]

SA_DQ

[41]

SA_DQ

SA_DQ

[42]

[43]

SA_DQ

SA_DQ

[44]

[45]

SA_DQ

SA_DQ

[46]

SA_

[47]

DQ

[48]

SA_DQ

[49]

SA_DQ

[50]

SA_DQ

SA_DQ

[51]

[52]

SA_DQ

SA_DQ

[53]

[54]

SA_DQ

SA_DQ

[55]

SA_DQ

[56]

[57]

SA_DQ

SA_DQ

[58]

[59]

SA_DQ

SA_DQ

[60]

[61]

SA_DQ

SA_DQ

[62]

SA_DQ

[63]

0]

SA_BS[

SA_BS[

1]

2]

SA_BS[

SA_CAS#

SA_RAS#

SA_W

E#

-BRIDGE_BGA1023~D

-BRIDGE_BGA1023~D

SANDY

SANDY

D1

D2

AP11

D3

D4

D5

D6

D7

D8

AR11

D9

D10

D11

D12

D13

D14

D15

AU13

D16

D17

D18

BA13

D19

BB11

D20

D21

D22

D23

D24

AV14

D25

AR14

D26

D27

AR19

D28

BA14

D29

AU14

D30

BB14

D31

BB17

D32

BA45

D33

AR43

D34

AW48

D35

BC48

D36

BC45

D37

AR45

D38

D39

D40

BA49

D41

AV49

D42

BB51

D43

D44

BB49

D45

AU49

D46

BA53

D47

BB55

D48

BA55

D49

AV56

D50

AP50

D51

AP53

D52

AV54

D53

D54

AP56

D55

AP52

D56

AN57

D57

AN53

D58

AG56

D59

AG53

D60

AN55

D61

AN52

D62

AG55

D63

AK56

BD37

BA28

BE3

BD39

4

_

CLK_DDR0

M

AU36

K[0]

SA_CL

K#[0]

SA_CL

SA_CKE[

0]

SA_CL

K[1]

K#[1]

SA_CL

1]

SA_CKE[

SA_CS#

[0]

[1]

SA_CS#

DT[0]

SA_O

DT[1]

SA_O

S#[0]

SA_DQ

S#[1]

SA_DQ

SA_DQ

S#[2]

S#[3]

SA_DQ

SA_DQ

S#[4]

S#[5]

SA_DQ

SA_DQ

S#[6]

SA_DQ

S#[7]

S[0]

SA_DQ

SA_DQ

S[1]

SA_

S[2]

DQ

S[3]

SA_DQ

S[4]

SA_DQ

S[5]

SA_DQ

SA_DQ

S[6]

S[7]

SA_DQ

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

A[0]

SA_M

SA_M

A[1]

SA_M

A[2]

SA_M

A[3]

SA_M

A[4]

A[5]

SA_M

SA_M

A[6]

A[7]

SA_M

SA_M

A[8]

A[9]

SA_M

SA_M

A[10]

A[11]

SA_M

SA_M

A[12]

SA_M

A[13]

SA_MA[14]

SA_M

A[15]

AV36

AY26

AT40

AU40

BB26

BB40

BC41

AY40

BA41

AL11

AR8

AV11

AT17

AV45

AY51

AT55

AK55

AJ11

AR10

AY11

AU17

AW45

AV51

AT56

AK54

BG35

BB34

BE35

BD35

AT34

AU34

BB32

AT32

AY32

AV32

BE37

BA30

BC30

AW41

AY28

AU26

CLK_DDR#0

M_

DDR_CKE0

CLK_DDR1

M_

M_

CLK_DDR#1

DDR_CKE1

DDR_CS0

DDR_CS1

DT0

M_O

DT1

M_O

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_

A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

DDR_A_

_DIMMA

_DIMMA

_DIMMA#

_DIMMA#

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

MA15

CLK_DDR0 12

M_

M_

CLK_DDR#0 12

CKE0

DDR_

M_

CLK_DDR1 12

CLK_DDR#1 12

M_

DDR_CKE1

DDR_CS0

DDR_CS1

DT0 12

M_O

M_O

DT1 12

DDR_A_

DDR_A_

DDR_A_

_DIMMA 12

_DIMMA 12

_DIMMA# 12

_DIMMA# 12

DQS#[0..7] 12

DQS[0..7] 12

MA[0..15] 12

3

DDR_B_

D[0..63]13

DDR_B_

BS013

BS113

DDR_B_

DDR_B_

BS213

CAS#13

DDR_B_

DDR_B_

RAS#13

WE#13

DDR_B_

DDR_B_

DDR_B_

DDR_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

D0

AL4

D1

AL1

B_

D2

AN3

D3

AR4

D4

AK4

D5

AK3

D6

AN4

D7

AR1

D8

AU4

D9

AT2

D10

AV4

D11

BA4

D12

AU3

D13

AR3

D14

AY2

D15

BA3

D16

BE9

D17

BD9

D18

BD13

D19

BF12

D20

BF8

D21

BD10

D22

BD14

D23

BE13

D24

BF16

D25

BE17

D26

BE18

D27

BE21

D28

BE14

D29

BG14

D30

BG18

D31

BF19

D32

BD50

D33

BF48

D34

BD53

D35

BF52

D36

BD49

D37

BE49

D38

BD54

D39

BE53

D40

BF56

D41

BE57

D42

BC59

D43

AY60

D44

BE54

D45

BG54

D46

BA58

D47

AW59

D48

AW58

D49

AU58

D50

B_

AN61

D51

AN59

D52

AU59

D53

AU61

D54

AN58

D55

AR58

D56

AK58

D57

AL58

D58

AG58

D59

AG59

D60

AM60

D61

AL59

D62

AF61

D63

AH60

BS0

BG39

BS1

BD42

BS2

AT22

CAS#

AV4

3

RAS#

BF4

0

WE#

BD45

2

D

D

U1

U1

[0]

SB_DQ

SB_DQ

[1]

[2]

SB_DQ

[3]

SB_DQ

SB_DQ

[4]

SB_DQ

[5]

SB_DQ

[6]

[7]

SB_DQ

[8]

SB_DQ

SB_DQ

[9]

SB_DQ

[10]

[11]

SB_DQ

[12]

SB_DQ

SB_DQ

[13]

[14]

SB_DQ

SB_DQ

[15]

[16]

SB_DQ

[17]

SB_DQ

SB_DQ

[18]

[19]

SB_DQ

[20]

SB_DQ

[21]

SB_DQ

SB_DQ

[22]

[23]

SB_DQ

[24]

SB_DQ

[25]

SB_DQ

[26]

SB_DQ

SB_DQ

[27]

[28]

SB_DQ

SB_DQ

[29]

[30]

SB_DQ

SB_DQ

[31]

[32]

SB_DQ

[33]

SB_DQ

SB_DQ

[34]

[35]

SB_DQ

SB_DQ

[36]

[37]

SB_DQ

SB_DQ

[38]

SB_DQ

[39]

SB_DQ

[40]

[41]

SB_DQ

[42]

SB_DQ

SB_DQ

[43]

[44]

SB_DQ

SB_DQ

[45]

[46]

SB_DQ

SB_DQ

[47]

SB_

[48]

DQ

[49]

SB_DQ

[50]

SB_DQ

[51]

SB_DQ

SB_DQ

[52]

[53]

SB_DQ

SB_DQ

[54]

[55]

SB_DQ

SB_DQ

[56]

SB_DQ

[57]

[58]

SB_DQ

SB_DQ

[59]

[60]

SB_DQ

SB_DQ

[61]

[62]

SB_DQ

SB_DQ

[63]

SB_BS[

0]

1]

SB_BS[

SB_BS[

2]

SB_CAS#

SB_RAS#

SB_WE#

S

S

ANDY-BRIDGE_BGA1023~D

ANDY-BRIDGE_BGA1023~D

M_

CLK_DDR2

BA34

SB_CL

K[0]

K#[0]

SB_CL

SB_CKE[

SB_CL

K[1]

SB_CL

K#[1]

SB_CKE[

_CS#[0]

SB

SB

_CS#[1]

DT[0]

SB_O

DT[1]

SB_O

SB_DQ

S#[0]

S#[1]

SB_DQ

S#[2]

SB_DQ

SB_DQ

S#[3]

S#[4]

SB_DQ

SB_DQ

S#[5]

S#[6]

SB_DQ

SB_DQ

S#[7]

S[0]

SB_DQ

SB_DQ

S[1]

SB_

S[2]

DQ

S[3]

SB_DQ

S[4]

SB_DQ

S[5]

SB_DQ

SB_DQ

S[6]

S[7]

SB_DQ

DDR SYSTEM MEMORY B

DDR SYSTEM MEMORY B

SB_M

A[0]

A[1]

SB_M

SB_M

A[2]

SB_M

A[3]

SB_M

A[4]

SB_M

A[5]

A[6]

SB_M

SB_M

A[7]

A[8]

SB_M

SB_M

A[9]

A[10]

SB_M

SB_M

A[11]

A[12]

SB_M

SB_M

A[13]

SB_M

A[14]

SB_MA[15]

_

CLK_DDR#2

M

AY34

AR22

0]

BA36

BB36

BF27

1]

BE41

BE47

AT43

BG47

AL3

AV3

BG11

BD17

BG51

BA59

AT60

AK59

AM2

AV1

BE11

BD18

BE51

BA61

AR59

AK61

BF32

BE33

BD33

AU30

BD30

AV30

BG30

BD29

BE30

BE28

BD43

AT28

AV28

BD46

AT26

AU22

DDR_CKE2

M_

CLK_DDR3

CLK_DDR#3

M_

DDR_CKE3

DDR_CS2

DDR_CS3

DT2

M_O

DT3

M_O

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_

B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

DDR_B_

_DIMMB

_DIMMB

_DIMMB#

_DIMMB#

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

MA15

1

_

CLK_DDR2 13

M

CLK_DDR#2 13

M_

DDR_CKE2

CLK_DDR3 13

M_

M_

CLK_DDR#3 13

DDR_CKE3

DDR_CS2

DDR_CS3

M_O

DT2 13

DT3 13

M_O

DDR_B_

DDR_B_

DDR_B_

_DIMMB 13

_DIMMB 13

_DIMMB# 13

_DIMMB# 13

DQS#[0..7] 13

DQS[0..7] 13

MA[0..15] 13

A A

DELL CONFIDENTIAL

C

C

C

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

o

o

Tit

Tit

Tit

le

le

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

le

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

o

Sa

Sa

Sa

ndy Bridge (3/6)

ndy Bridge (3/6)

ndy Bridge (3/6)

-6611P

-6611P

-6611P

LA

LA

LA

esday, Januar y 26, 2011

esday, Januar y 26, 2011

esday, Januar y 26, 2011

/PROPRIETARY

864W edn

864W edn

864W edn

of

of

1

of

0.3

0.3

0.3

Page 9

5

4

3

2

1

&'^ƚƌĂƉƐĨŽƌWƌŽĐĞƐƐŽƌ

CFG

2

D D

PEG Static Lane Reversal - CFG2 is for the 16x

1:(Default) Normal Operation; Lane #

CFG2

U1E

U1E

CFG

07

CFG

T11

T11

PAD~D@

PAD~D@

T13

T13

PAD~D@

PAD~D@

T17

T17

PAD~D@

PAD~D@

PAD~D@

PAD~D@

T18

T18

T15

T15

PAD~D@

+V

CC_CORE

H_CPU_

H_CPU_

H_CPU_

H_CPU_

+D

12

+D

12

RSVD3

RSVD1

RSVD2

RSVD4

IMM0_1_VREF_CPU

IMM0_1_CA_CPU

EDS 1.0 RSVD_12 -> VCC_DIE_SENSE

1 2

120 49.9_0402_1%~D@RC120 49.9_0402_1%~D@

C C

B B

CC_GFXCORE

+V

RC

RC

RC

RC

RC

RC

1 2

122 49.9_0402_1%~D@RC122 49.9_0402_1%~D@

1 2

121 49.9_0402_1%~D@RC121 49.9_0402_1%~D@

1 2

123 49.9_0402_1%~D@RC123 49.9_0402_1%~D@

96 1K_0402_5%~D@RC96 1K_0402_5%~D@

97 1K_0402_5%~D@RC97 1K_0402_5%~D@

T19

T19

T9 PAD~

T9 PAD~

T10

T10

T12

T12

T14

T14

T21

T21

T20

T20

MM0_1_VREF_CPU

+DI

+DI

MM0_1_CA_CPU

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

T22PAD~D @T22PAD~D @

T25PAD~D @T25PAD~D @

T26PAD~D @T26PAD~D @

T27PAD~D @T27PAD~D @

T28PAD~D @T28PAD~D @

T29PAD~D @T29PAD~D @

T30PAD~D @T30PAD~D @

T31PAD~D @T31PAD~D @

T32PAD~D @T32PAD~D @

T33PAD~D @T33PAD~D @

T34PAD~D @T34PAD~D @

T35PAD~D @T35PAD~D @

T36PAD~D @T36PAD~D @

T37PAD~D @T37PAD~D @

T38PAD~D @T38PAD~D @

T39PAD~D @T39PAD~D @

T40PAD~D @T40PAD~D @

T41PAD~D @T41PAD~D @

T42PAD~D @T42PAD~D @

T43PAD~D @T43PAD~D @

T44PAD~D @T44PAD~D @

D@

D@

H_CPU_

H_CPU_

H_CPU_

H_CPU_

0

CFG

1

2

CFG

3

CFG

CFG

4

5

CFG

CFG

6

7

CFG

CFG

8

CFG

9

10

CFG

11

CFG

12

CFG

CFG

13

14

CFG

CFG

15

16

CFG

CFG

17

RSVD3

RSVD4

RSVD1

RSVD2

CC_DIESENSE

TP_V

+D

IMM0_1_VREF_CPU

IMM0_1_CA_CPU

+D

PU_RSVD8

TP_C

TP_

PU_RSVD9

C

PU_RSVD10

TP_C

TP_C

PU_RSVD11

PU_RSVD12

TP_C

PU_RSVD13

TP_C

PU_RSVD14

TP_C

TP_C

PU_RSVD15

TP_C

PU_RSVD16

PU_RSVD17

TP_C

PU_RSVD18

TP_C

PU_RSVD19

TP_C

TP_C

PU_RSVD20

PU_RSVD21

TP_C

PU_RSVD22

TP_C

TP_C

PU_RSVD23

TP_C

PU_RSVD24

TP_C

PU_RSVD25

PU_RSVD26

TP_C

PU_RSVD27

TP_C

BA19

AV19

AT2

BB2

BB1

AY

BA2

AY

AU1

AU2

BD2

BD2

BD2

BD2

BG

BE2

BG

BE2

BF2

BE2

B50

[0]

CFG

C51

CFG

[1]

B54

[2]

CFG

D53

[3]

CFG

A51

CFG

[4]

C53

[5]

CFG

C55

[6]

CFG

H49

[7]

CFG

A55

CFG

[8]

H51

[9]

CFG

K49

[10]

CFG

K53

[11]

CFG

F53

[12]

CFG

G53

CFG

[13]

L51

[14]

CFG

F51

CFG

[15]

D52

[16]

CFG

L53

CFG

[17]

H43

VCC_VAL

1

1

9

21

2

22

9

1

1

2

5

6

22

2

26

6

3

4

VSS_VAL

VAXG_

VSSAXG_

VCC_DI

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

_SENSE

_SENSE

VAL_SENSE

VAL_SENSE

E_SENSE

RESERVED

RESERVED

K43

H45

K45

F48

H48

K48

DC_T

DC_

DC_T

DC_T

_TEST_A58

DC

DC

_TEST_A59

_TEST_C59

DC

DC

_TEST_A61

_TEST_C61

DC

DC

_TEST_D61

DC_T

EST_BD61

DC_TEST_

DC_TEST_

EST_BG61

DC_T

DC_T

EST_BG59

EST_BG58

DC_T

DC_T

DC_T

DC_TEST_

DC_T

DC_TEST_

DC_T

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

EST_A4

EST_C4

T

EST_D3

EST_D1

BE61

BE59

EST_BG4

EST_BG3

EST_BG1

EST_BD1

TP_C

PU_RSVD28

BE7

TP_C

PU_RSVD29

BG

7

TP_C

PU_RSVD30

N4

2

PU_RSVD31

TP_C

L42

TP_C

PU_RSVD32

L45

PU_RSVD33

TP_C

L47

PU_RSVD34

TP_C

3

M1

PU_RSVD35

TP_C

4

M1

PU_RSVD36

TP_C

4

U1

TP_C

PU_RSVD37

W1

4

PU_RSVD38

TP_C

3

P1

TP_C

PU_RSVD39

AT4

9

TP_C

PU_RSVD40

4

K2

PU_RSVD41

TP_C

AH2

TP_C

PU_RSVD42

AG

13

PU_RSVD43

TP_C

14

AM

TP_C

PU_RSVD44

AM

15

TP_C

PU_RSVD45

0

N5

TP

_DC_TEST_A4

A4

C4

_TEST_C4_D3

DC

D3

T

_DC_TEST_D1

P

D1

C_TEST_A58

TP_D

A58

A59

_TEST_A59_C59

DC

C59

A61

_TEST_A61_C61

DC

C61

TP_D

C_TEST_D61

D61

TP

_DC_TEST_BD61

BD61

BE61

BE59

BG61

BG59

BG58

BG4

BG3

BE3

BE3

BG1

BE1

BE1

BD1

BE59_BE61

DC_TEST_

DC

_TEST_BG59_BG61

_DC_TEST_BG58

TP

_DC_TEST_BG4

TP

DC_TEST_

BE3_BG3

BE1_BG1

DC_TEST_

_DC_TEST_BD1

TP

T45

T45

T46

T46

T47

T47

T48

T48

T49

T49

T50

T50

T51

T51

T52

T52

T53

T53

T55

T55

T109 P

T109 P

T110 P

T110 P

T111 P

T111 P

T112 P

T112 P

T113 P

T113 P

T114 P

T114 P

T115 P

T115 P

T116 P

T116 P

T117 P

T117 P

T118 P

T118 P

T119 P

T119 P

T120 P

T120 P

T121 P

T121 P

T122 P

T122 P

T123 P

T123 P

T124 P

T124 P

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

PAD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

AD~D@

Display Port Presence Strap

PCIE Port Bifurcation Straps

CFG[6:5]

definition matches socket pin map definition

0:Lane Reversed

CFG

1 : Disabled; No Physical Display Port

CFG4

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

CFG

CFG

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Device 1 function 1 enabled ; function 2

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

@

@

1K

1K

12

RC51

RC51

_0402_1%~D

_0402_1%~D

4

1K

1K

12

@

@

_0402_1%~D

_0402_1%~D

RC52

RC52

6

5

1K_0402_1%~D

1K_0402_1%~D

1K

1K

12

12

@RC54

@

@

@

_0402_1%~D

_0402_1%~D

RC54

RC53

RC53

-BRIDGE_BGA1023~D

-BRIDGE_BGA1023~D

SANDY

SANDY

CFG

7

@

@

1K

1K

12

RC56

RC56

_0402_1%~D

_0402_1%~D

PEG DEFER TRAINING

1: (Default) PEG Train immediately

CFG7

following xxRESETB de assertion

A A

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

0: PEG Wait for BIOS for training

DELL CONFIDENTIAL

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

mpal Electronics, Inc.

mpal Electronics, Inc.

mpal Electronics, Inc.

Co

Co

Co

Sa

Sa

Sa

LA

LA

LA

-6611P

-6611P

dnesday, January 26, 2011

dnesday, January 26, 2011

dnesday, January 26, 2011

-6611P

/PROPRIETARY

ndy Bridge (4/6)

ndy Bridge (4/6)

ndy Bridge (4/6)

964We

964We

964We

1

0.3

0.3

0.3

of

of

of

Page 10

5

CC_CORE

+V

D D

C C

2.

2.

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

1

2

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

1

2

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

1

2

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

1

2

,ŝŐŚͲ&ƌĞƋƵĞŶĐLJĞĐŽƵƉůŝŶŐ

2.2U_0402_6.3V6M~D

2.

2.

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

CC67

CC67

CC75

CC75

1

2

2.

2.

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

CC94

CC94

CC

CC

1

104

104

2

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

CC

CC

CC

CC

1

122

122

124

124

2

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

CC

CC

CC

CC

1

148

148

151

151

2

2.2U_0402_6.3V6M~D

2.

2.

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

CC

CC

CC76

CC76

1

1

2

2.

2.

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

1

2

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

1

2

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

1

2

1

123

123

2

2

2.

2.

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

CC95

CC95

CC96

CC96

1

1

2

2

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

CC

CC

CC

CC

1

127

127

125

125

2

@

@

CC

CC

1

152

152

2

@

@

2.

2.

2.

2.

2.

2.

2.

2.

2.

2.

2.

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

CC87

CC87

CC77

CC77

1

2

2.

2.

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

CC97

CC97

CC

CC

1

100

100

2

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

CC

CC

1

143

143

2

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

CC

CC

CC

CC

1

154

154

157

157

2

2U_0402_6.3V6M~D

CC71

CC71

CC72

CC72

1

1

2

2

2.

2.

2.

2.

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

CC98

CC98

CC99

CC99

1

1

2

2

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

C

C

1

C

C

201

201

2

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

CC

CC

CC

CC

1

1

155

155

160

160

2

2

@

@

2.

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

CC8

CC8

CC73

CC73

1

1

1

8

8

2

2

2

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

C

C

CC

CC

1

1

C

C

121

121

198

198

2

2

@

@

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

CC

CC

C

C

1

1

C

C

158

158

159

159

2

2

DŝĚͲ&ƌĞƋƵĞŶĐLJĞĐŽƵƉůŝŶŐ

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

1

1

CC

CC

CC

CC

111

111

110

B B

110

2

2

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

1

1

CC

CC

CC

CC

115

115

116

116

2

2

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

1

C

C

C

C

112

112

2

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

1

C

C

C

C

117

117

2

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

1

CC

CC

113

113

2

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

1

CC

CC

118

118

2

22U_0805_6.3VAM~D

1

1

CC

CC

CC

CC

114

114

181

181

2

2

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

1

1

CC

CC

CC

CC

119

119

186

186

2

2

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

1

1

CC

CC

C

C

C

C

183

183

182

182

2

2

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

1

1

C

C

CC

CC

C

C

187

187

189

189

2

2

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

1

1

1

CC

CC

CC

CC

185

185

184

184

2

1

CC

CC

188

188

2

2

2

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

1

1

CC

CC

190

190

2

2

>ŽǁͲ&ƌĞƋƵĞŶĐLJĞĐŽƵƉůŝŶŐ

1

+

+

9

9

CC12

CC12

470U_D2_2V-M~D

470U_D2_2V-M~D

2 3

A A

1

+

+

CC13

CC13

470U_D2_2V-M~D

470U_D2_2V-M~D

2 3

0

0

1

+

+

131

131

CC

CC

470U_D2_2V-M~D

470U_D2_2V-M~D

2 3

1

+

+

CC13

CC13

470U_D2_2V-M~D

470U_D2_2V-M~D

2 3

2

2

4

U1F

CC_CORE

+V

U1F

53A

A26

]

VCC[1

A29

VCC[2

]

A31

3

]

VCC[

A34

]

VCC[4

A35

VCC[5

]

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

2.2U_0402_6.3V6M~D

2.

2.

2U_0402_6.3V6M~D

2U_0402_6.3V6M~D

CC74

CC74

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

22U_0805_6.3VAM~D

1

CC

CC

CC

CC

194

194

192

192

2