Page 1

A

1 1

B

C

D

E

Compal Confidential

2 2

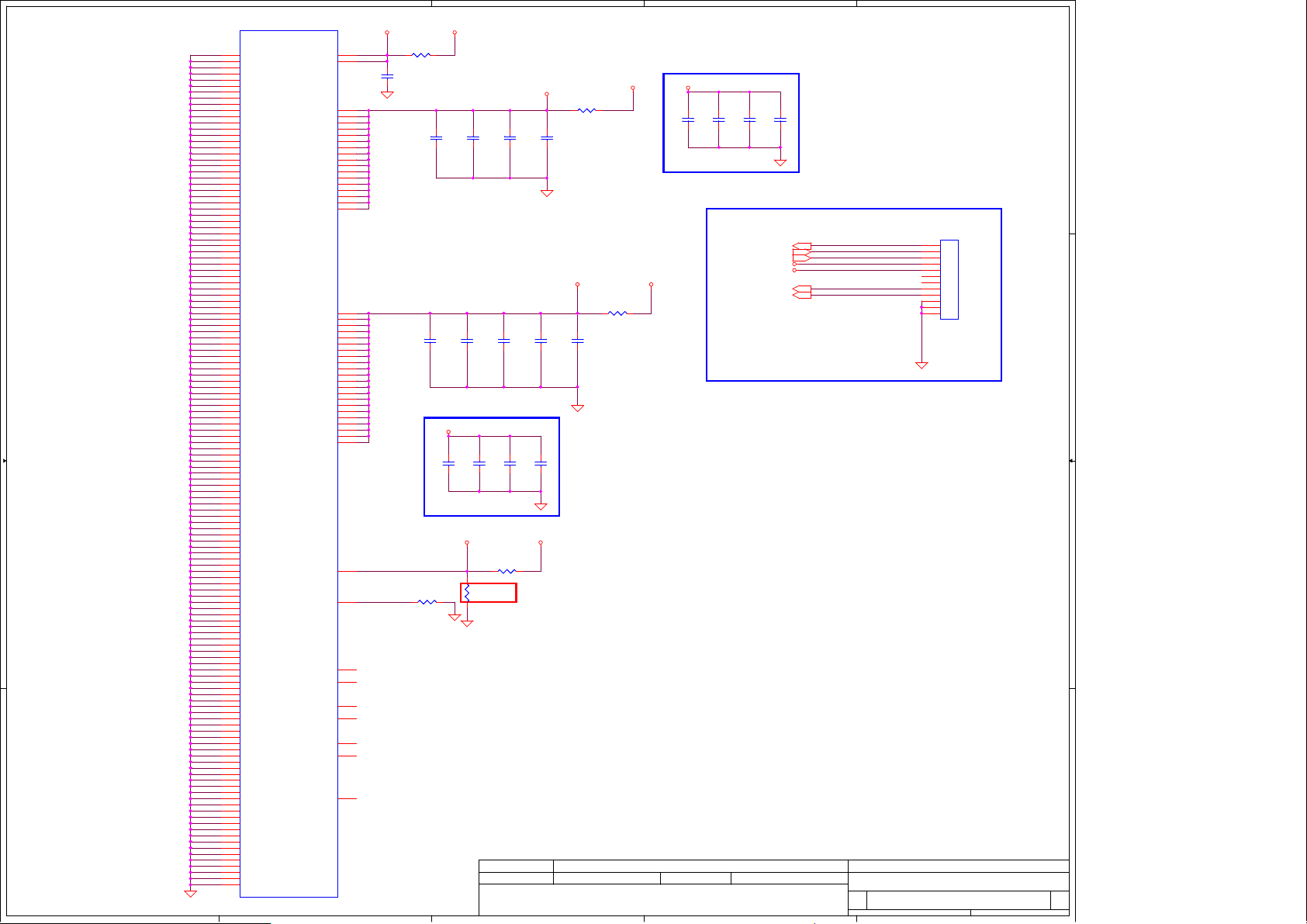

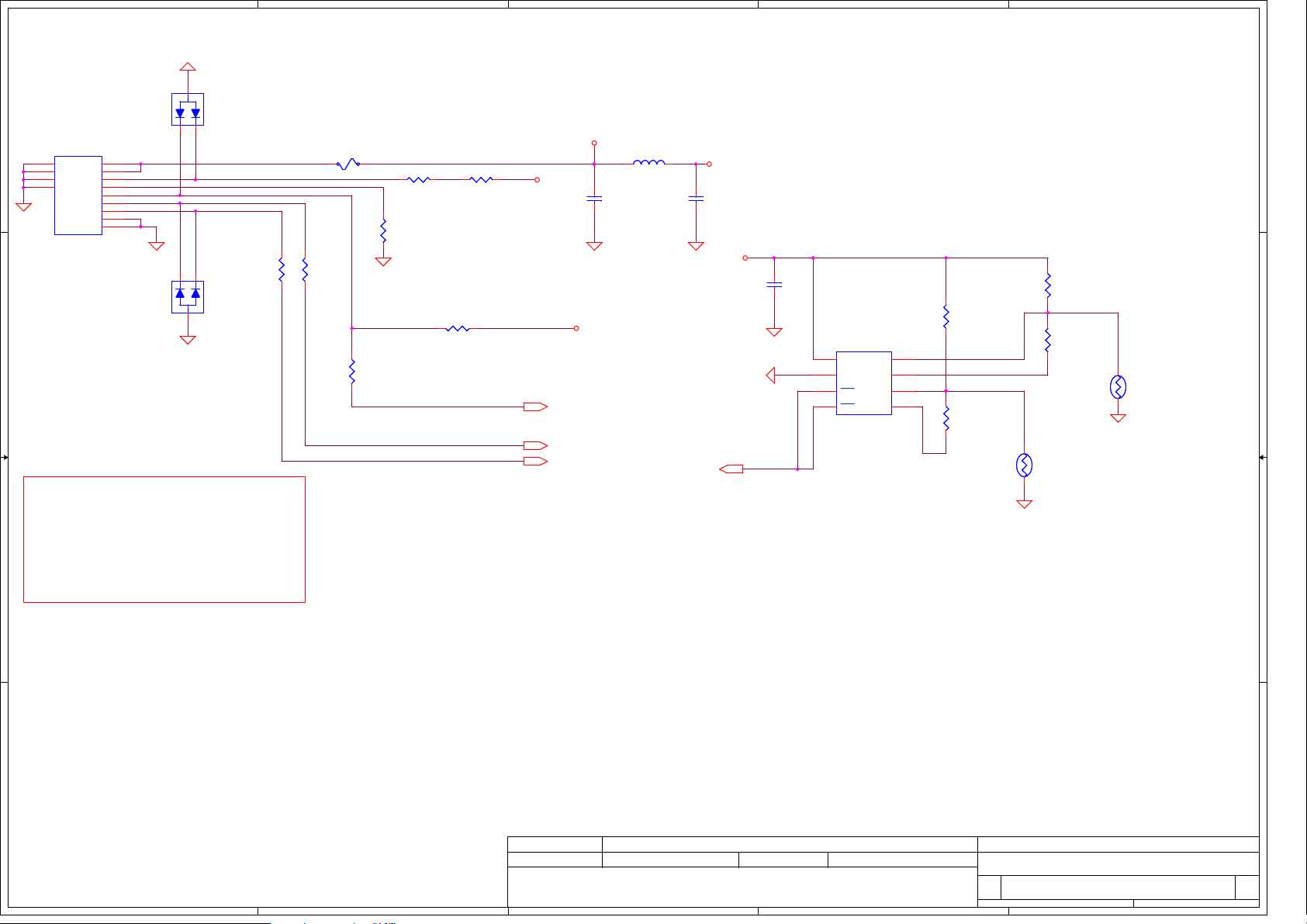

PAZ00 Schematics Document

Nvdia(T20) + four x4 DDRII

2010-07-15

REV: 1.0a

3 3

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

2008/09/202006/08/18

2008/09/202006/08/18

2008/09/202006/08/18

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

T20 schematic

T20 schematic

Wednesday, July 21, 2010

Wednesday, July 21, 2010

Wednesday, July 21, 2010

T20 schematic

E

0.1

0.1

1

1

1

0.1

33

33

33

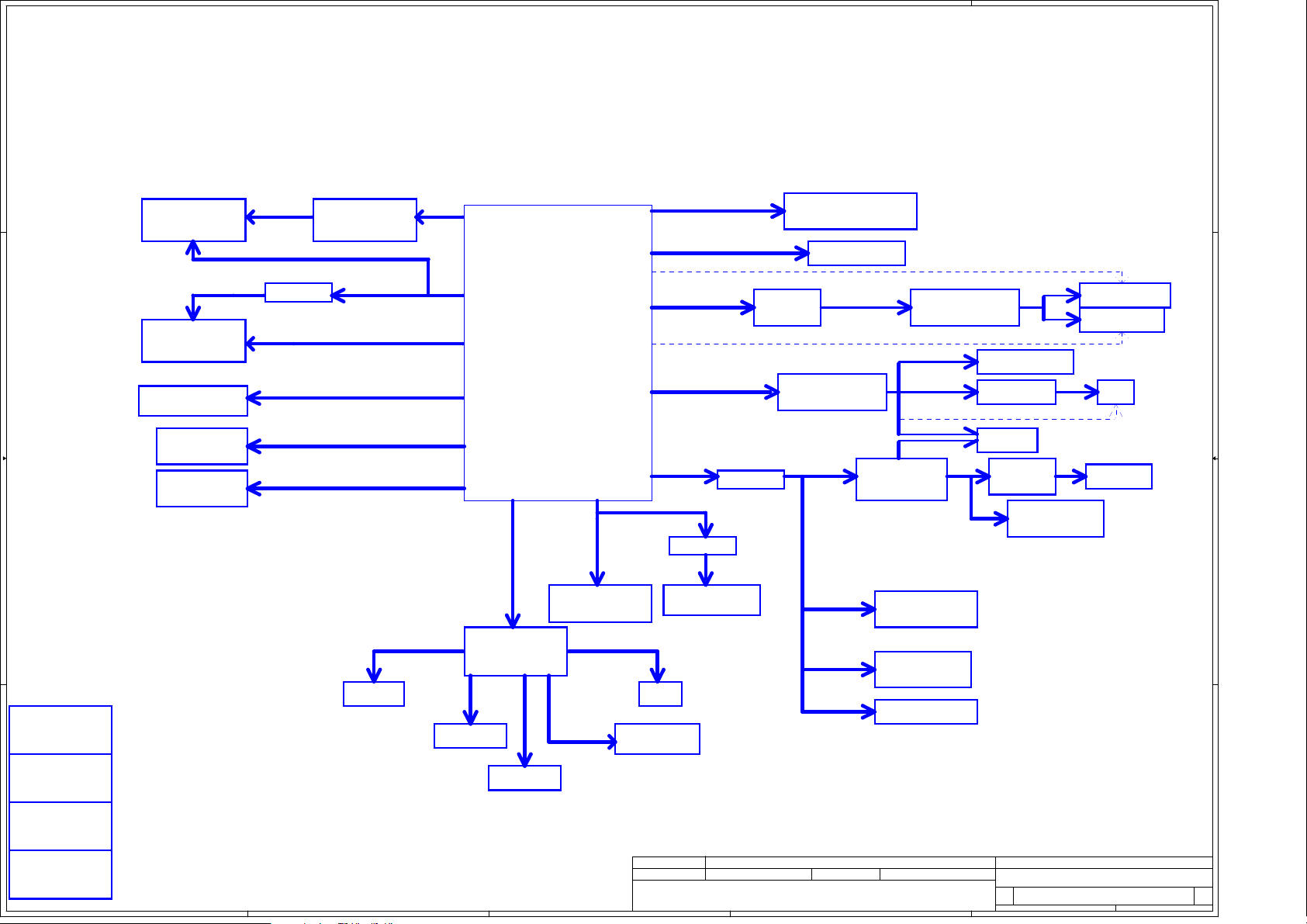

Page 2

A

1 1

B

C

D

E

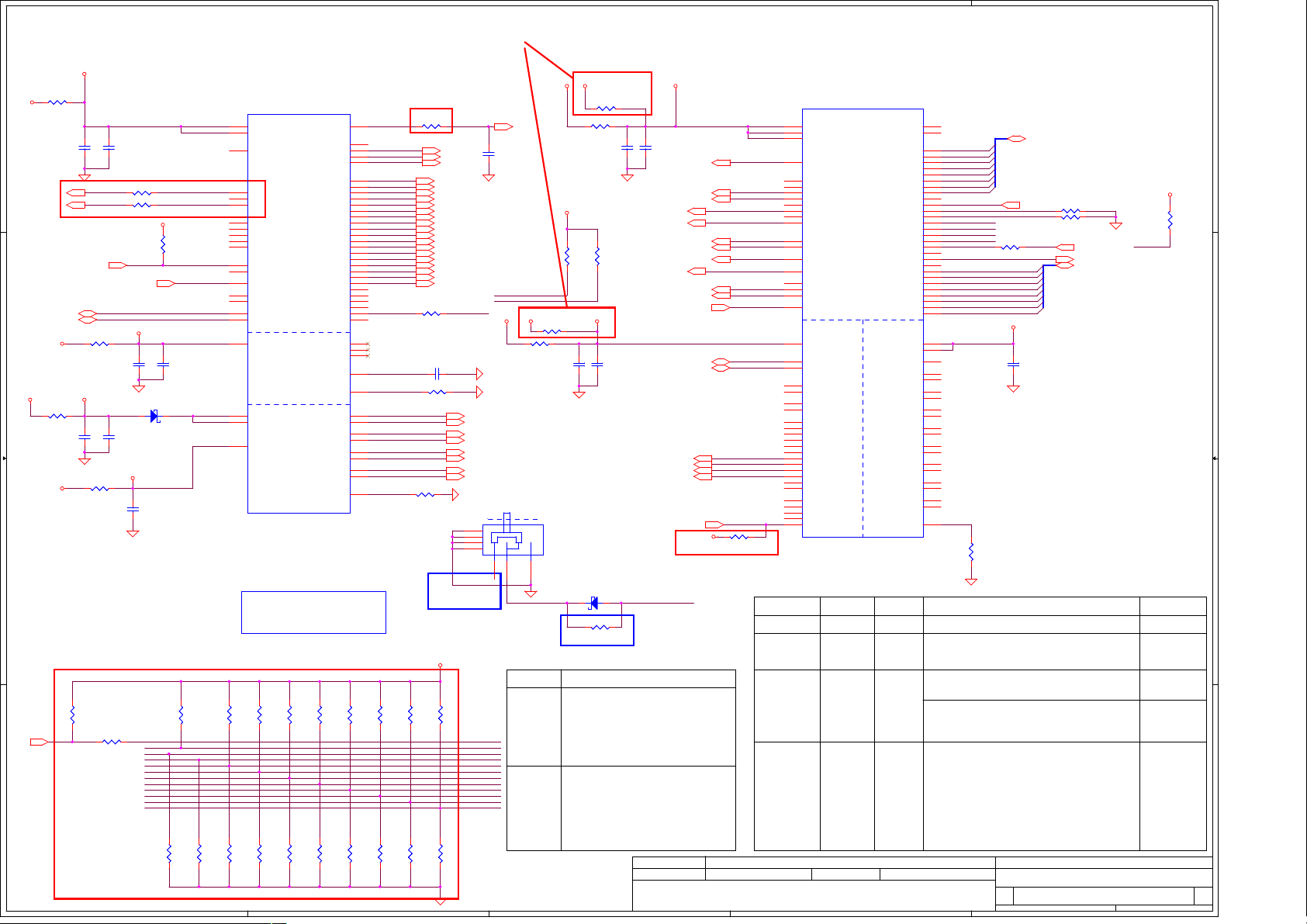

LCD Conn.

LVDS

DDC_I2C(5V)

2 2

HDMI Conn.

I2C LEVEL Shifter

LVDS Bridge

SN75LVDS83

DDC_I2C(3,3V)

HDMI

RGB

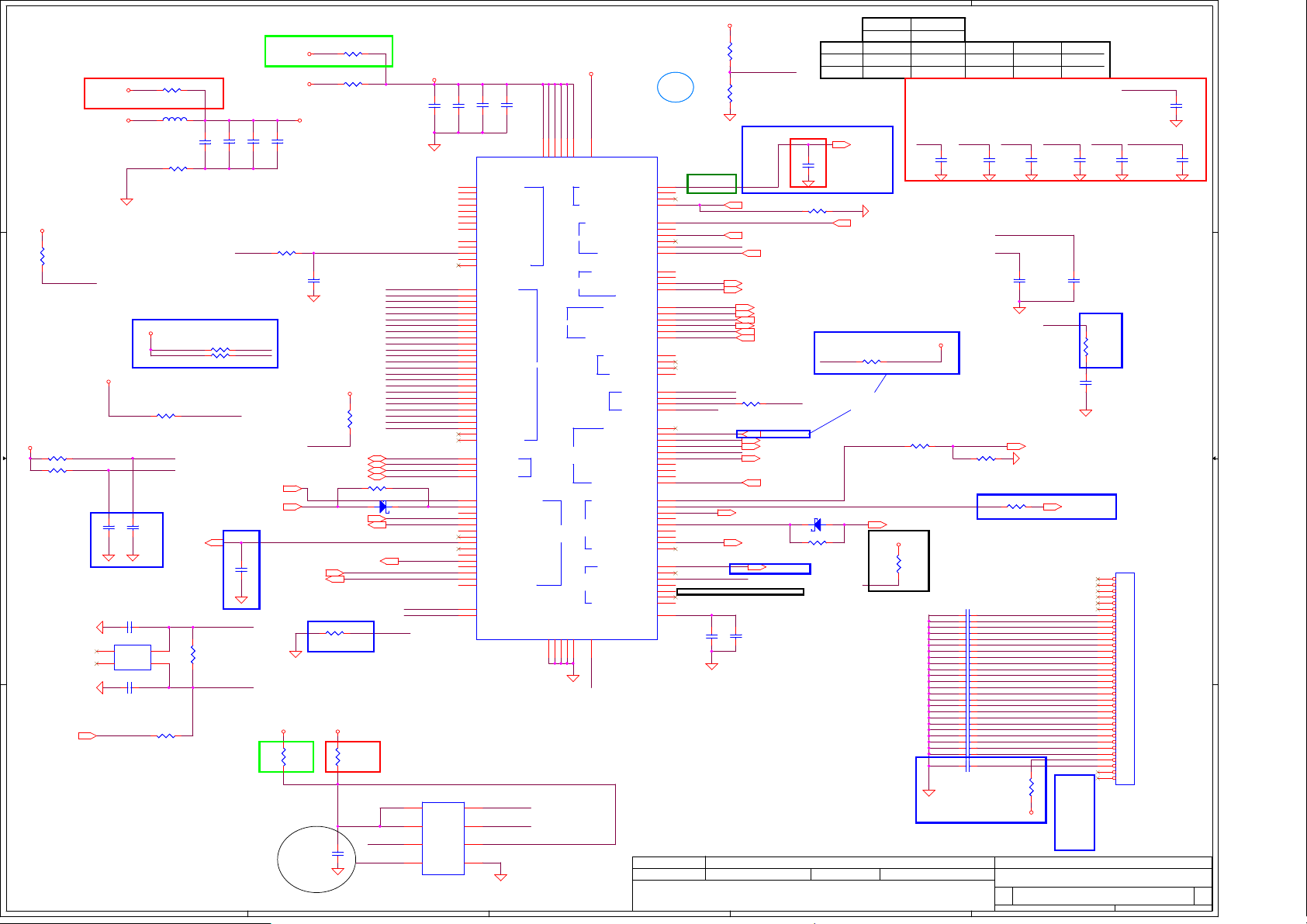

Nvidia Tegra T20

DDR2

USB1(Client)

(For Sirius sku)

UART

(For Procyon sku)

ULPI

(For Sirius sku)

SDIO

DDR2 SDRAM * 4

512M/1GB

USB PHY

(USB3315)

USB Port (Mini)

USB2 (HOST)

USB Hub *2 port

SMSC USB 2512

BT module

WIFI

USB Port (Full)

SD/MMC conn

SDIO1(3.3V)

eMMC

HSMMC

(4/8/16/32GB)

NAND Flash

(128M)

CAM_I2C(3.3V)

3 3

PWR_I2C(1.8V)

PMU

TI TPS658621

ENE KBC

PS2

KB926

USB3 (Host)

GNE_I2C(1.8V) GNE_I2C(3.3V)

I2C LEVEL Shifter

I2C LEVEL Shifter

PWR_I2C(3.3V)

Thermal Sensor

ADI ADT7421

USB Hub *4 port

SMSC USB 2514

GNE_I2C(3.3V)

GNE_I2C(3.3V)

USB2.0

USB 2.0

DMIC

Audio Codec

ALC5632

G-SENSOR

Bosch BMA150

Light sensor

WWAN

Webcam

Audio AMP

TPA6017

HeadPhone/Ext. MIC

SIM

Speaker

Intersil 29011

LED T/P

SPI

GNE_I2C(3.3V)

TPM ST19NP18

DC/DC Interface

SPI ROM

EC_I2C(3.3V)

Battery

DC IN

4 4

Keyboard

BATT IN

Security Classification

Security Classification

CHARGER

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

A

B

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

C

2008/12/22 2009/12/22

2008/12/22 2009/12/22

2008/12/22 2009/12/22

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Block Diagram

Block Diagram

Block Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

E

2 33Wednesday, July 21, 2010

2 33Wednesday, July 21, 2010

2 33Wednesday, July 21, 2010

0.1

0.1

0.1

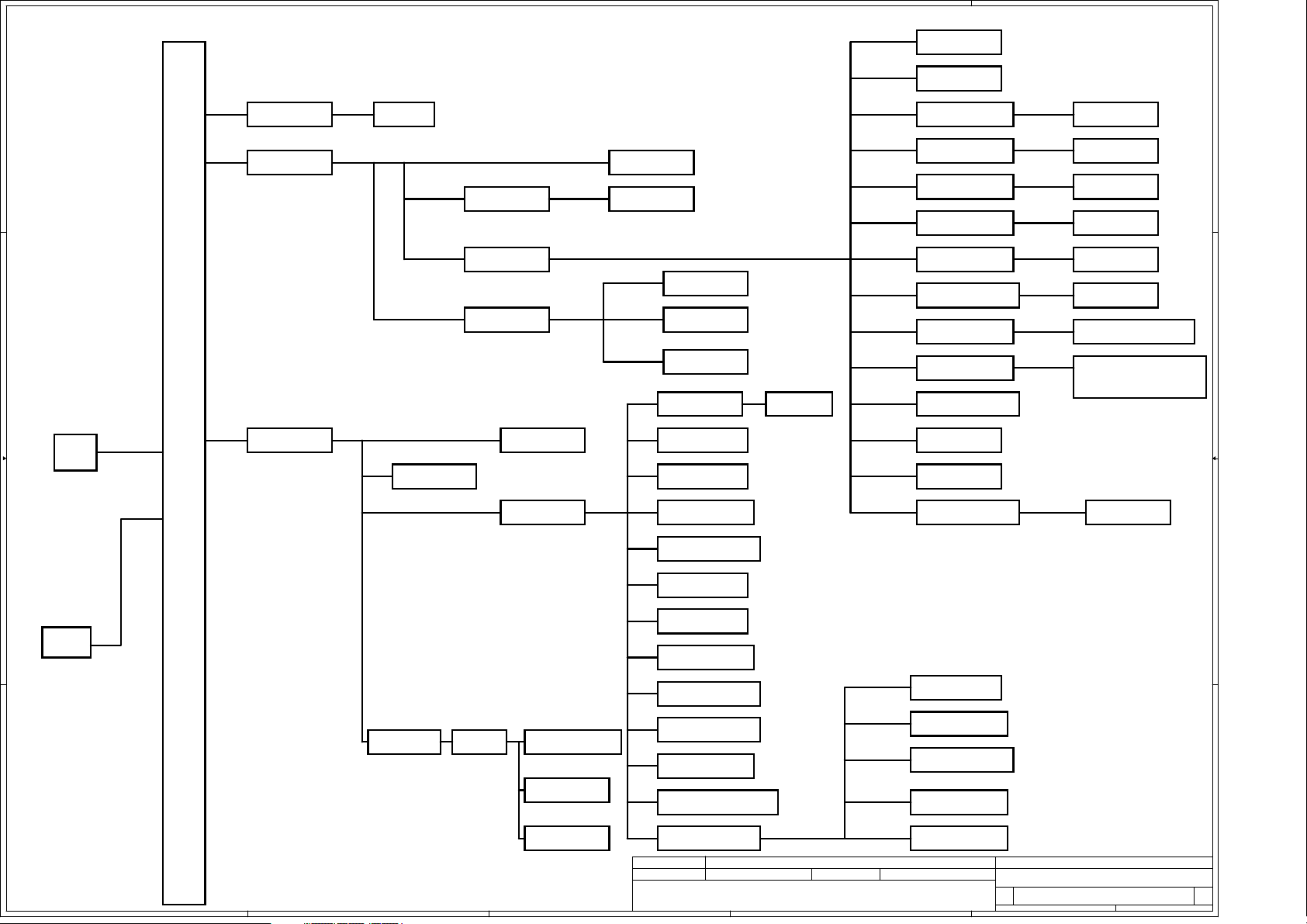

Page 3

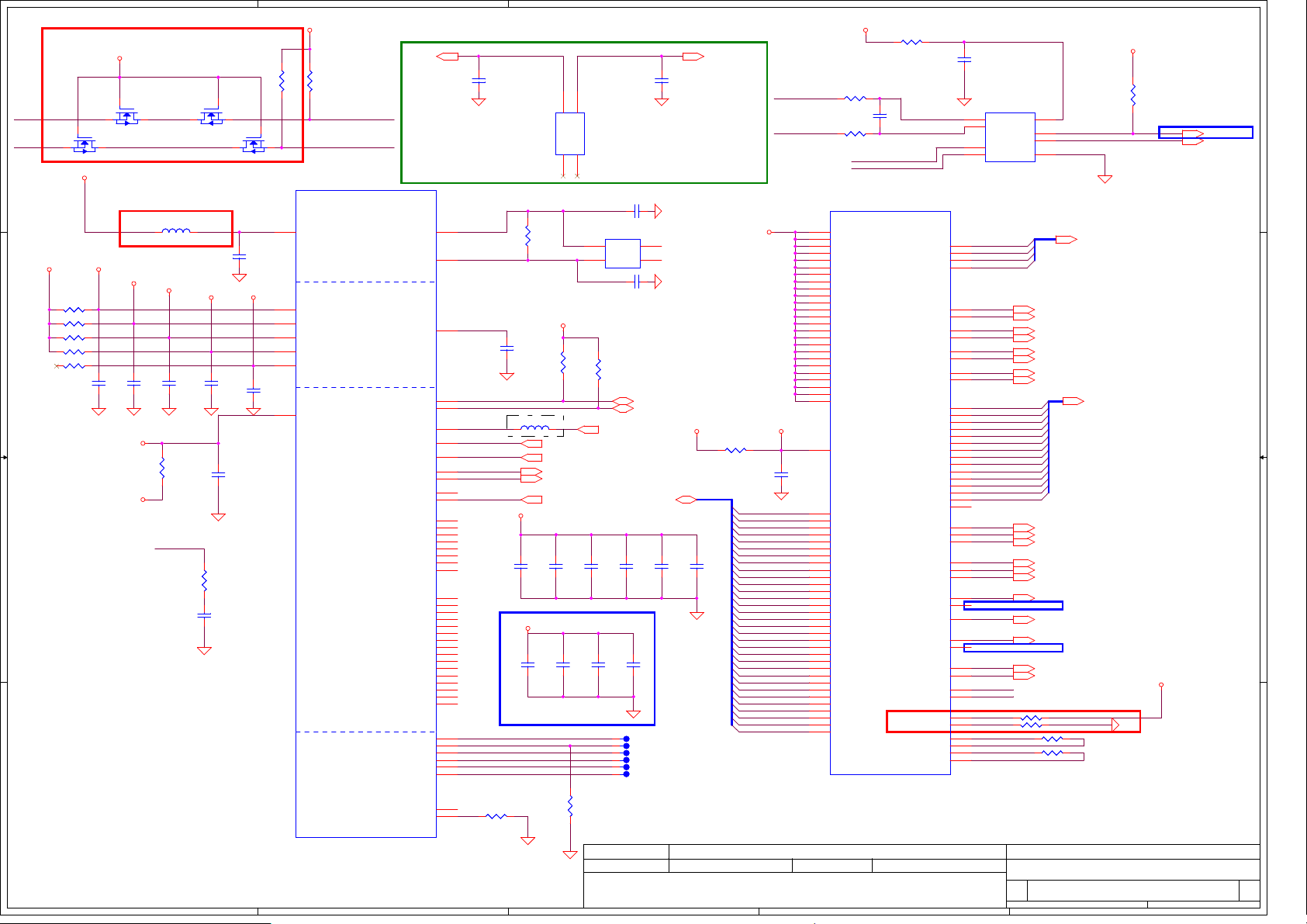

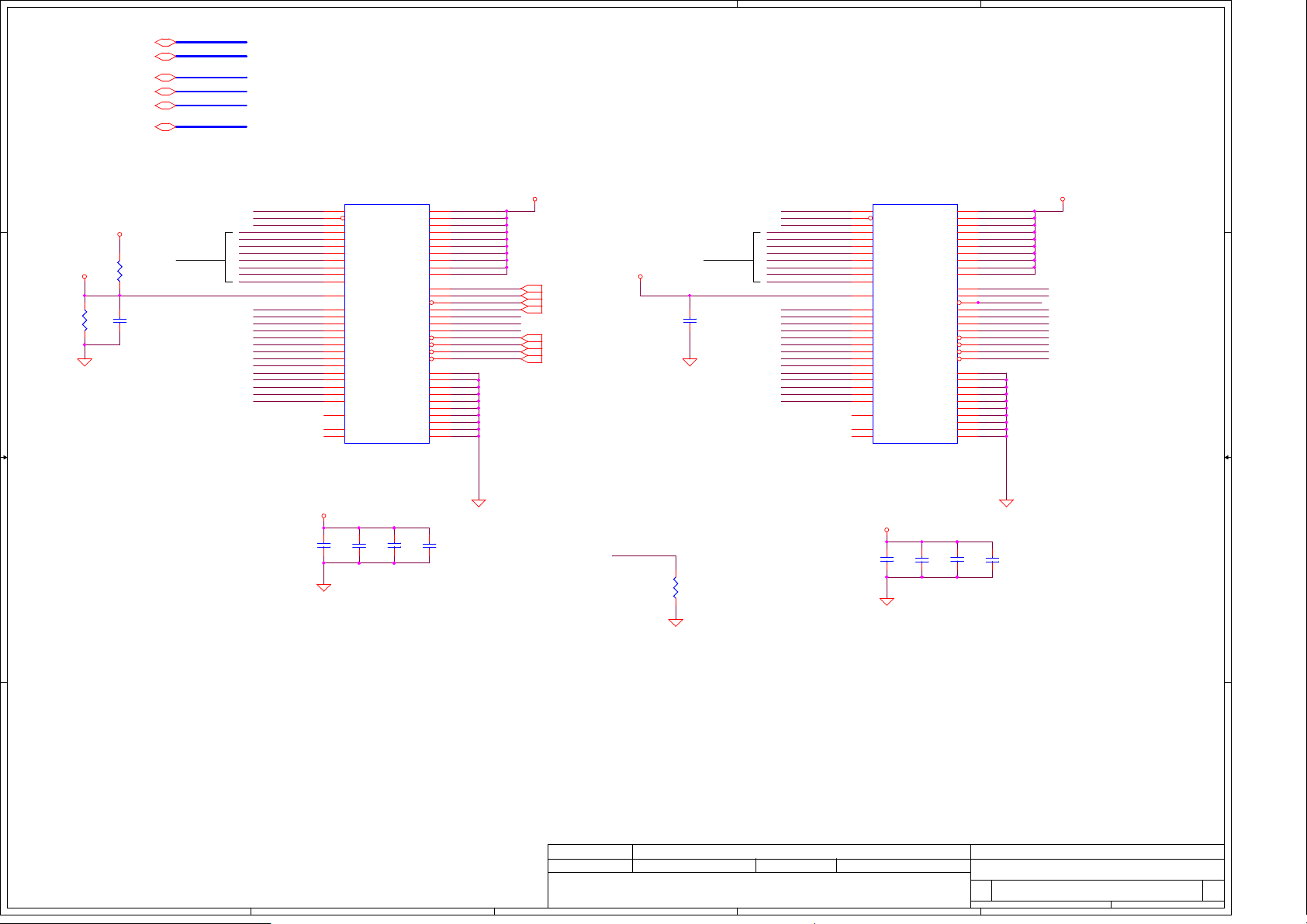

5

4

3

2

1

0.5A

5.5A

1A

D D

+LCD_INV Panel

6.036A

+5VALW

1.25A

+5VS

2A(SB)

0.75A

USB PWR SW

AMP

100mA

160mA

10mA

200mA

2.286A

PMU

C C

4A

0.5A6.5A

0.5A

DDR2

USB PHY+1.8VS

WiFi

20mA

130mA

100mA

100mA

1.2V

1.05VS

+3.3VS_LDO0

+1.1VS_LDO1

+1.2VS_LDO2

+3.3VS_LDO3

+1.8VS_LDO4

+2.85VS_LDO6

+3.3VS_LDO7

+1.8VS_LDO8

100mA

160mA

10mA

200mA

20mA

130mA

100mA

100mA

NC

AVDD_PLL

VDD_RTC

AVDD_USB

AVDD_OSC

AVDD_CRT

HDMI(AVDD_HDMI)

HDMI

(+AVDD_HDMI_PLL)

110mA

600mA

1.5A

150mA

+2.85VS_LDO9

+1.2VS_SM0

+1.0VS_SM1

+2.85VS_LDO5

150mA

EMMC

AC

VIN

B+

6.843A

15.25A

+3VALW KBC

0.5A

SPI ROM

0.5A

14.25A

+3VS

1.5A

+LCD_VDD Panel

0.5A

WebCam

1A

WiFi

1A

WWAN

0.5A

USB PHY

B B

BATTDC

0.45A

T20+3VS_S3

A A

0.15A

+VDDIO_NAND

0.15A

+VDDIO_VI

0.15A

+VDDIO_BB

5

4

1A

USB HUB x2

1A

Codec

0.5A

G sensor

0.5A

BT

0.5A

Light sensor

0.75A

Card Reader

0.5A

Thermal sensor

5A

T20

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

3

2009/08/28 2010/08/28

2009/08/28 2010/08/28

2009/08/28 2010/08/28

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

+VDDIO_LCD

+VDDIO_UART

+VDDIO_AUDIO

+VDD_FUSE

+VDDIO_SDIO

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

LA-5952P

LA-5952P

LA-5952P

Date: Sheet of

Date: Sheet of

Date: Sheet of

Power delivery

Power delivery

Power delivery

1

3 33Wednesday, July 21, 2010

3 33Wednesday, July 21, 2010

3 33Wednesday, July 21, 2010

0.1

0.1

0.1

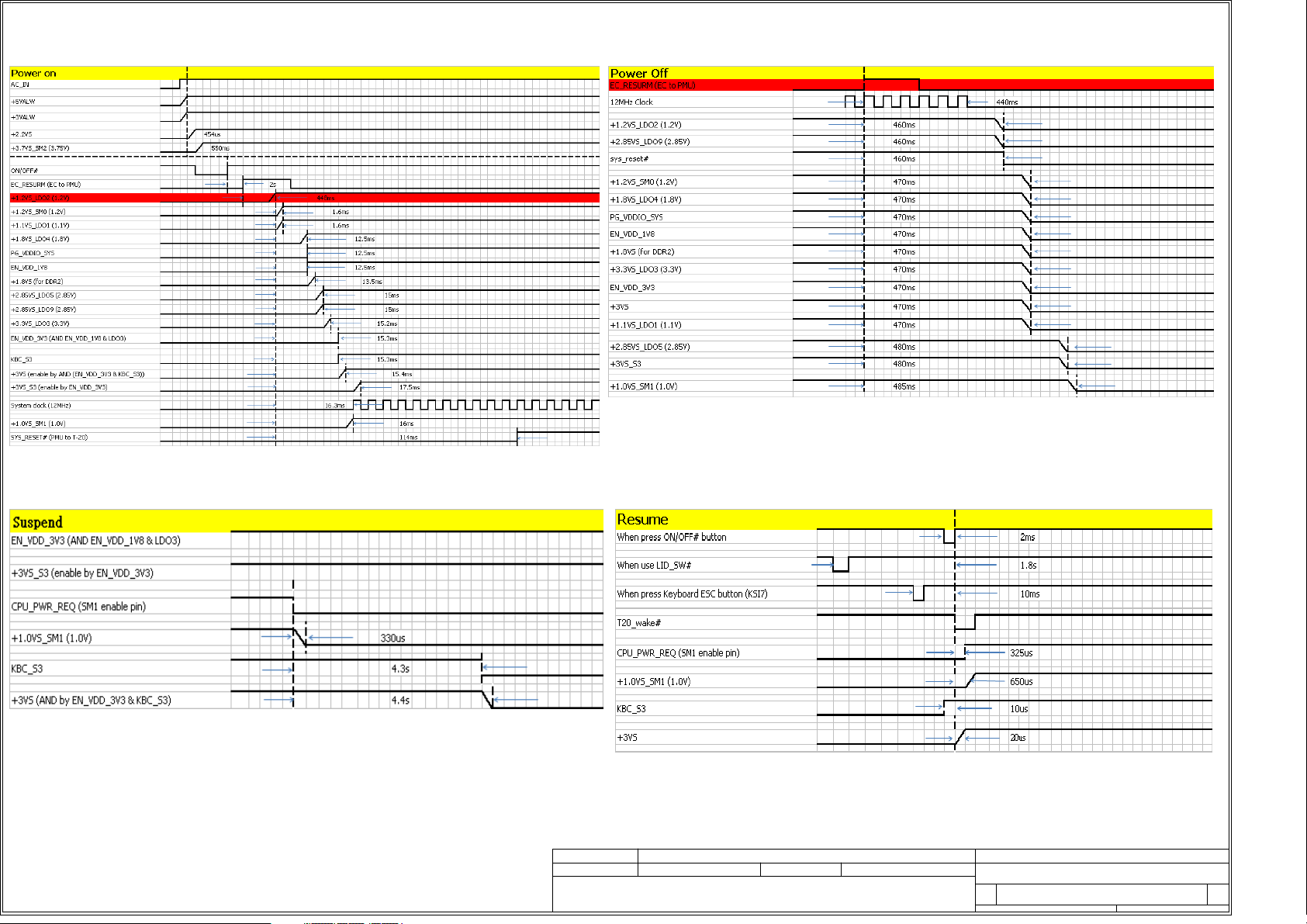

Page 4

A

1 1

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

A

2009/08/28 2010/08/28

2009/08/28 2010/08/28

2009/08/28 2010/08/28

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Power Sequence

Power Sequence

Power Sequence

LA-5952P

LA-5952P

LA-5952P

4 33Wednesday, July 21, 2010

4 33Wednesday, July 21, 2010

4 33Wednesday, July 21, 2010

0.1

0.1

0.1

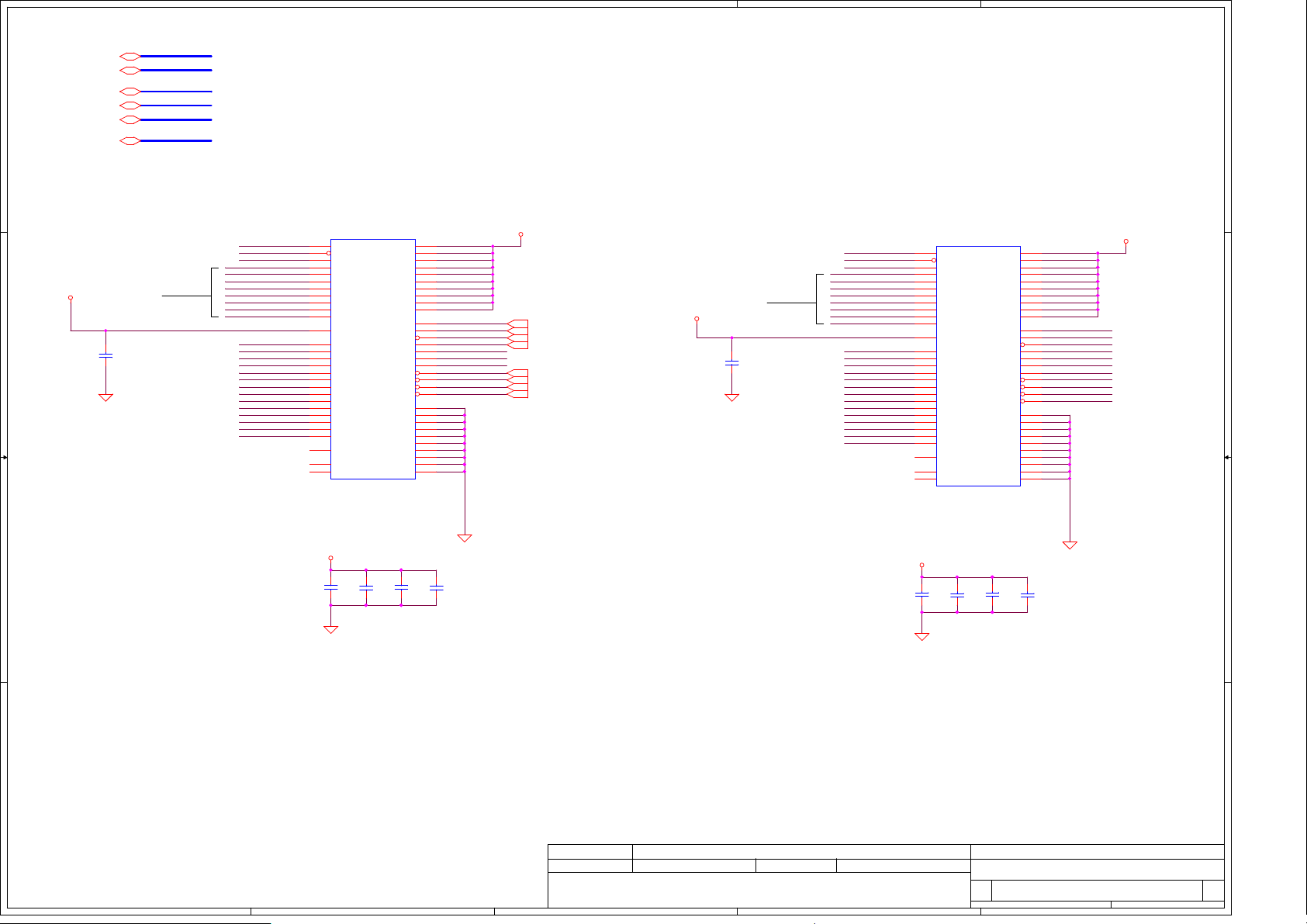

Page 5

A

B

C

D

E

Voltage Rails

S5

DescriptionPower Plane

VIN

B+

1 1

2 2

+VDD_CPU

+1.8V

+VDD_CORE

+RTCVCC RTC power

+3VS_S3 3.3V switched power rail ON OFFON

+3VALW

+3VS

+5VALW

+5VS

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

I2C/SM BUS Control

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

1.8V power rail for DDR

VCCP switched power rail

3.3V always on power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

S3S1

N/AN/AN/A

N/A N/A N/A

OFF

OFFON

ON

ON

ON

ON

ON

OFF

OFFOFFON

ONONON

ON ON*

OFF

OFF

ON ON*

OFF

OFFON

BOM configuration

BOM configuration

BOM configurationBOM configuration

@ : For reserve.

@ : For reserve.

@ : For reserve.@ : For reserve.

45@ : For 45 level.

45@ : For 45 level.

45@ : For 45 level.45@ : For 45 level.

PR@ : For Procyon sku only

PR@ : For Procyon sku only

PR@ : For Procyon sku onlyPR@ : For Procyon sku only

SI@ : For Sirius sku only

SI@ : For Sirius sku only

SI@ : For Sirius sku onlySI@ : For Sirius sku only

Table

SOURCE

EC_SMB_CK1

EC_SMB_DA1

DDC_SCL_3P3

DDC_SDA_3P3

CAM_I2C_SCL

CAM_I2C_SDA

GEN1_I2C_SCL

GEN1_I2C_SDA

PWR_I2C_SCL

3 3

PWR_I2C_SDA

(3.3V)

(3.3V)

(3.3V)

(3.3V)

(1.8V)

KB926

T-20

T-20

T-20

T-20

T-20

EC

KB926

V

(3.3V)

Battery PMIC

V

(3.3V)

V

(1.8V)

Thermal

Sensor

V

(3.3V)

Audio

Codec

V

(3.3V)

G sensor TPM

V

(3.3V)

V

(3.3V)

Light

sensor

V

(3.3V)

HDMI

V

(3.3V)

LCD

Panel

V

(3.3V)

ZZZ1

ZZZ1

X76 Hynix

X76 Hynix

X7624051L02

X7624051L02

ZZZ

ZZZ

PCB_LA-63 52P

PCB_LA-63 52P

DAZ0EF00100

DAZ0EF00100

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS T HE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS T HE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS T HE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUST ODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUST ODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUST ODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

2008/09/ 202006/08/ 18

2008/09/ 202006/08/ 18

2008/09/ 202006/08/ 18

D

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

Wednesd ay, July 21, 2010

Wednesd ay, July 21, 2010

Wednesd ay, July 21, 2010

E

5 33

5 33

5 33

0.1

0.1

0.1

Page 6

5

4

3

2

1

S3 PWR modify P VT

+VDDIO_LCD

+3VS

D D

LVDS_SHTDN#13

EN_VDD_PNL8,13

+2.85VS_LDO6

C C

+3.3VS_LDO7

B B

A A

12

R1 0_0402_5%R1 0_0402_5%

1

1

C3 0.1U_0201_6.3V6KC3 0.1U_0201_6.3V6K

Reverse T20.T25 to

C24.7U_0603_6.3V6K C24.7U_0603_6.3V6K

2

2

EN_VDD_PNL ,

T20.V25 to LVDS _SHTDN#

LVDS_SHTDN# LVDS_SHTDN#_PWR0

EN_VDD_PNL EN_VDD_PNL_PWR2

TEMP_ALERT#7

DDC_SCL_3P314

DDC_SDA_3P314

R12 0_0402_5%R12 0_0402_5%

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

+1.8VS_LDO8

Change R to 040 2(PVT),

Change all pull down resistor to 10K by NVIDI A suggest.(PVT2 )

FORCE_RECOVERY#

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

+AVDD_HDMI

12

1

C12

C12

2

12

R21

R21

47K_0402_1%

47K_0402_1%

+AVDD_VDAC

R9 0_0402_5%

R9 0_0402_5%

@

@

R13 0_0402_5%R13 0_0402_5%

19

R31

R31

1 2

47K_0402_1%

47K_0402_1%

R1270 0_0402_5%@R1270 0_0402_5%@

R1271 0_0402_5%@R1271 0_0402_5%@

HDMI_HPD14,19

DDC_SCL_3P3

DDC_SDA_3P3

12

C6

C6

3.3V

1

C13

C13

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

+AVDD_HDMI_PLL

12

1

2

5

12

12

+VDDIO_LCD

12

2.85V

1

1

C7

C7

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

2

D12

D12

2 1

RB161M-20_SOD123-2

RB161M-20_SOD123-2

C14

C14

0.1U_0402_10V7K

0.1U_0402_10V7K

R22

R22

12

R32

R32

R7

R7

100K_0402_1%

100K_0402_1%

TEMP_ALERT#

HDMI_HPD

1.8V

12

100K_0402_5%

100K_0402_5%

12

R33

R33

10K_0402_5%

10K_0402_5%

@R34

@

10K_0402_5%

10K_0402_5%

R23

R23

R34

U1D

U1D

U22

VDDIO_LCD1

V22

VDDIO_LCD2

Y24

LCD_M1

AD24

LCD_PWR0

U24

LCD_PWR1

AA24

LCD_PWR2

AB21

LCD_SCK

V24

LCD_CS0#

AC25

LCD_CS1#

AA25

LCD_SDOUT

W25

LCD_SDIN

AD23

LCD_DC0

AC24

LCD_DC1

V23

HDMI_INT#

Y22

CRT_HSYNC

AC23

CRT_VSYNC

W23

DDC_SCL

Y23

DDC_SDA

AH17

AVDD_VDAC

AA15

AVDD_HDMI_1

Y15

AVDD_HDMI_2

AA12

AVDD_HDMI_PLL

T20-H-A2 1G_FCBGA 664P

T20-H-A2 1G_FCBGA 664P

GMI_AD12

GMI_AD13

GMI_AD14

GMI_AD15

12

@

@

R24

R24

100K_0402_5%

100K_0402_5%

12

R35

R35

10K_0402_5%

10K_0402_5%

LCD_HSYNC

LCD_VSYNC

LCD

LCD

CRT

CRT

VDAC_VREF

VDAC_RSET

HDMI_TXCN

HDMI_TXD0N

HDMI_TXD0P

HDMI_TXD1N

HDMI_TXD1P

HDMI_TXD2N

HDMI_TXD2P

HDMI

HDMI

eMMC boot NAND boot

1 1

0

0

12

12

@

@

@

@

R25

R25

R26

R26

100K_0402_5%

100K_0402_5%

100K_0402_5%

100K_0402_5%

12

12

R36

R36

R37

R37

10K_0402_5%

10K_0402_5%

10K_0402_5%

10K_0402_5%

Change R1253 to SD028330A80

for RoHS part n eed

LCD_PCLK_R

V28

LCD_PCLK

AE24

LCD_WR#

LCD_DE

LCD_D00

LCD_D01

LCD_D02

LCD_D03

LCD_D04

LCD_D05

LCD_D06

LCD_D07

LCD_D08

LCD_D09

LCD_D10

LCD_D11

LCD_D12

LCD_D13

LCD_D14

LCD_D15

LCD_D16

LCD_D17

LCD_D18

LCD_D19

LCD_D20

LCD_D21

LCD_D22

LCD_D23

VDAC_R

VDAC_G

VDAC_B

HDMI_TXCP

HDMI_RSET

12

100K_0402_5%

100K_0402_5%

12

@R38

@

10K_0402_5%

10K_0402_5%

LCD_DE

U23

LCD_HSYNC

AD27

LCD_VSYNC

AD26

LCD_D00

AA26

LCD_D01

AC26

LCD_D02

AC27

LCD_D03

AC28

LCD_D04

AD25

LCD_D05

AD28

LCD_D06

Y26

LCD_D07

Y27

LCD_D08

Y28

LCD_D09

Y25

LCD_D10

AA28

LCD_D11

AA27

LCD_D12

U25

LCD_D13

U28

LCD_D14

U27

LCD_D15

U26

LCD_D16

V27

LCD_D17

V26

AB25

AA23

AB23

AA22

LVDS_SHTDN#_V25 LVDS_SHTDN#

V25

AC22

AB17

AB18

AE19

VDAC_VREF

AC17

VDAC_RSET

AE18

HDMI_TXCN

AF17

HDMI_TXCP

AG17

HDMI_TXD0N

AE16

HDMI_TXD0P

AE17

HDMI_TXD1N

AC18

HDMI_TXD1P

AD18

HDMI_TXD2N

AH18

HDMI_TXD2P

AG18

HDMI_RSET

AF18

100K_0402_5%

100K_0402_5%

@R39

@

10K_0402_5%

10K_0402_5%

12

@

@

R28

R28

R29

R29

100K_0402_5%

100K_0402_5%

12

R40

R40

R39

10K_0402_5%

10K_0402_5%

4

01EVT remove pull high

TO@

TO@

SAN@

SAN@

10

0

0

12

@

@

R27

R27

12

R38

R14 1K_0402_1%R 14 1K_0402_1%

12

12

R1253

R1253

12

33_0402_5%

33_0402_5%

LCD_DE 13

LCD_HSYNC 13

LCD_VSYNC 13

LCD_D00 13

LCD_D01 13

LCD_D02 13

LCD_D03 13

LCD_D04 13

LCD_D05 13

LCD_D06 13

LCD_D07 13

LCD_D08 13

LCD_D09 13

LCD_D10 13

LCD_D11 13

LCD_D12 13

LCD_D13 13

LCD_D14 13

LCD_D15 13

LCD_D16 13

LCD_D17 13

12

R1272 0_0402_5%R1272 0_0402_5%

C9 0.1U_0402_10V7KC9 0.1U_0402_10V7K

1 2

1 2

R11 1K_0402_1%R 11 1K_0402_1%

12

+VDDIO_NAND

12

@

@

R30

R30

100K_0402_5%

100K_0402_5%

12

R41

R41

10K_0402_5%

10K_0402_5%

LCD_PCLK

C1

C1

10P_0201_25V8

10P_0201_25V8

1 2

@

@

CAM_I2C_SCL

CAM_I2C_SDA

+3VS

HDMI_TXCN 14

HDMI_TXCP 14

HDMI_TXD0N 14

HDMI_TXD0P 14

HDMI_TXD1N 14

HDMI_TXD1P 14

HDMI_TXD2N 14

HDMI_TXD2P 14

SW1

@SW1

@

NSS507-212F-CCCG1T_3P

NSS507-212F-CCCG1T_3P

4

4

5

5

6

6

7

7

1

PAZ00 Procyon D DR / eMMC strap pin define

Net Name Description

100K_0402_5%

100K_0402_5%

NAND_RE#

NAND_WE#

NAND_CLE

NAND_ALE

GMI_AD12

GMI_AD13

GMI_AD14

GMI_AD15

NAND_D4

NAND_D5

NAND_D6

NAND_D7

SAN@ : SNADISK eMMC use

10K_0402_5%

10K_0402_5%

TO@ : Toshiba e MMC use

LCD_PCLK 13

+VDDIO_VI

R17

R17

2.2K_0402_5%

2.2K_0402_5%

+3VS_S3

R1279 0_0402_5%R1279 0_0402_5%

R10 0_0402_5%@ R10 0_0402_5%@

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

33221

RB751V-40TE17_SOD323-2

RB751V-40TE17_SOD323-2

NAND_D4

NAND_D5

NAND_D6

NAND_D7

+3VS

+3VS_S3

R1278 0_0402_5%R1278 0_0402_5%

12

R4 0_0402_5%@ R4 0_0402_5%@

C4

C4

2.2U_0603_6.3V6K

2.2U_0603_6.3V6K

12

12

R18

R18

2.2K_0402_5%

2.2K_0402_5%

+VDDIO_VI

12

12

1

1

C8

C8

C10

C10

2

2

0.1U_0402_10V7K

0.1U_0402_10V7K

D15

@ D15

@

1 2

12

R1238 0_0402_5%R1238 0_0402_5%

01EVT bypass SW1.2

NAND_D[5:4] DDR2 RAM configration.

00 Hynix 512M

NAND_D4=0 ; Install R38 ; @R27

NAND_D5=0 ; Install R39 ; @R28

01 Micron 512M

NAND_D4=1 ; Install R27 ; @R38

NAND_D5=0 ; Install R39 ; @R28

NAND_D[7:6] eMMC configration.

00 SANDISK eMMC

NAND_D6=0 ; Install R40 ; @R29

NAND_D7=0 ; Install R41 ; @R30

01 Toshiba eMMC

NAND_D6=1 ; Install R29 ; @R40

NAND_D7=0 ; Install R41 ; @R30

3

+VDDIO_NAND

U1E

12

1

2

1

C5

C5

0.1U_0402_10V7K

0.1U_0402_10V7K

2

NAND_ALE

NAND_CE0

NAND_CE1

HSMMC_CLK

EN_VDDIO_MMC

NAND_RE#

NAND_WE#

NAND_CLE

HSMMC_CMD

NAND_BSY#

NAND_WP#

CAM_I2C_SCL19

CAM_I2C_SDA19

TPM_RESET#

TPM_DATA#

TPM_ACCPCMD

LIGHT_INT

ACCELERO_INT#18

+VDDIO_NAND

SDIO1_CD#18

+VDDIO_VI

NAND_ALE

NAND_CE0

NAND_CE1

HSMMC_CLK

EN_VDDIO_MMC

NAND_RE#

NAND_WE#

NAND_CLE

HSMMC_CMD

NAND_BSY#

NAND_WP#

CAM_I2C_SCL

CAM_I2C_SDA

ACCELERO_INT#

R15 10K_0402_5%R15 10K_0402_5%

SDIO1_CD#

12

U1E

Y7

VDDIO_NAND_1

Y8

VDDIO_NAND_2

Y9

VDDIO_NAND_3

AH3

GMI_ADV#

AF5

GMI_CS0#

AF12

GMI_CS1#

AD12

GMI_CS2#

AC6

GMI_CS3#

AC12

GMI_CS4#

AB12

GMI_CS5#

AD5

GMI_CS6#

AD9

GMI_CS7#

AG9

GMI_OE#

AF6

GMI_WR#

AF3

GMI_CLK

AC9

GMI_DPD

AC7

GMI_RST#

AF1

GMI_WAIT

AF2

GMI_WP#

AC10

GMI_IORDY

VI MIPI

VI MIPI

L21

VDDIO_VI

H28

CAM_I2C_SCL

H27

CAM_I2C_SDA

L24

VI_MCLK

L28

VI_PCLK

L25

VI_HSYNC

K25

VI_VSYNC

H23

VI_D00

H25

VI_D01

J23

VI_D02

J28

VI_D03

J24

VI_D04

J27

VI_D05

J25

VI_D06

J26

VI_D07

K23

VI_D08

L26

VI_D09

L23

VI_D10

M22

VI_D11

L22

VI_GP0

M23

VI_GP3

J22

VI_GP4

L27

VI_GP5

M24

VI_GP6

T20-H-A2 1G_FCBGA 664P

T20-H-A2 1G_FCBGA 664P

NAND

NAND

GEN2_I2C_SCL

GEN2_I2C_SDA

GMI_AD0

GMI_AD1

GMI_AD2

GMI_AD3

GMI_AD4

GMI_AD5

GMI_AD6

GMI_AD7

GMI_AD8

GMI_AD9

GMI_AD10

GMI_AD11

GMI_AD12

GMI_AD13

GMI_AD14

GMI_AD15

GMI_AD16

GMI_AD17

GMI_AD18

GMI_AD19

GMI_AD20

GMI_AD21

GMI_AD22

GMI_AD23

GMI_AD24

GMI_AD25

GMI_AD26

GMI_AD27

AVDD_DSI_CSI_1

AVDD_DSI_CSI_2

DSI_CSI_RUP

CSI_CLKAN

CSI_CLKAP

CSI_D1AN

CSI_D1AP

CSI_D2AN

CSI_D2AP

CSI_CLKBN

CSI_CLKBP

CSI_D1BN

CSI_D1BP

DSI_CLKAN

DSI_CLKAP

DSI_D1AN

DSI_D1AP

DSI_D2AN

DSI_D2AP

DSI_CSI_RDN

AD11

AD6

AG5

AE9

AF11

AG6

AH8

AG11

AF9

AF8

AE6

AE12

AH12

AH6

AH11

AG3

AH9

AH5

AG12

AD3

AE5

AG8

AD8

AE7

AC5

AE11

AE8

AC11

AE10

AC8

AA17

Y16

AF21

AH26

AG26

AD20

AE20

AH23

AG23

AB20

AC20

AH24

AG24

AD21

AC21

AF20

AG20

AH21

AG21

AH20

Change +3VS to +VDDIO_VI 04/29

FORCE_RECOVERY#

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

THIS SHEET OF ENGINEERING DRAW ING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTR ONICS, INC. AND CONTAINS CONF IDENTIAL

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

AND TRADE SECRET INFORMATI ON. THIS SHEET MAY NOT BE TRANSFERED F ROM THE CUSTODY OF THE COMPETENT D IVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY C OMPAL ELECTRONICS, INC. NEITHER T HIS SHEET NOR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

MAY BE USED BY OR DISCLOSED TO ANY THI RD PARTY WITHOUT PRIOR WRIT TEN CONSENT OF COMPAL ELECTRONICS, INC .

Strap option

USB recovery

JTAG_ARM1

JTAG_ARM0

RAM_Code[3:0]

Boot_Select

[3:0]

2008/12/22 2009/12/22

2008/12/22 2009/12/22

2008/12/22 2009/12/22

Strap pin

GMI_OE#

GMI_CLK

GMI_ADV#

GMI_AD[7:4]

GMI_AD

[15:12]

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

2

Net Name Description

NAND_RE#

NAND_CLE

NAND_ALE

NAND_D[7:4]

GMI_AD

[15:12]

0 : USB recovery mode.

1 : Boot from secondary device.

00 : Serial JTAG chain, MPCORE and AVP.

01 : MPCORE only JTAG.

10 : AVP only JTAG.

11 : Reserved.

RAM_Code[3:2]: Secondary boot device configration.

RAM_Code[1:0]: DDR2 RAM configration.

0000 : eMMC primary x 4

0001 : eMMC primary x 8

0010 : eMMC primary x 4, high voltage

0011 : NAND

0100 : NAND (42nm)

0101 : Mobile LBA NAND

0110 : FlexMuxOne NAND

0111 : eSD x 4

1000 : SPI Flash

1001 : SNOR (Muxed x 16)

1010 : SNOR (Muxed x 32)

1011 : SNOR (Non-Muxed x 16)

1100 : MuxOne NAND

1101 : Reserved

1110 : Reserved

1111 : Use fuse data

NAND_D0

NAND_D1

NAND_D2

NAND_D3

NAND_D4

NAND_D5

NAND_D6

NAND_D7

SDIO1_WP

HSMMC_CD#

HSMMC_WP

GMI_AD12

GMI_AD13

GMI_AD14

GMI_AD15

T20_WAKE#_R

GMI_AD18

HSMMC_DAT0

HSMMC_DAT1

HSMMC_DAT2

HSMMC_DAT3

HSMMC_DAT4

HSMMC_DAT5

HSMMC_DAT6

HSMMC_DAT7

R16

R16

49.9_0402_1%

49.9_0402_1%

1 2

eMMC : 00 for Sandisk 01 for Toshiba

NAND Flash : 00 for Micron 01 for TBD

00 Hynix 512M

01 Micron 512M

10 TBD

11 TBD

NAND_D[0..7] 12

R5 100K_0402_5%R5 100K_0402_5%

SDIO1_WP 18

1 2

1 2

R6

R6

100K_0201_5%

100K_0201_5%

12

R8 0_0201_5%R8 0_0201_5%

+AVDD_DSI_CSI

1

C11

C11

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

Title

Title

Title

T20(1/4)LCD/CRT/HDMI/NAND

T20(1/4)LCD/CRT/HDMI/NAND

T20(1/4)LCD/CRT/HDMI/NAND

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

T20 schematic

T20 schematic

T20 schematic

Date: Sheet of

Date: Sheet of

Date: Sheet of

T20_WAKE# 9,19

GMI_AD18

HSMMC_DAT[0..7] 12

1.2V

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

1

+VDDIO_NAND

R1295

R1295

100K_0402_5%

100K_0402_5%

GMI_AD18

Default

1

00

PAZ00

L01-L04: 00

L05-L07: 01

00

PAZ00 : 0001

PAZ01 : 0011

6 33Wednesday, July 21, 2010

6 33Wednesday, July 21, 2010

6 33Wednesday, July 21, 2010

1 2

0.2

0.2

0.2

Page 7

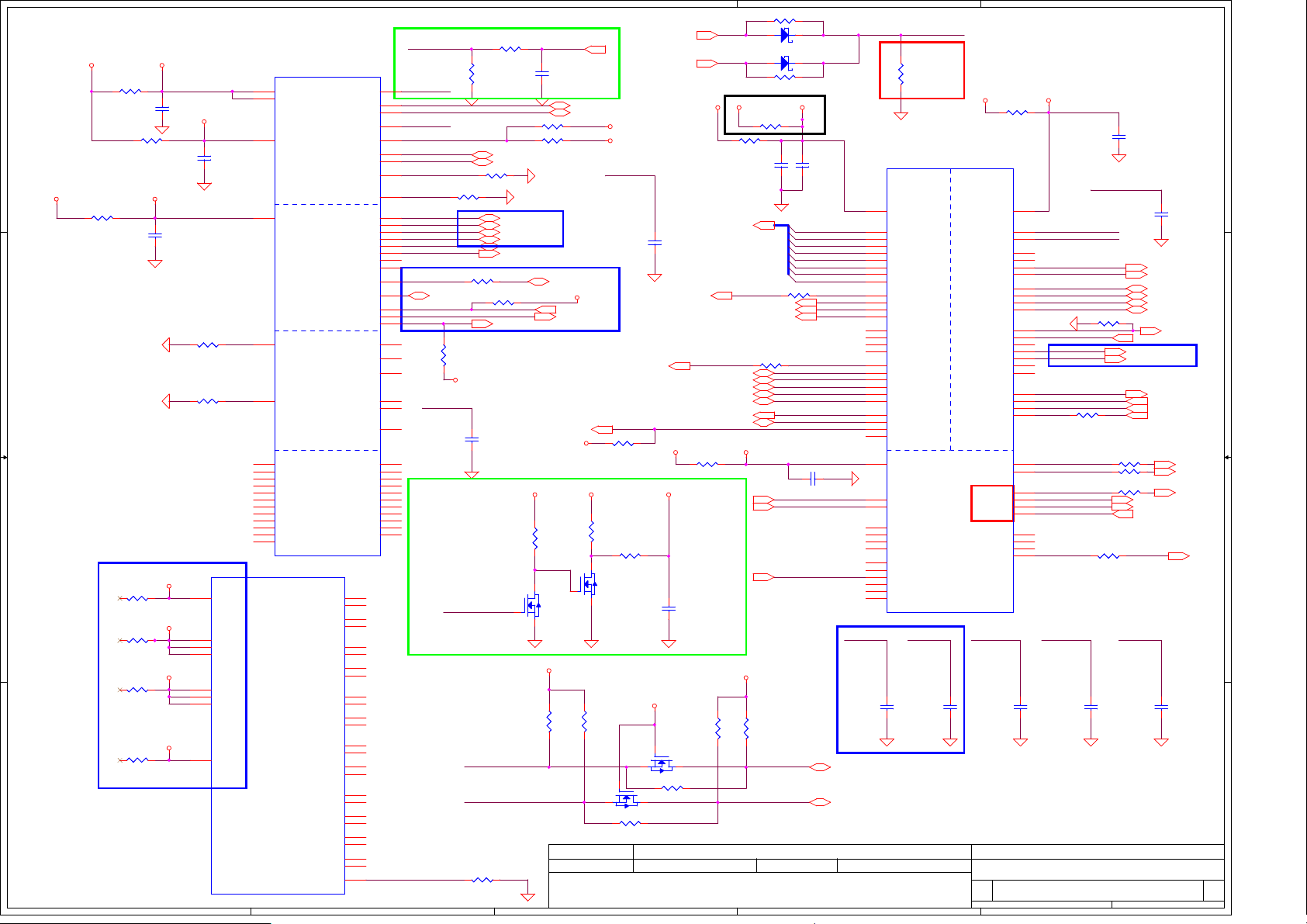

5

For leakage current issue(PVT2)

+3VS

5

Q31B

PWR_I2C_SCL

D D

PWR_I2C_SDA

2N7002DW-7-F_SOT363-6

2N7002DW-7-F_SOT363-6

1.8V

Q31B

2

2N7002DW-7-F_SOT363-6

2N7002DW-7-F_SOT363-6

Q31A

Q31A

+1.8VS_LDO4

3

4

61

2N7002DW-7-F_SOT363-6

2N7002DW-7-F_SOT363-6

2.2K_0402_5%

2.2K_0402_5%

5

Q33B

Q33B

3

4

6 1

2N7002DW-7-F_SOT363-6

2N7002DW-7-F_SOT363-6

sourcer request change L1 from

SM01000ER0T to SM01000ER00(Pre-MP 7/8)

220Ω @100MHz

L1

L1

1 2

FBMA-10-100505-221T_0402

FBMA-10-100505-221T_0402

1.1V

+1.1VS_LDO1

C C

B B

A A

+AVDD_PLL_P_C

1 2

0_0402_5%

0_0402_5%

1 2

0_0402_5%

0_0402_5%

1 2

0_0402_5%

0_0402_5%

1 2

0_0402_5%

0_0402_5%

1 2

0_0402_5%

0_0402_5%

R44

R44

R45

R45

R46

R46

R47

R47

R43

R43

1

C23

C23

2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

+1.8VS_SYS

+1.8VS_LDO4

1.1V

+AVDD_PLLU

1

2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1.8V

5

+AVDD_PLLX

C26

C26

1.1V

1

2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

R51

R51

0_0402_5%

0_0402_5%

1 2

CLK_32K_IN

+AVDD_PLLM +AVDD_PLLE

C27

C27

C22 4.7U_0603_6.3V6KC22 4.7U_0603_6.3V6K

1.1V

1

C28

C28

2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

C30

C30

2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

12

@

@

R267

R267

330_0402_5%

330_0402_5%

1

@

@

C232

C232

10P_0402_50V8J

10P_0402_50V8J

2

+AVDD_OSC

1

2

1.05V

1

2

0.1U_0402_25V4K

0.1U_0402_25V4K

+3VS

12

Q33A

Q33A

12

R193

R193

2.2K_0402_5%

2.2K_0402_5%

PWR_I2C_SCL_3V3

PWR_I2C_SDA_3V3

R168

R168

2

01EVT change MOS for EN power <3.3V

U1B

U1B

OSC, PLL, SYS

OSC, PLL, SYS

H12

AVDD_OSC

H14

AVDD_PLLA_P_C

AA18

AVDD_PLLU

L7

AVDD_PLLX

H15

AVDD_PLLM

Y1

AVDD_PLLE

@

@

C29

C29

G18

VDDIO_SYS

T20-H-A2 1G_FCBGA 664P

T20-H-A2 1G_FCBGA 664P

4

TPS658621_XTAL1

XTAL_IN

XTAL_OUT

AVDD_PLL_S_LF

PWR_I2C_SCL

PWR_I2C_SDA

SYS_RESET#

CLK_32K_IN

PWR_INT#

CORE_PWR_REQ

CPU_PWR_REQ

SYS_CLK_REQ

CLK_32K_OUT

KB_COL0

KB_COL1

KB_COL2

KB_COL3

KB_COL4

KB_COL5

KB_COL6

KB_COL7

KB_ROW00

KB_ROW01

KB_ROW02

KB_ROW03

KB_ROW04

KB_ROW05

KB_ROW06

KB_ROW07

KB_ROW08

KB_ROW09

KB_ROW10

KB_ROW11

KB_ROW12

KB_ROW13

KB_ROW14

KB_ROW15

JTAG_RTCK

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRST#

OWR

TEST_MODE_EN

4

T20_XTAL_IN

E3

T20_XTAL_OUT

E2

PLL_S_PLL_LF

G12

C1

C2

SYS_RESET#_R

D17

B14

D14

G14

C14

D7

D5

A6

D6

A5

B5

C5

B3

A3

C3

C12

B12

A12

D11

A11

B11

C11

C9

B9

A9

D8

A8

B8

C8

C6

B6

A17

B17

B15

C15

C17

A15

G11

A14

12

C285

C285

10P_0402_50V8J

10P_0402_50V8J

R42

R42

2M_0402_5%

2M_0402_5%

1

C25

C25

2

2.2K_0402_5%

2.2K_0402_5%

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

PWR_I2C_SCL

PWR_I2C_SDA

1 2

FBMA-10-100505-101T 0402

FBMA-10-100505-101T 0402

CLK_32K_IN

PWR_INT#

CORE_PWR_REQ

CPU_PWR_REQ

CLK_32K_OUT

+1.8VS

C15

C15

01EVT for WWAN noise

+1.8VS

C40

C40

JTAG_RTCK

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRST#

R59

R59

1 2

0_0201_5%

0_0201_5%

1 2

R48

R48

R50

R50

1

C16

C16

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

2

3

1

Y5

Y5

32.768KHZ_12.5PF_9H03200413

32.768KHZ_12.5PF_9H03200413

OSC4OSC

NC3NC

PVT move from PWR to HW part.

2

8P_0402_50V8J

8P_0402_50V8J

C21

C21

1 2

Y4 12MHZ 9PF X3S012000B91H-XY4 12MHZ 9PF X3S012000B91H-X

2

IN1NC

4

OUT3NC

C24

C24

1 2

8P_0402_50V8J

8P_0402_50V8J

+1.8VS

1.8V

12

12

R49

R49

2.2K_0402_5%

2.2K_0402_5%

PWR_I2C_SCL 28

Change R50 to bead SM01000DI00 for ESD issue

CLK_32K_IN 28

PWR_INT# 28

CORE_PWR_REQ

CPU_PWR_REQ

CLK_32K_OUT

PWR_I2C_SDA 28

SYS_RESET# 17,19,28

DDR_A_D[0..31]10,11

1.8V

1

1

C17

C17

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

C39

C39

C42

C42

2

47P_0402_50V8J

47P_0402_50V8J

47P_0402_50V8J

47P_0402_50V8J

12

1

C19

C19

C18

C18

2

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

1

C41

C41

2

2

47P_0402_50V8J

47P_0402_50V8J

47P_0402_50V8J

47P_0402_50V8J

T8T8

T9T9

T10T10

T11T11

T12T12

T13T13

R58

R58

10K_0201_5%

10K_0201_5%

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

3

12

1

2

TPS658621_XTAL2

C286

C286

10P_0402_50V8J

10P_0402_50V8J

+2.85VS_LDO9

1 2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

C20

C20

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

2008/10/03 2009/10/03

2008/10/03 2009/10/03

2008/10/03 2009/10/03

THERMD_P

THERMD_N

+1.8VS

2.85V

+VDD_DDR_RX

R520_0402_5% R520_0402_5%

1

C31

C31

2

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

Compal Secret Data

Compal Secret Data

Compal Secret Data

R238 100_0402_5%R238 100_0402_5%

1 2

1000P_0402_50V7K

1000P_0402_50V7K

1 2

R239 100_0402_5%R239 100_0402_5%

U1C

U1C

H20

VDDIO_DDR_01

J12

VDDIO_DDR_02

J13

VDDIO_DDR_03

J14

VDDIO_DDR_04

J15

VDDIO_DDR_05

J16

VDDIO_DDR_06

J17

VDDIO_DDR_07

J18

VDDIO_DDR_08

J19

VDDIO_DDR_09

J20

VDDIO_DDR_10

J21

VDDIO_DDR_11

K20

VDDIO_DDR_12

L16

VDDIO_DDR_13

L17

VDDIO_DDR_14

L20

VDDIO_DDR_15

M17

VDDIO_DDR_16

M18

VDDIO_DDR_17

M20

VDDIO_DDR_18

N18

VDDIO_DDR_19

N20

VDDIO_DDR_20

P20

VDDIO_DDR_21

R20

VDDIO_DDR_22

T20

VDDIO_DDR_23

U20

VDDIO_DDR_24

V20

VDDIO_DDR_25

H17

VDD_DDR_RX

F20

DDR_DQ00

E18

DDR_DQ01

D18

DDR_DQ02

F18

DDR_DQ03

F17

DDR_DQ04

E21

DDR_DQ05

D21

DDR_DQ06

F21

DDR_DQ07

E17

DDR_DQ08

D15

DDR_DQ09

F16

DDR_DQ10

E14

DDR_DQ11

F13

DDR_DQ12

D16

DDR_DQ13

D12

DDR_DQ14

D13

DDR_DQ15

F23

DDR_DQ16

F25

DDR_DQ17

H22

DDR_DQ18

G25

DDR_DQ19

F22

DDR_DQ20

D24

DDR_DQ21

H24

DDR_DQ22

E23

DDR_DQ23

F9

DDR_DQ24

F12

DDR_DQ25

E12

DDR_DQ26

E9

DDR_DQ27

F10

DDR_DQ28

G8

DDR_DQ29

F11

DDR_DQ30

G9

DDR_DQ31

T20-H-A2 1G_FCBGA 664P

T20-H-A2 1G_FCBGA 664P

Deciphered Date

Deciphered Date

Deciphered Date

2

+3VS

1

C212

C212

2

PWR_I2C_SCL_3V3

PWR_I2C_SDA_3V3

DDR2

DDR2

2

R232

R232

1 2

20_0402_5%

20_0402_5%

THERMD_F_P

THERMD_F_N

DDR_DM0

DDR_DM1

DDR_DM2

DDR_DM3

DDR_DQS0N

DDR_DQS0P

DDR_DQS1N

DDR_DQS1P

DDR_DQS2N

DDR_DQS2P

DDR_DQS3N

DDR_DQS3P

DDR_A00

DDR_A01

DDR_A02

DDR_A03

DDR_A04

DDR_A05

DDR_A06

DDR_A07

DDR_A08

DDR_A09

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

DDR_RAS#

DDR_CAS#

DDR_WE#

DDR_BA0

DDR_BA1

DDR_BA2

DDR_CS0#

DDR_CS1#

DDR_ODT0

DDR_CKE0

DDR_CKE1

DDR_CLK#

DDR_CLK

THERMD_N

THERMD_P

DDR_COMP_PU

DDR_COMP_PD

DDR_QUSE0

DDR_QUSE1

DDR_QUSE2

DDR_QUSE3

+3VS_TH

1

C211

C211

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

U22

U22

2

VDD

D+

3

D-

THERM#

ALERT#

8

SCL

7

SDA

GND

ADT7421ARMZ-REEL_MSOP8P

ADT7421ARMZ-REEL_MSOP8P

address 0X4C

DDR_A_DM0

F19

DDR_A_DM1

E15

DDR_A_DM2

G23

DDR_A_DM3

D9

D19

E20

F14

F15

E24

F24

E11

D10

DDR_A_MA0

A20

DDR_A_MA1

C24

DDR_A_MA2

D20

DDR_A_MA3

B20

DDR_A_MA4

F26

DDR_A_MA5

C26

DDR_A_MA6

C27

DDR_A_MA7

F28

DDR_A_MA8

A26

DDR_A_MA9

A23

DDR_A_MA10

D23

DDR_A_MA11

C20

DDR_A_MA12DDR_A_MA12

C18

DDR_A_MA13

E28

C28

B23

H26

F27

B26

A24

B24

E25

C23

B21

A21

C21

E27

E26

THERMD_N

E6

THERMD_P

F7

R53 49.9_0402_1%R53 49.9_0402_1%

E8

F8

G15

G17

A18

B18

1 2

R54 49.9_0402_1%R54 49.9_0402_1%

1 2

DDR_QUSE0

DDR_QUSE1

DDR_QUSE2

DDR_QUSE3

R55

R55

1 2

0_0402_5%

0_0402_5%

R57

R57

1 2

0_0201_5%

0_0201_5%

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

+3VALW

12

R237

R237

100K_0402_5%

100K_0402_5%

1

TEMP_THERM#

4

6

5

DDR_A_DM[0..3] 10,11

DDR_A_DQS#0 1 0

DDR_A_DQS0 10

DDR_A_DQS#1 1 0

DDR_A_DQS1 10

DDR_A_DQS#2 1 1

DDR_A_DQS2 11

DDR_A_DQS#3 1 1

DDR_A_DQS3 11

DDR_A_MA[0..13] 10,11

DDR_A_RAS# 10,11

DDR_A_CAS# 10,11

DDR_A_WE# 10,11

DDR_A_BS#0 10,11

DDR_A_BS#1 10,11

DDR_A_BS#2 10,11

M_CS#0 10,11

01EVT remove for x8 RAM

M_ODT 10,11

M_CKE0 10,11

01EVT remove for x8 RAM

M_CLK_DDR#0 10,11

M_CLK_DDR0 10,11

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

01EVT for thermal throttle

TEMP_ALERT#

+1.8VS

1

1.8V

7 33Wednesday, July 21, 2010

7 33Wednesday, July 21, 2010

7 33Wednesday, July 21, 2010

TEMP_THERM#

TEMP_ALERT# 6

0.1

0.1

0.1

Page 8

A

100607_Reserve L23, R1317 and C311 only

3.3V

+3.3VS_LDO3

2.2U_0603_6.3V6K

1 1

+3VS

2 2

2.2U_0603_6.3V6K

R68 0_0402_5 %R68 0_0402_5%

+AVDD_USB

R60

R60

12

0_0402_5%

0_0402_5%

C34

C34

R62 0_0402_5 %R62 0_0402_5%

+VDDIO_SDIO

12

Reserve PEI-E power trace

3 3

4 4

R92

R92

1 2

0_0402_5%

0_0402_5%

R78

R78

1 2

0_0402_5%

0_0402_5%

R80

R80

1 2

0_0402_5%

0_0402_5%

R85

R85

1 2

0_0402_5%

0_0402_5%

A

+AVDD_PEX_PLL

+AVDD_PEX

+VDD_PEX

+VDDIO_PEX_CLK

Change L23 to 0 ohm for

mini USB client only.(PVT4)

12

3.3V

+AVDD_USB_PLL

12

1

C33

C33

0.1U_0402_10V7K

0.1U_0402_10V7K

2

3.3V

1

C37

C37

0.1U_0402_10V7K

0.1U_0402_10V7K

2

12

R71 1K_0402_1%R71 1K_0402_1%

12

R72 1K_0402_1%R72 1K_0402_1%

U1H

U1H

P8

AVDD_PEX_PLL

R8

AVDD_PEX_1

R9

AVDD_PEX_2

T9

AVDD_PEX_3

U8

VDD_PEX_1

U9

VDD_PEX_2

V9

VDD_PEX_3

V8

VDDIO_PEX_CLK

T20-H-A2 1G_FCBGA 664P

T20-H-A2 1G_FCBGA 664P

U1F

U1F

AA14

AVDD_USB_1

Y14

AVDD_USB_2

AB11

AVDD_USB_PLL

VDDIO_SDIOP1SDIO3_DATA0

SDIO

SDIO

AB8

VDDIO_HSIC

AB9

AVDD_IC_USB

AA3

DNC_0001

AB4

DNC_0002

AB6

DNC_0003

AC13

DNC_0004

AC3

DNC_0005

AE21

DNC_0006

AE22

DNC_0007

AE23

DNC_0008

AF23

DNC_0009

AF24

DNC_0010

AF26

DNC_0011

AF27

DNC_0012

T20-H-A2 1G_FCBGA 664P

T20-H-A2 1G_FCBGA 664P

PEX

PEX

USB

USB

HSIC

HSIC

NC

NC

PEX_L0_TXN

PEX_L0_TXP

PEX_L0_RXN

PEX_L0_RXP

PEX_L1_TXN

PEX_L1_TXP

PEX_L1_RXN

PEX_L1_RXP

PEX_L2_TXN

PEX_L2_TXP

PEX_L2_RXN

PEX_L2_RXP

PEX_L3_TXN

PEX_L3_TXP

PEX_L3_RXN

PEX_L3_RXP

PEX_CLK_OUT1_N

PEX_CLK_OUT1_P

PEX_CLK_OUT2_N

PEX_CLK_OUT2_P

PEX_TSTCLKN

PEX_TSTCLKP

PEX_REFCLKN

PEX_REFCLKP

PEX_TERMP

USB1_VBUS

USB1_DN

USB1_DP

USB1_ID

USB3_VBUS

USB3_DN

USB3_DP

USB3_ID

USB_REXT

SDIO3_DATA1

SDIO3_DATA2

SDIO3_DATA3

SDIO3_DATA4

SDIO3_DATA5

SDIO3_DATA6

SDIO3_DATA7

SDIO3_CLK

SDIO3_CMD

GPIO_PV4

GPIO_PV5

GPIO_PV6

HSIC_DATA

HSIC_STROBE

HSIC_REXT

IC_DN

IC_DP

IC_REXT

DNC_00013

DNC_00014

DNC_00015

DNC_00016

DNC_00017

DNC_00018

DNC_00019

DNC_00020

DNC_00021

DNC_00022

DNC_00023

AD1

AD2

AA5

AA4

AC2

AC1

AA7

AA6

AA1

AA2

V4

V3

Y3

Y2

V6

V5

AC4

AD4

Y4

Y5

V1

V2

U1

U2

W6

B

For USB detect issue(PVT2)

L23

+USB1_VBUS +U SB1_VBUS_R

+VBUS

AD17

USB1_DN

AC14

USB1_DP

AD14

USB1_ID

AE14

+USB3_VBUS

AH14

USB3_DN

AH15

USB3_DP

B

AG15

AF15

AC16

R3

U3

U4

R4

T4

T6

R5

U7

R2

R1

P7

R7

R6

AC15

AD15

AE15

AF14

AG14

AE13

AF28

D22

G20

G21

M21

M7

R21

U5

V7

W4

Y6

PEX_TERMP

USB3_ID

USB_REXT

1 2

WF_LED

SDIO2_CMD 15

W_DISABLE#

PEX_RST0#

PEX_WAKE#

1 2

SDIO1_CLK_R

+USB1_VBUS

2N7002DW-7-F_SOT363-6

2N7002DW-7-F_SOT363-6

@

@

R86 2.49K_0402_1%

R86 2.49K_0402_1%

L23

1 2

0_0603_5%

0_0603_5%

R1317

@ R1317

@

100K_0402_1%

100K_0402_1%

1 2

L:HOST

H:Client

USB3_DN 16

USB3_DP 16

1 2

R65 10K_0402_5%R65 10K_0402_5%

R661K_0402_1% R661K_0402_1%

SDIO2_DAT0 15

SDIO2_DAT1 15

SDIO2_DAT2 15

SDIO2_DAT3 15

WF_RST# 15,20

12

R67 100K_0402_5 %R67 100K_0402_5%

1 2

1

C230

C230

10P_0402_50V8J

10P_0402_50V8J

2

WF_LED

PEX_WAKE# 15

01EVT modify GPIO pin

R206 33_0402_1%R206 33_0402_1%

R69

R69

100K_0402_5%

100K_0402_5%

+VDDIO_SDIO

100607_Modify mini USB detect circuit.

100K_0402_5%

100K_0402_5%

R229

R229

2.2K_0402_5%

2.2K_0402_5%

GEN1_I2C_SCL

GEN1_I2C_SDA

1 2

C

USB1_ID1: From Connector

USB1_ID1

USB1_ID2

USB1_ID2: From EC

S3 PWR modify PVT

+5VS

+5VALW

1

C233

C233

10P_0402_50V8J

10P_0402_50V8J

2

ULPI_CLK_R

SDIO1_CLK_R18

EC_REQUEST#

R73

R73

R79

R79

C

+3VS

R74 0_0402_5 %R74 0_0402_5%

+VBUS

0_0402_5%

0_0402_5%

R1267

R1267

1

@C280

@

0.01U_0402_16V7K

0.01U_0402_16V7K

2

+VDDIO_UART

2.2K_0402_5%

2.2K_0402_5%

5

@

@

Q5B

Q5B

4

2N7002DW-7-F_SOT363-6

2N7002DW-7-F_SOT363-6

2

1 2

R1225 0_0402_5%R1225 0_0402_5%

61

2005/05/26 2006/07/26

2005/05/26 2006/07/26

2005/05/26 2006/07/26

C280

3

SDIO1_CLK_R

SDIO1_CMD18

SDIO1_DAT018

SDIO1_DAT118

SDIO1_DAT218

SDIO1_DAT318

ULPI_RESET#1 6

EN_VDDIO_SD18

T20_Codec17

WF_PWDN#

R83

R83

USB1_DN 16

USB1_DP 16

12

12

+USB1_VBUS_R 16

ULPI_CLK_R

1

C311

@C311

@

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

R1262 0_0402_5%R1262 0_0402_5%

R63 0_0402_5 %@R 63 0_0402_5%@

3.3V

SDIO2_CLK 15

+VDDIO_SDIO

W_DISABLE#

PEX_RST0# 15,18

EC_REQUEST#19

+VDDIO_BB

+5VS +5VS

12

61

Q28A

Q28A

2

+VDDIO_UART

12

R81

@R81

@

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECT RONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANS FERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMPAL ELECTRONICS, INC.

1 2

100K_0402_5%

100K_0402_5%

12

10K_0402_5%

10K_0402_5%

1 2

3

Q28B

Q28B

2N7002DW-7-F_SOT363-6

2N7002DW-7-F_SOT363-6

5

4

For Layout specing issue.

12

R82

@R82

@

2.2K_0402_5%

2.2K_0402_5%

@

@

Q5A

Q5A

2N7002DW-7-F_SOT363-6

2N7002DW-7-F_SOT363-6

1 2

R1224 0_0402_5%R1224 0_0402_5%

Issued Date

Issued Date

Issued Date

+3VS

+3VS_S3

R12800_0402_5%R12800_0402_5%

R64 0_0402_5%@R64 0_0402_5%@

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

ULPI_D[0..7]

ULPI_CLK_R

ULPI_DIR

ULPI_NXT

ULPI_STP

+VDDIO_AUDIO

12

HP_DET17

+3VS

12

12

Compal Secret Data

Compal Secret Data

Compal Secret Data

R1303 0_0402_5%R1303 0_0402_5%

R1304 1K_0402_5%@ R1304 1K_0402_5%@

33_0402_1%

33_0402_1%

1 2

D1 RB751V-40TE17_SOD323-2@D1 RB751V-40TE17_SOD323-2@

D2 RB751V-40TE17_SOD323-2@D2 RB751V-40TE17_SOD323-2@

+VDDIO_BB

12

12

1

C35

C35

2

R177 10_0402_5%R177 10_0402_5%

R265

R265

SDIO1_CMD

SDIO1_DAT0

SDIO1_DAT1

SDIO1_DAT2

SDIO1_DAT3

ULPI_RESET#

T20_Codec

R84

R84

2.2K_0402_5%

2.2K_0402_5%

Deciphered Date

Deciphered Date

Deciphered Date

12

12

12

12

1

2

ULPI_D0

ULPI_D1

ULPI_D2

ULPI_D3

ULPI_D4

ULPI_D5

ULPI_D6

ULPI_D7

SDIO1_CLK

EN_VDDIO_SD

C38

C38

1 2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

HP_DET

D

Add R1303 and remove D1,D2 for mini USB client only.

USB1_ID

USB1_ID

3.3V

C36

C36

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

ULPI_CLK

12

ULPI_DIR

ULPI_NXT

ULPI_STP

GEN1_I2C_SCL_3V3 13 ,17,18

GEN1_I2C_SDA_3V3 13,17,18

U1G

U1G

M8

VDDIO_BB

P4

ULPI_DATA0

P6

ULPI_DATA1

N4

ULPI_DATA2

L3

ULPI_DATA3

L4

ULPI_DATA4

L6

ULPI_DATA5

P5

ULPI_DATA6

N6

ULPI_DATA7

M2

ULPI_CLK

M3

ULPI_DIR

M1

ULPI_NXT

P3

ULPI_STP

L2

DAP3_DIN

L1

DAP3_DOUT

J3

DAP3_FS

M4

DAP3_SCLK

M6

SDIO1_CLK

J5

SDIO1_CMD

K6

SDIO1_DATA0

K4

SDIO1_DATA1

M5

SDIO1_DATA2

L5

SDIO1_DATA3

P2

GPIO_PV0

J7

GPIO_PV1

U6

GPIO_PV2

J6

GPIO_PV3

P21

VDDIO_AUDIO

R25

SPDIF_IN

N23

SPDIF_OUT

M28

SPI1_SCK

M27

SPI1_CS0#

M26

SPI1_MOSI

P26

SPI1_MISO

P24

SPI2_SCK

P23

SPI2_CS0#

P22

SPI2_CS1#

P28

SPI2_CS2#

N25

SPI2_MOSI

M25

SPI2_MISO

T20-H-A2 1G_FCBGA 664P

T20-H-A2 1G_FCBGA 664P

1

2

D

R1254

@R1254

@

100K_0402_5%

100K_0402_5%

1 2

BB UART

BB UART

GEN1_I2C_SCL

GEN1_I2C_SDA

AUDIO

AUDIO

SDIO2_CLKDAP4_SCLK

C278

C278

10P_0402_50V8J

10P_0402_50V8J

1

C277

C277

10P_0402_50V8J

10P_0402_50V8J

2

01EVT EMI request

E

DVT for USB_ID folating issue

+3VS

R61 0_0402_5 %R61 0_0402_5%

VDDIO_UART

UART2_TXD

UART2_RXD

UART2_RTS#

UART2_CTS#

UART3_TXD

UART3_RXD

UART3_RTS#

UART3_CTS#

GPIO_PU0

GPIO_PU1

GPIO_PU2

GPIO_PU3

GPIO_PU4

GPIO_PU5

GPIO_PU6

DAP4_DIN

DAP4_DUT

DAP4_FS

DAP4_SCLK

DAP_MCLK1

DAP_MCLK2

DAP1_SCLK

DAP1_FS

DAP1_DUT

DAP1_DIN

DAP2_SCLK

DAP2_FS

DAP2_DUT

DAP2_DIN

DAP_MCLK1_R D AP_MCLK2_R DAP1_SCLK_R

Title

Title

Title

T20(3/4)USB/SDIO/UART/AUDIO

T20(3/4)USB/SDIO/UART/AUDIO

T20(3/4)USB/SDIO/UART/AUDIO

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet of

+VDDIO_UART

12

H11

GEN1_I2C_SCL

H6

GEN1_I2C_SDA

H5

H7

F4

UART1_TXD

G6

UART1_RXD

F5

F3

F2

F1

E4

BT_RST#

J1

G4

E1

LCD_BL_PWM

F6

LCD_BL_EN

E5

H4

J2

H1

J4

H3

H2

P27

R24

P25

R27

R28

R26

R23

R22

T23

T25

1

2

01EVT switch GPIO

R207 33_0402_1%R207 33_0402_1%

DAP_MCLK1

DAP_MCLK2

DAP1_SCLK

DAP1_FS

DAP1_DOUT

DAP1_DIN

EN_VDD_PNL_T25 EN_VDD_PNL

C228

C228

10P_0402_50V8J

10P_0402_50V8J

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

T20 schematic

T20 schematic

T20 schematic

LCD_BL_EN

R70

R70

1 2

100K_0402_5%

100K_0402_5%

12

R75 47_0402_5%R75 47_0402_5%

R76 47_0402_5%R76 47_0402_5%

R77 47_0402_5%R77 47_0402_5%

R1275 0_0402_5%R1275 0_0402_5%

1

C229

C229

10P_0402_50V8J

10P_0402_50V8J

2

E

1

C32

C32

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

BT_WAKEUP

LCD_BL_PWM

LCD_BL_EN

12

12

12

DAP1_FS

DAP1_DOUT

DAP1_DIN 17

12

8 33Wednesday, July 21, 2010

8 33Wednesday, July 21, 2010

8 33Wednesday, July 21, 2010

UART1_TXD

UART1_RXD

1

C289

@C289

@

0.1U_0402_10V6K

0.1U_0402_10V6K

2

UART3_TXD 15

UART3_RXD 15

UART3_RTS# 15

UART3_CTS# 15

BT_RST# 15

DAP4_DIN

DAP4_DOUT

DAP4_FS

DAP4_SCLK

DAP_MCLK1_R

DAP_MCLK2_R 16

DAP1_SCLK_R

EN_VDD_PNL 6

1

C227

C227

10P_0402_50V8J

10P_0402_50V8J

2

0.1

0.1

0.1

Page 9

A

U1A

U1A

CORE

A1

A2

A27

A28

AA10

AA13

AA16

AA19

AA21

AA8

AA9

1 1

2 2

3 3

4 4

A

AB24

AB27

AC19

AD10

AD13

AD16

AD19

AD22

AE25

AE27

AG10

AG13

AG16

AG19

AG22

AG25

AG27

AG28

AH27

AH28

W21

W24

W27

AB2

AB5

AD7

AE2

AE4

AG1

AG2

AG4

AG7

AH1

AH2

B1

B10

B13

B16

B19

B2

B22

B25

B27

B28

B4

B7

D2

D25

D27

D4

E10

E13

E16

E19

E22

E7

G2

G24

G27

G5

H10

H13

H16

H18

H19

H21

H8

K2

K21

K24

K27

K5

K8

L11

L12

L13

L14

L15

L18

L8

M12

N13

N14

N16

N17

N2

N21

N24

N27

N5

N8

P17

P18

R11

R14

R15

R17

R18

T11

T12

T14

T17

T18

T2

T21

T24

T27

T5

T8

U11

U12

U15

U18

U21

V11

V14

V15

V16

V21

W2

W5

W8

Y11

Y12

Y13

CORE

GND_001

GND_002

GND_003

GND_004

GND_005

GND_006

GND_007

GND_008

GND_009

GND_010

GND_011

GND_012

GND_013

GND_014

GND_015

GND_016

GND_017

GND_018

GND_019

GND_020

GND_021

GND_022

GND_023

GND_024

GND_025

GND_026

GND_027

GND_028

GND_029

GND_030

GND_031

GND_032

GND_033

GND_034

GND_035

GND_036

GND_037

GND_038

GND_039

GND_040

GND_041

GND_042

GND_043

GND_044

GND_045

GND_046

GND_047

GND_048

GND_049

GND_050

GND_051

GND_052

GND_053

GND_054

GND_055

GND_056

GND_057

GND_058

GND_059

GND_060

GND_061

GND_062

GND_063

GND_064

GND_065

GND_066

GND_067

GND_068

GND_069

GND_070

GND_071

GND_072

GND_073

GND_074

GND_075

GND_076

GND_077

GND_078

GND_079

GND_080

GND_081

GND_082

GND_083

GND_084

GND_085

GND_086

GND_087

GND_088

GND_089

GND_090

GND_091

GND_092

GND_093

GND_094

GND_095

GND_096

GND_097

GND_098

GND_099

GND_100

GND_101

GND_102

GND_103

GND_104

GND_105

GND_106

GND_107

GND_108

GND_109

GND_110

GND_111

GND_112

GND_113

GND_114

GND_115

GND_116

GND_117

GND_118

GND_119

GND_120

GND_121

GND_122

GND_123

GND_124

GND_125

GND_126

GND_127

GND_128

GND_129

GND_130

GND_131

GND_132

GND_133

GND_134

GND_135

GND_136

T20-H-A2 1G_FCBGA 664PT20_23X23

T20-H-A2 1G_FCBGA 664PT20_23X23

VDD_RTC_00 1

VDD_RTC_00 2

VDD_CPU_01

VDD_CPU_02

VDD_CPU_03

VDD_CPU_04

VDD_CPU_05

VDD_CPU_06

VDD_CPU_07

VDD_CPU_08

VDD_CPU_09

VDD_CPU_10

VDD_CPU_11

VDD_CPU_12

VDD_CPU_13

VDD_CPU_14

VDD_CPU_15

VDD_CPU_16

VDD_CPU_17

VDD_CORE_01

VDD_CORE_02

VDD_CORE_03

VDD_CORE_04

VDD_CORE_05

VDD_CORE_06

VDD_CORE_07

VDD_CORE_08

VDD_CORE_09

VDD_CORE_10

VDD_CORE_11

VDD_CORE_12

VDD_CORE_13

VDD_CORE_14

VDD_CORE_15

VDD_CORE_16

VDD_CORE_17

VDD_CORE_18

VDD_CORE_19

VDD_CORE_20

VDD_CORE_21

VDD_CORE_22

VPP_FUSE

VPP_KFUSE

VDD_CORE_SEN SE

GND_CORE_SE NSE

VDD_CPU_SENS E

GND_CPU_SEN SE

VDD_TP

GND_TP

VGND_TP

B

1.0~1.2V

+VDD_RTC

V12

R87 0_0402_5%R87 0_0402_5%

V13

1

2

H9

J10

J11

J8

J9

K9

L9

M11

M9

N11

N12

P11

P12

P13

P14

R12

R13

AA20

M13

M14

M15

M16

N15

P15

P16

R16

T13

T15

T16

U13

U14

U16

U17

V17

V18

W20

Y19

Y20

Y21

AB15

VDD_KFUSE

AB14

Y18

Y17

N9

P9

W9

Y10

AA11

B

+1.2VS_LDO2

12

C43

C43

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

C44

C44

2

1

C48

C48

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

01EVT for WWAN noise

+VDD_CORE

C102

C102

R94

R94

1 2

10K_0402_5%

10K_0402_5%

1

C45

C45

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

C49

C49

C50

C50

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

1

C101

C101

2

2

47P_0402_50V8J

47P_0402_50V8J

+VDD_FUSE

12

C53

C53

100K_0402_5%

100K_0402_5%

Change to 100K ( SD028100380 ) by NV suggest

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

C46

C46

2

1

2

1

C103

C103

2

47P_0402_50V8J

47P_0402_50V8J

3.3V

R93

@R93

@

0_0402_5%

0_0402_5%

Issued Date

Issued Date

Issued Date

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1.0~1.2V

C51

C51

0.1U_0402_25V4K

0.1U_0402_25V4K

C107

C107

47P_0402_50V8J

47P_0402_50V8J

12

C

0.9~1.0V

+VDD_CPU

1

2

1

2

1

2

+3VS

C

01EVT for WWAN noise

+1.0VS_SM1

1 2

R88 0_0805_5%R88 0_0805_5%

C47

C47

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

+VDD_CORE

1 2

R89 0_0805_5%R89 0_0805_5%

1

C52

C52

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

47P_0402_50V8J

47P_0402_50V8J

2007/05/29 2008/05/29

2007/05/29 2008/05/29

2007/05/29 2008/05/29

+VDD_CPU

C148

C148

+1.2VS_SM0

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

1

C108

C108

2

47P_0402_50V8J

47P_0402_50V8J

Change connector form ACES-87213 to ACES_87036 by ME 4/16 ,remove 5VS & 1.8VS

01EVT for T20 UART/ ENE TX/ WINBOND JTAG debug

1

C147

C147

2

47P_0402_50V8J

47P_0402_50V8J

D

1

C149

C149

2

47P_0402_50V8J

47P_0402_50V8J

UART1_RXD

UART1_TXD

T20_WAKE#6,19

+3VALW

+1.8VS

SYSTEM_RESET#28

EC_TX_P80_DATA

D

E

1

2

47P_0402_50V8J

47P_0402_50V8J

JP1

UART1_RXD

UART1_TXD

T20_WAKE#

SYSTEM_RESET#

EC_TX_P80_DATA

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

T20 schematic

T20 schematic

T20 schematic

Date: Sheet of

Date: Sheet of

Date: Sheet of

JP1

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

GND

12

GND

ACES_87036-1001-CP

ACES_87036-1001-CP

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

T20(4/4)Power/GND/NC

T20(4/4)Power/GND/NC

T20(4/4)Power/GND/NC

9 33W ednesday, July 21, 2010

9 33W ednesday, July 21, 2010

9 33W ednesday, July 21, 2010

E

0.1

0.1

0.1

Page 10

5

DDR_A_BS#[0..2]7,11

DDR_A_D[0..15]7

DDR_A_DQS[0..1]7

DDR_A_DQS#[0..1]7

DDR_A_MA[0..13]7,11

D D

DDR_A_DM[0..1]7

4

3

2

1

U3

@U3

DDR_A_DQS0

DDR_A_DQS#0

+1.8VS

R95

+VRAM_VREFA

R96

R96

1K_0402_1%

1K_0402_1%

C C

B B

R95

1K_0402_1%

1K_0402_1%

1 2

(SSTL-1.8) VREF = .5*VDDQ

2

C55

C55

0.1U_0402_10V7K

0.1U_0402_10V7K

1

1 2

Close to U7

DDR_A_DM0

DDR_A_D0

DDR_A_D6

DDR_A_D2

DDR_A_D3

DDR_A_D7

DDR_A_D4

DDR_A_D5

DDR_A_D1

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

0.01U_0402_25V7K

0.01U_0402_25V7K

@

B7

DQS

A8

DQS#

B3

DM/RDQS

C8

DQ0

C2

DQ1

D7

DQ2

D3

DQ3

D1

DQ4

D9

DQ5

B1

DQ6

B9

DQ7

E2

VREF

H8

A0

H3

A1

H7

A2

J2

A3

J8

A4

J3

A5

J7

A6

K2

A7

K8

A8

K3

A9

H2

A10

K7

A11

L2

A12

L8

A13

A2

NU/RDQS

L3

NC

L7

NC

HY5PS1G831CLFP-Y5_FBGA60~D

HY5PS1G831CLFP-Y5_FBGA60~D

+1.8VS

2

1

C56

C56

C57

C57

1

2

1U_0402_6.3V4Z

1U_0402_6.3V4Z

0.1U_0402_10V7K

0.1U_0402_10V7K

A9

VDDQ

C1

VDDQ

C3

VDDQ

C7

VDDQ

C9

VDDQ

A1

VDD

E9

VDD

H9

VDD

L1

VDD

E1

VDDL

ODT

CK

CK#

CKE

BA0

BA1

BA2

CS#

RAS#

CAS#

WE#

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

VSSDL

1

C58

C58

2

F9

E8

M_CLK_DDR#0

F8

F2

DDR_A_BS#0

G2

DDR_A_BS#1

G3

DDR_A_BS#2

G1

G8

F7

G7

F3

A7

B2

B8

D2

D8

A3

E3

J1

K9

E7

2

C59

C59

0.1U_0402_10V7K

0.1U_0402_10V7K

1

M_ODT

M_CLK_DDR0

DDR_A_RAS#

DDR_A_CAS#

DDR_A_WE#

+1.8VS +1.8VS

Group1Group0

+VRAM_VREFA

M_ODT 7

M_CKE0

M_CS#0

M_CLK_DDR0 7

M_CLK_DDR#0 7

M_CKE0 7

M_CS#0 7

DDR_A_RAS# 7

DDR_A_CAS# 7

DDR_A_WE# 7

M_ODT

2

1

R97

R97

10K_0402_5%

10K_0402_5%

1 2

C54

C54

0.1U_0402_10V7K

0.1U_0402_10V7K

(SSTL-1.8) VREF = .5*VDDQ

Close to U7

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DM1

DDR_A_D15

DDR_A_D10

DDR_A_D11

DDR_A_D8

DDR_A_D13

DDR_A_D14

DDR_A_D9

DDR_A_D12

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

0.01U_0402_25V7K

0.01U_0402_25V7K

U4

@U4

@

B7

DQS

A8

DQS#

B3

DM/RDQS

C8

DQ0

C2

DQ1

D7

DQ2

D3

DQ3

D1

DQ4