Page 1

A

1 1

B

C

D

E

Compal Confidential

2 2

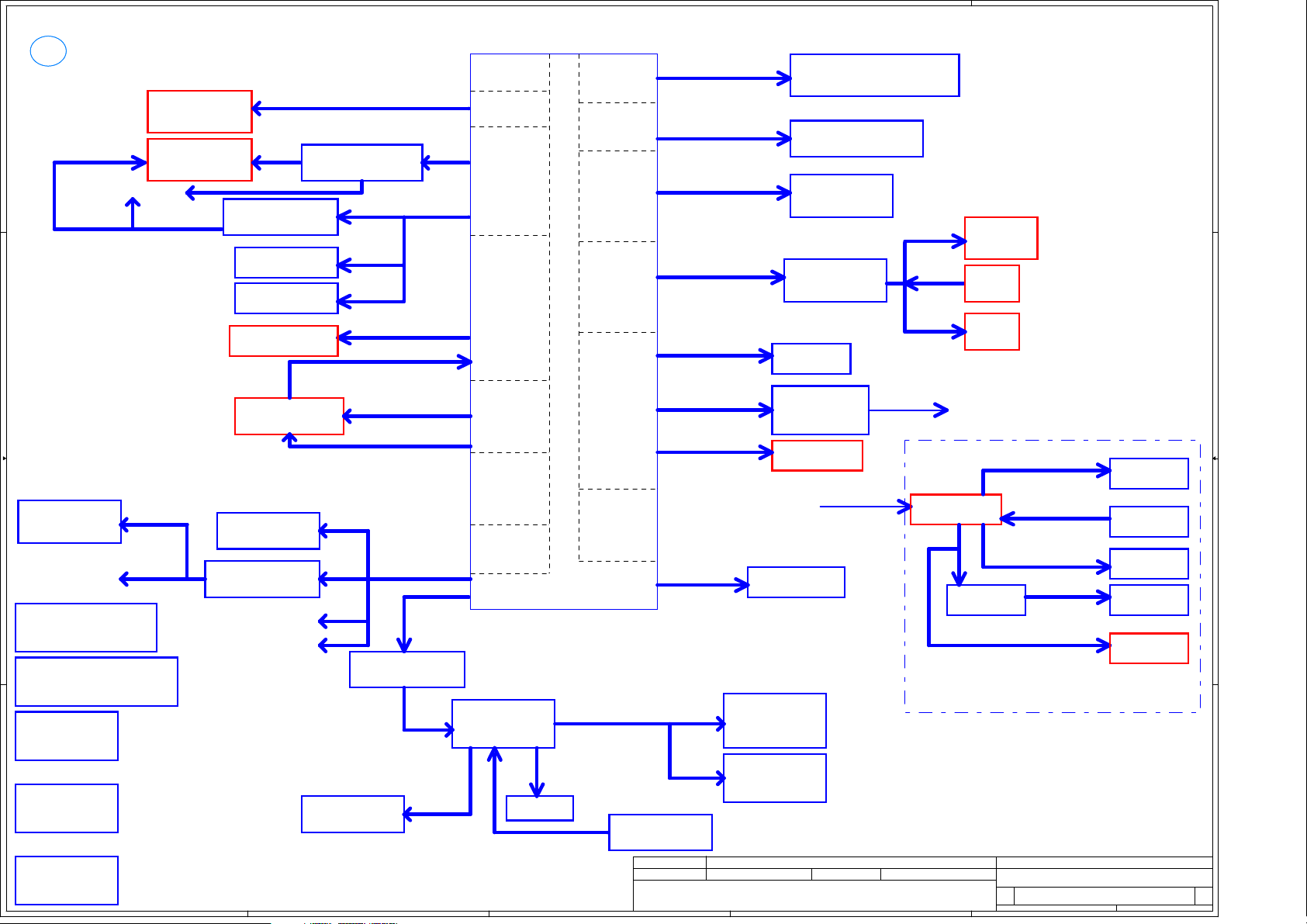

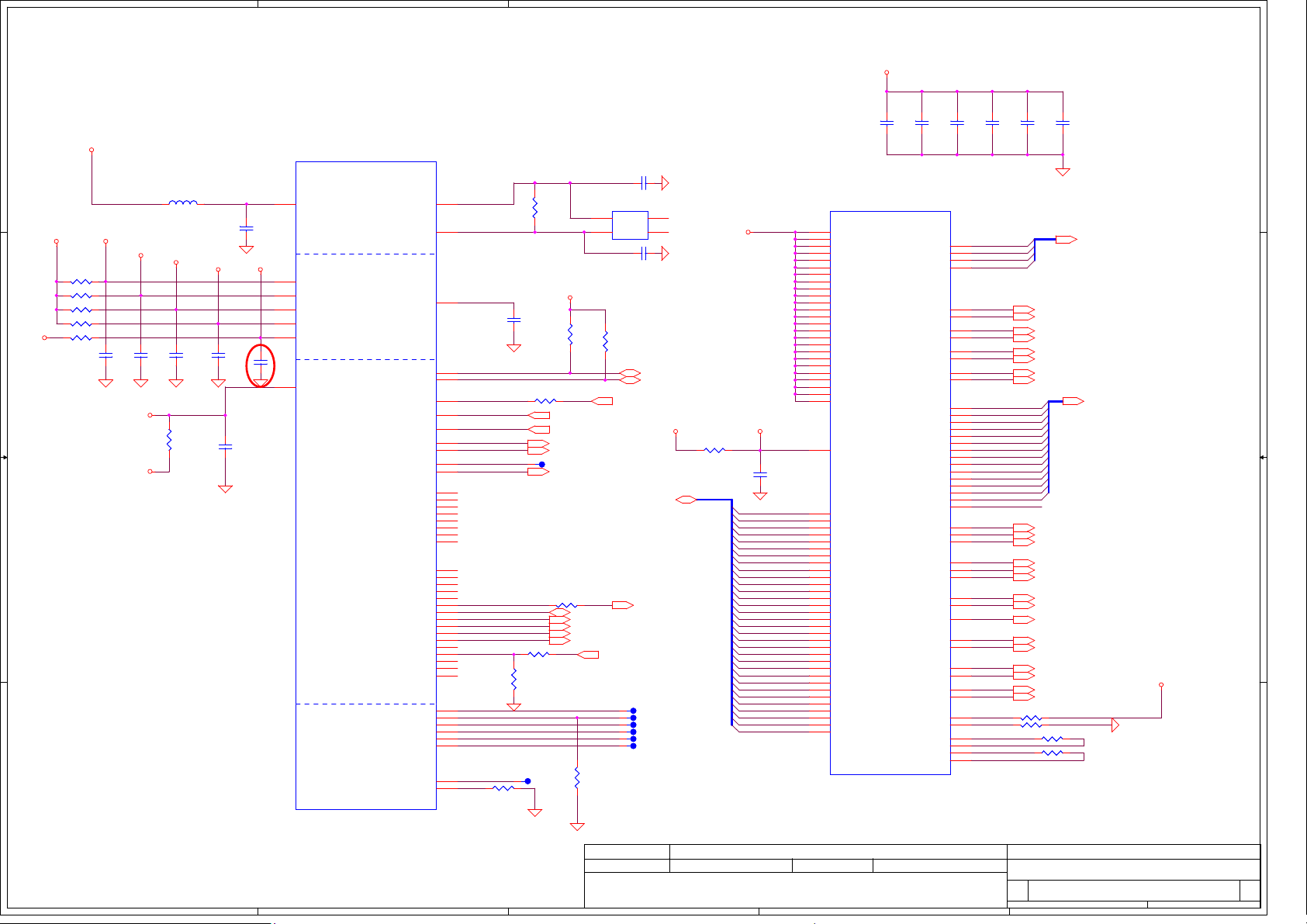

NAZ10 Schematics Document

Nvdia(T20) + DDRII

2010-02-24

REV: 0.3

3 3

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

2008/09/202006/08/18

2008/09/202006/08/18

2008/09/202006/08/18

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Cover Page

Cover Page

Cover Page

LA-6011P

LA-6011P

Friday, May 07, 2010

Friday, May 07, 2010

Friday, May 07, 2010

LA-6011P

E

0.2

0.2

1

1

1

0.2

34

34

34

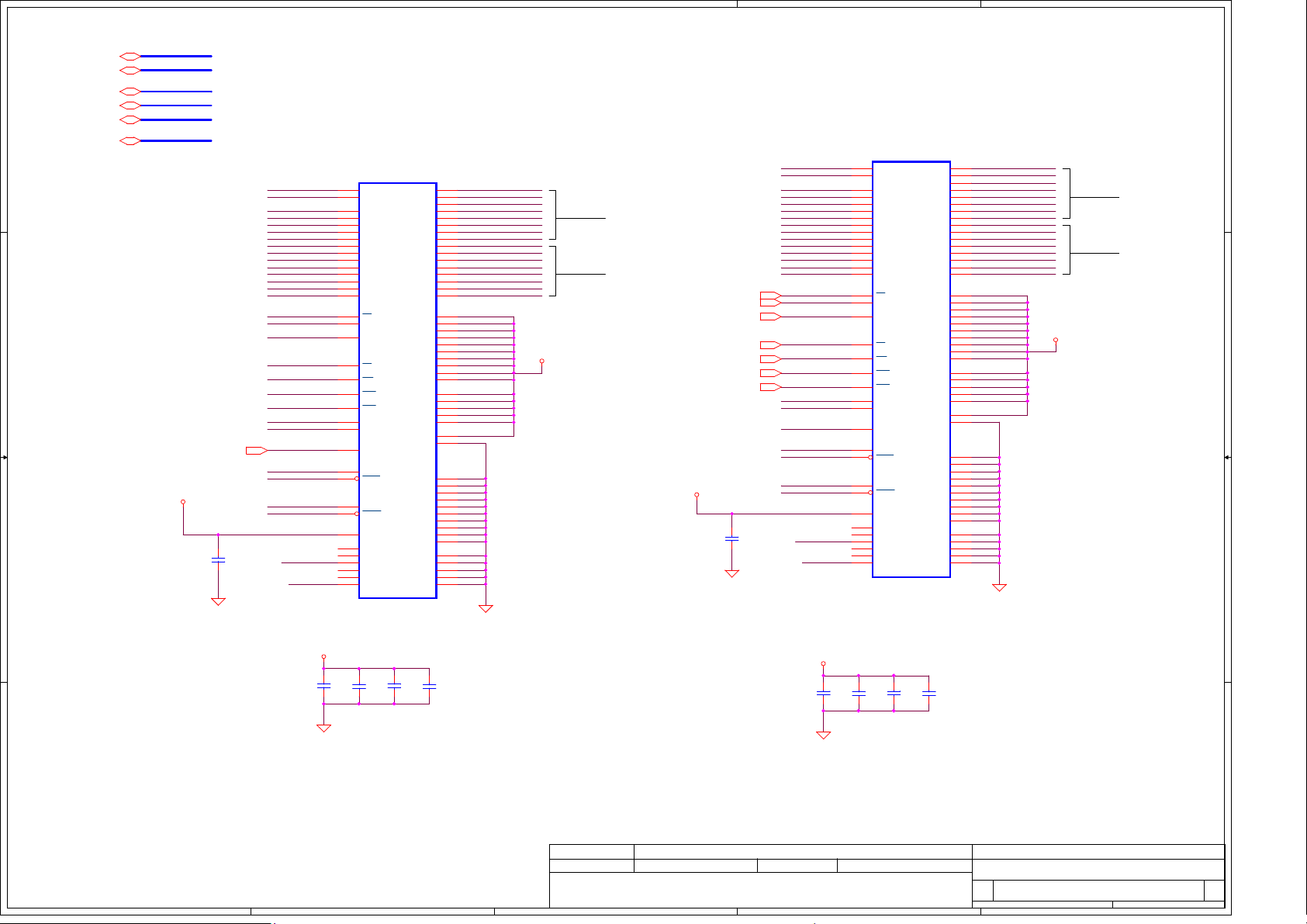

Page 2

A

ZZZ

ZZZ

DA60000G000

DA60000G000

PCB

PCB

1 1

to Docking HDMI

DDC_I2C(5V)

LCD Conn.

HDMI Conn.

I2C LEVEL SHIFT

HDMI

Analog switch

(PI3HDMI412ADZBE)

HDMI

Capacitor

Touch Screen

Resister

B

RGB

DDC_I2C(3,3V)

HDMI

U3H

VGA

U3G

LCD

U3I

HDMI

U3J U3K

ULPI

C

U3C

NAND Ctrl

U3D

DDR

U3E

U3F

BT656

VI&DSI/CSI

U3L

AUDIO

HSMMC X8

DDR2 X32

BT656

I2S(1.8V)

D

eMMC NAND

(SANDISK SDIN4C2-4G-T)

DDR2 SDRAM 512MB

(4PCS)

CAMERA Module

Audio Codec

(Wolfson WM8961)

E

by 16 bit *2 PCS PER RANK

TOTAL 2 RANK

INT Speaker

INT MIC

Touch Screen

2 2

Micro SD conn SDIO1

SDIO1(3.3V)

UART

U3M

USB1

USB Port

HeadPhone

I2S(1.8V)

U3B

WIFI module

SDIO2(1.8V)

UART(1.8V)

OSC,PLL,

key board

USB + mini-B connector

U3NU3O

PCIe&SDIO

HDMI ANALOG

SWITCH

3 3

G-SENSOR

I2C LEVEL SHIFTto LCD CONN

U3A

GEN_I2C(1.8V)GEN_I2C(3.3V)

core & fuse

U3P

U3Q

HSIC

Nvidia Tegra T20

+3VALW to +3VS Transfer

to Audio Codec

to CAMERA Module

CAM_I2C(1.8V)

ULPI

USB3

PWR_I2C(1.8V)

ULPI to USB

(SMSC USB3315)

3G Card

to Docking

PMU

USB2

DOCK CONN

HEADPHONE OUT

to Docking USB

AMPLIFIER

USB2

DC IN

HDMI

SPK

USB Port

DC IN

HDMI

SPEAKER

HeadPhone

I2C LEVEL SHIFT

+1.8VS to +1.8VS_S3 Transfer

Docking board

DC IN

CAM_I2C(3.3V)

ENE KBC

KB926 rev.D3

EC_I2C(3.3V)

BATT CONN

SPI

4 4

BATT IN

VIBRATOR

GPIO

SPI ROM

Temperature

Sensor

Light sensor

Security Classification

Security Classification

CHARGER

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

2008/09/202006/08/18

2008/09/202006/08/18

2008/09/202006/08/18

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Block Diagram

Block Diagram

Block Diagram

LA-6011P

LA-6011P

Friday, May 07, 2010

Friday, May 07, 2010

Friday, May 07, 2010

LA-6011P

E

0.2

0.2

2

2

2

0.2

34

34

34

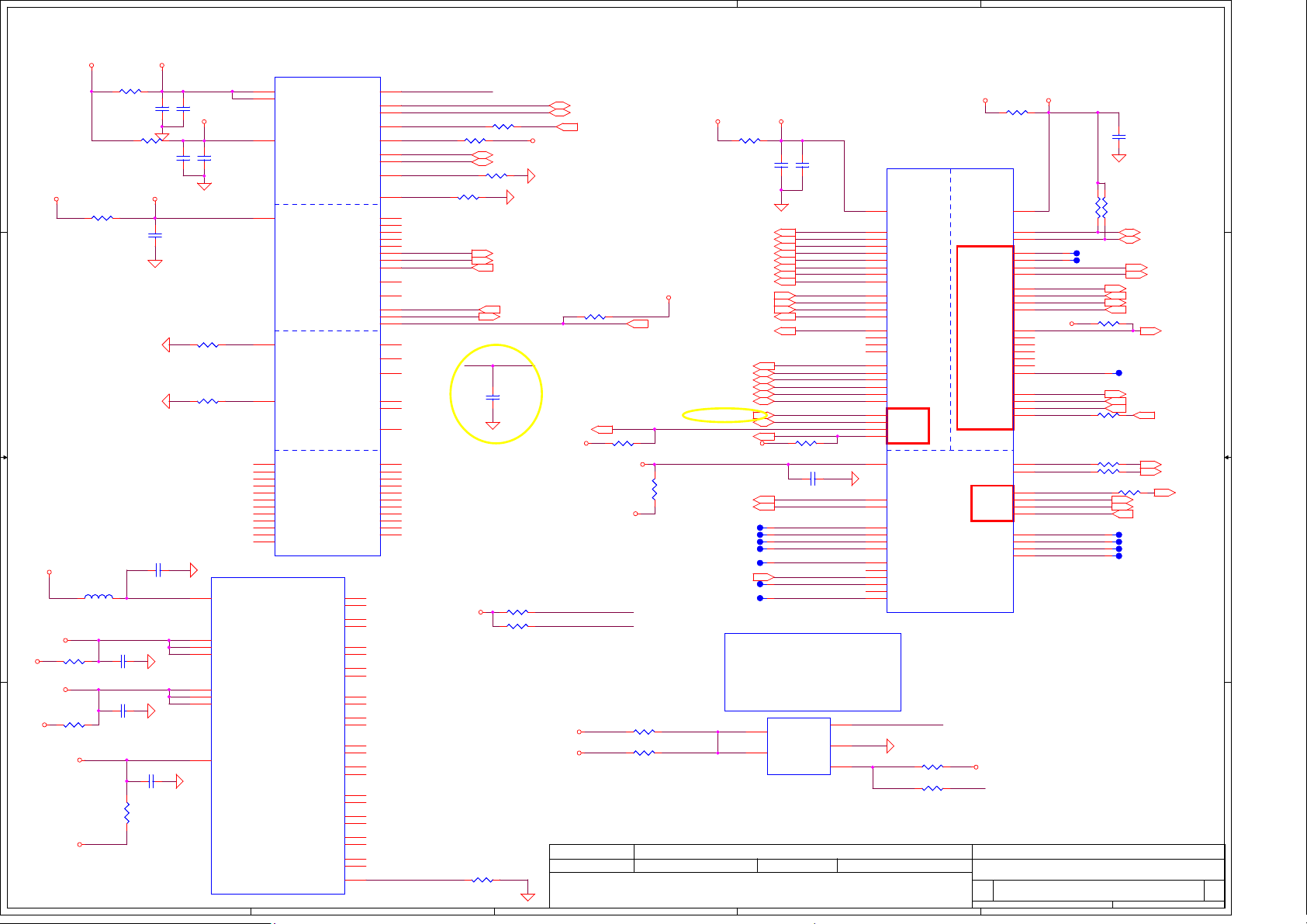

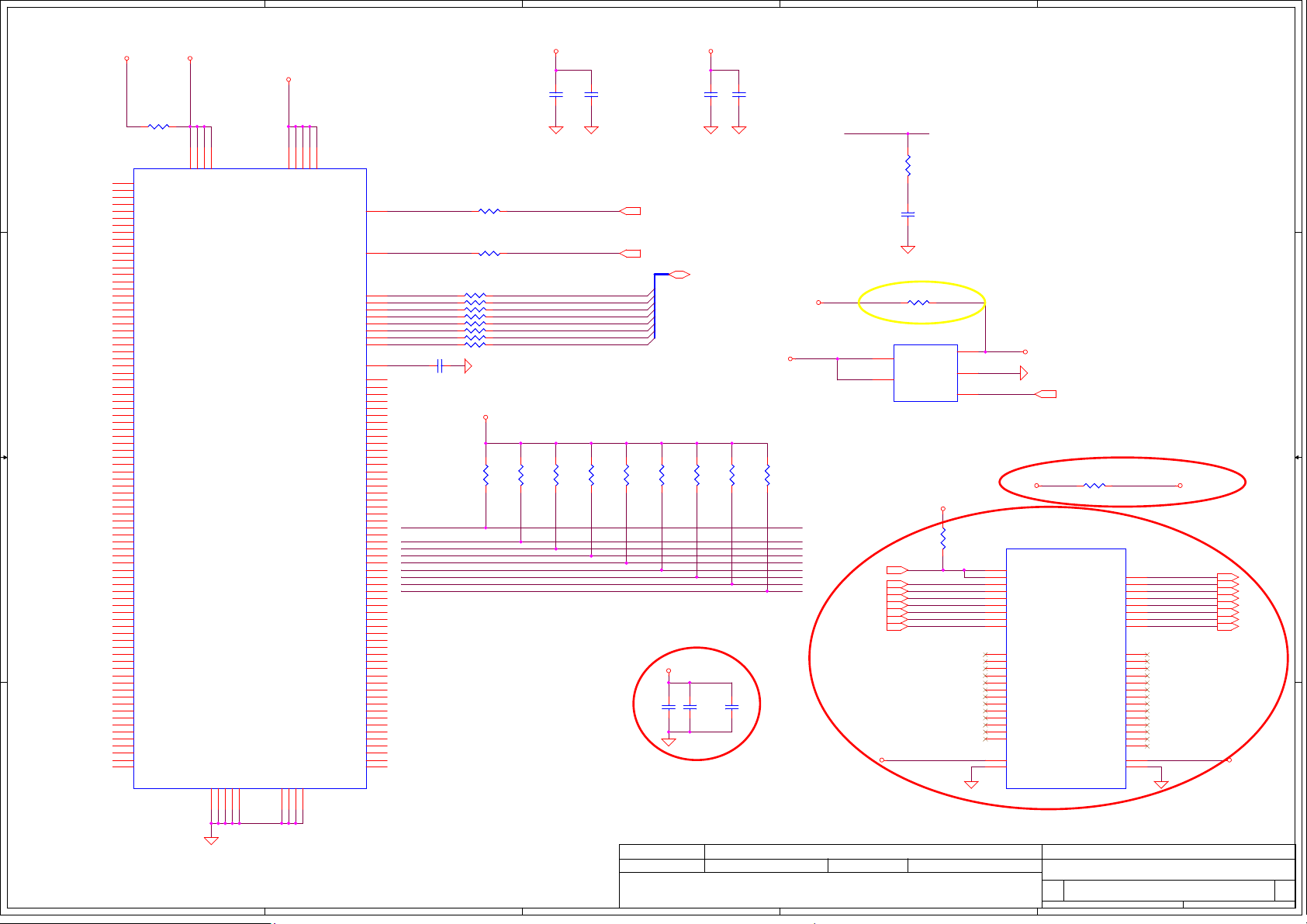

Page 3

A

1 1

B

C

D

E

Voltage Rails

DescriptionPower Plane

VIN

B+

+1.2VS_SM0

+1.0VS_SM1

+1.1VS_LDO1

+1.2VS_LDO2

Adapter power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

CPU voltage for CPU

AVDD_PLL power rail

T20 RTC power rail

+1.8VS_LDO4 T20 system power rail

+3.3VS_LDO3

+2.85VS_LDO5

2 2

+2.85VS_LDO6

+3.3VS_LDO7

+1.8VS_LDO8

T20 USB power rail

Core voltage for EMMC

Core voltage for CAMERA

T20 HDMI power rail

T20 HDMI PLL power rail

PWR_I2C address

Device

PMU

GEN1_I2C

Device

CAMERA

Audio Codec

G-sensor

Address

Address

0110 0000b

1001 0100b

0001 1101b

+2.85VS_LDO9 T20 DDR RX power rail

+3VALW

+3VS

+5VALW

+1.8VS

3.3V always on power rail

3.3V switched power rail for standby mode

5V always on power rail

1.8V always on power rail

+1.8VS_S3 1.8V switched power rail for standby mode

DDC_I2C

Device

Cap touch panel

cap sensor

Address

0010 0000b

0001 1010b

+3.3VS_RTC RTC power

CAM_I2C address

Device

Temperature sensor

BATT

Address

0100 010X b0110 100X b

GEN1_I2C_3V3

Device Address

HDMI Andlog switch 1100 000X b

HDMI_DDC_I2C

HDMI EDID

AddressDevice

1010 0000b

3 3

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS T HE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS T HE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS T HE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUST ODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUST ODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUST ODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR W RITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

2008/09/202006/08/18

2008/09/202006/08/18

2008/09/202006/08/18

D

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

Notes List

Notes List

Notes List

LA-6011P

LA-6011P

Friday, May 07, 2010

Friday, May 07, 2010

Friday, May 07, 2010

LA-6011P

0.2

0.2

0.2

3

3

3

E

34

34

34

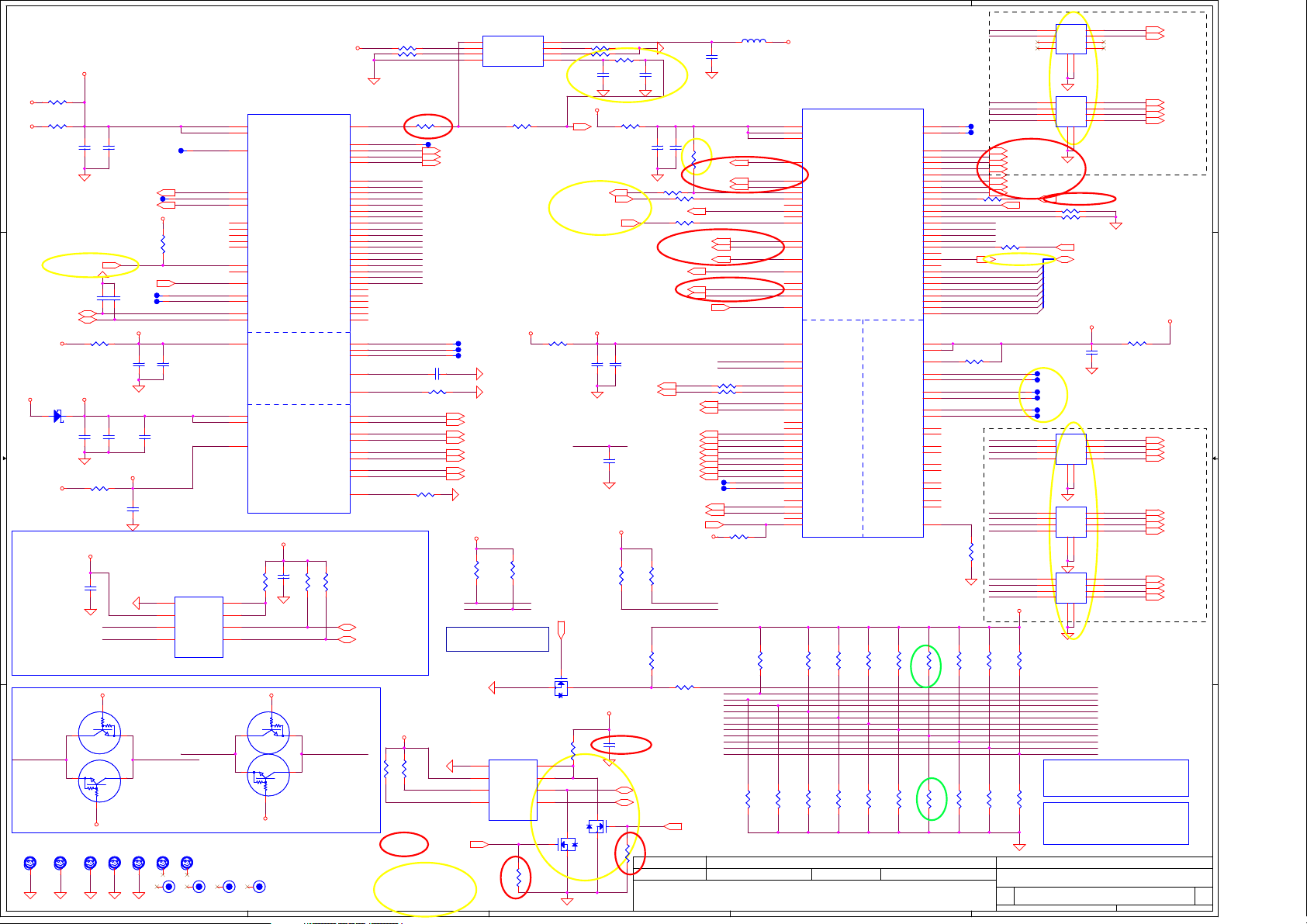

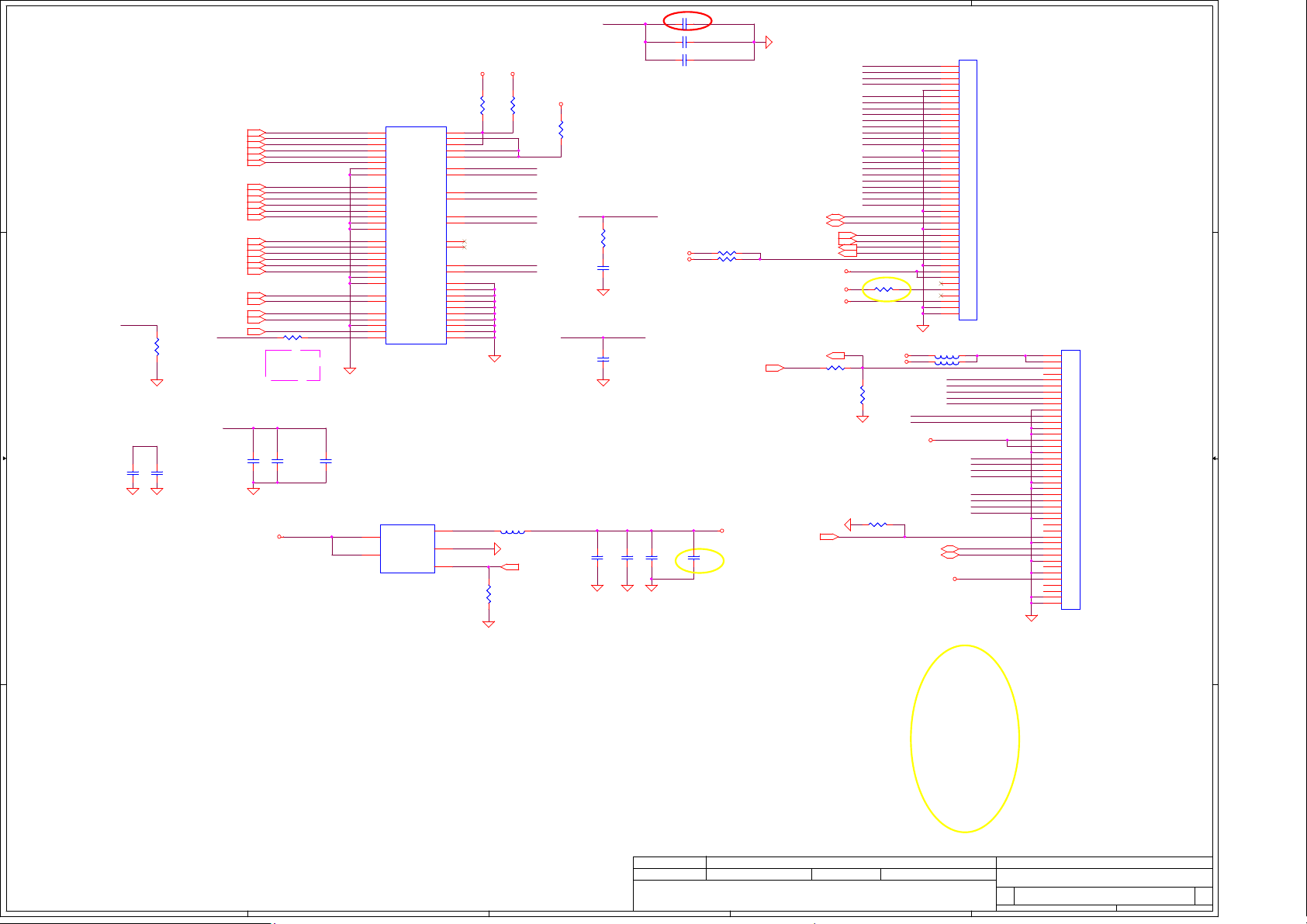

Page 4

5

+VDDIO_LCD

R943 0_0402_5%R943 0_0402_5%

R107 0_0402_5%

R107 0_0402_5%

@

@

C1

C1

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

68P_0402_50V8J

68P_0402_50V8J

DDC_SCL_3P3(11,14)

DDC_SDA_3P3(11,14)

2 1

D15

D15

2.2U_0402_6.3VMZ

2.2U_0402_6.3VMZ

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

H2

HOLEAH2HOLEA

1

1

12

12

1

2

TEMP_THERM#(14)

C1214

@ C1214

@

+AVDD_VDAC

R128 0_0201_5%

R128 0_0201_5%

@

@

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

+AVDD_HDMI

02/12 modify diode

1

C11

C11

2

R211 0_0201_5%R211 0_0201_5%

+1.8VS_S3

2

C207

C207

1

+3VS

O1G

3

G

I

2

@

@

+1.8VS_S3

H3

HOLEAH3HOLEA

1

1

C2

C2

2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

LVDS_SHTDN#(11)

TP125TP125

EN_VDD_PNL(11,15)

HDMI_HPD(18)

C1215

C1215

1

1

@

@

TP12TP12

TP13TP13

68P_0402_50V8J

68P_0402_50V8J

2

2

DDC_SCL_3P3

DDC_SDA_3P3

2.85V

12

1

C5

C5

2

@

@

3.3V

1

1

C12

C12

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

2

+AVDD_HDMI_PLL

12

1

C13

C13

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

CAM_I2C_SCL

CAM_I2C_SDA

2

DDTC124EUA-7-F_SOT323-3@

DDTC124EUA-7-F_SOT323-3@

I

Q34

Q34

3

CAM_I2C_SCL_3P3

1

O

Q36

Q36

DDTC124EUA-7-F_SOT323-3

DDTC124EUA-7-F_SOT323-3

H4

H5

HOLEAH4HOLEA

HOLEAH5HOLEA

1

1

5

TP124TP124

LVDS_SHTDN#

DBG_IRQ

EN_VDD_PNL

+VDDIO_LCD

R910

R910

100K_0201_5%

100K_0201_5%

1 2

HDMI_HPD

1

C6

C6

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

@

@

C1216

C1216

39P 50V J NPO 0402

39P 50V J NPO 0402

1.8V

U100

U100

1

GND

2

VREF1

3

SCL1

SDA14SDA2

Level shift

H7

H8

HOLEAH7HOLEA

HOLEAH8HOLEA

1

FD1FD1

1

PON_EN

CRT_HSYNC

CRT_VSYNC

VREF2

SCL2

CAM_I2C_SDA

1

FD2FD2

1

U1D

U1D

U22

VDDIO_LCD1

V22

VDDIO_LCD2

Y24

LCD_M1

AD24

LCD_PWR0

U24

LCD_PWR1

AA24

LCD_PWR2

AB21

LCD_SCK

V24

LCD_CS0#

AC25

LCD_CS1#

AA25

LCD_SDOUT

W25

LCD_SDIN

AD23

LCD_DC0

AC24

LCD_DC1

V23

HDMI_INT#

Y22

CRT_HSYNC

AC23

CRT_VSYNC

W23

DDC_SCL

Y23

DDC_SDA

AH17

AVDD_VDAC

AA15

AVDD_HDMI_1

Y15

AVDD_HDMI_2

AA12

AVDD_HDMI_PLL

T20_23X23

T20_23X23

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

R945

R945

200K_0201_1%

200K_0201_1%

8

EN

7

CAM_I2C_SCL_3P3

6

CAM_I2C_SDA_3P3

5

PCA9306DCUR_VSSOP8

PCA9306DCUR_VSSOP8

@ Q35

@

O1G

3

G

@

@

+1.8VS_S3

FD3FD3

1

1

LCD

LCD

CRT

CRT

HDMI

HDMI

+3VS

C208

C208

2

R147

R147

1

2.2K_0201_1%

2.2K_0201_1%

1 2

+3VS

2

DDTC124EUA-7-F_SOT323-3

DDTC124EUA-7-F_SOT323-3

I

Q35

O

I

Q37

Q37

DDTC124EUA-7-F_SOT323-3

DDTC124EUA-7-F_SOT323-3

2

FD4FD4

LCD_HSYNC

LCD_VSYNC

VDAC_VREF

VDAC_RSET

HDMI_TXCN

HDMI_TXD0N

HDMI_TXD0P

HDMI_TXD1N

HDMI_TXD1P

HDMI_TXD2N

HDMI_TXD2P

1 2

3

CAM_I2C_SDA_3P3

1

LCD_PCLK

LCD_WR#

HDMI_TXCP

HDMI_RSET

+3VS

D D

+1.8VS_S3

04/13 throttling function

+2.85VS_LDO6

C C

+3.3VS_LDO7

CH751H-40PT_SOD323-2

CH751H-40PT_SOD323-2

+1.8VS_LDO8

B B

CAM_I2C_SCL

A A

H1

HOLEAH1HOLEA

4

+3VS

03/04 modify to bead

LCD_PCLK_L

V28

LCD_WR#

AE24

LCD_DE

U23

LCD_DE

LCD_D00

LCD_D01

LCD_D02

LCD_D03

LCD_D04

LCD_D05

LCD_D06

LCD_D07

LCD_D08

LCD_D09

LCD_D10

LCD_D11

LCD_D12

LCD_D13

LCD_D14

LCD_D15

LCD_D16

LCD_D17

LCD_D18

LCD_D19

LCD_D20

LCD_D21

LCD_D22

LCD_D23

VDAC_R

VDAC_G

VDAC_B

1 2

AD27

AD26

AA26

AC26

AC27

AC28

AD25

AD28

Y26

Y27

Y28

Y25

AA28

AA27

U25

U28

U27

U26

V27

V26

AB25

AA23

AB23

AA22

V25

AC22

AB17

AB18

AE19

AC17

AE18

AF17

AG17

AE16

AE17

AC18

AD18

AH18

AG18

AF18

R225

R225

2.2K_0201_1%

2.2K_0201_1%

CAM_I2C_SCL_3P3 (15)

CAM_I2C_SDA_3P3 (15)

R180

R180

2.2K_0201_1%

2.2K_0201_1%

LCD_HSYNC

LCD_VSYNC

LCD_D00_R

LCD_D01_R

LCD_D02_R

LCD_D03_R

LCD_D04_R

LCD_D05_R

LCD_D06_R

LCD_D07_R

LCD_D08_R

LCD_D09_R

LCD_D10_R

LCD_D11_R

LCD_D12_R

LCD_D13_R

LCD_D14_R

LCD_D15_R

LCD_D16_R

LCD_D17_R

VDAC_VREF

VDAC_RSET

HDMI_TXCN

HDMI_TXCP

HDMI_TXD0N

HDMI_TXD0P

HDMI_TXD1N

HDMI_TXD1P

HDMI_TXD2N

HDMI_TXD2P

HDMI_RSET

04/23 delete D17

04/02 delete Q30 and Q31

4

@

@

12

R1039 0_0201_5%

R1039 0_0201_5%

12

R1040 0_0201_5%@ R1040 0_0201_5%@

12

R1042

R1042

S SUPPRE_ MURATA BLM15GA750SN1D 0402

S SUPPRE_ MURATA BLM15GA750SN1D 0402

TP17TP17

LCD_DE (11)

LCD_HSYNC (11)

LCD_VSYNC (11)

VGA_R

VGA_G

VGA_B

C10 0.1U_0201_6.3V6KC10 0.1U_0201_6.3V6K

1 2

1 2

R7 1K_0201_1%R7 1K_0201_1%

12

R21 1K_0201_1%R21 1K_0201_1%

10K_0201_5%

10K_0201_5%

H:force_recover mode

L:normal mode

+3VS

R234

R234

2.2K_0201_1%

2.2K_0201_1%

1 2

1 2

DDC_SCL_3P3

DDC_SDA_3P3

I2C_RST( 6)

U110

U110

1

CLKIN

2

PD#/OE

3

FS

GND4ModOUT

PCS3P73Z01BWG-08-CR_TDFN8_2X2

PCS3P73Z01BWG-08-CR_TDFN8_2X2

@

@

LCD_PCLK

R930 0_0402_5%R930 0_0402_5%

TP14TP14

TP15TP15

TP16TP16

HDMI_TXCN (18)

HDMI_TXCP (18)

HDMI_TXD0N (18)

HDMI_TXD0P (18)

HDMI_TXD1N (18)

HDMI_TXD1P (18)

HDMI_TXD2N (18)

HDMI_TXD2P (18)

+VDDIO_VI

R11

R11

1 2

VI_MCLK

VI_PCLK

BSS138W-7-F_SOT323-3~D

BSS138W-7-F_SOT323-3~D

U102

U102

1

GND

2

VREF1

3

SCL1

SDA14SDA2

PCA9306DCUR_VSSOP8

PCA9306DCUR_VSSOP8

I2C_RST

R1064

R1064

100K_0201_5%

100K_0201_5%

04/23 defualt low

SSEXTR

DLY_CTRL

+1.8VS_S3

R10

R10

10K_0201_5%

10K_0201_5%

1 2

Q15

Q15

200K_0201_1%

200K_0201_1%

EN

VREF2

SCL2

1 2

VDD

12

+3VS_SS

8

@

@

7

R1041 0_0201_5%

R1041 0_0201_5%

6

SSIC_CLK

R1055 0_0201_5%

R1055 0_0201_5%

5

C1228

C1228

33P_0201_25VNPO

33P_0201_25VNPO

@

@

+VDDIO_MMC

LCD_PCLK_R(11)

VIB_EN_T20#(19)

DOCK_ON(14,15,18)

PWR_OFF_AP(15)

04/02 ASC request

+VDDIO_VI

12

R134 0_0201_5%R134 0_0201_5%

C7

C7

2.2U_0402_6.3VMZ

2.2U_0402_6.3VMZ

VI_MCLK_R

C1217

C1217

39P 50V J NPO 0402

39P 50V J NPO 0402

@

@

2.2K_0201_1%

2.2K_0201_1%

FORCE_RECOVERY(15)

G

G

2

13

D

S

D

S

+VDDIO_HDMI

R946

R946

8

1 2

7

6

5

2

G

G

D

D

13

D

D

S

S

Q44

Q44

BSS138W-7-F_SOT323-3~D

BSS138W-7-F_SOT323-3~D

S

S

3

L22

@L22

@

@

12

12

12

1

1

2

C1234

C1234

R1056 0_0201_5%

R1056 0_0201_5%

33P_0201_25VNPO

33P_0201_25VNPO

@

@

2

04/12 add resistor and cap

04/02 pull high for default

12

R127 0_0402_5%R127 0_0402_5%

2.2U_0402_6.3VMZ

2.2U_0402_6.3VMZ

1

C3

C3

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

R1046 0_0402_5%R1046 0_0402_5%

R1047 0_0402_5%R1047 0_0402_5%

HSMMC_CLK(10)

R1048 0_0402_5%R1048 0_0402_5%

HSMMC_CMD(10)

NAND_BSY#(10)

NAND_WP#(10)

1.8V 1.2V

1

1

C8

C8

2

2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

VI_MCLK_R(16)

VI_PCLK_R(16)

VI_HSYNC(16)

VI_VSYNC(16)

1

2

+VDDIO_VI

13

ACCELERO_INT#(14)

12

12

R38

R38

47K_0201_1%

47K_0201_1%

2

1

BSS138W-7-F_SOT323-3~D

BSS138W-7-F_SOT323-3~D

Q43

Q43

3

R39

R39

2.2K_0201_1%

2.2K_0201_1%

12

R17

R17

C209

C209

1U_0402_6.3V4Z

1U_0402_6.3V4Z

04/23 0.1U change to 1U

HDMI_DDC_SCL (14,18)

HDMI_DDC_SDA (14,18)

LS_EN#

2

G

G

R1063

R1063

04/23 defualt low

100K_0201_5%

100K_0201_5%

Security Classification

Security Classification

Security Classification

1 2

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

@

@

+VDDIO_NAND

1

C4

C4

12

2

NAND_ALE(10)

R1045 100K_0201_5%R1045 100K_0201_5%

NAND_CE0(10)

NAND_CE1(10)

12

12

12

NAND_RE#(10)

NAND_WE#(10)

NAND_CLE(10)

SDIO1_CD#(13)

VI_MCLK_R

VI_D02(16)

VI_D03(16)

VI_D04(16)

VI_D05(16)

VI_D06(16)

VI_D07(16)

VI_D08(16)

VI_D09(16)

TP41TP41

TP42TP42

CAM_RST#(16)

CAM_PWDN(16)

+1.8VS_S3

CAM_I2C_SCL

CAM_I2C_SDA

R20

R20

1 2

47K_0201_1%

47K_0201_1%

LS_EN# (6)

1

2

VIB_EN_T20#_R

HSMMC_CLK

HSMMC_CMD

NAND_BSY#

NAND_WP#

@

1 2

FBMA-10-100505-121T_0402

FBMA-10-100505-121T_0402

C1229

C1229

0.01U_0201_16V7

0.01U_0201_16V7

@

@

NAND_ALE

DOCK_ON_R

PWR_OFF_AP_R

NAND_RE#

NAND_WE#

NAND_CLE

SDIO1_CD#

CAM_I2C_SCL

CAM_I2C_SDA

R931 0_0201_5%R931 0_0201_5%

12

12

R932 0_0201_5%R932 0_0201_5%

VI_HSYNC

VI_VSYNC

VI_D02

VI_D03

VI_D04

VI_D05

VI_D06

VI_D07

VI_D08

VI_D09

CAM_RST#

CAM_PWDN

ACCELERO_INT#

12

R944 10K_0201_5%R944 10K_0201_5%

12

R18

R18

12

R63

R63

100K_0201_5%

100K_0201_5%

VI_MCLK

VI_PCLK

R69

R69

100K_0201_5%

100K_0201_5%

12

+3VS

Y7

Y8

Y9

AH3

AF5

AF12

AD12

AC6

AC12

AB12

AD5

AD9

AG9

AF6

AF3

AC9

AC7

AF1

AF2

AC10

L21

H28

H27

L24

L28

L25

K25

H23

H25

J23

J28

J24

J27

J25

J26

K23

L26

L23

M22

L22

M23

J22

L27

M24

R68

R68

R70

R70

@

@

100K_0201_5%

100K_0201_5%

Compal Secret Data

Compal Secret Data

Compal Secret Data

2

03/02 EMI filter for RF request

U1E

U1E

VDDIO_NAND_1

VDDIO_NAND_2

VDDIO_NAND_3

GMI_ADV#

GMI_CS0#

GMI_CS1#

GMI_CS2#

GMI_CS3#

GMI_CS4#

GMI_CS5#

GMI_CS6#

GMI_CS7#

GMI_OE#

GMI_WR#

GMI_CLK

GMI_DPD

GMI_RST#

GMI_WAIT

GMI_WP#

GMI_IORDY

VI MIPI

VI MIPI

VDDIO_VI

CAM_I2C_SCL

CAM_I2C_SDA

VI_MCLK

VI_PCLK

VI_HSYNC

VI_VSYNC

VI_D00

VI_D01

VI_D02

VI_D03

VI_D04

VI_D05

VI_D06

VI_D07

VI_D08

VI_D09

VI_D10

VI_D11

VI_GP0

VI_GP3

VI_GP4

VI_GP5

VI_GP6

T20_23X23

T20_23X23

12

R66

R66

100K_0201_5%

100K_0201_5%

12

R29

R29

100K_0201_5%

100K_0201_5%

Deciphered Date

Deciphered Date

Deciphered Date

12

@

@

12

NAND

NAND

R65

R65

@

@

100K_0201_5%

100K_0201_5%

R30

R30

100K_0201_5%

100K_0201_5%

2

GEN2_I2C_SCL

GEN2_I2C_SDA

AVDD_DSI_CSI_1

AVDD_DSI_CSI_2

DSI_CSI_RUP

CSI_CLKAN

CSI_CLKAP

CSI_CLKBN

CSI_CLKBP

DSI_CLKAN

DSI_CLKAP

DSI_CSI_RDN

12

R64

R64

@

@

100K_0201_5%

100K_0201_5%

12

R35

R35

100K_0201_5%

100K_0201_5%

GMI_AD0

GMI_AD1

GMI_AD2

GMI_AD3

GMI_AD4

GMI_AD5

GMI_AD6

GMI_AD7

GMI_AD8

GMI_AD9

GMI_AD10

GMI_AD11

GMI_AD12

GMI_AD13

GMI_AD14

GMI_AD15

GMI_AD16

GMI_AD17

GMI_AD18

GMI_AD19

GMI_AD20

GMI_AD21

GMI_AD22

GMI_AD23

GMI_AD24

GMI_AD25

GMI_AD26

GMI_AD27

CSI_D1AN

CSI_D1AP

CSI_D2AN

CSI_D2AP

CSI_D1BN

CSI_D1BP

DSI_D1AN

DSI_D1AP

DSI_D2AN

DSI_D2AP

12

12

2008/09/202006/08/18

2008/09/202006/08/18

2008/09/202006/08/18

2G@

2G@

R42

R42

100K_0201_5%

100K_0201_5%

R31

R31

100K_0201_5%

100K_0201_5%

1G@

1G@

AD11

AD6

NAND_D0

AG5

NAND_D1

AE9

NAND_D2

AF11

NAND_D3

AG6

NAND_D4

AH8

NAND_D5

AG11

NAND_D6

AF9

NAND_D7

AF8

AE6

SDIO1_WP

AE12

HSMMC_CD#

AH12

HSMMC_WP

AH6

GMI_AD12

AH11

GMI_AD13

AG3

GMI_AD14

AH9

GMI_AD15

AH5

T20_WAKE#_R

AG12

AD3

AE5

AG8

AD8

AE7

AC5

AE11

AE8

AC11

AE10

AC8

02/12 add resistor

AA17

Y16

AF21

R1023 453_0402_1%R1023 453_0402_1%

AH26

AG26

AD20

AE20

AH23

AG23

AB20

AC20

AH24

AG24

AD21

AC21

AF20

AG20

AH21

AG21

AH20

R51

R51

49.9_0402_1%

49.9_0402_1%

12

12

R41

R41

@

@

100K_0201_5%

100K_0201_5%

12

12

R32

R32

100K_0201_5%

100K_0201_5%

LCD_D04_R

LCD_D05_R

LCD_D00_R

LCD_D01_R

LCD_D02_R

LCD_D03_R

TP47TP47

TP48TP48

1 2

R179 0_0201_5%R179 0_0201_5%

CPU_READY (15)

HSMMC_DAT0

HSMMC_DAT1

HSMMC_DAT2

HSMMC_DAT3

HSMMC_DAT4

HSMMC_DAT5

HSMMC_DAT6

HSMMC_DAT7

12

CSI_CLK#

CSI_CLK

CSI_A1#

CSI_A1

CSI_A2#

CSI_A2

LCD_D08_R

LCD_D09_R

LCD_D10_R

LCD_D11_R

LCD_D16_R

LCD_D17_R

LCD_D06_R

LCD_D07_R

1 2

LCD_D15_R

LCD_D14_R

LCD_D13_R

LCD_D12_R

+VDDIO_MMC

12

R40

R40

@

@

100K_0201_5%

100K_0201_5%

100K_0201_5%

100K_0201_5%

12

R36

R36

100K_0201_5%

100K_0201_5%

100K_0201_5%

100K_0201_5%

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

2

3

4

1

2

3

4

NAND_D0 (10)

NAND_D1 (10)

NAND_D2 (10)

NAND_D3 (10)

NAND_D4 (10)

NAND_D5 (10)

NAND_D6 (10)

NAND_D7 (10)

R2330_0201_5% R2330_0201_5%

SDIO1_WP (13)

12

04/12 GMI_AD18 modify to CPU_READY

TP51TP51

TP56TP56

TP57TP57

TP58TP58

TP59TP59

TP60TP60

1

2

3

4

1

2

3

4

L27

L27

1

2

3

4

12

R19

R19

@

@

100K_0201_5%

100K_0201_5%

GMI_AD12 1 1

GMI_AD13

GMI_AD14

12

GMI_AD15

R34

R34

RAM

100K_0201_5%

100K_0201_5%

NAND_D4

NAND_D5

NAND_D6

NAND_D7

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

T20(1/4)LCD/CRT/HDMI/NAND

T20(1/4)LCD/CRT/HDMI/NAND

T20(1/4)LCD/CRT/HDMI/NAND

Tuesday, May 11, 2010

Tuesday, May 11, 2010

Tuesday, May 11, 2010

1

L23

L23

5

A1

B1

6

A2

B2

7

A3

B3

8

A4

B4

GND9GND

ICVE21184E070R100FR_10P

ICVE21184E070R100FR_10P

10

L24

L24

5

A1

B1

6

A2

B2

7

A3

B3

8

A4

B4

GND9GND

ICVE21184E070R100FR_10P

ICVE21184E070R100FR_10P

10

CAP_TS_INT# (11)

R511 100K_0201_5%R511 100K_0201_5%

1 2

1 2

R512 100K_0201_5%R512 100K_0201_5%

T20_WAKE# (5,15)

HSMMC_DAT[0..7] (10)

02/23 add resistor

+AVDD_DSI_CSI

1

R1029 0_0402_5%R1029 0_0402_5%

C9

C9

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

04/12 modify test point

L25

L25

5

A1

B1

6

A2

B2

7

A3

B3

8

A4

B4

GND9GND

ICVE21184E070R100FR_10P

ICVE21184E070R100FR_10P

10

L26

L26

5

A1

B1

6

A2

B2

7

A3

B3

8

A4

B4

GND9GND

ICVE21184E070R100FR_10P

ICVE21184E070R100FR_10P

10

5

A1

B1

6

A2

B2

7

A3

B3

8

A4

B4

GND9GND

ICVE21184E070R100FR_10P

ICVE21184E070R100FR_10P

10

NAND_RE#

NAND_WE#

NAND_CLE

NAND_ALE

GMI_AD12

GMI_AD13

GMI_AD14

GMI_AD15

NAND_D4

NAND_D5

NAND_D6

NAND_D7

eMMC boot NAND boot

0

0

0 0

0

0

LA-6011P

LA-6011P

LA-6011P

1

LCD_D04 (11)

LCD_D05 (11)

LCD_D00 (11)

LCD_D01 (11)

LCD_D02 (11)

LCD_D03 (11)

+1.2VS

12

LCD_D08 (11)

LCD_D09 (11)

LCD_D10 (11)

LCD_D11 (11)

LCD_D16 (11)

LCD_D17 (11)

LCD_D06 (11)

LCD_D07 (11)

LCD_D15 (11)

LCD_D14 (11)

LCD_D13 (11)

LCD_D12 (11)

10

0

0

2G1G

10

0

0

0.2

0.2

4

4

4

0.2

34

34

34

Page 5

5

D D

+1.8VS_LDO4

+1.1VS_LDO1

1 2

0_0201_5%

0_0201_5%

1 2

0_0201_5%

0_0201_5%

1 2

0_0201_5%

0_0201_5%

1 2

0_0201_5%

0_0201_5%

1 2

+1.05VS

C C

B B

A A

0_0201_5%

0_0201_5%

@

@

1.8V

1.1V

+AVDD_PLL_P_C

+AVDD_PLLU

R212

R212

R213

R213

R214

R214

R215

R215

R216

R216

1

C24

C24

2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

+1.8VS_SYS

1.8V

+1.8VS_LDO4

220Ω @100MHz

L1

L1

1 2

FBMA-10-100505-221T_0402

FBMA-10-100505-221T_0402

1.1V

1.1V

+AVDD_PLLX

+AVDD_PLLM +AVDD_PLLE

1

1

C25

C25

C28

C28

2

2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

R210

R210

0_0201_5%

0_0201_5%

1 2

+AVDD_OSC

1.1V

1

C27

C27

2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

C30

C30

H12

C15

C15

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1.05V

H14

AA18

L7

H15

Y1

1

C29

C29

@

@

2

G18

U1B

U1B

OSC, PLL, SYS

OSC, PLL, SYS

AVDD_OSC

AVDD_PLLA_P_C

AVDD_PLLU

AVDD_PLLX

AVDD_PLLM

AVDD_PLLE

VDDIO_SYS

T20_23X23

T20_23X23

4

XTAL_IN

XTAL_OUT

AVDD_PLL_S_LF

PWR_I2C_SCL

PWR_I2C_SDA

SYS_RESET#

CLK_32K_IN

PWR_INT#

CORE_PWR_REQ

CPU_PWR_REQ

SYS_CLK_REQ

CLK_32K_OUT

KB_COL0

KB_COL1

KB_COL2

KB_COL3

KB_COL4

KB_COL5

KB_COL6

KB_COL7

KB_ROW00

KB_ROW01

KB_ROW02

KB_ROW03

KB_ROW04

KB_ROW05

KB_ROW06

KB_ROW07

KB_ROW08

KB_ROW09

KB_ROW10

KB_ROW11

KB_ROW12

KB_ROW13

KB_ROW14

KB_ROW15

JTAG_RTCK

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRST#

OWR

TEST_MODE_EN

T20_XTAL_IN

E3

T20_XTAL_OUT

E2

PLL_S_PLL_LF

G12

C1

C2

SYS_RESET#_R

D17

B14

D14

G14

C14

D7

D5

A6

D6

A5

B5

C5

B3

A3

C3

C12

B12

A12

D11

A11

B11

C11

C9

B9

A9

D8

A8

B8

C8

C6

B6

A17

B17

B15

C15

C17

A15

SNN_OWR

G11

A14

2M_0402_5%

2M_0402_5%

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

PWR_I2C_SCL

PWR_I2C_SDA

CLK_32K_IN

PWR_INT#

CORE_PWR_REQ

CPU_PWR_REQ

SYS_CLK_REQ

CLK_32K_OUT

SDIO2_CLK

SDIO2_CMD

SDIO2_DAT0

SDIO2_DAT1

SDIO2_DAT2

SDIO2_DAT3

JTAG_RTCK

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRST#

R50

R50

1 2

0_0201_5%

0_0201_5%

R43

R43

1 2

1

C26

C26

R45

R45

2

R226 0_0201_5%R226 0_0201_5%

CLK_32K_IN (15,28)

PWR_INT# (28)

CORE_PWR_REQ (28)

CPU_PWR_REQ (28)

TP27TP27

CLK_32K_OUT (20)

R933 0_0201_5%R933 0_0201_5%

R957 47K_0201 _1%

R957 47K_0201 _1%

1 2

@

@

12

R958

R958

57.6K_0402_1%

57.6K_0402_1%

@

@

TP28TP28

+1.8V

1.8V

12

2.2K_0201_1%

2.2K_0201_1%

12

12

SDIO2_CMD (20)

SDIO2_DAT0 (20)

SDIO2_DAT1 (20)

SDIO2_DAT2 (20)

SDIO2_DAT3 (20)

12

3

8P_0402_50V8J

8P_0402_50V8J

C16

C16

1 2

Y1 12MHZ 9PF X3S012000B91H-XY1 12MHZ 9PF X3S012000B91H-X

2

IN1NC

4

OUT3NC

C23

C23

1 2

8P_0402_50V8J

8P_0402_50V8J

12

R46

R46

2.2K_0201_1%

2.2K_0201_1%

PWR_I2C_SCL (28)

PWR_I2C_SDA (28)

SYS_RESET# (15,28)

+2.85VS_LDO9

DDR_A_D[0..31](8,9)

SDIO2_CLK_R (20)

connect to WIFI

T20_WAKE# (4,15)

TP127TP127

TP128TP128

TP129TP129

TP130TP130

TP131TP131

TP132TP132

R48

R48

10K_0201_5%

10K_0201_5%

+1.8V

PMU reset T20

+VDD_DDR_RX

R1290_0201 _5% R1290_0201_5%

1 2

C86

C86

2.85V

1

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

2

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

M17

M18

M20

N18

N20

R20

U20

H17

D18

D21

D15

D16

D12

D13

H22

G25

D24

H24

H20

J12

J13

J14

J15

J16

J17

J18

J19

J20

J21

K20

L16

L17

L20

P20

T20

V20

F20

E18

F18

F17

E21

F21

E17

F16

E14

F13

F23

F25

F22

E23

F9

F12

E12

E9

F10

G8

F11

G9

C31

C31

U1C

U1C

VDDIO_DDR_01

VDDIO_DDR_02

VDDIO_DDR_03

VDDIO_DDR_04

VDDIO_DDR_05

VDDIO_DDR_06

VDDIO_DDR_07

VDDIO_DDR_08

VDDIO_DDR_09

VDDIO_DDR_10

VDDIO_DDR_11

VDDIO_DDR_12

VDDIO_DDR_13

VDDIO_DDR_14

VDDIO_DDR_15

VDDIO_DDR_16

VDDIO_DDR_17

VDDIO_DDR_18

VDDIO_DDR_19

VDDIO_DDR_20

VDDIO_DDR_21

VDDIO_DDR_22

VDDIO_DDR_23

VDDIO_DDR_24

VDDIO_DDR_25

VDD_DDR_RX

DDR_DQ00

DDR_DQ01

DDR_DQ02

DDR_DQ03

DDR_DQ04

DDR_DQ05

DDR_DQ06

DDR_DQ07

DDR_DQ08

DDR_DQ09

DDR_DQ10

DDR_DQ11

DDR_DQ12

DDR_DQ13

DDR_DQ14

DDR_DQ15

DDR_DQ16

DDR_DQ17

DDR_DQ18

DDR_DQ19

DDR_DQ20

DDR_DQ21

DDR_DQ22

DDR_DQ23

DDR_DQ24

DDR_DQ25

DDR_DQ26

DDR_DQ27

DDR_DQ28

DDR_DQ29

DDR_DQ30

DDR_DQ31

T20_23X23

T20_23X23

2

+1.8V

DDR2

DDR2

1

C145

C145

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

DDR_DQS0N

DDR_DQS0P

DDR_DQS1N

DDR_DQS1P

DDR_DQS2N

DDR_DQS2P

DDR_DQS3N

DDR_DQS3P

DDR_RAS#

DDR_CAS#

DDR_CS0#

DDR_CS1#

DDR_ODT0

DDR_CKE0

DDR_CKE1

DDR_CLK#

THERMD_N

THERMD_P

DDR_COMP_PU

DDR_COMP_PD

DDR_QUSE0

DDR_QUSE1

DDR_QUSE2

DDR_QUSE3

1.8V

1

2

DDR_DM0

DDR_DM1

DDR_DM2

DDR_DM3

DDR_A00

DDR_A01

DDR_A02

DDR_A03

DDR_A04

DDR_A05

DDR_A06

DDR_A07

DDR_A08

DDR_A09

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

DDR_WE#

DDR_BA0

DDR_BA1

DDR_BA2

DDR_CLK

C146

C146

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

1

C147

C147

C148

C148

2

2

F19

E15

G23

D9

D19

E20

F14

F15

E24

F24

E11

D10

A20

C24

D20

B20

F26

C26

C27

F28

A26

A23

D23

C20

C18

E28

C28

B23

H26

F27

B26

A24

B24

E25

C23

B21

A21

C21

E27

E26

E6

F7

E8

F8

G15

G17

A18

B18

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

R6 49.9_0402_1%R6 49.9_0402_1%

R49 49.9_0402_1%R49 49.9_0402_1%

DDR_QUSE0

DDR_QUSE1

DDR_QUSE2

DDR_QUSE3

1

2

THERMD_N (14)

THERMD_P (14)

1 2

1 2

1 2

0_0201_5%

0_0201_5%

1 2

0_0201_5%

0_0201_5%

1

C149

C149

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

DDR_A_DM[0..3] (8,9)

DDR_A_DQS#0 (8,9)

DDR_A_DQS0 (8,9)

DDR_A_DQS#1 (8,9)

DDR_A_DQS1 (8,9)

DDR_A_DQS#2 (8,9)

DDR_A_DQS2 (8,9)

DDR_A_DQS#3 (8,9)

DDR_A_DQS3 (8,9)

DDR_A_MA[0..13] (8,9)

DDR_A_RAS# (8,9)

DDR_A_CAS# (8,9)

DDR_A_WE# (8,9)

DDR_A_BS#0 (8,9)

DDR_A_BS#1 (8,9)

DDR_A_BS#2 (8,9)

M_CS#0 (8)

M_CS#1 (9)

M_ODT (8,9)

M_CKE0 (8)

M_CKE1 (9)

M_CLK_DDR#0 (8,9)

M_CLK_DDR0 (8,9)

R9

R9

R8

R8

1

+1.8V

1.8V

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

2008/09/202006/08/18

2008/09/202006/08/18

2008/09/202006/08/18

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

T20(2/4)OSC/PLL/SYS/DDR

T20(2/4)OSC/PLL/SYS/DDR

T20(2/4)OSC/PLL/SYS/DDR

LA-6011P

LA-6011P

Friday, May 07, 2010

Friday, May 07, 2010

Friday, May 07, 2010

LA-6011P

1

0.2

0.2

5

5

5

0.2

34

34

34

Page 6

A

3.3V

+3.3VS_LDO3

2.2U_0603_6.3V6K

R135 0_0201_5%R135 0_0201_5%

1.05V

L2

L2

1 2

120Ω @100MHz

@

@

1 2

@

1 2

@

2.2U_0603_6.3V6K

R2180_0402_5%@R2180_0402_5%

R2170_0402_5%@R2170_0402_5%

3.3V

1 1

+3VS

2 2

+1.05VS

3 3

FBMA-10-100505-121T_0402

FBMA-10-100505-121T_0402

1.05V

+AVDD_PEX

+1.05VS

+VDD_PEX

1.05V

+1.05VS

+VDDIO_PEX_CLK

4 4

+3.3VS_LDO0

+AVDD_USB

R156

R156

12

0_0201_5%

0_0201_5%

C32

C32

R157 0_0201_5%R157 0_0201_5%

39P 50V J NPO 0402

39P 50V J NPO 0402

+VDDIO_SDIO

12

C39

C39

1 2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

+AVDD_PEX_PLL

C40

C40

1 2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

@

@

C41

C41

1 2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

@

@

C42

C42

1 2

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

12

R183

R183

0_0201_5%

0_0201_5%

@

@

A

1

12

2

12

1

C1219

C1219

2

3.3V

1

C37

C37

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

R58 1K_0201_1 %R58 1K_0201_1%

R59 1K_0201_1 %R59 1K_0201_1%

@

@

@

@

C1218

C1218

39P 50V J NPO 0402

39P 50V J NPO 0402

+AVDD_USB_PLL

3.3V

1

C33

C33

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

12

12

U1H

U1H

P8

AVDD_PEX_PLL

R8

AVDD_PEX_1

R9

AVDD_PEX_2

T9

AVDD_PEX_3

U8

VDD_PEX_1

U9

VDD_PEX_2

V9

VDD_PEX_3

V8

VDDIO_PEX_CLK

T20_23X23

T20_23X23

U1F

U1F

AA14

AVDD_USB_1

Y14

AVDD_USB_2

AB11

AVDD_USB_PLL

USB

USB

VDDIO_SDIOP1SDIO3_DATA0

SDIO

SDIO

AB8

VDDIO_HSIC

AB9

AVDD_IC_USB

HSIC

HSIC

AA3

DNC_0001

AB4

DNC_0002

AB6

DNC_0003

AC13

DNC_0004

AC3

DNC_0005

AE21

DNC_0006

AE22

DNC_0007

AE23

DNC_0008

AF23

DNC_0009

AF24

DNC_0010

AF26

DNC_0011

AF27

DNC_0012

T20_23X23

T20_23X23

PEX

PEX

PEX_L0_TXN

PEX_L0_TXP

PEX_L0_RXN

PEX_L0_RXP

PEX_L1_TXN

PEX_L1_TXP

PEX_L1_RXN

PEX_L1_RXP

PEX_L2_TXN

PEX_L2_TXP

PEX_L2_RXN

PEX_L2_RXP

PEX_L3_TXN

PEX_L3_TXP

PEX_L3_RXN

PEX_L3_RXP

PEX_CLK_OUT1_N

PEX_CLK_OUT1_P

PEX_CLK_OUT2_N

PEX_CLK_OUT2_P

PEX_TSTCLKN

PEX_TSTCLKP

PEX_REFCLKN

PEX_REFCLKP

PEX_TERMP

NC

NC

USB1_VBUS

USB1_DN

USB1_DP

USB1_ID

USB3_VBUS

USB3_DN

USB3_DP

USB3_ID

USB_REXT

SDIO3_DATA1

SDIO3_DATA2

SDIO3_DATA3

SDIO3_DATA4

SDIO3_DATA5

SDIO3_DATA6

SDIO3_DATA7

SDIO3_CLK

SDIO3_CMD

GPIO_PV4

GPIO_PV5

GPIO_PV6

HSIC_DATA

HSIC_STROBE

HSIC_REXT

IC_DN

IC_DP

IC_REXT

DNC_00013

DNC_00014

DNC_00015

DNC_00016

DNC_00017

DNC_00018

DNC_00019

DNC_00020

DNC_00021

DNC_00022

DNC_00023

AD1

AD2

AA5

AA4

AC2

AC1

AA7

AA6

AA1

AA2

V4

V3

Y3

Y2

V6

V5

AC4

AD4

Y4

Y5

V1

V2

U1

U2

W6

B

B

AD17

AC14

AD14

USB1_ID_R

AE14

AH14

AH15

AG15

AF15

AC16

R3

U3

U4

R4

T4

T6

R5

U7

R2

R1

P7

R7

R6

AC15

AD15

AE15

AF14

AG14

AE13

AF28

D22

G20

G21

M21

M7

R21

U5

V7

W4

Y6

PEX_TERMP

+USB1_VBUS

USB1_DN

USB1_DP

+USB3_VBUS

USB_REXT

PEX_WAKE#

PEX_RST0#

R223 0_0201_5%R223 0_0201_5%

R228 0_0201_5%R228 0_0201_5%

USB3_ID

R15 10K_0201_ 5%R15 10 K_0201_5%

1 2

TSC_INT

W_DISABLE#

+VDDIO_AUDIO

R60 2.49K_0402_1%R60 2.49K_0402_1%

1 2

12

USB3_DN (17)

USB3_DP (17)

1 2

R561K_0201_1% R561K_0201_1%

LS_EN# (4)

I2C_RST (4)

PEX_WAKE# (17)

PEX_RST0# (17)

ULPI_CLK

1

C1232

C1232

2

@

@

1 2

R982 10K_0201 _5%

R982 10K_0201 _5%

1 2

R983 10K_0201 _5%

R983 10K_0201 _5%

@

@

C

USB1_ID

12

+5VALW

L:HOST

H:Client

TSC_INT (11,14)

@

@

39P 50V J NPO 0402

39P 50V J NPO 0402

EC_REQUEST#(15)

+VDDIO_BB

USB1_DN (16)

USB1_DP (16)

USB1_ID (15,16)

R55

R55

1 2

100K_0201_5%

100K_0201_5%

WF_RST#

WF_PWDN#

micro SD

R230

R230

1 2

100K_0201_5%

100K_0201_5%

+VDDIO_AUDIO

+1.8VS_S3

L:HOST

H:Client

3.3V

+VDDIO_SDIO

W_DISABLE# (17)

EC_REQUEST#

12

R116

R116

0_0201_5%

0_0201_5%

WIFI

+3VS

R108 0_0201_5%R108 0_0201_5%

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

SDIO1_CLK(13)

SDIO1_CMD(13)

SDIO1_DAT0(13)

SDIO1_DAT1(13)

SDIO1_DAT2(13)

SDIO1_DAT3(13)

3G_EN#(15,17)

EN_VDDIO_SD(13)

WF_WAKE#(20)

WF_RST#(20)

WF_PWDN#(20)

HEAD_DET#(12,14)

ULPI_DAT0(16)

ULPI_DAT1(16)

ULPI_DAT2(16)

ULPI_DAT3(16)

ULPI_DAT4(16)

ULPI_DAT5(16)

ULPI_DAT6(16)

ULPI_DAT7(16)

ULPI_CLK(16)

ULPI_DIR(16)

ULPI_NXT(16)

ULPI_STP(16)

ULPI_RESET#(16)

+VDDIO_BB

TP133TP133

TP134TP134

TP135TP135

TP136TP136

TP54TP54

TP64TP64

TP55TP55

C35

C35

+VDDIO_BB

12

1

2

SDIO1_CLK

SDIO1_CMD

SDIO1_DAT0

SDIO1_DAT1

SDIO1_DAT2

SDIO1_DAT3

EN_VDDIO_SD

1 2

R981 10K_0201_5%R981 10K_0201_5%

C38

C38

1 2

WF_RST#

WF_PWDN#

SPI1_SCK

SPI1_CS0#

SPI1_MOSI

SPI1_MISO

3.3V

1

C36

C36

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

ULPI_CLK

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

VGA_DET#

HEAD_DET#

LOW_BAT#

EN_MIC_EXT#

USB ID defult low

Client HOST

ONMOS

U103

@

+USB_VOUT_F

+5VALW

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

@

R1020 0_0402_5%

R1020 0_0402_5%

R1021 0_0402_5%R1021 0_040 2_5%

C

12

12

+USB1_VBUS_IN

U103

5

IN

4

IN

G5243T11U_SOT23-5

G5243T11U_SOT23-5

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

OUT

GND

1

2

3

EN

D

M28

M27

M26

N25

M25

LOWHIGHID

OFF

VBUS_EN

2008/09/202006/08/18

2008/09/202006/08/18

2008/09/202006/08/18

D

U1G

U1G

BB UART

BB UART

M8

VDDIO_BB

P4

ULPI_DATA0

P6

ULPI_DATA1

N4

ULPI_DATA2

L3

ULPI_DATA3

L4

ULPI_DATA4

L6

ULPI_DATA5

P5

ULPI_DATA6

N6

ULPI_DATA7

M2

ULPI_CLK

M3

ULPI_DIR

M1

ULPI_NXT

P3

ULPI_STP

L2

DAP3_DIN

L1

DAP3_DOUT

J3

DAP3_FS

M4

DAP3_SCLK

M6

SDIO1_CLK

J5

SDIO1_CMD

K6

SDIO1_DATA0

K4

SDIO1_DATA1

M5

SDIO1_DATA2

L5

SDIO1_DATA3

P2

GPIO_PV0

J7

GPIO_PV1

U6

GPIO_PV2

J6

GPIO_PV3

P21

VDDIO_AUDIO

R25

SPDIF_IN

N23

SPDIF_OUT

SPI1_SCK

SPI1_CS0#

SPI1_MOSI

P26

SPI1_MISO

P24

SPI2_SCK

P23

SPI2_CS0#

P22

SPI2_CS1#

P28

SPI2_CS2#

SPI2_MOSI

SPI2_MISO

T20_23X23

T20_23X23

+USB1_VBUS

1 2

R44 10 K_0201_5%R44 10K_0201_5%

1 2

R122 0_0201_5%

R122 0_0201_5%

AUDIO

AUDIO

@

@

E

R54

R54

2.2K_0201_1%

2.2K_0201_1%

GEN1_I2C_SCL

GEN1_I2C_SDA

UART1_TXD

UART1_RXD

UART3_TXD

UART3_RXD

UART3_RTS#

UART3_CTS#

BT_IRQ#

DAP4_DIN

DAP4_DOUT

DAP4_FS

DAP4_SCLK

R935 0_0201_5%R935 0_0201_5%

R936 0_0201_5%R936 0_02 01_5%

DAP_MCLK1

DAP_MCLK2

R941 0_0201_5%R941 0_02 01_5%

DAP1_SCLK

DAP1_FS

DAP1_DOUT

DAP1_DIN

LA-6011P

LA-6011P

LA-6011P

1.8V

1

2

12

12

R57

R57

2.2K_0201_1%

2.2K_0201_1%

TP116TP116

TP117TP117

1 2

R940 10K_0201 _5%R940 10K_0201 _5%

TP118TP118

12

12

12

R937 0_0201_5%R937 0_0201_5%

TP111TP111

TP112TP112

TP113TP113

TP114TP114

E

C34

C34

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

GEN1_I2C_SCL (12,14,16)

GEN1_I2C_SDA (12,14,16)

UART1_TXD (12,14)

UART1_RXD (12,14)

UART3_TXD (20)

UART3_RXD (20)

UART3_RTS# (20)

UART3_CTS# (20)

DAP4_DIN (20)

DAP4_DOUT (20)

DAP4_FS (20)

12

DAP1_FS (12)

DAP1_DOUT (12)

DAP1_DIN (12)

6

6

6

+1.8VS_S3

R121 0_0201_5%R121 0_0201_5%

VDDIO_UART

GEN1_I2C_SCL

GEN1_I2C_SDA

UART2_TXD

UART2_RXD

UART2_RTS#

UART2_CTS#

UART3_TXD

UART3_RXD

UART3_RTS#

UART3_CTS#

GPIO_PU0

GPIO_PU1

GPIO_PU2

GPIO_PU3

GPIO_PU4

GPIO_PU5

GPIO_PU6

DAP4_DIN

DAP4_DUT

DAP4_FS

DAP4_SCLK

DAP_MCLK1

DAP_MCLK2

DAP1_SCLK

DAP1_FS

DAP1_DUT

DAP1_DIN

DAP2_SCLK

DAP2_FS

DAP2_DUT

DAP2_DIN

+3.3VS_LDO3

USB1_ID

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

+VDDIO_UART

12

H11

H6

H5

H7

F4

G6

F5

F3

F2

F1

E4

+VDDIO_UART

BT_RST#

J1

G4

E1

F6

E5

H4

J2

H1

J4

H3

H2

P27

R24

P25

R27

R28

R26

R23

R22

T23

T25

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

T20(3/4)USB/SDIO/UART/AUDIO

T20(3/4)USB/SDIO/UART/AUDIO

T20(3/4)USB/SDIO/UART/AUDIO

Friday, May 07, 2010

Friday, May 07, 2010

Friday, May 07, 2010

debug

BT_RST# (20)

DAP4_SCLK_R (20)

DAP_MCLK1_R (12)

DAP_MCLK2_R (16)

DAP1_SCLK_R (12)

34

34

34

0.2

0.2

0.2

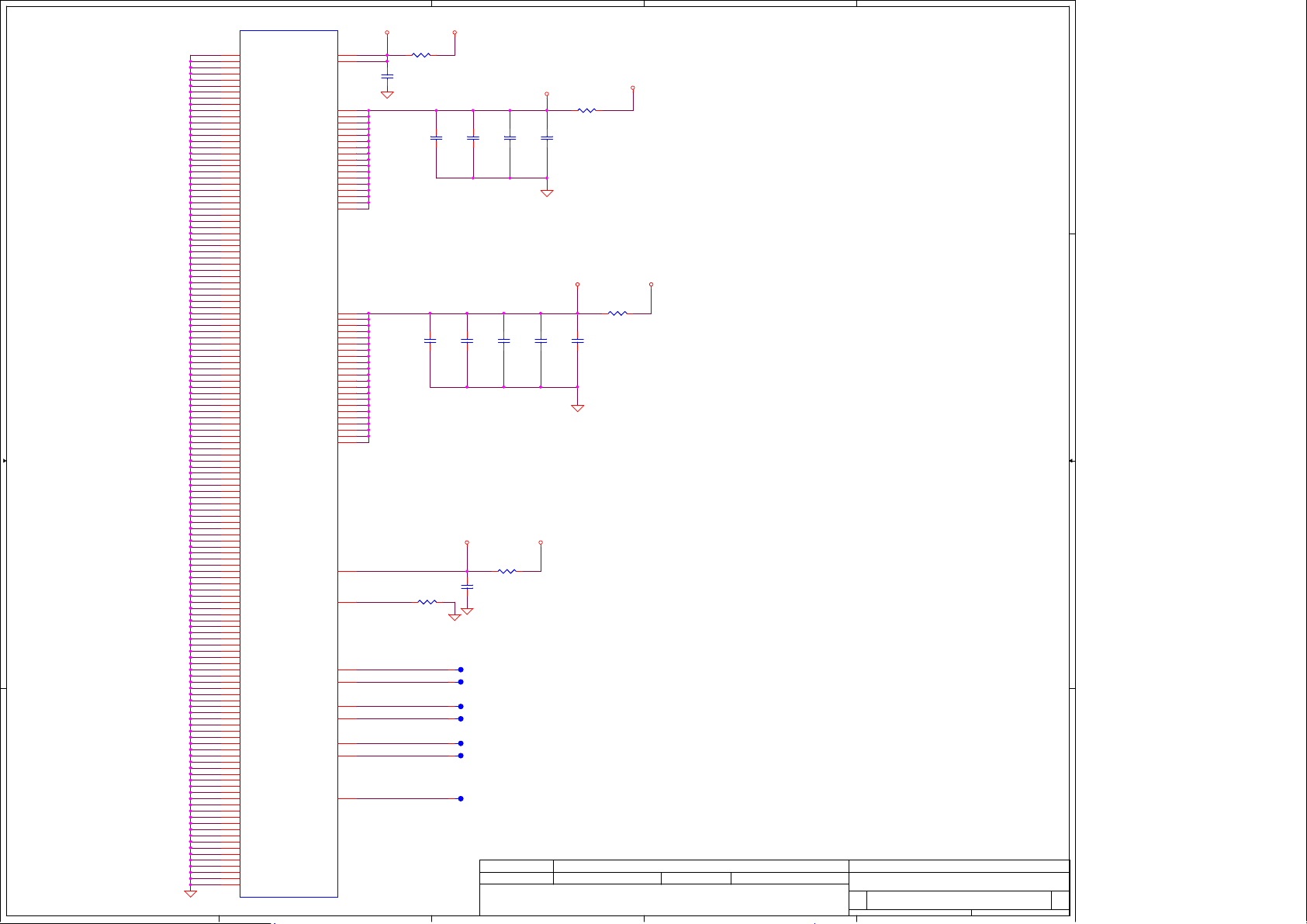

Page 7

A

U1A

U1A

CORE

GND_001

GND_002

GND_003

GND_004

GND_005

GND_006

GND_007

GND_008

GND_009

GND_010

GND_011

GND_012

GND_013

GND_014

GND_015

GND_016

GND_017

GND_018

GND_019

GND_020

GND_021

GND_022

GND_023

GND_024

GND_025

GND_026

GND_027

GND_028

GND_029

GND_030

GND_031

GND_032

GND_033

GND_034

GND_035

GND_036

GND_037

GND_038

GND_039

GND_040

GND_041

GND_042

GND_043

GND_044

GND_045

GND_046

GND_047

GND_048

GND_049

GND_050

GND_051

GND_052

GND_053

GND_054

GND_055

GND_056

GND_057

GND_058

GND_059

GND_060

GND_061

GND_062

GND_063

GND_064

GND_065

GND_066

GND_067

GND_068

GND_069

GND_070

GND_071

GND_072

GND_073

GND_074

GND_075

GND_076

GND_077

GND_078

GND_079

GND_080

GND_081

GND_082

GND_083

GND_084

GND_085

GND_086

GND_087

GND_088

GND_089

GND_090

GND_091

GND_092

GND_093

GND_094

GND_095

GND_096

GND_097

GND_098

GND_099

GND_100

GND_101

GND_102

GND_103

GND_104

GND_105

GND_106

GND_107

GND_108

GND_109

GND_110

GND_111

GND_112

GND_113

GND_114

GND_115

GND_116

GND_117

GND_118

GND_119

GND_120

GND_121

GND_122

GND_123

GND_124

GND_125

GND_126

GND_127

GND_128

GND_129

GND_130

GND_131

GND_132

GND_133

GND_134

GND_135

GND_136

T20_23X23

T20_23X23

CORE

A1

A2

A27

A28

AA10

AA13

AA16

AA19

AA21

AA8

AA9

1 1

2 2

3 3

4 4

A

AB24

AB27

AC19

AD10

AD13

AD16

AD19

AD22

AE25

AE27

AG10

AG13

AG16

AG19

AG22

AG25

AG27

AG28

AH27

AH28

W21

W24

W27

AB2

AB5

AD7

AE2

AE4

AG1

AG2

AG4

AG7

AH1

AH2

B1

B10

B13

B16

B19

B2

B22

B25

B27

B28

B4

B7

D2

D25

D27

D4

E10

E13

E16

E19

E22

E7

G2

G24

G27

G5

H10

H13

H16

H18

H19

H21

H8

K2

K21

K24

K27

K5

K8

L11

L12

L13

L14

L15

L18

L8

M12

N13

N14

N16

N17

N2

N21

N24

N27

N5

N8

P17

P18

R11

R14

R15

R17

R18

T11

T12

T14

T17

T18

T2

T21

T24

T27

T5

T8

U11

U12

U15

U18

U21

V11

V14

V15

V16

V21

W2

W5

W8

Y11

Y12

Y13

VDD_RTC_00 1

VDD_RTC_00 2

VDD_CPU_01

VDD_CPU_02

VDD_CPU_03

VDD_CPU_04

VDD_CPU_05

VDD_CPU_06

VDD_CPU_07

VDD_CPU_08

VDD_CPU_09

VDD_CPU_10

VDD_CPU_11

VDD_CPU_12

VDD_CPU_13

VDD_CPU_14

VDD_CPU_15

VDD_CPU_16

VDD_CPU_17

VDD_CORE_01

VDD_CORE_02

VDD_CORE_03

VDD_CORE_04

VDD_CORE_05

VDD_CORE_06

VDD_CORE_07

VDD_CORE_08

VDD_CORE_09

VDD_CORE_10

VDD_CORE_11

VDD_CORE_12

VDD_CORE_13

VDD_CORE_14

VDD_CORE_15

VDD_CORE_16

VDD_CORE_17

VDD_CORE_18

VDD_CORE_19

VDD_CORE_20

VDD_CORE_21

VDD_CORE_22

VPP_FUSE

VPP_KFUSE

VDD_CORE_SEN SE

GND_CORE_SE NSE

VDD_CPU_SENS E

GND_CPU_SEN SE

VDD_TP

GND_TP

VGND_TP

B

1.0~1.2V

+VDD_RTC

V12

R130 0_0201_5%R130 0_0201_5%

V13

1

2

H9

J10

J11

J8

J9

K9

L9

M11

M9

N11

N12

P11

P12

P13

P14

R12

R13

AA20

M13

M14

M15

M16

N15

P15

P16

R16

T13

T15

T16

U13

U14

U16

U17

V17

V18

W20

Y19

Y20

Y21

AB15

VDD_KFUSE

AB14

VDD_CORE_SENSE

Y18

GND_CORE_SENSE

Y17

VDD_CPU_SENSE

N9

GND_CPU_SENSE

P9

VDD_TP

W9

GND_TP

Y10

VGND_TP

AA11

B

C43

C43

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

C44

C44

1

C48

C48

2

R61

R61

1 2

10K_0201_5%

10K_0201_5%

+1.2VS_LDO2

12

1

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

C49

C49

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

C45

C45

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1

C50

C50

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

+VDD_FUSE

1

C53

C53

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

TP29TP29

TP30TP30

TP31TP31

TP32TP32

TP33TP33

TP34TP34

TP35TP35

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

C46

C46

2

1

2

3.3V

Issued Date

Issued Date

Issued Date

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

1.0~1.2V

C51

C51

0.1U_0402_10V7K

0.1U_0402_10V7K

12

C

0.9~1.0V

+VDD_CPU

1

2

+3VS

R1240_0201_5% R1240_0201_5%

C

1 2

R126 0_0805_5%R126 0_0805_5%

1

C47

C47

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

+VDD_CORE

0.1U_0402_10V7K

0.1U_0402_10V7K

R125 0_0805_5%R125 0_0805_5%

1

C52

C52

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

2

+1.0VS_SM1

1 2

+1.2VS_SM0

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

D

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

2008/09/202006/08/18

2008/09/202006/08/18

2008/09/202006/08/18

D

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

T20(4/4)PWR_GND_NC

T20(4/4)PWR_GND_NC

T20(4/4)PWR_GND_NC

Friday, May 07, 2010

Friday, May 07, 2010

Friday, May 07, 2010

E

LA-6011P

LA-6011P

LA-6011P

E

0.2

0.2

7

7

7

0.2

34

34

34

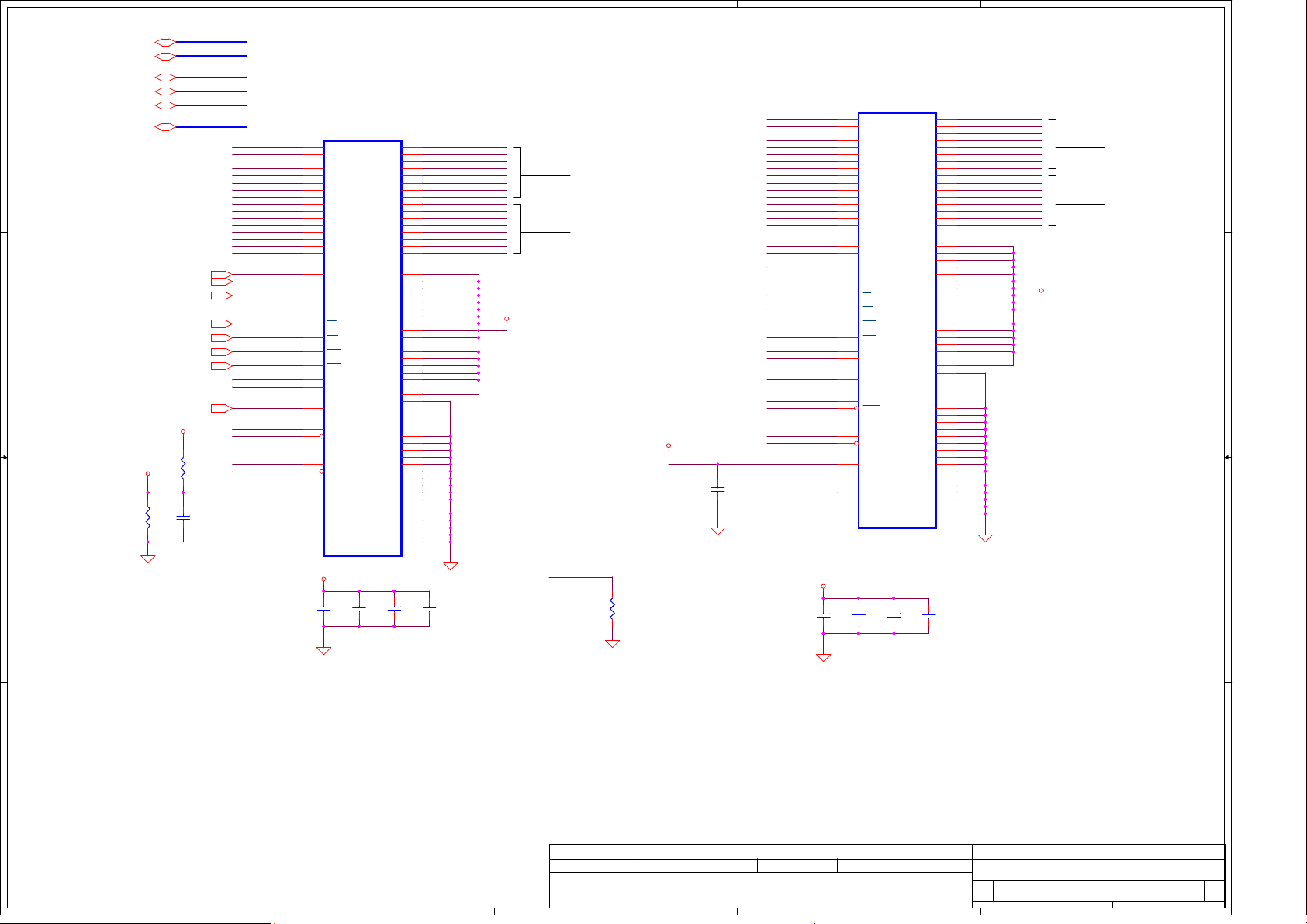

Page 8

5

DDR_A_BS#[0..2](5,9)

DDR_A_D[0..31](5,9)

DDR_A_DQS[0..3](5,9)

DDR_A_DQS#[0..3](5,9)

DDR_A_MA[0..13](5,9)

D D

C C

B B

DDR_A_DM[0..3](5,9)

1K_0201_1%

1K_0201_1%

+VRAM_VREFA

R457

R457

1 2

M_CLK_DDR#0(5,9)

M_CLK_DDR0(5,9)

M_CKE0(5)

M_CS#0(5)

DDR_A_WE#(5,9)

DDR_A_RAS#(5,9)

DDR_A_CAS#(5,9)

M_ODT(5,9)

+1.8V

R456

R456

1K_0201_1%

1K_0201_1%

1 2

2

C455

C455

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

Close to U7

DDR_A_BS#0

DDR_A_BS#1

DDR_A_MA12

DDR_A_MA11

DDR_A_MA10

DDR_A_MA9

DDR_A_MA8

DDR_A_MA7

DDR_A_MA6

DDR_A_MA5

DDR_A_MA4

DDR_A_MA3

DDR_A_MA2

DDR_A_MA1

DDR_A_MA0

M_CLK_DDR#0

M_CLK_DDR0

M_CKE0

M_CS#0

DDR_A_WE#

DDR_A_RAS#

DDR_A_CAS#

DDR_A_DM0

DDR_A_DM1

M_ODT

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

(SSTL-1.8) VREF = .5* VDDQ

DDR_A_BS#2

DDR_A_MA13

0.01U_0201_16V7

0.01U_0201_16V7

SA00002NW00

U28

U28

L2

L3

R2

P7

M2

P3

P8

P2

N7

N3

N8

N2

M7

M3

M8

K8

J8

K2

L8

K3

K7

L7

F3

B3

K9

F7

E8

B7

A8

J2

A2

E2

L1

R3

R7

R8

K4T51163QE-ZCE6_FBGA84

K4T51163QE-ZCE6_FBGA84

+1.8V

1

C456

C456

2

BA0

BA1

A12

A11

A10/AP

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CK

CK

CKE

CS

WE

RAS

CAS

LDM

UDM

ODT

LDQS

LDQS

UDQS

UDQS

VREF

NC#A2

NC#E2

NC#L1

NC#R3

NC#R7

NC#R8

2

C457

C457

1

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

4

B9

DQ15

B1

DQ14

D9

DQ13

D1

DQ12

D3

DQ11

D7

DQ10

C2

DQ9

C8

DQ8

F9

DQ7

F1

DQ6

H9

DQ5

H1

DQ4

H3

DQ3

H7

DQ2

G2

DQ1

G8

DQ0

A9

VDDQ1

C1

VDDQ2

C3

VDDQ3

C7

VDDQ4

C9

VDDQ5

E9

VDDQ6

G1

VDDQ7

G3

VDDQ8

G7

VDDQ9

G9

VDDQ10

A1

VDD1

E1

VDD2

J9

VDD3

M9

VDD4

R1

VDD5

J1

VDDL

J7

VSSDL

A7

VSSQ1

B2

VSSQ2

B8

VSSQ3

D2

VSSQ4

D8

VSSQ5

E7

VSSQ6

F2

VSSQ7

F8

VSSQ8

H2

VSSQ9

H8

VSSQ10

A3

VSS1

E3

VSS2

J3

VSS3

N1

VSS4

P9

VSS5

1

C458

C458

2

1U_0402_6.3V4Z

1U_0402_6.3V4Z

swap already

DDR_A_D13

DDR_A_D14

DDR_A_D8

DDR_A_D12

DDR_A_D11

DDR_A_D10

DDR_A_D15

DDR_A_D9

DDR_A_D7

DDR_A_D2

DDR_A_D5

DDR_A_D4

DDR_A_D3

DDR_A_D0

DDR_A_D1

DDR_A_D6

2

C463

C463

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

+1.8V

Group1

Group0

M_ODT

3

R458

R458

10K_0201_5%

10K_0201_5%

1 2

+VRAM_VREFA

(SSTL-1.8) VREF = .5* VDDQ

2

C454

C454

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

Close to U7

DDR_A_BS#0

DDR_A_BS#1

DDR_A_MA12

DDR_A_MA11

DDR_A_MA10

DDR_A_MA9

DDR_A_MA8

DDR_A_MA7

DDR_A_MA6

DDR_A_MA5

DDR_A_MA4

DDR_A_MA3

DDR_A_MA2

DDR_A_MA1

DDR_A_MA0

M_CLK_DDR#0

M_CLK_DDR0

M_CKE0

M_CS#0

DDR_A_WE#

DDR_A_RAS#

DDR_A_CAS#

DDR_A_DM2

DDR_A_DM3

M_ODT

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_BS#2

DDR_A_MA13

C459

C459

0.01U_0201_16V7

0.01U_0201_16V7

+1.8V

1

2

2

SA00002NW00

U29

U29

L2

BA0

L3

BA1

R2

A12

P7

A11

M2

A10/AP

P3

A9

P8

A8

P2

A7

N7

A6

N3

A5

N8

A4

N2

A3

M7

A2

M3

A1

M8

A0

K8

CK

J8

CK

K2

CKE

L8

CS

K3

WE

K7

RAS

L7

CAS

F3

LDM

B3

UDM

K9

ODT

F7

LDQS

E8

LDQS

B7

UDQS

A8

UDQS

J2

VREF

A2

NC#A2

E2

NC#E2

L1

NC#L1

R3

NC#R3

R7

NC#R7

R8

NC#R8

K4T51163QE-ZCE6_FBGA84

K4T51163QE-ZCE6_FBGA84

1

2

C461

C461

2

1

1U_0402_6.3V4Z

1U_0402_6.3V4Z

C460

C460

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDD1

VDD2

VDD3

VDD4

VDD5

VDDL

VSSDL

VSSQ1

VSSQ2

VSSQ3

VSSQ4

VSSQ5

VSSQ6

VSSQ7

VSSQ8

VSSQ9

VSSQ10

VSS1

VSS2

VSS3

VSS4

VSS5

swap D25,D27,D30,D31

DDR_A_D25

B9

DDR_A_D31

B1

DDR_A_D26

D9

DDR_A_D29

D1

DDR_A_D27

D3

DDR_A_D30

D7

DDR_A_D24

C2

DDR_A_D28

C8

DDR_A_D22

F9

DDR_A_D16

F1

DDR_A_D19

H9

DDR_A_D20

H1

DDR_A_D21

H3

DDR_A_D18

H7

DDR_A_D23

G2

DDR_A_D17

G8

A9

C1

C3

C7

C9

E9

G1

G3

G7

G9

A1

E1

J9

M9

R1

J1

J7

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

A3

E3

J3

N1

P9

2

C462

C462

0.1U_0201_6.3V6K

0.1U_0201_6.3V6K

1

1

Group3

Group2

+1.8V

A A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

2008/09/202006/08/18

2008/09/202006/08/18

2008/09/202006/08/18

2

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Compal Electronics, Inc.

DDRII-DEVICE DOWN(1/2)

DDRII-DEVICE DOWN(1/2)

DDRII-DEVICE DOWN(1/2)

LA-6011P

LA-6011P