Page 1

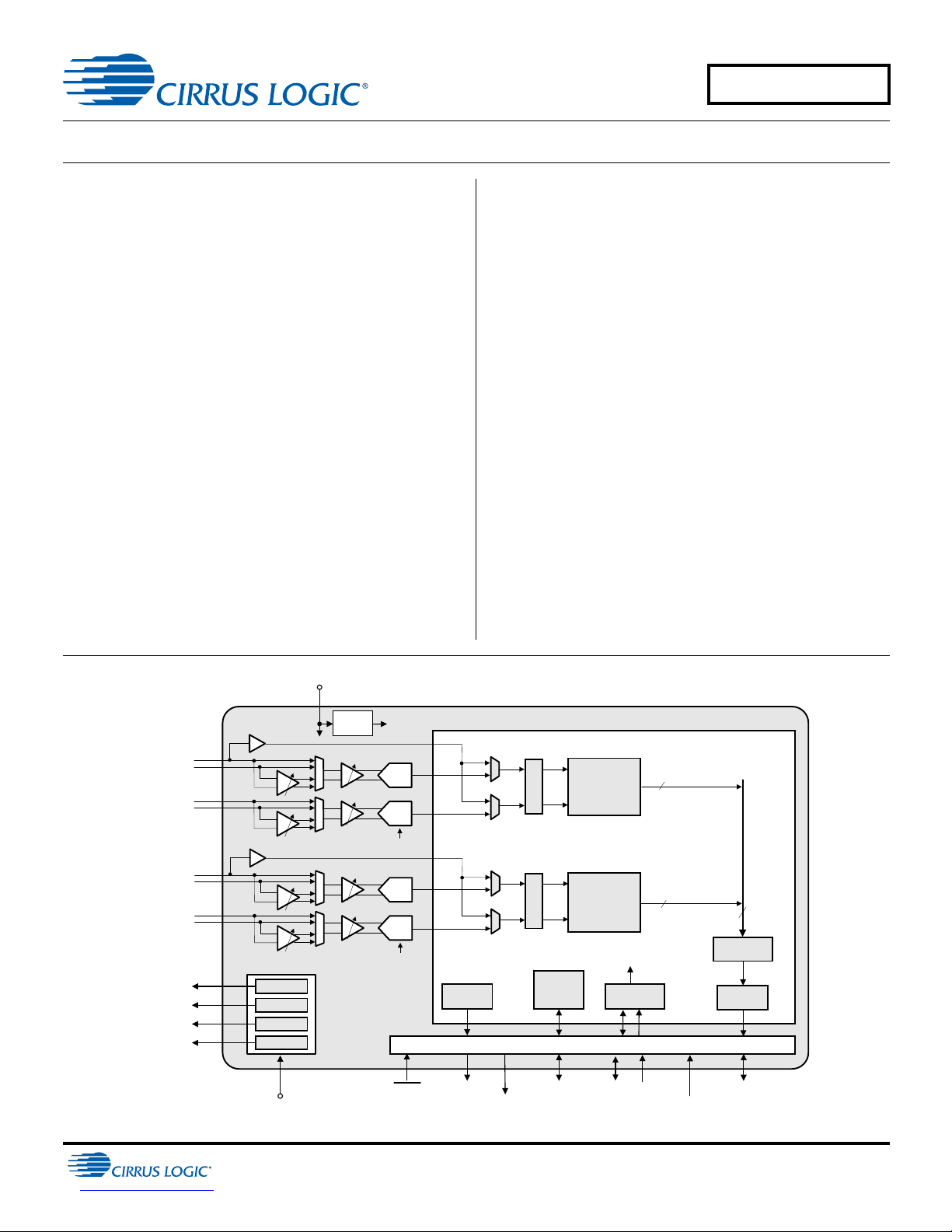

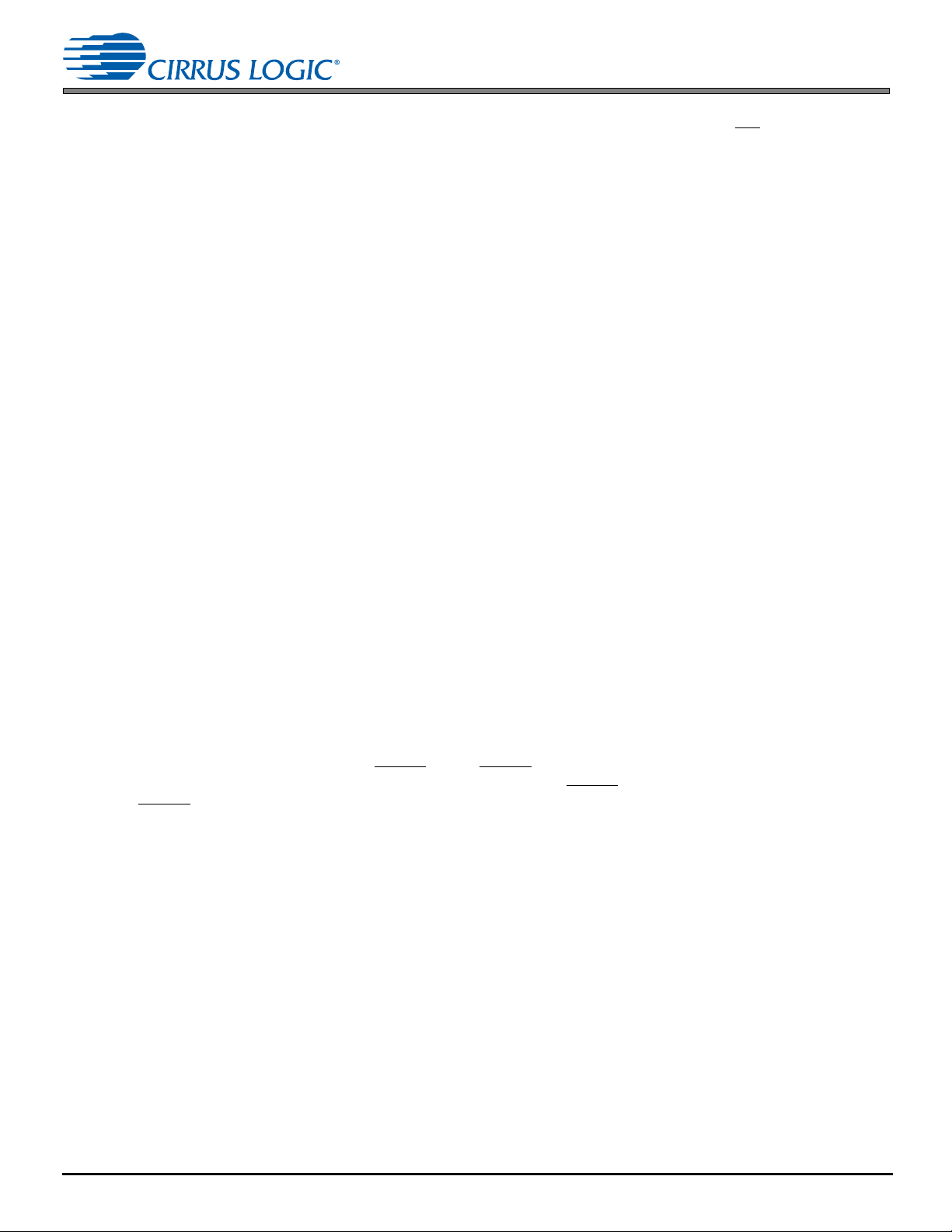

CS53L30

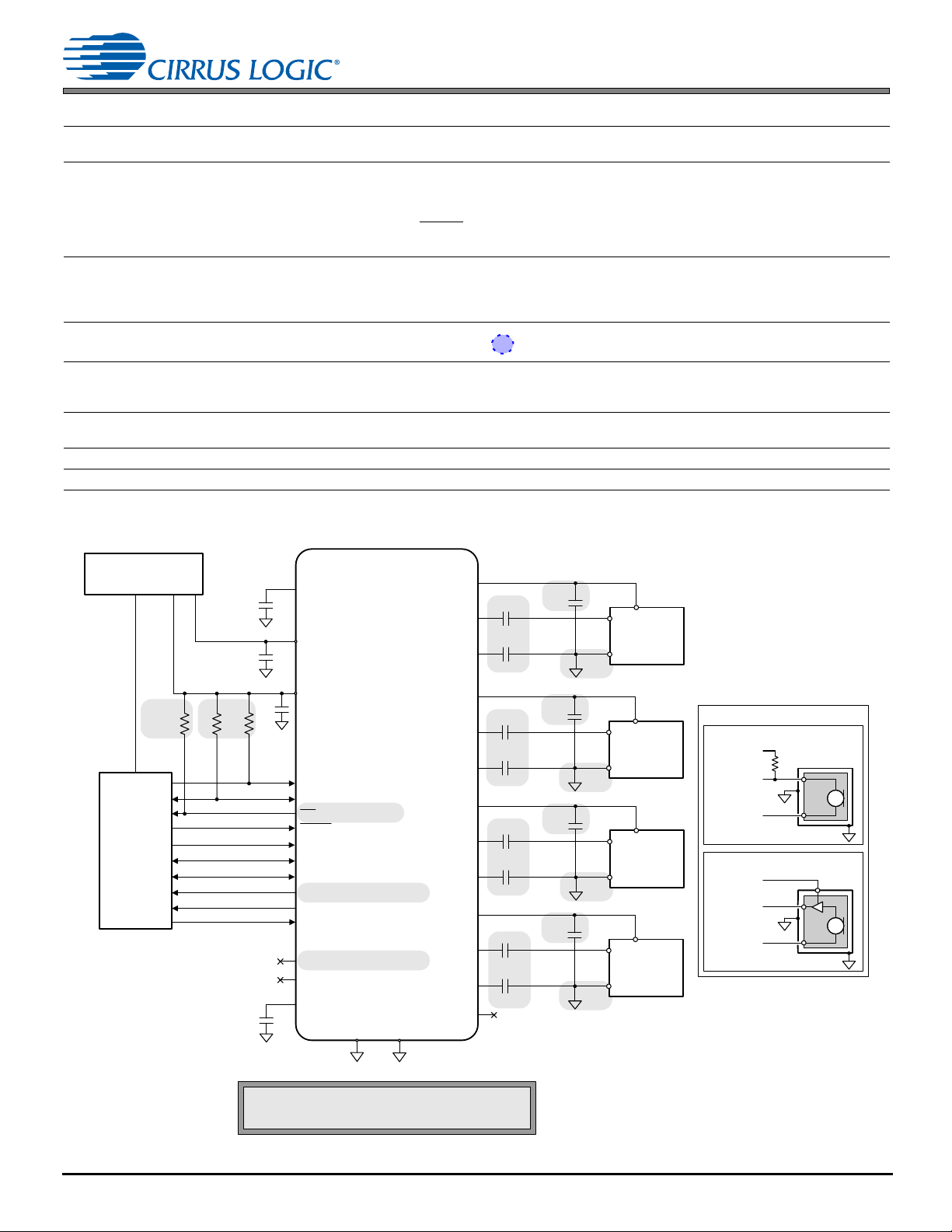

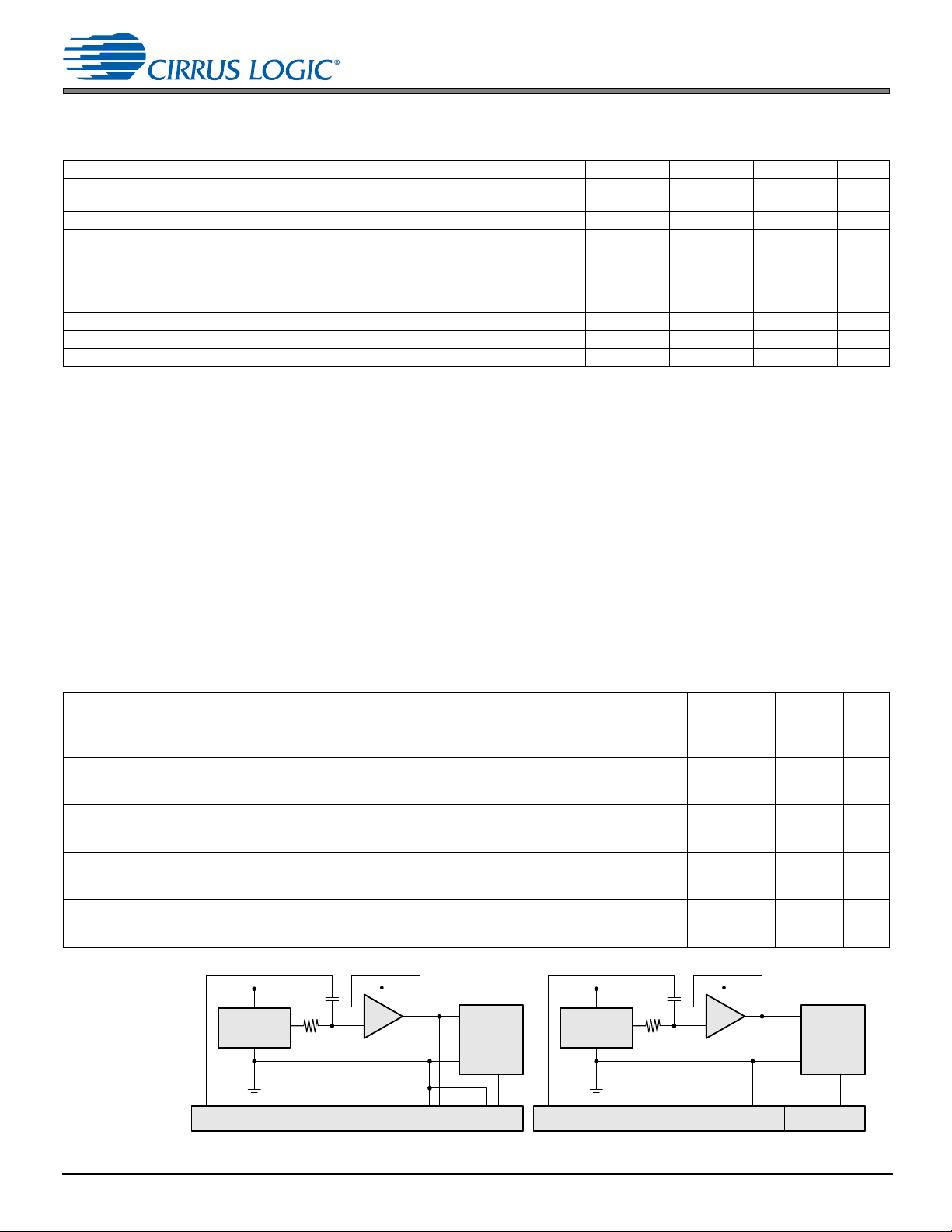

Digital Processing

Control

Port

Level Shifters

MIC1_BIAS

Serial Port

MIC2_BIAS

VP

MCLK

DMIC1_SCLK

MIC3_BIAS

MIC4_BIAS

–6 to +12 dB,

0.5 dB steps

+10 or +20 dB

ADC1B

–

+

–

+

Decimators

MIC1 B i a s

MIC2 B i a s

MIC3 B i a s

MIC4 B i a s

HPF , No i se

Gate, Volume,

Mute

Audio

Serial Port

Control Port

RESET

MCLK_INT

Clock Divider

Synchronizer

DMIC

ADC1A

–

+

LDO

VA

VD

2

2

4

MCLK_INT

HPF , No i se

Gate, Volume,

Mute

SYNC

MUTE

Synchronous

SRC

IN1+ /DMIC1_SD

IN2–

IN1–

IN2+

DMIC2_SCLK

–

+

–6 to +12 dB,

0.5 dB steps

+10 or +20 dB

ADC2B

–

+

–

+

Decimators

ADC2A

–

+

MCLK_INT

IN3+/DMIC2_SD

IN4–

IN3–

IN4+

–

+

CS53L30

Low-Power Quad-Channel Microphone ADC with TDM Output

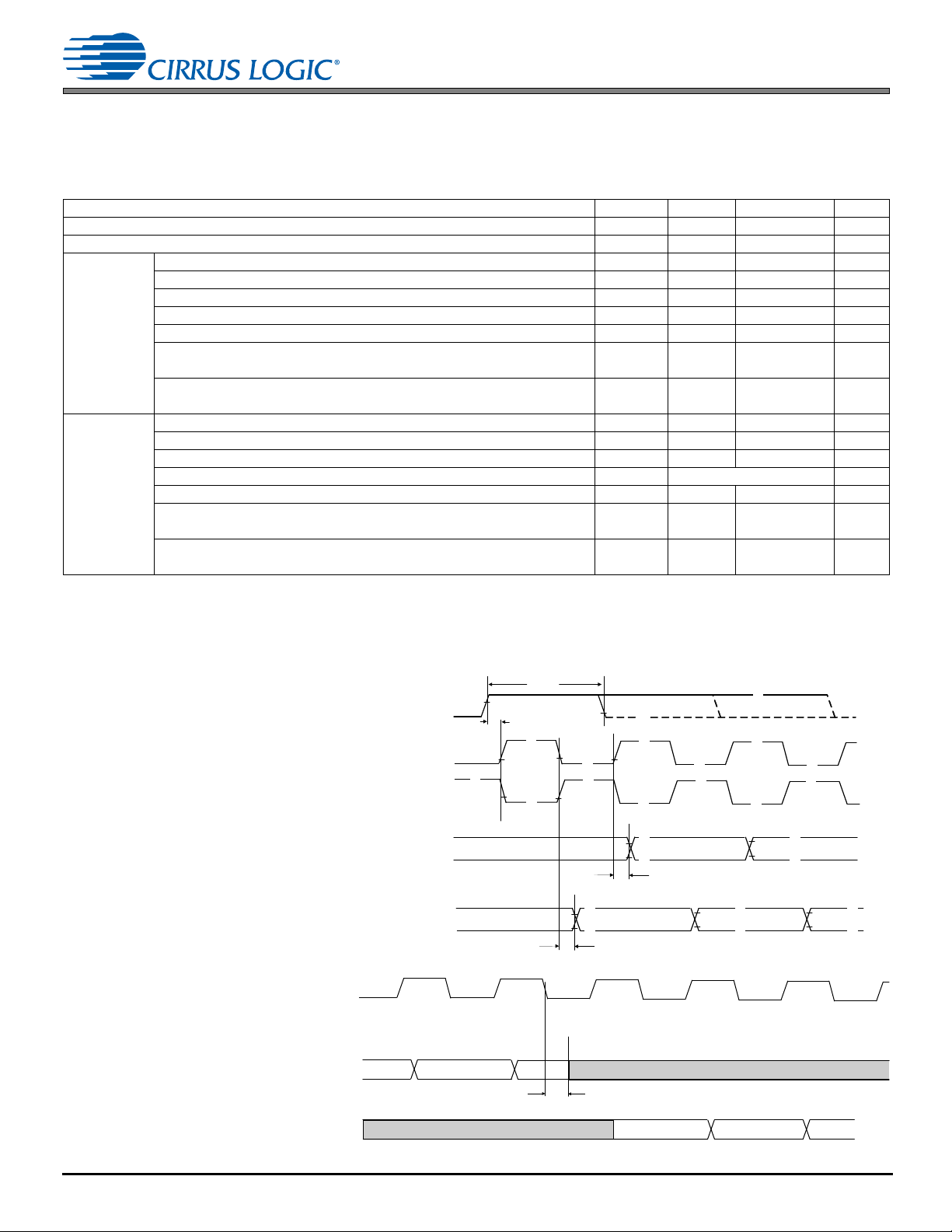

Analog Input and ADC Features

91-dB dynamic range (A-weighted) @ 0-dB gain

–84-dB THD+N @ 0-dB gain

Four fully differential inputs: Four an alog mic/line inputs

Four analog programmable gain amp lifie rs

–6 to +12 dB, in 0.5-dB steps

+10 or +20 dB boost for mic input

Four mic bias generators

MUTE pin for quick mic mute and programmable quick

power down

Digital Processing Features

Volume contro l, mute, programmable high-pass filter,

noise gate

Two digital mic (DMIC) interfaces

Digital Output Features

Two DMIC SCLK generators

2

Four-channel I

can be used to output 16 channels of 24-bit 16-kHz

sample rate data on a single TDM line.

S output or TDM output. Four CS53L30s

System Features

Native (no PLL required) support for 6-/12-MHz, 6.144-/

12.288-MHz, 5.6448-/1 1.2896-MHz, or 19.2-MHz ma ster

clock rates and 8- to 48-kHz audio sample rates

Master or Slave Mode. Clock dividers can be used to

generate common audio clocks from single-master clock

input.

Low power consumption

Less than 4.5-mW stereo (16 kHz) analog mic record

Less than 2.5-mW mono (8 kHz) analog mic record

Selectable mic bias and digital interface logic voltages

High-speed (400-kHz) I²C™ control port

Available in 30-ball WLCSP and 32-pin QFN

Applications

Voice-recognition systems

Advanced headsets and telephony systems

Voice recorders

Digital cameras and video cameras

http://www.cirrus.com

Copyright Cirrus Logic, Inc. 2013

(All Rights Reserved)

DS992F1

MAY '13

Page 2

CS53L30

General Description

The CS53L30 is a high-performance, low-power, quad-channel ADC. It is designed for use in multiple-mic applications

while consuming minimal board space and po we r.

The flexible ADC inputs can accommodate four channels of analog mic or line-input data in differential, pseudodifferential,

or single-ended mode, or four channels of digital mic data. The analog input path includes a +10- to +20-dB boost and a

–6- to +12-dB PGA. Digital mic data bypasses the analog gain circuits and is fed directly to the decimators.

Four mic bias generators are integrated into the device. The device also includes two digital mic serial clock outputs.

The CS53L30 includes several digital signal processing features such as high-pass filters, noise gate, and volume control.

The device can output its four channels of audio data over two I

CS53L30s can be used to output up to 16 channels of data over a single TDM line. This is done by settin g the appropriate

frame slots for each device, and each device then alternates between outputting data and setting the output pin to high

impedance.

The CS53L30 can operate as a serial port clock master or slave. In Master Mode, clock dividers are used to generate the

internal master clock and audio clocks from either the 6-/12-MHz, 6.144-/12.288-MHz, 5.6448-/11.2896-MHz, or 19.2-MHz

master clock.

The device is powered from VA, a 1.8-V nominal supply and VP, a typical battery supply. An internal LDO on the VA supply

powers the device’s digital core. The VP supply powers the mic bias generators and the AFE.

The CS53L30 is controlled by an I

pitch WLCSP package and 32-pin 5 x 5-mm QFN package.

2

C control port. A reset pin is also included. The device is available in a 30-ball 0.4-mm

2

S ports or a single TDM port. Additionally, up to four

2 DS992F1

Page 3

Table of Contents

1.1 WLCSP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

1.2 QFN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.3 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Table 3-1. Recommended Operating Conditions . . . . . . . . . . . . . . . . . . 9

Table 3-2. Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 3-3. Combined ADC On-Chip Analog, Digital Filter, SRC, and DMIC

Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 3-4. ADC High-Pass Filter (HPF) Characteristics . . . . . . . . . . . . . 9

Table 3-5. Analog-Input-to-Serial-Port Characteristics . . . . . . . . . . . . . 10

Table 3-6. MIC BIAS Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 3-7. Power-Supply Rejection Ratio (PSRR) Characteristics . . . . 11

Table 3-8. Power Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 3-9. Switching Specifications—Digital Mic Interface . . . . . . . . . . 14

Table 3-10. Specifications—I

2

S . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 3-11. Switching Specifications—Time-Division Multiplexed (TDM)

Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 3-12. Switching Specifications—I

2

C Control Port . . . . . . . . . . . . 16

Table 3-13. Digital Interface Specifications and Characteristics . . . . . . 17

Table 3-14. Thermal Overload Detection Characteristics . . . . . . . . . . . 17

4.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4.2 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.3 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4.4 Capture-Path Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.5 Digital Microphone (DMIC) Interface . . . . . . . . . . . . . . . . . . 23

4.6 Serial Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4.7 TDM Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

4.8 Synchronous Sample-Rate Converter (SRC) . . . . . . . . . . . .33

4.9 Multichip Synchronization Protocol . . . . . . . . . . . . . . . . . . . 34

4.10 Input Path Source Selection and Poweri ng . . . . . . . . . . . .34

4.11 Thermal Overload Notification . . . . . . . . . . . . . . . . . . . . . . 34

4.12 MUTE Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.13 Power-Up and Power-Down Control . . . . . . . . . . . . . . . . . 35

4.14 I

2

C Control Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.15 QFN Thermal Pad . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

5.1 Octal Microphone Array to the Audio Serial Port . . . . . . . . . 38

5.2 Power-Up Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

5.3 Power-Down Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

5.4 Capture-Path Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

5.5 MCLK Jitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

5.6 Frequency Response Considerations . . . . . . . . . . . . . . . . . 44

5.7 Connecting Unused Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

7 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

7.1 Device ID A and B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

7.2 Device ID C and D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

7.3 Device ID E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

7.4 Revision ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

7.5 Power Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

7.6 MCLK Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

7.7 Internal Sample Rate Control . . . . . . . . . . . . . . . . . . . . . . . . 48

7.8 Mic Bias Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

7.9 ASP Configuration Control . . . . . . . . . . . . . . . . . . . . . . . . . . 49

7.10 ASP Control 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

7.11 ASP TDM TX Control 1–4 . . . . . . . . . . . . . . . . . . . . . . . . .50

7.12 ASP TDM TX Enable 1–6 . . . . . . . . . . . . . . . . . . . . . . . . . . 50

7.13 ASP Control 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

7.14 Soft Ramp Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

7.15 LRCK Control 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

7.16 LRCK Control 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

7.17 MUTE

Pin Control 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

7.18 MUTE Pin Control 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

7.19 Input Bias Control 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

7.20 Input Bias Control 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

7.21 DMIC1 Stereo Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

7.22 DMIC2 Stereo Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

7.23 ADC1/DMIC1 Control 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

7.24 ADC1/DMIC1 Control 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

7.25 ADC1 Control 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

7.26 ADC1 Noise Gate Control . . . . . . . . . . . . . . . . . . . . . . . . . 54

7.27 ADC1A/1B AFE Control . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

7.28 ADC1A/1B Digital Volume . . . . . . . . . . . . . . . . . . . . . . . . . 54

7.29 ADC2/DMIC2 Control 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

7.30 ADC2/DMIC2 Control 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

7.31 ADC2 Control 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

7.32 ADC2 Noise Gate Control . . . . . . . . . . . . . . . . . . . . . . . . . 56

7.33 ADC2A/2B AFE Control . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

7.34 ADC2A/2B Digital Volume . . . . . . . . . . . . . . . . . . . . . . . . . 56

7.35 Device Interrupt Mask . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

7.36 Device Interrupt Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

8 Parameter Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

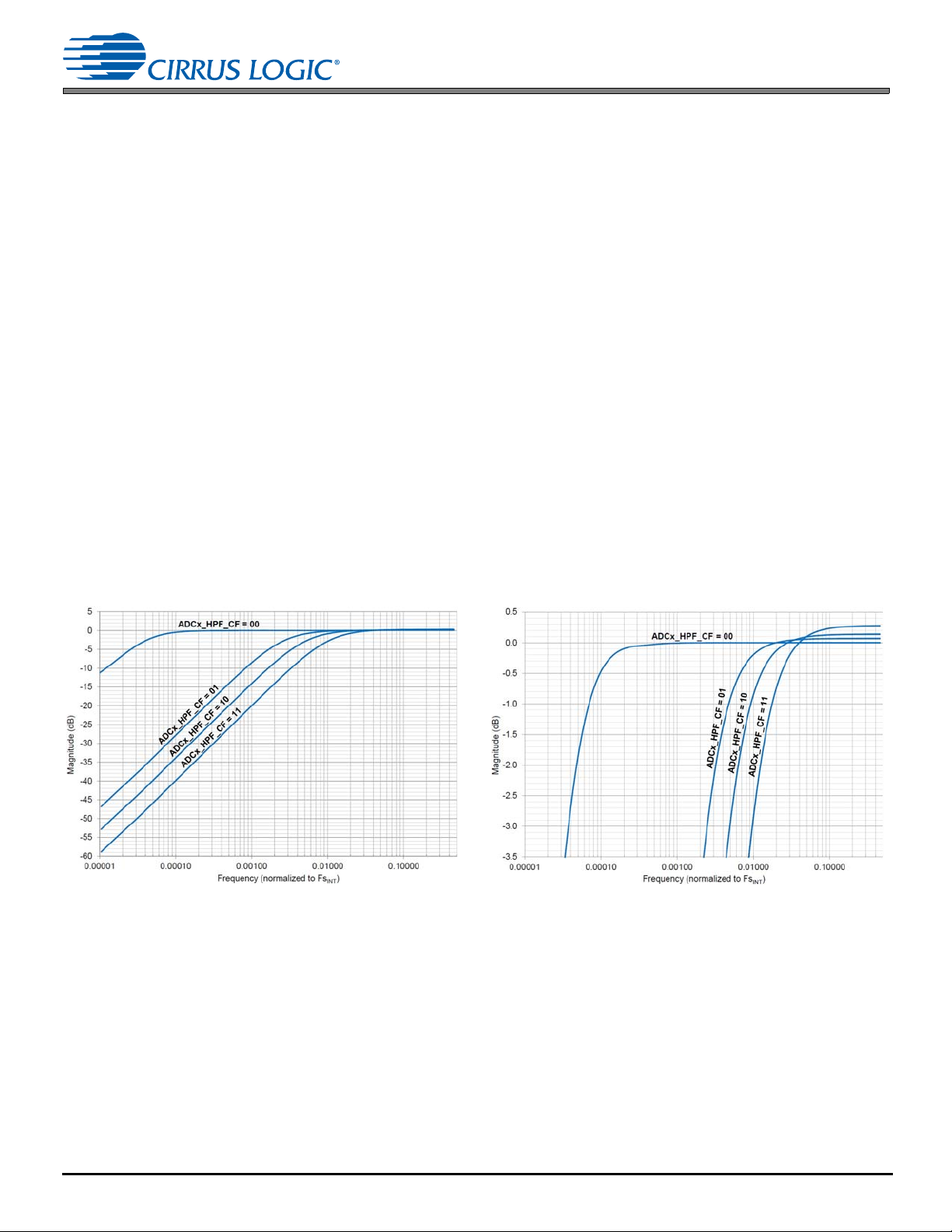

9 Plots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

9.1 Digital Filter Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

9.2 PGA Gain Linearity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

9.3 Dynamic Range Versus Sampling Frequency . . . . . . . . . . .63

9.4 FFTs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

10 Package Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

10.1 WLCSP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

10.2 QFN Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

11 Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

12 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

13 Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

CS53L30

DS992F1 3

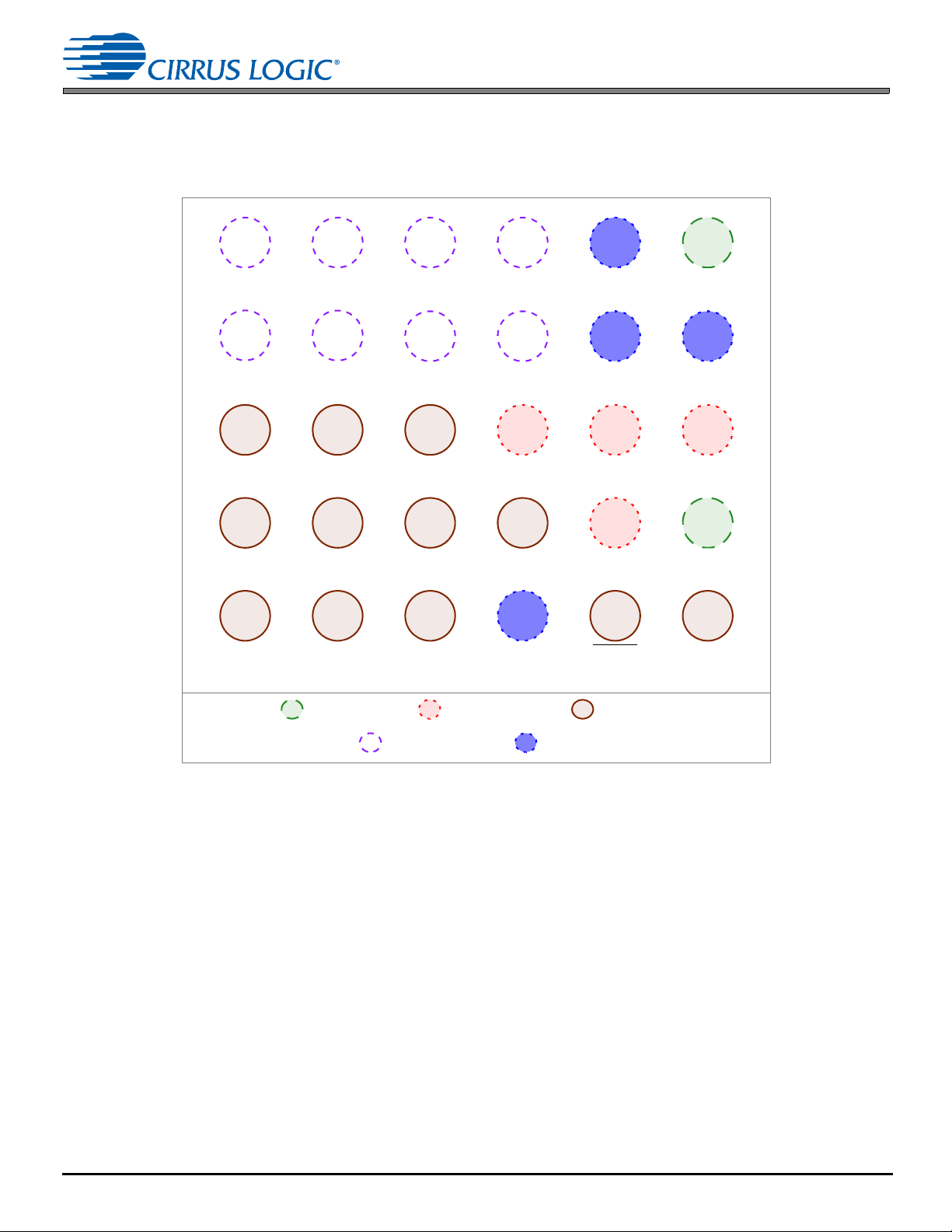

Page 4

1 Pin Descriptions

A1A2A3A4A5A6B1

B2

B3B4B5B6C1C2C3C4C5

C6

D1D2D3D4D5

D6

E1E2E3E4E5

E6

Filter pins Analog outputs Digital I/O

PowerCapture-path pins

1.1 WLCSP

CS53L30

1 Pin Descriptions

IN1+/DMIC1_

SD

IN1– IN2– IN3– IN4– GNDA VP

DMIC2_SCLK/

AD1

ASP_SDOUT1 ASP_SCLK SCL SYNC MIC4_BIAS MIC_BIAS_

MCLK SDA ASP_SDOUT2/

IN2+ IN3+/DMIC2_

SD

DMIC1_SCLK ASP_LRCK/

FSYNC

AD0

IN4+ VA FILT+

MIC1_BIAS MIC2_BIAS MIC3_BIAS

FILT

GNDD RESET

MUTE

Figure 1-1. Top-Down (Through-Package) View—30-Ball WLCSP Package

4 DS992F1

Page 5

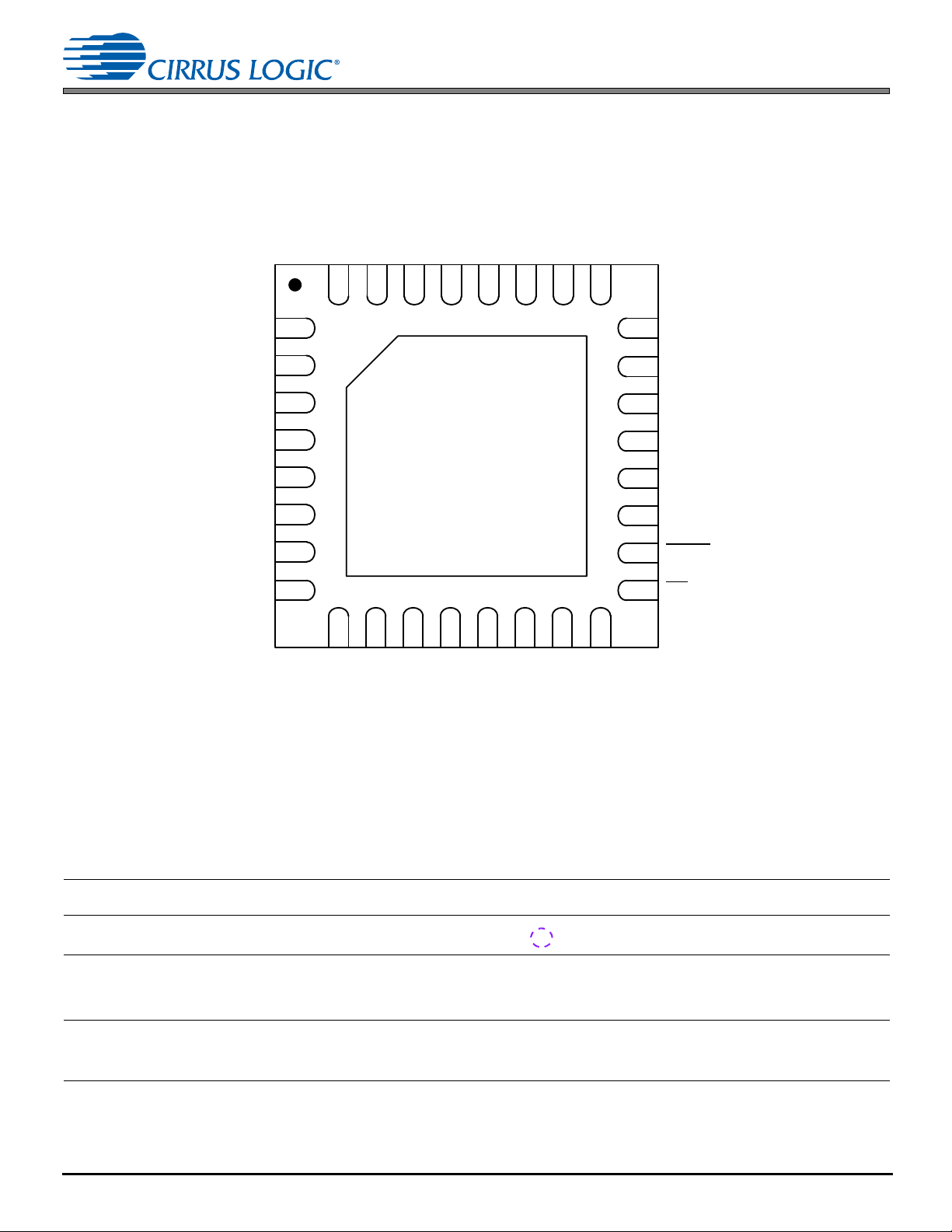

1.2 QFN

Thermal Pad

109

8

7

6

5

4

3

2

1

11 12 13 14 15 16

17

18

19

20

21

22

23

24

25

262728

29

303132

SCL

ASP_SDOUT2/AD0

ASP_LRCK/FSYNC

VA

GNDD

SYNC

RESET

INTGNDA

MUTE

IN1–

DMIC2_SCLK/AD1

IN1+/DMIC1_SD

DMIC1_SCLK

ASP_SDOUT1

ASP_SCLK

MCLK

SDA

MIC_BIAS_FILT

MIC4_BIAS

MIC3_BIAS

MIC2_BIAS

MIC1_BIAS

VP

FILT+

VA

IN4–

IN4+

IN3–

IN3+/DMIC2_SD

IN2–

IN2+

Capture-Path Pins

CS53L30

1.2 QFN

1.3 Pin Descriptions

Name

IN1+/DMIC1_SD

IN2+

IN3+/DMIC2_SD

IN4+

IN1–

IN2–

IN3–

IN4–

DS992F1 5

Figure 1-2. Top-Down (Through-Package) View—32-Pin QFN Package

Ball#Pin#Power

A1

31

A2

A3

A4

B1

B2

B3

B4

1

3

5

32

2

4

6

Supply

I/O Description

VA I Noninverting Inputs/DMIC Inputs.

VA I Inverting Inputs. Negative analog inputs

Positive analog inputs for the stereo

ADCs when CH_TYPE = 0 (default) or

DMIC inputs when CH_TYPE = 1.

for the stereo ADCs when CH_TYPE = 0

(default) or unused when CH_TYPE = 1.

Table 1-1. Pin Descriptions

Internal

Connection

Programmable — Hysteresis

Programmable — Hysteresis

Driver Receiver

State at

Reset

—

on CMOS

input

—

on CMOS

input

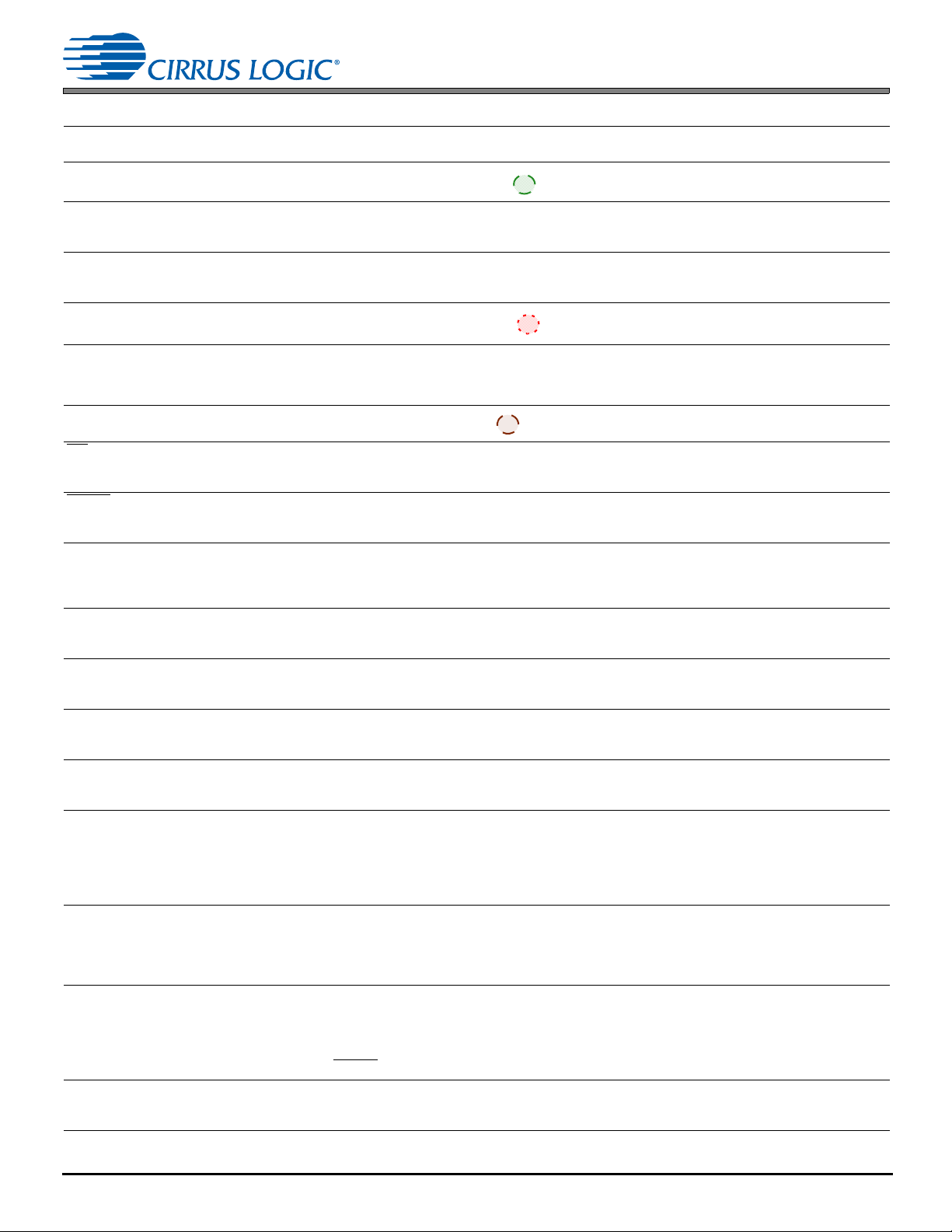

Page 6

Table 1-1. Pin Descriptions (Cont.)

Filter pins

Analog Outputs

Digital I/O

CS53L30

1.3 Pin Descriptions

Name

MIC_BIAS_FILT D6 15 VP I Mi crophone Bias Voltage Filter. Filter

FILT+ A6 9 VA O Positive Reference Filter. Positive

MIC1_BIAS

MIC2_BIAS

MIC3_BIAS

MIC4_BIAS

INT

RESET

SYNC D4 19 VA I/O Multidevice Synchronization Signal.

SCL D3 24 VA I Serial Control Port Clock. Serial clock

SDA E2 25 VA I/O Serial Control Data. Bidirectional data

MCLK E1 26 VA I Master Clock. Clock source for device’s

ASP_SCLK D2 27 VA I/O Audio Serial Clock. Audio bit clock. Input

ASP_LRCK/

FSYNC

ASP_SDOUT1 D1 28 VA O Audio Data Output. Output for the two’s

ASP_SDOUT2/

AD0

DMIC1_SCLK C2 29 VA O Digital MIC Interface 1 Serial Clock.

Ball#Pin#Power

C4

C5

C6

D5

—17 VA OInterrupt. Outgoing interrupt signal

E5 18 VA I Reset. The device enters a low power

C3 22 VA I/O Audio Left/Right Clock/Frame SYNC.

E3 23 VA I/O Au dio Data Output/Address Select.

Supply

11

12

13

14

I/O Description

connection for the internal quiescent

voltage used for the MICx_BIAS outputs.

reference voltage filter for internal

sampling circuits.

VP O Microphone Bias Voltage. Low-noise

bias supply for an external mic.

generated upon registering an error

(fault).

mode when this pin is driven low.

Synchronization output when SYNC_EN

is set, otherwise it is a synchronization

input. Defaults to input.

2

for the I

pin for the I

core.

in Slave Mode, output in Master Mode.

Identifies the start of each seri alized PCM

data word and indicates the active

channel on each serial PCM audio data

line. Input in Slave Mode, output in Master

Mode.

complement serial PCM data. Channels 1

and 2 are output in I

channels of data are output on this single

pin in TDM Mode.

Output for the two’s-complement serial

PCM data. Channels 3 and 4 are output in

2

I

immediately sets the I

RESET

High speed clock output to the digital

mics.

C port.

2

C port.

2

S Mode, while all four

S Mode. Along with DMIC2_SCLK/AD1,

is deasserted. Default is 0.

2

C address when

Internal

Connection

————

————

———Hi-Z

—CMOS

— — Hysteresis

Weak

pulldown

— — Hysteresis

—CMOS

Weak

pulldown

Weak

pulldown

Weak

pulldown

Weak

pulldown

Weak

pulldown

Weak

pulldown

Driver Receiver

open-drain

output

on CMOS

CMOS

output

open-drain

output

— Hysteresis

CMOS

output

CMOS

output

Tristateable

CMOS

output

Tristateable

CMOS

output

CMOS

output

Hysteresis

on CMOS

on CMOS

Hysteresis

on CMOS

on CMOS

Hysteresis

on CMOS

Hysteresis

on CMOS

—Hi-Z

input

input

input

input

input

input

input

—Hi-Z

—Hi-Z

—Hi-Z

State at

Reset

—

Hi-Z

—

—

—

Hi-Z

Hi-Z

6 DS992F1

Page 7

Table 1-1. Pin Descriptions (Cont.)

Power

CS53L30

GNDD

GNDA

DMIC1_SCLK

MIC1_BIAS

IN1

–

IN1+

MIC2_BIAS

IN2

–

IN2+

MIC3_BIAS

IN3

–

IN3+

MIC4_BIAS

IN4

–

IN4+

Analog Mic r op hone Conn ec tion

Two-wire microphone connection

Rbias

Ground Ring

MICx_BIAS

INx+

INx–

Three-wire microphone connection

Ground Ring

MICx_BIAS

INx+

INx–

1 µF

C

INM

C

INM

Analog

Microphone

(see

connection

diagram)

1 µF

C

INM

C

INM

Analog

Microphone

(see

connection

diagram)

1 µF

C

INM

C

INM

Analog

Microphone

(see

connection

diagram)

1 µF

C

INM

C

INM

Analog

Microphone

(see

connection

diagram)

MIC_BIAS_FILT

*

4.7 µF

SYNC

SCL

SDA

SoC

VA

0.1 µF

R

P

*

R

P

+1.8 V +1.8 V

VP

0.1 µF

*

+3.6 V

FILT+

2.2 µF

*

PMU

ASP_LRCK/F SYNC

ASP_SCLK

ASP_SDOUT2/AD0

ASP_SDOUT1

MCLK

RESET

MUTE

R

P_I

Key for Capacitor Types Required:

* U s e low ESR, X7R /X5R c apac it ors

All External Passive Component Values Shown Are Nominal Values.

DMIC2_SCLK/AD1

INT

Note 1

Note 3

Note 1

Note 3

Note 2

Note 2

Note 5

Note 4 Note 4

Note 7

Note 7

Note 2

Note 1

Note 3

Note 2

Note 1

Note 3

Note 6

CS53L30

2 Typical Connection Diagram

Name

DMIC2_SCLK/

AD1

Ball#Pin#Power

Supply

I/O Description

C1 30 VA I/O Digital MIC Interface 2 Serial Clock/

Address Select. High speed clock output

to the digital mics. Along with ASP_

SDOUT2/AD0, immediately sets the I

address when RESET

is deasserted.

2

C

Internal

Connection

Weak

pulldown

Driver Receiver

CMOS

—Hi-Z

output

State at

Reset

Default is 0.

MUTE E6 16 VA I Mute. Asserting this pin mutes all four

channels. Also can be programmed to

power down modules as configured in the

Weak

pulldown

— Hysteresis

on CMOS

input

MUTE pin control registers.

VA A5 7

N/A I Analog/Digital Power. Power supply for

21

analog circuitry and digital circuitry via

————

internal LDO.

VP B6 10 N/A I Analog Power. Power supply for mic

————

bias.

GNDA B5 8 N/A I Analog Ground. Ground reference. — — — —

GNDD E4 20 N/A I Digital Ground. Ground reference. — — — —

2 Typical Connection Diagram

—

Figure 2-1. Typical Connection Diagram—Analog Microphone Connections

DS992F1 7

Page 8

CS53L30

CS53L30

GNDDGNDA

Left Digital

Mic rophone 1

Right D igital

Mic rophone 1

IN1+/DMIC1_SD

DMIC1_SCLK

L/R

DATA

L/R

DATA

IN3+/DMIC2_SD

Left Digital

Mic rophone 2

Right Digital

Mic rophone 2

L/R

DATA

L/R

DATA

+1.8 V +1.8 V

VP

0.1 µF

*

+3.6 V

FILT+

MIC_BIAS_FILT

*

4.7 µF

PMU

SCL

SDA

SoC

VA

0.1 µ F

R

P

*

R

P

ASP_LRCK/FSYNC

ASP_SCLK

ASP_SDOUT1

MCLK

RESET

MUTE

R

P_I

Key for Capacitor Types Required:

* U s e low ESR, X7R/X5 R c apac it ors

All External Passive Component Values Shown Are Nominal Values.

0.47 µF

0. 47 µ F

0.47 µF

0.47 µF

MIC1_BIAS

MIC3_BIAS

DMIC2_SCLK/AD1

SYNC

IN1–, IN2+, IN2–,

IN3

–

, IN4+, IN4

–

ASP_SDOUT2/AD0

INT

Note 4 Note 4

Note 8

Note 7

Note 7

Note 6

2 Typical Connection Diagram

1. The MICx_BIAS compensation capacitor must be 1 µF (nominal values indicated, can vary from the nominal by ±20%). This value is bounded

by the stability of the amplifier and the maximum rise-t ime specification of the output.

Figure 2-2. Typical Connection Diagram—Digital Microphone Connections

2. The DC-blocking capacitor, C

impedance. See Table 3-5 and Section 4.4.2.

3. The reference terminal of the INx inputs connects to the ground pin of the mic cartridge in the pseudodifferential case. I n a fully differential

configuration, the reference terminal of the INx inputs connects to the inverting output terminal of differential mic.

4. R

and RP can be calculated by using the values in Table 3-14.

P_I

5. The value of R

6. The INT

7. ASP_SDOUT2/AD0 and DMIC2_SCLK/AD1 have internal pull-downs that allow for the default I

See Table 3-14 for typical and maximum pull-down values. If an I

pin is provided only on the QFN package.

, the bias resistor for electret condenser mics, is dictated by the mic cartridge.

BIAS

termination to VA is required. The minimum value resistor allowed on these I/O pins is 10 kThe time constant resulting from the pull-up/

pull-down resistor and the total net cap acit ance should be consi dered when determining the time required for the p in voltage t o settle befo re

RESET is deasserted.

8. Unconnected INx pins can be terminated with an internal weak_vcm or weak pull-down by setting the termin ation in the INxy_BIAS bit s. See

Section 5.7, Section 7.19, and Section 7.20.

, forms a high-pass filter whose corner frequency is determined by the capacitor value and the input

INM

2

C physical address other than the default is desired, then external resi stor

2

C address with no external components.

8 DS992F1

Page 9

CS53L30

3 Characteristics and Specification s

3 Characteristics and Specifications

Section 8 provides additional details about parameter definitions.

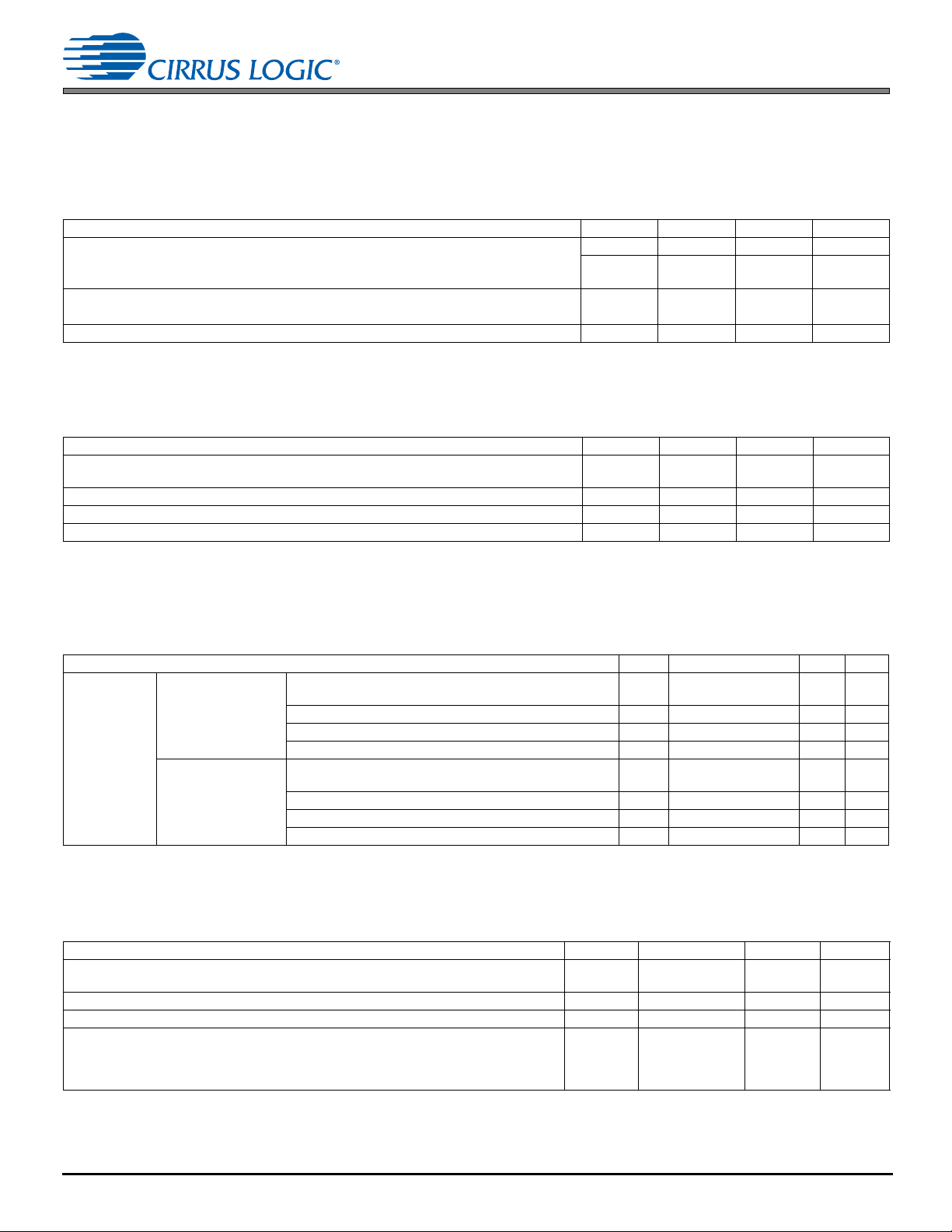

Table 3-1. Recommended Operating Conditions

Test conditions: GNDA = GNDD = 0 V; all voltages are with respect to ground.

Parameters

DC power supply Analog/Digital VA 1.71 1.89 V

External voltage applied to pin

2

Ambient temperature Commercial T

1.Device functional operation is guaranteed within these limits; operation outside them is not guaranteed or implied and may reduce device reliability.

2.The maximum over/under voltage is limited by the input current.

Table 3-2. Absolute Maximum Ratings

Test conditions: GNDA = GNDD = 0 V; all voltages are with respect to ground.

Parameters Symbol Min Max Units

DC power supply Analog/digital

Input current

Ambient operating temperature (power applied) T

Storage temperature (no power applied) T

CAUTION: Operation at or beyond these limits may permanently damage the device.

1.Any pin except supplies. Transient currents of up to ±100 mA on the capture-path pins do not cause SCR latch-up.

1

1

VP_MIN = 1

VP_MIN = 0

VA domain pins V

VP domain pins V

Mic bias

Symbol Min Max Unit

VP 3.2

3.0

IN-AI

IN-PI

A

VA

VP

I

in

A

stg

–0.3 VA + 0.3 V

–0.3 VP + 0.3 V

–10 +70 C

–0.3

–0.3

—±10mA

–50 +115 °C

–65 +150 °C

5.25

5.25

2.22

5.6

V

V

V

V

Table 3-3. Combined ADC On-Chip Analog, Digital Filter, SRC, and DMIC Characteristics

Test conditions (unless otherwise specified): TA = +25°C; MCLK = 12.288 MHz; characteristics do not include the effects of external AC-coupling

capacitors. Path is INx to SDOUT. Analog and digital gains are all set to 0 dB; HPF disabled.

1

–3.0-dB corner——

Min Typ Max Units

0.391

0.410

—

—

Fs

= Fs

int

Fs = 48 kHz

ext

=

ADC notch filter on

[2]

(ADCx_NOTCH_

DIS = 0)

Parameters

Passband –0.05-dB corner

Passband ripple (0 Hz to 0.394 Fs; normalized to 0 Hz) –0.13 — 0.14 dB

Stopband @ –70 dB — 0.492 —

ADC notch filter off

(ADCx_NOTCH_

DIS = 1)

Total group delay — 15.3/Fs

Passband –0.05-dB corner

–3.0-dB corner——

Passband ripple (0 Hz to 0.447 Fs; normalized to 0 Hz) –0.09 — 0.14 dB

+6.5/Fs

int

0.445

0.470

—s

ext

—

—

Stopband @ –70 dB — 0.639 —

Total group delay — 15.5/Fs

1.Specifications are normalized to Fs and can be denormalized by multiplying by Fs.

2.See Section 5.6 for information about combined filter response when Fs

is not equal to Fs

int

ext

.

+6.6/Fs

int

—s

ext

Table 3-4. ADC High-Pass Filter (HPF) Characteristics

Test conditions (unless specified otherwise): Analog and digital gains are all set to 0 dB; ADCx_HPF_CF = 00.

Passband

Passband ripple (0.417x10

Phase deviation @ 0.453 x 10

Filter settling time

2

–3

Fs to 0.417 Fs; normalized to 0.417 Fs) — — 0.01 dB

–3

3

Fs — 4.896 — °

ADCx_HPF_CF = 00 (3.88 x 10

ADCx_HPF_CF = 01 (2.5 x 10

ADCx_HPF_CF = 10 (4.9 x 10

ADCx_HPF_CF = 11 (9.7 x 10

Parameters

1.Response scales with Fs

2.Characteristics do not include effects of the analog HPF filter formed by the external AC-coupling capacitors and the input impedance.

3.Required time for the magnitude of the DC component present at the output of the HPF to reach 5% of the applied DC signal.

. Specifications are normalized to Fs

int

1

–0.05-dB corner

–3.0-dB corner

–5

x Fs

mode)

int

–3

x Fs

mode)

int

–3

x Fs

mode)

int

–3

x Fs

mode)

int

and are denormalized by multiplying by Fs

int

Min Typ Max Units

200/Fs

100/Fs

50/Fs

.

int

–4

–5

int

int

int

int

—

—

—

—

—

—

Fs

Fs

—

—

—

—

—

—

3.57x10

3.88x10

12260/Fs

Fs

Fs

Fs

Fs

Fs

Fs

int

int

s

s

s

s

DS992F1 9

Page 10

CS53L30

–60 dB,

1 kHz

INx+

INx–

MICx_BIAS

2.21 k

2.21 k

0.1 µF

0.1 µF

100 mVPP, 25 Hz

0.1 µF

INx+

INx–

3 Characteristics and Specification s

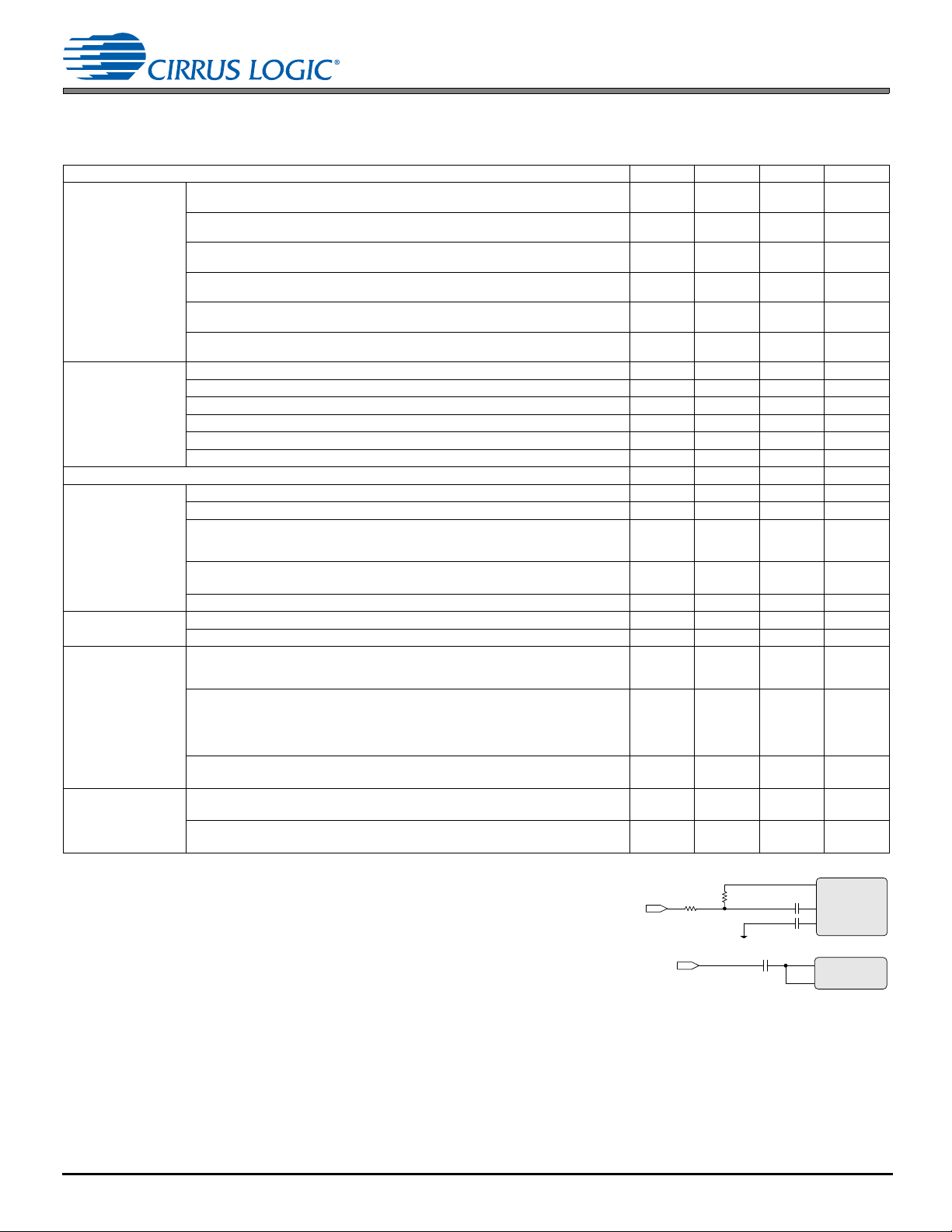

Table 3-5. Analog-Input-to-Serial-Port Characteristics

Test conditions (unless oth erwise spe cified): Fig. 2-1 shows CS53L30 connections; input is a full-scale 1- kHz sine wav e; ADCx_P REAMP = + 10 dB; ADCx_PGA_

VOL = 0 dB; GNDA = GNDD = 0; voltages are

min/max performance data ta ken with

Dynamic range

2

Preamp setting: Bypass, PGA setting: 0 dB A-weighted

Preamp setting: Bypass, PGA setting: +12 dB A-weighted

Preamp setting: +10 dB, PGA setting: 0 dB A-weighted

Preamp setting: +10 dB, PGA setting: +12 dB A-weighted

Preamp setting: +20 dB, PGA setting: 0 dB A-weighted

Preamp setting: +20 dB, PGA setting: +12 dB A-weighted

Total harmonic

distortion + noise

Preamp setting: Bypass, PGA setting: 0 dB –1 dB — –84 –78 dB

3

Preamp setting: Bypass, PGA setting: +12 dB –1 dB — –80 –74 dB

Preamp setting: +10 dB, PGA setting: 0 dB –1 dB — –76 –70 dB

Preamp setting: +10 dB, PGA setting: +12 dB –1 dB — –63 –57 dB

Preamp setting: +20 dB, PGA setting: 0 dB –1 dB — –70 –64 dB

Preamp setting: +20 dB, PGA setting: +12 dB –1 dB — –62 –56 dB

Common-mode rejection

4

DC accuracy Interchannel gain mismatch

Gain drift

5

— ±100 — ppm/°C

PGA A/B gain G

Preamp A/B gain G

Offset error

Phase accuracy Multichip interchannel phase mismatch

Interchannel phase mismatch

Input Interchannel isolation

Full-scale signal

input voltage

Input impedance

DC voltage at INx

(pin floating)

Preamp setting: Bypass ADCx_PDN = 0

11,12

Preamp setting: +10 dB or +20 dB ADCx_PDN = 0

1.Measures are referred to the applicable typical full-scale voltages. Applies to all THD+N and dynamic range values in the table.

2.INx dynamic range test configuration (pseudodifferential) Includes noise from MICx_BIAS

output (2.7-V setting) through a series 2.21-k resistor connected to INx. Input signal is –60 dB

down from the corresponding full-scale signal input voltage.

with respect to ground; param ete rs can vary with VA , typica l perfo rm ance data ta ken w ith VA= 1.8 V, VP = 3.6 V,

V

A = 1.8 V, VP = 3.6 V; TA = +25°C; measurement bandwidth is 20 Hz –20 kH z; LRC K= Fs = 48 kHz.

Parameters

1

unweighted8785

unweighted8078

unweighted8482

unweighted7472

unweighted7876

unweighted6664

Min Typ Max Units

93

91

86

84

90

88

80

78

84

82

72

70

—

—

—

—

—

—

—

—

—

—

—

—

—70—dB

5

MIN

G

MAX

G

MIN

G

6

7

8

8

9

10

Preamp setting: 0 dB, PGA setting: 0 dB

Preamp setting: +10 dB, PGA setting: 0 dB

Preamp setting: +10 dB, PGA setting: +12 dB

Preamp setting: +20 dB, PGA setting: 0 dB

Preamp setting: +20 dB, PGA setting: +12 dB

Preamp setting: 0 dB

MAX

217 Hz

1kHz

20 kHz

Preamp setting: +10 or +20 dB;450.9

ADCx_PDN = 1——

ADCx_PDN = 1——

—±0.2— dB

–6.25

11.75

0.375

9.5

19.9

—

—

—

—

—

—

0.78•VA

—

—

—

—

–6

12

0.5

10

20

128

0.5

0.5

90

90

80

0.82•VA

0.258•VA

0.064•VA

0.081•VA

0.020•VA

50

1

0.42•VA

0.50•VA

0.39•VA

0.50•VA

–5.75

12.25

0.625

10.5

20.5

—LSB

—

—

—

—

—

0.88•VA

—

—

—

—

—

—

—

—

—

—

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

°

°

dB

dB

dB

Vpp

Vpp

Vpp

Vpp

Vpp

k

M

V

V

V

V

3.Input signal amplitude is relative to typical full-scale signal input voltage.

4.INx CMRR test configuration

5.Measurements taken at all defined full-scale signal input voltages.

6.SDOUT code with ADC_HPF_ EN = 1, DIG_BOOSTx = 0. The offset is added at the ADC output; if two ADC sources are mixed, their offsets add.

7.Measured between two CS53L30 chips with input pairs IN1 selected and driven from same source with an MCLK of 19.2 MHz, 16-kHz sample rate,

and 8-kHz full-scale sine wave with preamp gain of +20 dB and PGA gain of +12 dB.

8.Measured between input pairs (IN1 to INx, IN2 to INx, IN3 to INx, IN4 to INx) with +20 dB preamp gain and +12 dB PGA gain.

9.ADC full-scale input voltage is measured between INx+ and INx– with the preamp set to bypass and the PGA set to 0-dB gain. Maximum input signal

level for INx depends on the preamp and PGA gain settings described in Section 5.4.1. The digital output level corresponding to ADC full-scale input

is less than 0 dBFS due to signal attenuation through the SRC; see Table 4-4.

10.Measured between INx+ and INx–.

11.INx pins are biased as specified when weak VCM is selected in the input bias control registers; see Section 7.19 and Section 7.20.

12.Changing gain settings to Bypass Mode may cause audible artifacts due to the difference in DC operating points between modes.

10 DS992F1

Page 11

CS53L30

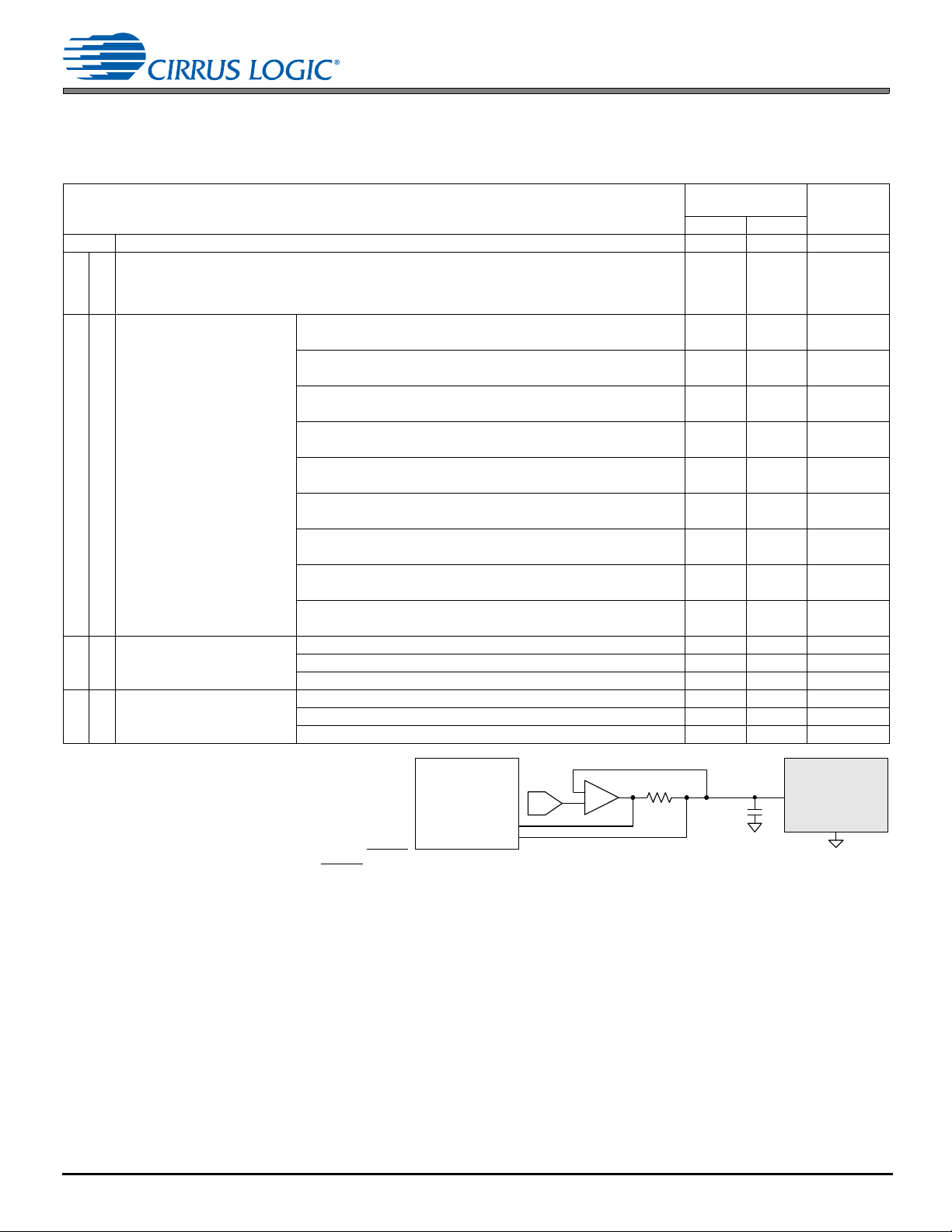

Operational

Amplifier

OUT

GND

Power DAC

OUT

GND

PWR

DUT

+5V +5V

++––

+

–

OUT

Analog Generator Analog Analy zer

Analog Test Equipment

Analog Output P S RR

Operational

Amplifier

OUT

GND

Power DAC

SDOUT

GND

PWR

DUT

+5V +5V

+–

+

–

OUT

Analog Generator Analog Analyzer

Test Equipment

Digital Output PSRR

Digital Analyzer

3 Characteristics and Specification s

Table 3-6. MIC BIAS Characteristics

Test conditions (unless otherwise specified): Fig. 2-1 shows CS53L30 connections; GNDA = GNDD = 0; all voltages are with respect to ground; VA =

1.8 V, VP = 3.6 V, T

Output voltage

Mic bias startup delay

Rise time

3

DC output current (I

Integrated output noise f = 100 Hz–20 kHz — 3 — µVrms

Dropout voltage

PSRR reduction voltage

Output resistance (R

1.The output voltage includes attenuation due to the MIC BIAS output resistance (R

2.Startup delay times are approximate and vary with MCLK

scaling factor. The MCLK

3.From 10% to 90% of typical output voltage. External capacitor on MICx_BIAS is as shown in Fig. 2-1.

4.Dropout voltage indicates the point where an output’s voltage starts to vary significantly with reductions to its supply voltage. When the VP supply

voltage drops below the programmed MICx_BIAS output voltage plus the dropout voltage, the MICx_BIAS output voltage progressively decreases as

its supply decreases.

Dropout voltage is measured by reducing the VP supply until MICx_BIAS drops 10 mV from its initial voltage with the default typical test condition VP

voltage (= 3.6 V, as in test conditions listed above). The difference between the VP supply voltage and the MICx_BIAS voltage at this point is the

dropout voltage. For instance, if the initial MICx_BIAS output is 2.86 V when VP = 3.6 V and VP = 3.19 V when MICx_BIAS drops to 2.85 V (–10 mV),

the dropout voltage is 340 mV (3.19 V – 2.85 V).

5.PSRR voltage indicates the point where an output’s supply PSRR starts to degrade significantly with supply voltage reductions. When the VP supply

voltage drops below the programmed MICx_BIAS output voltage plus the PSRR reduction voltage, the MICx_BIAS output’s PSRR progressively

decreases as its supply decreases.

PSRR reduction voltage is measured by reducing the VP supply until MICx_BIAS PSRR @ 217 Hz falls below 100 dB. The difference between the

VP supply voltage and the MICx_BIAS voltage at this point is the PSRR reduction voltage. For instance, if the MICx_BIAS PSRR falls to 99.9 dB

when VP is reduced to 3.25 V and the MICx_BIAS output voltage is 2.75 V at that point, PSRR reduction voltage is 500 mV (3.25 V – 2.75 V).

= +25°C; only one bias output is powered up at a time; MCLK_INT_SCALE = 0.

A

Parameters Min Typ Max Units

1

MIC_BIAS_CTRL = 01 (1.8-V mode)

MIC_BIAS_CTRL = 10 (2.7-V mode)

2

I

= 500 µA, MIC_BIAS_CTRL = 01 (1.8-V mode)

OUT

= 500 µA, MIC_BIAS_CTRL = 10 (2.7-V mode)

I

OUT

) Per output — — 2 mA

OUT

4

5

) I

OUT

frequency. If MCLK_INT_SCALE = 1, the startup delay time is scaled up by the MCLK

scaling factor is 1, 2, or 4, depending on Fs

INT

INT

EXT

= 2 mA

I

OUT

= 2-mA — 30 —

OUT

).

OUT

. See Table 4-2.

1.71

2.61

1.80

2.75

1.89

2.86

V

V

—10—ms

—

—

—

0.2

0.5

—

—

—

ms

ms

3

ms

— — 340 mV

— — 500 mV

INT

Table 3-7. Power-Supply Rejection Ratio (PSRR) Characteristics

Test conditions (unless specified otherwise): Fig. 2-1 shows CS53L30 connections; input test signal held low (all zero data); GNDA = GNDD = 0; voltages

are with respect to ground; VA = 1.8 V, VP = 3.6V; T

INx (32-dB analog gain)

PSRR with 100-mVpp signal AC coupled to VA supply

MICx_BIAS (MICx_BIAS = 2.7-V mode, I

PSRR with 100 mVpp signal AC coupled to VA supply

VP_MIN = 0 (3.0 V)

MICx_BIAS (MICx_BIAS = 2.7-V mode, I

PSRR with 100 mVpp signal AC coupled to VA supply

VP_MIN = 1 (3.2 V)

MICx_BIAS (MICx_BIAS = 2.7-V mode, I

PSRR with 100 mVpp signal AC coupled to VP supply

VP_MIN = 0 (3.0 V)

MICx_BIAS (MICx_BIAS = 2.7-V mode, I

PSRR with 1 Vpp signal AC coupled to VP supply

VP_MIN = 1 (3.2 V)

1.PSRR test

configuration:

Typical PSRR

can vary by

approximately

6 dB below the

indicated

values.

DS992F1 11

Parameters

OUT

OUT

OUT

OUT

= +25°C.

A

1

= 500 µA)

= 500 µA)

= 500 µA)

= 500 µA)

217 Hz

1kHz

20 kHz

217 Hz

1kHz

20 kHz

217 Hz

1kHz

20 kHz

217 Hz

1kHz

20 kHz

217 Hz

1kHz

20 kHz

Min Typical Max Units

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

70

70

55

105

100

95

105

100

95

90

90

70

120

115

105

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

Page 12

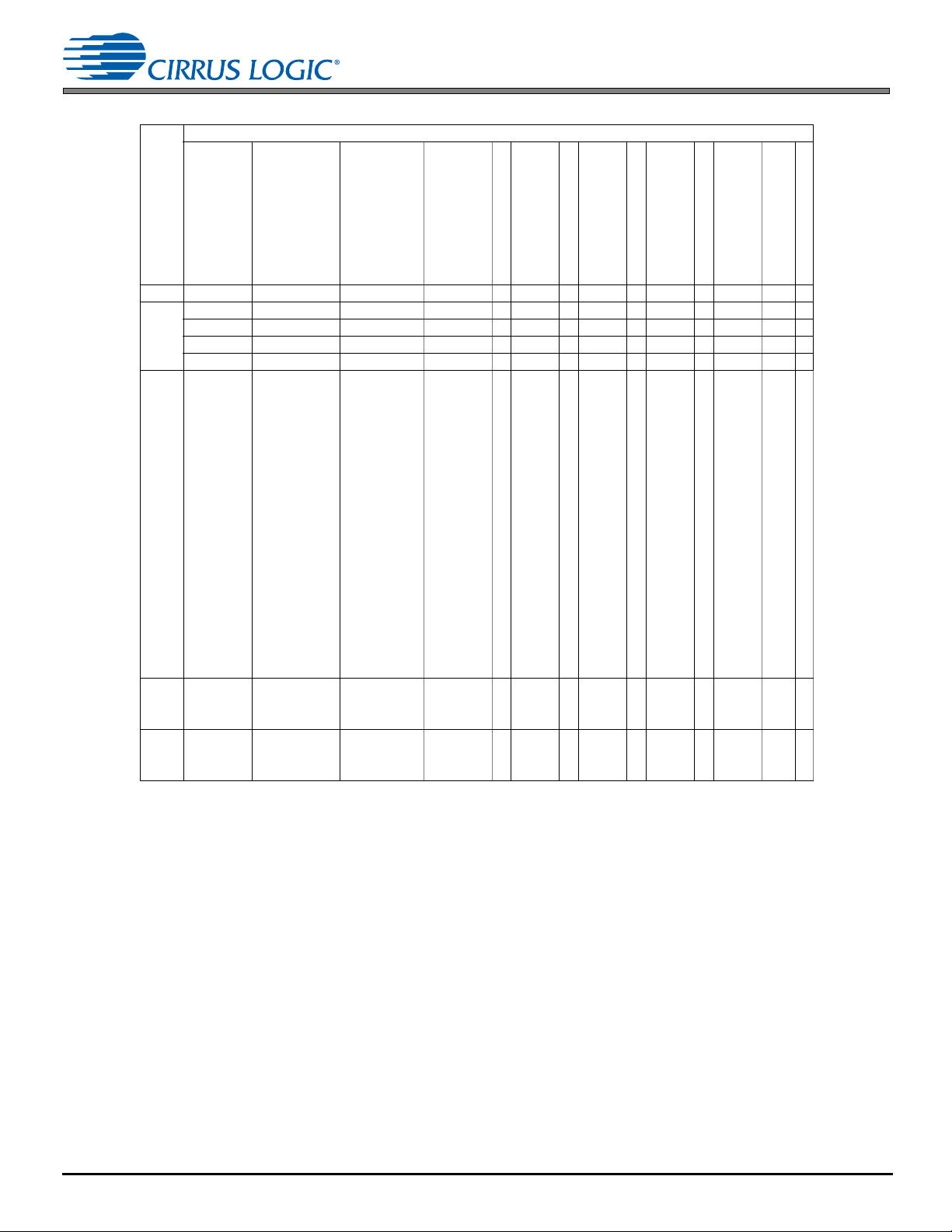

CS53L30

–

DAC

+

–

10

DUT

V

supply

GND

supply

0.1 µF

Voltmeter

+

3 Characteristics and Specification s

Table 3-8. Power Consumption

Test conditions (unless specified otherwise): Fig. 2-1 shows CS53L30 connections; GNDA = GNDD = 0 V; voltages are with respect to ground;

performance data taken with VA = 1.8 V, VP = 3.6 V; T

on any input; control port inactive; MCLK_INT_SCALE = 1.

(See Table 3-9 for register field settings.)

1 Standby

2A

Quiescent

2

3

B

C

D

3 A Capture, analog mic input,

ADCx_PREAMP = +20 dB,

BFs

ADCx_PGA_VOL = +12 dB

CFs

DFs

EFs

FFs

GFs

HFs

IFs

JFs

KFs

LFs

MFs

NFs

OFs

PFs

QFs

RFs

4 A Capture, analog line input,

ADCx_PREAMP = 0 dB,

BFs

ADCx_PGA_VOL = 0 dB

CFs

5 A Capture, digital mic input Fs

BFs

CFs

1.Power consumption test configuration.

The curren

t draw on the power supply pins is

derived from the measured voltage drop

across a 10- series resistor between the

associated supply source and the voltage

supply pin.

2.Standby configuration: Clock/data lines are held low; RESET = LOW; VA = 1.8 V, VP = 3.6 V

3.Quiescent configuration: data lines held low; RESET = HIGH

= +25°C; MCLK = 12.288 MHz; serial port set to Slave Mode; digital volume = 0 dB; no signal

A

Use Cases

1

Typical Current

(µA)

i

VA

i

VP

20 4

MCLK low, MCLK_DIS = x, PDN_ULP = 1, PDN_LP = x

MCLK active, MCLK_DIS = 1, PDN_ULP = 1, PDN_LP = x

MCLK low, MCLK_DIS = x, PDN_ULP = 0, PDN_LP = 1

MCLK active, MCLK_DIS = 1, PDN_ULP = 0, PDN_LP = 1

= 48 kHz, mono input, MICx_BIAS_PDN = 1 1998 58 3805

Fs

ext

= 48 kHz, mono input, MICx_BIAS_PDN = 0 2003 147 4136

ext

= 16 kHz, mono input, MICx_BIAS_PDN = 1 1423 58 2770

ext

= 16 kHz, mono input, MICx_BIAS_PDN = 0 1432 147 3107

ext

= 8 kHz, mono input, MICx_BIAS_PDN = 1 1046 58 2092

ext

= 8 kHz, mono input, MICx_BIAS_PDN = 0 1053 147 2425

ext

= 48 kHz, stereo input, MICx_BIAS_PDN = 1 2697 81 5147

ext

= 48 kHz, stereo input, MICx_BIAS_PDN = 0 2702 243 5739

ext

= 16 kHz, stereo input, MICx_BIAS_PDN = 1 1955 81 3811

ext

= 16 kHz, stereo input, MICx_BIAS_PDN = 0 1960 243 4405

ext

= 8 kHz, stereo input, MICx_BIAS_PDN = 1 1494 81 2981

ext

= 8 kHz, stereo input, MICx_BIAS_PDN = 0 1498 243 3573

ext

= 48 kHz, four-channel input, MICx_BIAS_PDN = 1 4138 145 7969

ext

= 48 kHz, four-channel input, MICx_BIAS_PDN = 0 4141 454 9087

ext

= 16 kHz, four-channel input, MICx_BIAS_PDN = 1 3033 145 5981

ext

= 16 kHz, four-channel input, MICx_BIAS_PDN = 0 3040 454 7106

ext

= 8 kHz, four-channel input, MICx_BIAS_PDN = 1 2397 145 4836

ext

= 8 kHz, four-channel input, MICx_BIAS_PDN = 0 2403 454 5959

ext

= 48 kHz, four-channel input, MICx_BIAS_PDN = 1 3151 145 6193

Fs

ext

= 16 kHz, four-channel input, MICx_BIAS_PDN = 1 2059 145 4227

ext

= 8 kHz, four-channel input, MICx_BIAS_PDN = 1 1429 145 3092

ext

= 48 kHz, four-channel input, MICx_BIAS_PDN = 0 2433 352 5645

ext

= 16 kHz, four-channel input, MICx_BIAS_PDN = 0 1366 352 3725

ext

= 8 kHz, four-channel input, MICx_BIAS_PDN = 0 881 352 2852

ext

7

54

103

134

1

1

19

19

Total Power

(µW)

101

253

308

17

12 DS992F1

Page 13

CS53L30

3 Characteristics and Specification s

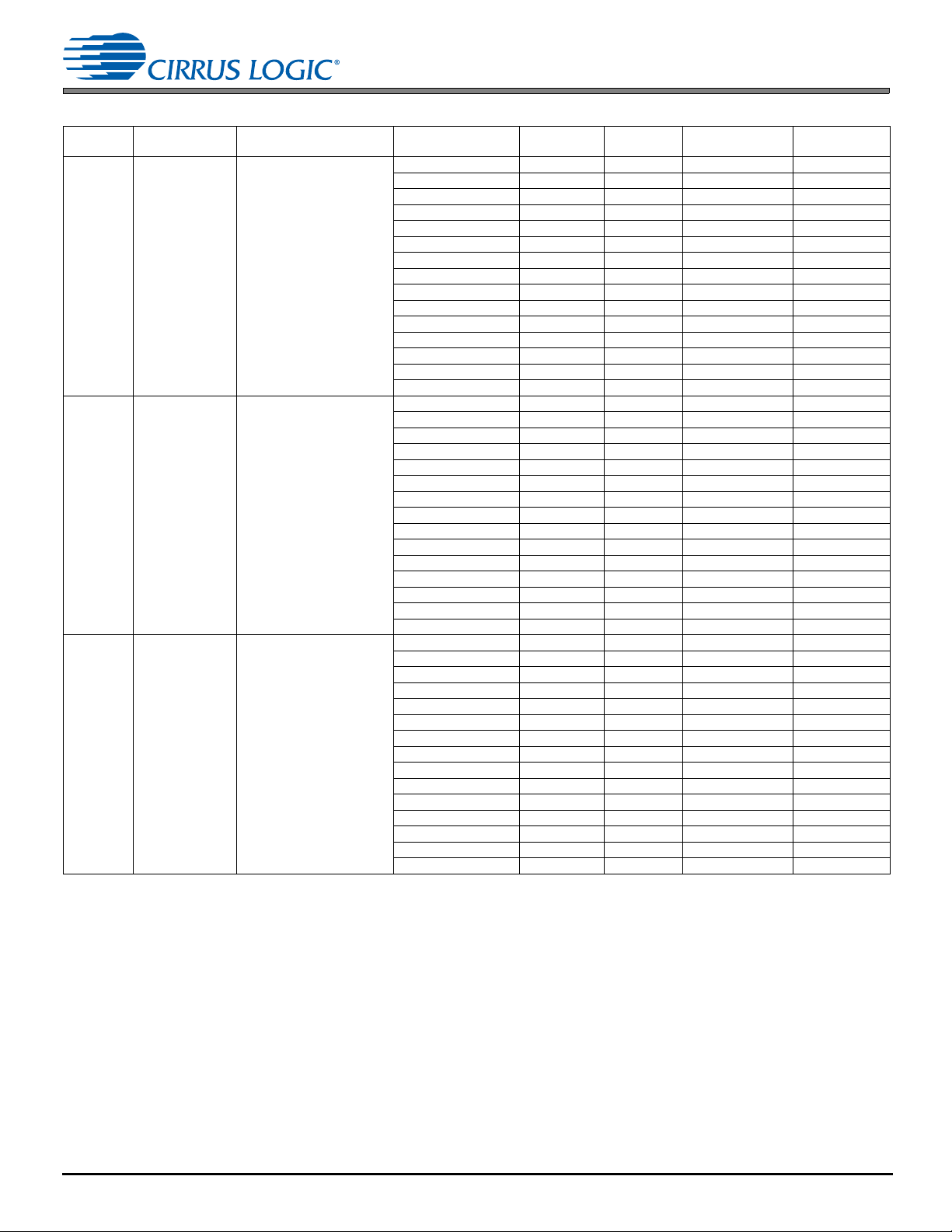

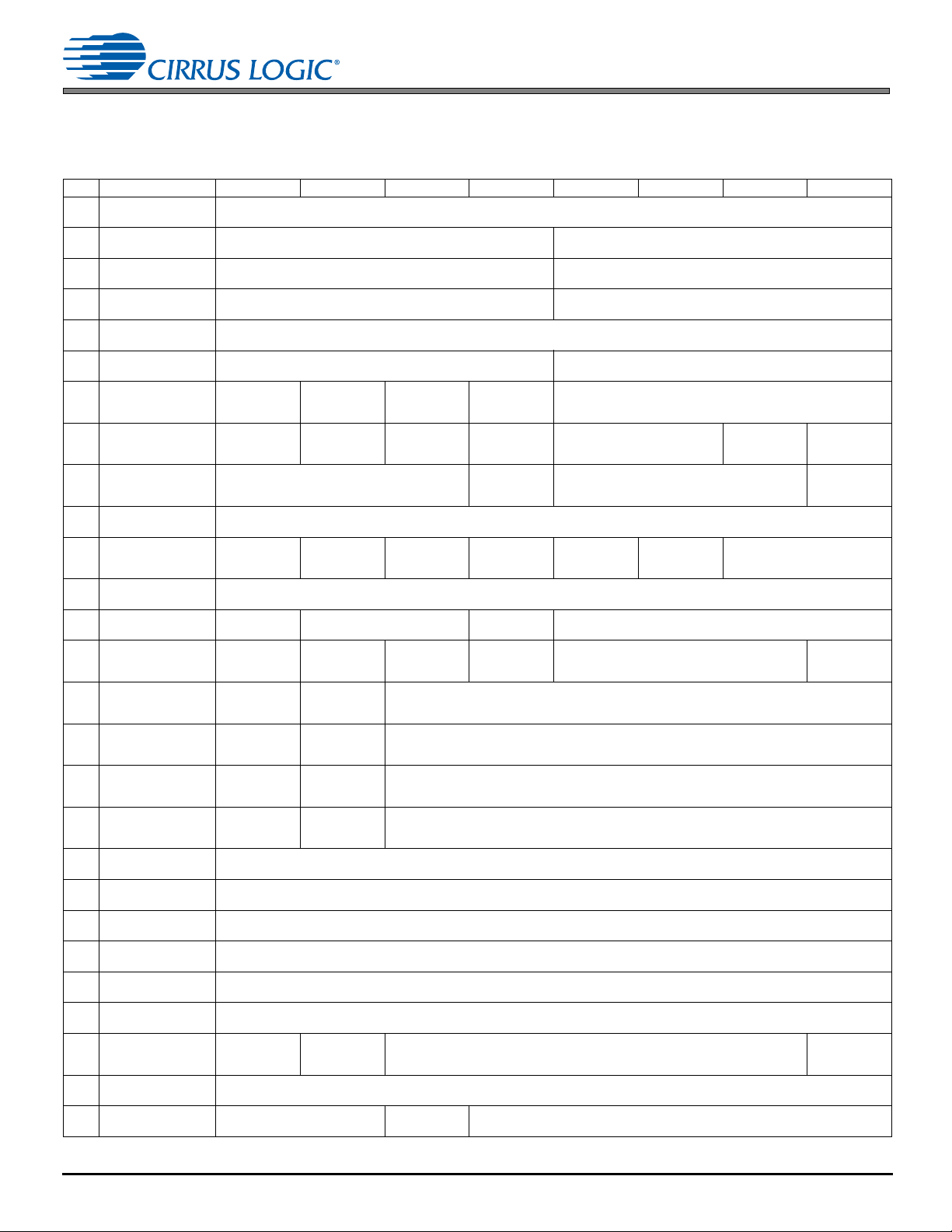

Table 3-9. Register Field Settings

Register Fields and Settings

Use

Cases

PDN_ULP

PDN_LP

MCLK_DIS

MCLK_INT_SCALE

MIC1_BIAS_PDN

MIC2_BIAS_PDN

MIC3_BIAS_PDN

MIC4_BIAS_PDN

MIC_BIAS_CTRL

ASP_RATE[3:0]

ASP_SDOUT1_PDN

ASP_SDOUT2_PDN

ASP_3ST

ADC1A_PDN

ADC1B_PDN

ADC2A_PDN

ADC2B_PDN

ADC1A_PREAMP[1:0]

ADC1A_PGA_VOL[5:0]

ADC1B_PREAMP[1:0]

ADC1B_PGA_VOL[5:0]

ADC2A_PREAMP[1:0]

ADC2A_PGA_VOL[5:0]

ADC2B_PREAMP[1:0]

ADC2B_PGA_VOL[5:0]

DMIC1_PDN

1 ————————— — ———————— — — — — — — — ———

2 A 1 ———————— — ———————— — — — — — — — ———

B 1 — 1 — ——— —— — ———————— — — — — — — — ———

C 0 1 ——————— — ———————— — — — — — — — ———

D 0 1 1 —————— — ———————— — — — — — — — ———

3 A 0 0 0 — 1 1 1 1 — 1100 0 1 0 0 1 1 1 10 011000 10 011000 10 011000 10 011000 1 1 0

B 0 0 0 — 0 1 1 1 10 1100 0 1 0 0 1 1 1 10 011000 10 011000 10 011000 10 011000 1 1 0

C 0 0 0 1 1 1 1 1 — 0101 0 1 0 0 1 1 1 10 011000 10 011000 10 011000 10 011000 1 1 0

D 0 0 0 1 0 1 1 1 10 0101 0 1 0 0 1 1 1 10 011000 10 011000 10 011000 10 011000 1 1 0

E 0 0 0 1 1 1 1 1 — 0001 0 1 0 0 1 1 1 10 011000 10 011000 10 011000 10 011000 1 1 0

F 0 0 0 1 0 1 1 1 10 0001 0 1 0 0 1 1 1 10 011000 10 011000 10 011000 10 011000 1 1 0

G 0 0 0 — 1 1 1 1 — 1100 0 1 0 0 0 1 1 10 011000 10 011000 10 011000 10 011000 1 1 0

H 0 0 0 — 0 0 1 1 10 1100 0 1 0 0 0 1 1 10 011000 10 011000 10 011000 10 011000 1 1 0

I 0 0 0 1 1 1 1 1 — 0101 0 1 0 0 0 1 1 10 011000 10 011000 10 011000 10 011000 1 1 0

J 0 0 0 1 0 0 1 1 10 0101 0 1 0 0 0 1 1 10 011000 10 011000 10 011000 10 011000 1 1 0

K 0 0 0 1 1 1 1 1 — 0001 0 1 0 0 0 1 1 10 011000 10 011000 10 011000 10 011000 1 1 0

L 0 0 0 1 0 0 1 1 10 0001 0 1 0 0 0 1 1 10 011000 10 011000 10 011000 10 011000 1 1 0

M 0 0 0 — 1 1 1 1 — 1100 0 0 0 0 0 0 0 10 011000 10 011000 10 011000 10 011000 1 1 0

N 0 0 0 — 0 0 0 0 10 1100 0 0 0 0 0 0 0 10 011000 10 011000 10 011000 10 011000 1 1 0

O 0 0 0 1 1 1 1 1 — 0101 0 0 0 0 0 0 0 10 011000 10 011000 10 011000 10 011000 1 1 0

P 0 0 0 1 0 0 0 0 10 0101 0 0 0 0 0 0 0 10 011000 10 011000 10 011000 10 011000 1 1 0

Q 0 0 0 1 1 1 1 1 — 0001 0 0 0 0 0 0 0 10 011000 10 011000 10 011000 10 011000 1 1 0

R 0 0 0 1 0 0 0 0 10 0001 0 0 0 0 0 0 0 10 011000 10 011000 10 011000 10 011000 1 1 0

4 A 0 0 0 — 1 1 1 1 — 1100 0 0 0 0 0 0 0 00 000000 00 000000 00 000000 00 000000 1 1 0

B 0 0 0 1 1 1 1 1 — 0101 0 0 0 0 0 0 0 00 000000 00 000000 00 000000 00 000000 1 1 0

C 0 0 0 1 1 1 1 1 — 0001 0 0 0 0 0 0 0 00 000000 00 000000 00 000000 00 000000 1 1 0

5 A 000—00001011000000000— — — — — — — — 000

B 000100001001010000000— — — — — — — — 000

C 000 10 0001000010000000— — — — — — — — 000

DMIC2_PDN

ASP_M/S

DS992F1 13

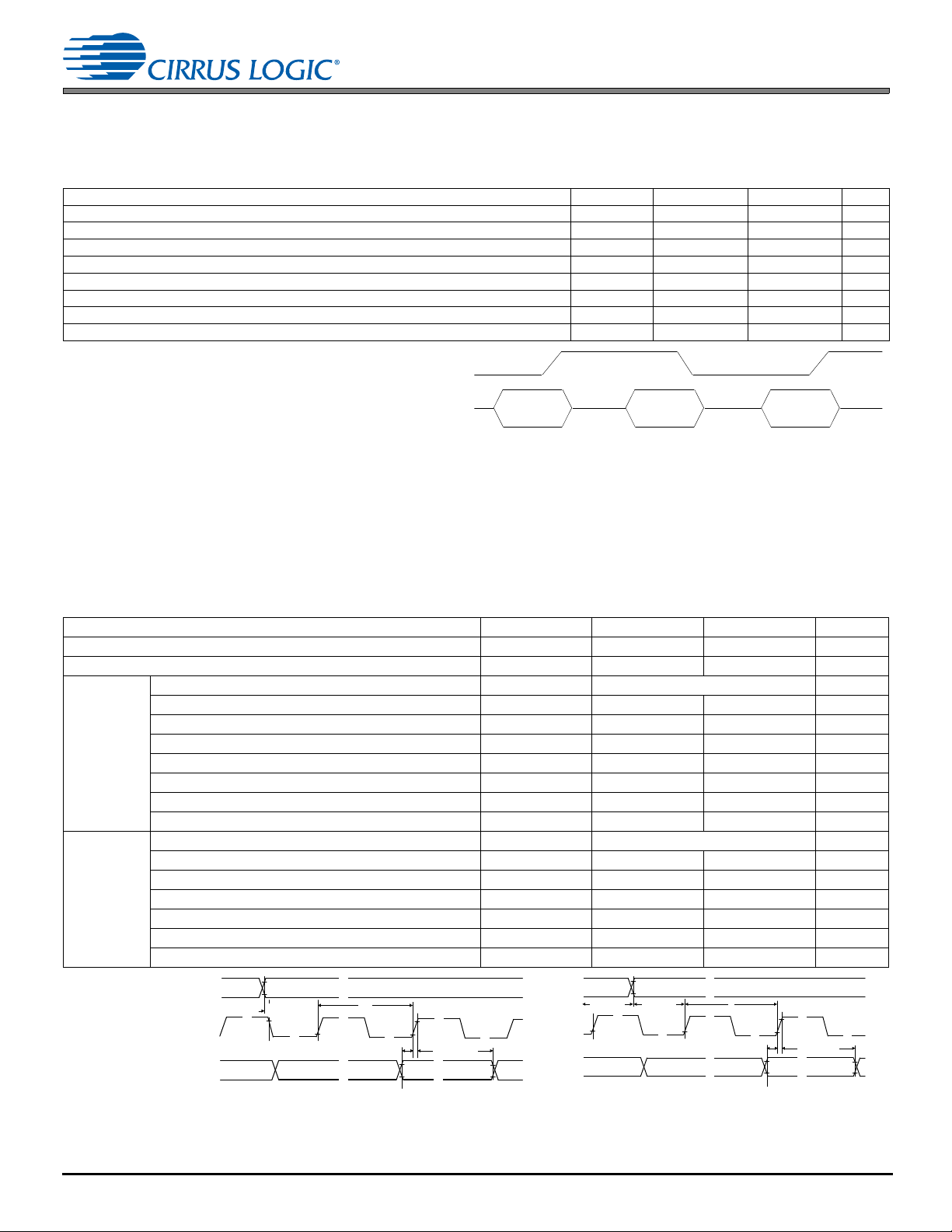

Page 14

CS53L30

DMIC_CLK

DMIC_SD

Left

(A, DA T A1)

Channel Dat a

Right

(B, DATA2)

Channel Dat a

Left

(A, DATA1)

Channel Dat a

t

hm(SK-SDO)

//

//

//

//

//

//

MSB

LRCK

SCLK

SDOUT

t

Pm

t

sm(SDO-SK)

//

//

//

//

//

//

t

sm(LK-SK)

t

hs(SK-SDO)

//

//

//

//

//

//

MSB

LRCK

SCLK

SDOUT

t

ss(LK-SK)

t

P

t

ss(SDO-SK)

//

//

//

//

//

//

t

hs(LK-SK)

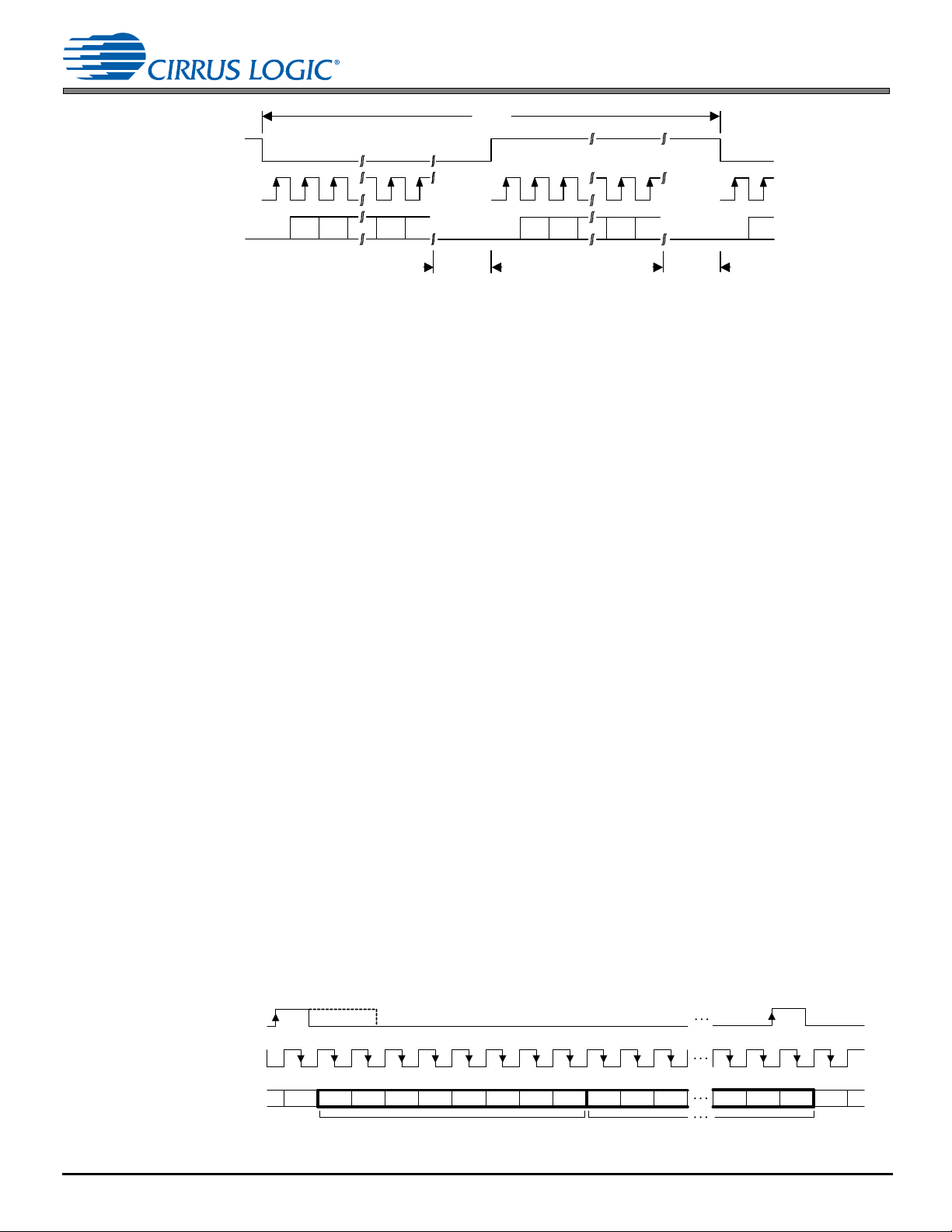

Serial Port Timing—Master Mode

Serial Port Timing—Slave Mode

3 Characteristics and Specification s

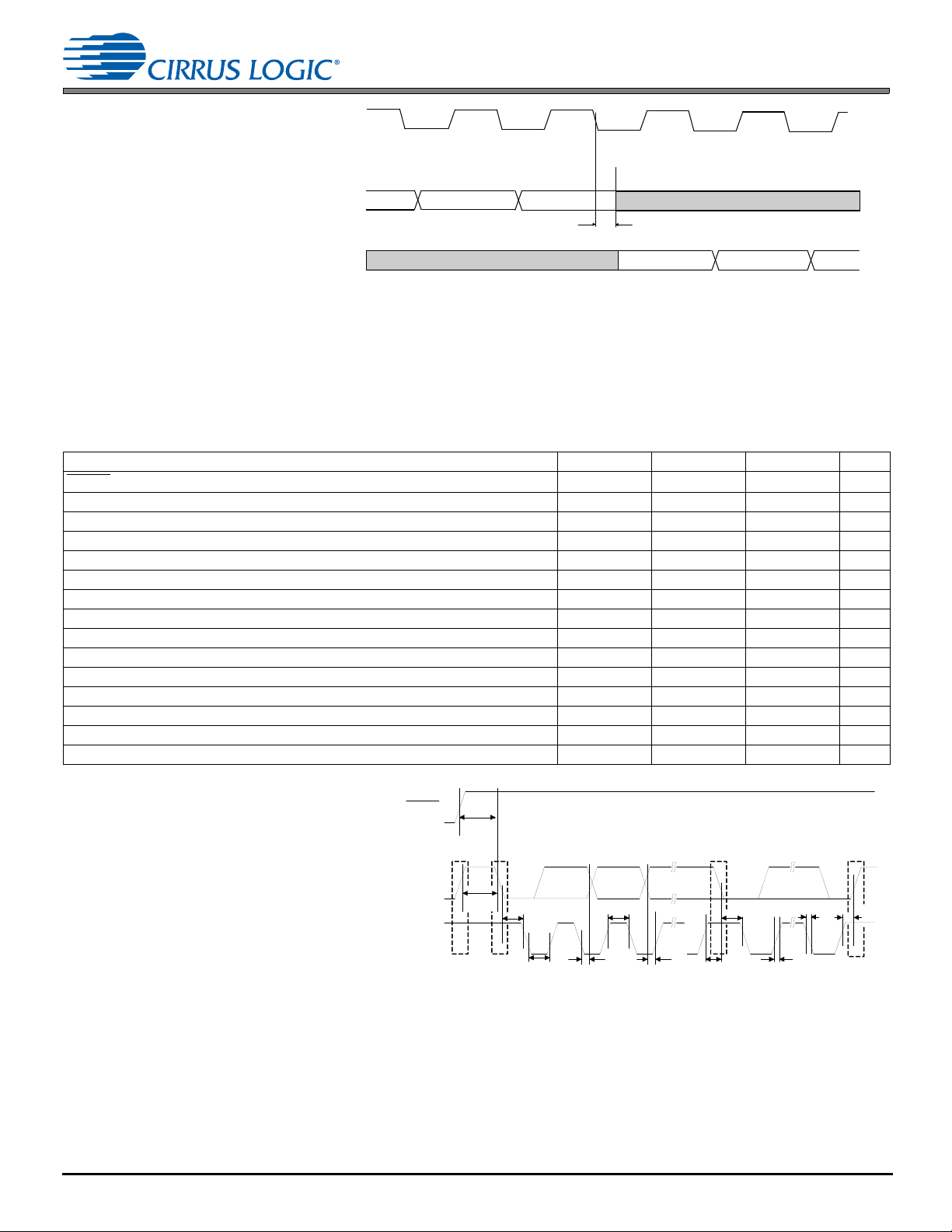

Table 3-10. Switching Specifications—Digital Mic Interface

Test conditions (unless specified otherwise): Fig. 2-1

parameters can vary with VA, typical performance data taken with VA = 1.8 V, VP = 3.6 V, min/max performance data taken with VA = 1.8V, VP = 3.6 V;

T

= +25°C; logic 0 = ground, logic 1 = VA; DMIC_DRIVE = 0 (normal); input timings are measured at VIL and VIH thresholds, and output timings are

A

measured at V

and VOH thresholds (see Table 3-14).

OL

Parameters

Output clock (DMICx_SCLK) frequency 1/t

DMICx_SCLK duty cycle

4

DMICx_SCLK rise time (10% to 90% of VA)

DMICx_SCLK fall time (90% to 10% of VA)

DMICx_SD setup time before DMICx_SCLK rising edge t

DMICx_SD hold time after DMICx_SCLK rising edge t

DMICx_SD setup time before DMICx_SCLK falling edge t

DMICx_SD hold time after DMICx_SCLK falling edge t

1.Digital mic interface timing

2.Oversampling rate of the digital mic must match the oversampling rate of the CS53L30 internal decimators.

3.The output clo ck frequency follows the internal MCLK rate divided by 2 or 4, as set in the ADCx/DMICx control registers (see DMIC1_SCLK_DIV on

p. 53 and DMIC2_SCLK_DIV on p. 55). DMICx_SCLK is further divided by up to a factor of 4 when MCLK_INT_SCALE is set (see p. 48). MCLK

source deviation from nominal supported rates is applied directly to the output clock rate by the same factor (e.g., a +100-ppm offset in the frequency

of MCLK becomes a +100-ppm offset of DMICx_SCLK.

4.Timing guaranteed with pull-up or pull-down resistor, with a minimum value 10 ktied to DMIC2_SCLK/AD1 for I2C address determination.

shows CS53L30 connections

1,2

4

4

; GNDA = GNDD = 0 V; voltages are with respect to ground;

Symbol Min Max Units

P

—3.2

[3]

—45 55%

t

r

t

f

s(SD-CLKR)

h(CLKR-SD)

s(SD-CLKF)

h(CLKF-SD)

—21ns

—13ns

10 — ns

4—ns

10 — ns

4—ns

MHz

Table 3-11. Specifications—I2S

Test conditions (unless specified otherwise): Fig. 2-1 shows CS53L30 connections; GNDA = GNDD = 0 V; all voltages are with respect to ground;

parameters can vary with VA; typical performance data taken with VA = 1.8 V, VP = 3.6 V; min/max performance data taken with VA = 1.8 V, VP = 3.6 V;

T

= +25°C; Test load for ASP_LRCK/FSYNC, ASP_SCLK, and ASP_SDOUTx CL = 60 pF; logic 0 = ground, logic 1 = VA; ASPx_DRIVE = 0; input

A

timings are measured at V

MCLK frequency — 1.024 19.2 MHz

MCLK duty cycle — 45 55 %

Slave mode Input sample rate (LRCK) Fs (See Table 4-2)kHz

LRCK duty cycle — 45 55 %

SCLK frequency 1/t

SCLK duty cycle — 45 55 %

SCLK rising edge to LRCK edge t

LRCK setup time before SCLK rising edge t

SDOUT setup time before SCLK rising edge t

SDOUT hold time after SCLK rising edge t

Master mode Output sample rate (LRCK) All speed modes Fs

LRCK duty cycle — 45 55 %

SCLK frequency 1/t

SCLK duty cycle — 33 67 %

LRCK time before SCLK falling edge t

SDOUT setup time before SCLK rising edge t

SDOUT hold time after SCLK rising edge t

1.Serial port

interface timing

and VIH thresholds, and output timings are measured at VOL and VOH thresholds (see Table 3-14).

IL

Parameters

1,2

Symbol Min Max Units

Ps

hs(LK-SK)

ss(LK-SK)

ss(SDO-SK)

hs(SK-SDO)

ext

Pm

sm(LK-SK)

sm(SDO-SK)

hm(SK-SDO)

— 64•Fs

10 — ns

40 — ns

20 — ns

30 — ns

(See Table 4-2)kHz

— 64•Fs

–2 +2 ns

20 — ns

30 — ns

ext

ext

Hz

Hz

2.MCLK must be stable before powering up the device. In Slave Mode, ASP_LRCK/FSYNC and ASP_SCLK must be stable before powering up the

device. Before making changes to any clock setting, the device must be powered down by setting either the PDN_ULP or PDN_LP bit.

14 DS992F1

Page 15

CS53L30

//

//

//

//

//

SLOT0:MSB

FSYNC (programmable

pulse width)

SCLK (SCLK_INV = 0)

SDOUT (SHIFT_LEFT = 0)

//

//

//

//

//

//

t

setup1

t

Fsync

t

CLK-Q1

SLOT0:MSB -1

//

//

//

SLOT0:MSB

SDOUT (SHIFT_LEFT = 1)

//

//

t

CLK-Q1

SLOT0:MSB -1

//

//

SLOT0:MSB -2

//

//

SCLK (SCLK_INV = 1)

//

//

//

//

//

SLOTx:LSB+1

SCLK

Device 0: SDOUT

t

HOLD2

SLOTx:LSB

SLOTx:MSB

Device 1: SDOUT

SLOTx:MSB -1

SLOTx:MSB -2

Output Not Driven (Hi-Z)

Output Not Driven (Hi-Z)

3 Characteristics and Specification s

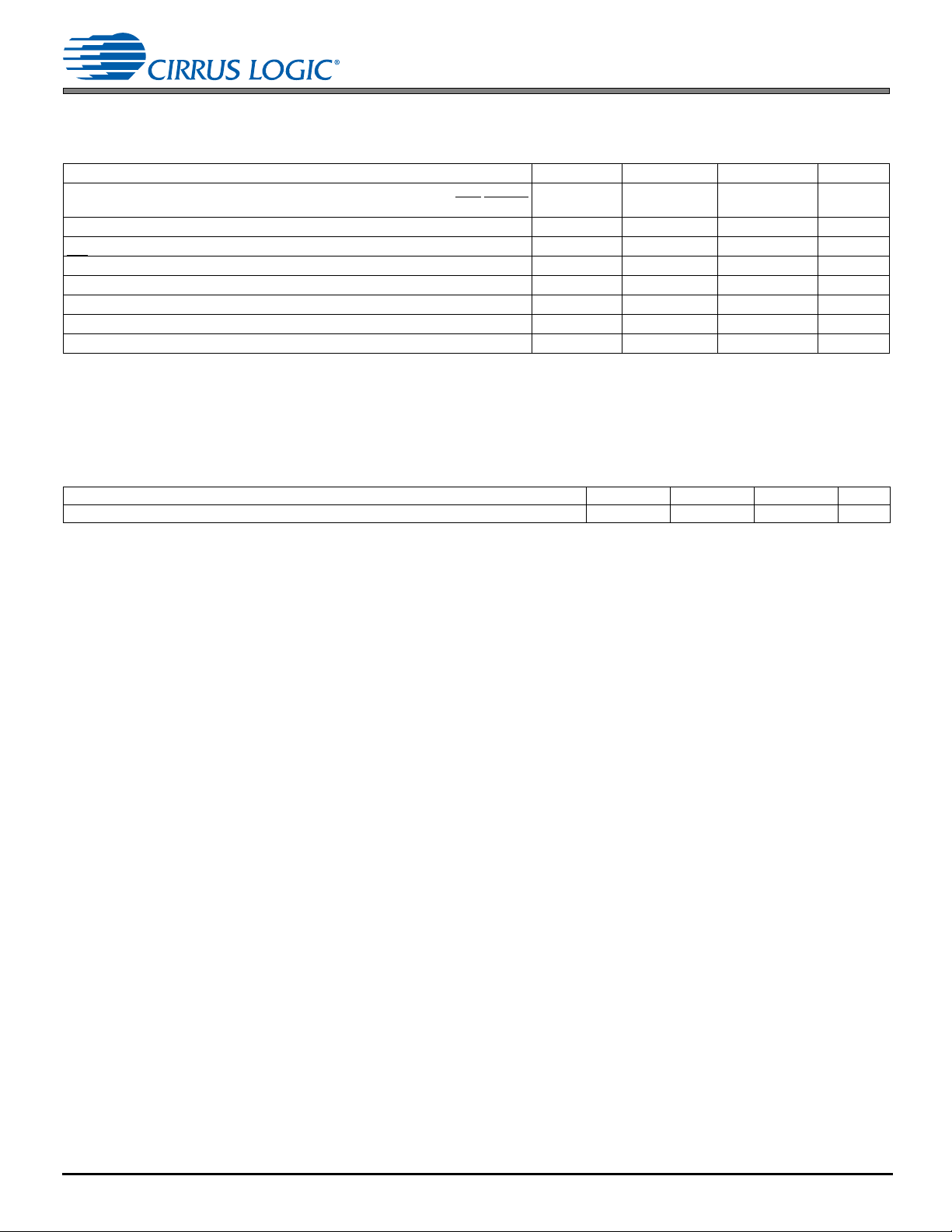

Table 3-12. Switching Specifications—Time-Division Multiplexed (TDM) Mode

Test conditions (unless specified otherwise): Fig. 2-1 shows CS53L30 connections; GNDA = GNDD = 0 V; all voltages are with respect to ground;

parameters can vary with VA; typical performance data taken with VA = 1.8 V, VP = 3.6 V; min/max performance data taken with VA = 1.8 V, VP = 3.6 V;

T

= +25°C; Test load for ASP_LRCK/FSYNC, ASP_SCLK, and ASP_SDOUT1 CL = 60 pF; logic 0 = ground, logic 1 = VA; ASPx_DRIVE = 0; input

A

timings are measured at V

MCLK frequency — 1.024 19.2 MHz

MCLK duty cycle —45 55 %

Slave mode Input sample rate (FSYNC)

FSYNC high time pulse

FSYNC setup time before SCLK rising edge t

SCLK frequency

SCLK duty cycle — 45 55 %

SDOUT delay time after SCLK rising edge

SDOUT hold time of LSB before transition to Hi-Z SHIFT_LEFT = 0

Master mode Output sample rate (FSYNC)

FSYNC high time pulse

FSYNC setup time before SCLK rising edge t

SCLK frequency f

SCLK duty cycle — 45 55 %

SDOUT delay time after SCLK rising edge SHIFT_LEFT = 0 t

SDOUT delay time after SCLK rising edge

SDOUT hold time of LSB before transition to Hi-Z SHIFT_LEFT = 0

1.Clock rates must be stable when the device is powered up and the serial port is not powered down. Therefore, the appropriate serial port must be

powered down before any clock rates are changed.

2.Maximum frequency for the highest supported nominal rate is indicated.

3.“n” refers to the total number of SCLKs in one FSYNC frame.

4.If MCLK_19MHZ_EN is set, the maximum SCLK frequency is 6.4 MHz. If SHIFT_LEFT is set, the maximum SCLK frequency is 6.4 MHz.

5.SCLK frequency must be high enough to provide the necessary SCLK cycles to capture all the serial audio port bits.

6.Single-device TDM timings

and VIH thresholds, and output timings are measured at VOL and VOH thresholds (see Table 3-14).

IL

Parameters Symbol Min Max Units

4,5

1,2

3

6

SHIFT_LEFT = 0 t

SHIFT_LEFT = 1 t

SHIFT_LEFT = 1

1

10

6

SHIFT_LEFT = 1 t

SHIFT_LEFT = 1

Fs

ext

t

FSYNC

SETUP1

f

SCLK

CLK-Q1

CLK-Q1

[7]

t

HOLD2

[8]

t

HOLD2

Fs

ext

t

FSYNC

SETUP1

SCLK

CLK-Q1

CLK-Q2

[7]

t

HOLD2

[8]

t

HOLD2

—48kHz

1/f

SCLK

20 — ns

—12.288MHz

—25ns

—45ns

10 30 ns

10 40 ns

—

1/f

SCLK

15 — ns

(See Table 4-3)MHz

—25ns

—45ns

10 30 ns

10 40 ns

Table 4-2 shows nominal MCLK rates and their associated configurations.

(n–1)/f

[9]

(n–1)/f

SCLK

SCLK

s

kHz

s

7.Hand-off timing for

multidevice systems

(SHIFT_LEFT = 0.

DS992F1 15

Page 16

CS53L30

SLOTx:LSB+1

SCLK

Device 0: SDOUT

t

HOLD2

SLOTx:LSB

SLOTx:MSB

SLOTx:MSB -1

SLOTx:MSB -2

Output Not Driven (Hi-Z)

Output Not Driven (Hi-Z)

t

buf

t

hdst

t

hdst

t

low

t

r

t

f

t

hdd

t

high

t

sud

t

sust

t

susp

Stop Start

Start

Stop

Repeated

SDA

SCL

t

irs

RESET

3 Characteristics and Specification s

8.Hand-off timing for multidevice

systems (SHIFT_LEFT = 1).

When SHIFT_LEFT = 1, it is

recommended to insert an empty

slot between devices on the

TDM bus to prevent contention

possibilities.

9.In Master Mode, the output sample rate follows the MCLK rate, per Section 4.6.5. MCLK deviations from the nominal supported rates are passed

directly to the output sample rate by the same factor (e.g., a +100 ppm offset in the frequency of MCLK becomes a +100 ppm offset in FSYNC).

10.“n” refers to number of SCLK cycles programmed in LRCK_TPWH[10:3] | LRCK_TPWH[2:0] (see p. 51) when

otherwise, t

has a 50% duty cycle.

FSYNC

Table 3-13. Switching Specifications—I2C Control Port

Test conditions (unless specified otherwise): Fig. 2-1

Parameters can vary with VA, typical performance data taken with VA = 1.8 V , VP = 3.6 V, min/max performance data taken with VA = 1.8V, VP = 3.6V;

T

= +25°C; logic 0 = ground, logic 1 = VA; input timings are measured at VIL and VIH thresholds, and output timings are measured at VOL and VOH

A

thresholds (see Table 3-14).

Parameter

rising edge to start

RESET

SCL clock frequency f

Start condition hold time (prior to first clock pulse) t

Clock low time t

Clock high time t

Setup time for repeated start condition t

SDA input hold time from SCL falling

3

SDA output hold time from SCL falling t

SDA setup time to SCL rising t

Rise time of SCL and SDA t

Fall time SCL and SDA t

Setup time for stop condition t

Bus free time between transmissions t

SDA bus capacitance C

SDA pull-up resistance R

1.All specifications are valid for the signals at the pins of the CS53L30 with the specified load capacitance.

2

2.I

C control port timing.

shows CS53L30 connections

1,2

; GNDA = GNDD = 0 V; all voltages are with respect to ground;

Symbol Min Max Unit

t

irs

scl

hdst

low

high

sust

t

hddi

hddo

sud

rc

fc

susp

buf

L

p

LRCK_50_NPW (see p. 51) is set;

500 — ns

— 550 kHz

0.6 — µs

1.3 — µs

0.6 — µs

0.6 — µs

00.9µs

0.2 0.9 µs

100 — ns

— 300 ns

— 300 ns

0.6 — µs

1.3 — µs

— 400 pF

500 —

3.Data must be held for sufficient time to bridge the transition time, tf, of SCL.

16 DS992F1

Page 17

CS53L30

3 Characteristics and Specification s

Table 3-14. Digital Interface Specifications and Charact eristics

Test conditions (unless specified otherwise): Fig. 2-1 shows CS53L30 connections; GNDA = GNDD = 0 V; all voltages are with respect to ground;

VA =1.8 V, VP = 3.6 V; T

Input leakage current

Internal weak pulldown — 550 2450 k

Input capacitance

current sink (VOL = 0.3 V max) — 825 — µA

INT

High-level output voltage

Low-level output voltage

High-level input voltage V

Low-level input voltage V

1.See Table 1-1 for serial and control port power rails.

2.Specification is per pin. Includes current through internal pull-down resistors on serial port.

3.IOH = –100 µA for x_DRIVE = 0; IOH = –67 µA for x_DRIVE = 1

4.IOL = 100 µA for x_DRIVE = 0; IOL = 67 µA for x_DRIVE = 1

Table 3-15. Thermal Overload Detection Characteristics

Test conditions (unless otherwise specified): GNDA = GNDD = 0; all voltages are with respect to ground; VA = 1.8 V, VP = 3.6 V.

Thermal overload detection threshold — 150 —

2

= +25°C

A

2

3

4

Parameters

MCLK, SYNC, MUTE, all serial port inputs

1

All control port inputs, INT,

RESET

Symbol Min Max Units

I

in

—

—

±4000

±100

—— 10pF

V

OH

V

OL

IH

IL

VA – 0.2 — V

—0.2V

0.70•VA — V

—0.30•VAV

Parameters Min Typ Max Units

nA

nA

C

DS992F1 17

Page 18

CS53L30

CS53L30

Digital Processing

Control

Port

Level Shifters

MIC1_BIAS

Serial Port

MIC2_BIAS

VP

MCLK

DMIC1_SCLK

MIC3_BIAS

MIC4_BIAS

–6 to +12 dB,

0.5 dB st eps

+10 or +20 dB

ADC1B

–

+

–

+

Decimators

–6 to +12 dB,

0.5 dB st eps

+10 or +20 dB

–

+

–

+

Decimators

MIC1 B i as

MIC2 B i as

MIC3 B i as

MIC4 B i as

HPF , No i se

Gate, Volum e,

Mute

Audio

Serial Port

Control Port

RESET

MCLK_INT

Clock Divider

Synchronizer

DMIC

ADC1A

ADC2B

ADC2A

–

+

–

+

LDO

VA

VD

2

2

4

MCLK_INT

MCLK_INT

HPF , No i se

Gate, Volum e,

Mute

SYNC

MUTE

Synchronous

SRC

IN2–

IN1–

IN2+

IN4–

IN3–

IN4+

DMIC2_SCLK

See Section 4.4.

See

Section 4.9.

See Section4.5.

See Section4.6.

See

Section4.8.

See Section4.14.

See Section 4.12.

See Section 4.2.

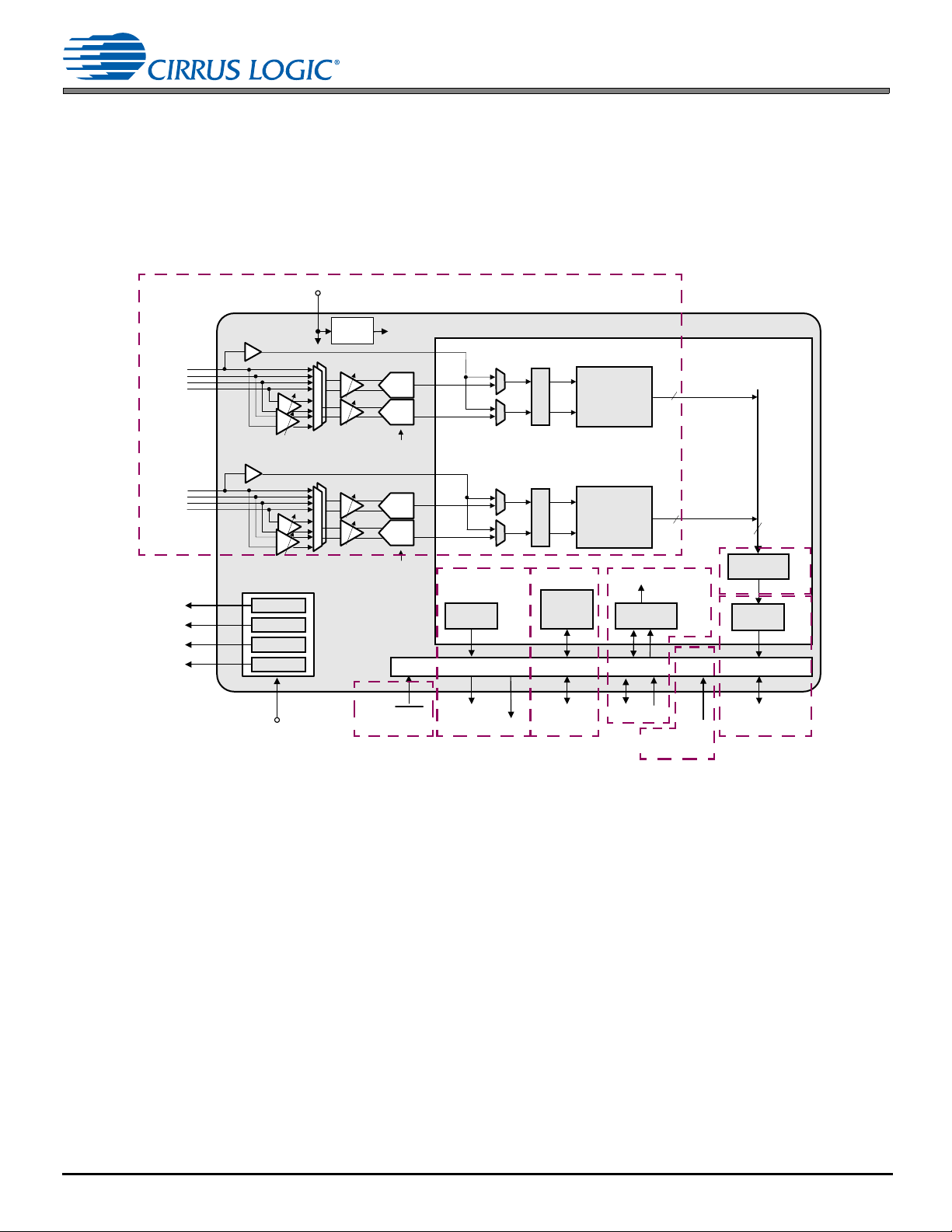

4 Functional Description

4 Functional Description

This section provides a general description of the CS53L30 architecture and detailed functional descriptions of the various

blocks that comprise the CS53L30.

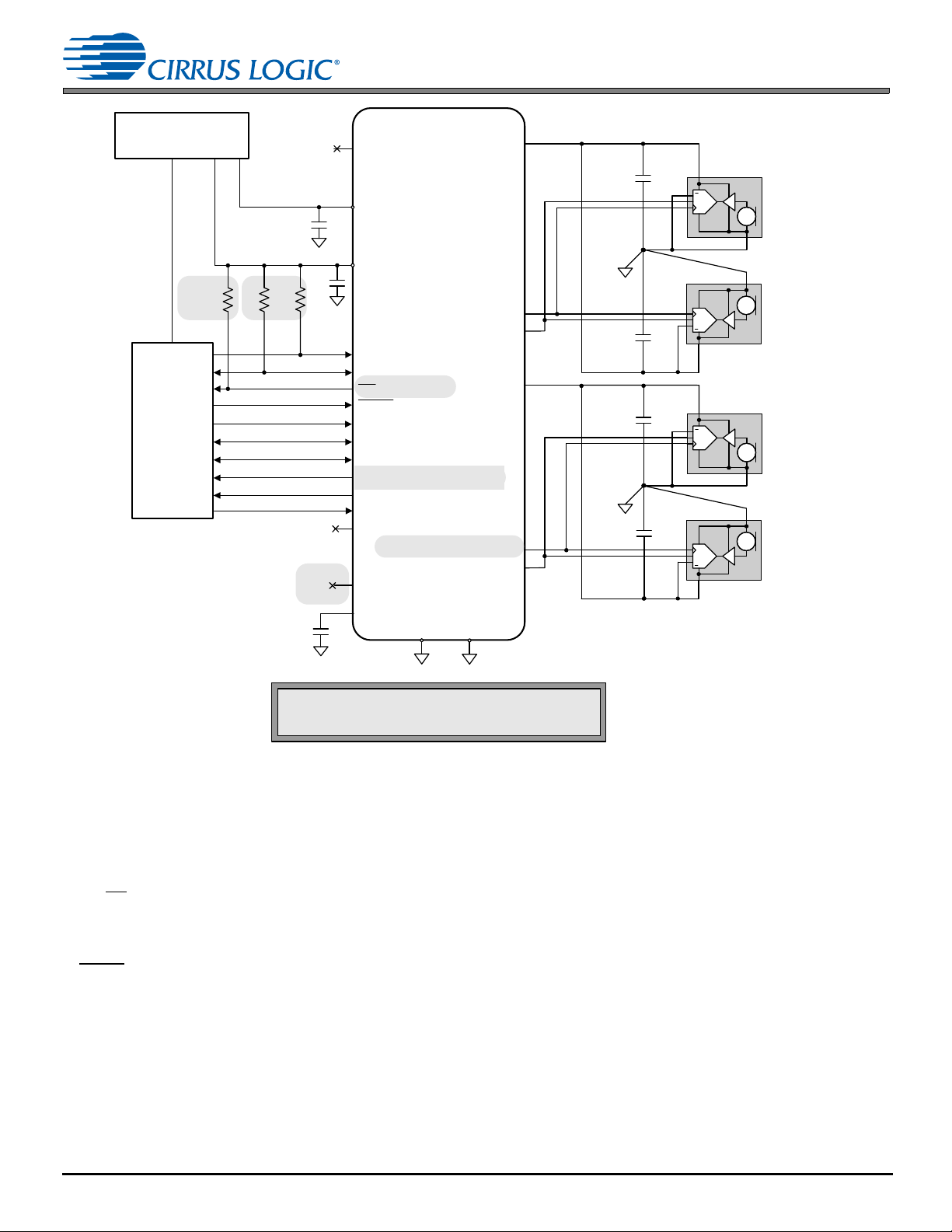

4.1 Overview

Fig. 4-1 is a block diagram of the CS53L30 with links to descriptions of major subblocks.

Figure 4-1. Overview of Signal Flow

The CS53L30 is a low-power, four-channel, 24-bit audio ADC. The ADCs are fed by fully differential analog inputs that

support mic and line-level input signals. The ADCs are designed usin g multibit delta-sigma techniques. The ADCs operate

at an optimal oversampling ratio balancing performance with power saving s. Enhanced power savings are possible when

the internal MCLK is scaled by setting MCLK_INT_SCALE (see p. 45). Table 4-2 lists supported sample rates with scaled

internal MCLK.

The serial data port operates at a selectable range of stan dard audio samp le rates as either timing master or slave. Core

timing is flexibly sourced, without the need of a PLL, by clocks with typical audio clock rates (N x 5.6448, or N x 6.1440

MHz; where N = 1 or 2), USB rates (6 or 12 MHz), or 3G and DVB rates (19.2 MHz).

The integrated LDO regulator allows the digital core to ope rate at a very low voltage , significantly reducing the CS53L30’s

overall power consumption.

The CS53L30 can operate in a system with multiple CS53L30s to increase the number of channels available. The

CS53L30s may be connected in a multidrop configuration in TDM Mode. Up to four CS53L30s can operate sim ultaneously

on the same TDM bus. Connecting together the SYNC pins of multiple CS53L30s allows operation with minimal

channel-to-channel phase mismatch across devices.

The signal to be converted can be either mic/line-level. The digital mic inputs (IN1+/DMIC1_SD, IN3+/DMIC2_SD) connect

directly to the decimators.

18 DS992F1

Page 19

The CS53L30 consists of the following blocks:

CS53L30

4.2 Resets

• Interrupts. The CS53L30 QFN package includes an open-drain, active-low interrupt output, INT

describes interrupts.

• Capture-path inputs. The analog input block, described in Section 4.4, allows selection from either analog line-level,

or analog mic sources. The selected analog source is fed into a mic preamplifier (whe n applicable ) and then into a

PGA, before entering the ADC. The pseudodifferential input configuration can provide noise rejection for

single-ended analog inputs. The digital mic inputs (IN1+/DMIC1_SD, IN3+/DMIC2_SD) connect directly to the

decimators.

• Serial ports. The CS53L30 has either two I

devices in the system such as applications processors. The serial data ports are described in Section 4.6.1. The

TDM port allows multidrop operation (i.e., tristate capable SDOUT driver) for sharing the TDM bus between multiple

devices, and flexible data structuring via control port registers.

• Synchronous sample rate converter (SRC). The SRC, described in Section 4.8, is used to bridge different sample

rates at the serial port within the digital-processing core.

• Multichip synchronization protocol. Some applications require more than four simultaneous audio channels

requiring multiple CS53L30s. In a subset of these multidevice applications, special attention to phase alignment of

audio channels is required. The CS53L30 has a synchro nization pr otocol to align all a udio chan nels a nd mi nimize

interchannel phase mismatch. Section 4.9 describes the synchronization protocol.

• Thermal overload notification. The CS53L30 can be configured to notify the system processor that its die

temperature is too high. This functionality is described in Section 4.11.

• Mute pin. The CS53L30 audio outputs can be muted with the assertion of the register-programmable MUTE pin.

The MUTE pin function can also be programmed to power-down ADCs, MICx_BIAS, etc., by setting the appropriate

bits in Section 7.17 and Section 7.18. Section 4.12 describes the MUTE pin functionality.

• Power management. Several registers provide independent powe r-down control of the analog and digital sections

of the CS53L30, allowing operation in select applications with minimal power consumption. Power management

considerations are described in Section 4.13.

• Control port operation. The control port is used to access the registers allowing the CS53L30 to be configured for

the desired operational modes and formats. The oper ation of the control port may be completely asynchronous with

respect to the audio sample rates. To avoid interference problems, the control port pins must remain static if no

operation is required. Control port operation is described in Section 4.14.

2

S output ports or one TDM output port allowing communication to other

. Section 4.3

4.2 Resets

The CS53L30 can be reset only by asserting RESET. When RESET is asserted, all registers and all state machines are

immediately set to their default values/states. No operation can begin until RESET

can begin, RESET

before the VA supply.

must be asserted at least once after the VA supply is broug ht up. The VP supply should be brought u p

is deasserted. Before normal operation

4.3 Interrupts

The status of events that may require special attention is recorded in the interrupt status register (see Section 7.36).

Interrupt status bits are sticky and read-to-clear: That is, once set, they remain set until the status register is read and the

associated interrupt condition is no longer present.

4.3.1 Interrupt Handling with the WLCSP Package

If the WLCSP package is used, events and conditions are detected in software by polling the interrupt status register. The

mask register can be ignored (see Section 7.35). Status register bits are cleared when read, as Fig. 4-2 shows. If the

underlying condition remains valid, the bit remains set even after the status register is read.

DS992F1 19

Page 20

CS53L30

Raw signal feeding

st atus re gi ster bi t

Stat us regis t er bi t

___

INT pin

Register read

signal

Stat us read val ue

0 110 10

Read Sourc e

10

Poll cycle

Interrupt

service

Extra read for

pre s ent state

Interrupt

service

Extra read for

pre s ent state

Poll cycle

Extra read for

pre s ent state

Poll cycle

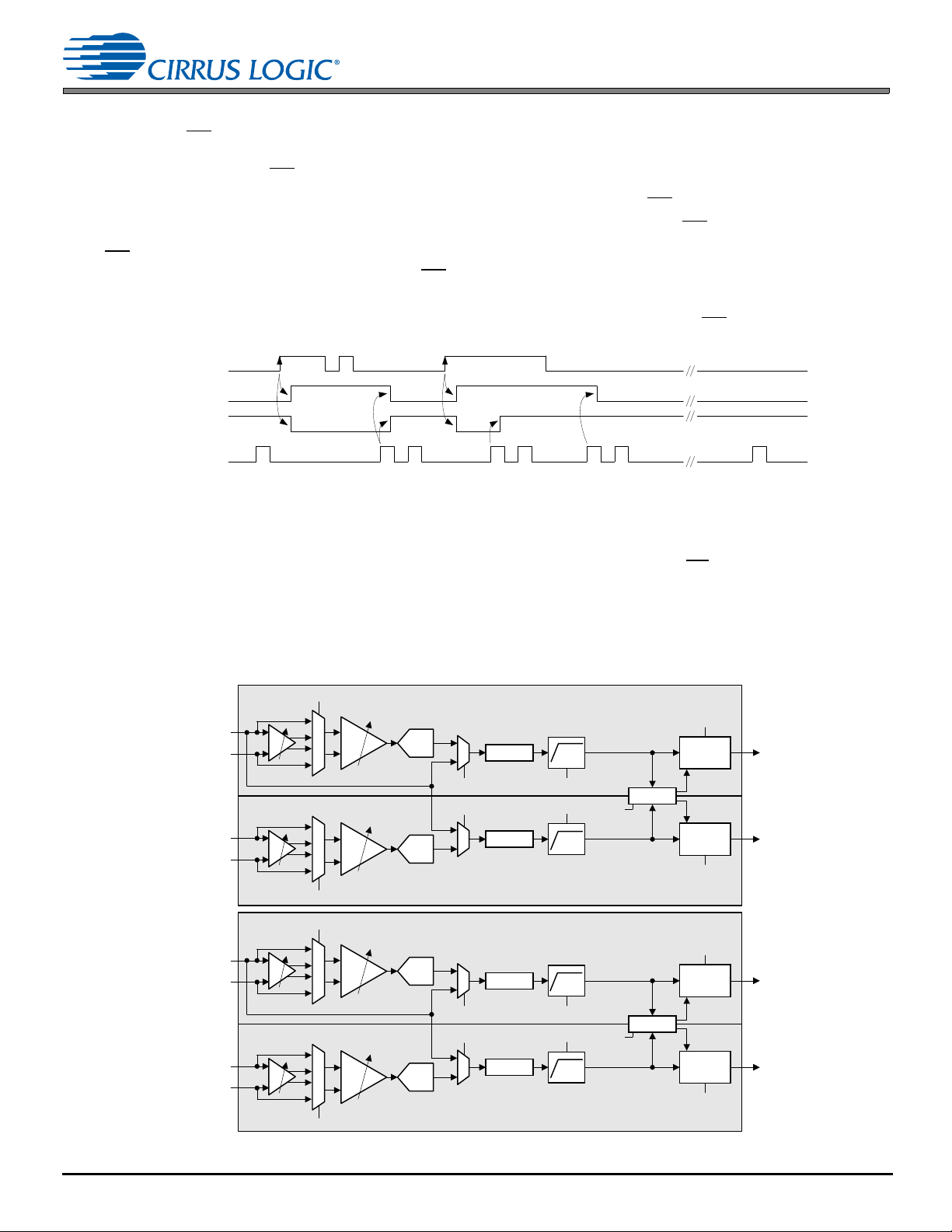

Channel 2B Data Path

Channel 2A Data Path

Channel 1B Data Path

Channel 1A Data Path

PGA

Decimator

PGA

Decimator

Digital Gain

Adjust

HPF

ADC1A

ADC1B

Digital Gain

Adjust

HPF

Noise Gate To Serial Port

PGA

Decimator

PGA

Decimator

Digital Gain

Adjust

HPF

ADC2A

ADC2B

Digital Gain

Adjust

HPF

Noise Gate To Serial Port

IN1 +/DMIC1_SD

IN 2 –

IN 1 –

IN2+

IN3 +/DMIC3_SD

IN4–

IN 3 –

IN4+

ADC1x_VOL

ADC1x_PGA_VOL

CH_TYPE

ADC1_HPF_EN

ADC1x_VOL

ADC1x_PREAMP

ADC1x_PREAMP

ADC2x_VOL

ADC2x_PGA_VOL

ADC2_HPF_EN

ADC2x_PGA_VOL

ADC2x_VOL

ADC2x_PREAMP

ADC2x_PREAMP

ADC1x_NG

ADC2x_NG

ADC1_HPF_EN

ADC1x_PGA_VOL

ADC2_HPF_EN

CH_TYPE

CH_TYPE

CH_TYPE

4.4 Capture-Path Inputs

4.3.2 Interrupt Handling with the QFN Package

The interrupt pin (INT) is implemented on the QFN package. Interrupt status bits can be individually masked by setting

corresponding bits in the interrupt mask register (see Section 7.35). The configuration of mask bits determines which

events cause the assertion of INT

:

• When an unmasked interrupt status event is detected, the status bit is set and INT

• When a masked interrupt status event is detected, the interrupt status bit is set, but INT

Once INT

remains present and the status bit is read, alth ou gh IN T

is asserted, it remains asserted until all status bits that are unmasked and set have been read. If a condition

is deasserted, the status bit remains set.

is asserted.

is not affected.

To clear any status bits set due to the initiation of a path or block, all interrupt status bits should be read after reset and

before normal operation begins. Otherwise, unmasking any previously set status bits causes INT

Figure 4-2. Example of Rising-Edge Sensitive, Sticky, Interru pt Status Bit Behavior (INT Pin in QFN only)

to assert.

4.4 Capture-Path Inputs

This section describes the line in and mic inputs. Fig. 4-3 shows the capture-path signal flow.

20 DS992F1

Figure 4-3. Capture-Path Signal Flow

Page 21

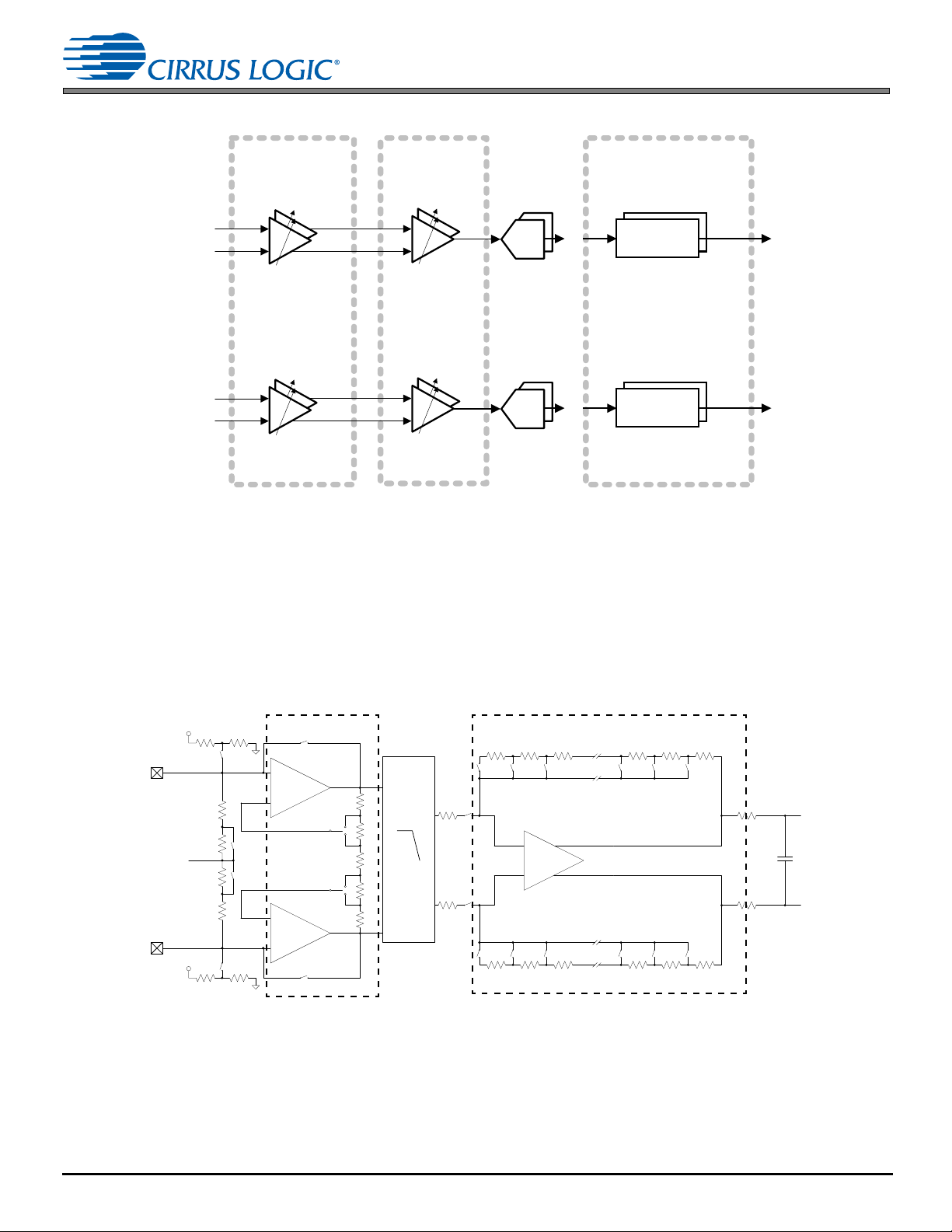

Fig. 4-4 shows details of the various analog input gain settings, including control register fields.

–6 to +12 dB

with 0.5-dB

steps

Bypas s, +10,

or +20 dB

0 or +20 dB

and/or

–96 to +12 dB

with 1-dB steps or

– dB (mute)

INx±,

(x=1,2)

Gain Adjust

Digital Gain

Adjust

ADC1xPGA

...

(Note 1)

(Note 1)

Bypas s, +10,

or +20 dB

INx±,

(x=3,4)

Gain AdjustDigital Gain

Adjust

ADC2xPGA

...

(Note 1)

(Note 1)

1. Gains within analog blocks vary with supply voltage, with temperat ure, and from part t o part. The gain val ues listed for these b locks

are typical values with nominal parts and conditions.

ADC1x_PREAMP

on p. 54

ADC1x_DIG_BOOST on p. 53

ADC1x_VOL on p. 54

ADC2x_PGA_VOL

on p. 56

ADC2x_PREAMP

on p. 56

ADC1x_PGA_VOL

on p. 54

ADC2x_DIG_BOOST on p. 55

ADC2x_VOL on p. 56

+

–

Preamp+

+

–

Preamp–

INx–

INx+

100 k

900 k

900 k

100 k

QuickRef

700 k 700 k

VA

Weak-VCM

700 k 700 k

Weak-VCM

VA

VCM

+

–

PGA

ADCx+

ADCx–

ADC1x_PGA_VOL

ADC2x_PGA_VOL

ADC1x_PREAMP

ADC2x_PREAMP

CS53L30

4.4 Capture-Path Inputs

Figure 4-4. Input Gain Paths

4.4.1 Analog Input Configurations

The CS53L30 implements fully differential analog input stages, as shown in Fig. 4-5. In addition to accepting fully

differential input signals, the inputs can be used in a pseudodifferential configuration to improve common mode noise

rejection with single-ended signals. In this configuration, a low-level referen ce signal is sensed at the ground point of the

internal mic or external mic jack and used as a pseudodifferential reference for the internal input amplifiers. Sitting between

the preamp and the PGA is an internal antialias filter with a first-order pole at 95 kHz and a first-order pole at 285 kHz.

Fig. 4-6 shows the INx interface and the related connections recommended for a fully differential internal mic. These

connections are truncated in Fig. 4-6.

Figure 4-5. Op-Amp Level Schematic—Analog Inputs

DS992F1 21

Page 22

CS53L30

Board Chip

MIC_BIAS_FILT

VP

IN1–

MIC1_BIAS

IN1+

CINM

CINM

Analog

Differential

Microphone

1.0 µF

4.7 µF

GNDA

n

Board Chip

GNDA

MIC_BIAS_FILT

VP

IN1+

IN1–

MIC1_BIAS

CINM

CINM

1.0 µF

4.7 µF

CINM

CINM

1.0 µF

CINM

CINM

1.0 µF

CINM

CINM

1.0 µF

IN2+

IN2–

MIC2_BIAS

IN3+

IN3–

MIC3_BIAS

IN4+

IN4–

MIC4_BIAS

Board ground connection made

local to the micr ophone car tridge.

Board ground connection made

local to the micr ophone car tridge.

Board ground connection made

local to the micr ophone car tridge.

Board ground connect ion made

local to the micr ophone c ar tridge.

Analog

Microphone

(see

connection

diagram)

Analog

Microphone

(see

connection

diagram)

Analog

Microphone

(see

connection

diagram)

Analog

Microphone

(see

connection

diagram)

Analog Microphone Connection

Two-wire microphone connection

Rbias

Gr ound Ring

MICx_BIAS

INx+

INx–

Three-wire microphone connection

Gr ound Ring

MICx_BIAS

INx+

INx–

4.4 Capture-Path Inputs

Figure 4-6. Fully Differential Mic Input Connections Example

Fig. 4-7 shows the IN1–IN4 interfaces and the related pseudodifferential connections recommended to achieve the best

common-mode rejection for single-ended internal mics.

22 DS992F1

Figure 4-7. Pseudodifferential Mic Input Connections Example

Page 23

CS53L30

f

c

1

2 1 M0.01 F

------------------------------------------------------ 15.9 H z==

f

c

1

2 50 k 0.1 F

---------------------------------------------------- 31.83 H z==

4.5 Digital Microphone (DMIC) Interface

4.4.2 External Coupling Capacitors

The analog inputs are internally biased to the internally generated common-mode voltage (VCM). Input signals must be

AC coupled using external capacitors (C

resistance may be combined with an external capacitor to achieve the desired cutoff frequency.

Eq. 4-1 provides an example for mic inputs.

Equation 4-1. External Coupling Capacitors—Mic Inputs

Eq. 4-2 provides an example for line inputs.

Equation 4-2. External Coupling Capacitors—Line Inputs

4.4.3 Capture-Path Pin Biasing

Capture-path pins are internally biased during normal operation. When connecting analog sources to the CS53L30, the

input must be AC-coupled with an external capacitor. These sources may bias the analog inputs:

• Quick-Ref. After an analog input is powered up, the Quick-Ref buffer charges the external capacitor with a

low-impedance bias source to minimize startup time.