Page 1

CS4953xx

32-bit Audio DSP Family

CS4953xx

Hardware User ’s Manual

Preliminary Product Information

http://www.cirrus.com

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

Copyright 2010 Cirrus Logic, Inc. FEB ’10

DS732UM10

Page 2

CS4953xx Hardware User’s Manual

Contacting Cirrus Logic Support

For all product questions and inquiries contact a Cirrus Logic Sales Representative.

To find the one nearest to you go to www.cirrus.com

I

MPORTANT NOTICE

“Preliminary” product information describes products that are in production, but for which full characterization data is not yet availabl e.

Cirrus Logic, Inc. and its sub si di ari es ( “Ci rrus”) believe that the inf ormat i on co nt ained in this document is accurate and reliable. However, the information

is subject to change without not ice and is provi ded “AS IS” wi thout warranty of an y kind (exp ress or implied). Customer s are advised to obtain the latest

version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the

terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability.

No responsibility is assu me d by C irrus for the u se of this inf ormati on, includ ing use o f this info rmat ion as the b asis for ma nufacture or sale of any items, or

for infringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license,

express or implied under any patents, mask work rights, copyrights, tradem arks, trade secrets or othe r intellectual proper ty ri g hts. Cir rus owns the copyrights associated with the informati on contained herein and gives consent for copies to be made of the in formation only for use within your organi zation

with respect to Cirrus integrated circuits or other products of Cirrus. This consent does not extend to other copying such as copying for general distribution,

advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICO NDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE

PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN PRODUCTS SURGICAL L Y IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT

PRODUCTS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCT S IN SUCH APPLICATIONS IS UND ERSTOOD TO BE FULLY

AT THE CUSTOMER'S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS

USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOM ER AGRE ES, BY SUCH USE, TO FULLY INDEMN IFY CIRRUS, ITS OF FICERS, DIRECTORS , EMPLOYE ES, DISTRIBUTORS AND OTHER AGENTS F ROM ANY AND A LL LIABILITY, INCLUDING ATTORNEYS ' FEES AND COS TS, THAT MAY RESU LT FROM OR ARISE

IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, the Cirrus Logic logo designs, DSP Composer, Cirrus Extra Surround, Cirrus Original Multichannel Surround, and Cirrus Original Surround are trademarks of Ci rrus Logi c, Inc. Al l other b rand and pr oduct names i n this d ocument may be trademarks o r service ma rks of their r espective

owners.

Dolby, Dolby Digital, Dolby Head phone, Dolby Virt ual Speaker, AC-3, and Pro Logic are registered trademarks of Dolby Laboratories, Inc. AAC, Dolby

Headphone2, Dolby Virtual Speaker2, and Dolby Digital Surround EX are trademarks of Dolby Laboratori es, Inc. Supply of an implem entation o f Dolby

technology does not convey a license nor imply a ri ght un der any pa t ent, or any ot her i ndu st ri al or i nt ell ect u al prope rt y ri ght of Dol by Lab oratories, to use

the implementation in any finished end-user or ready-to-use final product. It is hereby notified that a license for such use is required from Dolby Laboratories.

DTS and DTS Digital Surround are registered trademarks of the Digital Theater Systems, Inc. DTS-ES, DTS-ES 96/24, DTS Neo:6, DTS 96/24 are trademarks of the Digital Theater Systems, Inc. It is hereby notified that a third-party license from DTS is necessary to distribute software of DTS in any finished

end-user or ready-to-use final product.

®

is a registered trademark of THX Ltd. THx Ultra2 and THx Select2 are trademarks of THx Ltd.

THX

Re-equalization is a trademark of Lucasfilm, Ltd.

SRS, Circle Surround, and Trusur round XT are regist ered trade marks of SRS Labs, Inc. Circle Surround II is a trad emark of SRS Labs, Inc. The Ci rcle

Surround technology rights in corporated in the Cirrus Logic chi p are owned by SRS Labs, I nc. and by Valence Techn ology, Ltd. , and licensed t o Cirrus

Logic, Inc.

Users of any Cirrus Logic chip containing enabled Circle Surround

duction quantities for consumer electronics applications which may be granted upon submission of a preproduction sample to, and the satisfactory passing

of performance verification tests performed by SRS Labs, Inc., or Valence Technology, Ltd. E-mail requests for performance specifications and testing rate

schedule may be made to cslicense@srslabs.com. SRS Labs, Inc. an d Valence Tech nolog y, Ltd., reserve the right t o declin e a use li cense for any submission that does not pass performance specifications or is not in the consumer electronics classification.

All equipment manufactured using any Cirrus Logic chip containing enabled Circle Surround

panel in a manner approved in writing by SRS Labs, Inc., or Valence Technology, Ltd. If the Circle Surround logo is printed in user manuals, service manuals, or advertisements, it must appear in a form approved in writing by SRS Labs, Inc. or Valence Technology, Ltd. The rear panel of products containing

Circle Surround technol ogy and user manuals, service manuals, and advertising for those products must al l carry the legends as described i n Licensor’s

most current version of the Circle Surround Trademark Usage Manual.

Intel is a registered trademark of Intel Corporation.

Motorola and SPI are trademarks or registered trademarks of Motorola, Inc.

2

C is a trademark of Philips Semiconductor Corp.

I

Philips is a registered trademark of Koninkl ijk e Philips Electronics N.V. C o rp.

Sony and Direct Stream Digital are registered trademark of Sony Kabushiki Kaisha T.A. Sony Corporation.

®

technology (i.e., Circle Surround® licensees) must first sign a license to purchase pro-

®

technology must carry the Circle Surround® logo on the front

DS732UM10 Copyright 2010 Cirrus Logic, Inc. ii

Page 3

Contents

CS4953xx Hardware User’s Manual

Contents

Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .iii

Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . v

Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . vii

Chapter 1. Introduction.........................................................................................1-1

1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-1

1.1.1 Chip Features.................................................................................................................1-1

1.2 Functional Overview of the CS4953xx Chip . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-3

1.2.1 DSP Core .......................................................................................................................1-3

1.2.2 Security Extension module................... ....... ...... ...... ....... ...... ..........................................1-3

1.2.3 Debug Controller (DBC) .................................................................................................1-3

1.2.4 Digital Audio Output (DAO1, DAO2) Controller ..............................................................1-3

1.2.5 Digital Audio Input (DAI1) Controller ..............................................................................1-3

1.2.6 Compressed Data Input / Digital Audio Input (DAI2) Controller .....................................1-4

1.2.7 Direct Stream Digital

1.2.8 General Purpose I/O.......................................................................................................1-4

1.2.9 Parallel Control Port (Motorola

1.2.10 Serial Control Ports (SPI

1.2.11 SDRAM Controller........................................................................................................1-5

1.2.12 Flash Controller ............................................................................................................1-5

1.2.13 DMA Controller.............................................................................................................1-5

1.2.14 Timers...........................................................................................................................1-5

1.2.15 Clock Manager and PLL...............................................................................................1-6

1.2.16 Programmable Interrupt Controller...............................................................................1-6

®

(DSD) Controller.........................................................................1-4

®

/Intel® Standards) (Optional Feature).........................1-4

™

or I2C™ Standards)............................................................1-4

Chapter 2. Operational Modes..............................................................................2-1

2.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

2.2 Operational Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.3 Slave Boot Procedures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

2.3.1 Host Controlled Master Boot ..........................................................................................2-4

2.3.1.1 Performing a Host Controlled Master Boot (HCMB)......................................2-5

2.3.2 Slave Boot ......................................................................................................................2-7

2.3.2.1 Performing a Slave Boot................................................................................2-8

2.3.3 Boot Messages.............................................................................................................2-10

2.3.3.1 Slave Boot ..................................................................................................2-10

2.3.3.2 Host-Controlled Master Boot from Parallel ROMthe....................................2-10

2.3.3.3 Host-Controlled Master Boot from I

2.3.3.4 Host-Controlled Master Boot from SPI ROM...............................................2-11

2.3.3.5 Soft Reset ...................................................................................................2-12

2.3.3.6 Messages Read from CS4953xx.................................................................2-12

2.4 Master Boot Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13

2.5 Softboot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

2.5.1 Softboot Messaging......................................................................................................2-14

2.5.2 Softboot Procedure.......................................................................................................2-15

2.5.2.1 Softboot Procedure......................................................................................2-15

2.5.2.2 Softboot Example ........................................................................................2-16

2.5.2.3 Softboot Example Steps ..............................................................................2-17

2

C ROM................................................2-11

Chapter 3. Serial Control Port ..............................................................................3-1

3.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-1

DS732UM10 Copyright 2010 Cirrus Logic, Inc. iii

Page 4

Contents

CS4953xx Hardware User’s Manual

3.2 Serial Control Port Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-1

2

C Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-2

3.3 I

3.3.1 I

3.3.2 I

3.3.3 I

2

C System Bus Description...........................................................................................3-2

2

C Bus Dynamics ..........................................................................................................3-4

2

C Messaging................................................................................................................3-7

3.3.3.1 SCP1_BSY

3.3.3.2 Performing a Serial I

3.3.3.3 I

3.3.3.4 Performing a Serial I

3.3.3.5 I

3.3.3.6 SCP1_IRQ

3.4 SPI Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-13

3.4.1 SPI System Bus Description.........................................................................................3-15

3.4.2 SPI Bus Dynamics........................................................................................................3-15

3.4.2.1 SCP1_BSY

3.4.3 SPI Messaging .............................................................................................................3-16

3.4.3.1 Performing a Serial SPI Write......................................................................3-17

3.4.3.2 SPI Write Protocol .......................................................................................3-17

3.4.3.3 Performing a Serial SPI Read......................................................................3-18

3.4.3.4 SPI Read Protocol.......................................................................................3-19

3.4.3.5 SCP1_IRQ

Behavior.....................................................................................3-7

2

2

C Write Protocol..........................................................................................3-9

2

C Read Procedure ....................................................................................3-11

C Write ........................................................................3-8

2

C Read ........................................................................3-9

Behavior....................................................................................3-13

Behavior...................................................................................3-16

Behavior....................................................................................3-21

Chapter 4. Parallel Control Port ...........................................................................4-1

4.1 Parallel Control Availability. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

Chapter 5. Digital Audio Input Interface..............................................................5-1

5.1 Digital Audio Input Port Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-1

5.1.1 DAI Pin Description ................. ....... ...... ....... ...... ...... .............................................. .........5-1

5.1.2 Supported DAI Functional Blocks...................................................................................5-2

5.1.3 BDI Port... ...... ....... ...... ............................................. ....... ................................................5-3

5.1.4 Digital Audio Formats.....................................................................................................5-4

2

5.1.4.1 I

S Format .....................................................................................................5-4

5.1.4.2 Left-Justified Format......................................................................................5-5

5.2 DAI Hardware Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-5

5.2.1 DAI Hardware Naming Convention ................................................................................5-5

Chapter 6. Direct Stream Data (DSD) Input Interface.........................................6-1

6.1 Description of Digital Audio Input Port when Configured for DSD Input . . . . . . . . . . . . . . .6-1

6.1.1 DSD Pin Description................ ....... ...... ....... ...... ...... ....... ...... ....... ...... ....... ......................6-1

6.1.2 Supported DSD Functional Blocks .................................................................................6-1

Chapter 7. Digital Audio Output Interface...........................................................7-1

7.1 Digital Audio Output Port Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-1

7.1.1 DAO Pin Description.......................................................................................................7-1

7.1.2 Supported DAO Functional Blocks.................................................................................7-3

7.1.3 DAO Interface Formats...................................................................................................7-3

7.1.3.1 I

7.1.3.2 Left-Justified Format......................................................................................7-3

7.1.3.3 One-line Data Mode Format (Multichannel)...................................................7-4

7.1.4 DAO Hardware Configuration.........................................................................................7-4

7.1.5 S/PDIF Transmitter.......................................................................................................7-11

2

S Format .....................................................................................................7-3

iv Copyright 2010 Cirrus Logic, Inc. DS732UM10

Page 5

Figures

CS4953xx Hardware User’s Manual

Chapter 8. External Memory Interfaces...............................................................8-1

8.1 SDRAM Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-1

8.2 Flash Memory Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-2

8.2.1 Flash Controller Interface...............................................................................................8-2

8.3 SDRAM/Flash Controller Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-2

8.3.1 SDRAM/Flash Interface Signals.....................................................................................8-2

8.3.2 Configuring SDRAM/Flash Parameters............................................. ....... ...... ................8- 4

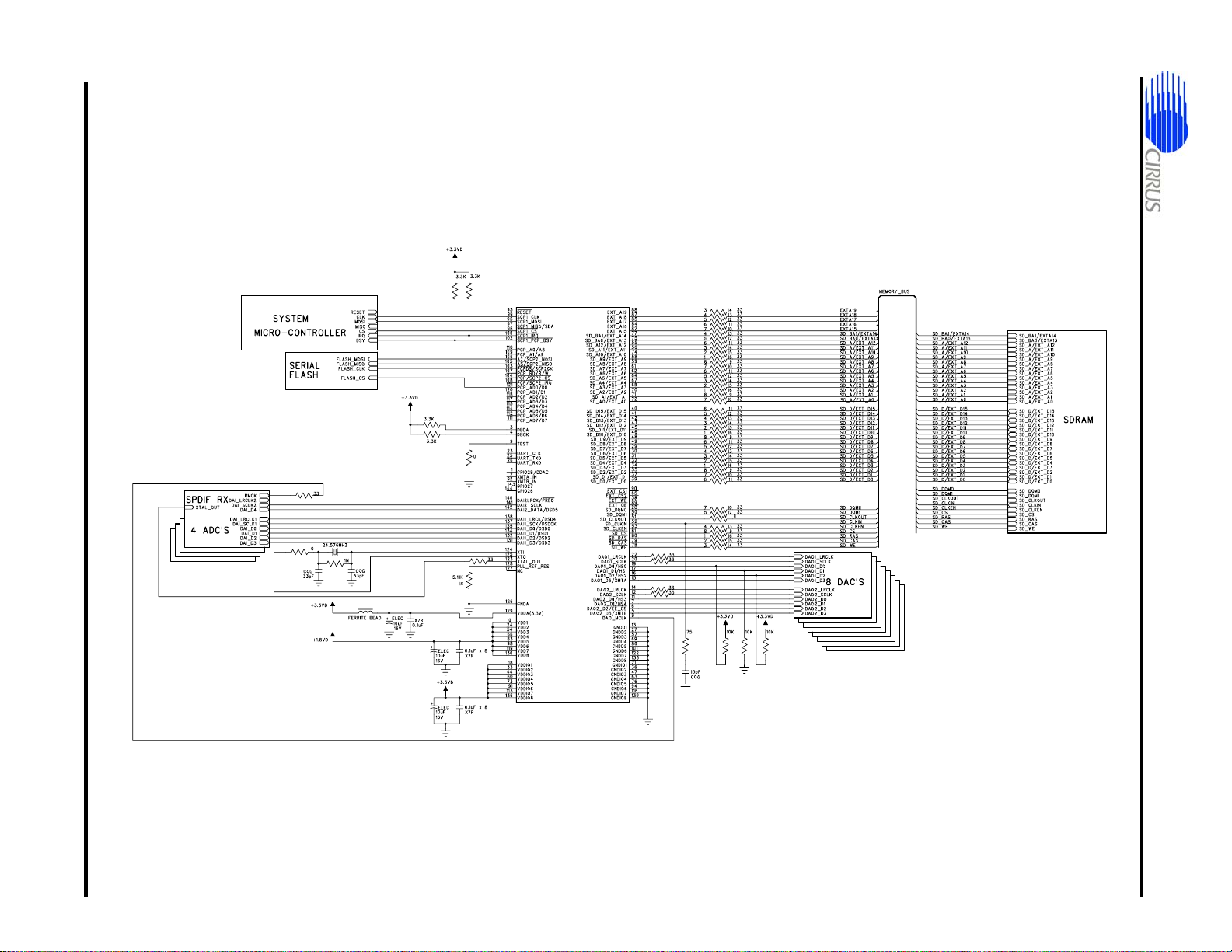

Chapter 9. System Integration..............................................................................9-1

9.1 Typical Connection Diagrams. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-1

9.2 Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-10

9.2.1 Power and Ground .......................................................................................................9-10

9.2.1.1 Power...........................................................................................................9-10

9.2.1.2 Ground.........................................................................................................9-10

9.2.1.3 Decoupling...................................................................................................9-11

9.2.2 PLL Filter ......................................................................................................................9-11

9.2.2.1 Analog Power Conditioning .........................................................................9-11

9.2.3 PLL ...............................................................................................................................9-12

9.3 Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-12

9.4 Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-13

9.4.1 Operational Mode.........................................................................................................9-13

9.5 144-Pin LQFP Pin Assigments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-15

9.6 128-Pin LQFP Pin Assigments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-16

9.7 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-17

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-29

Figures

Figure 1-1. CS4953xx Chip Functional Block Diagram .................................................................................1-2

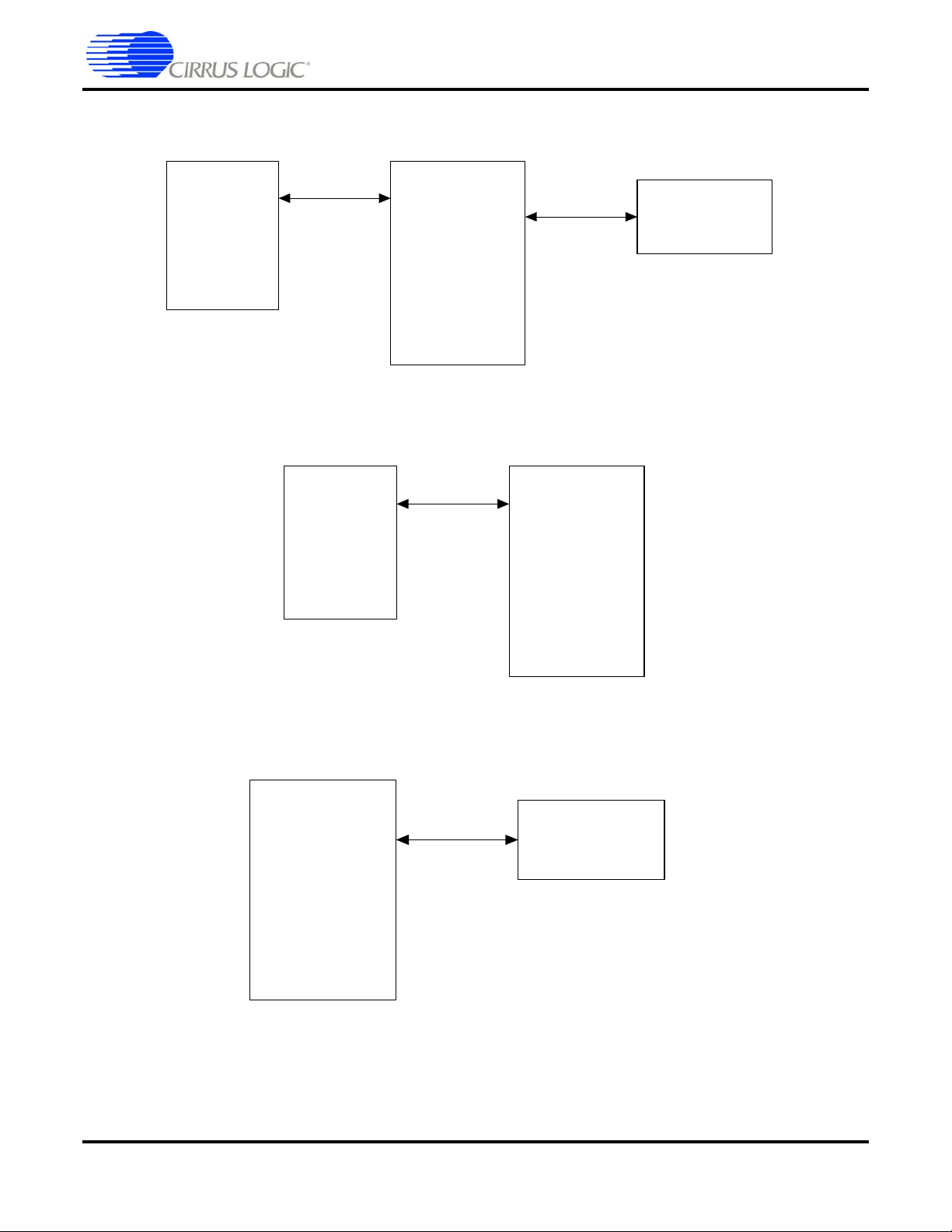

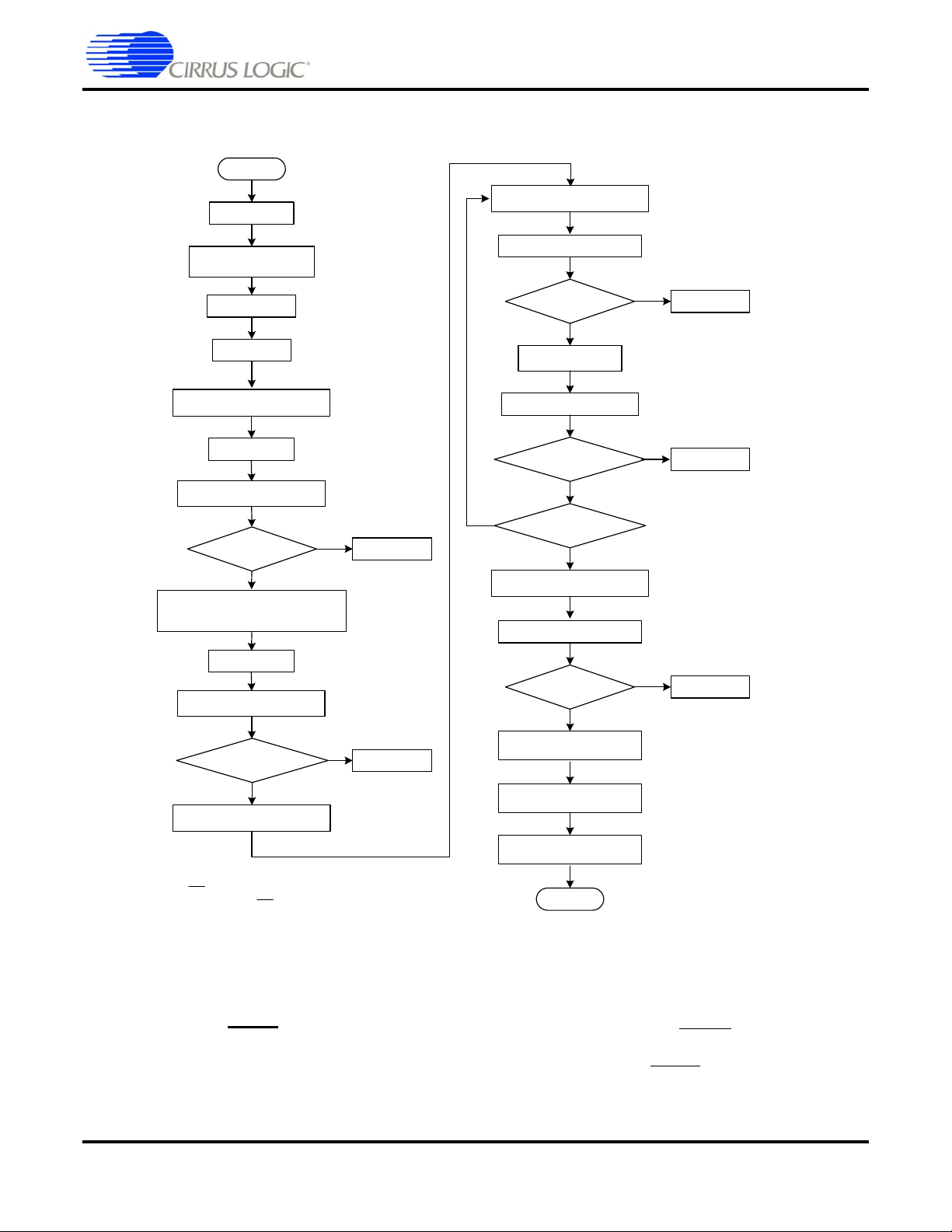

Figure 2-1. Operation Mode Block Diagrams ................................................................................................2-2

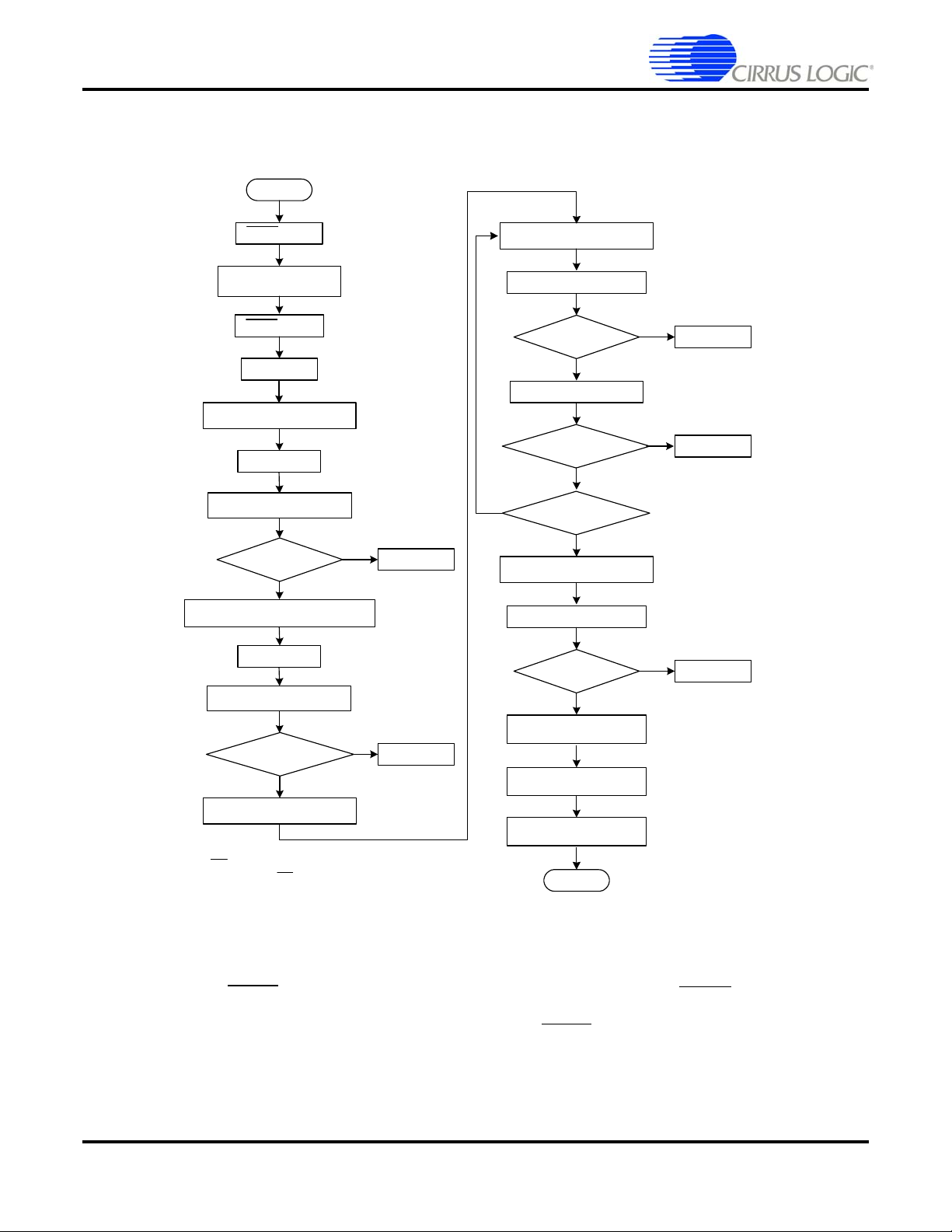

Figure 2-2. Host Controlled Master Boot.......................................................................................................2-5

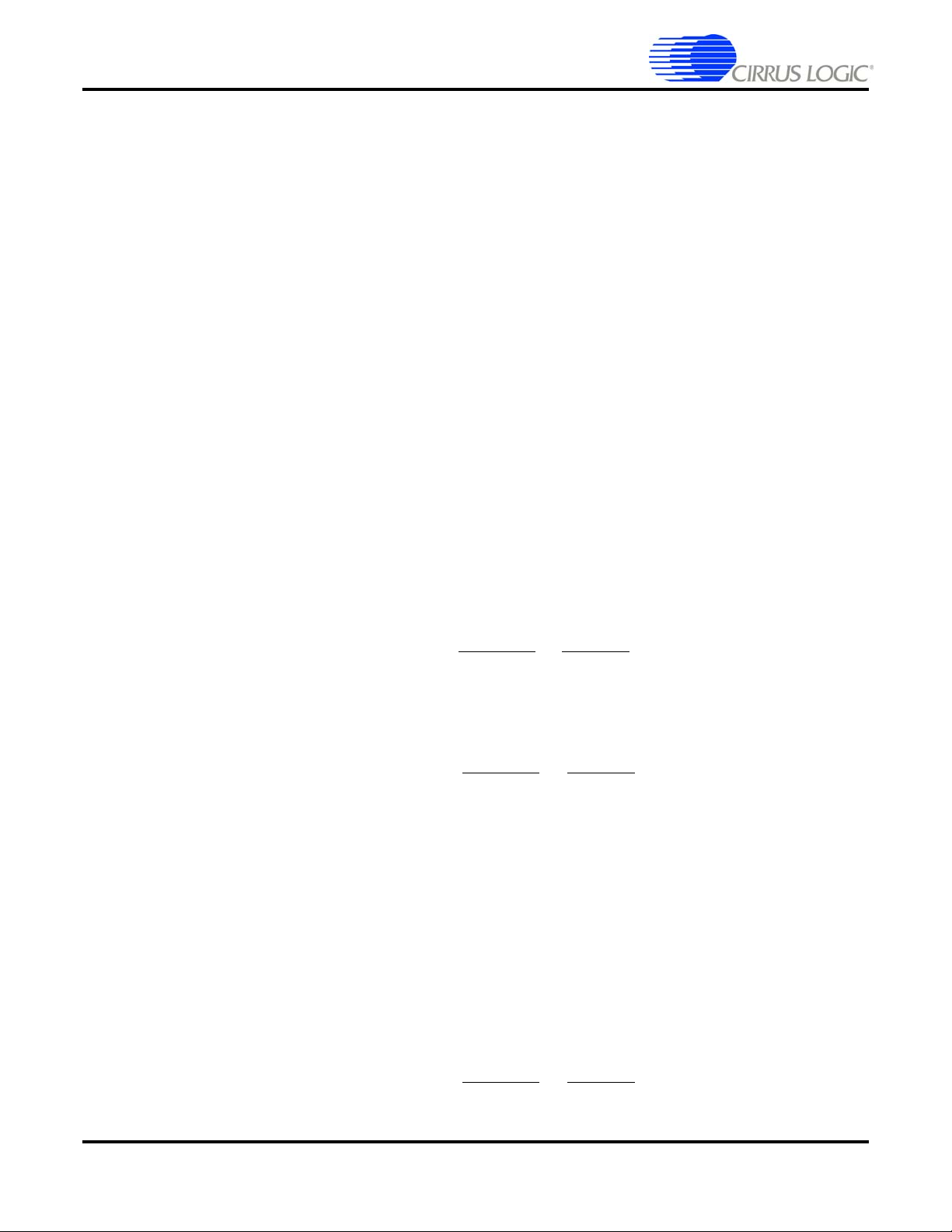

Figure 2-3. Slave Boot Sequence .................................................................................................................2-8

Figure 2-4. Master Boot Sequence Flowchart.............................................................................................2-13

Figure 2-5. Soft Boot Sequence Flowchart .................................................................................................2-15

Figure 2-6. Soft Boot Example Flowchart....................................................................................................2-16

Figure 3-1. Serial Control Port Internal Block Diagram .................................................................................3-2

Figure 3-2. Block Diagram of I

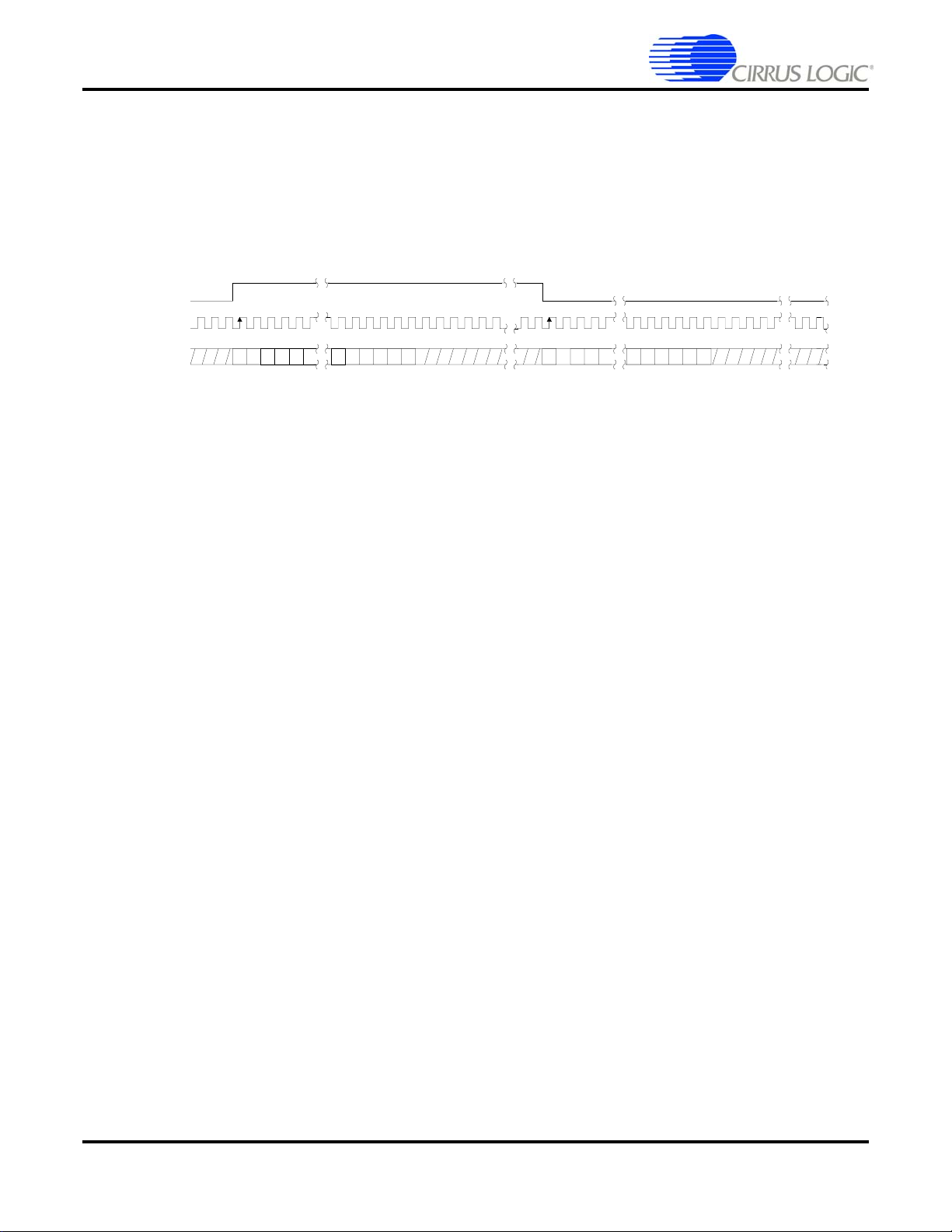

Figure 3-3. I

Figure 3-4. I

Figure 3-5. Data Byte with ACK and NACK ..................................................................................................3-6

2

C Start and Stop Conditions.....................................................................................................3-4

2

C Address with ACK and NACK...............................................................................................3-5

2

C System Bus ..............................................................................................3-3

Figure 3-6. Repeated Start Condition with ACK and NACK..........................................................................3-6

Figure 3-7. Stop Condition with ACK and NACK...........................................................................................3-7

DS732UM10 Copyright 2010 Cirrus Logic, Inc. v

Page 6

Figures

CS4953xx Hardware User’s Manual

Figure 3-8. I2C Write Flow Diagram ..............................................................................................................3-8

Figure 3-9. I

Figure 3-10. Sample Waveform for I

Figure 3-11. Sample Waveform for I

2

C Read Flow Diagram............................................................................................................3-10

2

C Write Functional TIming................................................................3-12

2

C Read Functional TIming................................................................3-12

Figure 3-12. SPI Serial Control Port Internal Block Diagram ......................................................................3-13

Figure 3-13. Block Diagram of SPI System Bus..........................................................................................3-15

Figure 3-14. Address and Data Bytes .........................................................................................................3-16

Figure 3-15. SPI Write Flow Diagram..........................................................................................................3-17

Figure 3-16. SPI Read Flow Diagram .........................................................................................................3-18

Figure 3-17. Sample Waveform for SPI Write Functional Timing................................................................3-20

Figure 3-18. Sample Waveform for SPI Read Functional Timing ...............................................................3-20

Figure 5-1. DAI Port Block Diagram..............................................................................................................5-3

Figure 5-2. I

2

S format (Rising Edge Valid SCLK)..........................................................................................5-4

Figure 5-3. Left-justified Format (Rising Edge Valid SCLK)..........................................................................5-5

Figure 6-1. DSD Port Block Diagram ............................................................................................................6-2

Figure 7-1. DAO Block Diagram....................................................................................................................7-2

Figure 7-2. I

2

S Compatible Serial Audio Formats (Rising Edge Valid) .........................................................7-3

Figure 7-3. Left-justified Digital Audio Formats (Rising Edge Valid DAO_SCLK) .........................................7-3

Figure 7-4. One-line Data Mode Digital Audio Formats ................................................................................7-4

Figure 8-1. SDRAM Interface Block Diagram................................................................................................8-1

Figure 9-1. LQFP-144, I

2

C Control, Serial FLASH, SDRAM, 7 DACs ..........................................................9-2

Figure 9-2. LQFP-144, SPI Control, Serial FLASH, SDRAM, 7 DACs..........................................................9-3

Figure 9-3. LQFP-144, SPI Control, Serial FLASH, SDRAM, 8 DACs..........................................................9-4

Figure 9-4. LQFP-144, I

2

C Control, Parallel Flash, SDRAM, 8 DACs ..........................................................9-5

Figure 9-5. LQFP-128, SPI Control, Parallel Flash, SDRAM, 8 DACs..........................................................9-6

Figure 9-6. LQFP-128, I

2

C Control, Serial FLASH, DSD Audio Input, SDRAM, 7 DACs..............................9-7

Figure 9-7. LQFP-144, SPI Control, Serial FLASH, DSD Audio Input, SDRAM, 7 DACs .............................9-8

Figure 9-8. LQFP-144, SPI Control, Serial FLASH, DSD Audio Input, SDRAM, 7 DACs .............................9-9

Figure 9-9. PLL Filter Topology...................................................................................................................9-12

Figure 9-10. Crystal Oscillator Circuit Diagram ...........................................................................................9-13

Figure 9-11. 144-Pin LQFP Pin Layout .......................................................................................................9-15

Figure 9-12. 128-Pin LQFP Pin Layout .......................................................................................................9-16

vi Copyright 2010 Cirrus Logic, Inc. DS732UM10

Page 7

CS4953xx Hardware User’s Manual

Tables

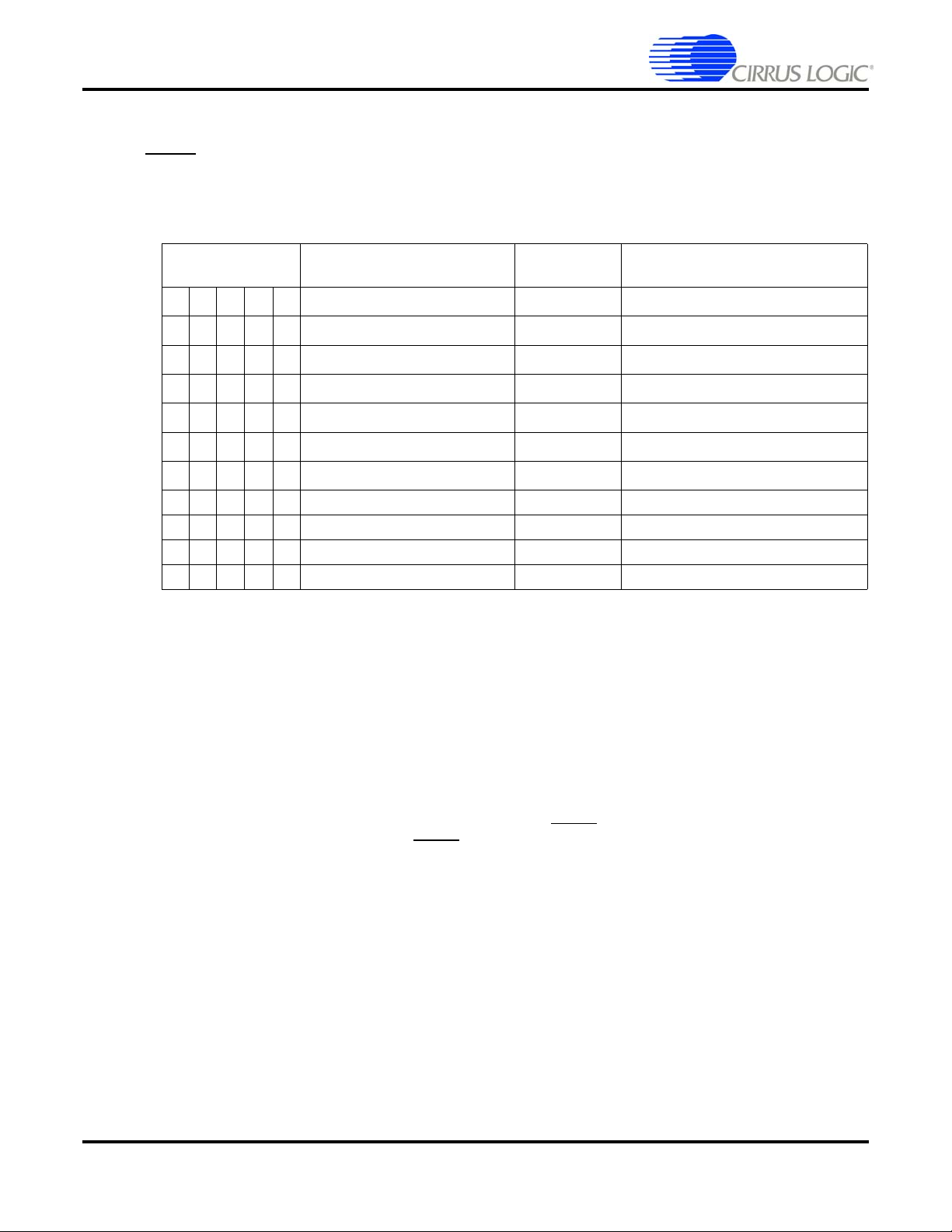

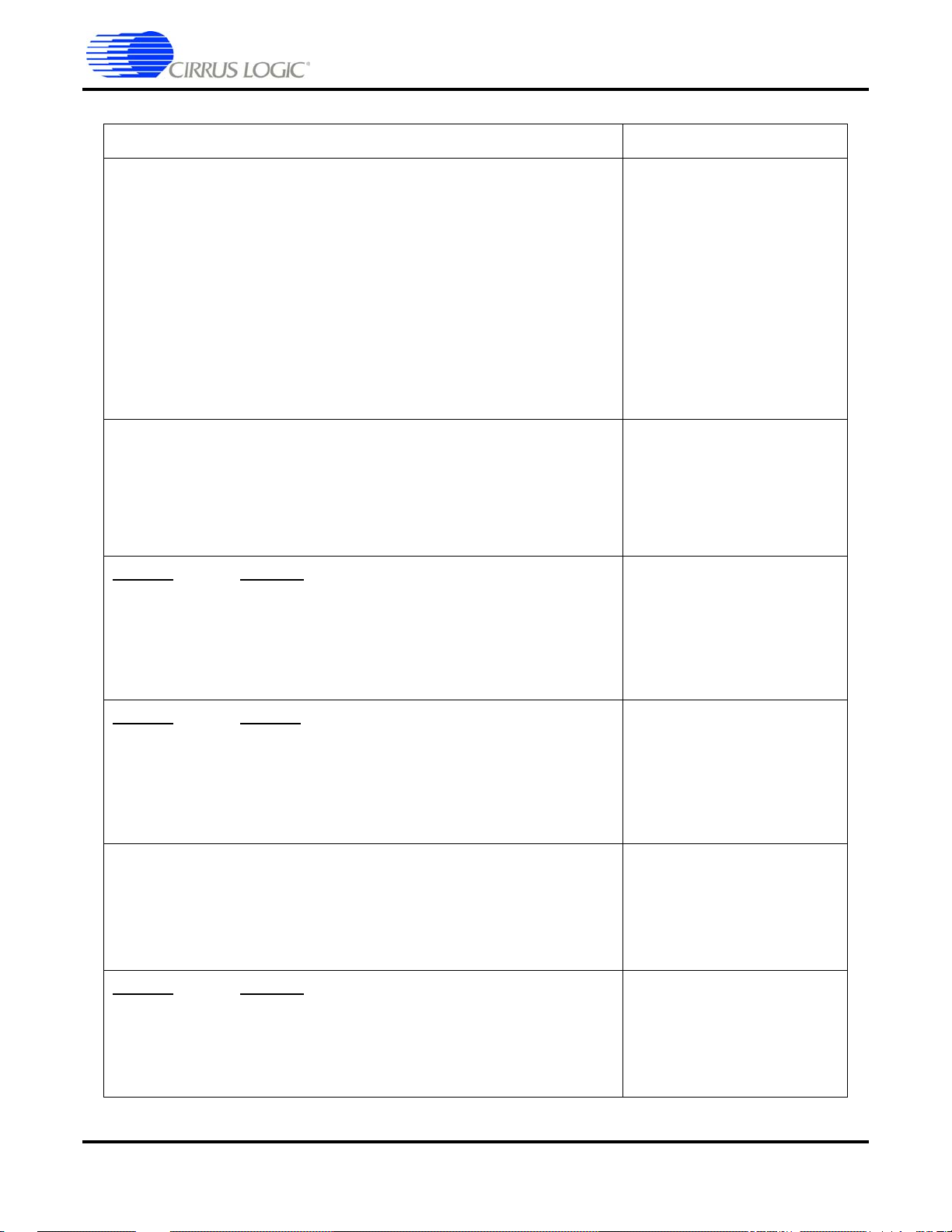

Table 2-1. Operation Modes..........................................................................................................................2-3

Table 2-2. SLAVE_BOOT message for CS4953xx.....................................................................................2-10

Table 2-3. HCMB_PARALLEL Message for CS4953xx ..............................................................................2-10

Table 2-4. HCMB_I2C message for the CS4953xx.....................................................................................2-11

Table 2-5. HCMB_SPI message for CS4953xx ..........................................................................................2-11

Tables

Table 2-6. GPIO Pins Available as EE_CS

Table 2-7. SOFT_RESET message for CS4953xx .....................................................................................2-12

Table 2-8. Boot Read Messages from CS4953xx.......................................................................................2-12

Table 2-9. Boot Command Messages for CS4953xx..................................................................................2-13

Table 2-10. SOFTBOOT Message..............................................................................................................2-14

Table 2-11. SOFTBOOT_ACK Message ....................................................................................................2-14

Table 3-1. Serial Control Port 1 I

Table 3-2. Serial Control Port SPI Signals ..................................................................................................3-14

Table 5-1. Digital Audio Input Port ................................................................................................................5-1

Table 5-2. Bursty Data Input (BDI) Pins........................................................................................................5-4

Table 5-3. Input Data Format Configuration (Input Parameter A) .................................................................5-6

Table 5-4. Input SCLK Polarity Configuration (Input Parameter B)...............................................................5-7

Table 5-5. Input LRCLK Polarity Configuration (Input Parameter C) ............................................................5-8

Table 5-6. Input DAI Mode Configuration (Input Parameter D).....................................................................5-8

Table 6-1. DSDl Audio Input Port..................................................................................................................6-1

Table 7-1. Digital Audio Output (DAO1 & DAO2) Pins..................................................................................7-1

Table 7-2. Output Clock Mode Configuration (Parameter A) ........................................................................7-5

2

C Signals..................................................................................................3-3

in HCMB..................................................................................2-12

Table 7-3. DAO1 & DAO2 Clocking Relationship Configuration (Parameter B)............................................7-5

Table 7-4. Output DAO_SCLK/LRCLK Configuration (Parameter C) ...........................................................7-6

Table 7-5. Output Data Format Configuration (Parameter D).......................................................................7-9

Table 7-6. Output DAO_LRCLK Polarity Configuration (Parameter E).......................................................7-10

Table 7-7. Output DAO_SCLK Polarity Configuration (Parameter F) .........................................................7-10

Table 7-8. Output Channel Configuration (Parameter G)............................................................................7-11

Table 7-9. S/PDIF Transmitter Pins ............................................................................................................7-11

Table 7-10. S/PDIF Transmitter Configuration............................................................................................7-12

Table 7-11. DSP Bypass Configuration.......................................................................................................7-12

Table 8-1. SDRAM Interface Signals ............................................................................................................8-2

Table 8-2. SDRAM/Flash Controller Parameters ..........................................................................................8-5

Table 9-1. Core Supply Pins .......................................................................................................................9-10

Table 9-2. I/O Supply Pins ..........................................................................................................................9-10

Table 9-3. Core and I/O Ground Pins..........................................................................................................9-11

DS732UM10 Copyright 2010 Cirrus Logic, Inc. vii

Page 8

CS4953xx Hardware User’s Manual

Table 9-4. PLL Supply Pins.........................................................................................................................9-11

Table 9-5. PLL Filter Pins............................................................................................................................9-12

Table 9-6. Reference PLL Component Values............................................................................................9-12

Table 9-7. DSP Core Clock Pins.................................................................................................................9-13

Table 9-8. Reset Pin....................................................................................................................................9-14

Table 9-9. Hardware Strap Pins..................................................................................................................9-14

Table 9-10. Pin Assignments ......................................................................................................................9-17

viii Copyright 2010 Cirrus Logic, Inc. DS732UM10

Page 9

Overview

CS4953xx Hardware User’s Manual

1.1 Overview

The CS4953xx is a programmable audio DSP that combines a programmable, 32-bit fixed-point general

purpose DSP with dedicated audio peripherals. Its audio-centric interfaces facilitate the coding of highprecision audio applications and provide a seamless connection to external audio peripheral ICs.

The CS4953xx is a 32-bit RAM-based processor that provides up to 150 MIPS of processing power and

includes all standard codes in ROM. It has been designed with a generous amount of on-chip program

and data RAM, and has all necessary peripherals required to support the latest standards in consumer

entertainment products. In addition, external SDRAM and Flash memory interfaces can be used to

expand the data memory. This device is suitable for a variety of high-performance audio applications.

These include:

• Audio/Video Receivers

•DVD Receivers

•Stereo TVs

•Mini Systems

• Shelf Systems

• Digital Speakers

• Car Audio Head Units and Amplifiers

•Set-top Boxes

Chapter 1

Introduction

1.1.1 Chip Features

The CS4953xx includes the following features:

• Various Decoding/processing Standards • Customer Software Security Keys

• 12-channel Serial Audio Inputs • 16-channel PCM Output

• Dual 32-bit Audio DSP with Dual MAC • Dual S/PDIF Transmitters

• Large On-chip X,Y, and Program RAM

• Supports SDR AM & Flash Memo ries • Digital Audio Input (DAI) Port for Aud io Data Delivery

• Parallel Control Using Motorola

®

Intel

Communication Standards

™

• Two Serial Control Ports Using SPI

Standards

2

S or LJ Format

in I

®

or

• GPIO Support for All Common Sub-circui t s

or I2C™

1-1 Copyright 2010 Cirrus Logic, Inc. DS732UM10

Page 10

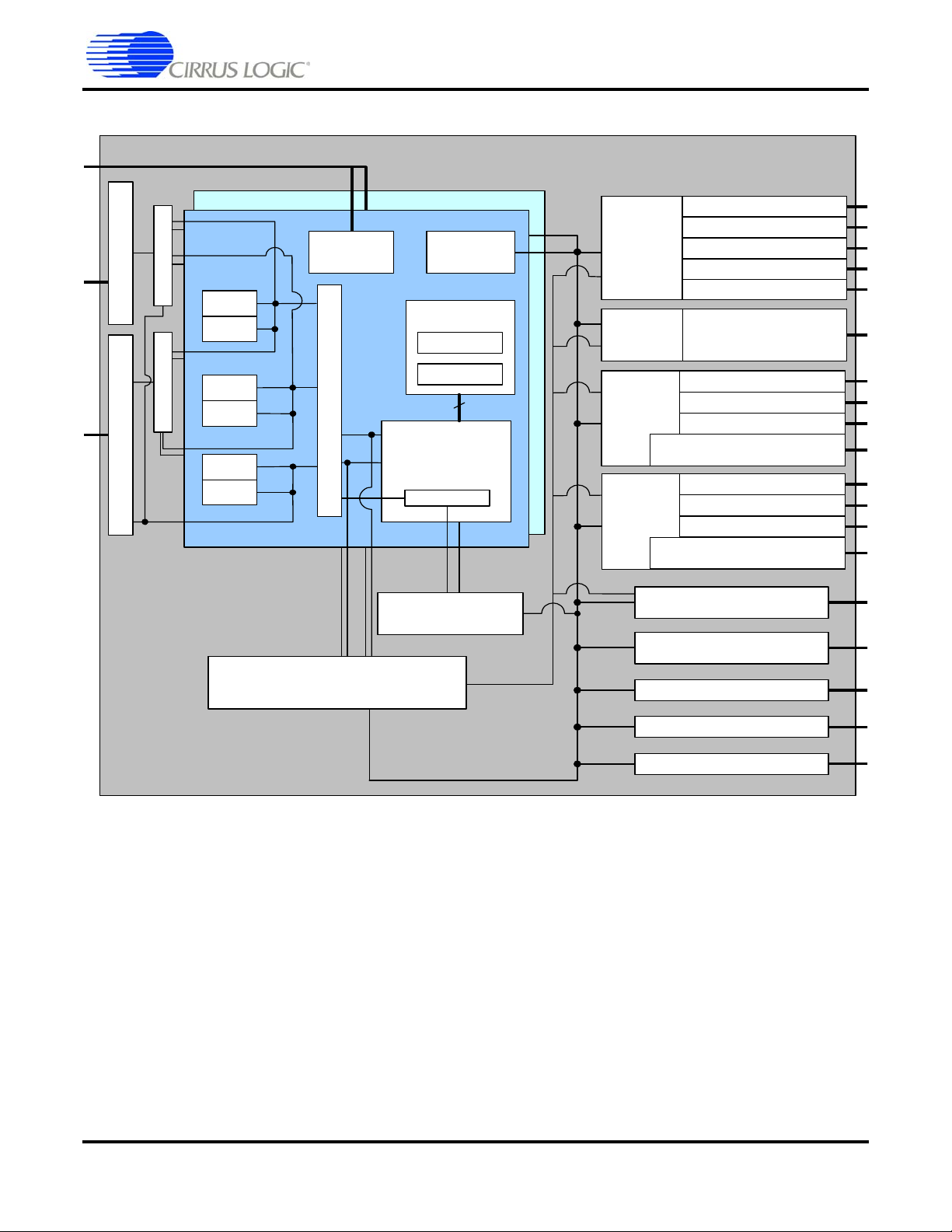

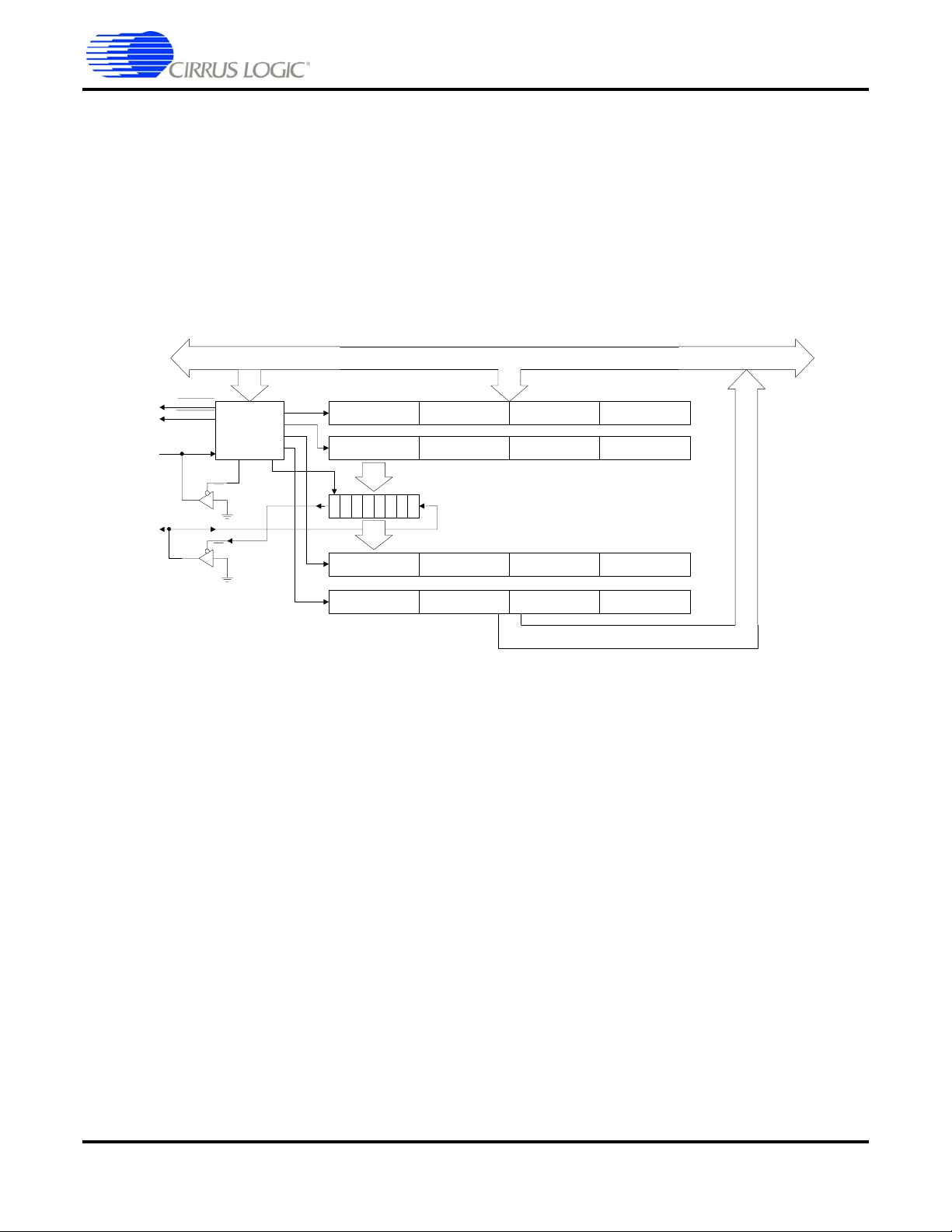

Figure 1-1 illustrates the functional block diagram for the CS4953xx chip.

CS4953xx

Overview

CS4953xx Hardware User’s Manual

DSPB

DSPA

Debug

X

Y

P

Con troller

Memory Controller

X

Y

P

32-bit Dual Datapath

ArbiterArbiter

SRAM

ROM

SRAM

ROM

SDRAM Controller SRAM / FLASH Controller

SRAM

ROM

Peripheral

Bus

Con troller

Ext (64 bit)

Log/Exp

Security

64 bit

DSP

with 72-bit

Accumulators

Decryptor

Programmable

Interrupt Co n tro ll e r

DAI1

DAI

Controller

DAI2

DAI

Con troller

DAO1

DAO

Controller

DAO2

DAO

Controller

Stereo Audio Input/DSD

Stereo Audio Input/DSD

Stereo Audio Input/DSD

Stereo Audio Input/DSD

Stereo Audio Input/DSD

Stereo Audio Input /

Bursty Da ta Inpu t/DSD

Stereo Audio Output

Stereo Audio Output

Stereo Audio Output

Stereo Audio Output or

SPD IF Tran smitter

Stereo Audio Output

Stereo Audio Output

Stereo Audio Output

Stereo Audio Output or

SPD IF Tran s mitter

Parallel C o n t ro l Port

Serial Control Port

DMA Controller with 11 Stereo Channels

Peripheral Bus

DMA Bus

Timers

GPIOs

Clock Manager and PLL

Figure 1-1. CS4953xx Chip Functional Block Diagram

See AN288, “CS4953xx/CS497xxx for a list of audio decoding/processing algorithms that are supported

by the CS4953xx: These firmwware modules and their associated application notes are available through

the Cirrus Logic Software Licensing Program. .

The CS4953xx contains sufficient on-chip memory to support decoding of all major audio decoding

algorithms available today. The CS4953xx supports a glueless SDRAM/Flash interface for increased allchannel delays. The memory interface also supports connection to an external 8- or 16-bit-wide EPROM

or Flash memory for code storage, thus allowing products to be field upgraded as new audio algorithms

are developed.

This chip, teamed with the Cirrus certified decoder library, Cirrus digital interface products, and mixedsignal data converters, enables the design of next-generation digital entertainment products.

DS732UM10 Copyright 2010 Cirrus Logic, Inc 1-2

Page 11

Functional Overview of the CS4953xx Chip

CS4953xx Hardware User’s Manual

1.2 Functional Overview of the CS4953xx Chip

The CS4953xx chip supports a maximum clock speed of 150 MHz in a 144-pin LQFP or 128-pin LQFP

package. A high-level functional description of the CS4953xx chip is provided in this section.

1.2.1 DSP Core

The CS4953xx DSP core is a pair of general purpose, 32-bit, fixed-point, fully programmable digital signal

processors that achieve high performance through an efficient instruction set and highly parallel

architecture. The device uses two’s complement fractional number representation, and employs busses

for two data memory spaces and one program memory space.

CS4953xx core enhancements include portability of the design, speed improvement, and improvements

for synthesis, verification, and testability. Each member of the CS4953xx family has different SRAM and

ROM sizes. Please refer to the CS4953xx data sheet for details.

1.2.2 Security Extension module

This module is a 64-bit extension module that allows the CS4953xx device to be placed in a secure mode

where decryption is activated via a 128-bit key. This key is written to the security extension in two 64-bit

move instructions. Secure mode is disabled by default, and must be explicitly enabled.

1.2.3 Debug Controller (DBC)

An I2C slave debug controller (DBC) is integrated within the CS4953xx DSP core. Two pins are reserved

for connecting a PC host to the debug ports on either DSP. The debug port consists of two modules, an

2

I

C slave and a debug master. The DBC master sends dedicated signals into the DSP core to initiate

debug actions and it receives acknowledge signals from the core to indicate the requested action has

been taken. Basically, this interface allows the DBC to insert instructions into the pipeline. The core will

acknowledge the action when it determines the pipeline is in the appropriate state for the inserted action

to be taken.

1.2.4 Digital Audio Output (DAO1, DAO2) Controller

The CS4953xx has two Digital Audio Output (DAO) controllers, each of which contains 4 stereo output

ports. One port on each DAO can be used as a S/PDIF transmitter. The DAO ports can transmit up to 16

channels of audio sample data in I

buffers which are 32 bits wide. Four of the channels can also serve as output buffers for the two S/PDIF

transmitters. The O/S can dedicate DMA channels to fill the DAO data buffers from memory. DAO control

is handled through the peripheral bus.

2

S-compatible format. The audio samples are stored in 16 channel

1.2.5 Digital Audio Input (DAI1) Controller

The CS4953xx Digital Audio Input (DAI) controller has four stereo input ports and DAI control is handled

through the peripheral bus. Each DAI pin can be configured to load audio samples in a variety of formats.

In addition to accepting multiple formats, the DAI controller has the ability to accept multiple stereo

channels on a single DAI1_DATAx pin. All four DAI pins are slaves and normally share the same serial

input clock pins (DAI1_SCLK and DAI1_LRCLK). Pins DAI1_DATA[3:0] may also be reconfigured to use

the DAO serial input clock pins (DAOx_SCLK and DAOx_LRCLK). A single global configuration register

provides a set of enable bits to ensure that ports may be started synchronously.

1-3 Copyright 2010 Cirrus Logic, Inc. DS732UM10

Page 12

Functional Overview of the CS4953xx Chip

CS4953xx Hardware User’s Manual

1.2.6 Compressed Data Input / Digital Audio Input (DAI2) Controller

The DAI2 controller has one input port and its own SCLK and LRCLK and can be used for accepting PCM

data in the same way as DAI1, but is used primarily for the delivery of compressed data. When configured

for compressed data input, custom internal hardware is enabled that off-loads some pre-processing of the

incoming stream to help maximize the MIPS available in the DSP core for user-customized applications.

1.2.7 Direct Stream Digital® (DSD) Controller

The CS4953xx also has a DSD controller which allows the DSP to be integrated into a system that

supports SACD audio. The DSD controller pins are shared with the DAI1 and DAI2 ports. The DSD port

consists of a bit clock (DSD_CLK) and six DSD data inputs (DSD[5:0]).

1.2.8 General Purpose I/O

A 32-bit general-purpose I/O (GPIO) port is provided on the CS4953xx chip to enhance system flexibility.

Many of the functional pins can be used for either GPIO or peripherals.

Each GPIO pin can be individually configured as an output, an input, or an input with interrupt. A GPIO

interrupt can be triggered on a rising edge (0-to-1 transition), falling edge (1-to-0 transition), or logic level

(either 0 or 1). Each pin configured as an input with interrupt can be assigned its own interrupt trigger

condition. All GPIOs share a common interrupt vector.

1.2.9 Parallel Control Port (Motorola®/Intel® Standards) (Optional Feature)

The CS4953xx parallel control port allows an external device such as a microcontroller to communicate

with the CS4953xx chip using either a Motorola

Only one of the two communication modes can be selected at a time. For external device-control

purposes, the CS4953xx is in slave mode for all communication protocols, although it can request the

external device to perform a read. The parallel control port supports direct memory access (DMA) and can

be used simultaneously with the CS4953xx serial control port.

The parallel control port communication mode selection occurs as the CS4953xx exits a reset condition.

The rising edge of the RESET

boot style. Configuration of the three address input pins A[2:0] allows one of the parallel configuration

registers to be selected and accessed.

pin samples the HS[4:0] pins to determine the communication mode and

®

-type or Intel®-type parallel communication standard.

1.2.10 Serial Control Ports (SPI™ or I2C™ Standards)

The CS4953xx has two serial control ports (SCP) that support SPI™ and I2C™ Master/Slave

communication modes. The serial control port allows external devices such as microcontrollers to

2C

communicate with the CS4953xx chip through either I

be configured as either a master or a slave.

The CS4953xx SPI and I

main difference between the two is the protocol being implemented between the CS4953xx and the

external device. In addition, the I

2

to the I

needed.

C protocol. If this mode is enabled, the I2C slave will hold SCP1_CLK low to delay a transfer as

2

C serial communication modes are identical from a functional standpoint. The

2

C slave has a true I2C mode that utilizes data flow mechanisms inherent

or SPI serial communication standards and can

By default, SCP1 is configured as a slave for external device-controlled data transfers. As a slave, it

cannot drive the clock signal nor initiate data transfers.

DS732UM10 Copyright 2010 Cirrus Logic, Inc 1-4

Page 13

Functional Overview of the CS4953xx Chip

CS4953xx Hardware User’s Manual

By default, SCP2 is configured as a master to access a serial FLASH/EEPROM for either booting the

DSP or retrieving configuration information. As a master, it can drive the clock signal at up to 1/2 of the

DSP’s core clock speed.

The CS4953xx has two additional serial communication pins not specified in either the I

specification. The port uses the SCP1_IRQ

port uses the SCP1_BSY

A serial control port can be operated simultaneously with the CS4953xx parallel control port.

pin to warn the host to pause communication.

1.2.11 SDRAM Controller

The CS4953xx supports a glueless external SDRAM interface to extend the data memory of the DSP

during runtime. The SDRAM controller provides 2-port access to X and Y memory space, a quad-word

read buffer, and a double-buffered quad-word write buffer . One SDRAM controller port is dedicated to P

memory space and the second port is shared by X and Y memories. The X/Y port has dual write buffers

and a single read buffer, and the P memory port has a single read buffer. One of these buffers is four 32bit words (128 bits). Every “miss” to the read buffer will cause the SDRAM controller to burst eight 16-bit

reads on the SDRAM interface. The SDRAM controller supports SDRAMs from 2 MB to 64 MB with

various row, bank, and column configurations. The SDRAM controller runs synchronous to HCLK, the

global chip clock.

1.2.12 Flash Controller

The CS4953xx supports a glueless external Flash interface that allows autoboot from a parallel Flash or

EEPROM device extending data memory and/or program memory during DSP runtime. Flash can be

accessed using 8-bit, 16-bit, and 32-bit data modes (1-byte, 2-byte, and 4-byte words) and using an 8-bit

or 16-bit data bus, where the word width is the number of bytes per transfer, and the data bus size is the

width of the physical interface to Flash. Separate chip select pins allow Flash devices to be connected

without additional chip select logic. Thus, the interface supports up to 512k x 16 bits of Flash. The external

Flash interface serially accesses the X, Y, and P memory spaces on the CS4953xx chip.

2

C or SPI

pin to indicate that a read message is ready for the host. The

1.2.13 DMA Controller

The DMA controller contains 12 stereo channels. The O/S uses 11 stereo channels, 6 for the DAO (2 are

for the S/PDIF transmitters), 4 for the DAI, and one for the parallel control port. The addition of the DMA

channel for the parallel control port allows compressed audio data to be input over this port. The DMA

block is able to move data to/from X or Y memory, or alternate between both X and Y memory. The DMA

controller moves data to/from X and/or Y memory opportunistically (if the core is not currently accessing

that particular memory space during the current cycle). The DMA controller has a “Dead Man’s” timer so

that if the core is running an inner loop and accessing memory every cycle, the DMA controller can

interrupt the core to run a DMA cycle.

1.2.14 Timers

A 32-bit timer block runs off the CS4953xx DSP clock. The timer count decrements with each clock tick of

the DSP clock when the timer is enabled. When the timer count reaches zero, it is re-initialized, and may

be programmed to generate an interrupt to the DSP.

1-5 Copyright 2010 Cirrus Logic, Inc. DS732UM10

Page 14

1.2.15 Clock Manager and PLL

The CS4953xx Clock Manager and PLL module contains an Analog PLL, RTL Clock Synthesizer, and

Clock Manager. The Analog PLL is a customized analog hard macro that contains the Phase Detector

(PD), Charge Pump, Loop Filter, VCO, and other non-digital PLL logic. The Clock Synthesizer is a digital

design wrapper around the analog PLL that allows clock frequency ranges to be programmed. The Clock

Manager is a digital design wrapper for the Clock Synthesizer that provides the logic (control registers)

necessary to meet chip cloc ki ng re qui re men ts.

The Clock Manager and PLL module generates two master clocks:

• HCLK - global chip clock (clocks the DSP core, internal memories, SDRAM, Flash, and all

peripherals)

• OVFS - oversampled audio clock. This clock feeds the DAO block which has dividers to generate

the DAO_MCLK, DAO_SCLK, and DAO_LRCLK.

The Clock Manager has the ability to bypass the PLL so that the HCLK will run directly off the PLL

Reference Clock (REFCLK). While operating in this mode, the OVFS clock can still be divided off the VCO

so the PLL can be tested.

1.2.16 Programmable Interrupt Controller

Functional Overview of the CS4953xx Chip

CS4953xx Hardware User’s Manual

The Programmable Interrupt Controller (PIC) forces all incoming interrupts to be synchronized to the

global clock, HCLK. The PIC provides up to 16 interrupts to the DSP Core. The interrupts are prioritized

with interrupt 0 as the highest priority and interrupt 15 as the lowest priority. Each interrupt has a

corresponding interrupt address that is also supplied to the DSP core. The interrupt address is the same

as the IRQ number (interrupt 0 uses interrupt address 0 and interrupt 15 uses interrupt address 15). Both

an enable mask and a run mask are provided for each interrupt. The enable mask allows the enabled

interrupts to generate a PIC_REQ signal to the DSP core, and the run mask allows the enabled interrupts

to generate a PIC_CLR, thereby bringing the core out of its halt state when it accepts the interrupt.

1

§§

1. The “§§” symbol is used throughout this manual to indicate the end of the text flow in a chapt e r.

DS732UM10 Copyright 2010 Cirrus Logic, Inc 1-6

Page 15

Overview

CS4953xx Hardware User’s Manual

2.1 Overview

The CS4953xx has several operational modes that can be used to conform to many system

configurations. The operational modes for the CS4953xx specify both the communication mode and boot

mode. This chapter discusses the selection of operational modes, booting procedures and performing a

soft reset.

The CS4953xx can be either a slave device or a master device for the boot procedure. In Master Boot

Mode, the CS4953xx is the master boot device and can automatically boot the application code from

either serial or parallel external ROM (the slave boot device). In Slave Boot Mode, the CS4953xx is the

slave boot device and requires the system host controller (the master boot device) to determine how to

boot the application code. The system host controller can either load the application code or the host can

direct the CS4953xx to boot application code from serial or parallel external ROM. See Figure 2-1 on

page 2-2.

Chapter 2

Operational Modes

Thus, there are three boot modes for the CS4953xx:

• Master Boot (From serial or parallel external ROM)

• Slave Boot (Using SPI, I

• Host Controlled Master Boot (serial or parallel external ROM)

When the CS4953xx is configured for an operational mode where it is the slave boot device, one of the

below communication modes must be specified by the host controller (that is, the master boot device).

These communication modes are described in detail in Chapter 3, "", Chapter 3, "Serial Control Port" and

Chapter 4, "", Chapter 4, "Parallel Control Port". Please see these chapters for block diagrams and

flowcharts depicting each of the CS4963x boot modes.

2

C, Intel, Motorola, or Multiplexed Intel protocols.)

2-1 Copyright 2010 Cirrus Logic, Inc. DS732UM10

Page 16

Overview

CS4953xx Hardware User’s Manual

System H ost

C ontro lle r

(M as ter)

Control Bus

Host Controlled Master Boot

(Recom m en ded for most systems)

System H o st

C o ntro ller

(M as ter)

CS 4953xx

(Slav e)

Control B us

P a ralle l

M e mory Bu s /

SCP2

CS4953xx

(Slav e)

E x te rn a l ROM /

Ext. Serial Flash

CS4953xx

(M a ste r)

Figure 2-1. Operation Mode Block Diagrams

Slave Boot

External

Memory Bus

E x te rn a l ROM

(S lave )

Master Boot

(Not currently supported by O /S)

DS732UM10 Copyright 2010 Cirrus Logic, Inc 2-2

Page 17

Operational Mode Selection

CS4953xx Hardware User’s Manual

2.2 Operational Mode Selection

The operational mode for the CS4953xx is selected by the values of the HS[4:0] pins on the rising edge of

RESET

determines the method for loading application code. The table below shows the different operational

modes and the HS[4:0] values for each mode.

. This value determines the communication mode used until the part is reset again. This value also

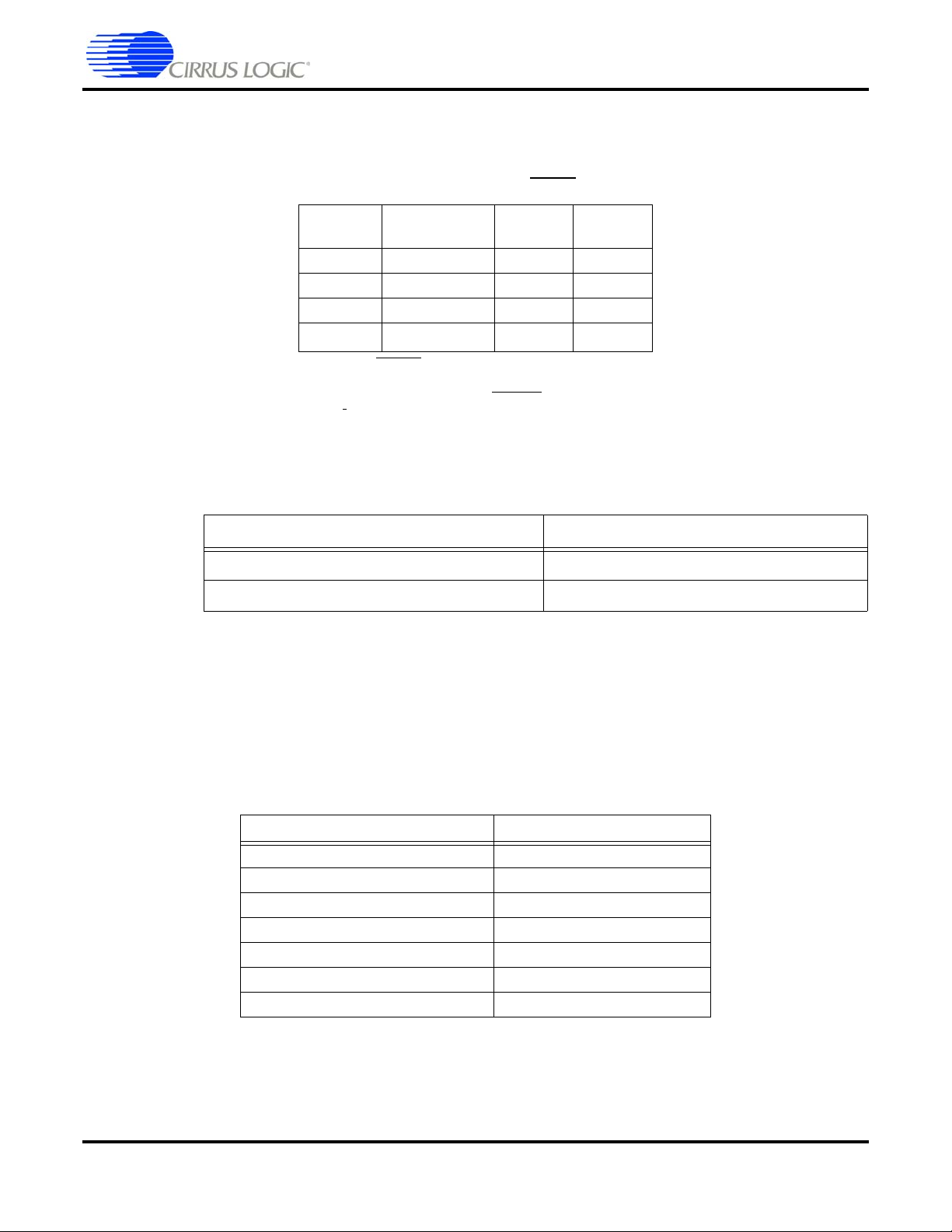

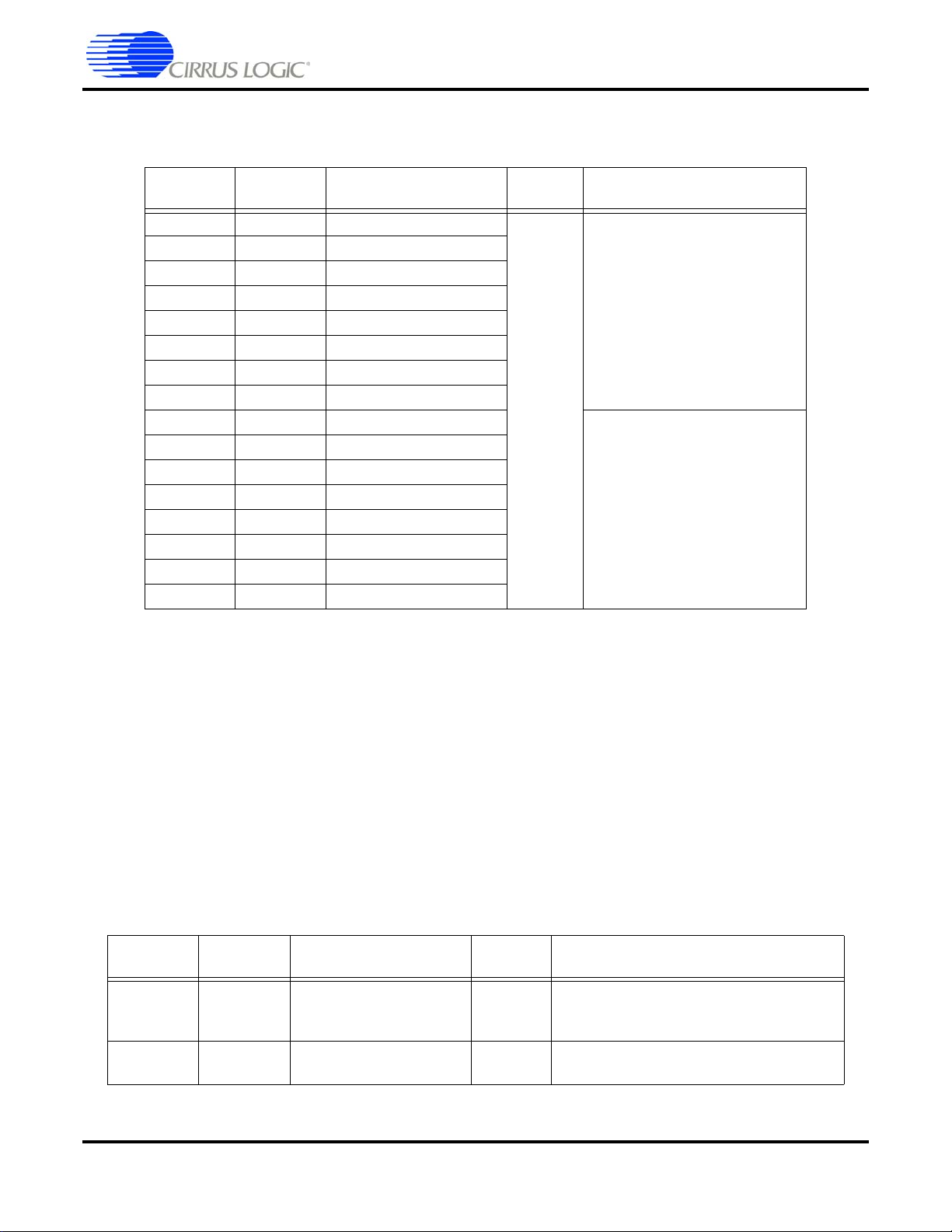

Table 2-1. Operation Modes

HS[4:0] Mode

X0000

Master SCP1 I

2

C

Boot Master

Device

CS4953xx

X 1 0 0 0 Master SCP1 SPI1 CS4953xx

X 0 0 0 1 Master SCP1 SPI2 CS4953xx

X 1 0 0 1 Master SCP1 SPI3 CS4953xx

X 0 0 1 0 Master 8-bit Flash CS4953xx

X 1 0 1 0 Master 16-bit Flash CS4953xx

XX10 0

Slave/HCMB SCP1 I

2

C

System Host CS4953xx

I2C External ROM

SPI (Mode 1) External ROM

SPI (Mode 2) External ROM

SPI (Mode 3) External ROM

8-bit External ROM

16-bit External ROM

Boot Slave Device

1,8

2, 5, 7, 8

3, 5, 7, 8

4, 5, 7, 8

6

6

X X 1 0 1 Slave/HCMB SCP1 SPI System Host CS4953xx

X X 1 1 0 Slave/HCMB PCP Intel System Host CS4953xx

X X 1 1 1 Slave/HCMB PCP Motorola System Host CS4953xx

X X 0 1 1 Slave/HCMB PCP Mux System Host CS4953xx

1. In I2C master mode, the Image Start address (0x0) is sent as a 16-bit value, with the default I2C address of

2. SPI master mode 1 is to support the legacy 16-bit SPI EEPROM. The following defaults are used: SPI

3. In SPI Master mode 2, the following defaults are us ed: SPI Command Byte 0x68, Imag e Start address 0x0 is

4. In SPI Master mode 3, the following defaults are used: SPI command byte 0x03, Image Start address 0x0 is

5. For all SPI Master boot modes, by default GPIO20 is used as EE_CS

6. For Flash Master modes, the following defaults are used: clock ratio=1:1, Endian Mode = little-endian, Chip

7. Master Boot Modes are currently not supported by the O/S.

8. F

2

0x50, I

Command Byte 0x03, Image Start address 0x0 is sent as a 16-bit value, no dummy bytes, SPI clock

frequency = F

sent as a 24-bit value, 4 dummy bytes sent foll owin g the address (and before reading im age dat a ), SPI cl oc k

frequency = F

sent as a 24-bit value, no dummy bytes, SPI clock frequency= F

EEPROM devices.

configured to select an alternate pin for EE_CS

Select polarity = acti ve -low, 0-cycle delay from CS/Address Change to O utp ut Enable, 4-cycle delay from C S

to Read Access.

C clock frequency= F

/4.

dclk

/ 2. This mode supports the Atmel SPI Flash memory.

dclk

is specified in the CS4953xx data sheet.

dclk

dclk

/72.

/ 2. This mode supports the ST SPI

dclk

, but the HCMB message can be

.

2-3 Copyright 2010 Cirrus Logic, Inc. DS732UM10

Page 18

2.3 Slave Boot Procedures

When the CS4953xx is the slave boot device, the system host controller (as the master boot device) must

follow an outlined procedure for correctly loading application code. The two methods of slave boot for the

CS4953xx, slave boot and host-controlled master boot are described in this section. Each of these

methods requires the system host controller to send messages to, and read back messages from, the

CS4953xx. These messages have been outlined in Section 2.3.3 "Boot Messages" on page 2-10.

The CS4953xx ha s dif feren t .uld files (overlays) for certain processing tasks. Slave booting the CS4953xx

requires loading multiple overlays - differing from previous Cirrus Logic Audio DSP families (this is,

CS493xx, CS494xxx). Please refer to AN288, “CS4953xx Firmware User’s Manual” regarding more

information on the breakdown of processing tasks for each overlay.

Pseudocode and flowcharts will be used to describe each of these boot procedures in detail. The flow

charts use the following messages:

Slave Boot Procedures

CS4953xx Hardware User’s Manual

• Write_* –

• Read_* – Read from CS4953xx

Please note that * above can be replaced by SPI, I

the mode of host communication. For each case, the general download algorithm is the same. The

system designer should also refer to the control port sections of this document in Chapter 3, "", Chapter 3,

"Serial Control Port" and Chapter 4, "", Chapter 4, "Para llel Contr o l Port" for the details of when writing to

and reading from the CS4953xx is valid.

One feature that is of special note – the entire boot procedure for the CS4953xx can be made of a

combination of slave boot and host-controlled master boot procedures. An example can be seen in

Figure 2-3 on page 8.

After completing the full download to the CS4953xx, a KICK START message is sent to cause the

application code begin execution. Please note that it takes time to lock the PLL and initialize the SDRAM

interface when initially booting the DSP. Typically this time is less than 200 ms. If a message is sent to the

DSP during this time, the SCP1_BSY

when the SCP1_BSY

host must reboot the DSP.

Write to CS4953xx

pin will go low to indicate that the DSP is busy. Any messages sent

pin is LOW will be lost. If the SCP1_BSY pin stays LOW longer than 200 ms the

2.3.1 Host Controlled Master Boot

The Host Controlled Master Boot (HCMB) procedure is a sequence where the system host controller

instructs the CS4953xx to boot application code from either the external memory interface (ROM or

Flash), or the serial control interface (serial SPI Flash/EEPROM or I

controller can communicate with the CS4953xx via SPI, I

Multiplexed Intel, or Motorola). The external memory start address of the code image, as well as the data

rate, are specified by the host by the HCMB_<MODE> message. These messages are defined in Section

2.3.3 "Boot Messages" on page 2-10.

2

C, Intel®, Multiplexed Intel, or Motorola® depending on

2

C EEPROM). The syste m ho st

2

C, or one of the three parallel formats (Intel,

DS732UM10 Copyright 2010 Cirrus Logic, Inc 2-4

Page 19

Slave Boot Procedures

,

n

CS4953xx Hardware User’s Manual

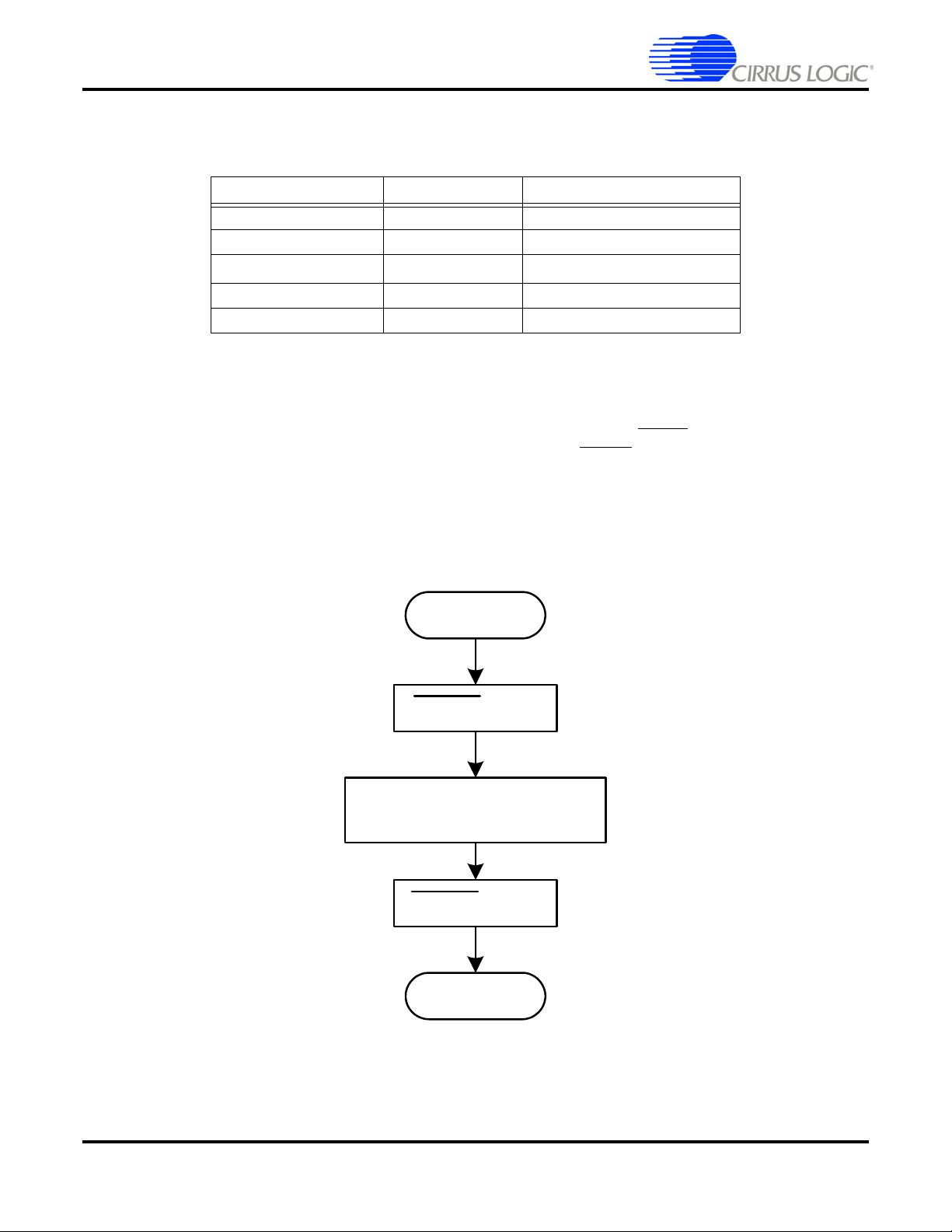

2.3.1.1 Performing a Host Controlled Master Boot (HCMB)

Figure 2-2 shows the steps taken during a Host Controlled Master Boot (HCMB). The procedure is

discussed in Section 2.3.1.1.1.

START

RESET (LOW)

SET HS[3:0] PINS FOR

OPERATI ONAL MODE

RESET (HIGH)

WAIT 50 μS

WRITE_* (SLAVE_BOOT)

WAIT 10 μS

READ_* (MSG)

==BOOT_START

WRITE_* (BOOT_ ASSIST_A.ULD FILE)

Or (boot_assist_xtal_div2_a*.uld)

WAIT 10 μS

READ_* (MSG)

BOOT_SUCCESS

(SOFT_RESET_DSP_A)

NOTE 1. Read four bytes from the DSP.

IRQ will not drop for this read sequence.

NOTE 2. Obey IRQ for all reads from

this point forward.

NOTE 1

MSG

Y

NOTE 1

MSG==

Y

WRITE_*

N

N

EXIT(ERROR)

EXIT(ERROR)

WRITE_* (HCMB_<MODE>)

READ_* (MSG)

MSG

==BOOT_START

Y

READ_* (MSG)

MSG==

BOOT_SUCCESS

Y

MORE .ULD FILES?

WRITE_* (SOFT_RESET)

READ_* (MSG)

MSG ==APP_START

SEND HARDWARE

CONFIGURATIONS

SEND FIRMWARE

CONFIGURATIONS

WRITE_* (KICKSTART)

DONE

NOTE 2

N

EXIT(ERROR)

N

EXIT (ERROR)

Y

N

N

EXIT (ERROR)

Y

* is replaced with SPI

I2C, etc. dependi ng o

the communication

protocol used.

Figure 2-2. Host Controlled Master Boot

2.3.1.1.1 Host Controlled Master Boot (HCMB) Procedure

1. Toggle RESET. A download sequence is started when the host holds the RESET pin low for the

required time. The mode pins, HS[4:0] must be in the appropriate state to set the host communication

mode before and immediately after the rising edge of RESET

typically used to set the default state of the HS[4:0] pins.

2.

Send the SLAVE_BOOT message. The host sends the appropriate SLAVE_BOOT message to the

CS4953xx using the control port specified (serial port/parallel port) and format specified (I

Intel, etc.) by the HS[4:0] pins at reset.

2-5 Copyright 2010 Cirrus Logic, Inc. DS732UM10

. Pull-up and pull-down resistors are

2

C, SPI,

Page 20

Slave Boot Procedures

CS4953xx Hardware User’s Manual

3. Wait for 10 μS.

Read the BOOT_START message (See NOTE 1 in Figure 2- 2). If the initialization is successful,

4.

CS4953xx sends out the BOOT_START message and the host proceeds to Step 6.

If initialization fails, the host must return to

Step 1, and if failure is met again, the communication

timing and protocol should be inspected.

5.

The host sends the boot assist BOOT_ASSIST_A.uld file or boot_assist_xtal_div2_a*.uld (sets

XTAL_OUT =XTAL/2) to the CS4953xx DSP.

6. Wait 10

7.

Read the BOOT_SUCCESS message (See NOTE 1 in Figure 2-2). The host then reads a message

μS

from the appropriate communications port. Each.ULD file contains a checksum that is compared at

the end of the boot process. CS4953xx sends a BOOT_SUCCESS message to the host if the

checksum is correct after the download.

If the checksum was incorrect, CS4953xx responds with a BOOT_ERROR_CHECKSUM message.

This indicates that the image read by the DSP is corrupted. The communications interface hardware

and code image integrity should be checked if this occurs.

8.

Send the SOFT_RESET_DSP_A command: After reading the BO O T_SU CCES S mes s age on the

boot assist code image/overlay, the host must send this message. If boot_assist_xtal_div2_a*.uld was

sent in

9.

Send the correct HCMB_<MODE> message. The host sends to the CS4953xx the appropriate

Step 5, the XTAL_OUT frequency will change to XTAL/2 after the soft reset has taken place.

HCMB_<MODE> message, where <MODE> indicates the type of external ROM: PARALLEL, SPI, or

2

C. This message tells CS4953xx the start address of the downloadable image (.ULD file) and

I

identifies which port will be used to access FLASH memory.

10.

Wait for IRQ low . Th e host the n wait s for SC P1_IRQ (o r PCP_IRQ) to go low . ( See NOTE 2 in Figure

2-2)

11.

Read the BOOT_START message. If the initialization is successful, CS4953xx will send the

BOOT_START message to the host.

If initialization fails, the host must return to

Step 1, and if failure is met again, the communication

timing and protocol should be inspected.

12.

Wait for IRQ low. After receiving the BOOT_START message, the host then waits for SCP1_IRQ (or

PCP_IRQ

) to go low. This indicates that the DSP has written a message to the output buffer and the

boot process is complete.

13.

Read the BOOT_SUCCESS message. The host then reads a message from the appropriate

communications port. Each.ULD file contains a checksum that is compared at the end of the boot

process. The CS4953xx sends a BOOT_SUCCESS message to the host if the checksum is correct

after the download.

If the checksum was incorrect, CS4953xx responds with a BOOT_ERROR_CHECKSUM message.

This indicates that the image read by the DSP is corrupted. The communications interface hardware

and code image integrity should be checked if this occurs.

14.

Repeat Steps 9-13 for all code images/Overlays. The host repeats these steps until all overlays for

the application have been successfully loaded. See the application note for more information on the

overlays necessary at start-up.

15.

Send the SOFT_RESET message. After reading the BOOT_SUCCESS message on the last code

image/overlay, the host must send a SOFT_RESET message which will cause the application code to

begin executing.

16.

Wait for IRQ low. The host then waits for SCP1_IRQ (or PCP_IRQ) to go low.

DS732UM10 Copyright 2010 Cirrus Logic, Inc 2-6

Page 21

Slave Boot Procedures

CS4953xx Hardware User’s Manual

17. Read the APP_START message. If code execution is successful, the CS4953xx sends out an

APP_START message. This indicates that the code has been initialized and can accept further

configuration messages. The host should not attempt further communication with the CS4953xx until

the APP_START message has been read.

If the CS4953xx does not send an application start message, the host must return to

18.

Send Hardware Configuration messages. The master boot procedure is completed. The operating

system on the CS4953xx is now ready for host configuration of hardware and software.

Hardware configuration messages are used to define the behavior of the CS4953xx’s audio ports.

19.

Send Software Configuration messages.The software configuration messages are specific to each

application. The application code User’s Guide for each application provides a list of all pertinent

configuration messages.

20.

Send the KICKSTART message. The CS4953xx application locks the PLL and begins processing

audio after receiving this message.

2.3.2 Slave Boot

The Slave Boot procedure is a sequence in which the external host is the bus master and directly loads

the CS4953xx application code. The system host controller has each of the five communication modes

available, as specified in Table 2-1. from either the serial control interface (SPI or I

control interface (Intel, multiplexed Intel, or Motorola modes). The boot messages used can be found in

Section 2.3.3 "Boot Messages" on page 2-10. For information on how to configure the CS4953xx

overlays, such as hardware configuration messages, software configuration messages, and the kick-start

message, please refer to AN288, “CS4953x x /CS4 97x xx Fir mware User’s Manual.”

Step 1.

2

C) or the parallel

2-7 Copyright 2010 Cirrus Logic, Inc. DS732UM10

Page 22

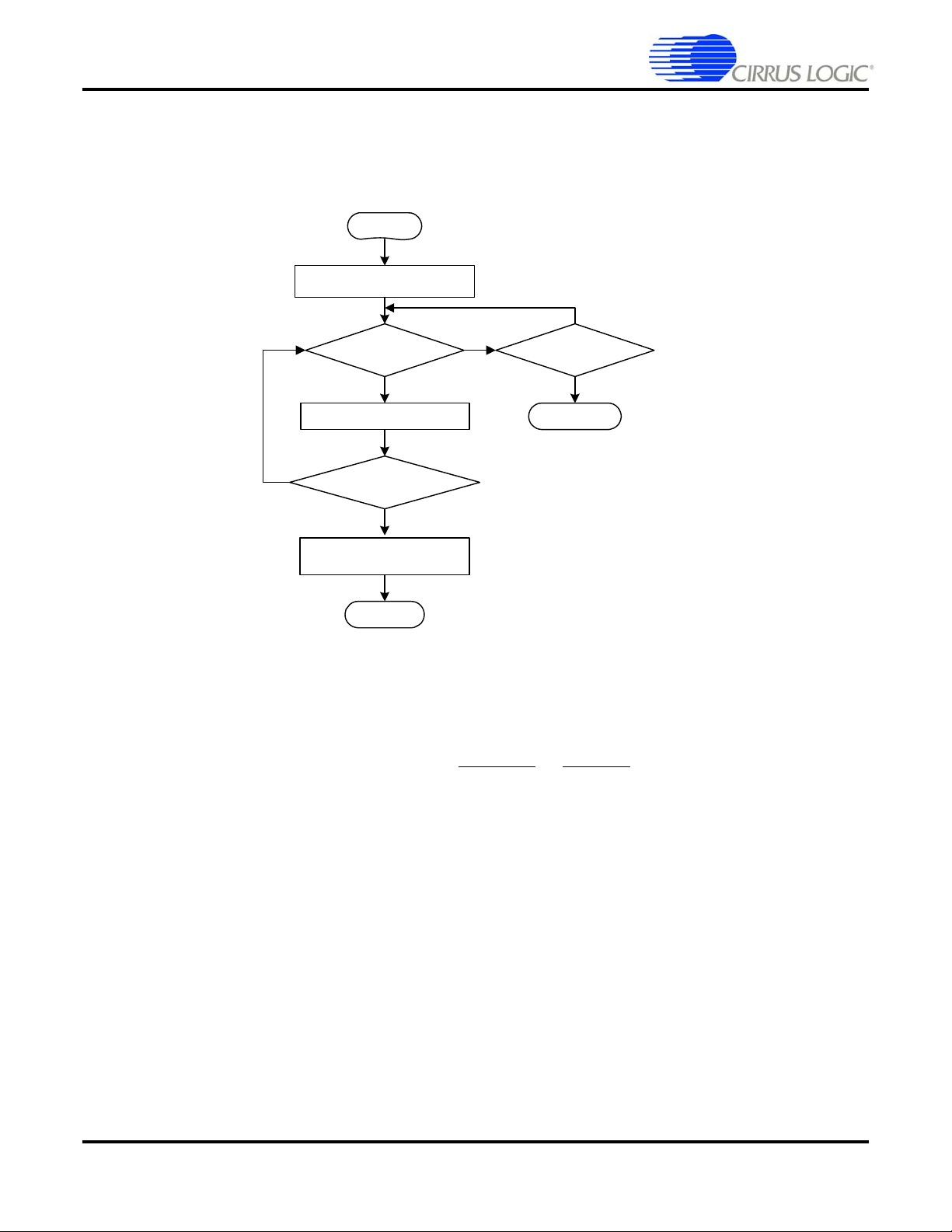

2.3.2.1 Performi ng a Slave Boot

.

n

Figure 2-3 shows the steps taken during a Slave boot. The procedure is discussed in Section 2.3.2.1.1..

START

Slave Boot Procedures

CS4953xx Hardware User’s Manual

RESET# (LOW)

SET HS[3:0] PINS FOR

OPERATIONAL MODE

RESET# (HIGH)

WAIT 50 μS

WRITE_* (SLAVE_BOOT)

WAIT 10 μS

READ_* (MSG)

==BOOT_START

WRITE_* (BOOT_ ASSIST_A.ULD FILE)

Or (boot_assist_xtal_div2_a*.uld)

NOTE 1

MSG

Y

N

EXIT(ERROR)

WRITE_*(SLAVE_BOOT)

READ_*(MSG)

==BOOT_START

WRITE_*(.ULD FILE)

READ_* (MSG)

BOOT_SUCCESS

Y

MORE .ULD FILES?

WRITE_* (SOF T_RESET)

READ_* (MSG)

MSG

MSG==

NOTE 2

N

EXIT (ERROR)

Y

N

EXIT(ERROR)

Y

N

WAIT 10 μS

N

EXIT (ERROR)

* is replaced with SCP, I2C, etc

depending on the com m unicatio

READ_* (M SG)

BOOT_SUCCESS

(SOFT_RESET_DSP_A)

NOTE 1

MSG==

Y

WRITE_*

N

EXIT(ERROR)

MSG ==APP _START

Y

SEND HARDWARE

CONFIGURATIONS

SEND FIRMWARE

CONFIGURATIONS

WRITE_* (KICKSTART)

protocol used.

NOTE 1. Read four bytes from the DSP.

IRQ will not drop for this read sequence.

NOTE 2. Obey IRQ for all reads from

this point forward.

DONE

Figure 2-3. Slave Boot Sequence

2.3.2.1.1 Slave Boot Procedure

1. Toggle RESET. A download sequence is started when the host holds the RESET pin low for the

required time. The mode pins (HS[4:0]) must be in the appropriate state to set the host

communication mode before and immediately after the rising edge of RESET

resistors are typically used to set the default state of the HS[4:0] pins.

. Pull-up and pull-down

2. Wait for 50

μs.

DS732UM10 Copyright 2010 Cirrus Logic, Inc 2-8

Page 23

Slave Boot Procedures

CS4953xx Hardware User’s Manual

3. Send the SLAVE_BOOT message. The host sends the appropriate SLAVE_BOOT message to the

CS4953xx using the control port specified (serial port/parallel port) and format specified (I

Intel, etc.) by the HS[4:0] pins at reset.

2

C, SPI,

4. Wait for 10

Read the BOOT_START message (See NOTE 1 in Figure 2- 3). If the initialization is successful,

5.

μS.

CS4953xx sends out the BOOT_START message and the host proceeds to Step 6.

If initialization fails, the host must return to

Step 1, and if failure is met again, the communication

timing and protocol should be inspected.

6.

The host sends the boot assist BOOT_ASSIST_A.uld file or boot_assist_xtal_div2_a*.uld (sets

XTAL_OUT =XTAL/2) to the CS4953xx DSP.

7. Wait 10

Read the BOOT_SUCCESS message (See NOTE 1 in Figure 2-3). The host then reads a message

8.

μS

from the appropriate communications port. Each.ULD file contains a checksum that is compared at

the end of the boot process. CS4953xx sends a BOOT_SUCCESS message to the host if the

checksum is correct after the download.

If the checksum was incorrect, CS4953xx responds with a BOOT_ERROR_CHECKSUM message.

This indicates that the image read by the DSP is corrupted. The communications interface hardware

and code image integrity should be checked if this occurs.

9.

Send the SOFT_RESET_DSP_A command: After reading the BO O T_SU CCES S mes s age on the

boot assist code image/overlay, the host must send this message. If boot_assist_xtal_div2_a*.uld was

sent in

10.

Send the SLAVE_BOOT message. The host sends the appropriate SLAVE_BOOT message to the

CS4953xx using the control port specified (serial port/parallel port) and format specified (I

Step 6, the XTAL_OUT frequency will change to XTAL/2 after the soft reset has taken place.

2

C, SPI,

Intel, etc.) by the HS[4:0] pins at reset.

11.

Wait for IRQ low . Th e host t hen wait s for SCP1_IR Q (or PCP_IRQ) to go low. (See NOTE 2 in Figure

2-3)

12.

Read the BOOT_START message. If the initialization is successful, CS4953xx sends out the

BOOT_START message and the host proceeds to Step 6.

13.

Send the ULD File. The host sends a.uld file to the CS4953xxx.

14.

Wait for IRQ low. The host then waits for SCP1_IRQ (or PCP_IRQ) to go low.

15.

Read the BOOT_SUCCESS message. The host then reads a message from the appropriate

communications port. Each.ULD file contains a checksum that is compared at the end of the boot

process. CS4953xx sends a BOOT_SUCCESS message to the host if the checksum is correct after

the download.

If the checksum was incorrect, CS4953xx responds with a BOOT_ERROR_CHECKSUM message.

This indicates that the image read by the DSP is corrupted. The communications interface hardware

and code image integrity should be checked if this occurs.

16.

Repeat Steps 10-15 for all code images/overlays. The host repeats these steps until all overlays

for the application have been successfully loaded. See the application note for more information on

the overlays necessary at start-up.

17.

Send the SOFT_RESET message. After reading the BOOT_SUCCESS message on the last code

image/overlay, the host must send a SOFT_RESET message which will cause the application code to

begin executing.

18.

Wait for IRQ low. The host then waits for SCP1_IRQ (or PCP_IRQ) to go low.

19.

Read the APP_START message. If code execution is successful, the CS4953xx sends out a

2-9 Copyright 2010 Cirrus Logic, Inc. DS732UM10

Page 24

Slave Boot Procedures

CS4953xx Hardware User’s Manual

APP_START message. This indicates that the code has been initialized and can accept further

configuration messages. The host should not attempt further communication with the CS4953xx until

the APP_START message has been read.

If the CS4953xx does not send an application start message, the host must return to

20.

Send Hardware Configuration messages. The slave boot procedure is completed. The operating

system on the CS4953xx is now ready for host configuration of hardware and software.

Hardware configuration messages are used to define the behavior of the CS4953xx’s audio ports. A

more detailed description of the hardware configurations can be found in Section x of this manual.

21.

Send Software Configuration messages.The software configuration messages are specific to each

application. The application code user’s guide for each application provides a list of all pertinent

configuration messages.

22.

Send the KICKSTART message(s). The CS4953xx application locks the PLL and begins processing

audio after receiving this message.

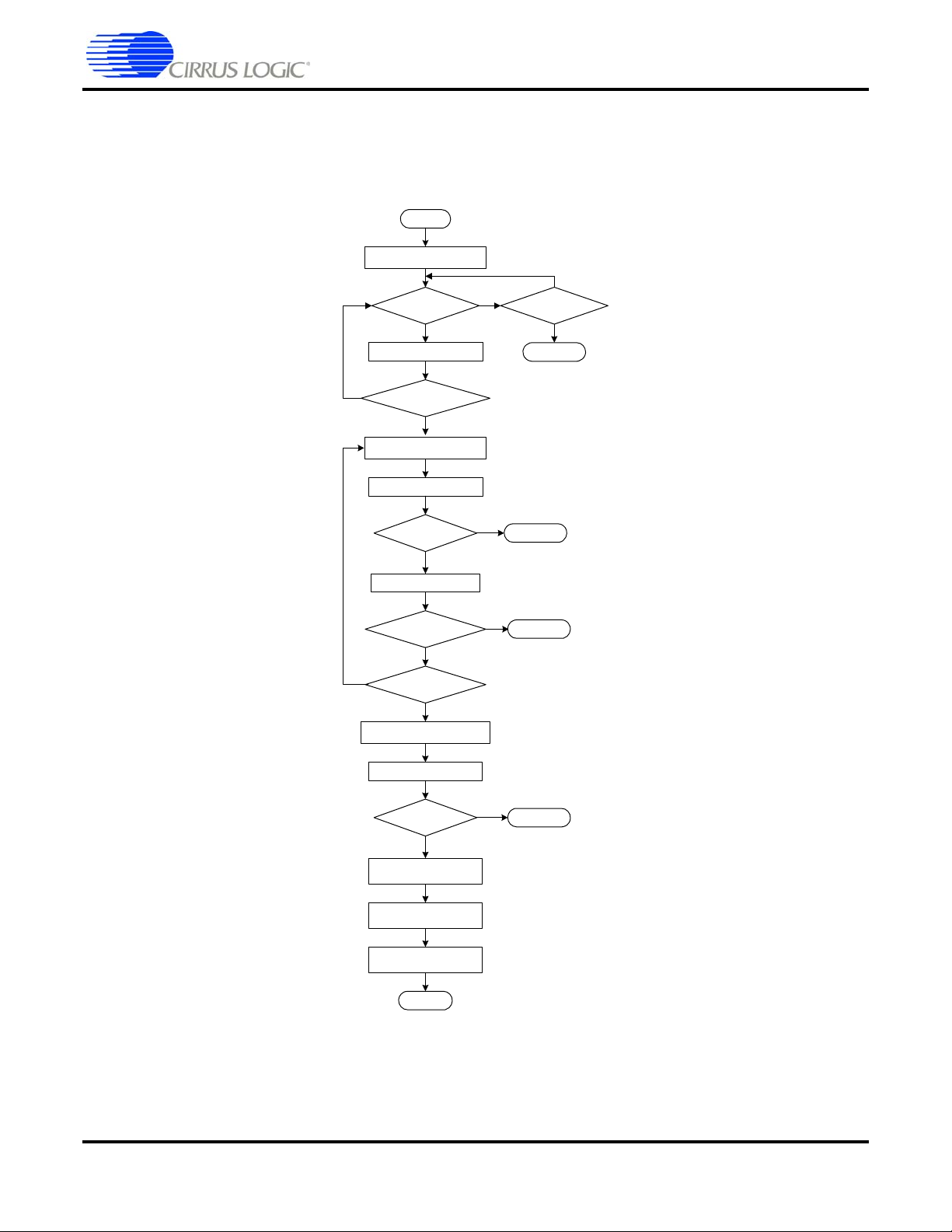

2.3.3 Boot Messages

The Slave Boot and Host-Controlled Master Boot procedures use a number of messages to configure and

synchronize the boot process. Please use the messages listed below when implementing the boot

process as a part of the system host controller firmware.

2.3.3.1 Slave Boot

Step 1.

Table 2-2. SLAVE_BOOT message for CS4953xx

MNEMONIC VALUE

SLAVE_BOOT 0x8000 0000

The SLAVE_BOOT message is used when the system host controller will send each .uld file directly to the