CATALYST CAT1026, CAT1027 Service Manual

查询CAT1027LI-25供应商

CAT1026, CAT1027

Dual Voltage Supervisory Circuits with

2

C Serial 2k-bit CMOS EEPROM

I

FEATURES

Precision VCC Power Supply Voltage Monitor

— 5V, 3.3V and 3V systems

— Five threshold voltage options

Additional voltage monitoring

— Externally adjustable down to 1.25V

Watchdog timer (CAT1027 only)

Active High or Low Reset

— Valid reset guaranteed at V

2

400kHz I

2.7V to 5.5V Operation

Low power CMOS technology

16-Byte Page Write Buffer

Built-in inadvertent write protection

1,000,000 Program/Erase cycles

Manual Reset capability

100 year data retention

Industrial and extended temperature ranges

8-pin DIP, SOIC, TSSOP, MSOP or TDFN

(3 x 3mm foot-print) packages

— TDFN max height is 0.8mm

For Ordering Information details, see page 19.

C Bus

CC

= 1V

DESCRIPTION

The CAT1026 and CAT1027 are complete memory

and supervisory solutions for microcontroller-based

systems. A 2k-bit serial EEPROM memory and a

system power supervisor with brown-out protection

are integrated together in low power CMOS techno–

logy. Memory interface is via a 400kHz I

The CAT1026 and CAT1027 provide a precision V

sense circuit with five reset threshold voltage options

that support 5V, 3.3V and 3V systems. The power

2

C bus.

CC

supply monitor and reset circuit protects memory and

systems controllers during power up/down and

against brownout conditions. If power supply voltages

are out of tolerance reset signals become active

preventing the system microcontroller, ASIC, or

peripherals from operating.

The CAT1026 features two open drain reset outputs:

one (RESET) drives high and the other (RESET

drives low whenever V

Reset outputs become inactive typically 200 ms after

the supply voltage exceeds the reset threshold value.

With both active high and low reset signals, interface

to microcontrollers and other ICs is simple. CAT1027

has only a RESET

can be used as an input for push-button manual reset

capability.

The CAT1026 and CAT1027 provide an auxiliary

voltage sensor input, V

a second system supply. The auxiliary high impedance comparator drives the open drain output, V

whenever the sense voltage is below 1.25V threshold.

The CAT1027 is designed with a 1.6 second

watchdog timer circuit that resets a system to a known

state if software or a hardware glitch halts or “hangs”

the system. The CAT1027 features a watchdog timer

interrupt input, WDI.

The on-chip 2k-bit EEPROM memory features a 16-byte

page. In addition, hardware data protection is provided

by a V

whenever V

reaches the reset threshold during power up.

Available packages include 8-pin DIP and surface

mount, 8-pin SO, 8-pin TSSOP, 8-pin TDFN and 8-pin

MSOP packages. The TDFN package thickness is

0.8mm maximum. TDFN footprint is 3 x 3mm.

¯¯¯¯¯¯

sense circuit that prevents writes to memory

CC

CC

output. In addition, the RESET

falls below the reset threshold or until VCC

falls below the threshold.

CC

¯¯¯¯¯¯

, which is used to monitor

SENSE

¯¯¯¯¯¯

pin

LOW

)

,

© 2007 Catalyst Semiconductor, Inc. 1 Doc. No. 3010 Rev. L

Characteristics subject to change without notice

CAT1026, CAT1027

L

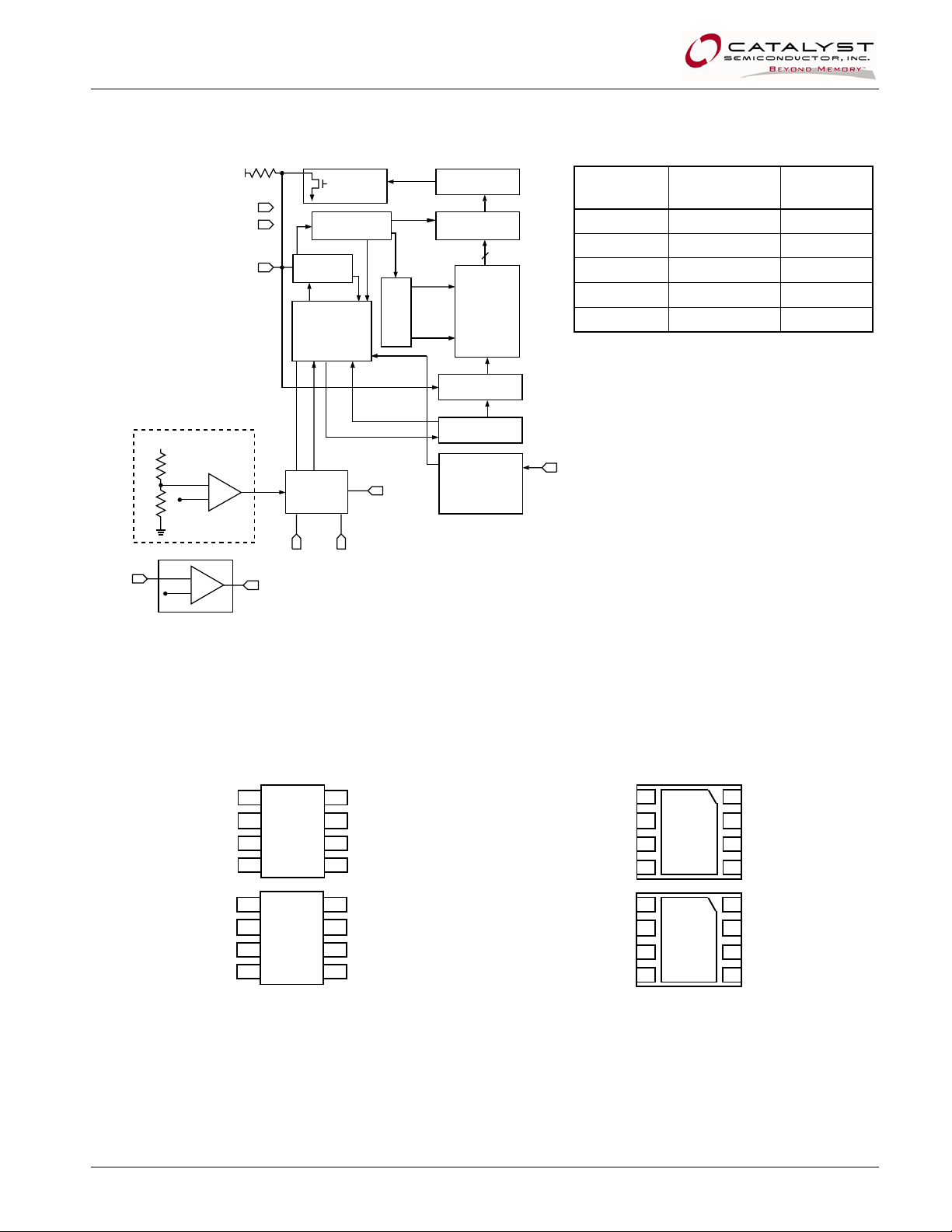

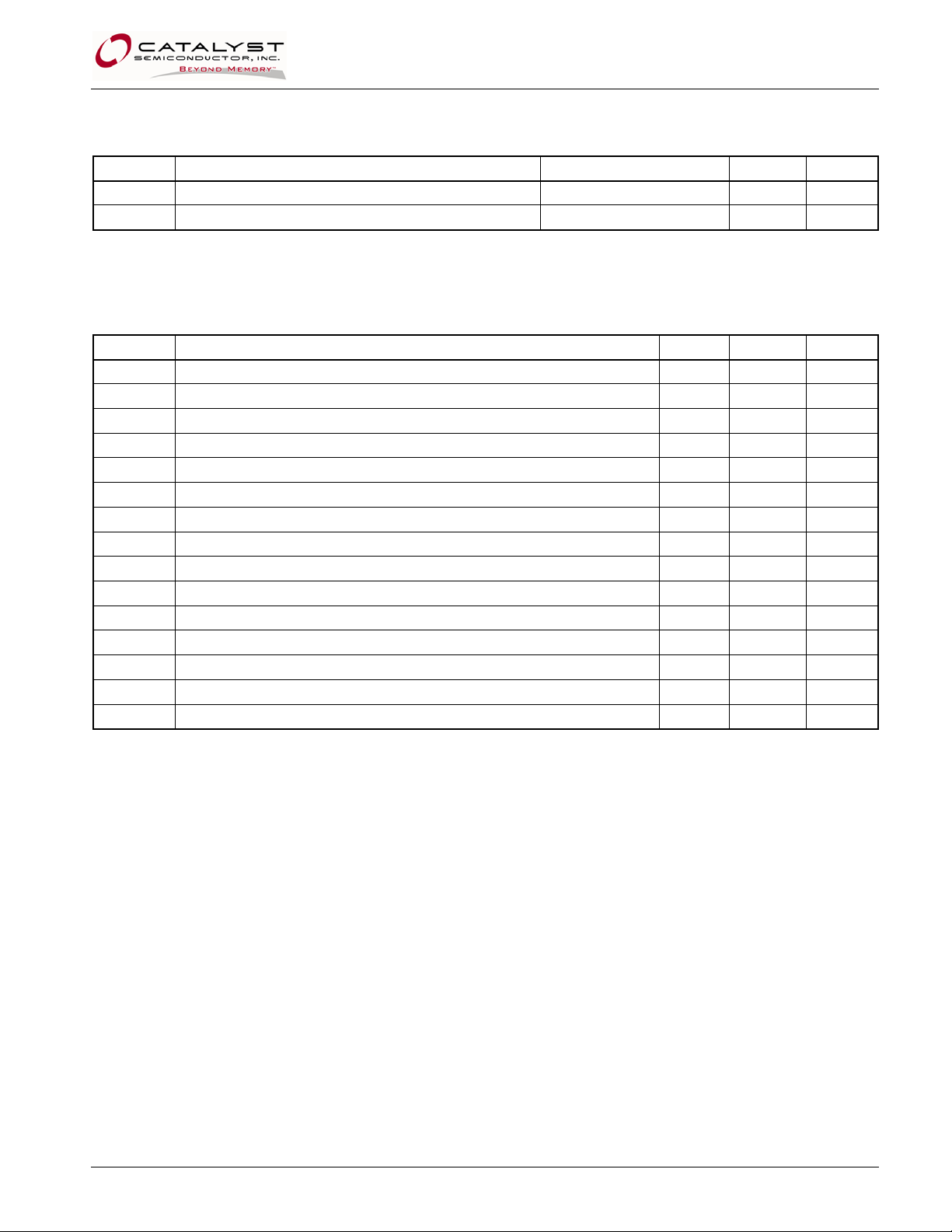

BLOCK DIAGRAM

EXTERNAL LOAD

V

CC

V

SS

SDA

V

CC

V

CC Monitor

+

-

V

REF

AuxiliaryVoltage Monitor

V

SENSE

V

REF

+

-

(CAT1026)

V

LOW

START/STOP

RESET

Controller

RESET

D

OUT

ACK

WORDADDRESS

BUFFERS

LOGIC

CONTROL

LOGIC

RESET

XDEC

WDI

(CAT1027)

SENSEAMPS

SHIFT REGISTERS

COLUMN

DECODERS

2kbit

EEPROM

DATA IN STORAG E

HI GH VOLTAGE/

TIMING CONTROL

STATE COUNTERS

SLAVE

ADDRESS

COMPARATORS

RESET THRESHOLD OPTION

Part Dash

Number

-45 4.50 4.75

-42 4.25 4.50

-30 3.00 3.15

-28 2.85 3.00

-25 2.55 2.70

SC

Minimum

Threshold

Maximum

Threshold

PIN CONFIGURATION

DIP Package (L)

SOIC Package (W)

TSSOP Package (Y)

MSOP Package (Z)

V

1 8 VCC

LOW

¯¯¯¯¯¯

RESET

¯¯¯¯¯¯

RESET

2 7 RESET

V

SENSE

VSS 4 5 SDA

V

LOW

V

SENSE

VSS 4 5 SDA

CAT1026

3 6 SCL

1 8 VCC

2 7 WDI

CAT1027

3 6 SCL

(Bottom View)

TDFN Package: 3mm x 3mm

0.8mm maximum height - (ZD4)

VCC8 1 V

RESET 7 2

SCL 6

SDA 5 4 VSS

VCC8 1 V

WDI 7 2

SCL 6

SDA 5 4 VSS

CAT1026

CAT1027

3 V

3 V

LOW

¯¯¯¯¯¯

RESET

SENSE

LOW

¯¯¯¯¯¯

RESET

SENSE

Doc. No. 3010 Rev. L 2 © 2007 Catalyst Semiconductor, Inc.

Characteristics subject to change without notice

CAT1026, CAT1027

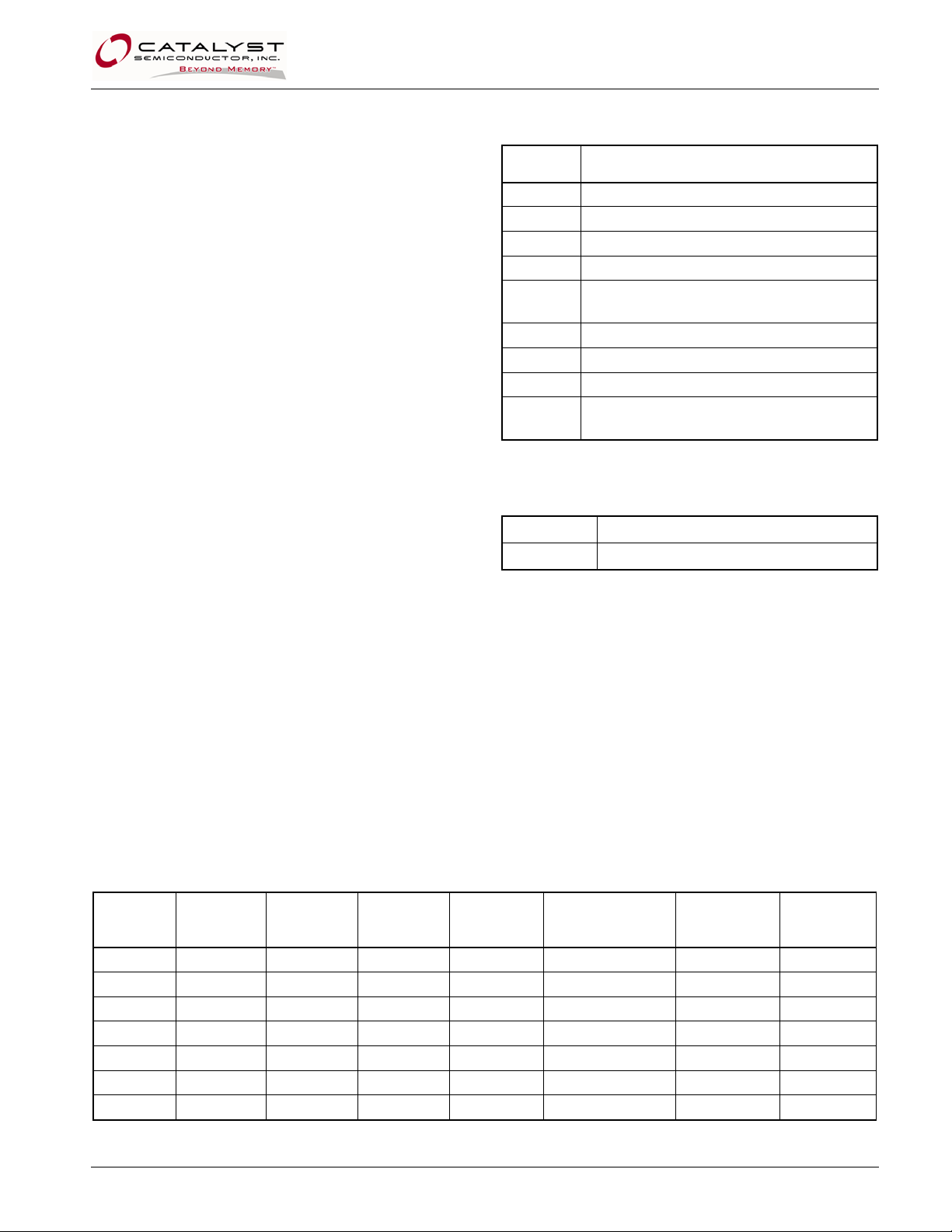

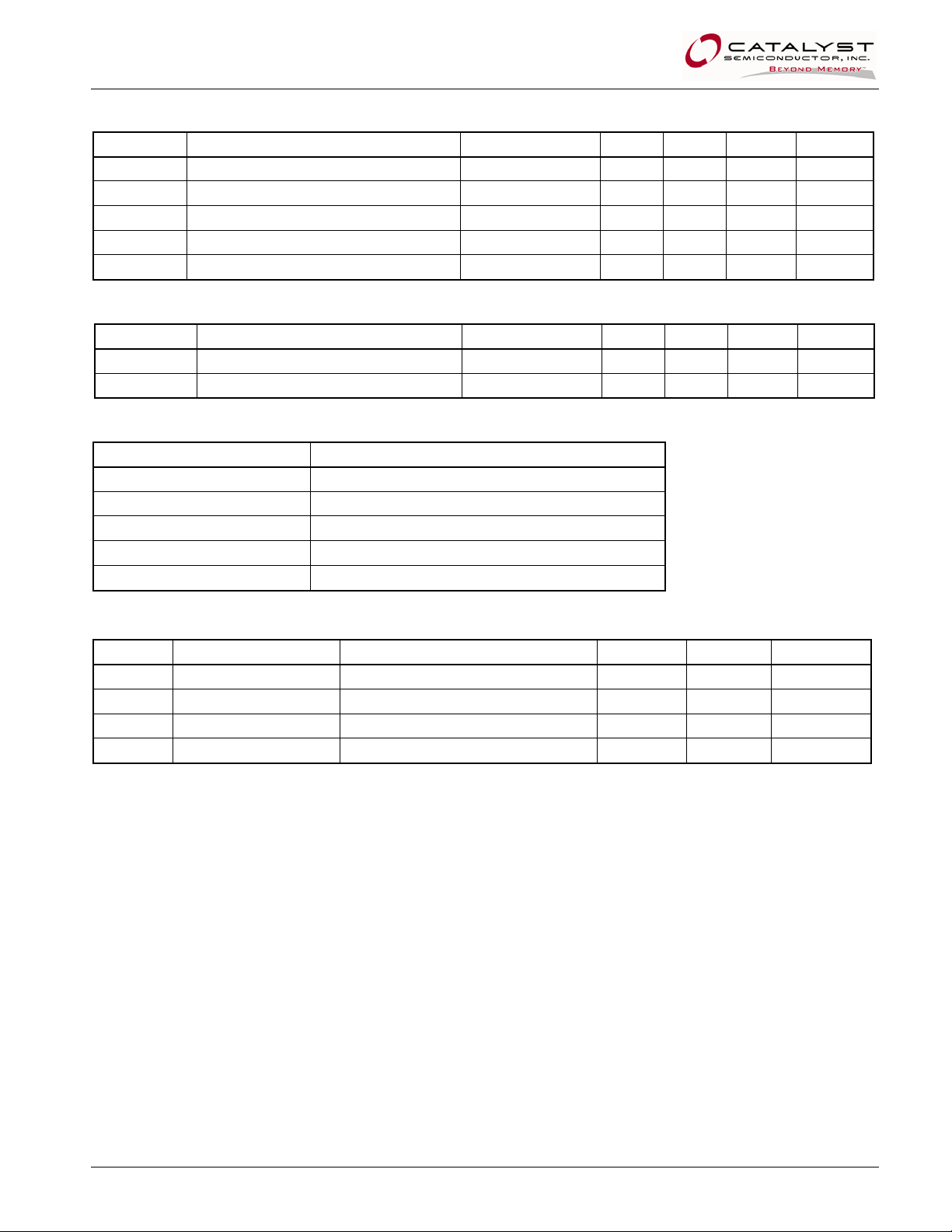

PIN DESCRIPTION

RESET/RESET

(RESET CAT1026 Only)

These are open drain pins and RESET

as a manual reset trigger input. By forcing a reset

condition on the pin the device will initiate and

maintain a reset condition. The RESET pin must be

connected through a pull-down resistor, and the

¯¯¯¯¯¯

RESET

resistor.

SDA: SERIAL DATA ADDRESS

The bidirectional serial data/address pin is used to

transfer all data into and out of the device. The SDA

pin is an open drain output and can be wire-ORed

with other open drain or open collector outputs.

SCL: SERIAL CLOCK

Serial clock input.

V

SENSE

The V

compared against CAT1026 and CAT1027 internal

reference voltage of 1.25V typically. Whenever the

input voltage is lower than 1.25V, the open drain V

output will be driven low. An external resistor divider is

used to set the voltage level to be sensed. Connect

V

SENSE

¯¯¯¯¯¯

pin must be connected through a pull-up

: AUXILIARY VOLTAGE MONITOR INPUT

SENSE

to VCC if unused.

: RESET OUTPUTs

¯¯¯¯¯¯

input is a second voltage monitor which is

can be used

LOW

PIN FUNCTION

Pin

Name

¯¯¯¯¯¯

RESET

VSS Ground

SDA Serial Data/Address

SCL Clock Input

RESET

VCC Power Supply

V

SENSE

V

LOW

WDI

Function

Active Low Reset Input/Output

Active High Reset Output

(CAT1026 only)

Auxiliary Voltage Monitor Input

Auxiliary Voltage Monitor Output

Watchdog Timer Interrupt

(CAT1027 only)

OPERATING TEMPERATURE RANGE

Industrial -40ºC to 85ºC

Extended -40ºC to 125ºC

: AUXILIARY VOLTAGE MONITOR OUTPUT

V

LOW

This open drain output goes low when V

than 1.25V and goes high when V

reference voltage.

WDI (CAT1027 Only): WATCHDOG TIMER INTERRUPT

Watchdog Timer Interrupt Input is used to reset the

watchdog timer. If a transition from high to low or low

to high does not occur every 1.6 seconds, the RESET

outputs will be driven active.

SENSE

is less

SENSE

exceeds the

CAT10XX FAMILY OVERVIEW

Manual

Device

CAT1021

CAT1022

CAT1023

CAT1024

CAT1025

CAT1026

CAT1027

For supervisory circuits with embedded 16k EEPROM, please refer to the CAT1161, CAT1162 and CAT1163

data sheets.

© 2007 Catalyst Semiconductor, Inc. 3 Doc. No. 3010 Rev. L

Characteristics subject to change without notice

Reset

Input Pin

Watchdog

Watchdog

Monitor

Pin

SDA

SDA 2k

WDI

2k

Write

Protection

Pin

Independent

Auxiliary

Voltage Sense

RESET:

Active High

and LOW

WDI

2k

EEPROM

2k

2k

2k

2k

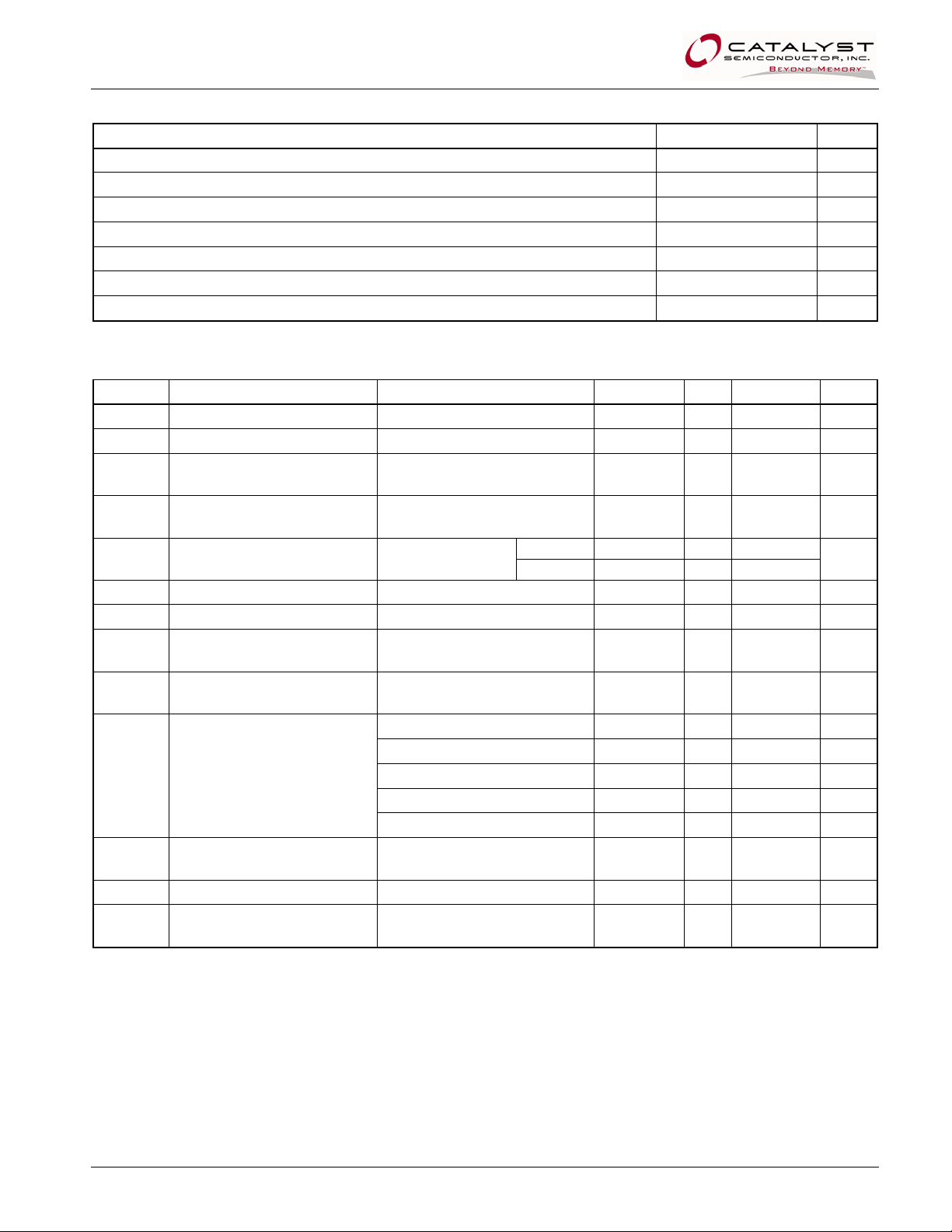

CAT1026, CAT1027

ABSOLUTE MAXIMUM RATINGS

Parameters Ratings Units

Temperature Under Bias –55 to +125 ºC

Storage Temperature –65 to +150 ºC

Voltage on any Pin with Respect to Ground

VCC with Respect to Ground –2.0 to 7.0 V

Package Power Dissipation Capability (TA = 25°C) 1.0 W

Lead Soldering Temperature (10 secs) 300 ºC

Output Short Circuit Current

D.C. OPERATING CHARACTERISTICS

V

= 2.7V to 5.5V and over the recommended temperature conditions unless otherwise specified.

CC

Symbol Parameter Test Conditions Min Typ Max Units

ILI Input Leakage Current VIN = GND to Vcc -2 10 µA

ILO Output Leakage Current VIN = GND to Vcc -10 10 µA

I

CC1

I

CC2

Power Supply Current

(Write)

Power Supply Current

(Read)

ISB Standby Current

(4)

V

Input Low Voltage -0.5 0.3 x Vcc V

IL

(4)

V

Input High Voltage 0.7 x Vcc Vcc + 0.5 V

IH

VOL

VOH

Output Low Voltage

¯¯¯¯¯¯

(SDA, RESET

)

Output High Voltage

(RESET)

VTH Reset Threshold

V

RVALID

V

V

RT

REF

Reset Output Valid V

Voltage

(5)

Reset Threshold Hysteresis 15 mV

Auxiliary Voltage Monitor

Threshold

(1)

(2)

–2.0 to VCC + 2.0 V

(3)

100 mA

f

= 400kHz

SCL

= 5.5V

V

CC

f

= 400kHz

SCL

= 5.5V

V

CC

Vcc = 5.5V,

= GND or Vcc

V

IN

I

= 3mA

OL

= 2.7V

V

CC

I

= -0.4mA

OH

= 2.7V

V

CC

CAT1026 50

CAT1027 60

3 mA

1 mA

µA

0.4 V

Vcc - 0.75 V

CAT102x-45 (VCC = 5.0V) 4.50 4.75 V

CAT102x-42 (VCC = 5.0V) 4.25 4.50

CAT102x-30 (VCC = 3.3V) 3.00 3.15

CAT102x-28 (VCC = 3.3V) 2.85 3.00

= 3.0V) 2.55 2.70

CC

CC

CAT102x-25 (V

1.00 V

1.2 1.25 1.3 VS

Notes:

(1) Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this

specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

(2) The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DC

voltage on output pins is V

(3) Output shorted for no more than one second. No more than one output shorted at a time.

min and VIH max are reference values only and are not tested.

(4) V

IL

(5) This parameter is tested initially and after a design or process change that affects the parameter. Not 100% tested.

© 2007 Catalyst Semiconductor, Inc. 4 Doc. No. 3010 Rev. L

Characteristics subject to change without notice

+0.5V, which may overshoot to VCC +2.0V for periods of less than 20 ns.

CC

CAT1026, CAT1027

CAPACITANCE

T

= 25ºC, f = 1.0MHz, VCC = 5V

A

Symbol Test Test Conditions Max Units

(1)

C

Output Capacitance V

OUT

(1)

C

Input Capacitance VIN = 0V 6 pF

IN

AC CHARACTERISTICS

= 2.7V to 5.5V and over the recommended temperature conditions, unless otherwise specified.

V

CC

Memory Read & Write Cycle

(2)

Symbol Parameter Min Max Units

f

Clock Frequency 400 kHz

SCL

tSP Input Filter Spike Suppression (SDA, SCL) 100 ns

t

Clock Low Period 1.3 µs

LOW

t

Clock High Period 0.6 µs

HIGH

(1)

t

SDA and SCL Rise Time 300 ns

R

(1)

t

SDA and SCL Fall Time 300 ns

F

t

Start Condition Hold Time 0.6 µs

HD; STA

t

Start Condition Setup Time (for a Repeated Start) 0.6 µs

SU; STA

t

Data Input Hold Time 0 ns

HD; DAT

t

Data Input Setup Time 100 ns

SU; DAT

t

Stop Condition Setup Time 0.6 µs

SU; STO

tAA SCL Low to Data Out Valid 900 ns

tDH Data Out Hold Time 50 ns

(1)

t

Time the Bus must be Free Before a New Transmission Can Start 1.3 µs

BUF

(3)

t

Write Cycle Time (Byte or Page) 5 ms

WC

= 0V 8 pF

OUT

Notes:

(1) This parameter is characterized initially and after a design or process change that affects the parameter. Not 100% tested.

(2) Test Conditions according to “AC Test Conditions” table.

(3) The write cycle time is the time from a valid stop condition of a write sequence to the end of the internal program/erase cycle. During the

write cycle, the bus interface circuits are disabled, SDA is allowed to remain high and the device does not respond to its slave address.

© 2007 Catalyst Semiconductor, Inc. 5 Doc. No. 3010 Rev. L

Characteristics subject to change without notice

CAT1026, CAT1027

VOLTAGE MONITOR AND RESET CIRCUIT AC CHARACTERISTICS

Symbol Parameter Test Conditions Min Typ Max Units

t

Reset Timeout Note 2 130 200 270 ms

PURST

t

VTH to RESET Output Delay Note 3 5 µs

RDP

t

VCC Glitch Reject Pulse Width Note 4, 5 30 ns

GLITCH

tWD Watchdod Timeout Note 1 1.0 1.6 2.1 s

t

V

RPD2

SENSE

to V

Delay Note 5 5 µs

LOW

POWER-UP TIMING

(6), (7)

Symbol Parameter Test Conditions Min Typ Max Units

t

Power-Up to Read Operation 270 ms

PUR

t

Power-Up to Write Operation 270 ms

PUW

AC TEST CONDITIONS

Parameter Test Conditions

Input Pulse Voltages 0.2VCC to 0.8VCC

Input Rise and Fall Times 10ns

Input Reference Voltages 0.3VCC, 0.7VCC

Output Reference Voltages 0.5VCC

Output Load Current Source: I

= 3mA; CL = 100pF

OL

RELIABILITY CHARACTERISTICS

Symbol Parameter Reference Test Method Min Max Units

(6)

N

Endurance MIL-STD-883, Test Method 1033 1,000,000 Cycles/Byte

END

(6)

T

Data Retention MIL-STD-883, Test Method 1008 100 Years

DR

(6)

V

ESD Susceptibility MIL-STD-883, Test Method 3015 2000 Volts

ZAP

(6)(8)

I

Latch-Up JEDEC Standard 17 100 mA

LTH

Notes:

(1) Test Conditions according to “AC Test Conditions” table.

(2) Power-up, Input Reference Voltage V

(3) Power-Down, Input Reference Voltage V

Glitch Reference Voltage = V

(4) V

CC

5) 0 < V

(6) This parameter is characterized initially and after a design or process change that affects the parameter. Not 100% tested.

(7) t

PUR

(8) Latch-up protection is provided for stresses up to 100mA on input and output pins from -1 V to VCC + 1 V.

SENSE

and t

- VCC, V

are the delays required from the time VCC is stable until the specified memory operation can be initiated.

PUW

Output Reference Voltage and Load according to “AC Test Conditions” Table.

LOW

= VTH, Reset Output Reference Voltage and Load according to “AC Test Conditions” Table

CC

= VTH, Reset Output Reference Voltage and Load according to “AC Test Conditions” Table

CC

; Based on characterization data

THmin

Doc. No. 3010 Rev. L 6 © 2007 Catalyst Semiconductor, Inc.

Characteristics subject to change without notice

Loading...

Loading...