CATALYST CAT1024, CAT1025 Preliminary Information

T

T

查询CAT1024JE-25TE13供应商

Preliminary Information

CAT1024, CAT1025

Supervisory Circuits with I2C Serial 2k-bit CMOS EEPROM and Manual Reset

FEATURES

■ Precision power supply voltage monitor

— 5V, 3.3V and 3V systems

— Five threshold voltage options

■ Active high or low reset

— Valid reset guaranteed at V

■ 400kHz I

2

C bus

CC

= 1V

■ 3.0V to 5.5V operation

■ Low power CMOS technology

DESCRIPTION

The CAT1024 and CAT1025 are complete memory and

supervisory solutions for microcontroller-based systems.

A 2k-bit serial EEPROM memory and a system power

supervisor with brown-out protection are integrated

together in low power CMOS technology. Memory

interface is via a 400kHz I2C bus.

The CAT1025 provides a precision VCC sense circuit

and two open drain outputs: one (RESET) drives high

and the other (RESET) drives low whenever VCC falls

below the reset threshold voltage. The CAT1025 also

has a Write Protect input (WP). Write operations are

disabled if WP is connected to a logic high.

The CAT1024 also provides a precision VCC sense

circuit, but has only a RESET output and does not have

a Write Protect input.

The power supply monitor and reset circuit protect

memory and system controllers during power up/down

and against brownout conditions. Five reset threshold

■ 16-Byte page write buffer

■ Built-in inadvertent write protection

— WP pin (CAT1025)

■ 1,000,000 Program/Erase cycles

■ Manual reset input

■ 100 year data retention

■ 8-pin DIP, SOIC, TSSOP, MSOP &

TDFN (3x3mm foot print) packages

■ Industrial and extended temperature ranges

voltages support 5V, 3.3V and 3V systems. If power supply

voltages are out of tolerance reset signals become active,

preventing the system microcontroller, ASIC or peripherals

from operating. Reset signals become inactive typically 200

ms after the supply voltage exceeds the reset threshold

level. With both active high and low reset signals, interface

to microcontrollers and other ICs is simple. In addition, the

RESET pin or a separate input, MR, can be used as an input

for push-button manual reset capability.

The CAT1024/25 memory features a 16-byte page. In

addition, hardware data protection is provided by a V

sense circuit that prevents writes to memory whenever V

falls below the reset threshold or until VCC reaches the reset

threshold during power up.

Available packages include an 8-pin DIP, 8-pin SOIC, 8-pin

TSSOP, 8-pin TDFN and 8-pin MSOP. The TDFN package

thickness is 0.8mm maximum. TDFN footprint is 3x3mm.

N

E

G

F

O

R

L

A

H

L

E

A

E

E

E

E

TM

R

D

F

CC

CC

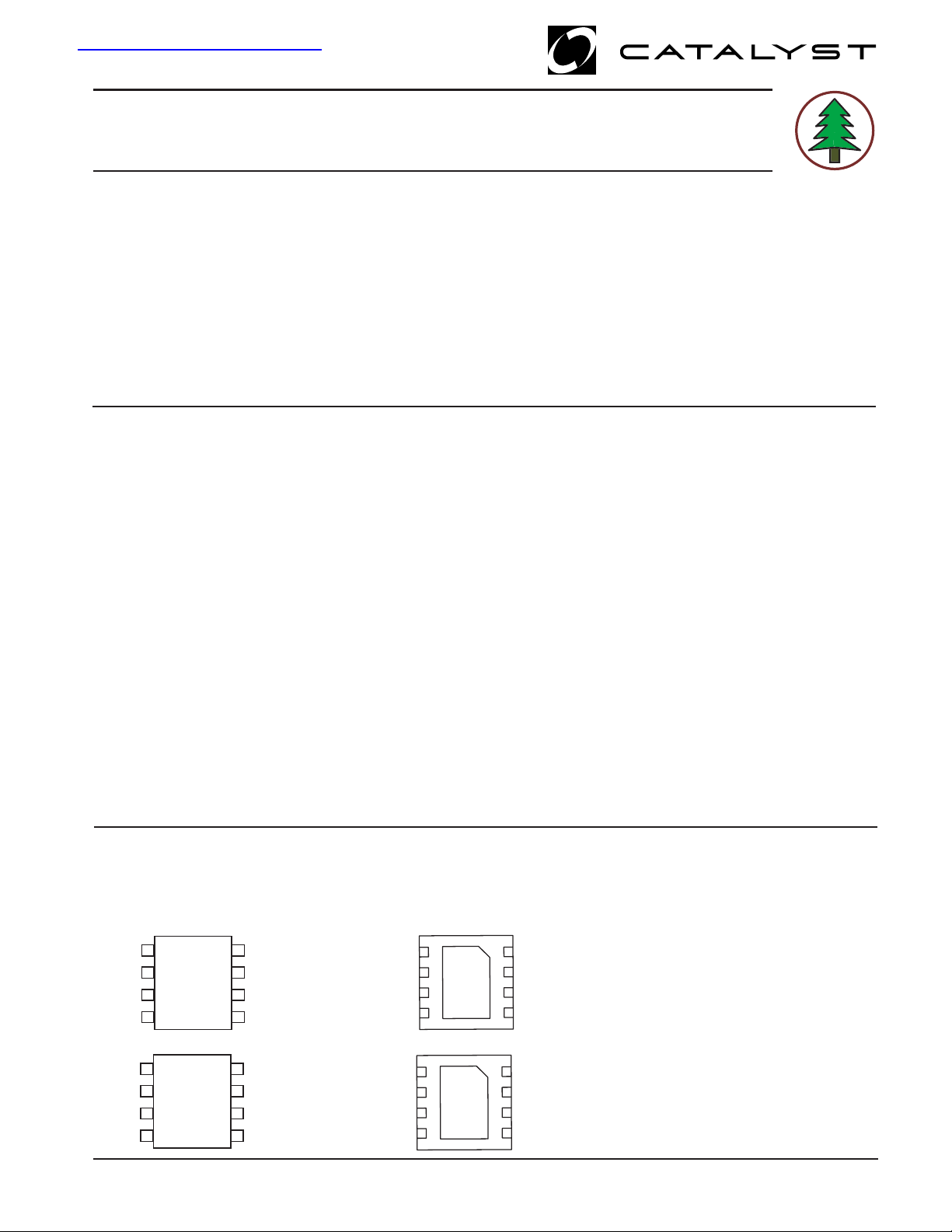

PIN CONFIGURATION

DIP Package (P, L)

SOIC Package (J, W)

TSSOP Package (U, Y)

MSOP Package (R, Z)

1

MR V

RESET

RESET

RESET

© 2004 by Catalyst Semiconductor, Inc.

Characteristics subject to change without notice

2

CAT1024

NC

3

V

4

SS

1

MR V

2

CAT1025

3

V

4

SS

8

CC

NC

7

SCL

6

SDA

5

8

V

CC

CC

WP

7

SCL

6

SDA

5

(Bottom View)

TDFN Package: 3mm x 3mm

0.8mm maximum height - (RD4, ZD4)

V

CC

NC

SCL

SDA

V

CC

WP

SCL

SDA

8

7

6

5

8

7

6

5

CAT1024

CAT1025

1

2

3

4

1

2

3

4

MR

RESE

NC

V

SS

MR

RESE

RESET

V

SS

Doc No. 3008, Rev. M

CAT1024, CAT1025

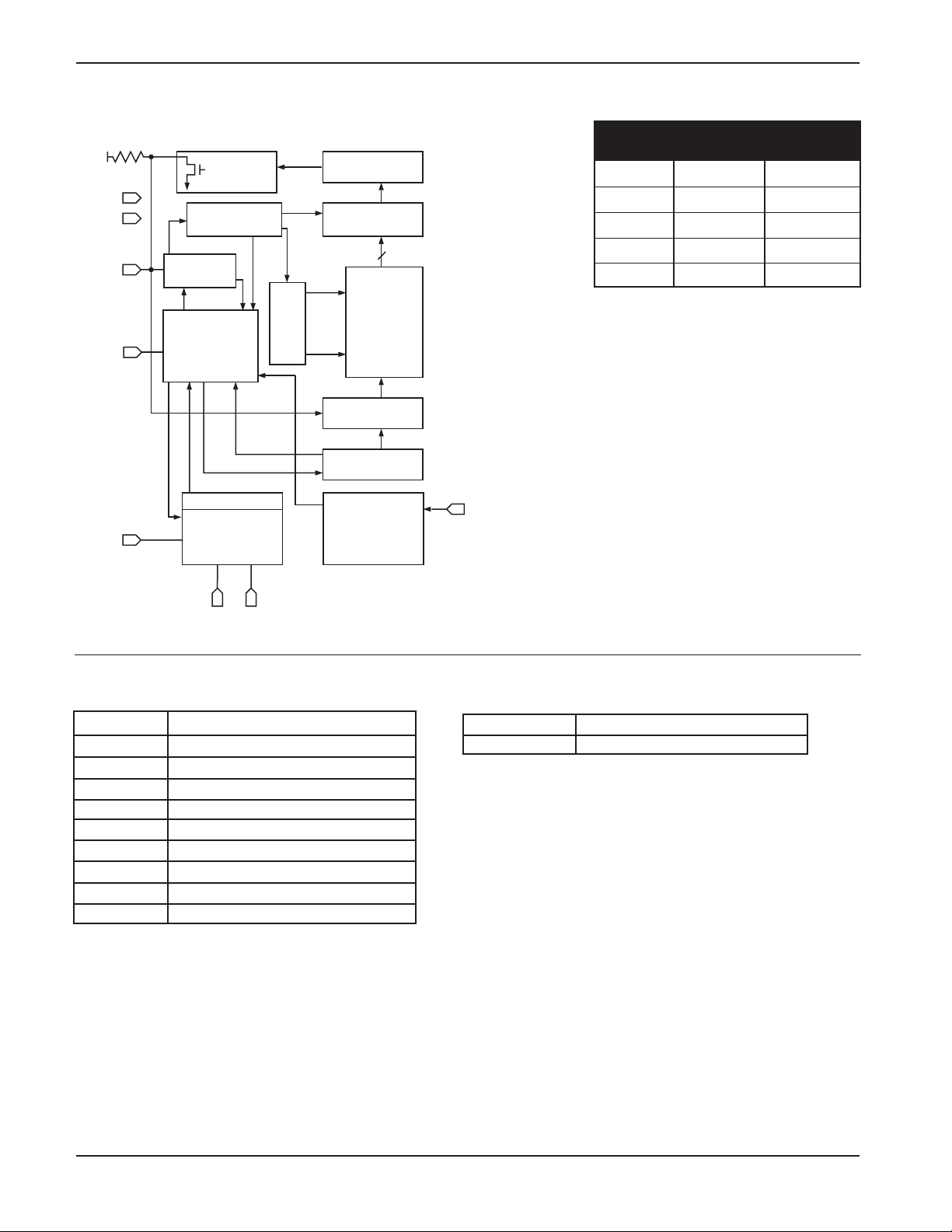

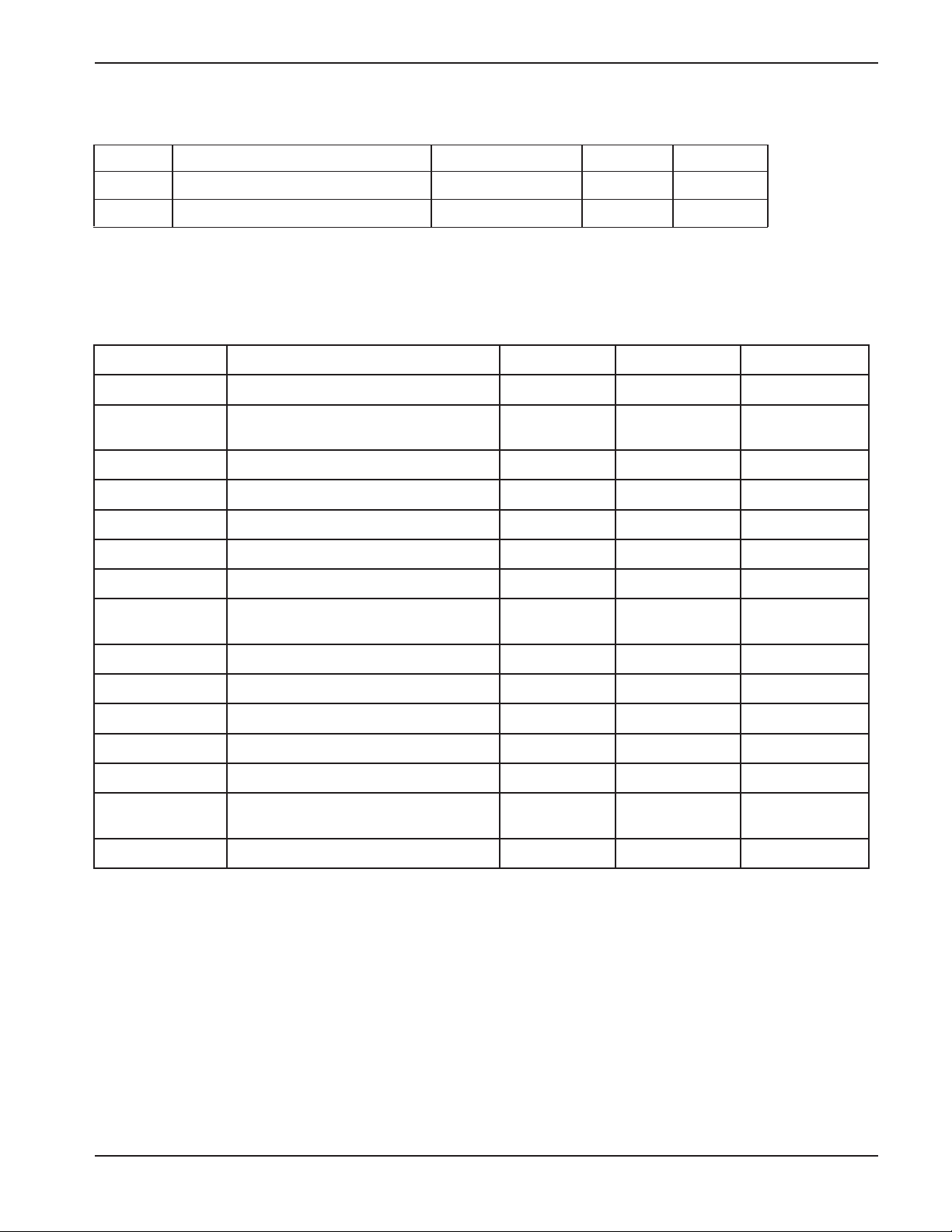

BLOCK DIAGRAM — CAT1024, CAT1025

EXTERNAL LOAD

SENSE AMPS

SHIFT REGISTERS

COLUMN

DECODERS

2kbit

EEPROM

DATA IN STORAGE

HIGH VOL T A GE/

TIMING CONTROL

STATE COUNTERS

SLAVE

ADDRESS

COMPARATORS

V

CC

V

SS

SDA

WP*

MR

D

ACK

WORD ADDRESS

BUFFERS

START/STOP

LOGIC

CONTROL

LOGIC

RESET Controller

Precision

Vcc Monitor

OUT

XDEC

Threshold Voltage Options

Part Dash Minimum Maximum

Number Threshold Threshold

-45 4.50 4.75

-42 4.25 4.50

-30 3.00 3.15

-28 2.85 3.00

-25 2.55 2.70

SCL

*

*CAT1025 Only

RESET RESET

PIN FUNCTIONS

Pin Name Function

NC No Connect

RESET Active Low Reset Input/Output

V

SS

SDA Serial Data/Address

SCL Clock Input

RESET Active High Reset Output (CAT1025 only)

V

CC

WP Write Protect (CAT1025 only)

MR Manual Reset Input

Ground

Power Supply

OPERATING TEMPERATURE RANGE

Industrial -40˚C to 85˚C

Extended -40˚C to 125˚C

Doc. No. 3008, Rev. M

2

PIN DESCRIPTION

CAT1024, CAT1025

RESET/

RESETRESET

RESET: RESET OUTPUTS

RESETRESET

(RESET CAT1025 Only)

These are open drain pins and RESET can be used as a

manual reset trigger input. By forcing a reset condition on

the pin the device will initiate and maintain a reset condition.

The RESET pin must be connected through a pull-down

resistor, and the RESET pin must be connected through a

pull-up resistor.

SDA: SERIAL DATA ADDRESS

The bidirectional serial data/address pin is used to transfer

all data into and out of the device. The SDA pin is an open

drain output and can be wire-ORed with other open drain

or open collector outputs.

SCL: SERIAL CLOCK

Serial clock input.

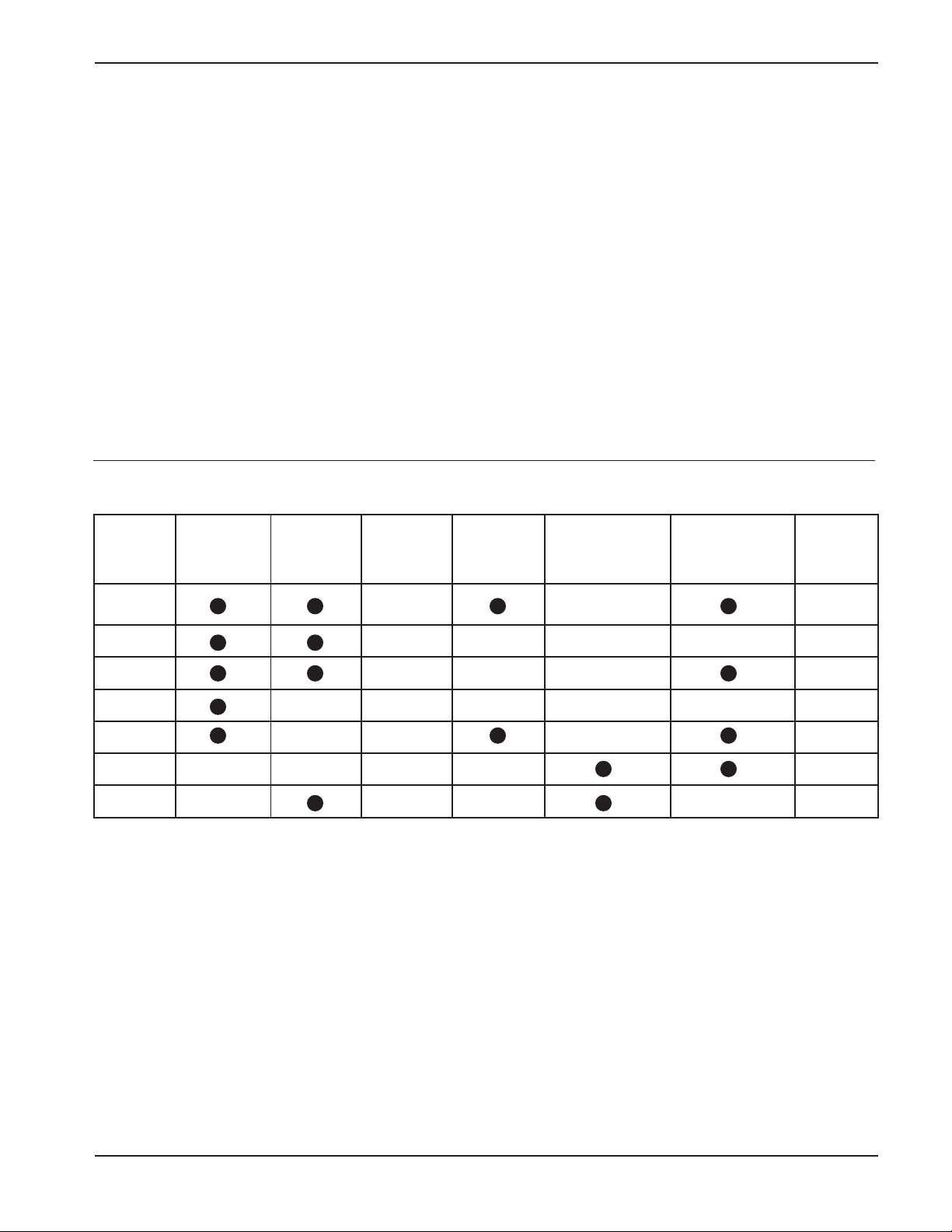

CAT10XX FAMILY OVERVIEW

launaM

eciveD

teseR

niPtupnI

godhctaW

godhctaW

rotinoM

niP

MR:MR:

MR: MANUAL RESET INPUT

MR:MR:

Manual Reset input is a debounced input that can be

connected to an external source for Manual Reset.

Pulling the MR input low will generate a Reset condition.

Reset outputs are active while MR input is low and for

the reset timeout period after MR returns to high. The

input has an internal pull-up resistor.

WP (CAT1025 Only): WRITE PROTECT INPUT

When tied to V

or left unconnected write operations

SS

to the entire array are allowed. When tied to VCC, the

entire array is protected. This input has an internal pull

down resistor.

etirW

noitcetorP

niP

tnednepednI

yrailixuA

esneSegatloV

evitcA:TESER

WOLdnahgiH

MORPEE

1201TAC ADS k2

2201TAC ADS k2

3201TAC IDW k2

4201TAC k2

5201TAC k2

6201TAC k2

7201TAC IDW k2

For supervisory circuits with embedded 16k EEPROM, please refer to the CAT1161, CAT1162 and CAT1163

data sheets.

3

Doc No. 3008, Rev. M

CAT1024, CAT1025

ABSOLUTE MAXIMUM RATINGS

Temperature Under Bias ................. –55°C to +125°C

Storage Temperature....................... –65°C to +150°C

Voltage on any Pin with

Respect to Ground

with Respect to Ground ............... –2.0V to +7.0V

V

CC

Package Power Dissipation

Capability (T

(1)

............ –2.0V to +VCC +2.0V

= 25°C) ................................... 1.0W

A

Stresses above those listed under “Absolute Maximum Ratings” may

cause permanent damage to the device. These are stress ratings only,

and functional operation of the device at these or any other conditions

outside of those listed in the operational sections of this specification

is not implied. Exposure to any absolute maximum rating for extended

periods may affect device performance and reliability.

Note:

(1) The minimum DC input voltage is –0.5V. During transitions,

inputs may undershoot to –2.0V for periods of less than 20 ns.

Maximum DC voltage on output pins is VCC +0.5V, which may

overshoot to V

(2) Output shorted for no more than one second. No more than

one output shorted at a time.

+2.0V for periods of less than 20 ns.

CC

Lead Soldering Temperature (10 secs) ............ 300°C

Output Short Circuit Current

(2)

........................ 100 mA

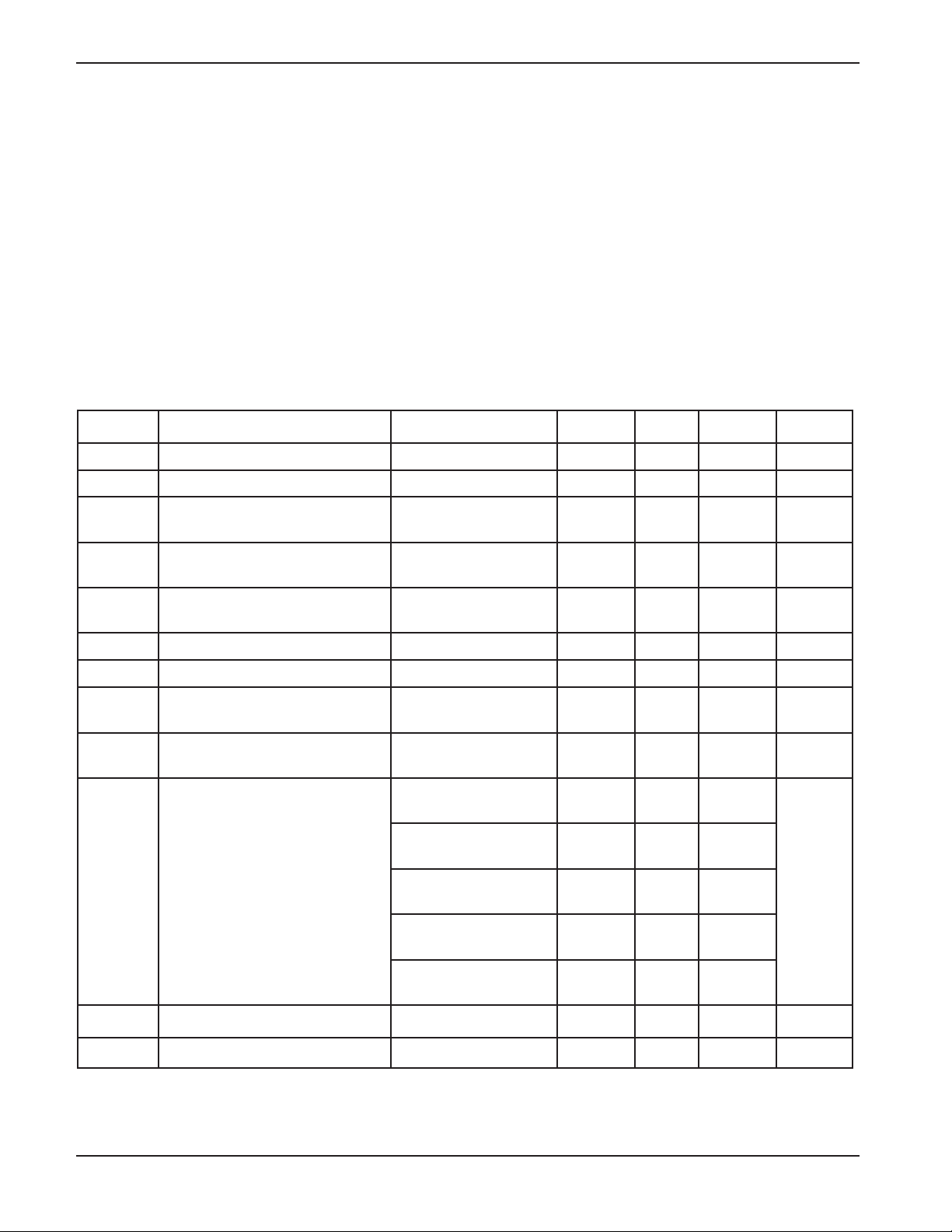

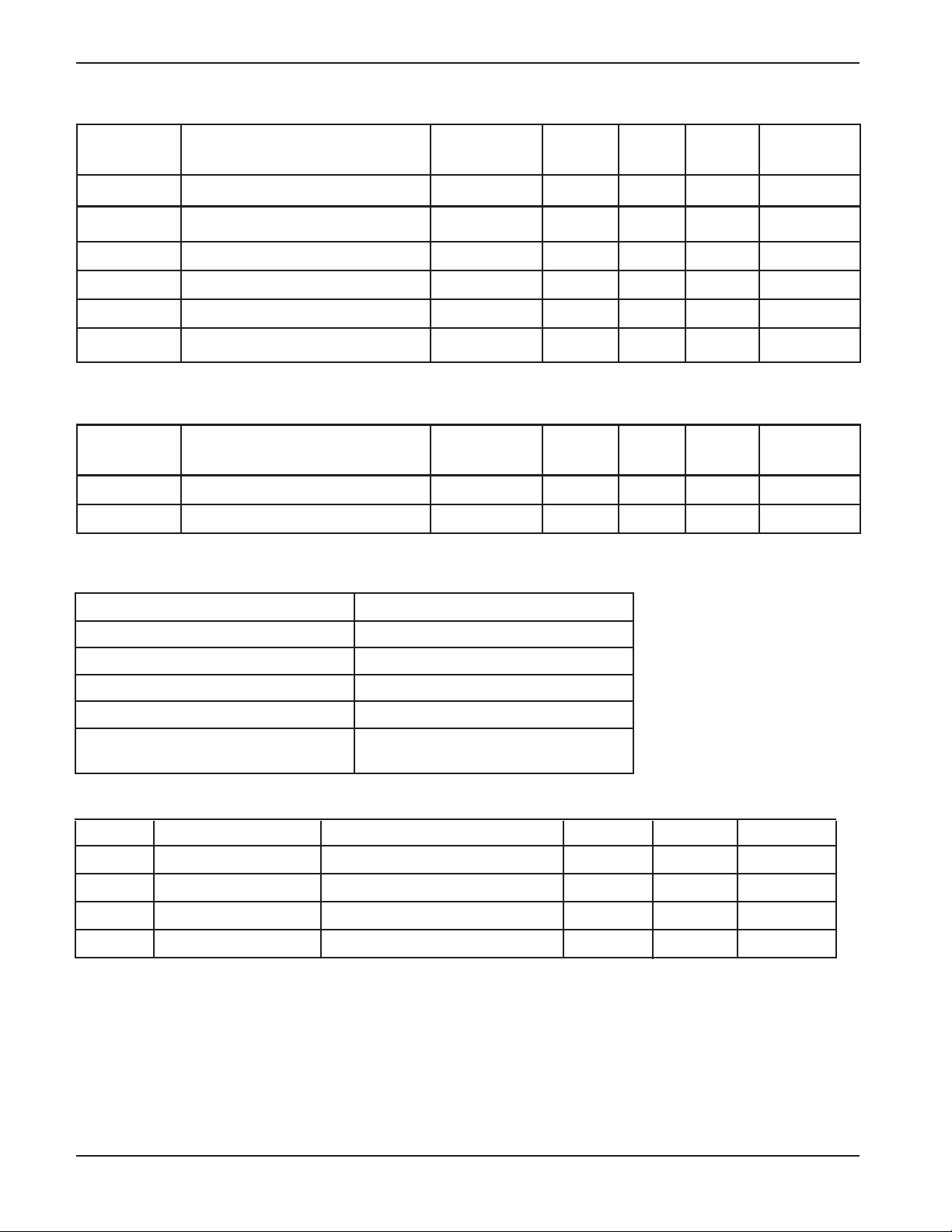

D.C. OPERATING CHARACTERISTICS

VCC = +3.0V to +5.5V and over the recommended temperature conditions unless otherwise specified.

lobmySretemaraPsnoitidnoCtseTniMpyTxaMstinU

I

IL

I

OL

I

1CC

I

2CC

I

BS

)1(

V

LI

)1(

V

HI

V

LO

V

HO

V

HT

V

DILAVR

)2(

V

TR

Notes:

1. VIL min and VIH max are reference values only and are not tested.

2. This parameter is tested initially and after a design or process change that affects the parameter. Not 100% tested.

,ADS( TESER )

)TESER(

tnerruCegakaeLtupnIV

tnerruCegakaeLtuptuOV

)etirW(tnerruCylppuSrewoP

)daeR(tnerruCylppuSrewoP

tnerruCybdnatS

NI

NI

f

LCS

V

CC

f

LCS

V

CC

V

NI

egatloVwoLtupnI5.0-ccVx3.0V

egatloVhgiHtupnIccVx7.05.0+ccVV

egatloVwoLtuptuO

egatloVhgiHtuptuO

dlohserhTteseR

VdilaVtuptuOteseR

CC

egatloV00.1V

I

LO

V

CC

I

HO

V

CC

V(

CC

V(

CC

V(

CC

V(

CC

V(

CC

siseretsyHdlohserhTteseR51Vm

ccVotDNG=2-01Aµ

ccVotDNG=01-01Aµ

zHk004=

V5.5=

zHk004=

V5.5=

,V5.5=ccV

ccVroDNG=

Am3=

V7.2=

Am4.0-=

V7.2=

54-x201TAC

)V5=

24-x201TAC

)V5=

03-x201TAC

)V3.3=

82-x201TAC

)V3.3=

52-x201TAC

)V3=

-ccV

57.0

05.457.4

52.405.4

00.351.3

58.200.3

55.207.2

3Am

1Am

04Aµ

4.0V

V

V

Doc. No. 3008, Rev. M

4

CAPACITANCE

TA = 25°C, f = 1.0 MHz, VCC = 5V

Symbol Test Test Conditions Max Units

(1)

C

C

OUT

(1)

IN

Output Capacitance V

= 0V 8 pF

OUT

Input Capacitance VIN = 0V 6 pF

AC CHARACTERISTICS

V

= 3.0V to 5.5V and over the recommended temperature conditions, unless otherwise specified.

CC

2

elcyCetirW&daeRyromeM

lobmySretemaraPniMxaMstinU

CAT1024, CAT1025

f

LCS

t

PS

t

WOL

t

HGIH

)1(

t

R

)1(

t

F

t

ATS;DH

t

ATS;US

t

TAD;DH

t

TAD;US

t

OTS;US

t

AA

t

HD

)1(

t

FUB

)3(

t

CW

ycneuqerFkcolC004zHk

ekipSretliFtupnI

)LCS,ADS(noisserppuS

001sn

doirePwoLkcolC3.1sµ

doirePhgiHkcolC6.0sµ

emiTesiRLCSdnaADS003sn

emiTllaFLCSdnaADS003sn

emiTdloHnoitidnoCtratS6.0sµ

emiTputeSnoitidnoCtratS

)tratSdetaepeRarof(

6.0sµ

emiTdloHtupnIataD0sn

emiTputeStupnIataD001sn

emiTputeSnoitidnoCpotS6.0sµ

dilaVtuOataDotwoLLCS009sn

emiTdloHtuOataD05sn

aerofeBeerFebtsumsuBehtemiT

tratSnaCnoissimsnarTweN

3.1sµ

)egaProetyB(emiTelcyCetirW5sm

Notes:

1. This parameter is characterized initially and after a design or process change that affects the parameter. Not 100% tested.

2. Test Conditions according to “AC Test Conditions” table.

3. The write cycle time is the time from a valid stop condition of a write sequence to the end of the internal program/erase cycle. During the write

cycle, the bus interface circuits are disabled, SDA is allowed to remain high and the device does not respond to its slave address.

5

Doc No. 3008, Rev. M

CAT1024, CAT1025

RESET CIRCUIT AC CHARACTERISTICS

lobmySretemaraP

t

TSRUP

t

DPR

t

HCTILG

V

HT

V

CC

hctilGRMytinummIhctilGteseRlaunaM1etoN001sn

t

WRM

t

DRM

GNIMITPU-REWOP

lobmySretemaraP

t

RUP

t

WUP

AC TEST CONDITIONS

tseT

snoitidnoC

niMpyTxaMstinU

tuoemiTteseR2etoN031002072sm

yaleDtuptuOTESERot3etoN5sµ

htdiWesluPtcejeRhctilG5,4etoN03sn

htdiWesluPRM1etoN5 sµ

yaleDtuptuOTESERottupnIRM1etoN1sµ

6,5

tseT

snoitidnoC

niMpyTxaMstinU

noitarepOdaeRotpU-rewoP 072sm

noitarepOetirWotpU-rewoP 072sm

retemaraPsnoitidnoCtseT

segatloVesluPtupnIV2.0

CC

V8.0ot

CC

semiTllaFdnaesiRtupnIsn01

segatloVecnerefeRtupnIV3.0

segatloVecnerefeRtuptuOV5.0

daoLtuptuO

C

L

V7.0,

CC

CC

CC

I:ecruoStnerruC

LO

;Am3=

Fp001=

RELIABILITY CHARACTERISTICS

Symbol Parameter Reference Test Method Min Max Units

(5)

N

END

(5)

T

DR

(5)

V

ZAP

(5)(7)

I

LTH

Notes:

1. Test Conditions according to “AC Test Conditions” table.

2. Power-up, Input Reference Voltage VCC = VTH, Reset Output Reference Voltage and Load according to “AC Test Conditions” Table

3. Power-Down, Input Reference Voltage VCC = VTH, Reset Output Reference Voltage and Load according to “AC Test Conditions” Table

4. VCC Glitch Reference Voltage = V

5. This parameter is characterized initially and after a design or process change that affects the parameter. Not 100% tested.

6. t

and t

PUR

7. Latch-up protection is provided for stresses up to 100mA on input and output pins from -1V to VCC + 1V.

Endurance MIL-STD-883, Test Method 1033 1,000,000 Cycles/Byte

Data Retention MIL-STD-883, Test Method 1008 100 Years

ESD Susceptibility MIL-STD-883, Test Method 3015 2000 Volts

Latch-Up JEDEC Standard 17 100 mA

; Based on characterization data

THmin

are the delays required from the time VCC is stable until the specified memory operation can be initiated.

PUW

Doc. No. 3008, Rev. M

6

Loading...

Loading...